NSC ADC0848MWC, ADC0848MDC, ADC0848CCJ, ADC0848BJ Datasheet

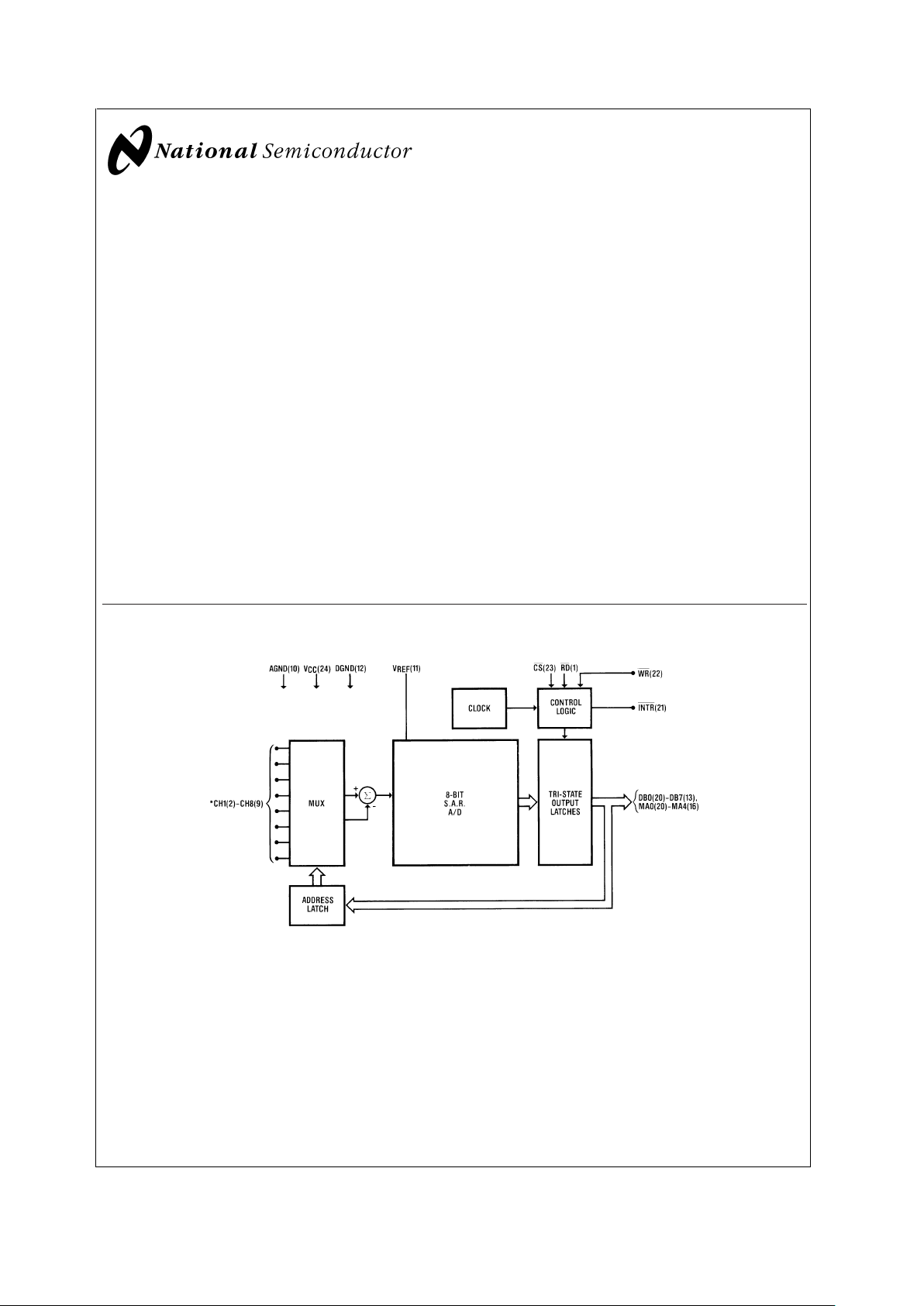

ADC0844/ADC0848

8-Bit µP Compatible A/D Converters with Multiplexer

Options

General Description

The ADC0844 and ADC0848 are CMOS 8-bit successive

approximation A/D converters with versatile analog input

multiplexers. The 4-channel or 8-channel multiplexers can

be software configured for single-ended, differential or

pseudo-differential modes of operation.

The differential mode provides low frequency input common

mode rejection and allows offsetting the analog range of the

converter. In addition, the A/D’s reference can be adjusted

enabling the conversion of reduced analog ranges with 8-bit

resolution.

The A/Ds are designed to operate from the control bus of a

wide variety of microprocessors. TRI-STATE output latches

that directly drive the data bus permit the A/Ds to be configured as memory locations or I/O devices to the microprocessor with no interface logic necessary.

Features

n Easy interface to all microprocessors

n Operates ratiometrically or with 5 V

DC

voltage reference

n No zero or full-scale adjust required

n 4-channel or 8-channel multiplexer with address logic

n Internal clock

n 0V to 5V input range with single 5V power supply

n 0.3" standard width 20-pin or 24-pin DIP

n 28 Pin Molded Chip Carrier Package

Key Specifications

n Resolution 8 Bits

n Total Unadjusted Error

±

1

⁄2LSB and±1 LSB

n Single Supply 5 V

DC

n Low Power 15 mW

n Conversion Time 40 µs

Block and Connection Diagrams

DS005016-1

*ADC0848 shown in DIP Package CH5-CH8 not included on the ADC0844

June 1999

ADC0844/ADC0848 8-Bit µP Compatible A/D Converters with Multiplexer Options

© 2001 National Semiconductor Corporation DS005016 www.national.com

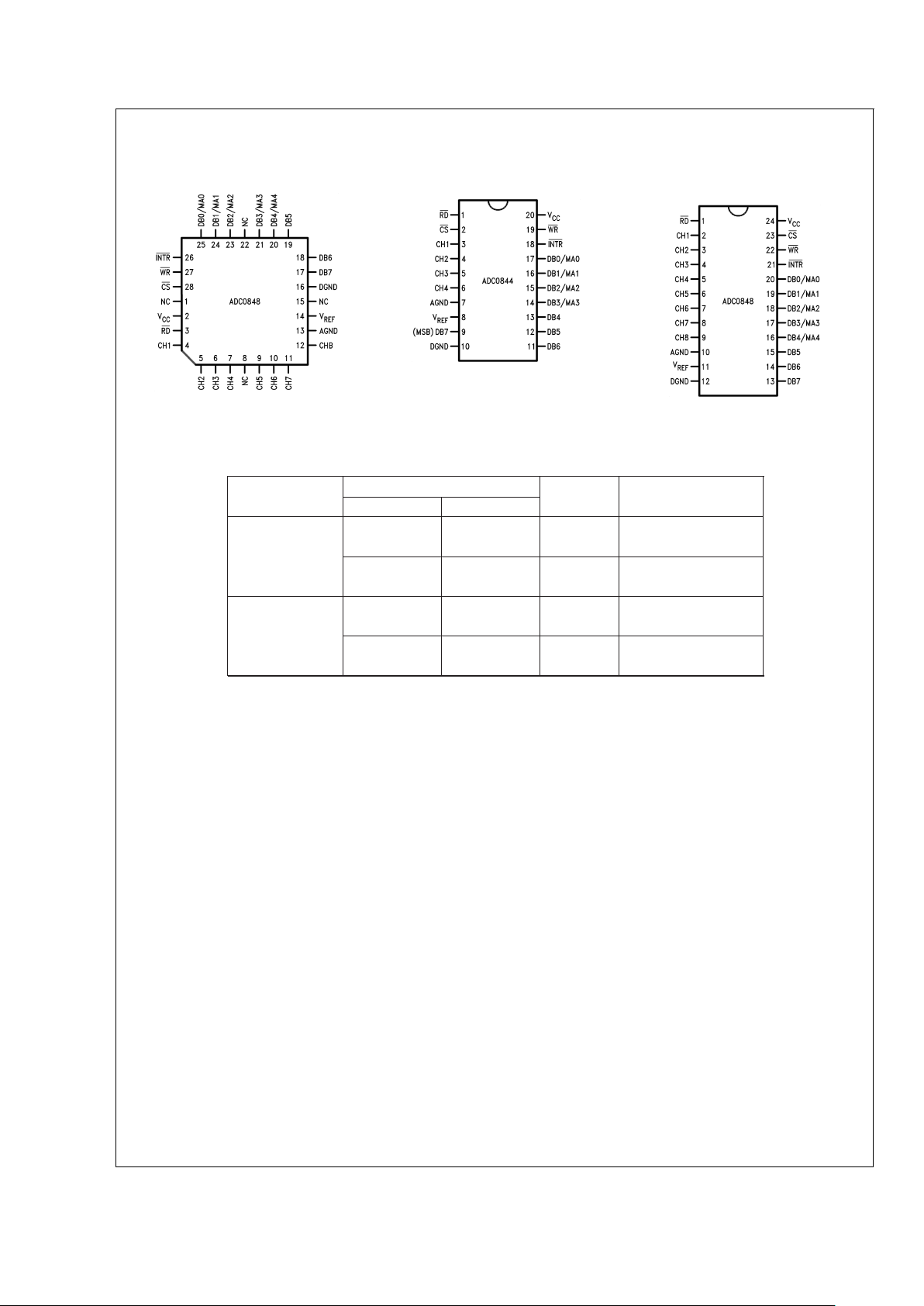

Block and Connection Diagrams (Continued)

Ordering Information

Temperature Total Unadjusted Error MUX Package

Range

±

1

⁄2LSB

±

1 LSB Channels Outline

ADC0844CCN 4 N20A

0˚C to +70˚C Molded Dip

ADC0848BCN 8 N24C

ADC0848CCN Molded Dip

−40˚C to +85˚C

ADC0844BCJ 4 J20A

ADC0844CCJ Cerdip

ADC0848BCV 8 V28A

ADC0848CCV Molded Chip Carrier

Molded Chip Carrier Package

DS005016-29

Top View

See Ordering Information

Dual-In-Line Package

DS005016-2

Top View

Dual-In-Line Package

DS005016-30

Top View

ADC0844/ADC0848

www.national.com 2

Absolute Maximum Ratings (Notes 1, 2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

) 6.5V

Voltage

Logic Control Inputs −0.3V to +15V

At Other Inputs and Outputs −0.3V to V

CC

+0.3V

Input Current at Any Pin (Note 3) 5 mA

Package Input Current (Note 3) 20 mA

Storage Temperature −65˚C to +150˚C

Package Dissipation at T

A

=25˚C 875 mW

ESD Susceptibility (Note 4) 800V

Lead Temperature

(Soldering, 10 seconds)

Dual-In-Line Package (Plastic) 260˚C

Dual-In-Line Package (Ceramic) 300˚C

Molded Chip Carrier Package

Vapor Phase (60 seconds) 215˚C

Infrared (15 seconds) 220˚C

Operating Conditions (Notes 1, 2)

Supply Voltage (V

CC

) 4.5 VDCto 6.0 V

DC

Temperature Range T

MIN≤TA≤TMAX

ADC0844CCN, ADC0848BCN, 0˚C≤TA≤70˚C

ADC0848CCN

ADC0844BCJ, ADC0844CCJ, −40˚C≤T

A

≤85˚C

ADC0848BCV, ADC0848CCV

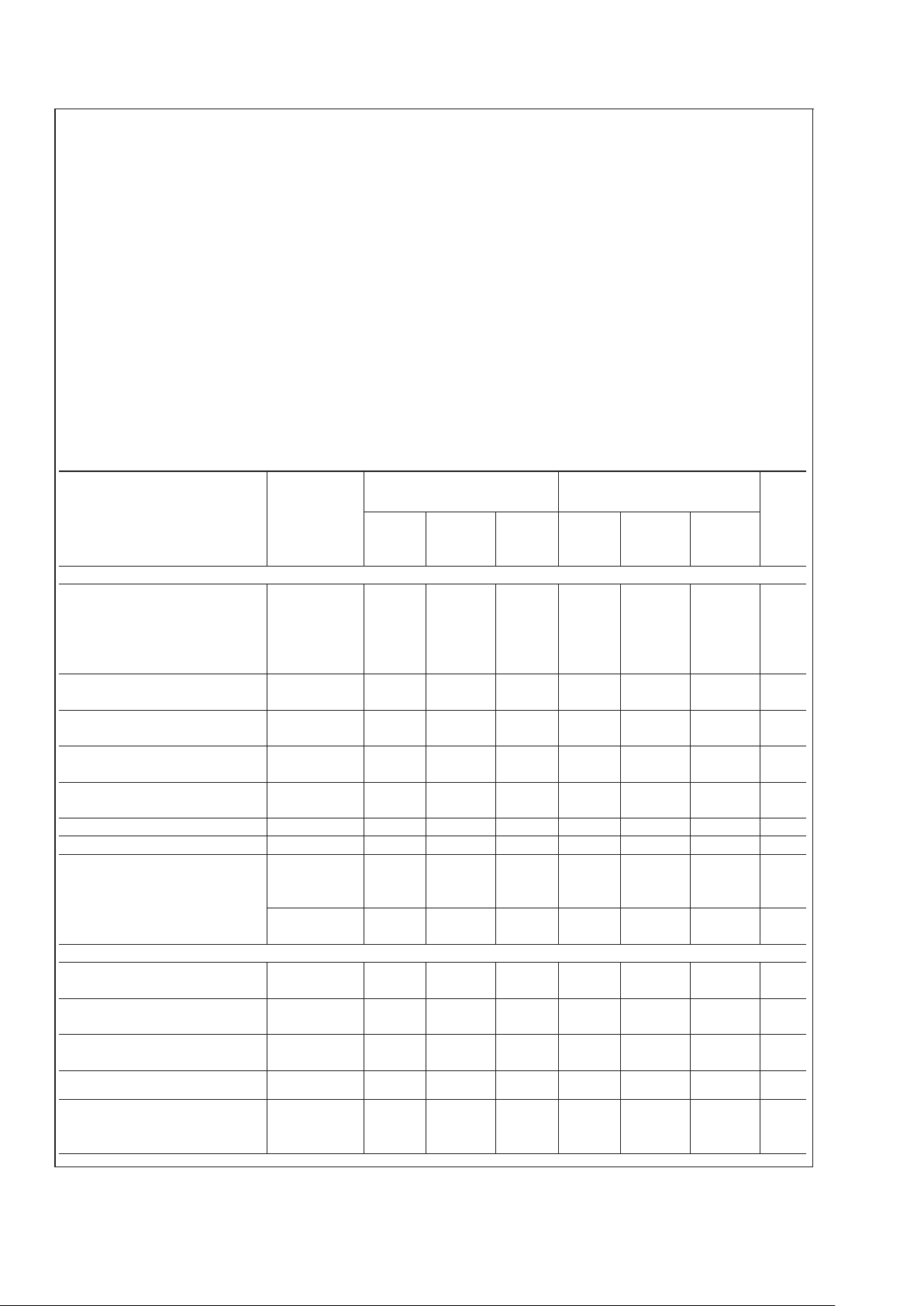

Electrical Characteristics

The following specifications apply for VCC=5VDCunless otherwise specified.Boldface limits apply from T

MIN

to T

MAX

; all

other limits T

A=Tj

= 25˚C.

Parameter Conditions

ADC0844BCJ

ADC0844CCJ

ADC0844CCN

ADC0848BCN, ADC0848CCN

ADC0848BCV, ADC0848CCV

Limit

Units

Typ Tested Design Typ Tested Design

(Note 5) Limit Limit (Note 5) Limit Limit

(Note 6) (Note 7) (Note 6) (Note 7)

CONVERTER AND MULTIPLEXER CHARACTERISTICS

Maximum Total V

REF

=5.00 V

DC

Unadjusted Error (Note 8)

ADC0844BCN, ADC0848BCN, BCV

±

1

⁄

2

±

1

⁄

2

LSB

ADC0844CCN, ADC0848CCN, CCV

±

1

±

1 LSB

ADC0844CCJ

±

1 LSB

Minimum Reference 2.4 1.1 2.4 1.2 1.1 kΩ

Input Resistance

Maximum Reference 2.4 5.9 2.4 5.4 5.9 kΩ

Input Resistance

Maximum Common-Mode (Note 9) V

CC

+0.05 VCC+0.05 VCC+0.05 V

Input Voltage

Minimum Common-Mode (Note 9) GND−0.05 GND−0.05 GND−0.05 V

Input Voltage

DC Common-Mode Error Differential Mode

±

1/16

±

1

⁄

4

±

1/16

±

1

⁄

4

±

1

⁄

4

LSB

Power Supply Sensitivity V

CC

=5V±5%

±

1/16

±

1

⁄

8

±

1/16

±

1

⁄

8

±

1

⁄

8

LSB

Off Channel Leakage (Note 10)

Current On Channel=5V, −1 −0.1 −1 µA

Off Channel=0V

On Channel=0V, 1 0.1 1 µA

Off Channel=5V

DIGITAL AND DC CHARACTERISTICS

V

IN(1)

, Logical “1” Input VCC=5.25V 2.0 2.0 2.0 V

Voltage (Min)

V

IN(0)

, Logical “0” Input VCC=4.75V 0.8 0.8 0.8 V

Voltage (Max)

I

IN(1)

, Logical “1” Input VIN=5.0V 0.005 1 0.005 1 µA

Current (Max)

I

IN(0)

, Logical “0” Input

Current (Max)

VIN=0V −0.005 −1 −0.005 −1 µA

V

OUT(1)

, Logical “1” VCC=4.75V

Output Voltage (Min) I

OUT

=−360 µA 2.4 2.8 2.4 V

I

OUT

=−10 µA 4.5 4.6 4.5 V

ADC0844/ADC0848

www.national.com3

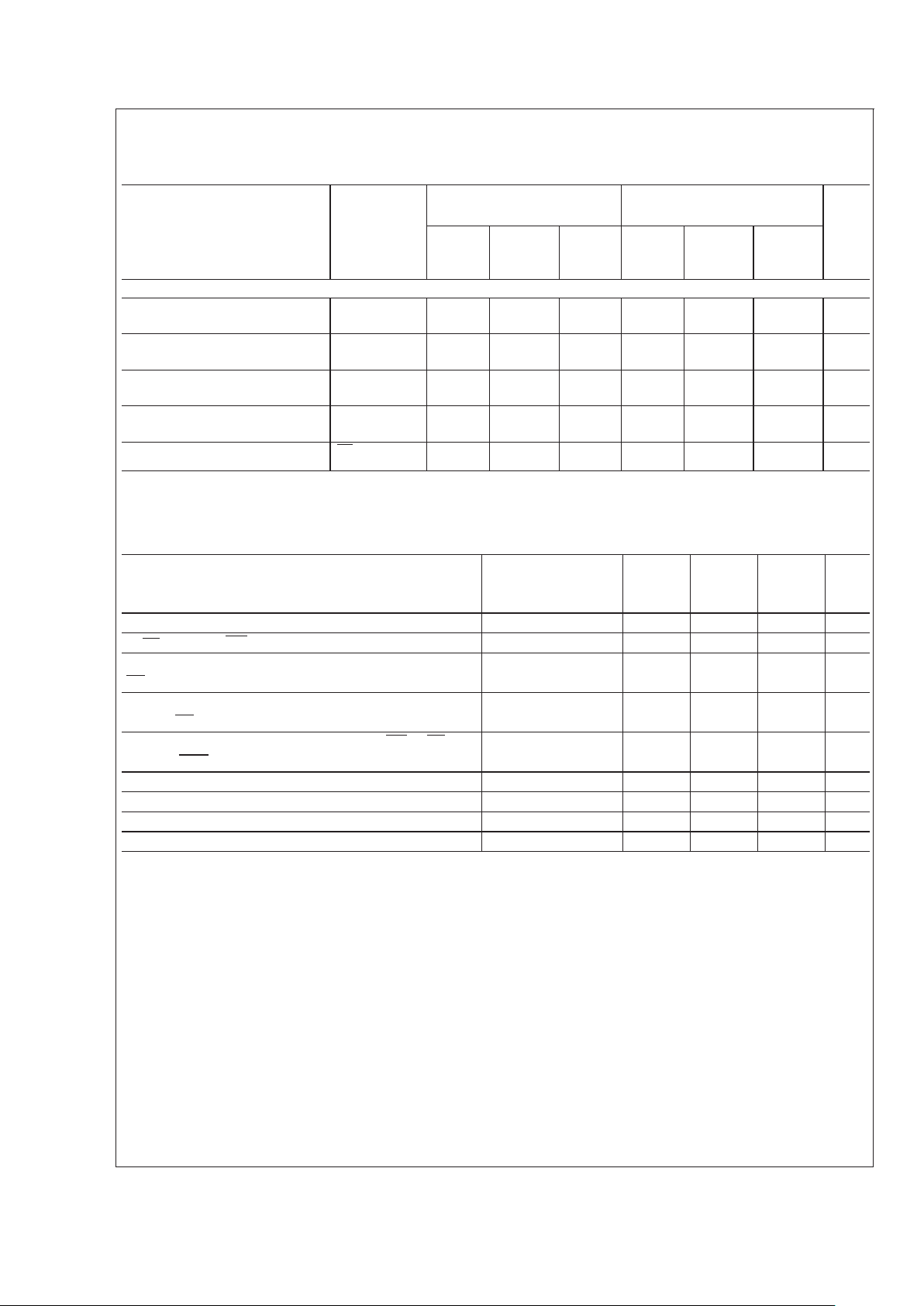

Electrical Characteristics (Continued)

The following specifications apply for VCC=5VDCunless otherwise specified.Boldface limits apply from T

MIN

to T

MAX

; all

other limits T

A=Tj

= 25˚C.

Parameter Conditions

ADC0844BCJ

ADC0844CCJ

ADC0844CCN

ADC0848BCN, ADC0848CCN

ADC0848BCV, ADC0848CCV

Limit

Units

Typ Tested Design Typ Tested Design

(Note 5) Limit Limit (Note 5) Limit Limit

(Note 6) (Note 7) (Note 6) (Note 7)

DIGITAL AND DC CHARACTERISTICS

V

OUT(0)

, Logical “0” VCC=4.75V 0.4 0.34 0.4 V

Output Voltage (Max) I

OUT

=1.6 mA

I

OUT

, TRI-STATE Output V

OUT

=0V −0.01 −3 −0.01 −0.3 −3 µA

Current (Max) V

OUT

=5V 0.01 3 0.01 0.3 3 µA

I

SOURCE

, Output Source V

OUT

=0V −14 −6.5 −14 −7.5 −6.5 mA

Current (Min)

I

SINK

, Output Sink V

OUT=VCC

16 8.0 16 9.0 8.0 mA

Current (Min)

I

CC

, Supply Current (Max) CS =1, V

REF

Open

1 2.5 1 2.3 2.5 mA

AC Electrical Characteristics

The following specifications apply for VCC=5VDC,tr=tf= 10 ns unless otherwise specified. Boldface limits apply from T

MIN

to T

MAX

; all other limits TA=Tj= 25˚C.

Tested Design

Parameter Conditions Typ Limit Limit Units

(Note 5) (Note 6) (Note 7)

t

C

, Maximum Conversion Time (See Graph) 30 40 60 µs

t

W(WR)

, Minimum WR Pulse Width (Note 11) 50 150 ns

t

ACC

, Maximum Access Time (Delay from Falling Edge of CL= 100 pF 145 225 ns

RD to Output Data Valid)

(Note 11)

t

1H,t0H

, TRI-STATE Control (Maximum Delay from Rising CL= 10 pF, RL= 10k 125 200 ns

Edge of RD to Hi-Z State)

(Note 11)

t

WI,tRI

, Maximum Delay from Falling Edge of WR or RD to (Note 11) 200 400 ns

Reset of INTR

tDS, Minimum Data Set-Up Time (Note 11) 50 100 ns

t

DH

, Minimum Data Hold Time (Note 11) 0 50 ns

C

IN

, Capacitance of Logic Inputs 5 pF

C

OUT

, Capacitance of Logic Outputs 5 pF

Note 1: Absolute Maximum Ratingsindicate limits beyond which damageto the device may occur. DC andAC electrical specificationsdo not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to the ground pins.

Note 3: When the input voltage (V

IN

) at any pin exceeds the power supply rails (V

IN

<

V−or V

IN

>

V+) the absolute value of the current at that pinshould be limited

to 5 mA or less. The 20 mA package input current limits the number of pins that can exceed the power supply boundaries witha5mAcurrent limit to four.

Note 4: Human body model, 100 pF discharged through a 1.5 kΩ resistor.

Note 5: Typicals are at 25˚C and represent most likely parametric norm.

Note 6: Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 7: Design limits are guaranteed by not 100% tested. These limits are not used to calculate outgoing quality levels.

Note 8: Total unadjusted error includes offset, full-scale, linearity, and multiplexer error.

Note 9: For V

IN

(−) ≥ VIN(+) the digital outputcode will be 0000 0000. Twoon-chip diodes are tied to each analog input, which will forward-conduct for analog input

voltages one diode drop below ground or one diode drop greaterthan V

CC

supply.Be careful during testingat low VCClevels (4.5V), as high level analog inputs (5V)

can cause this input diode to conduct, especially at elevated temperatures, and cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias

of either diode. This means that as long as the analog V

IN

does not exceed the supply voltage by more than 50 mV, the output code will be correct. To achieve an

absolute 0 V

DC

to5VDCinput voltage range will therefore require a minimum supply voltage of4.950 VDCover temperature variations, initial tolerance and loading.

Note 10: Off channel leakage current is measured after the channel selection.

Note 11: The temperature coefficient is 0.3%/˚C.

ADC0844/ADC0848

www.national.com 4

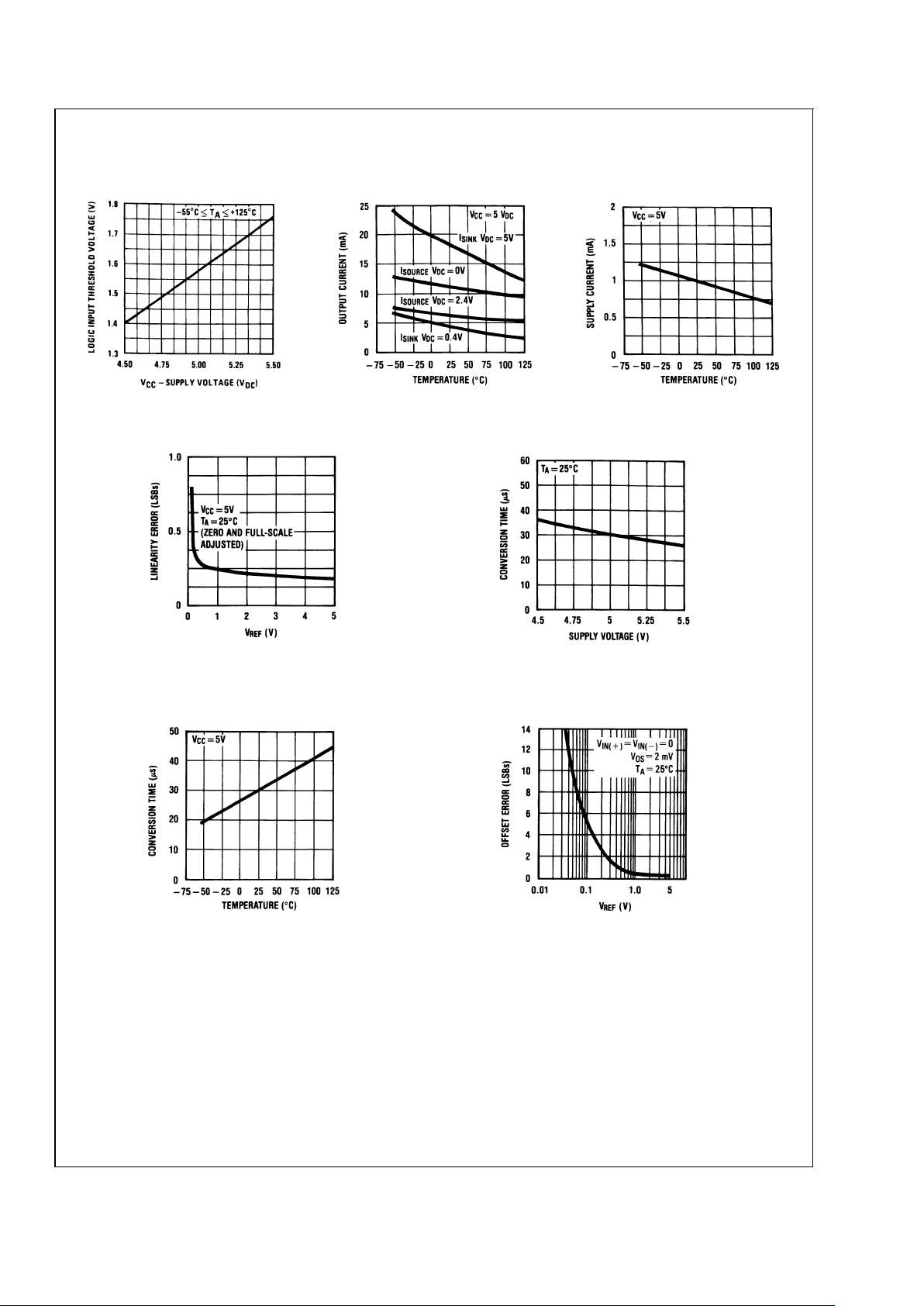

Typical Performance Characteristics

Logic Input Threshold

Voltage vs Supply Voltage

DS005016-31

Output Current vs

Temperature

DS005016-32

Power Supply Current vs

Temperature

DS005016-33

Linearity Error vs V

REF

DS005016-34

Conversion Time vs V

SUPPLY

DS005016-35

Conversion Time vs

Temperature

DS005016-36

Unadjusted Offset Error vs

V

REF

Voltage

DS005016-37

ADC0844/ADC0848

www.national.com5

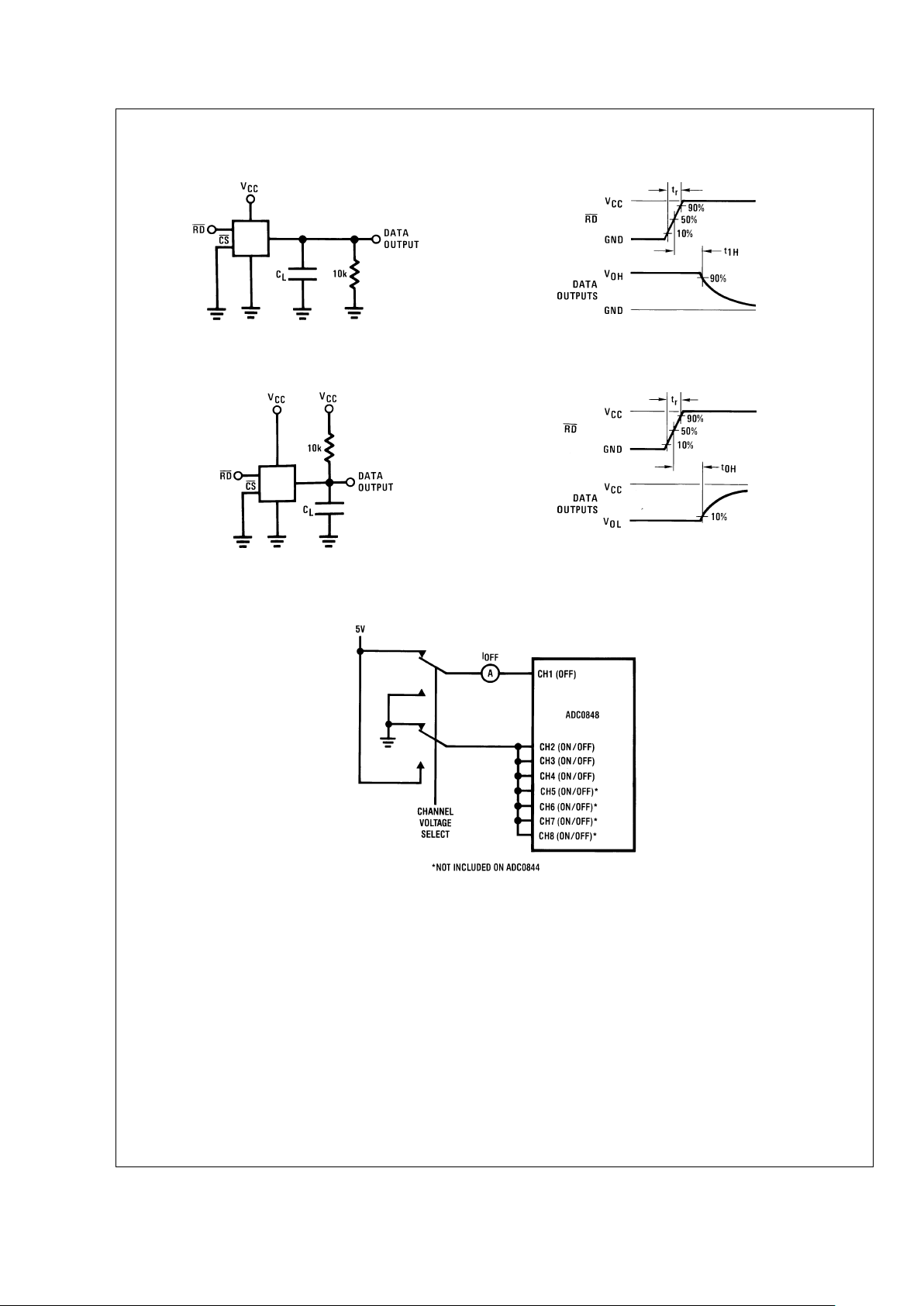

TRI-STATE Test Circuits and Waveforms

Leakage Current Test Circuit

t

1H

DS005016-4

t1H,CL=10pF

DS005016-5

tr=20ns

t

0H

DS005016-6

t0H,CL=10pF

DS005016-7

tr=20ns

DS005016-8

ADC0844/ADC0848

www.national.com 6

Loading...

Loading...