NSC ADC08138CIN, ADC08138BIWMX, ADC08138BIWM, ADC08138BIN, ADC08134CIN Datasheet

...

ADC08131/ADC08134/ADC08138

8-Bit High-Speed Serial I/O A/D Converters with

Multiplexer Options, Voltage Reference, and Track/Hold

Function

General Description

The ADC08131/ADC08134/ADC08138 are 8-bit successive

approximation A/D converters with serial I/O and configurable input multiplexers with up to 8 channels. The serial

I/O is configured to comply with the NSC MICROWIRE

™

serial data exchange standard for easy interface to the

COPS

™

family of controllers, and can easily interface with

standard shift registers or microprocessors.

All three devices providea 2.5V band-gap derived reference

with guaranteed performance over temperature.

Atrack/hold function allows the analog voltage at the positive

input to vary during the actual A/D conversion.

The analog inputs can be configured to operate in various

combinations of single-ended, differential, or

pseudo-differential modes. In addition, input voltage spans

as small as 1V can be accommodated.

Applications

n Digitizing automotive sensors

n Process control/monitoring

n Remote sensing in noisy environments

n Embedded diagnostics

Features

n Serial digital data link requires few I/O pins

n Analog input track/hold function

n 4- or 8-channel input multiplexer options with address

logic

n On-chip 2.5V band-gap reference (

±

2% over

temperature guaranteed)

n No zero or full scale adjustment required

n TTL/CMOS input/output compatible

n 0V to 5V analog input range with single 5V power

supply

Key Specifications

n Resolution 8 Bits

n Conversion time (f

C

= 1 MHz) 8 µs (Max)

n Power dissipation 20 mW (Max)

n Single supply 5 V

DC

(±5%)

n Total unadjusted error

±

1

⁄2LSB and±1 LSB

n Linearity Error (V

REF

= 2.5V)

±

1

⁄2LSB

n No missing codes (over temperature)

n On-board Reference +2.5V

±

1.5% (Max)

Ordering Information

Industrial Package

(−40˚C ≤ T

A

≤ +85˚C)

ADC08131CIWM M14B

ADC08134CIWM M14B

ADC08138CIWM M20B

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

COPS

™

microcontrollers and MICROWIRE™are trademarks of National Semiconductor Corporation.

June 1999

ADC08131/ADC08134/ADC08138 8-Bit High-Speed Serial I/O A/D Converters with Multiplexer

Options, Voltage Reference, and Track/Hold Function

© 2001 National Semiconductor Corporation DS010749 www.national.com

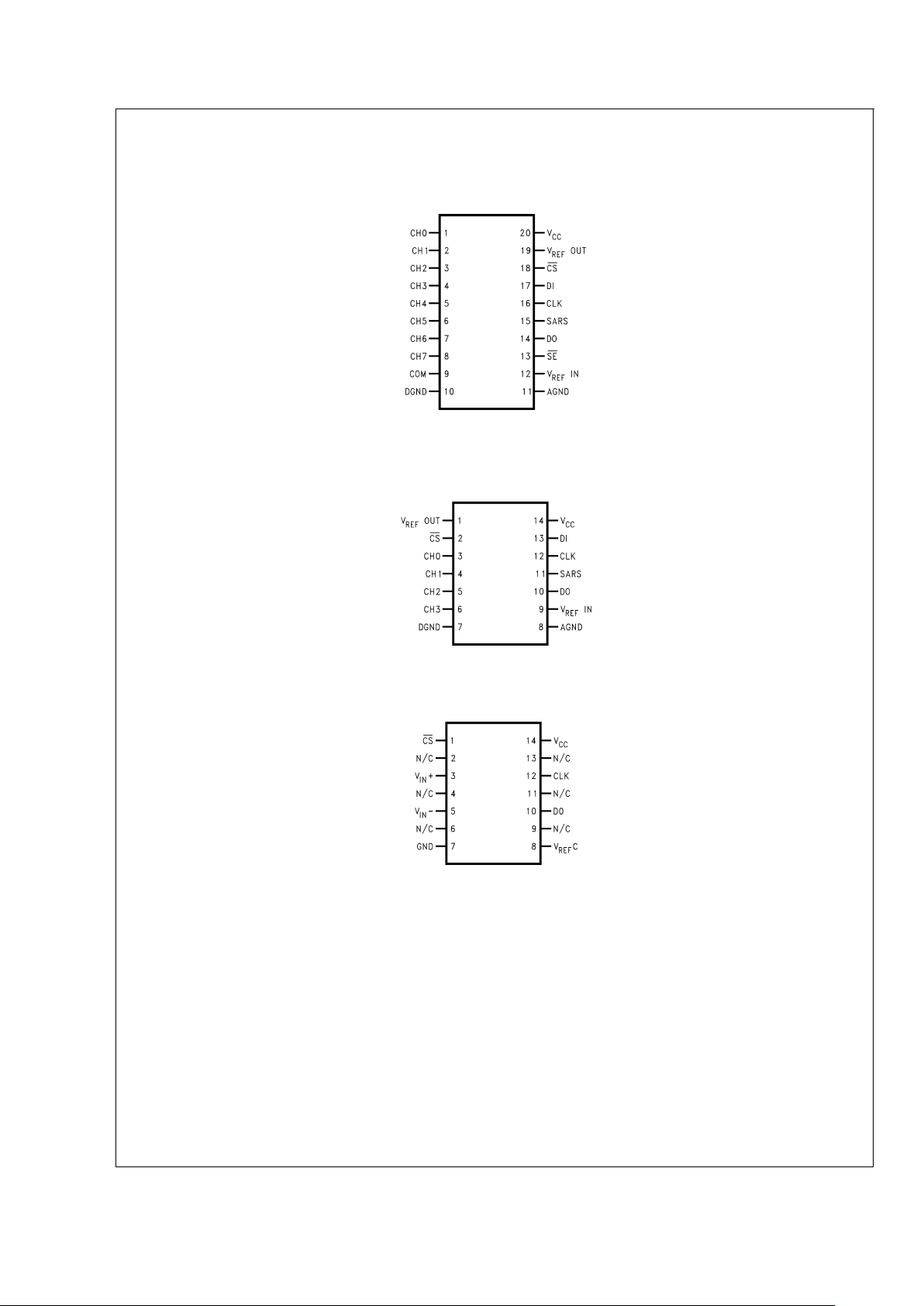

Connection Diagrams

ADC08138CIWM

Small Outline

Packages

DS010749-2

ADC08134CIWM

Small Outline

Packages

DS010749-3

ADC08131CIWM

Small Outline Package

DS010749-4

ADC08131/ADC08134/ADC08138

www.national.com 2

Absolute Maximum Ratings (Notes 1, 3)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

Supply Voltage (V

CC

) 6.5V

Voltage at Inputs and Outputs −0.3V to V

CC

+ 0.3V

Input Current at Any Pin (Note 4)

±

5mA

Package Input Current (Note 4)

±

20 mA

Power Dissipation at T

A

= 25˚C

(Note 5) 800 mW

ESD Susceptibility (Note 6) 1500V

Soldering Information

N Package (10 sec.)

SO Package:

Vapor Phase (60 sec.)

Infrared (15 sec.) (Note 7)

260˚C

215˚C

220˚C

Storage Temperature −65˚C to +150˚C

Operating Ratings (Notes 2, 3)

Temperature Range T

MIN

≤ TA≤ T

MAX

−40˚C ≤ TA≤ +85˚C

Supply Voltage (V

CC

) 4.5 VDCto 6.3 V

DC

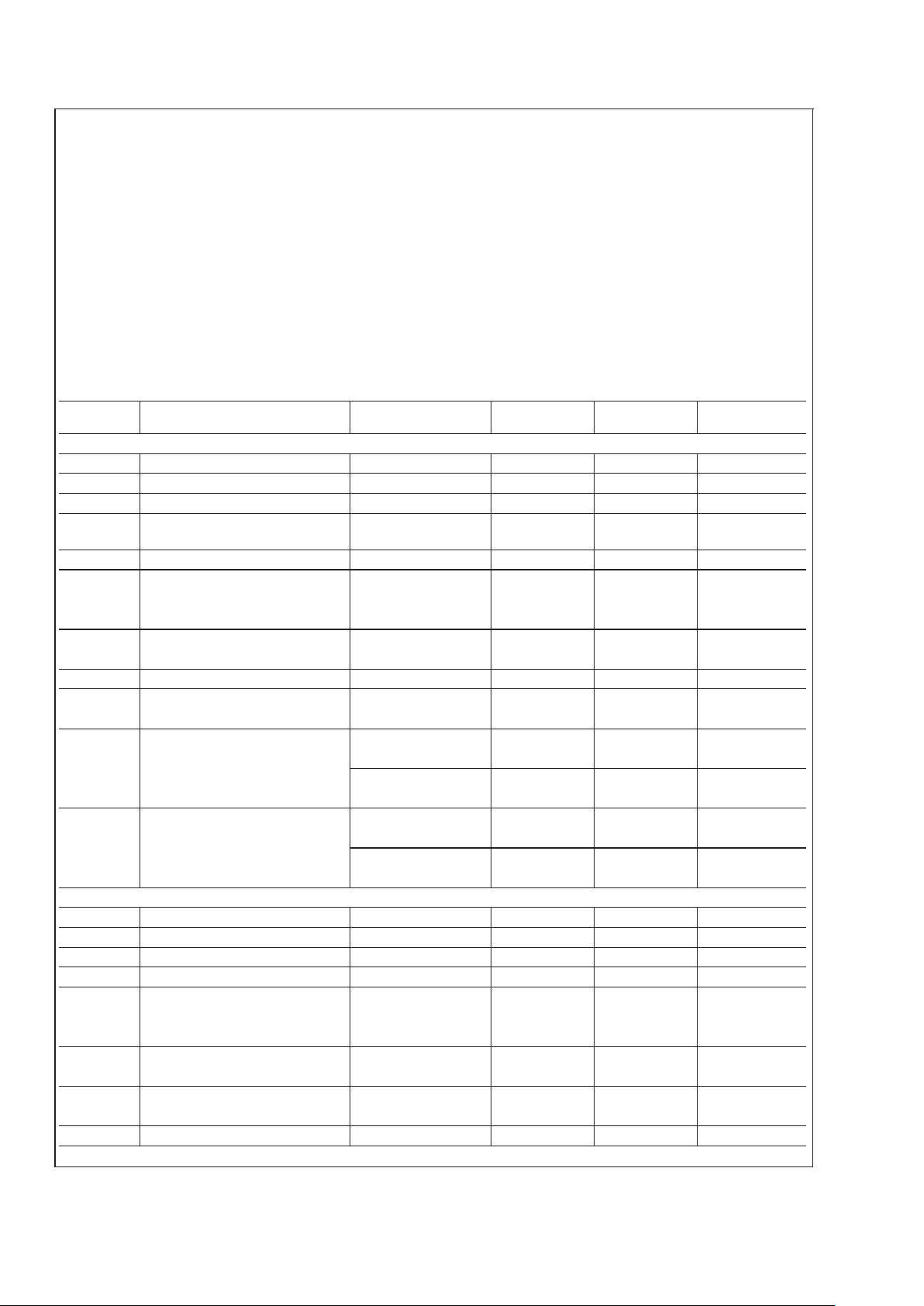

Electrical Characteristics

The following specifications apply for VCC=+5VDC,V

REF

= +2.5 VDCand f

CLK

= 1 MHz unless otherwise specified. Boldface

limits apply for T

A=TJ=TMIN

to T

MAX

; all other limits TA=TJ= 25˚C.

Symbol Parameter Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

CONVERTER AND MULTIPLEXER CHARACTERISTICS

Linearity Error V

REF

= +2.5 V

DC

±

1 LSB (max)

Full Scale Error V

REF

= +2.5 V

DC

±

1 LSB (max)

Zero Error V

REF

= +2.5 V

DC

±

1 LSB (max)

Total Unadjusted Error

V

REF

=+5V

DC

(Note 10)

±

1 LSB (max)

Differential Linearity V

REF

= +2.5 V

DC

8 Bits (min)

R

REF

Reference Input Resistance (Note 11)

3.5 kΩ

1.3 kΩ (min)

6.0 kΩ (max)

V

IN

Analog Input Voltage (Note 12)

(V

CC

+ 0.05) V (max)

(GND − 0.05) V (min)

DC Common-Mode Error V

REF

= 2.5 V

DC

±

1

⁄

2

LSB (max)

Power Supply Sensitivity

V

CC

= +5V±5%,

±

1

⁄

4

LSB (max)

V

REF

= +2.5 V

DC

On Channel Leakage Current

(Note 13)

On Channel = 5V, 0.2

µA (max)

Off Channel = 0V 1

On Channel = 0V, −0.2

µA (max)

Off Channel = 5V −1

Off Channel Leakage Current

(Note 13)

On Channel = 5V, −0.2

µA (max)

Off Channel = 0V −1

On Channel = 0V, 0.2

µA (max)

Off Channel = 5V 1

DIGITAL AND DC CHARACTERISTICS

V

IN(1)

Logical “1” Input Voltage VCC= 5.25V 2.0 V (min)

V

IN(0)

Logical “0” Input Voltage VCC= 4.75V 0.8 V (max)

I

IN(1)

Logical “1” Input Current VIN= 5.0V 1 µA (max)

I

IN(0)

Logical “0” Input Current VIN=0V −1 µA (max)

V

CC

= 4.75V:

V

OUT(1)

Logical “1” Output Voltage I

OUT

= −360 µA 2.4 V (min)

I

OUT

= −10 µA 4.5 V (min)

V

OUT(0)

Logical “0” Output Voltage

V

CC

= 4.75V 0.4 V (max)

I

OUT

= 1.6 mA

I

OUT

TRI-STATE®Output Current

V

OUT

=0V −3.0 µA (max)

V

OUT

=5V 3.0 µA (max)

I

SOURCE

Output Source Current V

OUT

=0V −6.5 mA (min)

ADC08131/ADC08134/ADC08138

www.national.com3

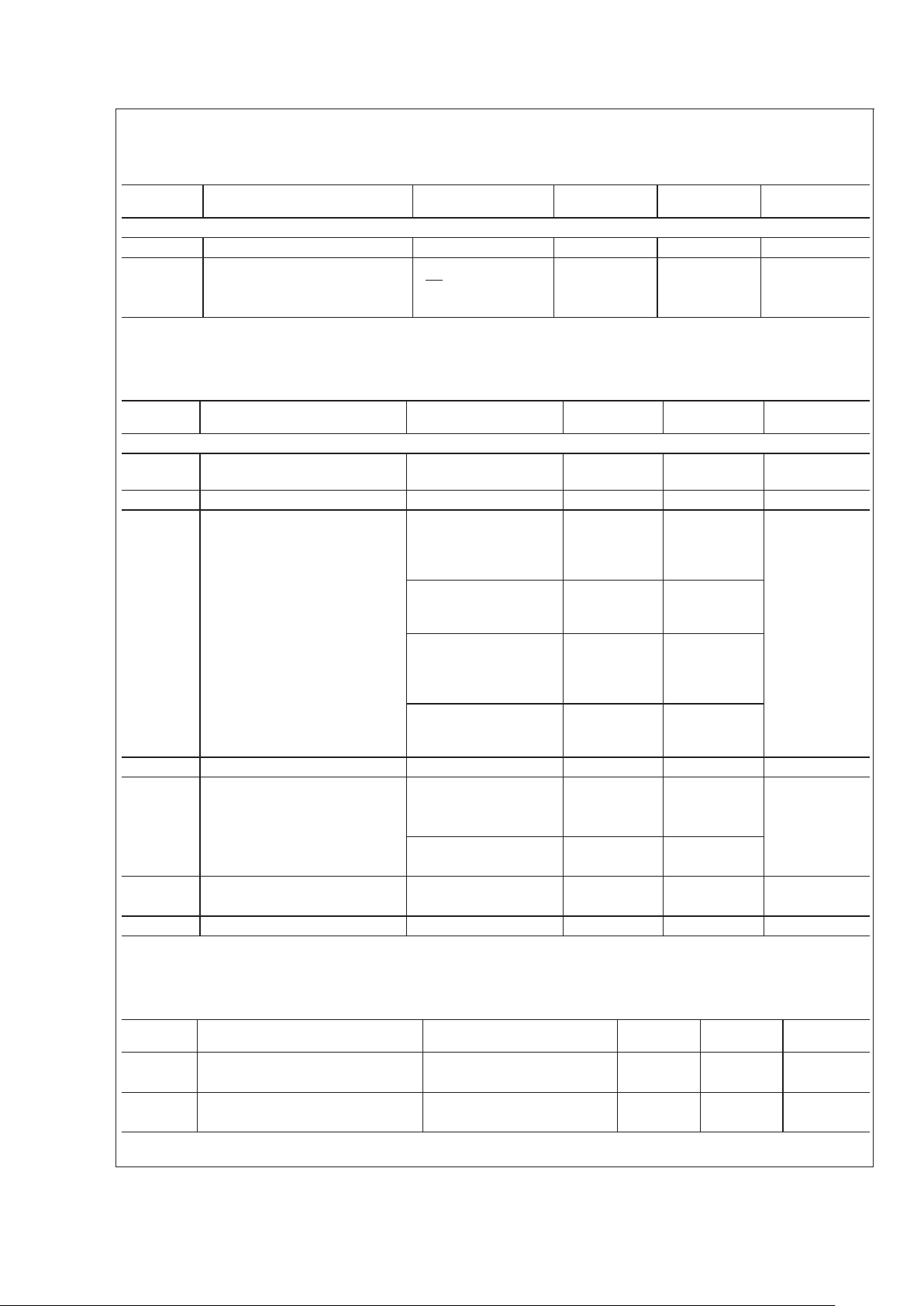

Electrical Characteristics (Continued)

The following specifications apply for VCC=+5VDC,V

REF

= +2.5 VDCand f

CLK

= 1 MHz unless otherwise specified. Boldface

limits apply for T

A=TJ=TMIN

to T

MAX

; all other limits TA=TJ= 25˚C.

Symbol Parameter Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

DIGITAL AND DC CHARACTERISTICS

I

SINK

Output Sink Current V

OUT=VCC

8.0 mA (min)

Supply Current

I

CC

ADC08134, ADC08138 CS = HIGH 3.0 mA (max)

ADC08131 (Note 16) 6.0 mA (max)

Electrical Characteristics

The following specifications apply for VCC=+5VDC, and f

CLK

= 1 MHz unless otherwise specified. Boldface limits apply for

T

A=TJ=TMIN

to T

MAX

; all other limits TA=TJ= 25˚C.

Symbol Parameter Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

REFERENCE CHARACTERISTICS

V

REF

OUT Output Voltage DC08134, ADC08138

2.5

±

2%

2.5

±

1.5% V

∆V

REF

/∆T Temperature Coefficient 40 ppm/˚C

∆V

REF

/∆ILLoad Regulation (Note 17)

Sourcing

(0 ≤ I

L

≤ +4 mA)

ADC08134,

ADC08138

0.003 0.1

%/mA

(max)

Sourcing

(0 ≤ I

L

≤ +2 mA)

ADC08131

0.003 0.1

Sinking

(−1 ≤ I

L

≤ 0 mA)

ADC08134,

ADC08138

0.2 0.5

Sinking

(−1 ≤ I

L

≤ 0 mA)

ADC08131

0.2 0.5

Line Regulation 4.75V ≤ V

CC

≤ 5.25V 0.5 6 mV (max)

V

REF

=0V

mA

(max)

ADC08134, 8 25

I

SC

Short Circuit Current ADC08138

V

REF

=0V

8 25

ADC08131

T

SU

Start-Up Time

V

CC

:0V→5V

20 ms

C

L

= 100 µF

∆V

REF

/∆t Long Term Stability 200 ppm/1 kHr

Electrical Characteristics

The following specifications apply for VCC=+5VDC,V

REF

= +2.5 VDCand tr=tf= 20 ns unless otherwise specified. Boldface

limits apply for T

A=TJ=TMIN

to T

MAX

; all other limits TA=TJ= 25˚C.

Symbol Parameter Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

f

CLK

Clock Frequency

10 kHz (min)

1 MHz (max)

Clock Duty Cycle 40 % (min)

(Note 14) 60 % (max)

ADC08131/ADC08134/ADC08138

www.national.com 4

Electrical Characteristics (Continued)

The following specifications apply for VCC=+5VDC,V

REF

= +2.5 VDCand tr=tf= 20 ns unless otherwise specified. Boldface

limits apply for T

A=TJ=TMIN

to T

MAX

; all other limits TA=TJ= 25˚C.

Symbol Parameter Conditions

Typical

(Note 8)

Limits

(Note 9)

Units

(Limits)

T

C

Conversion Time (Not Including

f

CLK

= 1 MHz

8 1/f

CLK

(max)

MUX Addressing Time) 8 µs (max)

t

CA

Acquisition Time

1

⁄

2

1/f

CLK

(max)

t

SELECT

CLK High while CS is High 50 ns

t

SET-UP

CS Falling Edge or Data Input

25 ns (min)

Valid to CLK Rising Edge

t

HOLD

Data Input Valid after CLK Rising

Edge

20 ns (min)

t

pd1,tpd0

CLK Falling Edge to Output Data

Valid (Note 15)

C

L

= 100 pF:

Data MSB First 250 ns (max)

Data LSB First 200 ns (max)

t

1H,t0H

TRI-STATE Delay from Rising Edge

of CS to Data Output and SARS

Hi-Z

C

L

= 10 pF, RL=10kΩ

50 ns

(see TRI-STATE Test Circuits)

C

L

= 100 pF, RL=2kΩ 180 ns (max)

C

IN

Capacitance of Logic Inputs 5 pF

C

OUT

Capacitance of Logic Outputs 5 pF

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits. For guaranteed

specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance

characteristics may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to AGND = DGND = 0 V

DC

, unless otherwise specified.

Note 4: When the input voltage (V

IN

) at any pin exceeds the power supplies (V

IN

<

(AGND or DGND) or V

IN

>

AVCC) the current at that pin should be limited to

5 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four

pins.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

JMAX

, θJAand the ambient temperature, TA. The maximum

allowable power dissipation at any temperature is P

D

=(T

JMAX−TA

)/θJAor the number given in the Absolute Maximum Ratings, whichever is lower. For these

devices T

JMAX

= 125˚C. The typical thermal resistances (θJA) of these parts when board mounted for the ADC 08131 and the ADC08134 is 140˚C/W and 91˚C/W

for the ADC08138.

Note 6: Human body model, 100 pF capacitor discharged through a 1.5 kΩ resistor.

Note 7: See AN450 “Surface Mounting Methods and Their Effect on Product Reliability” or Linear Data Book section “Surface Mount” for other methods of soldering

surface mount devices.

Note 8: Typicals are at T

J

= 25˚C and represent the most likely parametric norm.

Note 9: Guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 10: Total unadjusted error includes zero, full-scale, linearity, and multiplexer error. Total unadjusted error with V

REF

= +5V only applies to the ADC08134 and

ADC08138. See (Note 16).

Note 11: Cannot be tested for the ADC08131.

Note 12: For V

IN(−)

≥ V

IN(+)

the digital code will be 0000 0000. Two on-chip diodes are tied to each analog input (see Block Diagram) which will forward-conduct

for analog input voltages one diode drop below ground or one diode drop greater than V

CC

supply. During testing at low VCClevels (e.g., 4.5V), high level analog

inputs (e.g., 5V) can cause an input diode to conduct, especially at elevated temperatures. This will cause errors for analog inputs near full-scale. The specification

allows 50 mV forward bias of either diode; this means that as long as the analog V

IN

does not exceed the supply voltage by more than 50 mV, the output code will

be correct. Exceeding this range on an unselected channel will corrupt the reading of a selected channel. Achievement of an absolute 0 V

DC

to5VDCinput voltage

range will therefore require a minimum supply voltage of 4.950 V

DC

over temperature variations, initial tolerance and loading.

Note 13: Channel leakage current is measured after a single-ended channel is selected and the clock is turned off. For off channel leakage current the following

two cases are considered: one, with the selected channel tied high (5 V

DC

) and the remaining seven off channels tied low (0 VDC), total current flow through the off

channels is measured; two, with the selected channel tied low and the off channels tied high, total current flow through the off channels is again measured. The two

cases considered for determining on channel leakage current are the same except total current flow through the selected channel is measured.

Note 14: A 40% to 60% duty cycle range insures proper operation at all clockfrequencies.Inthecasethatanavailableclockhasadutycycleoutsideoftheselimits

the minimum time the clock is high or low must be at least 450 ns. The maximum time the clock can be high or low is 100 µs.

Note 15: Since data, MSB first, is theoutputofthecomparator used in the successive approximation loop, an additional delay is built in (see Block Diagram) to allow

for comparator response time.

Note 16: For the ADC08131 V

REF

IN is internally tied to the on chip 2.5V band-gap reference output; therefore, the supply current is larger because it includes the

reference current (700 µA typical, 2 mA maximum).

Note 17: Load regulation test conditions and specifications for the ADC08131 differ from those of the ADC08134 and ADC08138 because the ADC08131 has the

on-board reference as a permanent load.

ADC08131/ADC08134/ADC08138

www.national.com5

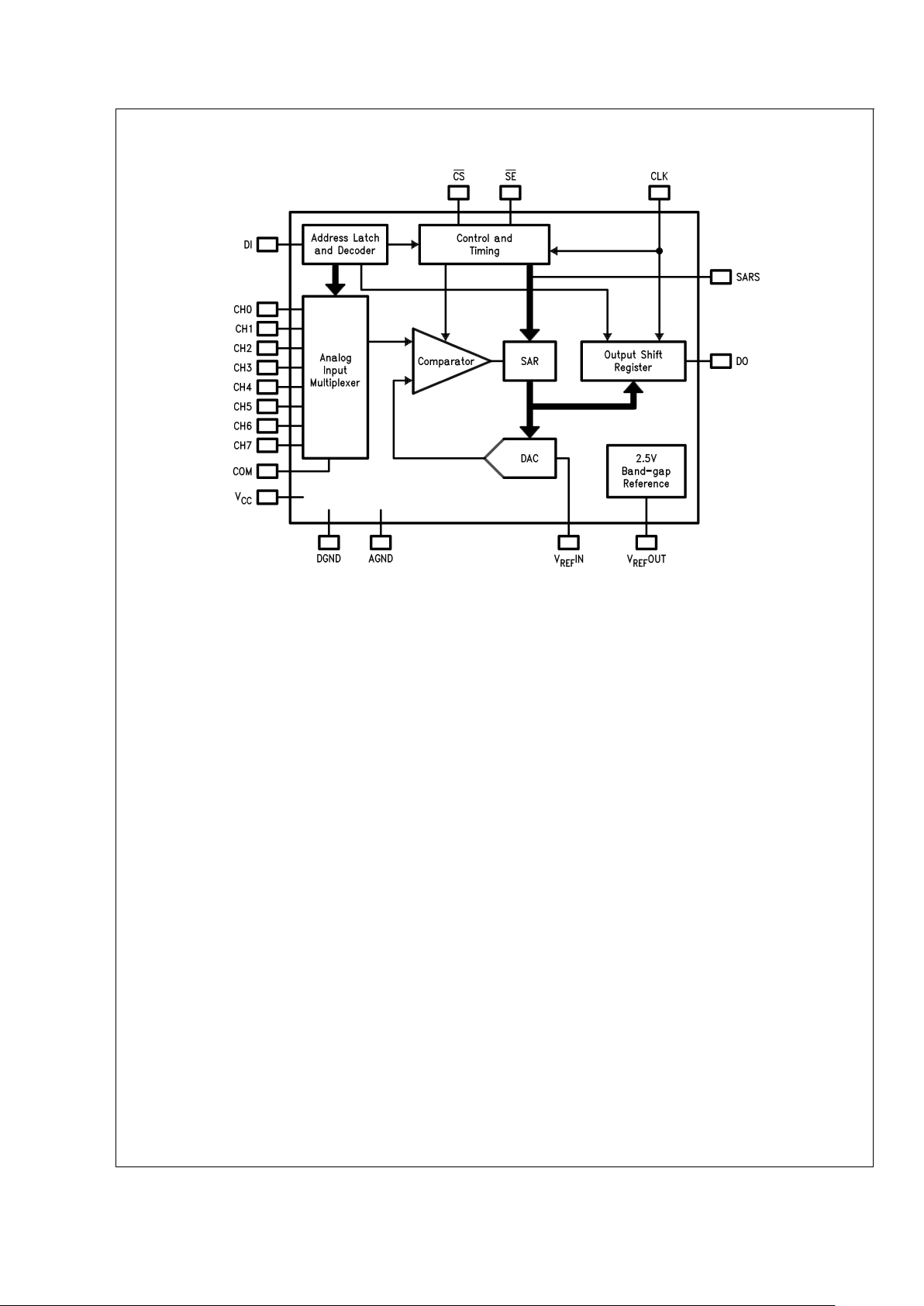

ADC08138 Simplified Block Diagram

DS010749-1

ADC08131/ADC08134/ADC08138

www.national.com 6

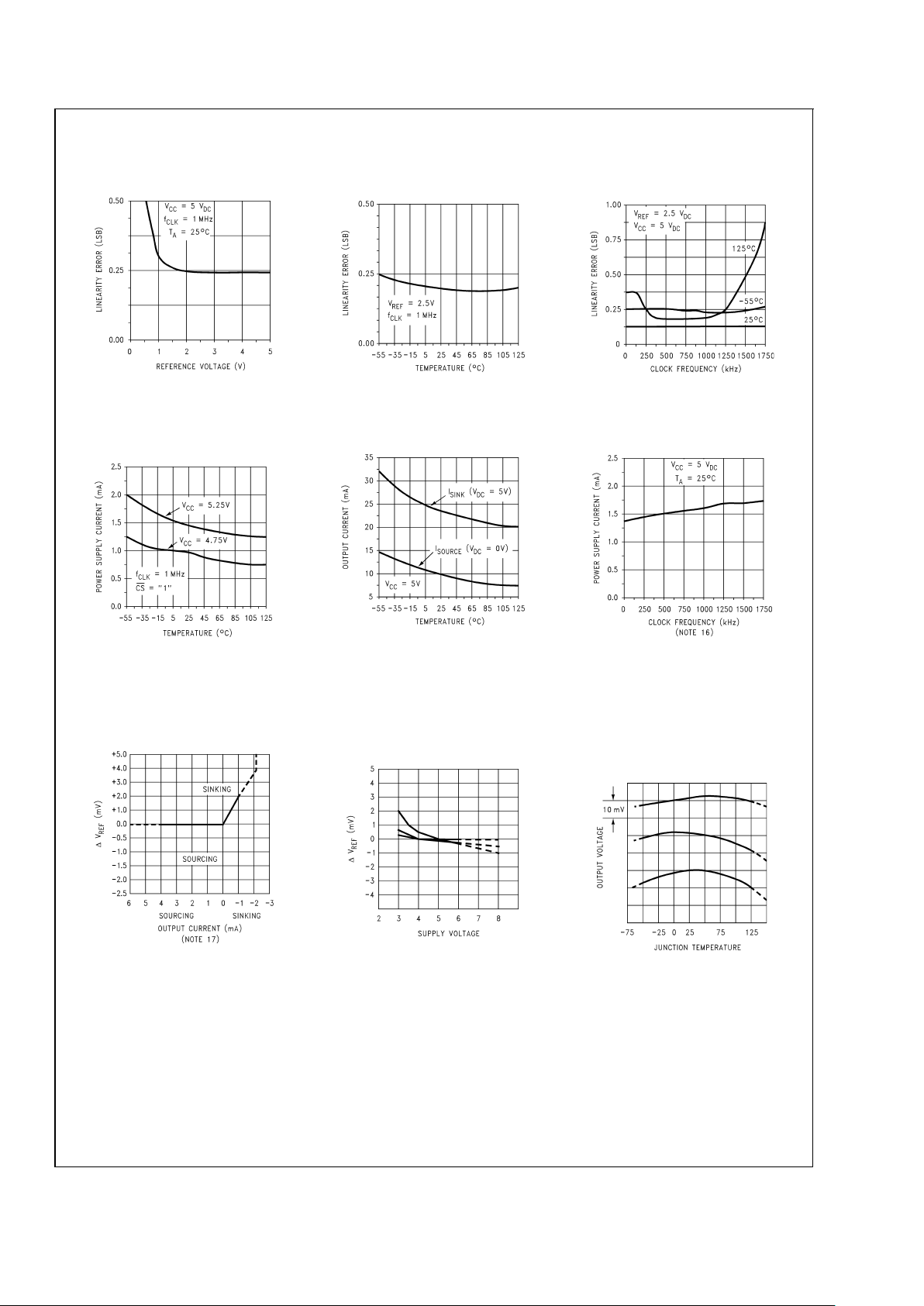

Typical Converter Performance Characteristics

Typical Reference Performance Characteristics

Linearity Error vs

Reference Voltage

DS010749-27

Linearity Error vs

Temperature

DS010749-28

Linearity Error vs

Clock Frequency

DS010749-29

Power Supply Current vs

Temperature (ADC08138,

ADC08134)

DS010749-30

Output Current vs

Temperature

DS010749-31

Power Supply Current

vs Clock Frequency

DS010749-32

Note: For ADC08131 add I

REF

Load Regulation

DS010749-33

Line Regulation

(3 Typical Parts)

DS010749-34

Output Drift

vs Temperature

(3 Typical Parts)

DS010749-35

ADC08131/ADC08134/ADC08138

www.national.com7

Loading...

Loading...