NSC 5962-9321701QSA, 5962-9321701Q2A, 5962-9321701QRA Datasheet

54ABT273

Octal D-Type Flip-Flop

General Description

The ’ABT273 has eight edge-triggered D-type flip-flops with

individual D inputs and Q outputs. The common buffered

Clock (CP) and Master Reset (MR) inputs load and reset

(clear) all flip-flops simultaneously.

The register is fully edge-triggered. The state of each D input, one setup time before the LOW-to-HIGH clock transition, is transferred to the corresponding flip-flop’s Q output.

All outputs will be forced LOW independently of Clock or

Data inputsby a LOW voltage level on the MR input. The device is usefulfor applicationswhere the true output onlyis required and the Clock and Master Reset are common to all

storage elements.

Features

n Eight edge-triggered D flip-flops

Ordering Code

Military Package Package Description

Number

54ABT273J-QML J20A 20-Lead Ceramic Dual-In-Line

54ABT273W-QML W20A 20-Lead Cerpack

54ABT273E-QML E20A 20-Lead Ceramic Leadless Chip Carrier, Type C

n Buffered common clock

n Buffered, asynchronous Master Reset

n See ’ABT377 for clock enable version

n See ’ABT373 for transparent latch version

n See ’ABT374 for TRI-STATE

n Output sink capability of 48 mA, source capability of

24 mA

n Guaranteed latchup protection

n High impedance glitch free bus loading during entire

power up and power down cycle

n Non-destructive hot insertion capability

n Disable time less than enable time to avoid bus

contention

n Standard Microcircuit Drawing (SMD) 5962-9321701

®

version

54ABT273 Octal D-Type Flip-Flop

July 1998

TRI-STATE®is a registered trademark of National Semiconductor Corporation.

© 1998 National Semiconductor Corporation DS100205 www.national.com

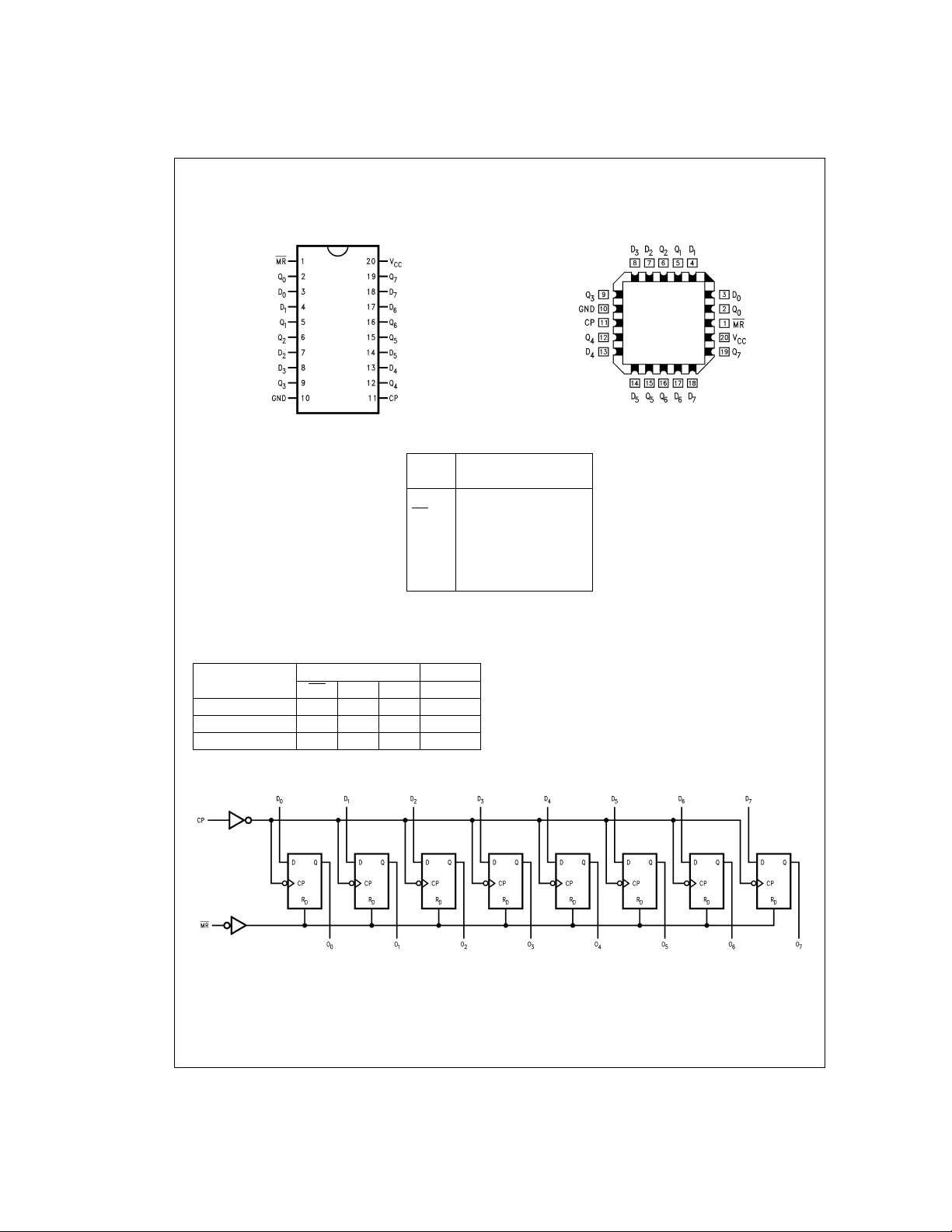

Connection Diagrams

Pin Assignment for DIP

and Flatpack

DS100205-1

Pin Description

Names

D

0–D7

MR

CP Clock Pulse Input

Q

0–Q7

Truth Table

Mode Select-Function Table

Operating Mode Inputs Output

MR

CP D

Reset (Clear) L X X L

Load “1” H

Load “0” H

N

N

n

hH

lL

Data Inputs

Master Reset

(Active LOW)

(Active Rising Edge)

Data Outputs

Q

n

Pin Assignment

for LCC

DS100205-2

=

H

HIGH Voltage Level steady state

h=HIGH Voltage Level one setup time prior tothe LOW-to-HIGH clock transition

L=LOW Voltage Level steady state

I=LOW Voltage Level one setup time prior to the LOW-to-HIGH clock transition

X=Immaterial

=

N

LOW-to-HIGH clock transition

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com 2

DS100205-3

Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

DC Latchup Source Current −500 mA

(Across Comm Operating Range)

Over Voltage Latchup V

Distributors for availability and specifications.

Storage Temperature −65˚C to +150˚C

Ambient Temperature under Bias −55˚C to +125˚C

Junction Temperature under Bias

Ceramic −55˚C to +175˚C

Pin Potential to

V

CC

Ground Pin −0.5V to +7.0V

Input Voltage (Note 2) −0.5V to +7.0V

Input Current (Note 2) −30 mA to +5.0 mA

Voltage Applied to Any Output

in the Disabled or

Power-Off State −0.5V to +4.75V

in the HIGH State −0.5V to V

Current Applied to Output

in LOW State (Max) twice the rated I

(mA)

OL

Recommended Operating

Conditions

Free Air Ambient Temperature

Military −55˚C to +125˚C

Supply Voltage

Military +4.5V to +5.5V

Minimum Input Edge Rate (∆V/∆t)

Data Input 50 mV/ns

Enable Input 20 mV/ns

Note 1: Absolute maximum ratings are values beyond whichthe device may

be damaged or have its usefullifeimpaired. Functional operation under these

conditions is not implied.

CC

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

DC Electrical Characteristics

Symbol Parameter ABT273 Units V

Min Typ Max

V

V

V

V

V

I

I

I

V

I

I

I

I

I

I

Input HIGH Voltage 2.0 V Recognized HIGH Signal

IH

Input LOW Voltage 0.8 V Recognized LOW Signal

IL

Input Clamp Diode Voltage −1.2 V Min I

CD

Output HIGH Voltage 54ABT 2.5 I

OH

54ABT 2.0 V Min I

Output LOW Voltage 54ABT 0.55 V Min I

OL

Input HIGH Current 5 µA Max V

IH

5V

Input HIGH Current 7 µA Max V

BVI

Breakdown Test

Input LOW Current −5 µA Max V

IL

−5 V

Input Leakage Test 4.75 V 0.0 I

ID

Output Short-Circuit Current −100 −275 mA Max V

OS

Output High Leakage Current 50 µA Max V

CEX

Power Supply Current 50 µA Max All Outputs HIGH

CCH

Power Supply Current 30 mA Max All Outputs LOW

CCL

Maximum ICC/Input Outputs Enabled V

CCT

1.5 mA Max Data Input V

CCD

Dynamic I

CC

No Load 0.3 mA/ Max Outputs Open (Note 3)

MHz One Bit Toggling, 50%Duty Cycle

Note 3: For 8 bits toggling, I

Note 4: Guaranteed but not tested.

CCD

<

0.5 mA/MHz.

CC

=

−18 mA

IN

=

−3 mA

OH

=

−24 mA

OH

=

48 mA

OL

=

2.7V (Note 4)

IN

=

V

IN

CC

=

7.0V

IN

=

0.5V (Note 4)

IN

=

0.0V

IN

=

1.9 µA

ID

All Other Pins Grounded

=

0.0V

OUT

=

V

OUT

CC

=

− 2.1V

V

I

CC

All Others at V

Conditions

=

− 2.1V

V

I

CC

or GND

CC

CC

+ 4.5V

3 www.national.com

Loading...

Loading...