NSC 5962-9220101MDA, 5962-9220101MCA, 5962-9220101M2A Datasheet

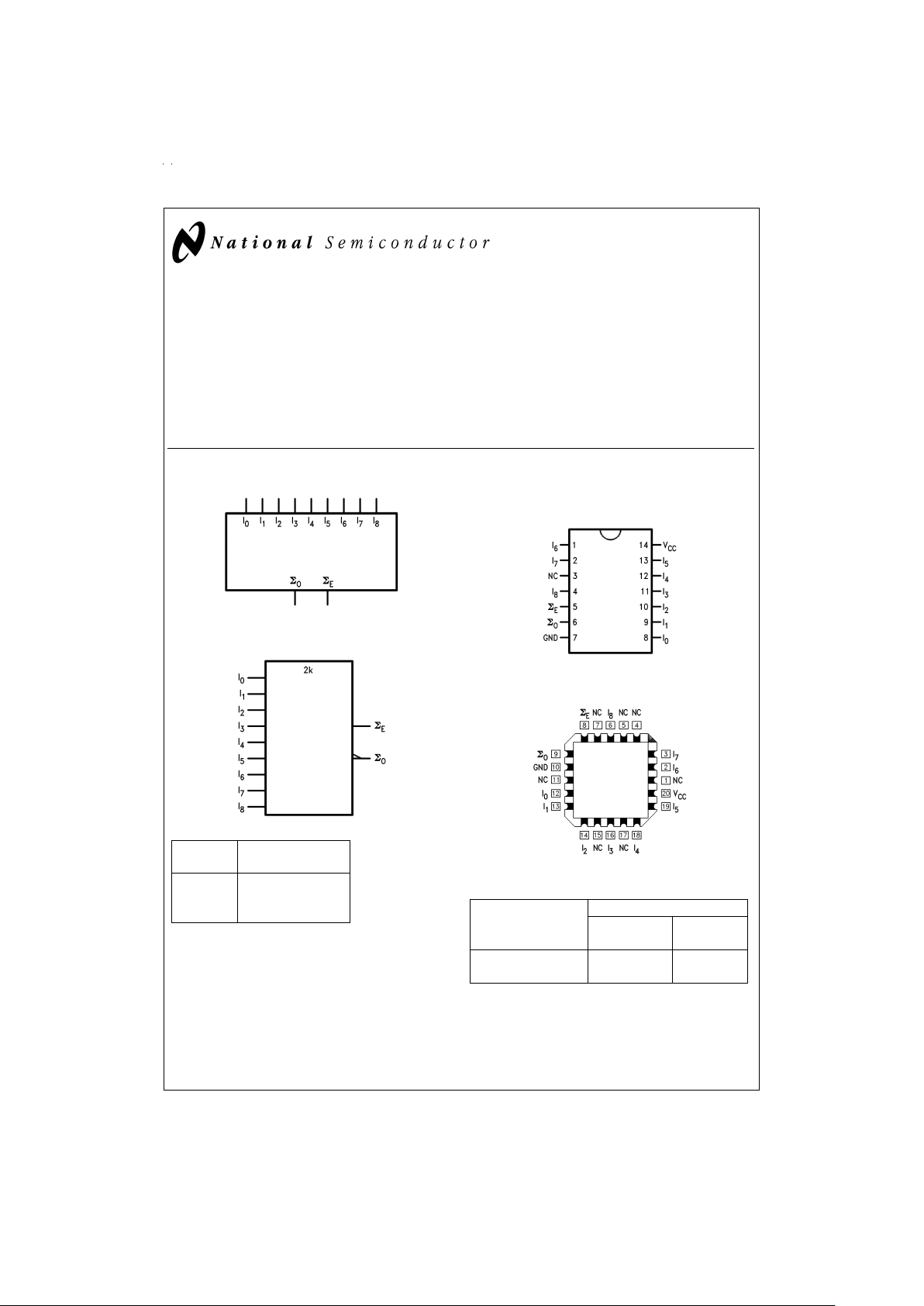

54AC280

9-Bit Parity Generator/Checker

General Description

The ’AC280 is a high-speed parity generator/checker that

accepts nine bits of input data and detects whether an even

or an odd number of theseinputsisHIGH. If an even number

of inputs is HIGH, the Sum Even output is HIGH. If an odd

number is HIGH, the Sum Even output is LOW. The Sum

Odd output is the complement of the Sum Even output.

Features

n ICCreduced by 50

%

n 9-bit width for memory applications

n Standard Microcircuit Drawing (SMD) 5962-92201

Logic Symbols

Pin

Names

Description

I

0–I8

Data Inputs

∑

O

Odd Parity Output

∑

E

Even Parity Output

Connection Diagrams

Truth Table

Number of Outputs

HIGH Inputs

∑

Even

∑

Odd

I

0–I8

0, 2, 4, 6, 8 H L

1, 3, 5, 7, 9 L H

H=HIGH Voltage Level

L=LOW Voltage Level

FACT™is a trademark of Fairchild Semiconductor Corporation.

DS100359-1

IEEE/IEC

DS100359-4

Pin Assignment for

DIP and Flatpak

DS100359-2

Pin Assignment for LCC

DS100359-3

September 1998

54AC280 9-Bit Parity Generator/Checker

© 1998 National Semiconductor Corporation DS100359 www.national.com

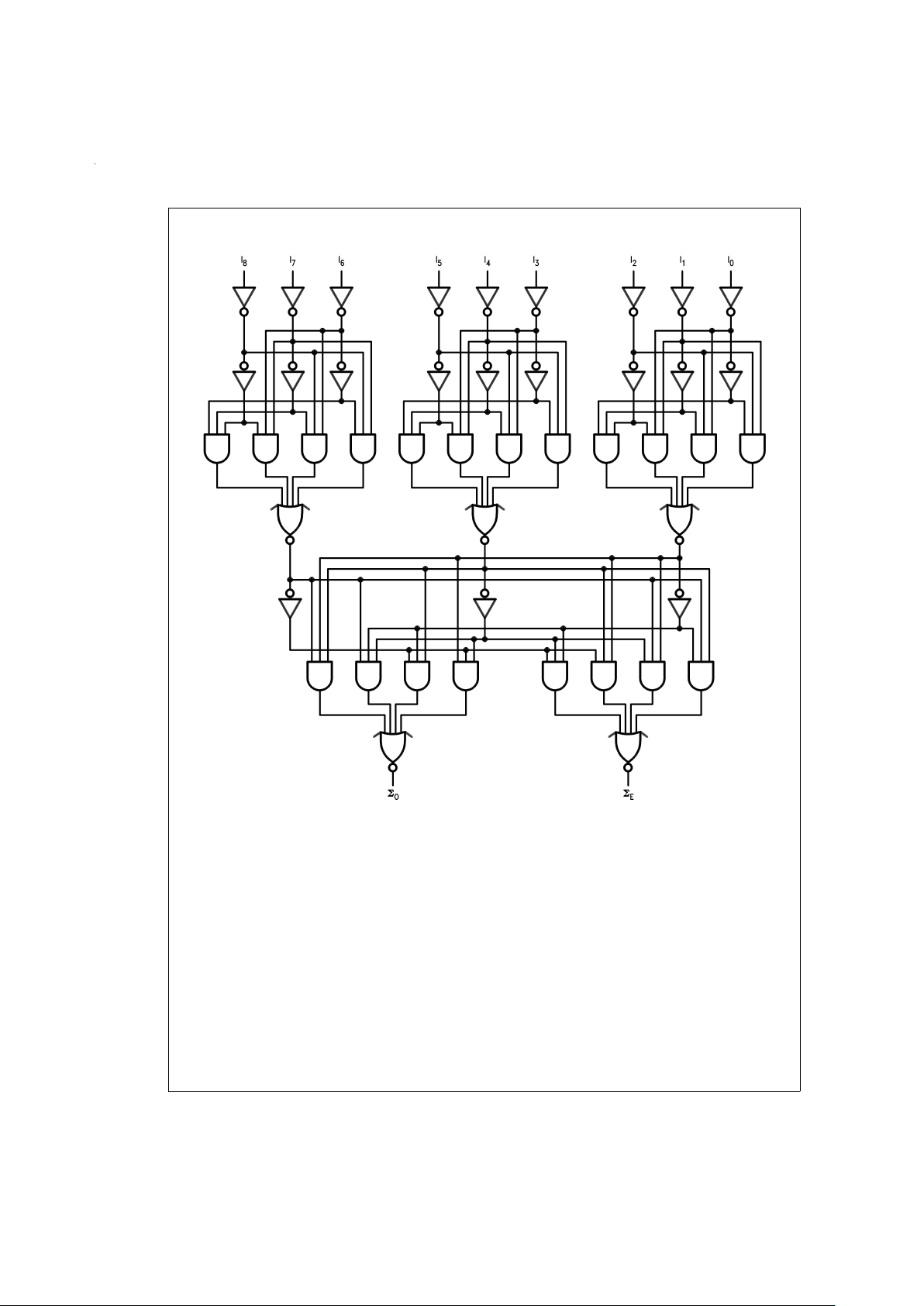

Logic Diagram

DS100359-5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

www.national.com 2

Loading...

Loading...