NSC 5962-9219701MLA, 5962-9219701MKA, 5962-9219701M3A Datasheet

54ACTQ657

Quiet Series Octal Bidirectional Transceiver with 8-Bit

Parity Generator/Checker and TRI-STATE

®

Outputs

General Description

The ACTQ657 contains eight non-inverting buffers with

TRI-STATEoutputs and an 8-bit parity generator/checker. Intended for bus oriented applications, the device combines

the ’245 and the ’280 functions in one package.

The ACTQ utilizes NSC Quiet Series technology to guarantee quiet output switching and improved dynamic threshold

performance. FACT Quiet Series

™

features GTO™output

control and undershoot corrector in addition to a split ground

bus for superior performance.

Features

n Guaranteed simultaneous switching noise level and

dynamic threshold performance

n Combines the ’245 and the ’280 functions in one

package

n Outputs source/sink 24 mA

n ’ACTQ has TTL-compatible inputs

n Standard Microcircuit Drawing (SMD)

5962-92197

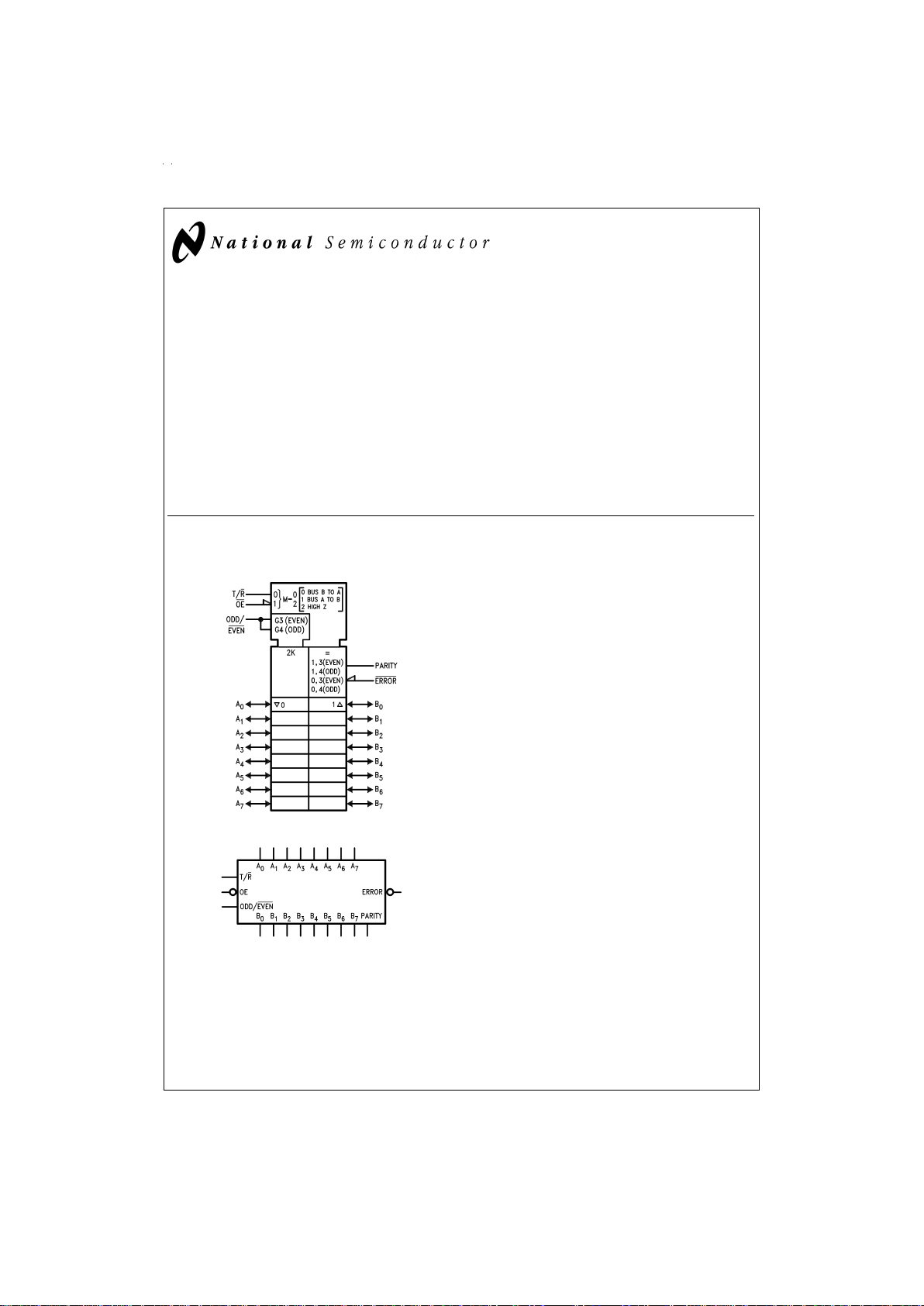

Logic Symbols

GTO™is a trademark of National Semiconductor Corporation.

TRI-STATE

®

is a registered trademark of National Semiconductor Corporation.

FACT Quiet Series

™

is a trademark of Fairchild Semiconductor Corporation.

IEEE/IEC

DS100244-1

DS100244-4

September 1998

54ACTQ657 Quiet Series Octal Bidirectional Transceiver with 8-Bit Parity Generator/Checker and

TRI-STATE Outputs

© 1998 National Semiconductor Corporation DS100244 www.national.com

Connection Diagrams

Pin Names Description

A

0–A7

Data Inputs/TRI-STATE Outputs

B

0–B7

Data Inputs/TRI-STATE Outputs

T/R

Transmit/Receive Input

OE

Enable Input

PARITY Parity Input/TRI-STATE Output

ODD/EVEN

ODD/EVEN Parity Input

ERROR Error TRI-STATE Output

Pin Assignment

for DIP and Flatpak

DS100244-2

Pin Assignment

for LCC

DS100244-3

www.national.com 2

Functional Description

The Transmit/Receive (T/R) input determines the direction of

the data flow through the bidirectional transceivers. Transmit

(active HIGH) enables data from the Aport to the B port; Receive (active LOW) enables data from the B port to the A

port.

The Output Enable (OE) input disables the parity and

ERROR outputs and both the A and B ports by placing them

in a HIGH-Z condition when the Output Enable input is

HIGH.

When transmitting (T/R HIGH), the parity generator detects

whether an even or odd number of bits on the A port are

HIGH and compares these with the condition of the parity select (ODD/EVEN). If the Parity Select is HIGH and an even

number of A inputs are HIGH, the Parity output is HIGH.

In receiving mode (T/R LOW), the parity select and number

of HIGH inputs on port B are compared to the condition of

the Parity input. If an even number of bits on the B port are

HIGH, the parity select is HIGH, and the PARITY input is

HIGH, then ERROR will be HIGH to indicate no error. If an

odd number of bits on the B port are HIGH, the parity select

is HIGH, and the PARITY input is HIGH, the ERROR will be

LOW indicating an error.

www.national.com3

Loading...

Loading...