NSC 5962-9209001M3A, 54F827SDMQB Datasheet

TL/F/9598

54F/74F827

#

74F828 10-Bit Buffers/Line Drivers

December 1994

54F/74F827#74F828

10-Bit Buffers/Line Drivers

General Description

The ’F827 and ’F828 10-bit bus buffers provide high performance bus interface buffering for wide data/address

paths or buses carrying parity. The 10-bit buffers have NOR

output enables for maximum control flexibility.

The ’F827 and ’F828 are functionally- and pin-compatible to

AMD’s Am29827 and Am29828. The ’F828 is an inverting

version of the ’F827.

Features

Y

TRI-STATEÉoutput

Y

’F828 is inverting

Y

Direct replacement for AMD’s Am29827 and Am29828

Commercial Military

Package

Package Description

Number

74F827SPC N24C 24-Lead (0.300×Wide) Molded Dual-In-Line

54F827SDM (Note 2) J24F 24-Lead (0.300×Wide) Ceramic Dual-In-Line

74F827SC (Note 1) M24B 24-Lead (0.300×Wide) Molded Small Outline, JEDEC

54F827FM (Note 2) W24C 24-Lead Cerpack

54F827LM (Note 2) E28A 24-Lead Ceramic Leadless Chip Carrier, Type C

74F828SPC N24C 24-Lead (0.300×Wide) Molded Dual-In-Line

74F828SC (Note 1) M24B 24-Lead (0.300×Wide) Molded Small Outline, JEDEC

Note 1: Devices also available in 13×reel. Use suffixeSCX.

Note 2: Military grade device with environmental and burn-in processing. Use suffix

e

SDMQB, FMQB and LMQB.

Connection Diagrams

Pin Assignment for

DIP, Flatpak and SOIC

Pin Assignment

for LCC

’F827

TL/F/9598– 1

’F828

TL/F/9598– 8

’F827

TL/F/9598– 2

TRI-STATEÉis a registered trademark of National Semiconductor Corporation.

C

1995 National Semiconductor Corporation RRD-B30M75/Printed in U. S. A.

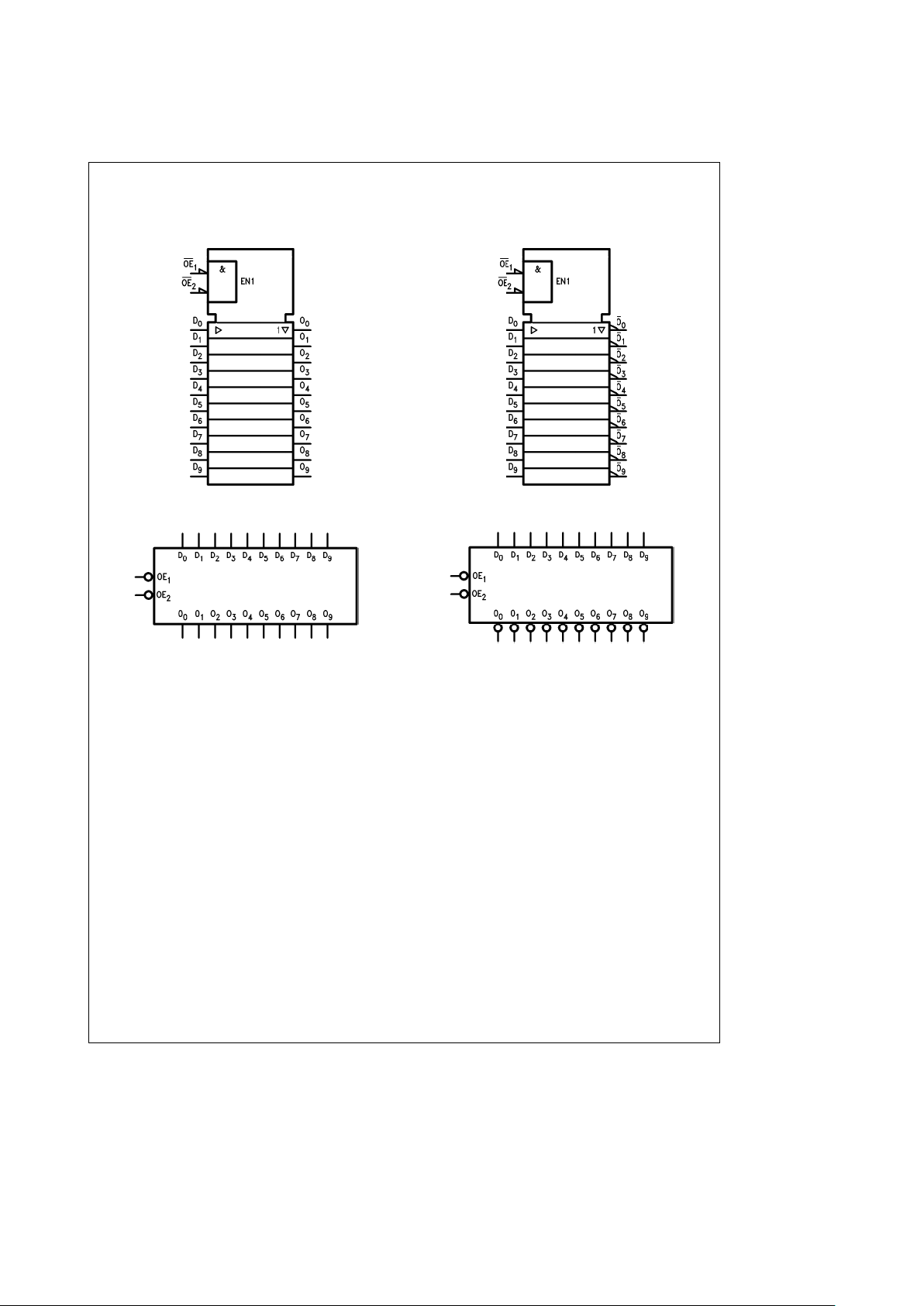

Logic Symbols

IEEE/IEC

’F827

TL/F/9598– 6

IEEE/IEC

’F828

TL/F/9598– 7

’F827

TL/F/9598– 3

’F828

TL/F/9598– 10

2

Unit Loading/Fan Out

54F/74F

Pin Names Description

U.L. Input I

IH/IIL

HIGH/LOW Output IOH/I

OL

OE1,OE2Output Enable Input 1.0/1.0 20 mA/b0.6 mA

D

0–D7

Data Inputs 1.0/1.0 20 mA/b0.6 mA

O

0–O7

Data Outputs, TRI-STATE 600/106.6 (80)b12 mA/64 mA (48 mA)

Functional Description

The ’F827 and ’F828 are line drivers designed to be employed as memory address drivers, clock drivers and busoriented transmitters/receivers which provide improved PC

board density. The devices have TRI-STATE outputs controlled by the Output Enable (OE

) pins. The outputs can sink

64 mA (48 mA mil) and source 15 mA. Input clamp diodes

limit high-speed termination effects.

Function Table

Inputs Outputs

OE D

n

O

n

Function

’F827 ’F828

L H H L Transparent

L L L H Transparent

H X Z Z High Z

HeHIGH Voltage level

L

e

LOW Voltage Level

Z

e

High Impedance

X

e

Immaterial

Logic Diagrams

’F827

TL/F/9598– 4

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

’F828

TL/F/9598– 11

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

3

Loading...

Loading...