Page 1

Page 2

RM-84/99

Nokia Customer Care System Module

(This page left intentionally blank.)

Page 1–2 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 3

RM-84/99

System Module Nokia Customer Care

Table of Contents

Baseband description....................................................................................................................................................................1–7

System module block diagram.............................................................................................................................................1–7

Baseband functional description.........................................................................................................................................1–8

Absolute maximum ratings.................................................................................................................................................1–10

Phone modes of operation..................................................................................................................................................1–10

Power distribution.................................................................................................................................................................1–14

Clocking scheme......................................................................................................................................................................1–16

Bluetooth/FM module............................................................................................................................................................1–17

USB...............................................................................................................................................................................................1–17

SIM interface.............................................................................................................................................................................1–17

RS MMC interface.....................................................................................................................................................................1–18

Battery interface.....................................................................................................................................................................1–19

Camera interfaces...................................................................................................................................................................1–19

Back camera.......................................................................................................................................................................1–19

Camera construction........................................................................................................................................................1–20

Back camera slider detection switch..........................................................................................................................1–22

Flash LED..............................................................................................................................................................................1–23

Front camera......................................................................................................................................................................1–24

User interface...........................................................................................................................................................................1–25

Display interface................................................................................................................................................................1–25

Keyboard..............................................................................................................................................................................1–26

Display and keyboard backlight...................................................................................................................................1–28

ALS interface.......................................................................................................................................................................1–29

ASICs............................................................................................................................................................................................1–30

RAP3G ASIC..........................................................................................................................................................................1–30

Retu EM ASIC.......................................................................................................................................................................1–30

Tahvo EM ASIC.....................................................................................................................................................................1–30

Device memories.....................................................................................................................................................................1–30

RAP3G memories NOR flash and SDRAM....................................................................................................................1–30

Combo memory.................................................................................................................................................................1–31

Audio concept................................................................................................................................................................................1–31

Audio HW architecture..........................................................................................................................................................1–31

Internal microphone..............................................................................................................................................................1–32

External microphone.............................................................................................................................................................1–32

Internal earpiece.....................................................................................................................................................................1–33

Internal speaker......................................................................................................................................................................1–33

External earpiece....................................................................................................................................................................1–34

Vibra circuitry...........................................................................................................................................................................1–34

Pop-portTM connector...........................................................................................................................................................1–35

Baseband technical specifications..........................................................................................................................................1–36

External interfaces..................................................................................................................................................................1–36

External interfaces............................................................................................................................................................1–36

ACI interface electrical characteristics........................................................................................................................1–36

VOUT electrical characteristics......................................................................................................................................1–37

USB IF electrical characteristics....................................................................................................................................1–37

FBUS interface electrical characteristics....................................................................................................................1–38

Headset hook detection interface (XMICN) electrical characteristics...............................................................1–38

Audio signal electrical characteristics........................................................................................................................1–39

SIM IF connections............................................................................................................................................................1–39

RS MMC interface connections.......................................................................................................................................1–39

Issue 1 Company Confidential Page 1–3

Copyright ©2005 Nokia. All Rights Reserved.

Page 4

RM-84/99

Nokia Customer Care System Module

Charger connector and charging interface connections & electrical characteristics..................................1–40

Battery connector and interface connections & electrical characteristics......................................................1–41

Internal interfaces..................................................................................................................................................................1–41

Internal interfaces............................................................................................................................................................1–41

UI module connector and IF connections.................................................................................................................1–42

Keyboard interface electrical characteristics...........................................................................................................1–43

Display connector and interface connections..........................................................................................................1–44

Camera interface connections and electrical characteristics..............................................................................1–45

Front camera interface and electrical characteristics...........................................................................................1–47

Flash LED interface and electrical characteristics...................................................................................................1–49

Slider switch electrical characteristics.......................................................................................................................1–50

Back-up battery interface connections and electrical characteristics..............................................................1–50

RF description................................................................................................................................................................................1–50

Receiver......................................................................................................................................................................................1–50

Introduction to receiver functionality........................................................................................................................1–50

WCDMA receiver.................................................................................................................................................................1–50

GSM receiver........................................................................................................................................................................1–51

Transmitter...............................................................................................................................................................................1–51

Introduction to transmitter functionality.................................................................................................................1–51

WCDMA transmitter..........................................................................................................................................................1–51

GSM transmitter.................................................................................................................................................................1–53

Frequency synthesizers.........................................................................................................................................................1–56

Regulators.................................................................................................................................................................................1–57

Frequency mappings...................................................................................................................................................................1–58

EGSM900 frequencies.............................................................................................................................................................1–58

GSM1800 frequencies............................................................................................................................................................1–59

GSM1900 frequencies............................................................................................................................................................1–60

WCDMA Rx frequencies..........................................................................................................................................................1–61

WCDMA Tx frequencies..........................................................................................................................................................1–62

List of Tables

Table 1 Camera specifications..................................................................................................................................................1–20

Table 2 Keymatrix.........................................................................................................................................................................1–26

Table 3 LED driver control signals............................................................................................................................................1–29

Table 4 ALS resistor values.........................................................................................................................................................1–29

Table 5 Audio connector pin assignments...........................................................................................................................1–35

Table 6 Charging interface connections................................................................................................................................1–40

Table 7 Charging IF electrical characteristics.......................................................................................................................1–40

Table 8 Battery interface connections...................................................................................................................................1–41

Table 9 Battery IF electrical characteristics..........................................................................................................................1–41

Table 10 User interface connections......................................................................................................................................1–42

Table 11 Display interface connections.................................................................................................................................1–44

Table 12 Camera interface connections................................................................................................................................1–45

Table 13 Camera CCP IF electrical characteristics...............................................................................................................1–46

Table 14 Camera supply voltage characteristics.................................................................................................................1–47

Table 15 Camera control IF electrical characteristics........................................................................................................1–47

Table 16 Front camera interface connections.....................................................................................................................1–47

Table 17 Front camera voltage levels from Helen point of view...................................................................................1–49

Table 18 Front camera voltage levels from camera module point of view...............................................................1–49

Table 19 Front camera supply voltage characteristics......................................................................................................1–49

Table 20 Flash LED interface connections.............................................................................................................................1–49

Page 1–4 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 5

RM-84/99

System Module Nokia Customer Care

Table 21 Flash LED interface electrical characteristics .....................................................................................................1–50

Table 22 Back-up battery connections...................................................................................................................................1–50

Table 23 Back-up battery electrical characteristics...........................................................................................................1–50

List of Figures

Figure 1 System level block diagram........................................................................................................................................1–7

Figure 2 Functional block diagram............................................................................................................................................1–8

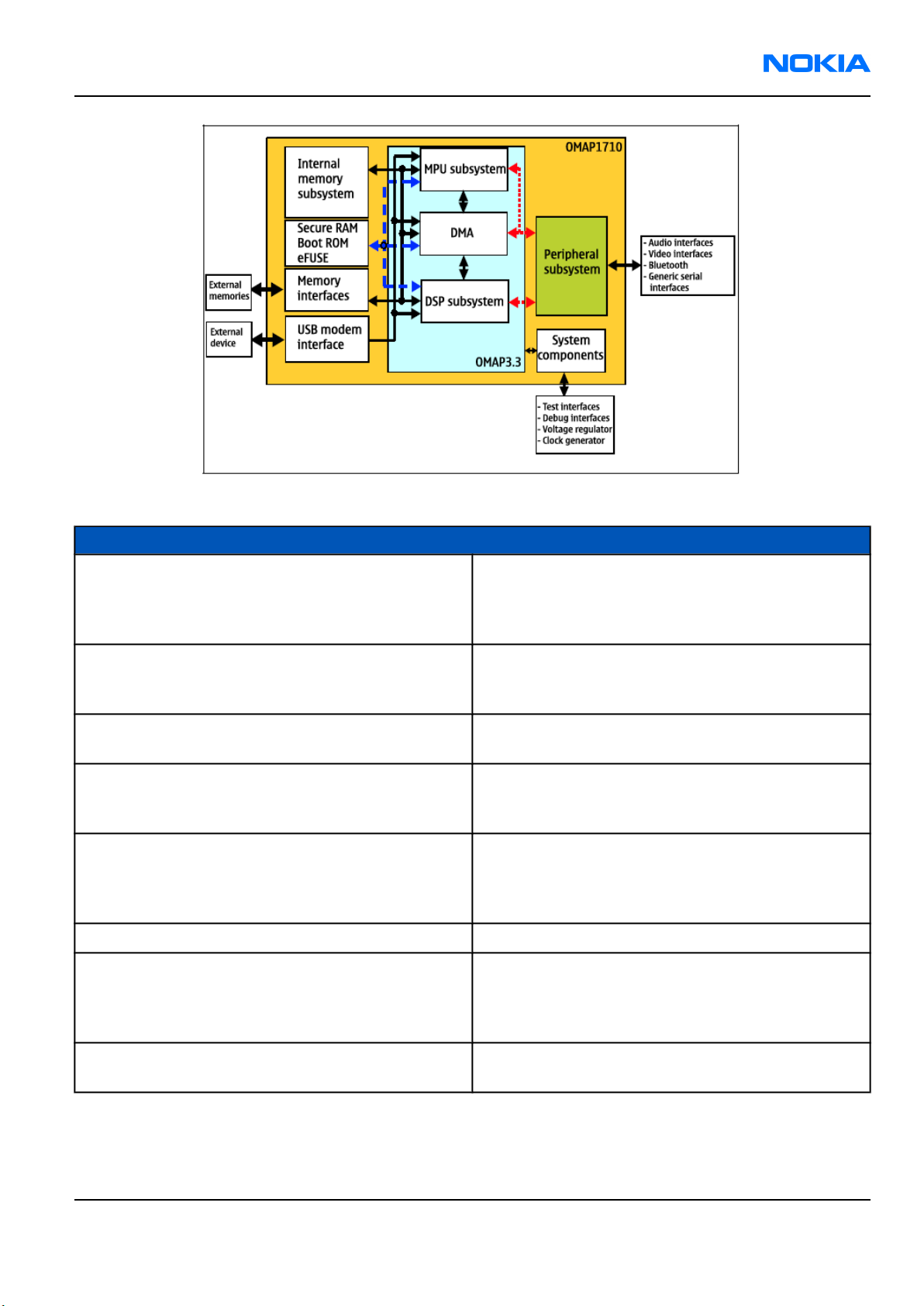

Figure 3 OMAP1710 high level block diagram.......................................................................................................................1–9

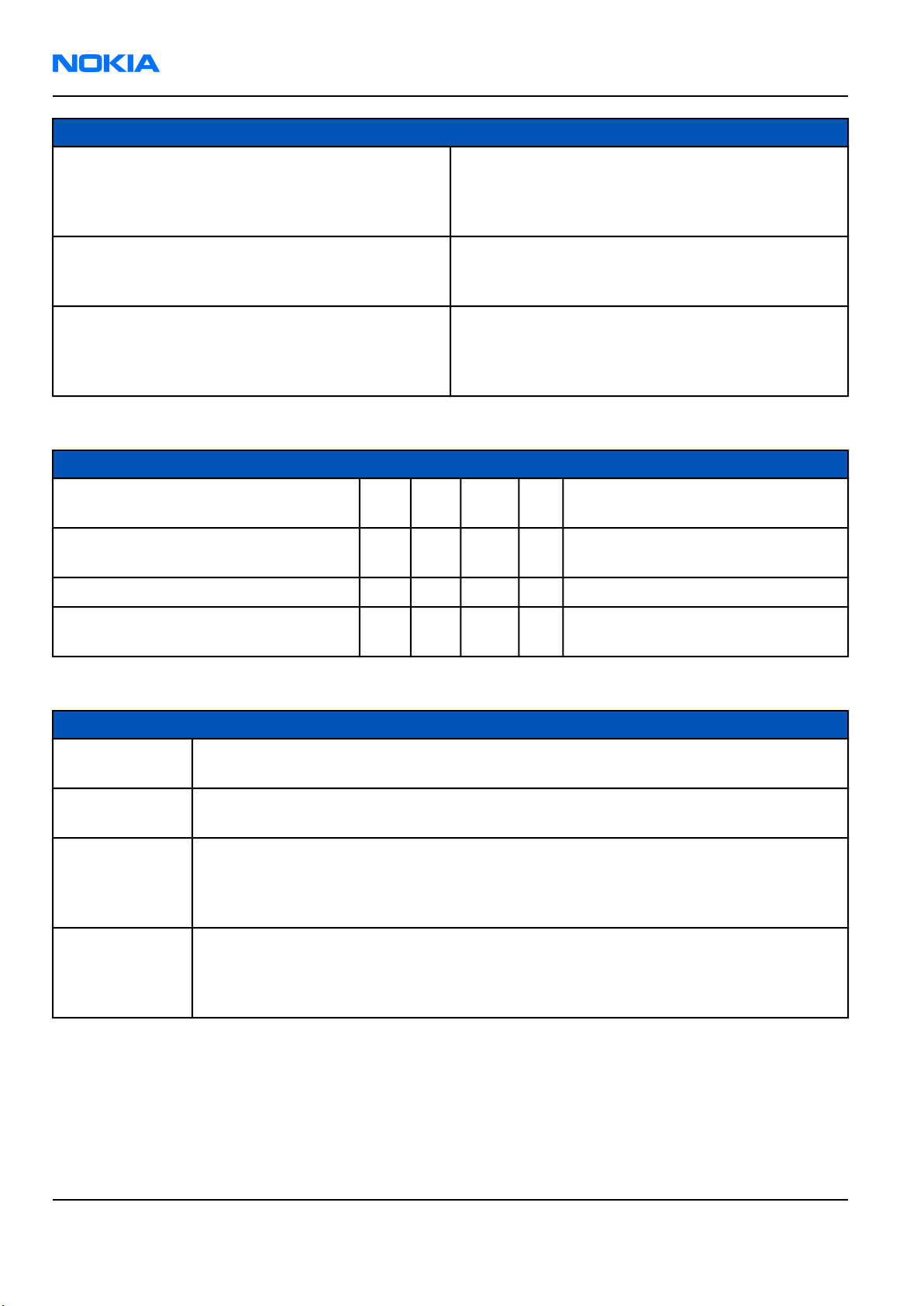

Figure 4 State diagram...............................................................................................................................................................1–12

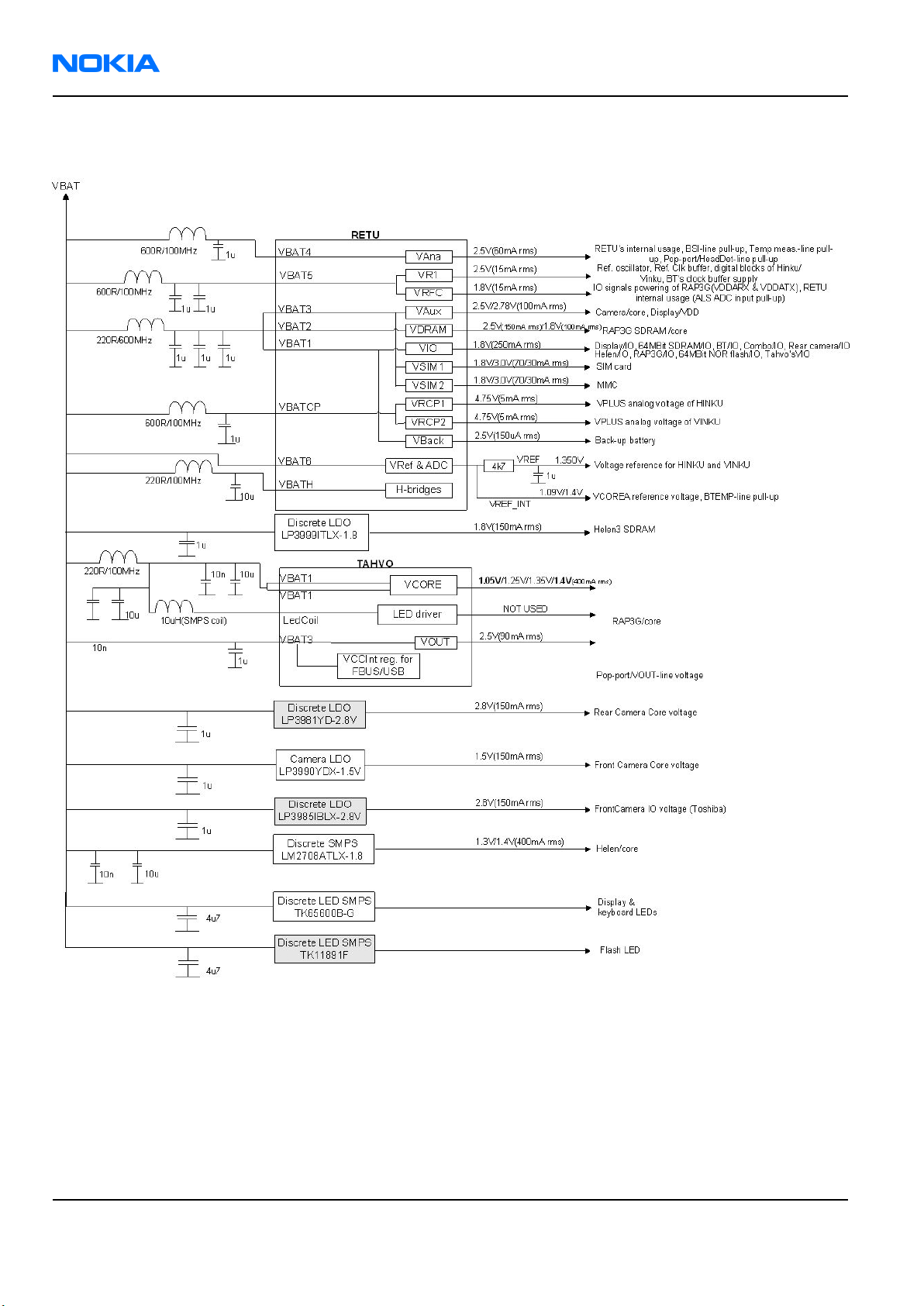

Figure 5 Power distribution diagram.....................................................................................................................................1–14

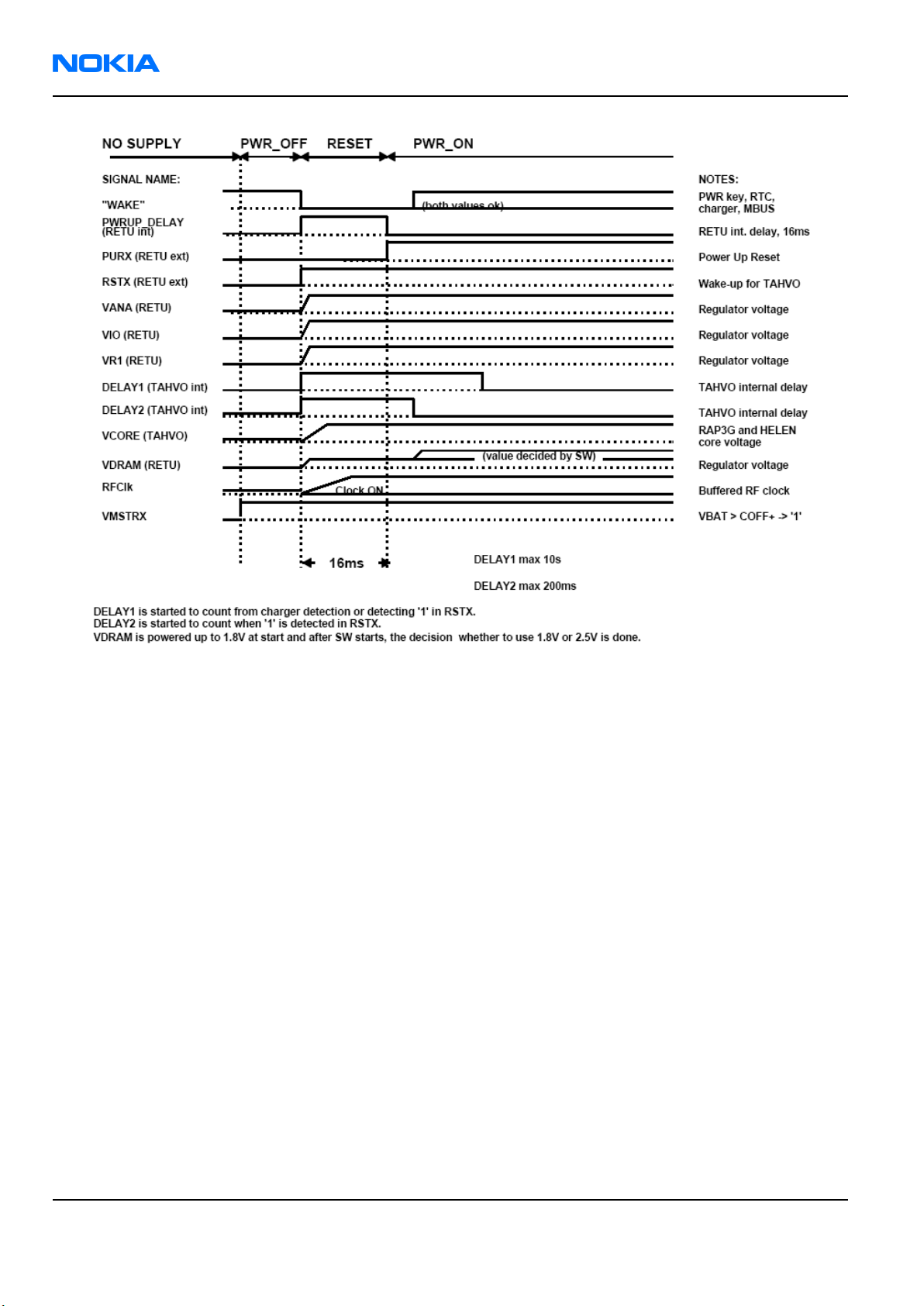

Figure 6 System start-up timing..............................................................................................................................................1–16

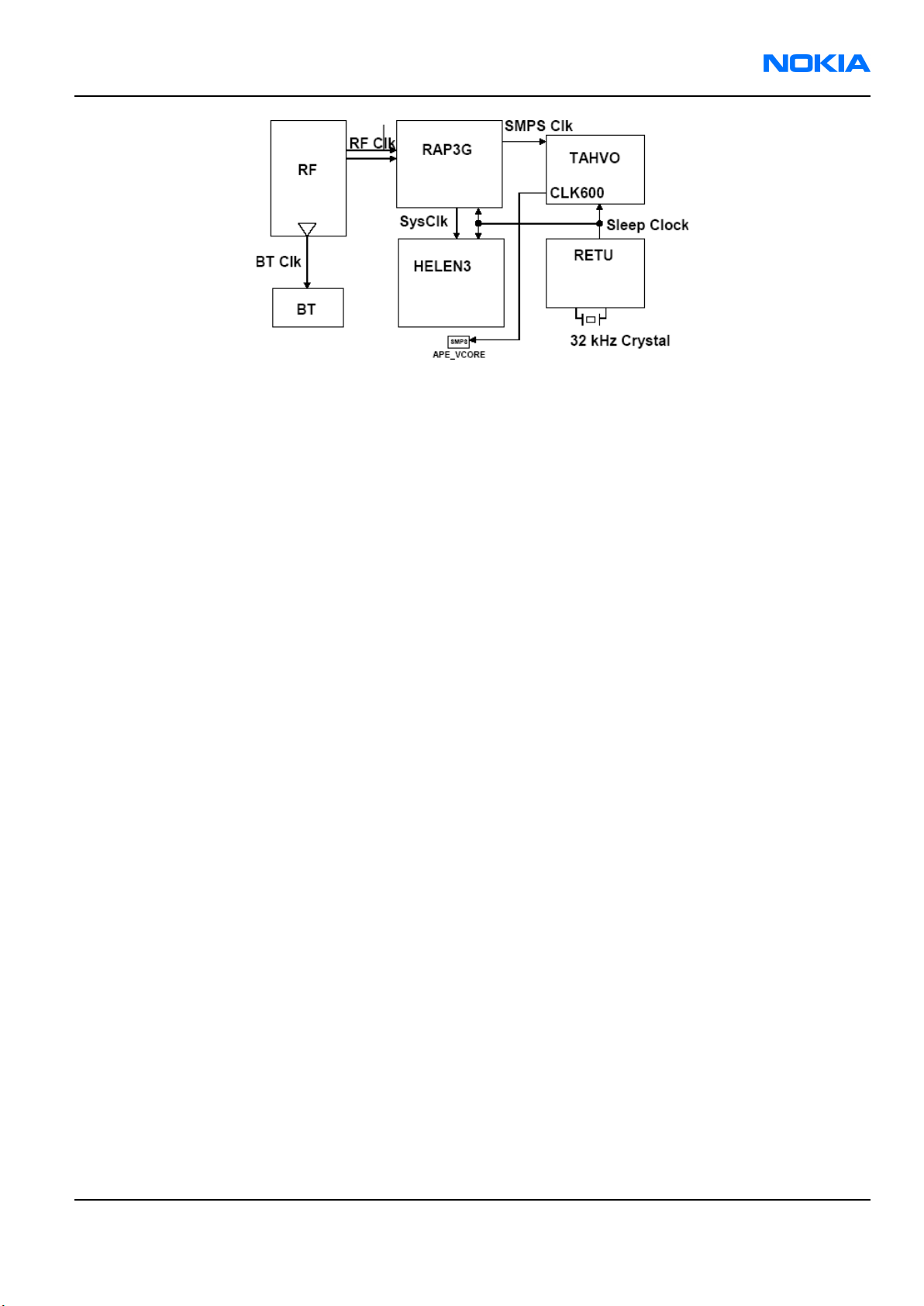

Figure 7 Clocking scheme...........................................................................................................................................................1–17

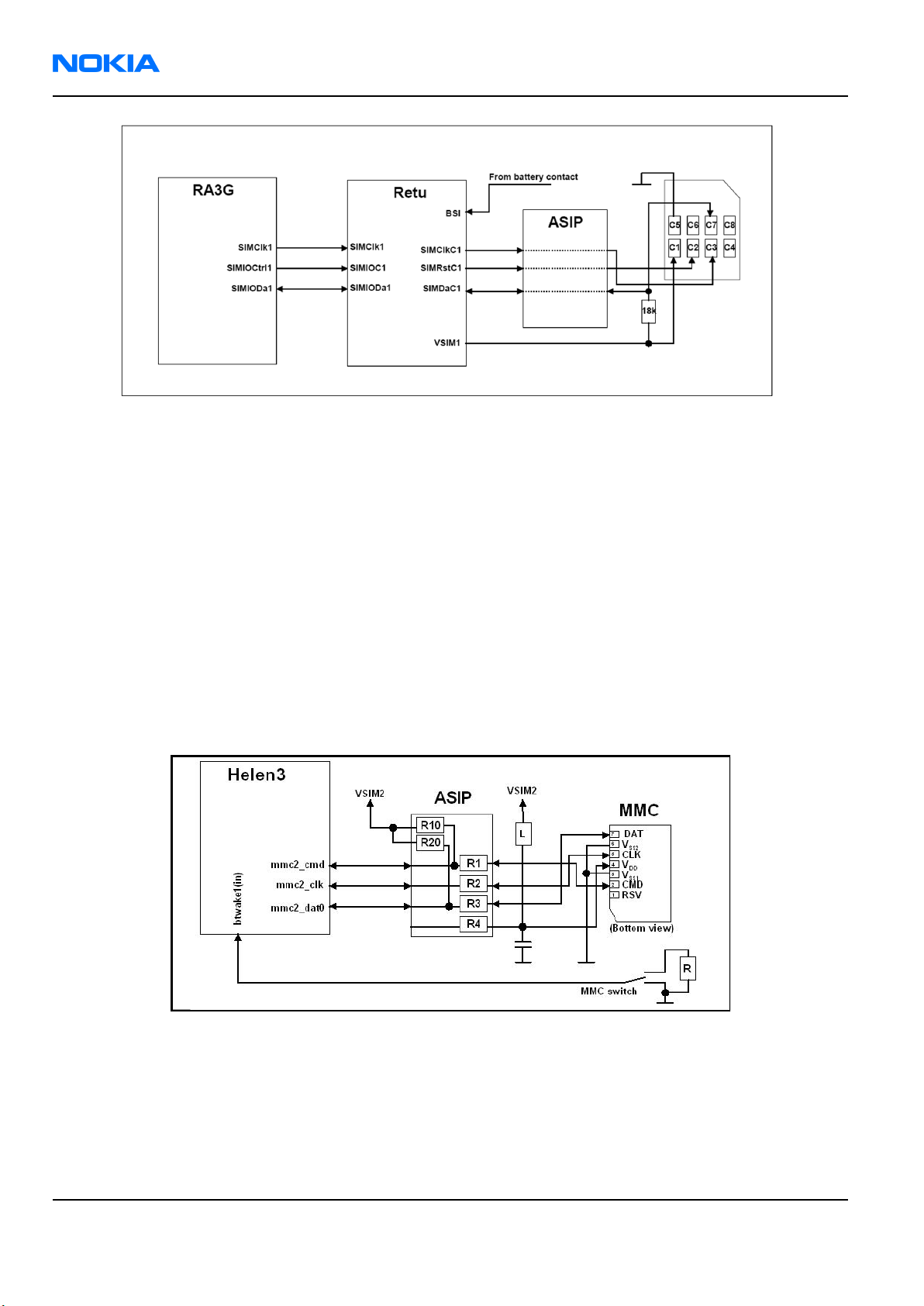

Figure 8 SIM interface..................................................................................................................................................................1–18

Figure 9 MMC interface................................................................................................................................................................1–18

Figure 10 Battery pin order.......................................................................................................................................................1–19

Figure 11 Block diagram of the back camera module......................................................................................................1–20

Figure 12 Camera module cross section and assembly principle..................................................................................1–21

Figure 13 Camera module bottom view including serial numbering..........................................................................1–21

Figure 14 Slider switch connection.........................................................................................................................................1–23

Figure 15 Simplified flash LED connection............................................................................................................................1–24

Figure 16 Front camera connections......................................................................................................................................1–25

Figure 17 General diagram of the LCD module...................................................................................................................1–25

Figure 18 Keyboard layout.........................................................................................................................................................1–28

Figure 19 ALS HW implementation.........................................................................................................................................1–29

Figure 20 Audio block diagram................................................................................................................................................1–32

Figure 21 Internal microphone circuitry...............................................................................................................................1–32

Figure 22 External microphone circuitry (Pop-Port connects to the right side).......................................................1–33

Figure 23 Internal earpiece circuitry......................................................................................................................................1–33

Figure 24 Internal speaker circuitry........................................................................................................................................1–34

Figure 25 External earpiece circuitry (Pop-Port connected on the right)...................................................................1–34

Figure 26 Vibra circuitry.............................................................................................................................................................1–35

Figure 27 External audio connector........................................................................................................................................1–35

Figure 28 Charger connector.....................................................................................................................................................1–40

Figure 29 Battery connector......................................................................................................................................................1–41

Figure 30 UI connector................................................................................................................................................................1–42

Figure 31 Display connector......................................................................................................................................................1–44

Figure 32 WCDMA transmitter...................................................................................................................................................1–52

Figure 33 Block diagram of DCDC converter and WCDMA PA...........................................................................................1–53

Figure 34 GSM transmitter.........................................................................................................................................................1–54

Figure 35 GSM/EDGE power control topology and control signals................................................................................1–55

Figure 36 Power control signal usage in GSM (GMSK) and EDGE (8PSK) transmission............................................1–55

Figure 37 Phase locked loop in N7500 and N7501 (PLL)..................................................................................................1–56

Figure 38 RF supply connections from the BB mixed mode ASIC..................................................................................1–57

Issue 1 Company Confidential Page 1–5

Copyright ©2005 Nokia. All Rights Reserved.

Page 6

RM-84/99

Nokia Customer Care System Module

(This page left intentionally blank.)

Page 1–6 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 7

RM-84/99

System Module Nokia Customer Care

Baseband description

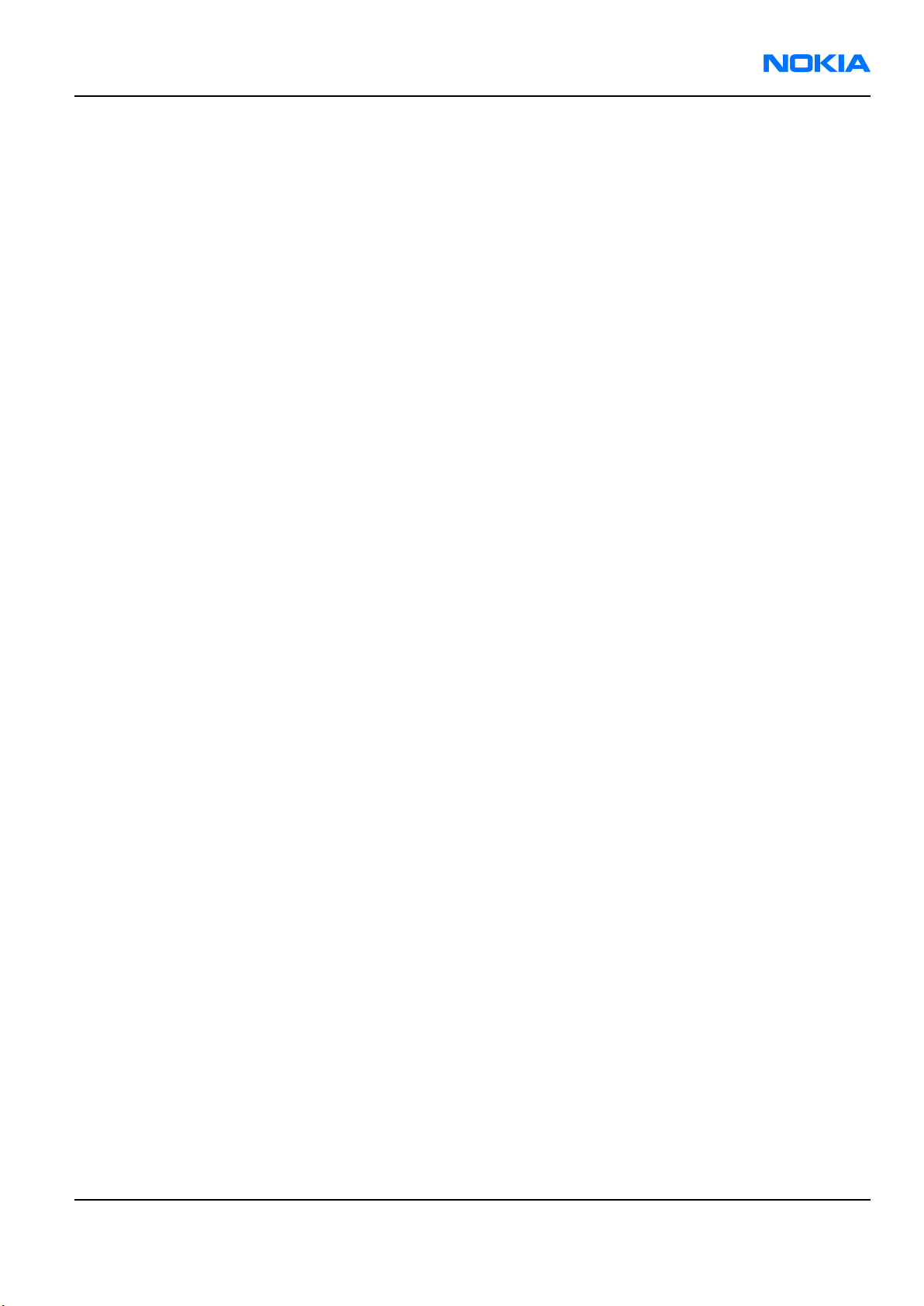

System module block diagram

The device consists of two different main modules: transceiver and UI. The transceiver board consists of

baseband and RF components. The UI board consists of key domes and keypad backlights. Connection between

the UI and the transceiver board is established via a board-to-board spring connector.

Note: In this description, the user interface HW covers display, camera, keyboard, keyboard backlight

and ALS.

Figure 1 System level block diagram

Issue 1 Company Confidential Page 1–7

Copyright ©2005 Nokia. All Rights Reserved.

Page 8

RM-84/99

Nokia Customer Care System Module

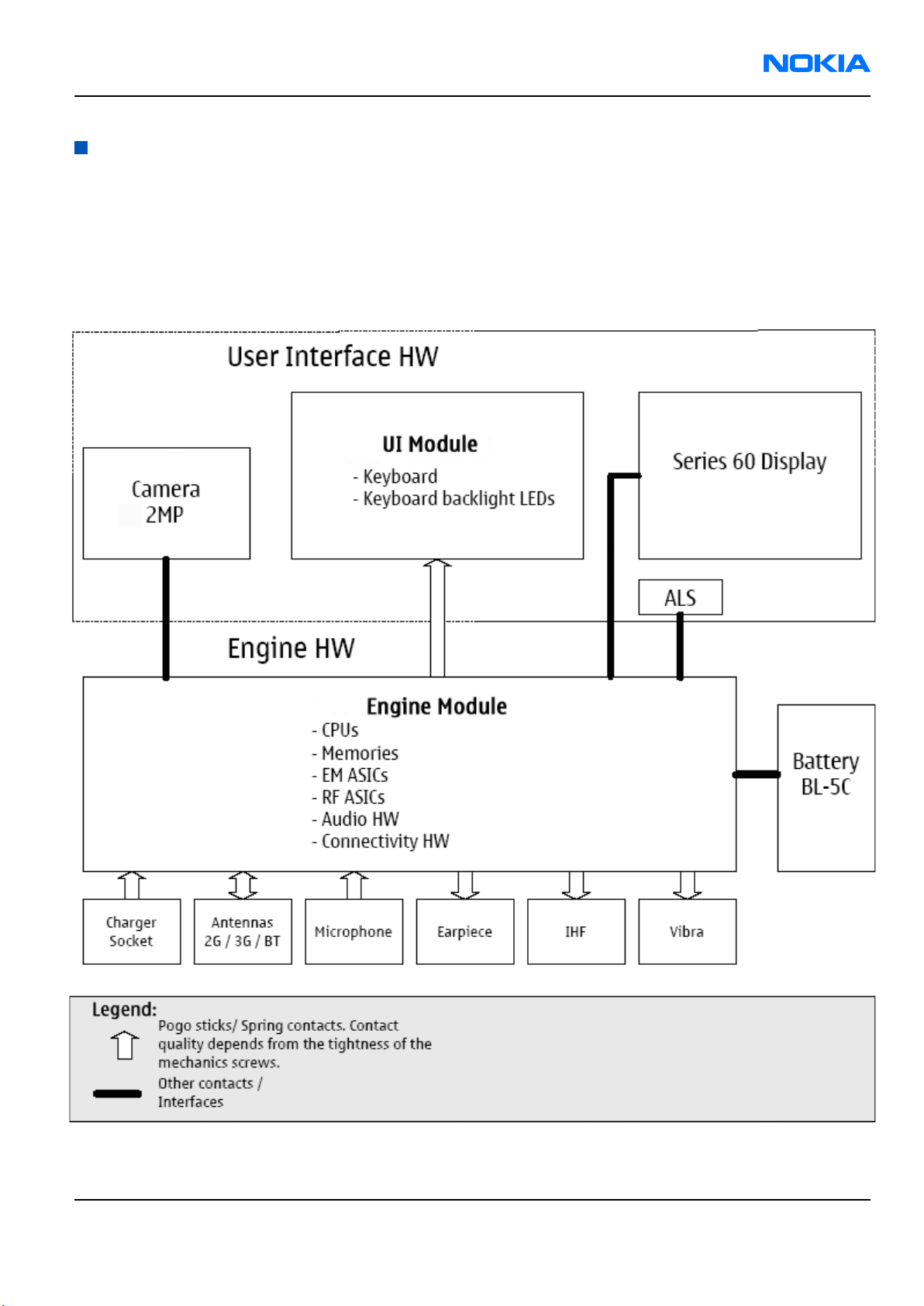

Baseband functional description

Digital baseband consists of an ISA (Intelligent Software Architecture) based modem and Symbian based

application sections. The modem functionality is in RAP3G, and OMAP acts as a platform for Symbian applications.

The terms ISA and Symbian are used refer to the software environment of these devices.

The modem section consists of a RAP3G ASIC with NOR FLASH and SDRAM memory as the core. RAP3G supports

cellular protocols of WCDMA (3GPP R-4) and GSM (EDGE class 10, GPRS phase2). The modem SDRAM memory has

64Mbits of memory and NOR flash has 64Mbits of memory. RAP3G operates with the system clock of 38.4 MHz,

which comes from the VCTCXO.

The application section includes an OMAP ASIC with DDR/NAND combo memory as the core. The OMAP ASIC uses

a 19.2MHz clock, which comes from the RAP3G divided by two from the 38.4 MHz system clock.

Figure 2 Functional block diagram

OMAP processor (Helen3 (OMAP1710)) is also called an application ASIC because it is processing application SW

and handles the UI SW. It consists of OMAP3.3 and peripheral subsystems such as camera, display and keyboard

driver blocks.

Page 1–8 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 9

RM-84/99

System Module Nokia Customer Care

Figure 3 OMAP1710 high level block diagram

Section Description

Helen3 (OMAP1710) processor also called an application ASIC because it is

processing application SW and handles the UI SW. It

consists of OMAP3.3 and peripheral subsystems like

camera, display and keyboard driver blocks.

OMAP3.3 consists of ARM926 (MPU subsystem), TMS320C55x

(DSP subsystem), DMA and OMAP3.3s internal

peripherals.

Helen3 (OMAP1710) MPU subsystem based on an ARM926EJ. MPU is able to perform most

of the application operations on the chip.

System DMA component mainly used to help the MPU and DSP perform data

memory transfer-specific tasks, leaving more

available MIPS for both processors.

DSP subsystem based on a TMS320C55x™ DSP core, which is

responsible for intensive data computing tasks like

real-time audio and video handling on application

side, e.g. voice recording.

Internal memory subsystem composed of a single port SRAM.

Secure modules Helen3 (OMAP1710) contains a set of several

components, including ROM, a single port SRAM, and

eFUSE cells. These components enable the system to

support secure applications.

Memory interfaces The memory interfaces define the system memory

access organization of Helen3 (OMAP1710).

Issue 1 Company Confidential Page 1–9

Copyright ©2005 Nokia. All Rights Reserved.

Page 10

RM-84/99

Nokia Customer Care System Module

Section Description

USB & modem interface These two modules enable the platform to support a

universal serial link and a dedicated modem

interface, enabling a high data transfer rate between

the modem and the application chip.

System components System components are group of modules

responsible for managing system interactions such

as interrupt, clock control and idle.

Peripheral subsystem The peripheral subsystem defines all the

components used to interface Helen3 (OMAP1710)

with specific external devices such as camera,

keyboard, display, etc.

Absolute maximum ratings

Signal Min Nom Max Unit Notes

Battery voltage (idle) -0.3 +4.5 V Battery voltage maximum value is

specified during charging is active

Battery voltage (Call) +3.

2

Charger input voltage -0.3 +16V V

Back-Up supply voltage 0 2.5 2.7 V Maximum capacity of the backup

+4.3 V Battery voltage maximum value is

specified during charging is active

power supply assumed to be 15 µAh.

Phone modes of operation

Mode Description

NO_SUPPLY (dead) mode means that the main battery is not present or its voltage is too low (below

RETU master reset threshold) and that the back-up battery voltage is too low.

BACK_UP The main battery is not present or its voltage is too low but back-up battery voltage is

adequate and the 32kHz oscillator is running (RTC is on).

PWR_OFF In this mode (warm), the main battery is present and its voltage is over RETU master reset

threshold. All regulators are disabled, PurX is on low state, the RTC is on and the oscillator

is on. PWR_OFF (cold) mode is almost the same as PWR_OFF (warm), but the RTC and the

oscillator are off.

RESET RESET mode is a synonym for start-up sequence. In this mode certain regulators are

enabled and after they and RFClk have stabilized, the system reset (PurX) is released and

PWR_ON mode entered. RESET mode uses 32kHz clock to count the REST mode delay

(typically 16ms).

Page 1–10 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 11

RM-84/99

System Module Nokia Customer Care

Mode Description

SLEEP SLEEP mode is entered only from PWR_ON mode with the aid of SW when the system’s

activity is low. There are in principle three different sleep modes:

• OMAP1710 sleep

• RAP3G sleep

• OMAP and RAP3G sleep (deep sleep)

In SLEEP mode RETU’s regulators VIO, VDRAM, VSIM1, VSIM2, VAUX and Vana are in low

quiescent current mode (output voltages still present but regulators will not give as much

current out). Other regulators including VR1 supplying system clock oscillator are

disabled.

In SLEEP mode, TAHVO VCORE SMPS regulator is in low quiescent current mode (if sleep

mode is not internally disabled). Linear regulator VOUT state depends on the accessory

connected to the system connector (Pop-Port), if there is any.

FLASHING FLASHING mode is for SW downloading. FLASHING mode is not really a RETU or TAHVO

state but rather a system state. From RETU and TAHVO point of view, it is like PWR_ON.

The state is entered from PWR_ON. It is possible to use external voltage (VPP) during

flashing to speed up the process (provided that the memory components support the

feature).

Issue 1 Company Confidential Page 1–11

Copyright ©2005 Nokia. All Rights Reserved.

Page 12

RM-84/99

Nokia Customer Care System Module

Figure 4 State diagram

Voltage limits

Parameter Description Value

VMSTR Master reset threshold (RETU) 2.2V (typ.)

Threshold for charging, rising

VMSTR+

VMSTR-

VCOFF+ Hardware cutoff (rising) 2.9V (typ.)

VCOFF- Hardware cutoff (falling) 2.6V (typ.)

SWCOFF SW cutoff limit ~3.2V

Page 1–12 Company Confidential Issue 1

(TAHVO) 2.1V (typ.)

Threshold for charging, falling

(TAHVO) 1.9V (typ.)

Copyright ©2005 Nokia. All Rights Reserved.

Page 13

RM-84/99

System Module Nokia Customer Care

The master reset threshold controls the internal reset of Retu / (Tahvo). If battery voltage is above VMSTR,

Tahvo’s charging control logic is alive. Also, RTC is active and supplied from the main battery. Above VMSTR,

Tahvo allows the system to be powered on although this may not succeed due to voltage drops during start

up. SW can also consider battery voltage too low for operation and power down the system.

Power key

The system boots up when power key is pressed (adequate battery voltage, VBAT, present).

Power down can be initiated by pressing the power key again (the system is powered down with the aid of

SW). Power on key is connected to Retu ASIC via PWRONX signal.

Issue 1 Company Confidential Page 1–13

Copyright ©2005 Nokia. All Rights Reserved.

Page 14

RM-84/99

Nokia Customer Care System Module

Power distribution

Figure 5 Power distribution diagram

Power supply components:

• RETU

• TAHVO

• Helen VCORE SMPS

• BT

• LDO

• camera LDO

Page 1–14 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 15

RM-84/99

System Module Nokia Customer Care

• backlight SMPS

All the above are powered by the main battery voltage.

Battery voltage is also used on the RF side for power amplifiers (GSM PA & WCDMA PA) and for RF ASICs Hinku

(Rx) & Vinku(Tx).

Discrete power supplies are used to generate 2.8V to BT, 1.5V for the camera IO voltage, 2.8V for the front camera

IO voltage, 1.3V/1.5V for Helen 3 and 18V for the backlight LEDs.

The device supports both 1.8V/3V SIM cards which are powered by RETU / VSIM1. RETUs VSIM2 is used to power

RS MMC 1.8V only. USB accessories which needs power from the device are powered by TAHVO / VOUT.

Because LED driver in TAHVO is not used, the external SMPS is used instead. External LED SMPS is still controlled

by TAHVO and powered by battery voltage.

System power-up

After inserting the main battery, regulators started by HW are enabled. SW checks, if there is some reason to

keep the power on. If not, the system is set to power off state by watchdog. Power up can be caused by the

following reasons:

• Power key is pressed

• Charger is connected

• RTC alarm occurs

• MBUS wake-up

After that:

• Retu activates sleep clock and VANA, VDRAM, VIO and VR1 regulators.

• Voltage appearing at Retu’s RSTX pin is used for enabling Tahvo ASIC.

• Tahvo enables VCORE regulator and its internal RC-oscillator (600kHz).

• VCTCXO regulator is set ON and RF clock (main system clock) is started to produce.

• Retu will release PURX ~ 16ms after power up is enabled (the RF clock is then stable enough).

• Synchronizing clock (2.4MHz) for Tahvo is started to be produced. After PURX is released and two rising edges

of 2.4MHz synchronous clock have been detected in SMPSClk input Tahvo is starting to use that instead of

600kHz internal RC-oscillator.

• HW start-up procedure has been finalized and the system is up and running. Now it is possible for SW to

switch ON other needed regulators.

Issue 1 Company Confidential Page 1–15

Copyright ©2005 Nokia. All Rights Reserved.

Page 16

RM-84/99

Nokia Customer Care System Module

Figure 6 System start-up timing

Clocking scheme

There are two main clocks in the system: 38.4MHz RF clock produced by VCTCXO in RF section and 32.768kHz

sleep clock produced by RETU with an external crystal.

RF clock is generated only when VCTCXO is powered on by RETU regulator. Regulator itself is activated by SleepX

signals from both RAP3G and Helen3. When both CPUs are on sleep, RF clock is stopped.

RF clock is used by RAP3G that then provides (divided) 19.2MHz SysClk further to OMAP. Both RAPG and Helen3

have internal PLLs which then create clock signals for other peripheral devices/interfaces like RS MMC, SIM, CCP,

I2C and memories.

32k Sleep Clock is always powered on after startup. Sleep clock is used by RAP3G and OMAP for low-power

operation.

SMPS Clk is 2.4MHz clock line from RAP3G to Tahvo used for switch mode regulator synchronizing in active

mode. In deep sleep mode, when VCTCXO is off, this signal is set to '0'-state.

BT Clk is 38.4MHz signal from Hinku ASIC to the Bluetooth system.

CLK600 is 600KHz signal from Tahvo to APE VCORE SMPS. The clock source is internal RC oscillator in Tahvo (during

the power-up sequence) or RAP3G SMPS Clk divided by 4 after the power-up sequence.

Page 1–16 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 17

RM-84/99

System Module Nokia Customer Care

Figure 7 Clocking scheme

Bluetooth/FM module

The Bluetooth and FM radio solutions of the device are realised with a combined BTFM module. This module

has the Bluetooth solution and FM radio solution combined into a single component. However, the two solutions

are electrically isolated from one another.

Bluetooth

Bluetooth provides a fully digital link for communication between a master unit and one or more slave units.

The system provides a radio link that offers a high degree of flexibility to support various applications and

product scenarios. Data and control interface for a low power RF module is provided. Data rate is regulated

between the master and the slave.

The device Bluetooth is based on CSR's BC4 BT ASIC (BTHFM1.0).

The UART1 interface handles the transfer of control and data information between OMAP1710 and the BT system

(BC4).

The PCM interface is used for audio data transfer between RAP3G and the BT system (BC4).

FM radio

The second part of the BTFM module contains the FM radio.

The antenna for the FM radio is provided by plugging in an external wired headset to the Pop-port™ connector.

It is not possible to listen to the FM radio without a wired headset connected. The FM radio is controlled by I2C

commands from RAP3G. The audio output of the FM radio is fed to the headset via the RETU ASIC, so the rest of

the phone can sleep while the FM radio is active.

USB

USB (Universal Serial Bus) provides a wired connectivity between a USB host PC and peripheral devices.

USB is a differential serial bus for USB devices. USB controller (RAP3G) supports USB specification revision 2.0

with full speed USB (12 Mbps). The device is connected to the USB host through the Pop-Port™ connector. The

USB bus is hot plugged capable, which means that USB devices may be plugged in/out at any time.

SIM interface

The device has one SIM (Subscriber Identification Module) interface. The SIM card is located under the battery.

The SIM interface consists of an internal interface between RAP3G and Retu and of an external interface between

Retu and SIM contacts. The main SIM interface functionality is in RAP3G while Retu takes care of power up/down,

card detection, ATR (Answer To Reset) counting and level shifting. For Retu external SIM IF connections, see SIM

interface connections (Page 1–39).

The SIM IF is shown in the following figure:

Issue 1 Company Confidential Page 1–17

Copyright ©2005 Nokia. All Rights Reserved.

Page 18

RM-84/99

Nokia Customer Care System Module

Figure 8 SIM interface

Retu handles the detection of the SIM card. The detection method is based in the BSI line. Because of the location

of the SIM card, removing the battery causes a quick power down of the SIM IF.

The Retu SIM1 interface supports both 1.8V and 3.0V SIM cards. The SIM interface voltage is first 1.8V when the

SIM card is inserted, and if the card does not response to the ATR a 3V interface voltage is used.

The data communication between the card and the phone is asynchronous half duplex, and the clock supplied

to the card is 1-5MHz, which is 3.2MHz by default (in GSM system). The data baud rate is the SIM card clock

frequency divided by 372 (by default), 64, 32 or 16.

RS MMC interface

The reduced size (24mm x 18mm x 1.4mm) multimedia card slot is located under the battery. The device

supports RS MMC hot insertion, which enables to remove/insert the card when the phone is powered on.

The RS MMC card is connected to the Helen3 processor MMC/SDIO2 (1.8V) interface. The MMC interface is shown

in the following figure:

Figure 9 MMC interface

The basic multimedia card concept is based on the following communication signals: CLK, CMD and DAT.

With each cycle of the CLK signal, one bit transfer on the DAT and CMD line is performed. The maximum CLK

frequency is 20MHz.

Page 1–18 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 19

RM-84/99

System Module Nokia Customer Care

CMD is a bi-directional command channel used for card initialization and data transfer commands. The CMD

signal has two operational modes: open-drain and push-pull mode. The open-drain mode is used for card

initialization and the push-pull mode for fast command transfer. CMD commands are sent by the host and CMD

responses are sent by the card.

DAT is a bi-directional data channel, which operates in the push-pull mode.

The detection of the RS MMC card removal/insertion is done via the RS MMC cover switch. The RS MMC cover

switch gives an interrupt to the SW when the cover is opened or closed. After opening the RS MMC cover lid (RS

MMC SW signal is connected to GND via cover switch), SW powers down the card and switches off the RS MMC

power supply (VSIM2). When the RS MMC cover lid is closed (RS MMC SW signal is internally connected in Helen3

to 1.8V), the card inserted is identified.

Note: Removing the RS MMC while writing to it, may corrupt the data stored in the card.

See Also

• RS MMC interface connections (Page 1–39)

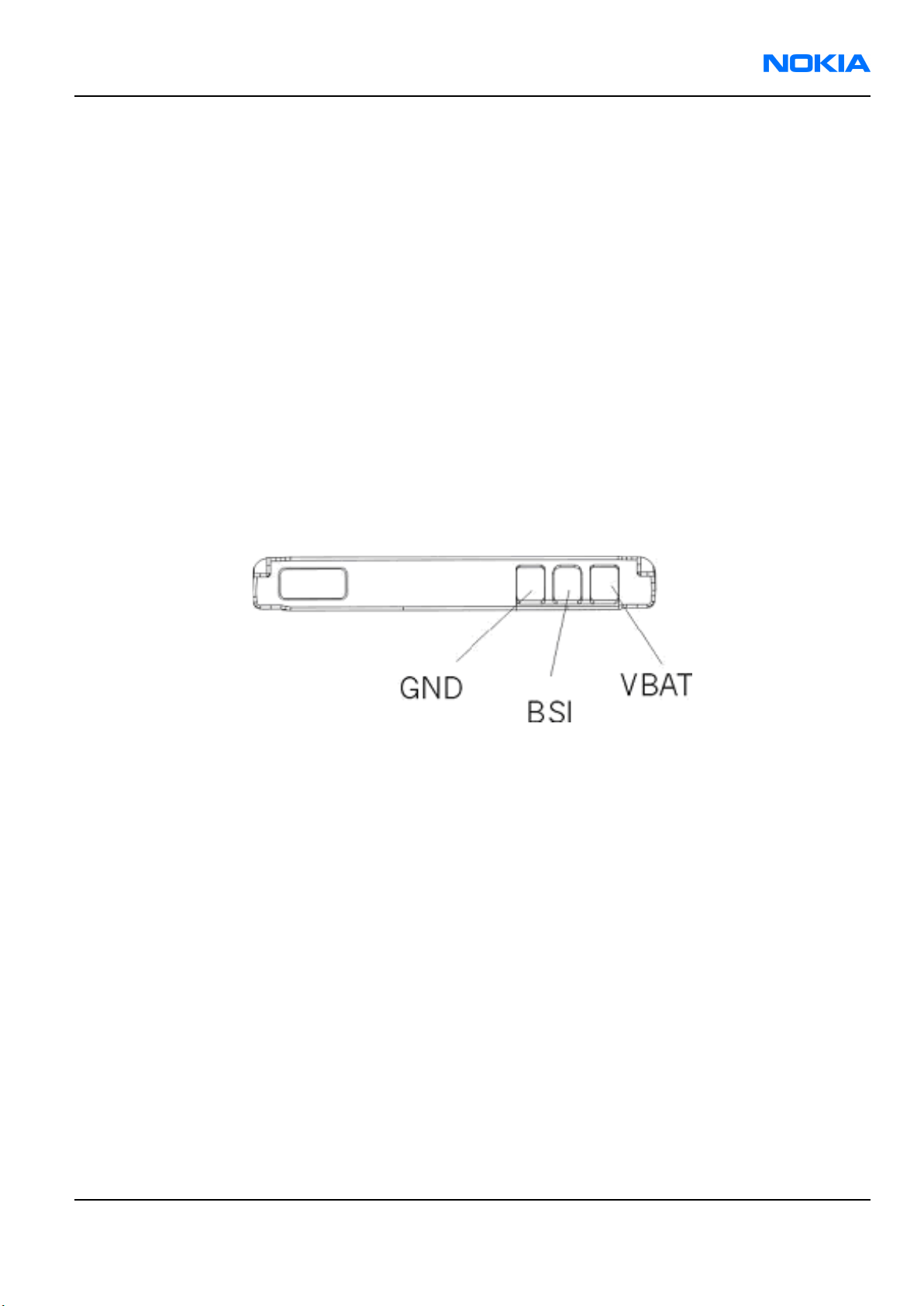

Battery interface

The battery interface supports the NMP 3-pole battery interface. The interface consists of three connectors:

VBAT, BSI and GND.

The BSI line is used to recognize the battery capacity by a battery internal pull down resistor.

Figure 10 Battery pin order

Battery temperature is estimated by measuring separate battery temperature NTC via the BTEMP line, which is

located on the transceiver PWB, at a place where the phone temperature is most stabile.

For service purposes, the device SW can be forced into local mode by using pull down resistors connected to

the BSI line.

Camera interfaces

Back camera

The back camera of the device uses a 2.0 megapixel camera module with a sensor resolution of 1600 x 1200.

The following block diagram shows how a CCP bus is used to transfer image data from the camera module to

the phone engine. This bi-directional control bus is a software-implemented I2C interface.

The camera regulator N1470 powers the digital parts of the camera, and a VAUX power rail is used for powering

the analogue parts.

A CAMVCTRL signal (Vctrl) is used for activating the camera module. When the Vctrl signal is High, the module

enters the power on mode. When the signal is Low, the module enters the power off mode.

A CAMCLK signal feeds the system clock for the camera module.

Issue 1 Company Confidential Page 1–19

Copyright ©2005 Nokia. All Rights Reserved.

Page 20

RM-84/99

Nokia Customer Care System Module

Figure 11 Block diagram of the back camera module

Camera construction

This section describes the mechanical construction of the camera module for getting a better understanding

of the actual mechanical structure of the module.

Table 1 Camera specifications

Sensor type CMOS Sensor

Photo detectors 2 million

F number/Aperture f/3.2

Focal length 4.8 mm (35 mm equivalent 37 mm)

Focus range 40 cm to infinity

Still Image resolutions 1600 x 1200, 640 x 480

Still images file format EXIF (JPEG), *.jpg

Video resolutions 352 x 288, 176 x 144, 128 x 96. All 15 frames per

second

Video clip length Maximal clip length is 1 hour or limited to MMS size

Video file format MPEG-4 *.mp4 and 3GPP, *.3gp

Exposure Automatic

White Balance Automatic or adjustable

Page 1–20 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 21

RM-84/99

System Module Nokia Customer Care

ISO 250 – 1000 (Automatic)

Colours 16.7 million / 24-bit

Capture Modes Still capture: Auto, User, Portrait, Landscape, Night,

Sports

Video capture: Normal and Night

Figure 12 Camera module cross section and assembly principle

Figure 13 Camera module bottom view including serial numbering

Issue 1 Company Confidential Page 1–21

Copyright ©2005 Nokia. All Rights Reserved.

Page 22

RM-84/99

Nokia Customer Care System Module

The camera module as a component is not a repairable part, meaning that the components inside the module

may not be changed. Cleaning dust from the front face is allowed only. Use clean compressed air.

The camera module uses socket type connecting. For versioning, laser marked serial numbering is used on the

PWB.

The main parts of the module are:

• Lens unit including lens aperture.

• Infrared filter; used to prevent infrared light from contaminating the image colors. The IR filter is glued to

the EMI shielded camera body.

• Camera body; made of conductive metallized plastic and attached to the PWB with glue.

• Sensor array including DSP functions is glued and wire-bonded to the PWB.

• PWB, FR-4 type

• Passive components

• Camera protection window; part of the phone cover mechanics

• Dust gasket between the lens unit and camera protection window

Back camera slider detection switch

The back camera and flash LED have a cover slider, which position is detected with a slider switch (slider sensor).

When the slider covers the back camera and flash LED (upper position), the slider switch is open circuit (not

pressed) and the OMAP1710 is connected to VIO. When the slider is slid down, the switch is pressed and it

connects the Helen pin mcbsp1_sync to GND (typical 160mV) and activates the back camera application

Page 1–22 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 23

RM-84/99

System Module Nokia Customer Care

Figure 14 Slider switch connection

Flash LED

The device back camera has a flash LED (FLED), providing better lighting conditions in darker environments. The

same LED is also used as an indicator light to indicate video clip recording.

The FLED is located next to the back camera under the camera slide. It cannot be used when the slide is closed,

and it is only used in the still image mode or as an indicator for video recording or image capturing. The

operating range of the FLED is approximately 1 m (~22 Lux) and 1.5 m (~9 Lux).

The connections between the main PWB and the FLED are implemented with a small PWB attached to the device

mechanics.

The FLED has four white LEDs connected in series in one module. The module also includes a lens with its plastic

housing.

The dimensions of the FLED are 6.5 x 7.5 x 3.5 mm.

Issue 1 Company Confidential Page 1–23

Copyright ©2005 Nokia. All Rights Reserved.

Page 24

RM-84/99

Nokia Customer Care System Module

Figure 15 Simplified flash LED connection

Front camera

The front camera has VGA (640x480) resolution, and it is mainly used for video calls. It can also be used as a still

camera and camcorder.

The front camera is controlled and its data is collected by Helen APE. The I/O voltage of Helen is 1.8V and the I/

O voltage of the camera is 2.8V. Because of this, a level shifter is used for the interface between Helen and the

camera.

The front camera has the following characteristics:

Sensor type: CMOS

Sensor Photo detectors: VGA

F number/Aperture: f/2.9

Focal length: 4.5 mm

Focus range: 40 cm to infinity

Still Image resolutions: 640 x 480

Video resolutions: 176 x 144, 128 x 96 both 15 frames per second.

Video clip length: 30 seconds or free, maximal clip length in free mode is 1

hour

Video file format: MPEG-4 *.mp4 and 3GPP, *.3gp (64 kbps in short clip

mode, 128 kbps in maximum mode)

Exposure: Automatic and manual

White Balance: Automatic or adjustable

ISO: 250 - 1000 (Automatic)

Capture Modes: Still capture mode, video mode, sequence mode 10,20 or

30 seconds.

Page 1–24 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 25

RM-84/99

System Module Nokia Customer Care

Figure 16 Front camera connections

User interface

Display interface

Display module mechanical concept

Figure 17 General diagram of the LCD module

Display features:

• 262,144 colours

Issue 1 Company Confidential Page 1–25

Copyright ©2005 Nokia. All Rights Reserved.

Page 26

RM-84/99

Nokia Customer Care System Module

• Partial display function Power saving by pausing display process on part of the screen.

• Built-in RAM capacity 176rows x 208lines x 18bits = 658,944 bits

The display has two different operating modes:

1 Normal mode, Full screen, 260k colours

2 Normal Partial mode, 260k colors but only part of the display is active

The module includes:

• FPWB foil including connector and discretes and driver circuits

• display panel (glass)

• drivers including display controller and 176 x 208 x 18 bits RAM

• backlight system: lightguide, LEDs and necessary optical sheets

• supporting mechanics

• metal frame (stainless steel)

• plastic frame

The interconnection between the LCD module and the Nokia engine is implemented with a 24-pin board-toboard connector.

Display is controlled via MeSSi-8 interface by Helen3. All MeSSi-8 signals go through the EMC filtering ASIPs.

The display module does not require any tunings in service.

Keyboard

The device keyboard is connected to the main PWB with a board-to-board connector.

The keymatrix has six rows and four columns. The voice key on the main PWB and the navigation key are

connected to the same keymatrix.

Table 2 Keymatrix

Key Row# kbc_# Column# kbr# Switch Ref.

0 6 0 U21

1 3 2 U19

2 2 1 U14

3 2 2 U16

4 5 3 U23

5 3 0 U18

6 3 3 U20

7 2 0 U15

8 2 3 U17

9 4 0 U22

* 4 1 U21

# 4 3 S2

END 5 0 U13

SEND 1 1 U1

EDIT 6 1 U11

Page 1–26 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 27

RM-84/99

System Module Nokia Customer Care

Key Row# kbc_# Column# kbr# Switch Ref.

CLEAR 6 2 U10

APPS 6 3 U12

Operator 5 2 U9

NAVI Left 0 2 S320

NAVI Right 0 3

NAVI Up 1 2

NAVI Down 1 3

NAVI Select 1 0

Left Soft Key 0 0 U7

Right Soft Key 0 1 U6

Camera 4 2 S1

Voice Not Required

Issue 1 Company Confidential Page 1–27

Copyright ©2005 Nokia. All Rights Reserved.

Page 28

RM-84/99

Nokia Customer Care System Module

Keyboard layout

Figure 18 Keyboard layout

Display and keyboard backlight

The device has one LED Driver (SMPS) that is used to drive both display and keyboard LEDs.

The LED driver consists of two LED chains: display LED chain and keyboard LED chain. Both chains contain four

LEDs, eight in total.

The current adjustment of the driver is done from the display LED branch. The keyboard current also depends

on the display brightness.

Typically, keyboard LEDs are turned ON only in dark ambient lighting conditions.

Page 1–28 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 29

RM-84/99

System Module Nokia Customer Care

Table 3 LED driver control signals

From To Voltage Function

GenOut1 TAHVO R2302 (10k) 0V / 1.8V Maximum current

GenOut2 TAHVO R2301 (4k7) 0V / 1.8V

control (0V ->max

curr.)

PWM TAHVO J2309, N2301 PWM 0%-100%,

1.8V

GenOut3 TAHVO V2300 0V / 1.8V Keyboard LEDs ON

Current PWM

control (16 steps)

(1.8V) /OFF (0V)

ALS interface

Ambient Light Sensor (ALS) is located in the upper part of the phone. It consists of the following components:

• lightguide (part of the front cover)

• phototransistor (V4400) + resistor (R4401)

• NTC + resistors (R4400, R4402, R4403)

• RETU EM ASIC (N2200)

Information on ambient lighting is used to control the backlights of the phone:

• Keypad lighting is switched on only when the environment is dark / dim

• Display backlights are dimmed, when the environment is dark / dim

The ambient light sensor itself is a photo transistor, which is temperature-compensated by an external NTC

resistor. Retu reads the light sensor (LS) and temperature (LST) results.

ALS calibration is not possible in the service points. ALS is serviced by replacing faulty phototransistors.

Figure 19 ALS HW implementation

Table 4 ALS resistor values

Symbol R1 R2 R3 R4 R5 R6 R7 NTC-res

470

Value 5 kOhm 15 kOhm 30 kOhm 50 kOhm

Issue 1 Company Confidential Page 1–29

Copyright ©2005 Nokia. All Rights Reserved.

kOhm

100

kohm

470

kohm 47 kOhm

Page 30

RM-84/99

Nokia Customer Care System Module

ASICs

RAP3G ASIC

RAP3G ASIC is a 3G Radio Application Processor. RAM memory is integrated into RAP3G.

In general RAP3G consists of three separate parts:

• Processor subsystem (PSS) that includes the main processor and related functions

• MCU peripherals that are mainly controlled by MCU

• DSP peripherals that are mainly controlled by DSP

RAP3G core voltage (1.4V) is generated from Tahvo VCORE and I/O voltage (1.8V) is from Retu VIO. The core

voltage in sleep mode is lowered to 1.05V.

Retu EM ASIC

Retu EM ASIC includes the following functional blocks:

• Start up logic and reset control

• Charger detection

• Battery voltage monitoring

• 32.768kHz clock with external crystal

• Real time clock with external backup battery

• SIM card interface

• Stereo audio codecs and amplifiers

• A/D converter

• Regulators

• Vibra interface

• Digital interface (CBUS)

Tahvo EM ASIC

Tahvo EM ASIC includes the. following functional blocks:

• Core supply generation

• Charge control circuitry

• Level shifter and regulator for USB/FBUS

• Current gauge for battery current measuring

• External LED driver control interface

• Digital interface (CBUS)

Device memories

RAP3G memories NOR flash and SDRAM

Modem memory consists of 64 Mbit SDRAM and 64 Mbit NOR flash memories.

SDRAM is a dynamic memory for ISA (Intelligent Software Architecture) SW.

NOR is used for ISA SW code and PM data and CDSP (Cellular Digital Signal Processor) SW code.

16-bit wide SDRAM interface consists of a DDR SDRAM controller from ARM, DCDL/DLLs and wrapper logic. 32-bit

wide flash interface is implemented by using an EMC module.

SDRAM core voltage (1.8V) is generated from Retu VDRAM and I/O voltage (1.8V) is from VIO. NOR flash uses VIO

for both core and I/O voltages.

Page 1–30 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 31

RM-84/99

System Module Nokia Customer Care

Combo memory

The application memory of the device consists of NAND/DDR combo memory. The stacked DDR/NAND application

memory has 512 Mbits of DDR memory and 512 Mbits of flash memory. DDR DRAM memory is stacked above

the NAND flash.

OMAP includes a 16-bit dedicated memory interface called External Memory Interface Fast (EMIFF). This is used

to support an interface for the DDR memory. Helen3 (OMAP1710) provides also a NAND flash controller located

in the shared peripheral bus, providing support for 8-bit NAND flash. The interface requires an 8-bit address bus

multiplexed with 8-bit data bus and several control signals.

The core voltage for DDR is 1.8V, which is generated by a discrete LDO (LP3999-1.8). 1.8V (VIO) is for DDR I/O

voltage. Both NAND core and I/O voltages are 1.8V generated by VIO.

Audio concept

Audio HW architecture

The functional core of the audio hardware is built around two ASICs: RAP 3G CMT engine ASIC and the mixedsignal ASIC Retu.

Retu provides an interface for the transducers and the accessory connector. Because audio amplifiers are also

integrated into Retu, the only discrete electronics components needed for audio paths are audio filtering

components and EMC/ESD components.

There are three audio transducers:

• 8mm dynamic earpiece

• 16mm dynamic speaker

• electret microphone module

In addition to the audio transducers, Retu also provides an output for the dynamic vibra component.

All galvanic audio accessories are connected to the Pop-Port™ accessory connector.

A Bluetooth audio module that is connected to RAP3G supports Bluetooth audio functionality.

There is a separate application ASIC, OMAP 1710, for Symbian applications.

Issue 1 Company Confidential Page 1–31

Copyright ©2005 Nokia. All Rights Reserved.

Page 32

RM-84/99

Nokia Customer Care System Module

Figure 20 Audio block diagram

Internal microphone

Internal microphone is used for HandPortable (HP) and Internal HandsFree (IHF) call modes.

An analogue electret microphone is connected to Retu ASIC’s Mic1P and Mic1N inputs via asymmetric electrical

connection.

The microphone is biased by Retu ASIC MicB1 bias voltage output.

Figure 21 Internal microphone circuitry

External microphone

Galvanic accessories are connected to the system connector (Pop-PortTM).

Page 1–32 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 33

RM-84/99

System Module Nokia Customer Care

Accessory audio mode is automatically enabled/disabled during connection/disconnection of dedicated phone

accessories.

External microphone circuitry is biased by Retu ASIC MicB2 bias voltage output. The circuitry provides a

symmetrical connection for the microphone from the Pop-PortTMconnections, XMICN and XMICP, to Retu ASIC

inputs, Mic2P and Mic2N.

Figure 22 External microphone circuitry (Pop-Port connects to the right side)

Internal earpiece

The internal earpiece is used in the HandPortable (HP) call mode. A dynamic 8 mm earpiece capsule is connected

to Retu ASIC’s differential outputs EarP and EarN.

Figure 23 Internal earpiece circuitry

Internal speaker

The internal speaker is used in Internal HandsFree (IHF) call mode.

A dynamic 16 mm speaker is connected to Retu ASIC’s outputs HFSpP and HFSpN.

The IHF amplifier integrated in Retu is a Digital Pulse Modulated Amplifier (DPMA).

Issue 1 Company Confidential Page 1–33

Copyright ©2005 Nokia. All Rights Reserved.

Page 34

RM-84/99

Nokia Customer Care System Module

Figure 24 Internal speaker circuitry

External earpiece

All galvanic accessories are connected to the system connector (Pop-Port™).

The accessory audio mode is automatically enabled/disabled during connection/disconnection of dedicated

phone accessories.

Retu ASIC provides two output channels in either single-ended or differential format. Retu ASIC outputs XearL

and XearLC form the left channel audio output, and XearR and XearRC the right channel audio output. XearLC

and XearRC are the ground pins if the output works in a single-ended operation.

In the Pop-Port™ side, HSEAR P and HSEAR N form the left channel output, and HSEAR R P and HSEAR R N the

right channel output. Respectively, HSEAR N and HSEAR R N are the ground pins if the output works in a singleended operation.

Figure 25 External earpiece circuitry (Pop-Port connected on the right)

Vibra circuitry

Vibra is used for vibra-alarm function.

The vibra motor is connected to the Retu ASIC VibraP and VibraN Pulse Width Modulated (PWM) outputs.

Page 1–34 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 35

RM-84/99

System Module Nokia Customer Care

Figure 26 Vibra circuitry

Pop-portTM connector

Pop-PortTM connector provides a fully differential 4–wire stereo line-level output connection and fully

differential 2-wire mono line-level or microphone level input connection.

The handsfree driver in Retu is meant for the headset.

The output is driven in a fully differential mode. In the fully differential mode, the handsfree pin is the negative

output and the HFCM pin is the positive output. The gain of the handsfree driver in the differential mode is 6 dB.

The earpiece and headset signals are multiplexed so that the outputs cannot be used simultaneously.

Figure 27 External audio connector

Table 5 Audio connector pin assignments

Pin #/ Signal

name

1/ Charge V Charge DC 0-9V/ 0.85A

2/ GND Charge GND - 0.85A 100mΩ (PWB+

3/ ACI ACI 1kbits/s Digital 0 / 47Ω Insertion &

4/ Vout DC out DC 2.78V 70 mA 100mΩ (PWB+

9 / XMIC N Audio in 300-8k 1Vpp &

Signal

description

Spectral range Voltage/

Current levels

2.5-2.78V

2.5V 90mA

2.5-2.78VDC

Max or nominal

serial

impedance

conn.)

conn.)

Notes

removal

detection

200mW

Issue 1 Company Confidential Page 1–35

Copyright ©2005 Nokia. All Rights Reserved.

Page 36

RM-84/99

Nokia Customer Care System Module

Pin #/ Signal

name

10 / XMIC P Audio in 300-8k 1Vpp &

11 / HEAR N Audio out 20-20k 1Vpp 10Ω

12 / HEAR P Audio out 20-20k 1Vpp 10Ω

13 / HEAR R N Audio out 20-20k 1Vpp 10Ω Not conn. in

14 / HEAR R P Audio out 20-20k 1Vpp 10Ω Not conn. in

Signal

description

Spectral range Voltage/

Current levels

2.5-2.78VDC

Max or nominal

serial

impedance

Notes

mono

mono

Baseband technical specifications

External interfaces

External interfaces

Name of Connection Connector reference

USB X2001

Charger X2000

Headset X2001

SIM X2700

RS MMC X5200

Battery connector X2070

ACI interface electrical characteristics

Description Parameter Min Typ Max Unit Notes

Accessory detection

Headset

detection

threshold

Headset

detection

hysteresis

Headset

detection

pull ups

1.75 1.9 2.05 V Retu specific

25 mV

1 2 4 uA

After Mbus is switched to HeadDet

Page 1–36 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 37

RM-84/99

System Module Nokia Customer Care

Description Parameter Min Typ Max Unit Notes

High-level

V

IH

0.7 x V

DDS

V

DDS

V RAP3G

input

voltage

(VDDS = 1.8V)

Low-level

V

IL

0 0.3 x V

DDS

V

input

voltage

High-level

V

OH

0.8 x V

DDS

V

DDS

V

output

voltage

Low-level

V

OL

0 0.22 x VDDS V

output

voltage

Rise/fall

tR/tF

25 ns

time

VOUT electrical characteristics

Description Parameter Min Max Unit Notes

Vout regulator

for external

accessories

VOUT 2.43 2.57 V Max load 90mA

specific

USB IF electrical characteristics

Description Parameter Min Max Unit Notes

Absolute

maximum

voltage on D+

and D-

Supply voltage VBUS 4.4 5.25 V

Supply current:

Functioning I

Suspended I

Unconfigured I

High-level

input voltage:

High (driven) V

High (floating) V

Low-level input

voltage

V

D+/D-

VBUS

VBUS

VBUS

IH

IHZ

V

IL

-1 4.6 V USB

specification

revision 2.0

100 mA

500 uA

100 mA

V

2

2.7 3.6

0.8 V

Issue 1 Company Confidential Page 1–37

Copyright ©2005 Nokia. All Rights Reserved.

Page 38

RM-84/99

Nokia Customer Care System Module

Description Parameter Min Max Unit Notes

Differential

V

DI

0.2 V |(D+) - (D-)|

input

sensitivity

Differential

V

CM

0.8 2.5 V Included VDI

input voltage

range

Low-level

V

OL

0 0.3 V

output voltage

High-level

V

OH

2.8 3.6 V

output voltage

(driven)

Output signal

V

CRS

1.3 2 V

crossover

voltage

FBUS interface electrical characteristics

Description Parameter Min Max Unit Notes

High-level

input voltage

V

IH

0.7 x V

DDSHV2

V

DDSHV2

V Helen2/3 specific

range

Low-level

V

IL

0 0.3 x V

DDSHV2

V

Input voltage

High-level

V

OH

0.8 x V

DDSHV2

V

DDSHV2

V

output

voltage

Low-level

V

OL

0 0.22 x V

DDSHV2

V

output

voltage

Rise/fall time

tR/tF

0 25 ns

(VDDSHV2 = 1.8V)

Headset hook detection interface (XMICN) electrical characteristics

Description Min Typ Max Unit Notes

Hook detection

threshold 1

Hook detection

threshold 2

Hook detection

hysteresis

1.25 1.35 1.45 V Two fixed

thresholds

0.5 0.6 0.7 V

inside Retu.

Selectable by

SW

25 mV

Hook detection

1 2 4 uA

pull ups

Page 1–38 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 39

RM-84/99

System Module Nokia Customer Care

Audio signal electrical characteristics

Description Parameter Typ Unit Notes

XMIC N Audio in 1 V

XMIC P Audio in 1 V

HSEAR N Audio out 1 V

pp

pp

pp

DC Offset 2.5-2.78V

DC Offset 2.5-2.78V

10Ω nominal serial

impedance

HSEAR P Audio out 1 V

pp

10Ω nominal serial

impedance

HSEAR R N Audio out 1 V

pp

10Ω nominal serial

impedance

Not connected in

mono

HSEAR R P Audio out 1 V

pp

10Ω nominal serial

impedance

Not connected in

mono

SIM IF connections

Pin Signal I/O Engine connection Notes

C1 VSIM Out Retu VSIM1 Supply voltage

to SIM card,

1.8V or 3.0V.

C2 SIMRST Out Retu SIM1Rst Reset signal to

SIM card

C3 SIMCLK Out Retu SIM1ClkC Clock signal to

SIM card

C5 GND - GND Ground

C7 SIMDATA In/Out Retu SIM1DaC Data input /

output

RS MMC interface connections

Pin Signal I/O Engine connection Notes

1 RSV NC NC Reserved for

future use

2 CMD <-> Helen2/3 MMC2_CMD Command/

Response

3 Vss1 GND Ground

4 V

DD

<- Retu VSIM2 VSIM2, supply

voltage 1.8

(Max 70mA)

Issue 1 Company Confidential Page 1–39

Copyright ©2005 Nokia. All Rights Reserved.

Page 40

RM-84/99

Nokia Customer Care System Module

Pin Signal I/O Engine connection Notes

5 CLK <- Helen2/3 MMC2_CLK External clock

for the MMC

card, Max 20

MHz

6 Vss2 GND Ground

7 DAT <-> Helen2/3 MMC2_DAT0 Bi-directional

data bus

- MMCDET -> Helen2/3 btwake1(in)

[P10]

Charger connector and charging interface connections & electrical characteristics

Figure 28 Charger connector

MMC card

detect

Table 6 Charging interface connections

Pin Signal I/O Engine connection Notes

1 Vchar In Tahvo VCharIn1, 2 Charging

voltage /

charger

detection,

Center pin

2 Charge GND Ground Charger ground

Table 7 Charging IF electrical characteristics

Description Parameter Min Max Unit Notes

Vchar V Charge 0 9 V Center pin

Vchar I Charge 0.85 A Center pin

Charge GND 0.85 A

Page 1–40 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 41

RM-84/99

System Module Nokia Customer Care

Description Parameter Min Max Unit Notes

Threshold for

V

MSTR+

2.1 V Typical value

charging, rising

(TAHVO)

Threshold for

V

MSTR-

1.9 V Typical value

charging,

falling (TAHVO)

Battery connector and interface connections & electrical characteristics

Figure 29 Battery connector

Table 8 Battery interface connections

Pin Signal I/O Engine connection Notes

1 VBAT -> Retu VBAT Battery voltage

2 BSI -> Retu BSI Battery size

indication

(fixed resistor

inside the

battery pack)

3 GND GND Ground

Table 9 Battery IF electrical characteristics

Description Parameter Max Unit

Operation voltage V

Current rating I

IN

IN

4.23 VDC

0.9 A

Internal interfaces

Internal interfaces

Name of Connection Connector reference

UI connector X4400

Display X4401

Back camera X1470

Front camera X1472

Issue 1 Company Confidential Page 1–41

Copyright ©2005 Nokia. All Rights Reserved.

Page 42

RM-84/99

Nokia Customer Care System Module

Name of Connection Connector reference

ALS V4400

Vibra M2100

Microphone B2100

Earpiece B2101

IHF speaker B2102

UI module connector and IF connections

Figure 30 UI connector

Table 10 User interface connections

Pin Signal I/O Engine connection Notes

1 GND GND

2 LED+ <- N2301 VLEDOUT2

3 Col2 -> Helen3 Kbc_2

->

4 LED-

->

5 Col1

6 GND GND

R2305 + V2300 SETCURR2

Helen3 Kbc_1

Discrete

Backlight SMPS

(controlled by

Tahvo)

Serial resistor +

Transistor

switch

(controlled by

Tahvo)

Voice switch

connection

Page 1–42 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 43

RM-84/99

System Module Nokia Customer Care

Pin Signal I/O Engine connection Notes

7 Row3 -> Helen3 Kbr_3

8 Row2 -> Helen3 Kbr_2

9 Row1 -> Helen3 Kbr_1

10 Row6 -> Helen3 Kbr_6

11 Row0 -> Helen3 Kbr_0

12 Col0 -> Helen3 Kbc_0

Voice switch

13 Row5 -> Helen3 Kbr_5

connection

14 Row4 -> Helen3 Kbr_4

15 GND GND

16 Col3 -> Helen3 Kbc_3

Keyboard interface electrical characteristics

Description Parameter Min Typ Max Unit Notes

High-level

V

IH

0.65* V

DDS

V

DDS

0.3+ V

DDS

V Row

input voltage

Low-level

V

IL

-0.3 0 0.35* V

DDS

V Row

input voltage

High-level

V

OH

1.62 V

DDS

1.98 V Column

output

voltage

Low-level

V

OL

0 0.45 V Column

output

voltage

(VDDS = 1.8V)

Issue 1 Company Confidential Page 1–43

Copyright ©2005 Nokia. All Rights Reserved.

Page 44

RM-84/99

Nokia Customer Care System Module

Display connector and interface connections

Figure 31 Display connector

Table 11 Display interface connections

Pin Signal I/O Engine connection Notes

1 GND

WRX

2

3 GND

4 D0 <-> Helen3 Lcdda0 Data

5 D1 <-> Helen3 Lcdda1 Data

6 D2 <-> Helen3 Lcdda2 Data

7 D3 <-> Helen3 Lcdda3 Data

8 GND

VDDI

9

10 VDD <- Retu VAUX Core voltage

11 GND

-> Helen3 Lcdwrx

<- Retu VIO

Write Enable

(active low)

Interface

voltage

LEDin

12

13 LEDout -> R2304 SETCURR1 Sink resistor

14 GND

Page 1–44 Company Confidential Issue 1

<- N2301 VLEDOUT1

Copyright ©2005 Nokia. All Rights Reserved.

N2301 is

controlled by

Tahvo

Page 45

RM-84/99

System Module Nokia Customer Care

Pin Signal I/O Engine connection Notes

CSX

15

D/CX

16

17 GND

18 D7 <-> Helen3 Lcdda7 Data

19 D6 <-> Helen3 Lcdda6 Data

20 D5 <-> Helen3 Lcdda5 Data

21 D4 <-> Helen3 Lcdda4 Data

22 TE -> Helen3 Te Tearing Effect

RDX

23

RESX

24

<- Helen3 Lcdcsx

<- Helen3 Lcdcmd

<- Helen3 Lcdrdx

<- Helen3 Gpio_60

Chip Select

(active low)

Data/

Command

select

(high=data,

low

=command)

Read Enable

(active low)

Reset (active

low)

Camera interface connections and electrical characteristics

Table 12 Camera interface connections

Pin Signal I/O Engine connection Notes

1 GND1

2 SDA <-> Helen3 sda

3 D+ -> Helen3 Ccpdap

4 SCL <- Helen3 scl

5 D- -> Helen3 Ccpdan

Ground line

corresponding

to VDD

I2C serial

control bus

data

Differential

serial data,

positive node

I2C serial

control bus

clock

Differential

serial data,

negative node

System clock

for camera

6 CAMCLK <- Helen3 ExtClk

Issue 1 Company Confidential Page 1–45

Copyright ©2005 Nokia. All Rights Reserved.

module

Page 46

RM-84/99

Nokia Customer Care System Module

Pin Signal I/O Engine connection Notes

Camera Digital

7 VDDI <- Regulator VCAM

8 GND3

9 CLK+ -> Helen3 Ccpclkp

10 CAMVCTRL <- Helen3 VCtrl

11 CLK- -> Helen3 Ccpclkn

12 VDD <- Retu VAUX

Voltage

Ground line

corresponding

to ExtClk

Differential

serial clock,

positive node

Camera

module

activating

signal

Differential

serial clock,

negative node

Camera

Analog

Voltage

Strobe timing

13 Strobe -> Camera Cam_strobe

14 GND2

Table 13 Camera CCP IF electrical characteristics

Description Parameter Min Typ Max Unit Notes

Common

mode

voltage

Differential

voltage

swing

Operating

frequency

Differential

rise and fall

time

VCMF 0.8 0.9 1 V -1

VOD 100 150 250 mV -2

fCLK 1 175 MHz SW controls

300 800 ps -3

pulse

Ground line

corresponding

to VDDI

frequency

Note:

• Common mode voltage is a mean value of high and low states of one single-ended signal.

• Differential voltage swing is differential amplitude between signals of differential pair.

• Differential transitions should be only measured with good equipment (bandwith > 1GHz),

otherwise results will seem too slow.

Page 1–46 Company Confidential Issue 1

Copyright ©2005 Nokia. All Rights Reserved.

Page 47

RM-84/99

System Module Nokia Customer Care

Table 14 Camera supply voltage characteristics

Description Parameter Min Typ Max Unit

Camera analog

voltage

Camera digital

voltage

Description Parameter Min Typ. Max Unit Notes

SDA, SCL,

Vctrl, ExtClk

SDA, SCL,

Vctrl, ExtClk

SDA VOL 0 - 0.4 V High-level

Regulator

Enable

VDD 2.37 2.5 2.63 V

VDDI 1.4 1.5 1.65V V

Table 15 Camera control IF electrical characteristics

VIH 1.5 1.8 VDD V High-level

input

voltage

VIL 0 - 0.54 V Low-level

input

voltage

output

voltage

VOH 1.35 1.8 2.3V V Helen3 GPIO

High-level

output

voltage

Cam_strobe VOH 0.8 x VDD - VDD High-level

output

voltage

Cam_strobe VOL 0 - 0.4 V Low-level

output