Page 1

PAMS Technical Documentation

NSM–1 Series Transceivers

System Module

Issue 2 01/00

Page 2

NSM–1

PAMS

System Module

CONTENTS

Transceiver NSM–1 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Introduction 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Mode Description 3–6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Interconnection Diagram 3–7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Module 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Description 3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External and Internal Connectors 3–8. . . . . . . . . . . . . . . . . . . . .

System Connector Contacts 3–9. . . . . . . . . . . . . . . . . . . . . . .

RF Connector Contacts 3–10. . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply Voltages and Power Consumtion 3–10. . . . . . . . . . . .

Power Distribution Diagram 3–11. . . . . . . . . . . . . . . . . . . . . . .

Baseband Module 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Block Diagram 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Summary 3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Bottom Connector External Contacts 3–14. . . . . . . . . . . . . . .

Bottom Connector Signals 3–14. . . . . . . . . . . . . . . . . . . . . . . .

Battery Connector 3–16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SIM Card Connector 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Microphone 3–17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Infrared Module Connections 3–17. . . . . . . . . . . . . . . . . . . . . .

RTC Backup Battery 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Buzzer 3–18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Baseband Power Distribution 3–19. . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery charging 3–19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Startup Charging 3–20. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Overvoltage Protection 3–21. . . . . . . . . . . . . . . . . . . .

Battery Removal During Charging 3–22. . . . . . . . . . . . . . . . . .

Different PWM Frequencies ( 1Hz and 32 Hz) 3–23. . . . . . .

Battery Identification 3–24. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Battery Temperature 3–25. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply Voltage Regulators 3–25. . . . . . . . . . . . . . . . . . . . . . . .

Switched Mode Supply VSIM 3–27. . . . . . . . . . . . . . . . . . . . . .

Power Up 3–27. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power up with a charger 3–28. . . . . . . . . . . . . . . . . . . . . . . . . .

Power Up With The Power Switch (PWRONX) 3–28. . . . . . .

Power Up by RTC 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Up by IBI 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Acting Dead 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Active Mode 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Sleep Mode 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Charging 3–29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Off 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Technical Documentation

Page 3–2

Issue 2 01/00

Page 3

PAMS

NSM–1

Technical Documentation

Watchdog 3–30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Audio control 3–31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

External Audio Connections 3–32. . . . . . . . . . . . . . . . . . . . . . .

Analog Audio Accessory Detection 3–33. . . . . . . . . . . . . . . . .

Headset Detection 3–33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Audio Connections 3–34. . . . . . . . . . . . . . . . . . . . . . . .

4–wire PCM Serial Interface 3–34. . . . . . . . . . . . . . . . . . . . . . .

Alert Signal Generation 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . .

Digital Control 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MAD2 3–35. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Memories 3–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Program Memory 3–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

SRAM Memory 3–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

EEPROM Memory 3–45. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MCU Memory Map 3–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Flash Programming 3–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

COBBA–GJ 3–46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Infrared Transceiver Module 3–47. . . . . . . . . . . . . . . . . . . . . . .

Real Time Clock 3–47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RTC backup battery charging 3–48. . . . . . . . . . . . . . . . . . . . . .

Vibra Alerting Device 3–48. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

IBI Accessories 3–49. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Phone Power–on by IBI 3–49. . . . . . . . . . . . . . . . . . . . . . . . . . .

IBI power–on by phone 3–49. . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Module 3–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Description 3–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF block 3–50. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum Ratings 3–51. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF Frequency Plan 3–52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power Distribution Diagram 3–53. . . . . . . . . . . . . . . . . . . . . . . . . .

DC Characteristics 3–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Regulators 3–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Control Signals 3–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Frequency synthesizers 3–54. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver 3–56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter 3–58. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AGC strategy 3–61. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AFC function 3–62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Receiver blocks 3–62. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX interstage filter GSM 3–62. . . . . . . . . . . . . . . . . . . . . . . . . . . .

RX interstage filter DCS1800 3–62. . . . . . . . . . . . . . . . . . . . . . . .

GSM UHF–mixer in CRFU3 3–62. . . . . . . . . . . . . . . . . . . . . . . . .

DCS1800 UHF–mixer in CRFU3 3–63. . . . . . . . . . . . . . . . . . . . .

Transmitter Blocks 3–63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TX interstage filter GSM 3–63. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Module

Issue 2 01/00

Page 3–3

Page 4

NSM–1

PAMS

System Module

TX interstage filter DCS1800 3–63. . . . . . . . . . . . . . . . . . . . . . . .

Power amplifier MMIC GSM 3–63. . . . . . . . . . . . . . . . . . . . . . . . .

Power amplifier MMIC DCS1800 3–63. . . . . . . . . . . . . . . . . . . . .

Synthesizer blocks 3–64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

VHF VCO 3–64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF PLL 3–64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF PLL block in SUMMA 3–64. . . . . . . . . . . . . . . . . . . . . . . . . .

UHF VCO module 3–64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

UHF local signal input in CRFU3 3–65. . . . . . . . . . . . . . . . . . . . .

Connections 3–65. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

RF connector and antenna switch 3–65. . . . . . . . . . . . . . . . . . . .

Timings 3–70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synthesizer control timing 3–70. . . . . . . . . . . . . . . . . . . . . . . . . . .

Transmitter power switching timing diagram 3–72. . . . . . . . . . .

Synthesizer clocking 3–72. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parts list of UG3 (EDMS Issue 6.3) Code: 0201113 3–73. . . . . . . . . .

Technical Documentation

Parts list of UG3 (EDMS Issue 9.6) Code: 0201113 3–83. . . . . . . . . .

Parts list of UG3MA (EDMS Issue 1.1) Code: 0201380 3–83. . . . . .

Parts list of UG3MA (EDMS Issue 4.6) Code: 0201380 3–83. . . . . .

Schematic Diagrams: UG3

Block Diagram of Baseband (Version 2.1 Edit 98) layout version 9.1 UG3/A3–1

Block Diagram of COBBA, CCONT and MAD UG3/A3–2. . . . . . . . . . . . . . .

Circuit Diagram of Power Supply (Version 2.2 Edit 295) layout 10.3 UG3/A3–3.

Circuit Diagram of SIM Connector (Version 2.2 Edit 97) layout 10.3 UG3/A3–4

Circuit Diagram of CPU Block (Version 2.2 Edit 200) layout 10.3 UG3/A3–5. .

Circuit Diagram of Audio (Version 2.2 Edit 155) layout 10.3 UG3/A3–6. .

Circuit Diagram of IR Module (Version 2.2 Edit 126) for layout 10.3 UG3/A3–7

RF Block Diagram UG3/A3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Diagram of RF Block (Version 2.2 Edit 382) for layout 10.3 UG3/A3–9.

Circuit Diagram of UIF (Version 2.2 Edit 124) for layout 10.3 UG3/A3–10.

Layout Diagram of UG3 – Top (Version 10.3) UG3/A3–11. . . . . . . . . . . . . . .

Layout Diagram of UG3 – Bottom (Version 10.3) UG3/A3–11. . . . . . . . . . . .

Testpoint references UG3/A3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Diagram of Power Supply (Version 2.26 Edit 314) UG3/A3–13. . . . .

Circuit Diagram of CPU Block (Version 2.26 Edit 217) UG3/A3–14. . . . . . .

Page 3–4

Issue 2 01/00

Page 5

PAMS

NSM–1

Technical Documentation

Circuit Diagram of UIF (Version 2.26 Edit 138) UG3/A3–15. . . . . . . . . . . . .

Circuit Diagram of SIM Connector (Version 2.26 Edit 110) UG3/A3–16. . . .

Circuit Diagram of RF Block (Version 2.26 Edit 328) UG3/A3–17. . . . . . . .

Circuit Diagram of Audio (Version 2.26 Edit 169) UG3/A3–18. . . . . . . . . . .

Circuit Diagram of IR Module (Version 2.26 Edit 139) UG3/A3–19. . . . . . .

Layout Diagram of UG3 – TOP (Version 11) UG3/A3–20. . . . . . . . . . . . . . . .

Layout Diagram of UG3 – BOTTOM (Version 11) UG3/A3–20. . . . . . . . . . . .

Schematic Diagrams: UG3MA

Block Diagram of Baseband (Version 2.1 Edit 98) layout 9.1 UG3MA/A3–1.

Block Diagram of COBBA, CCONT and MAD UG3MA/A3–2. . . . . . . . . . . . . . .

System Module

Circuit Diagram of Power Supply (V. 2.31 Edit 299) layout 10.4 UG3MA/A3–3

Circuit Diagram of SIM Connector (V. 2.31 Edit 99) layout 10.4 UG3MA/A3–4

Circuit Diagram of CPU Block (V. 2.31 Edit 203) layout 10.4 UG3MA/A3–5. .

Circuit Diagram of Audio (Version 2.31 Edit 155) layout 10.4 UG3MA/A3–6.

Circuit Diagram of IR Module (V. 2.31 Edit 128) layout 10.4 UG3MA/A3–7. . .

RF Block Diagram UG3MA/A3–8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Diagram of RF Block (V. 2.31 Edit 309) layout 10.4 UG3MA/A3–9. . . .

Circuit Diagram of UIF (Version 2.31 Edit 126) layout 10.4 UG3MA/A3–10. . .

Layout Diagram of UG3MA – Top (Version 10.4) UG3MA/A3–11. . . . . . . . . . . .

Layout Diagram of UG3MA – Bottom (Version 10.4) UG3MA/A3–11. . . . . . . . .

Testpoint references UG3/A3–12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Circuit Diagram of Power Supply (Version 2.36 Edit 314) UG3MA/A3–13. . . . .

Circiut Diagram of CPU Block (Version 2.36 Edit 217) UG3MA/A3–14. . . . . . .

Circuit Diagram of UIF (Version 2.36 Edit 139) UG3MA/A3–15. . . . . . . . . . . . .

Circuit Diagram of SIM Connector (Version 2.36 Edit 110) UG3MA/A3–16. . . .

Circuit Diagram of RF Block (Version 2.36 Edit 334) UG3MA/A3–17. . . . . . . .

Circuit Diagram of Audio (Version 2.36 Edit 170) UG3MA/A3–18. . . . . . . . . . .

Circuit Diagram of IR Module (Version 2.36 Edit 139) UG3MA/A3–19. . . . . . .

Layout Diagram of UG3MA – TOP (Version 11) UG3MA/A3–20. . . . . . . . . . . . .

Layout Daigram of UG3MA – BOTTOM (Version 11) UG3MA/A3–20. . . . . . . . .

Issue 2 01/00

Page 3–5

Page 6

NSM–1

PAMS

System Module

Transceiver NSM–1

Introduction

The NSM–1 is a dualband transceiver unit designed for operation in

GSM900, GSM1800 and GSM900/1800 dualband networks. GSM pow-

er class is 4 and PCN power class is 1.

The transceiver has full graphic display, and the user interface is based

on two soft keys.

The transceiver has leakage tolerant earpiece and omnidirectional micro-

phone providing excellent audio quality. Transceiver supports full rate, en-

hanced full rate and half rate speech decoding.

The antenna is a fixed helix. External antenna connection is provided by

rear RF connector

Integrated IR link provides for connection between two NSM–1NY trans-

ceivers or a transceiver and a PC, or a transceiver and a printer.

Technical Documentation

The small SIM ( Subscriber Identity Module ) card is located inside the

phone, beneath the battery pack.

Mode Description

There are five different operation modes:

– power off mode

– idle mode

– active mode

– charge mode

– local mode

In the power off mode only the circuits needed for power up are supplied.

In the idle mode circuits are powered down and only sleep clock is run-

ning.

In the active mode all the circuits are supplied with power although some

parts might be in the idle state part of the time.

The charge mode is effective in parallel with all previous modes. The

charge mode itself consists of two different states, i.e. the charge and the

maintenance mode.

Page 3–6

The local mode is used for alignment and testing.

Issue 2 01/00

Page 7

PAMS

NSM–1

Technical Documentation

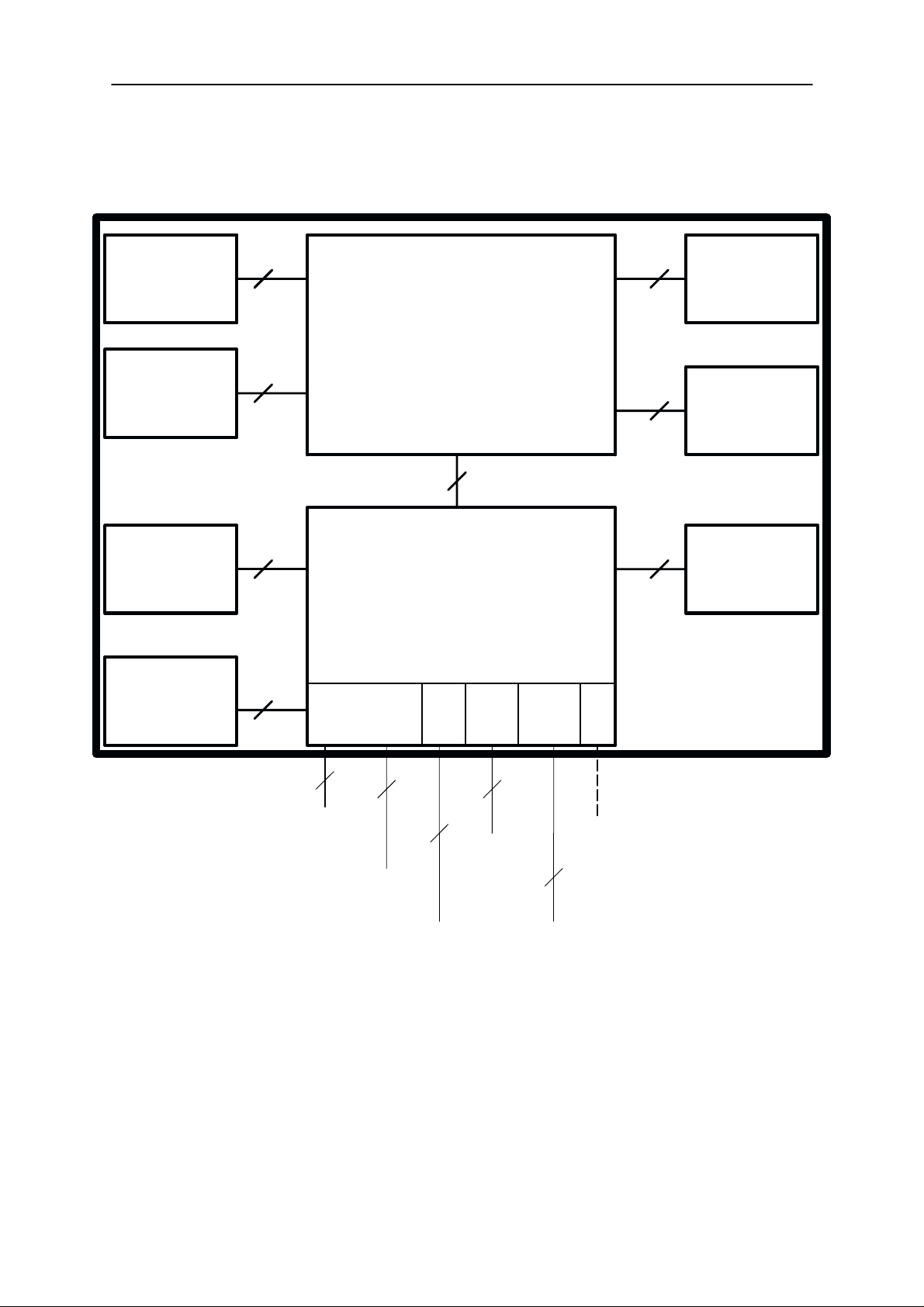

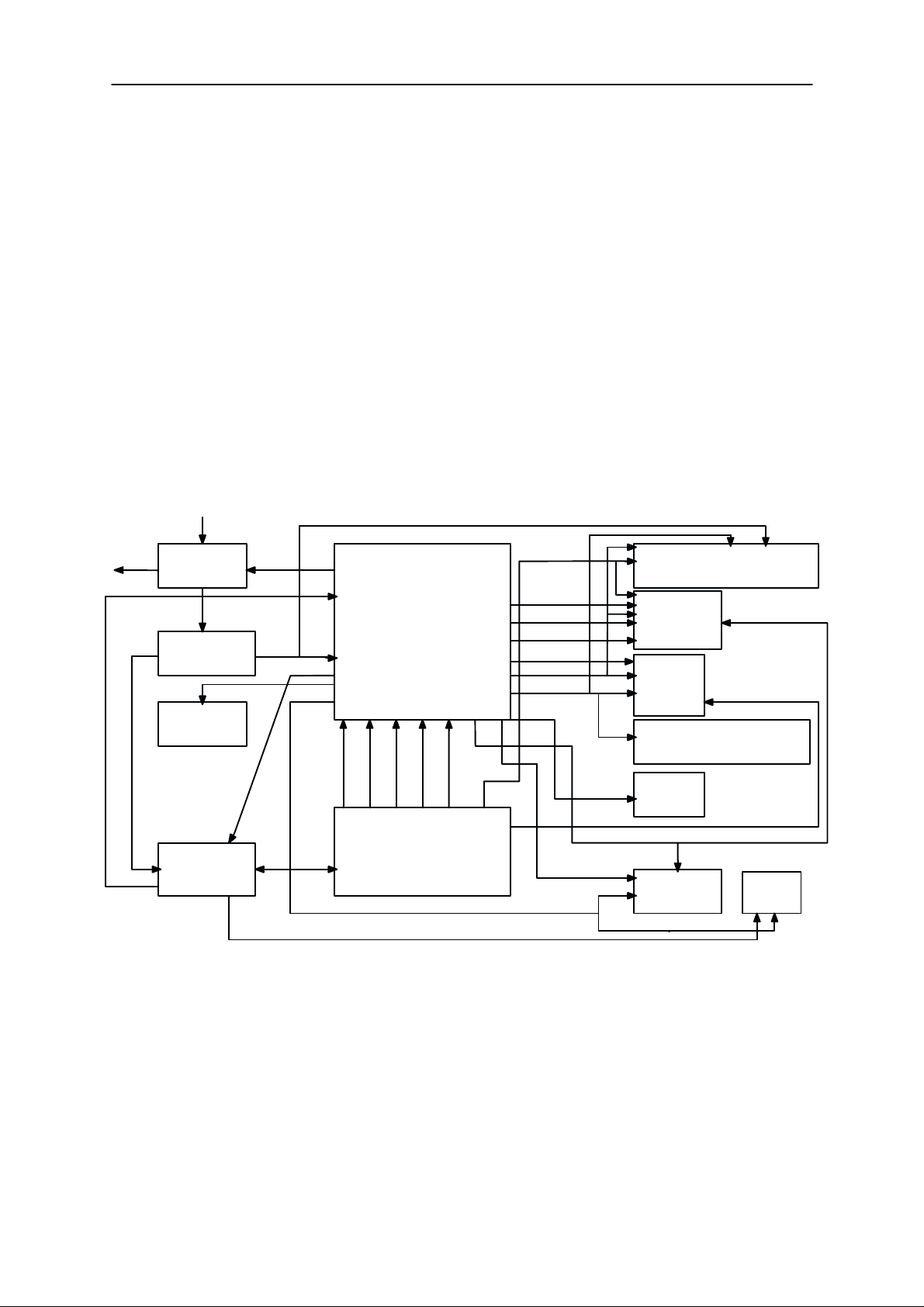

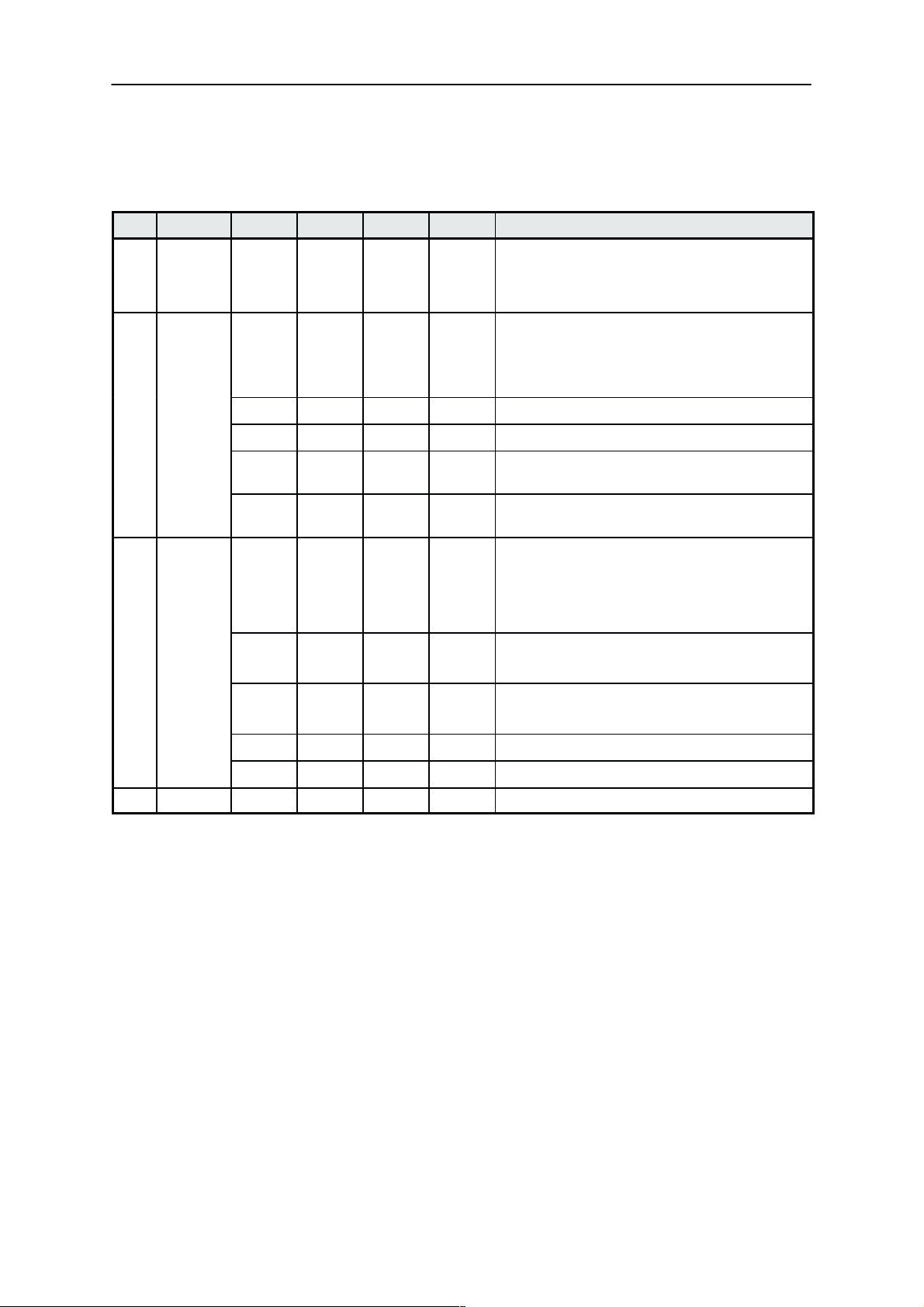

Interconnection Diagram

10 9

10

Keypad Display

Keypad

System Module

User Interface

Module

1

PWR Key

RTC

battery

UE4

28

2

System/RF

Module

2

Speaker

1

Antenna

MIC

connectors for external signals

2

System

Connector

3 + 3 6

Charger

accessories

UG3

RF SIM

2

SIM

card

external

antenna

battery

6

Battery

IR

NSM–1

IR Link

4

Issue 2 01/00

Page 3–7

Page 8

NSM–1

PAMS

System Module

System Module

Circuit Description

The transceiver electronics consist of the Radio Module, RF + System

blocks, the UI PCB, the display module and audio components. The key-

pad and the display module are connected to the Radio Module with a

connectors. System blocks and RF blocks are interconnected with PCB

wiring. The Transceiver is connected to accessories via a bottom system

connector with charging and accessory control.

The System blocks provide the MCU, DSP and Logic control functions in

MAD ASIC, external memories, audio processing and RF control hard-

ware in COBBA ASIC. Power supply circuitry CCONT ASIC delivers oper-

ating voltages both for the System and the RF blocks.

The RF block is designed for a handportable phone which operates in the

GSM and DCS1800 systems. The purpose of the RF block is to receive

and demodulate the radio frequency signal from the base station and to

transmit a modulated RF signal to the base station. The SUMMA ASIC is

used for VHF and PLL functions. The CRFU3 ASIC is used at the front

end.

Technical Documentation

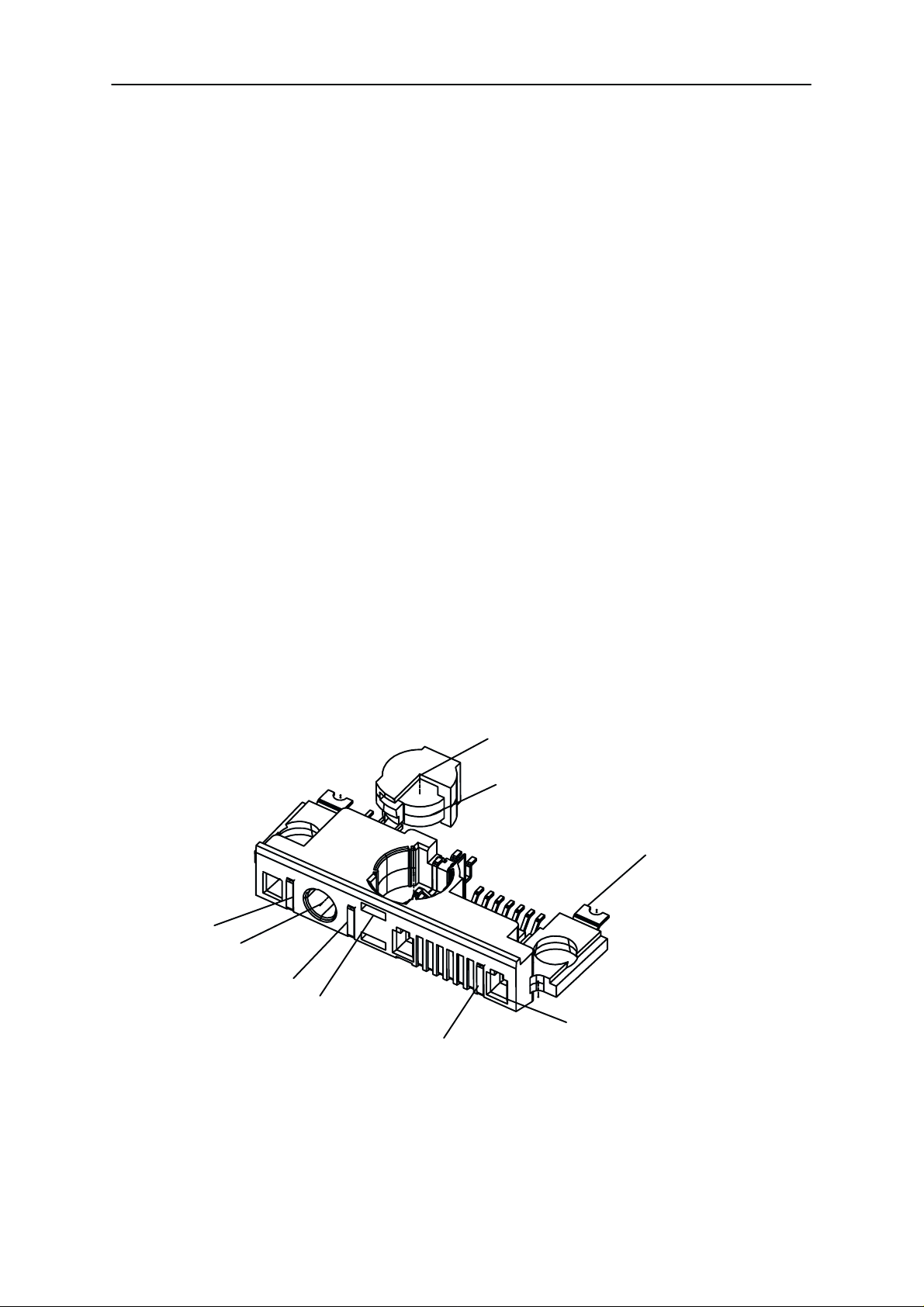

External and Internal Connectors

Contact 1

DC–jack

Contact 2

Microphone port

Contacts

3...8

Contact 9

Rubber boot

Microphone

Solderable element,

2 pcs

Cable/Cradle connector,

guiding/fixing hole, 3 pcs

Page 3–8

Issue 2 01/00

Page 9

PAMS

NSM–1

Technical Documentation

System Connector Contacts

Con-

tact

1 VIN Charger input volt-

DC–

JACK

DC–

JACK

Line

Sym-

bol

L_GND Charger ground

VIN Charger input volt-

Parameter Mini-

age

Charger input cur-

rent

input

age

Charger input cur-

rent

System Module

Typical

mum

7.1

720

7.24

320

0 0 0 V/ Supply ground

7.1

720

7.24

320

/ Nomi-

nal

8.4

800

7.6

370

8.4

800

7.6

370

Maxi-

mum

9.3

850

7.95

420

9.3

850

7.95

420

Unit / Notes

V/ Unloaded ACP–9 Charger

mA/ Supply current

V/ Unloaded ACP–7 Charger

mA/ Supply current

V/ Unloaded ACP–9 Charger

mA/ Supply current

V/ Unloaded ACP–7 Charger

mA/ Supply current

DC–

JACK

2 CHRG

Mic

ports

3 XMIC Input signal volt-

4 SGND Signal ground 0 0 mVrms

5 XEAR Output signal volt-

6 MBUS I/O low voltage

7 FBUS_RXInput low voltage

CHRG

CTRL

CTRL

Output high voltage

PWM frequency

Output high voltage

PWM frequency

Acoustic signal N/A N/A N/A Microphone sound ports

age

age

I/O high voltage

Input high voltage02.0

2.0

2.0

0

2.0

2.8 V/ Charger control (PWM)

32

2.8 V/ Charger control (PWM)

32

60 1 Vpp mVrms

80 1 Vpp mVrms

0.8

2.8

0.8

2.8

high

Hz /PWM frequency for

charger

high

Hz /PWM frequency for

charger

Serial bidirectional control

bus.

Baud rate 9600 Bit/s

V/ Fbus receive.

V/ Serial Data, Baud rate

9.6k–230.4kBit/s

8 FBUS_TXOutput low voltage

Output high voltage

9 L_GND Charger ground

input

Issue 2 01/00

0

2.0

0 0 0 V/ Supply ground

0.8

2.8

V/ Fbus transmit.

V/ Serial Data, Baud rate

9.6k–230.4kBit/s

Page 3–9

Page 10

NSM–1

PAMS

System Module

Technical Documentation

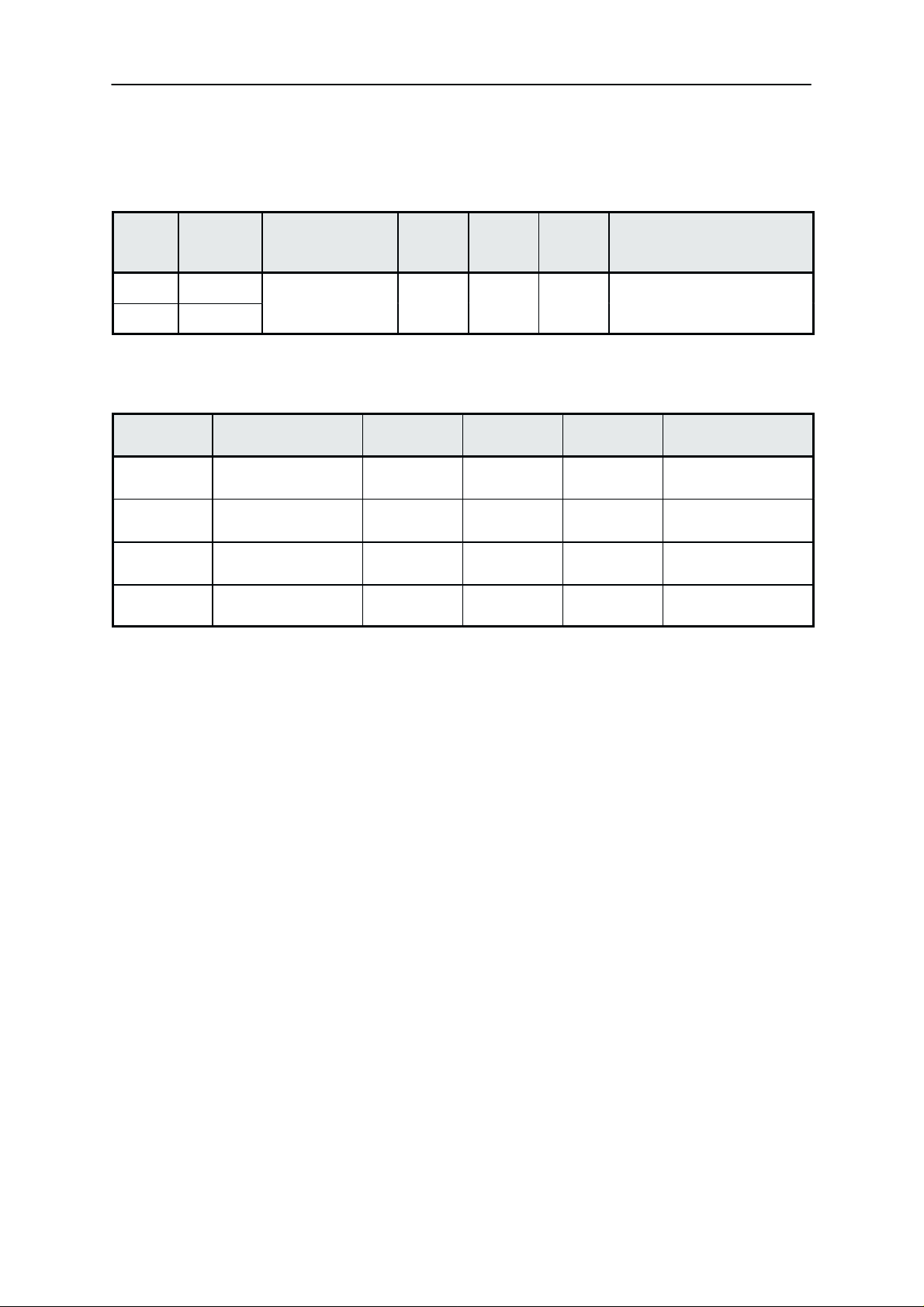

RF Connector Contacts

Con-

tact

1 EXT_ANT

2 GND

Line

Symbol

Parameter Mini-

mum

Impedance 50ohm tor,

Typical

/ Nomi-

nal

Maxi-

mum

External antenna connec0 V DC

Unit / Notes

Supply Voltages and Power Consumtion

Connector Line Symbol Minimum Typical /

Nominal

Charging VIN 7.1 8.4 9.3 V/ Travel charger,

Charging VIN 7.25 7.6 7.95 V/ Travel charger.

Charging I / VIN 720 800 850 mA/ Travel char-

Charging I / VIN 320 370 420 mA/ Travel char-

Maximum/

Peak

Unit / Notes

ACP–9

ACP–7

ger, ACP–9

ger, ACP–7

Page 3–10

Issue 2 01/00

Page 11

PAMS

NSM–1

Technical Documentation

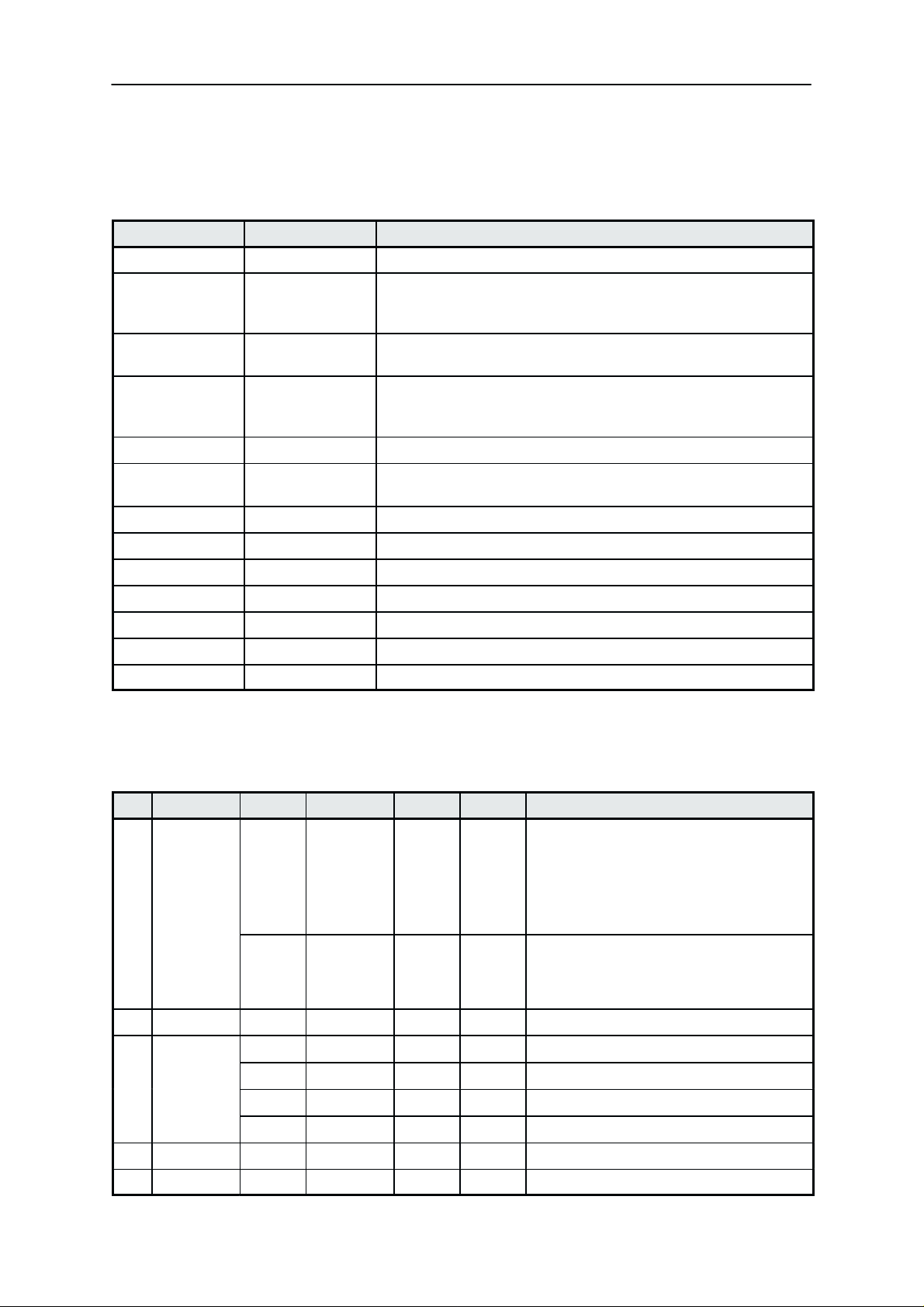

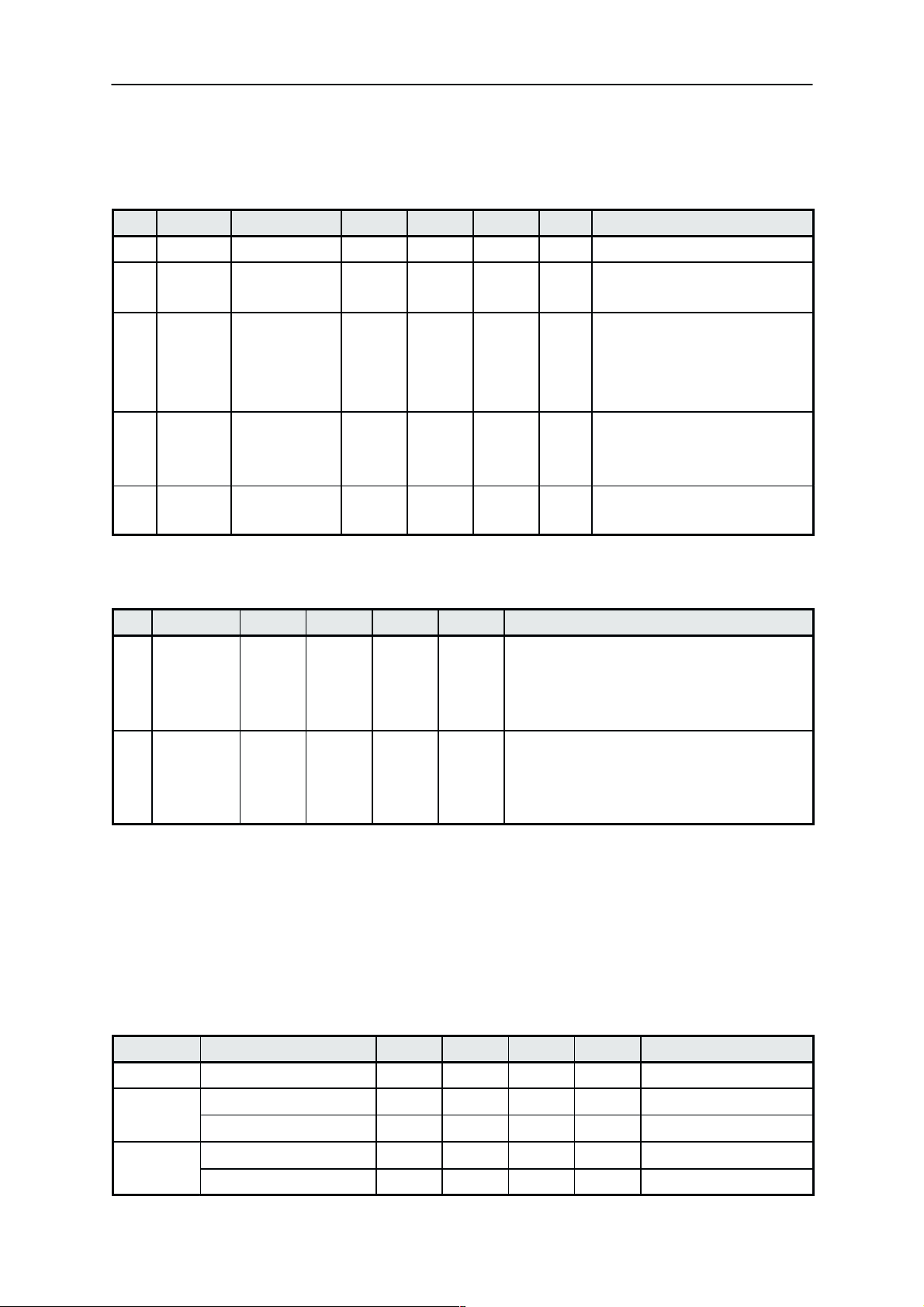

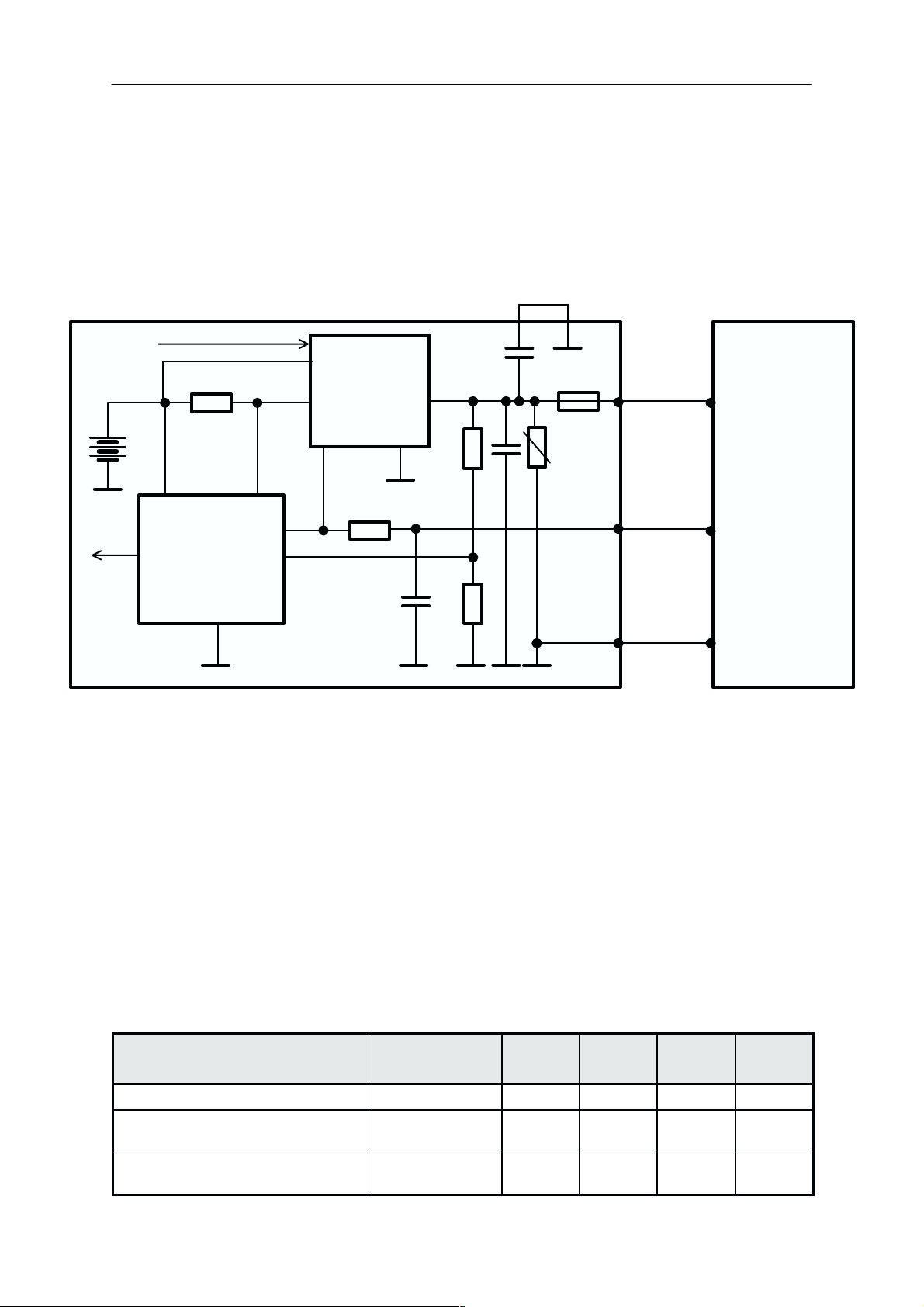

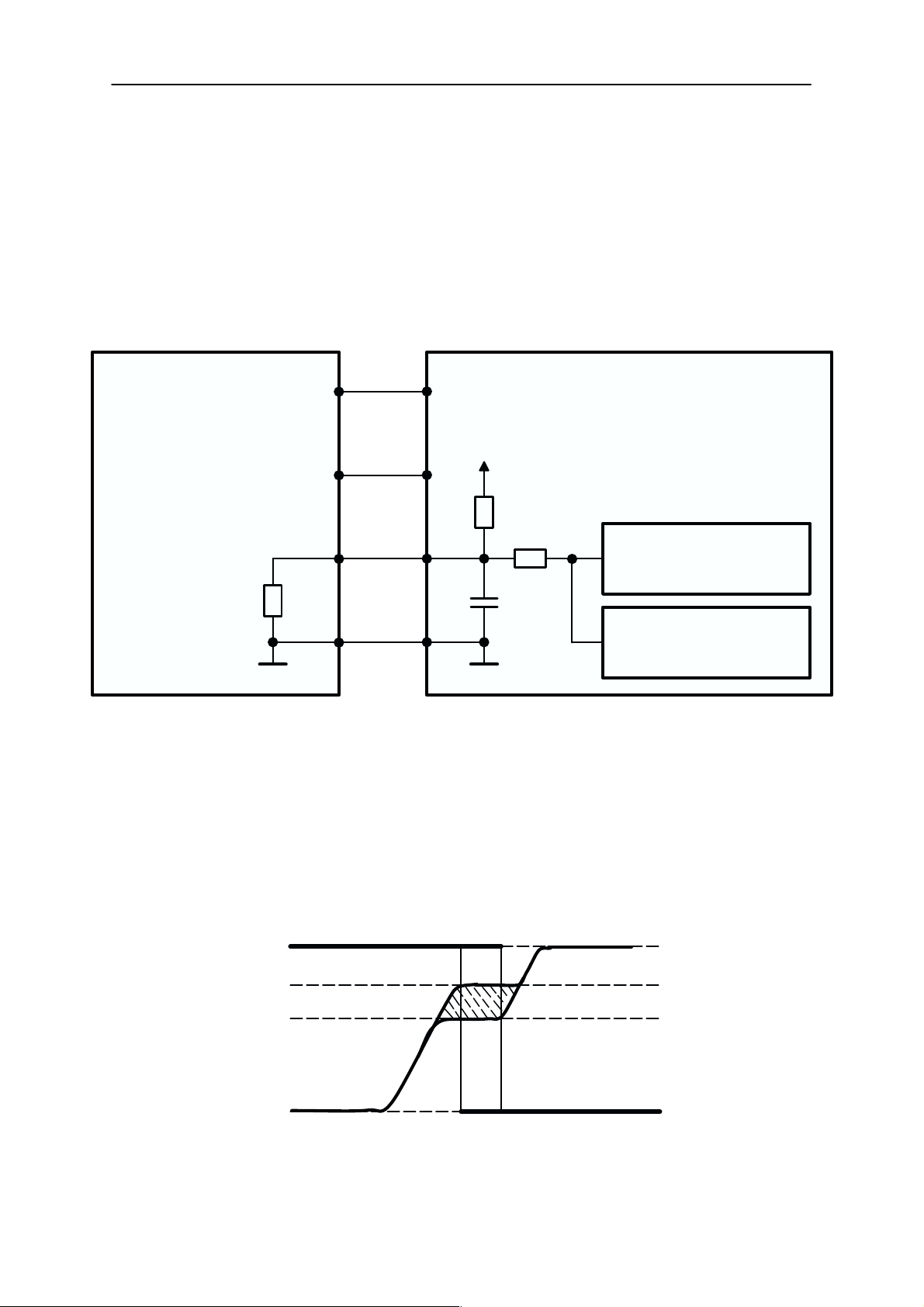

Power Distribution Diagram

The power supply is based on the ASIC circuit CCONT. The chip consists

of regulators and control circuits providing functions like power up, reset

and watchdog. External buffering is required to provide more current on

some blocks.

The MCU and the CCONT circuits control charging together, detection

being carried out by the CCONT and higher level intelligent control by the

MCU. The MCU measures battery voltage by means of the CCONT. The

CCONT also measures charger voltage, temperature and size of the battery.

Detailed power distribution diagrams are given in Baseband blocks and

RF blocks later in the document.

V_IN

PWM

CHARGING

CIRCUITRY

PWM

CCONT

TXP

VBAT

System Module

bias

power det

POWER AMPLIFIER

VBAT

BATTERY

VBAT

Note: VTX uses

a discrete

transistor to increse

VR7 output

capability

VSIM

SIM

V5V

VBAT

VBB

V

T

X

P

W

R

Y

X

N

P

P

W

W

R

R

S

R

S

C

I

X

M

O

P

P

W

R

T

W

X

R

P

MAD

VBB

UIF

PWRONX MEM

5V

VBB

V5V/VCP

VRX_2

VSYN_2

VRX_1

V_TX

VSYN_1

VSYN_1

VXO

VCOBBA

VREF

VBB

SUMMA

CRFU3

VREF

BAND SEL

RF SYNTHESIZERS

VCXO

COBBA

Issue 2 01/00

Page 3–11

Page 12

NSM–1

PAMS

System Module

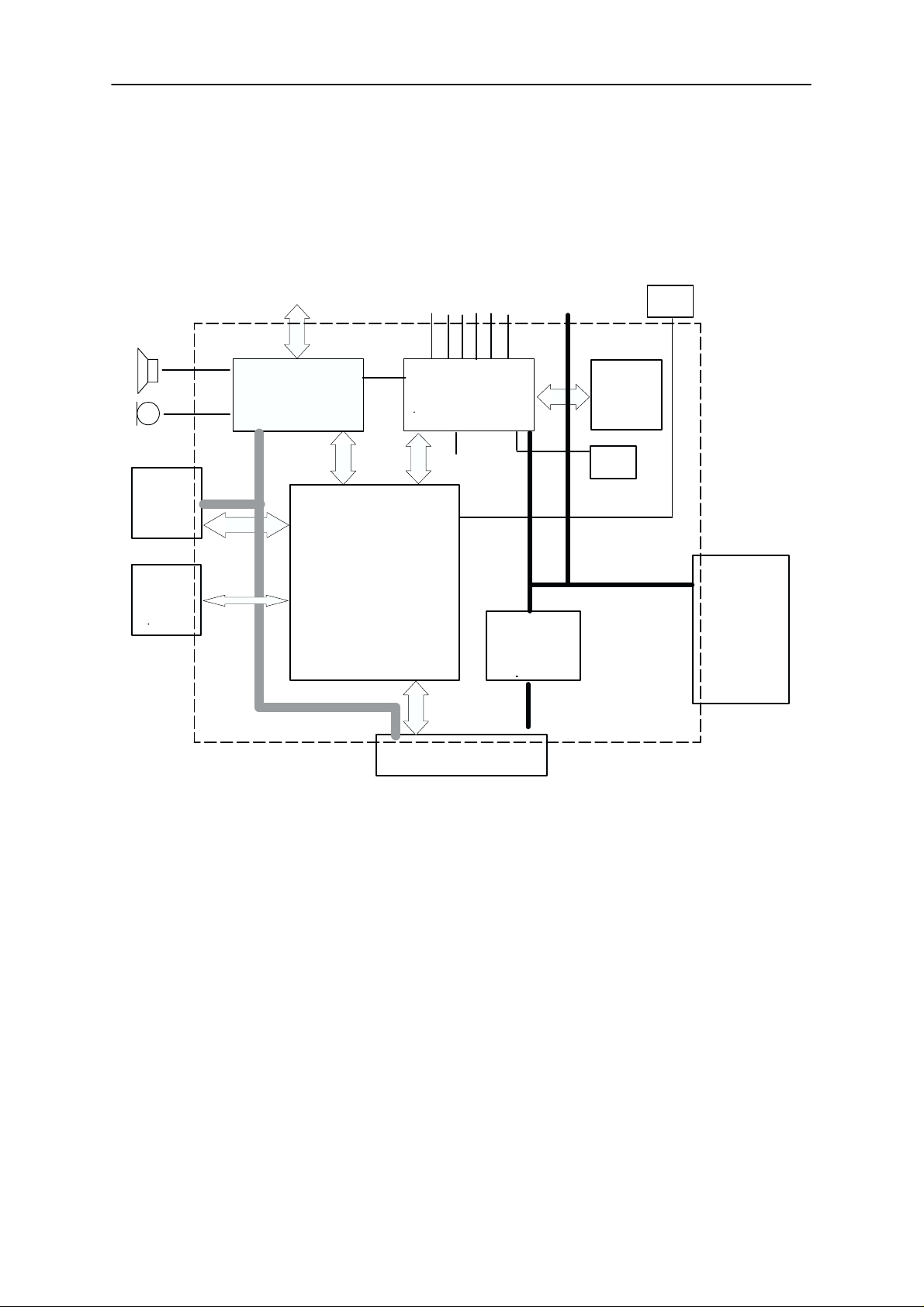

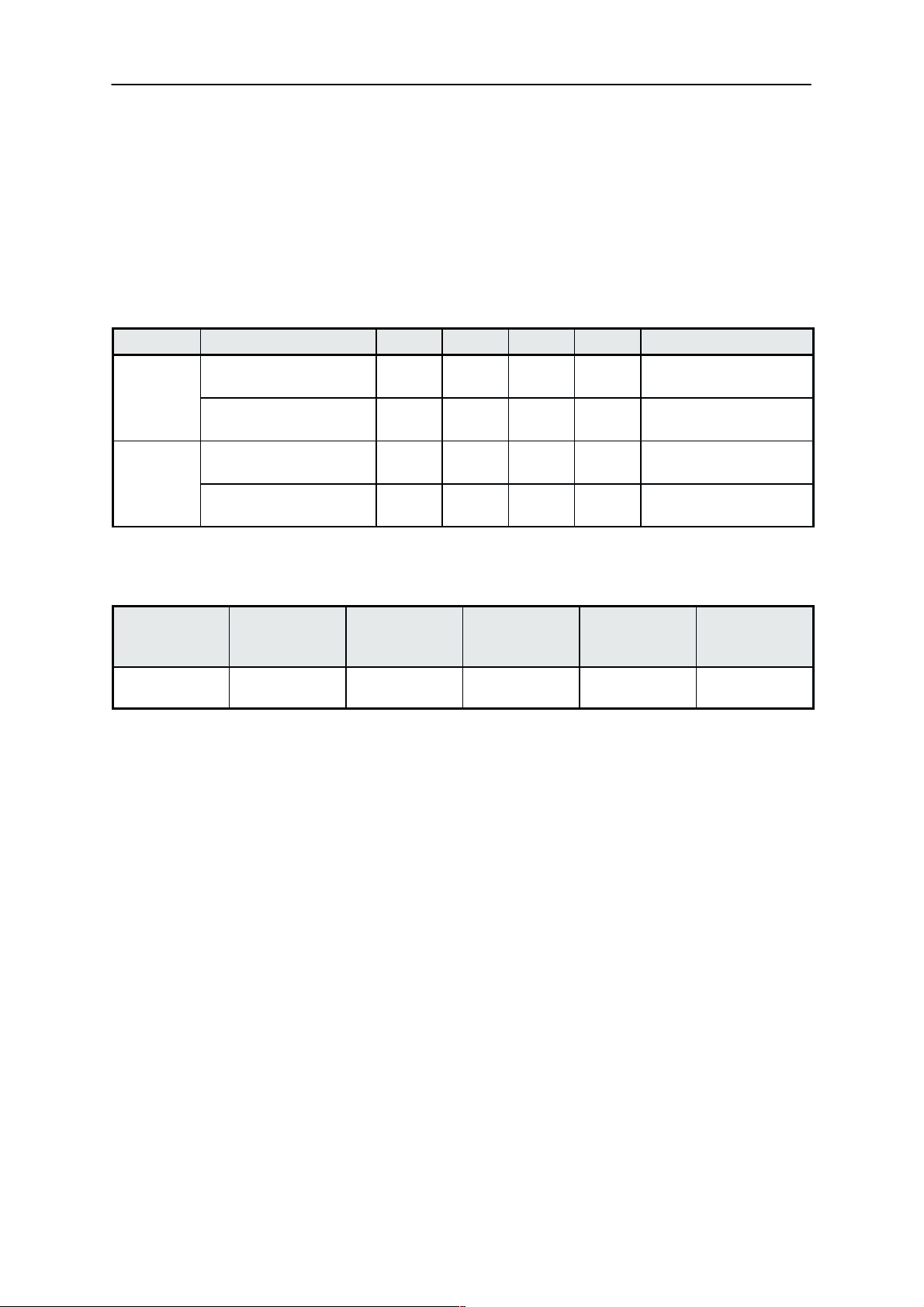

Baseband Module

Block Diagram

TX/RX SIGNALS

COBBA

UI

COBBA SUPPLY

RF SUPPLIES

CCONT

BB SUPPLY

Technical Documentation

PA SUPPLY

32kHz

CLK

SLEEP CLOCK

SIM

13MHz

CLK

SYSTEM CLOCK

IR

AUDIOLINES

BASEBAND

Technical Summary

The baseband module consists of four asics, CHAPS, CCONT, COBBA–

GJ and MAD2, which take care of the baseband functions of NSM–1.

The baseband is running from a 2.8V power rail, which is supplied by a

power controlling asic. In the CCONT asic there are 6 individually controlled regulator outputs for RF–section and two outputs for the baseband. In addition there is one +5V power supply output (V5V) for flash

programming voltage and other purposes where a higher voltage is needed. The CCONT contains also a SIM interface, which supports both 3V

and 5V SIM–cards. A real time clock function is integrated into the

CCONT, which utilizes the same 32kHz clock supply as the sleep clock. A

backup power supply is provided for the RTC, which keeps the real time

clock running when the main battery is removed. The backup power supply is a rechargable polyacene battery. The backup time with this battery

is minimum of ten minutes.

MAD

+

MEMORIES

VBAT

BATTERY

CHAPS

SYSCON

Page 3–12

Issue 2 01/00

Page 13

PAMS

NSM–1

Technical Documentation

The interface between the baseband and the RF section is handled by a

specific asic. The COBBA asic provides A/D and D/A conversion of the

in–phase and quadrature receive and transmit signal paths and also A/D

and D/A conversions of received and transmitted audio signals to and

from the UI section. The COBBA supplies the analog TXC and AFC signals to rf section according to the MAD DSP digital control and converts

analog AGC into digital signal for the DSP. Data transmission between the

COBBA and the MAD is implemented using a parallel connection for high

speed signalling and a serial connection for PCM coded audio signals.

Digital speech processing is handled by the MAD asic. The COBBA asic

is a dual voltage circuit, the digital parts are running from the baseband

supply VBB and the analog parts are running from the analog supply

VCOBBA.

The baseband supports three external microphone inputs and two external earphone outputs. The inputs can be taken from an internal microphone, a headset microphone or from an external microphone signal

source. The microphone signals from different sources are connected to

separate inputs at the COBBA asic.

System Module

The output for the internal earphone is a dual ended type output capable

of driving a dynamic type speaker. Input and output signal source selection and gain control is performed inside the COBBA asic according to

control messages from the MAD. Keypad tones, DTMF, and other audio

tones are generated and encoded by the MAD and transmitted to the

COBBA for decoding. A buzzer and an external vibra alert control signals

are generated by the MAD with separate PWM outputs.

EMC shieding is implemented using a metallized plastic B–cover with a

conductive rubber seal on the ribs. On the other side the engine is

shielded with a frame having a conductive rubber on the inner walls,

which makes a contact to a ground ring of the engine board and a

ground plane of the UI–board. Heat generated by the circuitry will be conducted out via the PCB ground planes.

Issue 2 01/00

Page 3–13

Page 14

NSM–1

PAMS

System Module

Technical Documentation

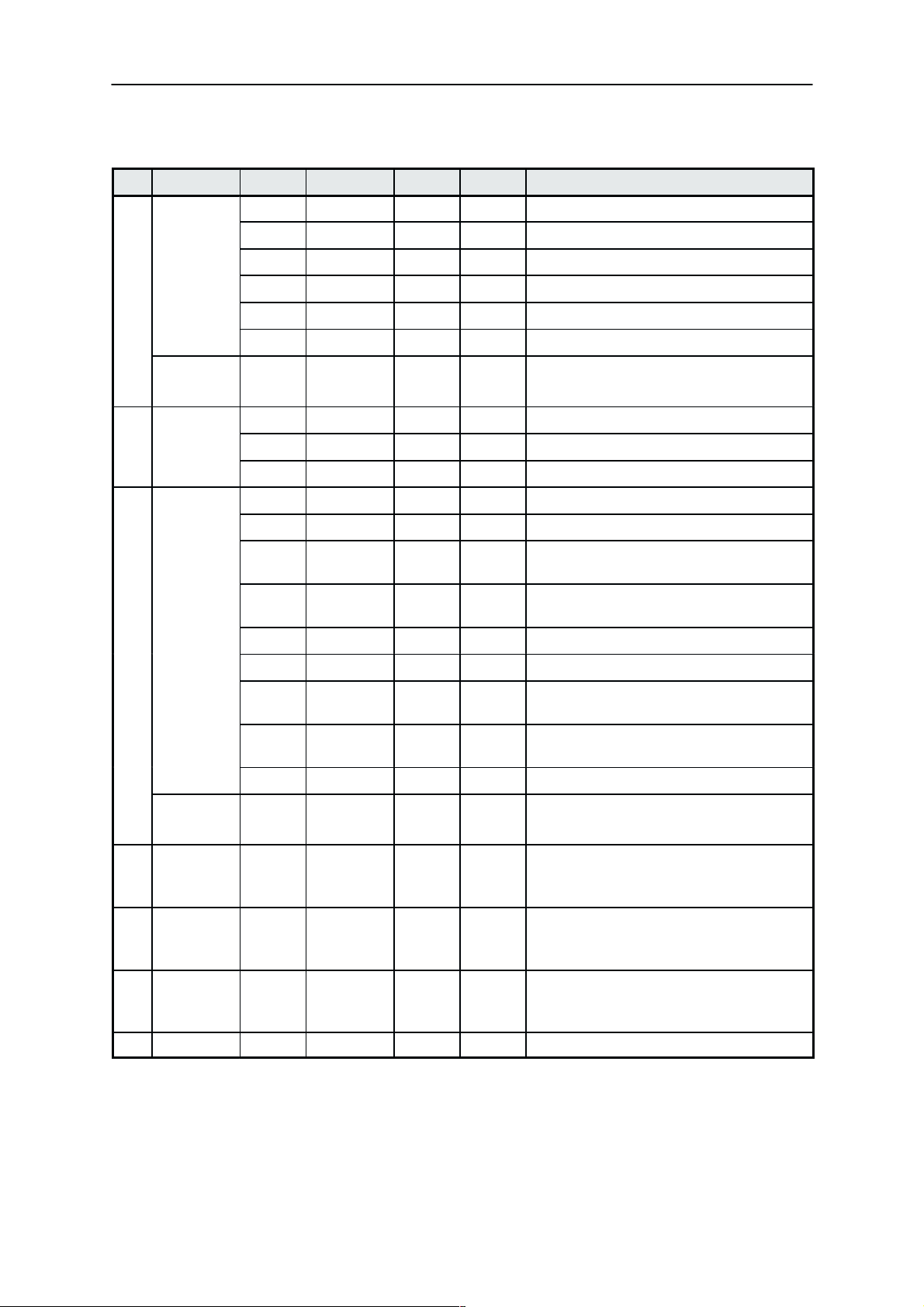

Bottom Connector External Contacts

Contact Line Symbol Function

1 VIN Charger input voltage

DC–jack

side contact

(DC–plug ring)

DC–jack

center pin

DC–jack

side contact

(DC–plug jacket)

2 CHRG_CTRL Charger control output (from phone)

Microphone

acoustic ports

3 XMIC Accessory microphone signal input (to phone)

4 SGND Accessory signal ground

L_GND Charger ground

VIN Charger input voltage

CHRG_CTRL Charger control output (from phone)

Acoustic signal (to phone)

5 XEAR Accessory earphone signal output (from phone)

6 MBUS MBUS, bidirectional serial data i/o

7 FBUS_RX FBUS, unidirectional serial data input (to phone)

8 FBUS_TX FBUS, unidirectional serial data output (from phone)

9 L_GND Charger ground

Bottom Connector Signals

Pin Name Min Typ Max Unit Notes

1,3 VIN

2 L_GND 0 0 V Supply ground

7.25

3.25

320

7.1

3.25

720

7.6

3.6

370

8.4

3.6

800

7.95

16.9

3.95

420

9.3

3.95

850

V

V

V

mA

V

V

mA

Unloaded ACP–7 Charger (5kohms

load)

Peak output voltage (5kohms load)

Loaded output voltage (10ohms load)

Supply current

Unloaded ACP–9 Charger

Loaded output voltage (10ohms load)

Supply current

4,5 CHRG_

CTRL

6 MICP N/A see section Internal microphone

7 MICN N/A see section Internal microphone

Page 3–14

0 0.5 V Charger control PWM low

2.0 2.85 V Charger control PWM high

32 Hz PWM frequency for a fast charger

1 99 % PWM duty cycle

Issue 2 01/00

Page 15

PAMS

NSM–1

Technical Documentation

8 XMIC

HMIC 0 3.2 29.3 mV Microphone signal

9 SGND

10 XEAR

2.0 2.2 kΩ Input AC impedance

1.47 1.55 V Mute (output DC level)

2.5 2.85 V Unmute (output DC level)

100 600 µA Bias current

System Module

NotesUnitMaxTypMinNamePin

1 Vpp Maximum signal level

58 490 mV Maximum signal level

Connected to COBBA MIC3P input

47 Ω Output AC impedance (ref. GND)

10 µF Series output capacitance

380 Ω Resistance to phone ground

47 Ω Output AC impedance (ref. GND)

10 µF Series output capacitance

16 300 Ω Load AC impedance to SGND (Head-

set)

4.7 10 kΩ Load AC impedance to SGND (Accessory)

1.0 Vpp Maximum output level (no load)

22 626 mV Output signal level

10 kΩ Load DC resistance to SGND (Acces-

sory)

16 1500 Ω Load DC resistance to SGND (Head-

set)

2.8 V DC voltage (47k pull–up to VBB)

HEAR 28 626 mV Earphone signal (HF– HFCM)

Connected to COBBA HF output

11 MBUS 0 logic low 0.8 V Serial bidirectional control bus.

2.0 logic high 2.85

12 FBUS_RX 0 logic low 0.8 V Fbus receive. Serial Data

2.0 logic high 2.85

13 FBUS_TX 0 logic low 0.5 V Fbus transmit. Serial Data

2.0 logic high 2.85

Baud rate 9600 Bit/s

Phone has a 4k7 pullup resistor

Baud rate 9.6k–230.4kBit/s

Phone has a 220k pulldown resistor

Baud rate 9.6k–230.4kBit/s

Phone has a 47k pullup resistor

14 GND 0 0.3 V Supply ground

Issue 2 01/00

Page 3–15

Page 16

NSM–1

PAMS

System Module

Technical Documentation

Battery Connector

Pin Name Min Typ Max Unit Notes

1 BVOLT 3.0 3.6 4.5 V Battery voltage

2 BSI

3 BTEMP

5.0

5.3

0 2.85 V Battery size indication

2.2 18 kohm Battery indication resistor (Ni battery)

20 22 24 kohm Battery indication resistor (service battery)

27 51 kohm Battery indication resistor (4.1V Lithium

68 91 kohm Battery indication resistor (4.2V Lithium bat-

0 1.4 V Battery temperature indication

Maximum voltage in call state with charger

Maximum voltage in idle state with charger

Phone has 100kohm pull up resistor.

SIM Card removal detection

(Treshold is 2.4V@VBB=2.8V)

battery)

tery)

Phone has a 100k (+–5%) pullup resistor,

Battery package has a NTC pulldown resis-

tor:

47k+–5%@+25C , B=4050+–3%

2.1

5

1.9

90

0 1 kohm Local mode initialization (in production)

20 22 25 kHz PWM control to VIBRA BA TTERY

4 BGND 0 0 V Battery ground

10

100

3

20

2.85

200

V

ms

V

ms

Phone power up by battery (input)

Power up pulse width

Battery power up by phone (output)

Power up pulse width

Page 3–16

Issue 2 01/00

Page 17

PAMS

NSM–1

Technical Documentation

System Module

SIM Card Connector

Pin Name Parameter Min Typ Max Unit Notes

4 GND GND 0 0 V Ground

3, 5 VSIM 5V SIM Card

3V SIM Card

6 DATA 5V Vin/Vout

3V Vin/Vout

2 SIMRST 5V SIM Card

3V SIM Card

1 SIMCLK Frequency

Trise/Tfall

4.8

2.8

4.0

0

2.8

0

4.0

2.8

5.0

3.0

”1”

”0”

”1”

”0”

”1”

”1”

3.25

5.2

3.2

VSIM

0.5

VSIM

0.5

VSIM

VSIM

25

V Supply voltage

V SIM data

Trise/Tfall max 1us

V SIM reset

MHz

ns

SIM clock

Internal Microphone

Pin Name Min Typ Max Unit Notes

6 MICP 0.55 4.1 mV Connected to COBBA MIC2N input. The

maximum value corresponds to1 kHz, 0

dBmO network level with input amplifier

gain set to 32 dB. typical value is maximum value – 16 dB.

7 MICN 0.55 4.1 mV Connected to COBBA MIC2P input. The

maximum value corresponds to1 kHz, 0

dBmO network level with input amplifier

gain set to 32 dB. typical value is maximum value – 16 dB.

Infrared Module Connections

An infrared transceiver module is designed to substitute an electrical

cable between the phone and a PC. The infrared transceiver module is a

stand alone component capable to perform infrared transmitting and receiving functions by transforming signals transmitted in infrared light from

and to electrical data pulses running in two wire asyncronous databus. In

DCT3 the module is placed inside the phone at the top of the phone.

Signal Parameter Min Typ Max Unit Notes

IRON IR–module on/off 2.0 2.85 V Iout@2mA

FBUS_RX

FBUS_TX

IR receive pulse 0 0.8 V

IR receive no pulse 2.0 2.85 V

IR transmit pulse 2.0 2.85 V Iout@2mA

IR transmit no pulse 0 0.5 V

Issue 2 01/00

Page 3–17

Page 18

NSM–1

PAMS

System Module

Technical Documentation

RTC Backup Battery

The RTC block in CCONT needs a power backup to keep the clock running when the phone battery is disconnected. The backup power is supplied from a rechargable polyacene battery that can keep the clock running minimum of 10 minutes. The backup battery is charged from the

main battery through CHAPS.

Signal Parameter Min Typ Max Unit Notes

VBACK

VBACK

Backup battery charging from CHAPS

Backup battery charging from CHAPS

Backup battery supply

to CCONT

Backup battery supply

to CCONT

3.02 3.15 3.28 V

100 200 500 uA Vout@VBAT–0.2V

2 3.28 V Battery capacity

65uAh

80 uA

Buzzer

Signal Maximum

BuzzPWM /

BUZZER

Input

output cur-

rent

2mA 2.5V 0.2V 0...50 (128 lin-

high level

Input

low level

Level (PWM)

range, %

ear steps)

Frequency

range, Hz

440...4700

Page 3–18

Issue 2 01/00

Page 19

PAMS

NSM–1

Technical Documentation

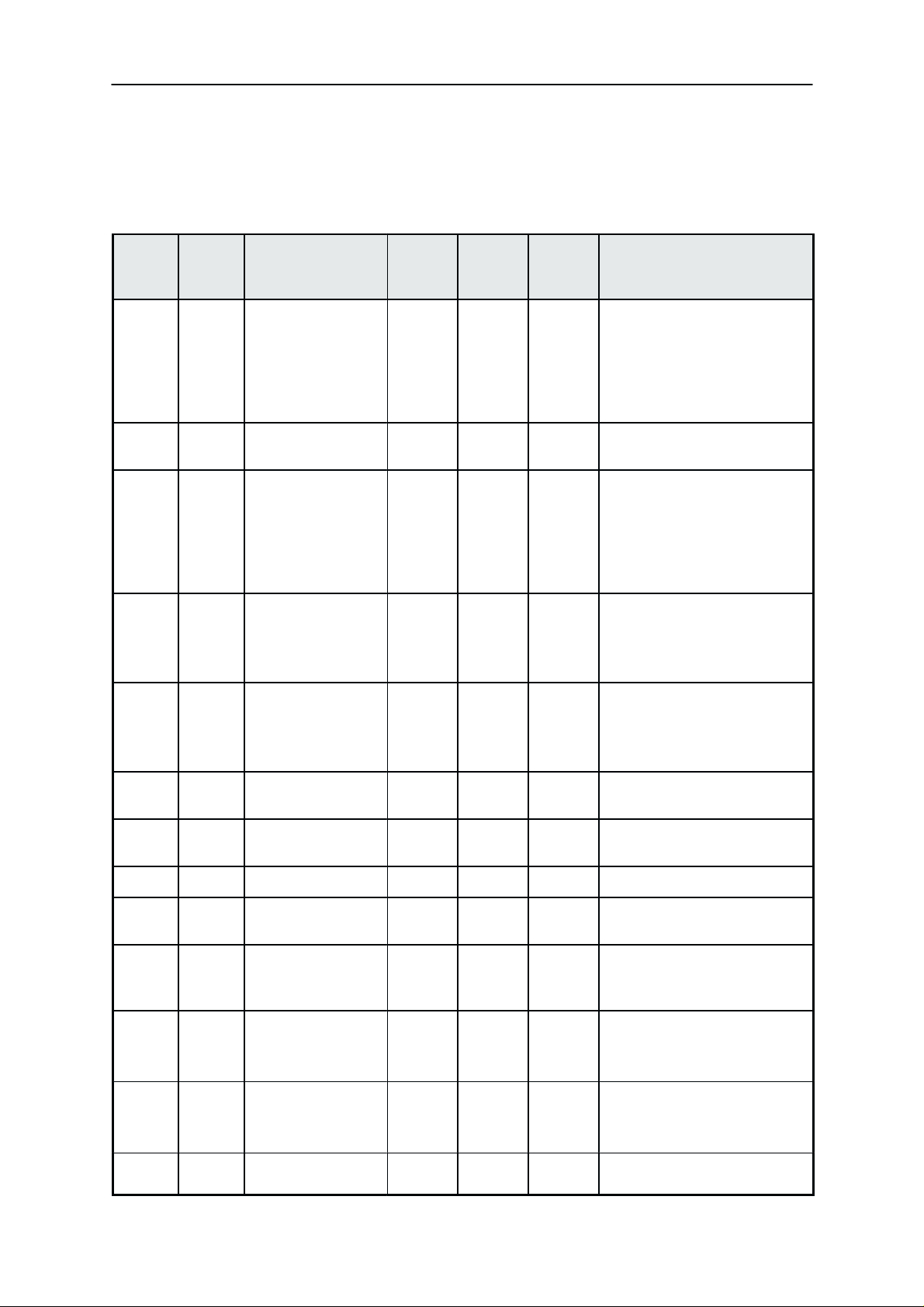

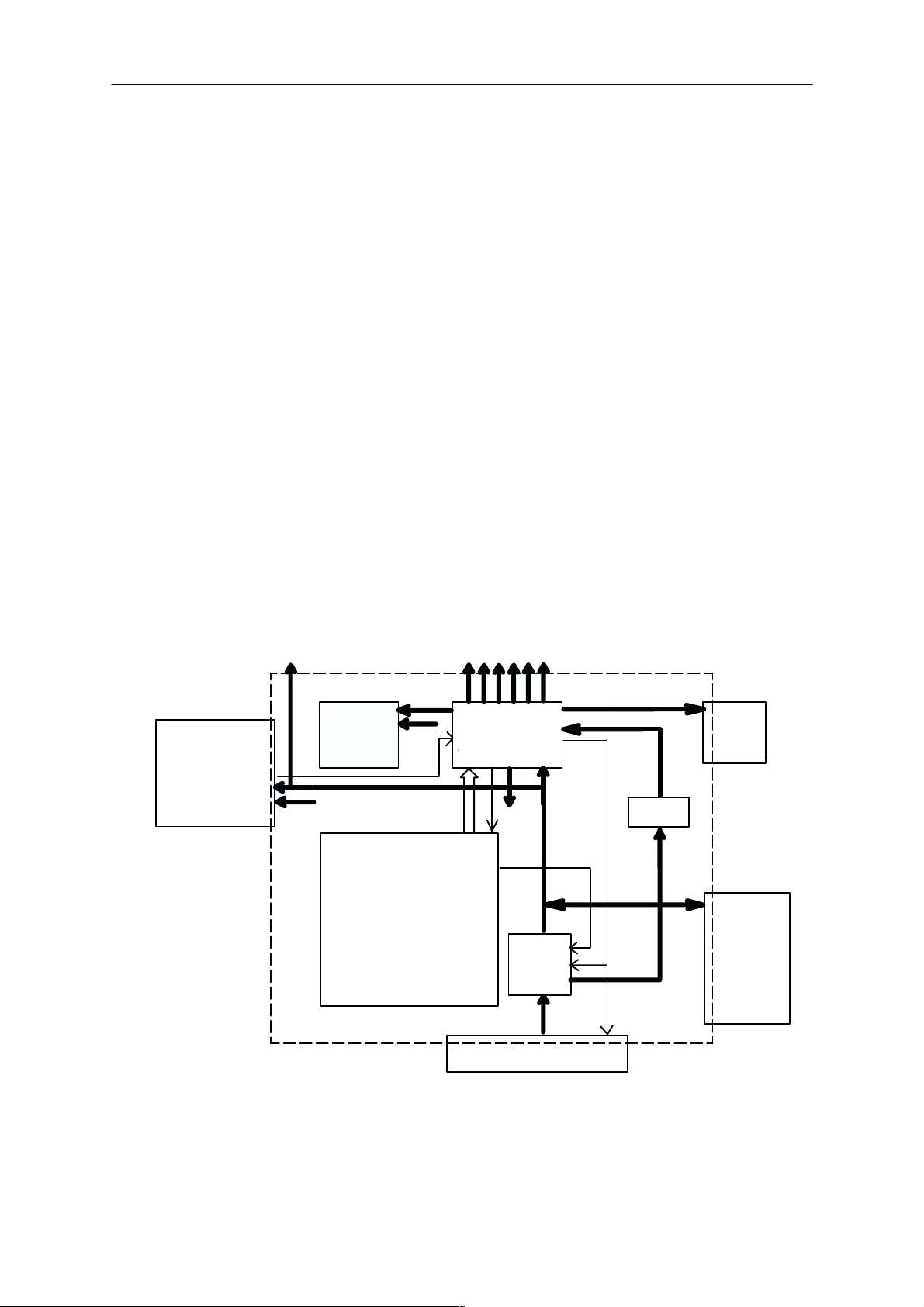

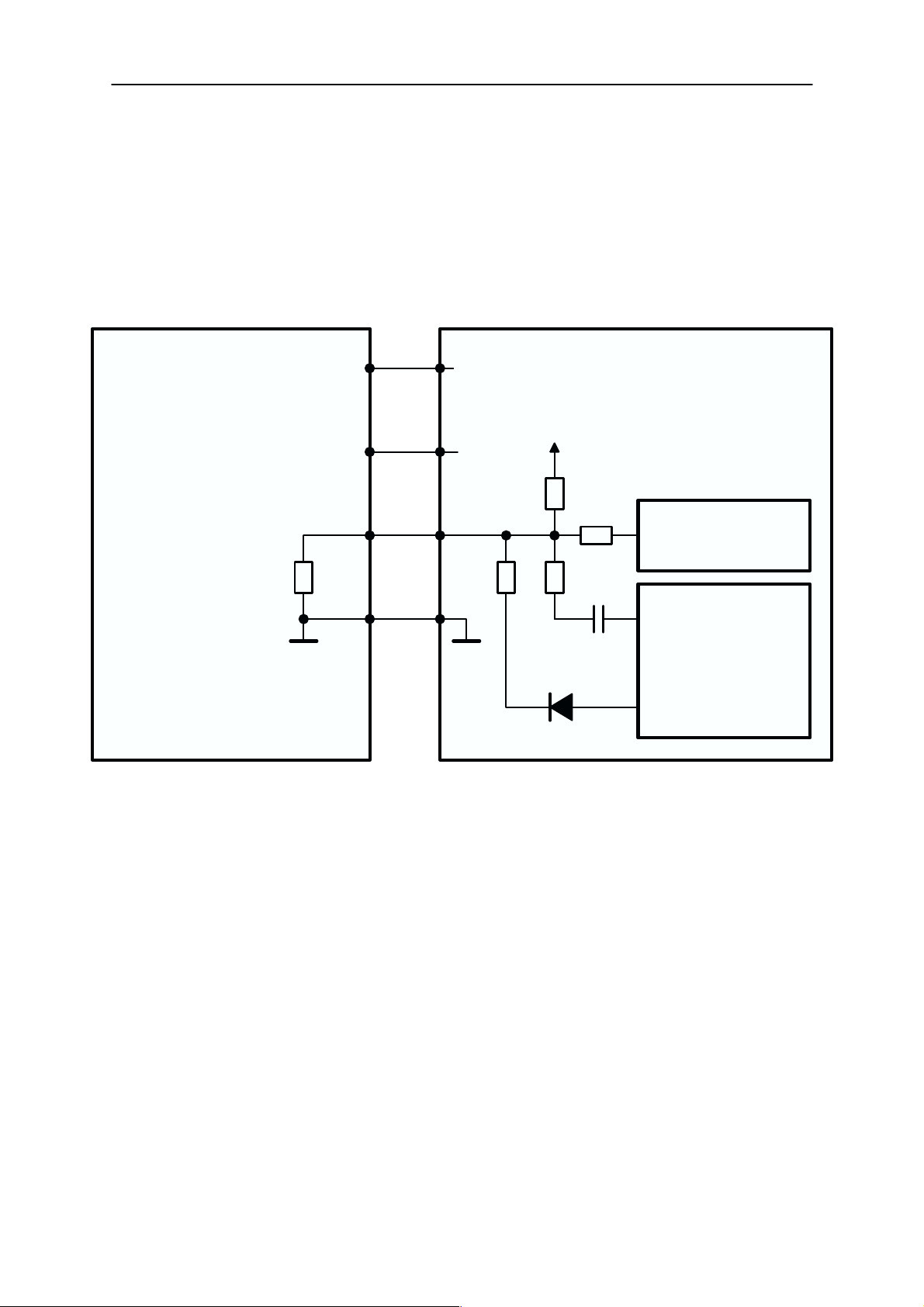

Baseband Power Distribution

Functional Description

In normal operation the baseband is powered from the phone‘s battery.

The battery consists of three Nickel Metal Hydride cells. There is also a

possibility to use batteries consisting of one Lithium–Ion cell. An external

charger can be used for recharging the battery and supplying power to

the phone. The charger can be either a standard charger that can deliver

around 400 mA or so called performance charger, which can deliver supply current up to 850 mA.

The baseband contains components that control power distribution to

whole phone excluding those parts that use continuous battery supply.

The battery feeds power directly to three parts of the system: CCONT,

power amplifier, and UI (buzzer and display and keyboard lights). Figure

below shows a block diagram of the power distribution.

The power management circuit CHAPS provides protection agains overvoltages, charger failures and pirate chargers etc. that would otherwise

cause damage to the phone.

System Module

PA SUPPLY

VCOBBA

COBBA

UI

VBAT

VBB

BASEBAND

VBB

MAD

+

MEMORIES

RF SUPPLIES

CCONT

PWRONX

CNTVR

BOTTOM CONNECTOR

PWM

VBB

PURX

LIM

CHAPS

VIN

VSIM

VBAT

RTC

BACKUP

SIM

BATTERY

Battery charging

The electrical specifications give the idle voltages produced by the acceptable chargers at the DC connector input. The absolute maximum in-

Issue 2 01/00

Page 3–19

Page 20

NSM–1

PAMS

System Module

MAD

VBAT

MAD

CCONTINT

Technical Documentation

put voltage is 30V due to the transient suppressor that is protecting the

charger input. At phone end there is no difference between a plug–in

charger or a desktop charger. The DC–jack pins and bottom connector

charging pads are connected together inside the phone.

0R22

PWM_OUT

CCONT

GND

ICHAR

VCHAR

LIM

VOUT

CHAPS

RSENSE

PWM

VCH

GND

47k

22k

1n

4k7

27p

1u

1,5A

30V

VIN

CHRG_CTRL

L_GND

CHARGER

NOT IN

ACP–7

TRANSCEIVER

Startup Charging

When a charger is connected, the CHAPS is supplying a startup current

minimum of 130mA to the phone. The startup current provides initial

charging to a phone with an empty battery. Startup circuit charges the

battery until the battery voltage level is reaches 3.0V (+/– 0.1V) and the

CCONT releases the PURX reset signal and program execution starts.

Charging mode is changed from startup charging to PWM charging that is

controlled by the MCU software. If the battery voltage reaches 3.55V

(3.75V maximum) before the program has taken control over the charging, the startup current is switched off. The startup current is switched on

again when the battery voltage is sunken 100mV (nominal).

Parameter Symbol Min Typ Max Unit

VOUT Start– up mode cutoff limit Vstart 3.45 3.55 3.75 V

VOUT Start– up mode hysteresis

NOTE: Cout = 4.7 uF

Start–up regulator output current

VOUT = 0V ... Vstart

Vstarthys 80 100 200 mV

Istart 130 165 200 mA

Page 3–20

Issue 2 01/00

Page 21

PAMS

NSM–1

Technical Documentation

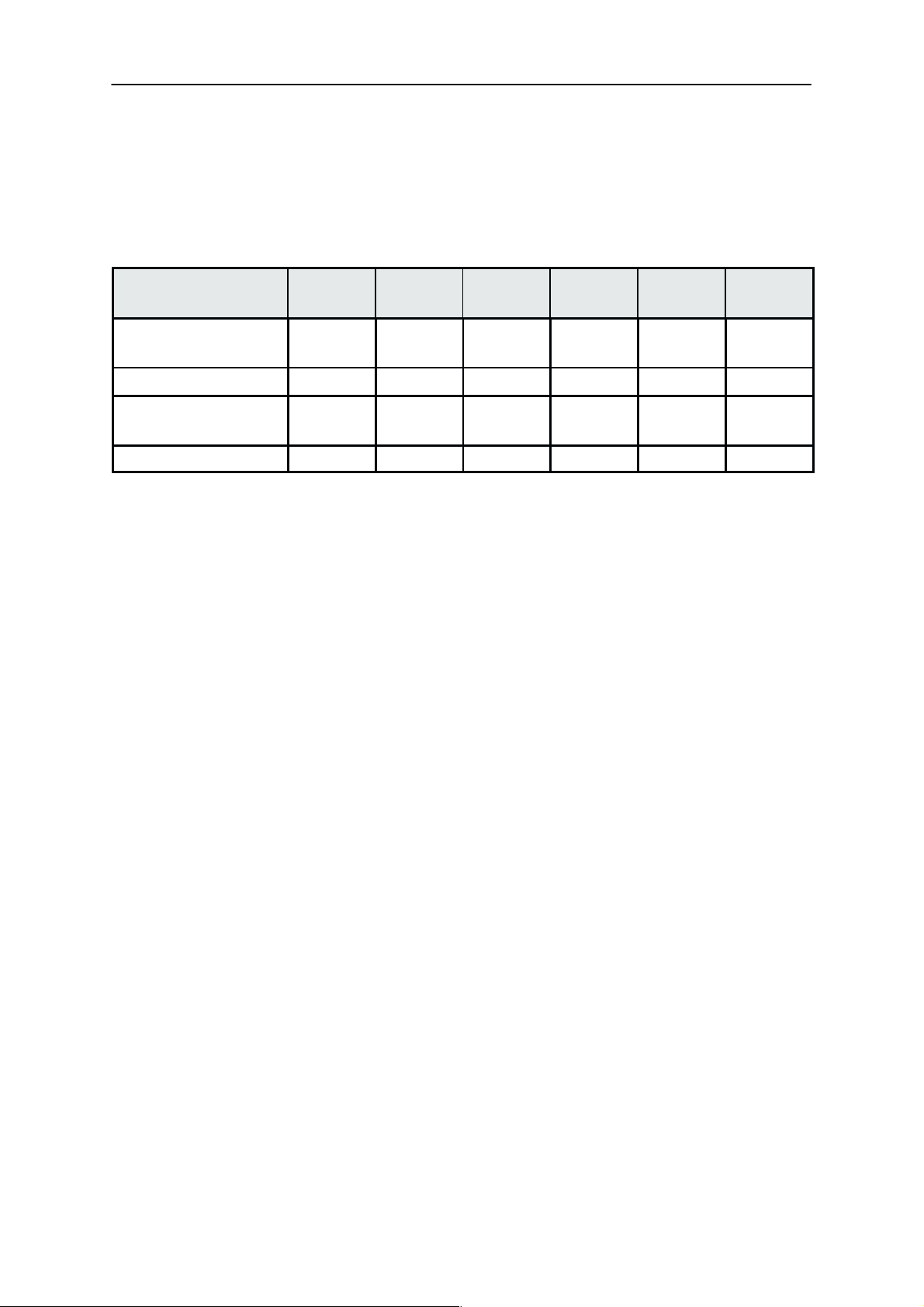

Battery Overvoltage Protection

Output overvoltage protection is used to protect phone from damage.

This function is also used to define the protection cutoff voltage for different battery types (Li or Ni). The power switch is immediately turned OFF if

the voltage in VOUT rises above the selected limit VLIM1 or VLIM2.

Parameter Symbol LIM input Min Typ Max Unit

Output voltage cutoff limit

(during transmission or Li–

battery)

Output voltage cutoff limit

(no transmission or Ni–bat-

tery)

VLIM1 LOW 4.4 4.6 4.8 V

VLIM2 HIGH 4.8 5.0 5.2 V

The voltage limit (VLIM1 or VLIM2) is selected by logic LOW or logic

HIGH on the CHAPS (N101) LIM– input pin. Default value is lower limit

VLIM1.

System Module

VCH

VCH<VOUT

VOUT

VLIM1 or VLIM2

When the switch in output overvoltage situation has once turned OFF, it

stays OFF until the the battery voltage falls below VLIM1 (or VLIM2) and

PWM = LOW is detected. The switch can be turned on again by setting

PWM = HIGH.

t

t

SWITCH

PWM (32Hz)

Issue 2 01/00

ON OFF

ON

Page 3–21

Page 22

NSM–1

PAMS

System Module

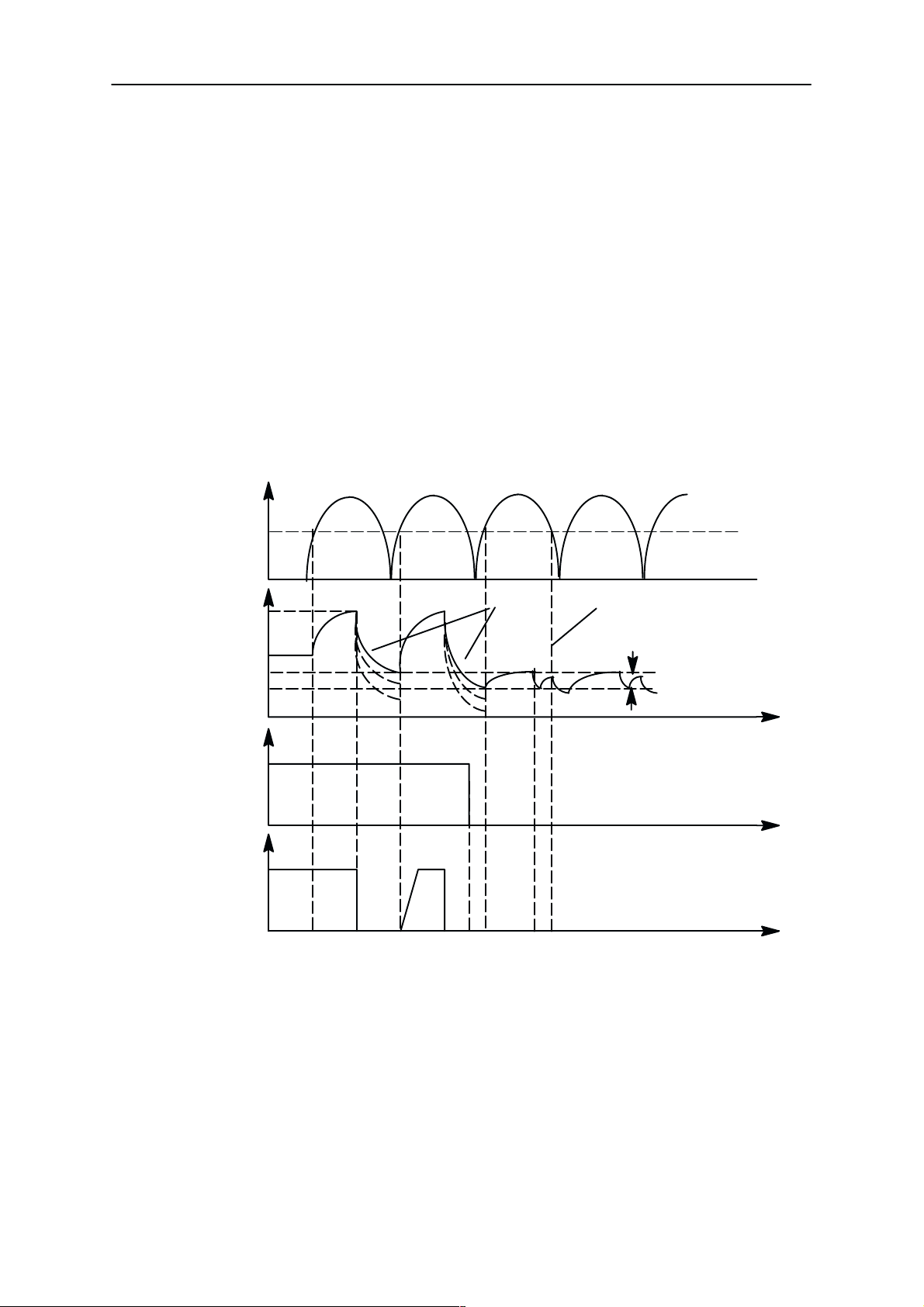

Battery Removal During Charging

Output overvoltage protection is also needed in case the main battery is

removed when charger connected or charger is connected before the battery is connected to the phone.

With a charger connected, if VOUT exceeds VLIM1 (or VLIM2), CHAPS

turns switch OFF until the charger input has sunken below Vpor (nominal

3.0V, maximum 3.4V). MCU software will stop the charging (turn off

PWM) when it detects that battery has been removed. The CHAPS remains in protection state as long as PWM stays HIGH after the output

overvoltage situation has occured.

VCH

(Standard

Charger)

VOUT

Vpor

VLIM

4V

Vstart

Droop depends on load

& C in phone

Technical Documentation

Istart off due to VCH<Vpor

Vstarthys

PWM

SWITCH

1.1Battery removed, (standard) charger connected, VOUT rises (follows charger voltage)

2. VOUT exceeds limit VLIM(X), switch is turned immediately OFF

3.3VOUT falls (because no battery) , also VCH<Vpor (standard chargers full–rectified

4. Software sets PWM = LOW –> CHAPS does not enter PWM mode

5. PWM low –> Startup mode, startup current flows until Vstart limit reached

6. VOUT exceeds limit Vstart, Istart is turned off

7. VCH falls below Vpor

”1”

”0”

ON

OFF

2

output). When VCH > Vpor and VOUT < VLIM(X) –> switch turned on again (also PWM

is still HIGH) and VOUT again exceeds VLIM(X).

5

4

6

7

t

t

t

Page 3–22

Issue 2 01/00

Page 23

PAMS

NSM–1

Technical Documentation

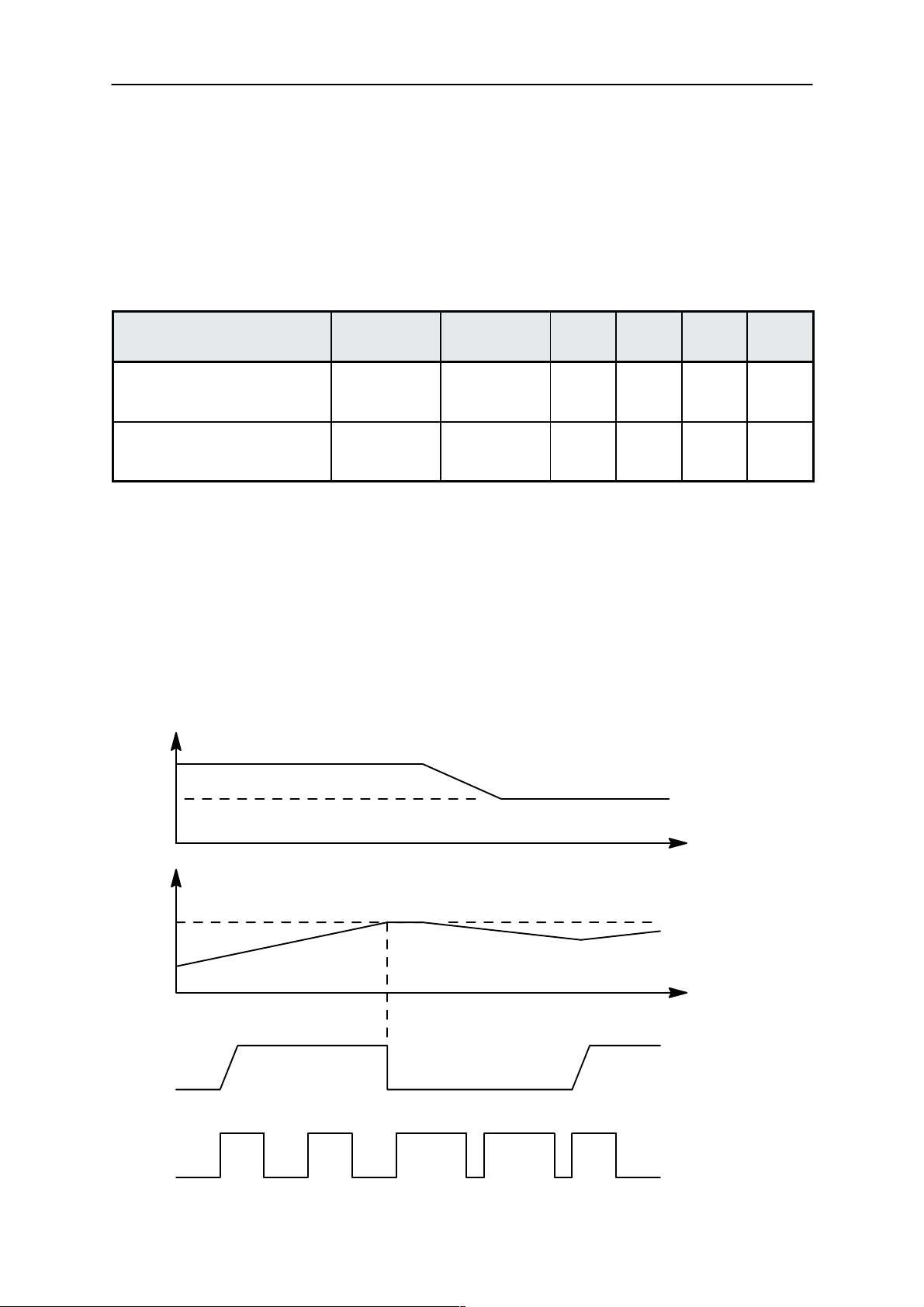

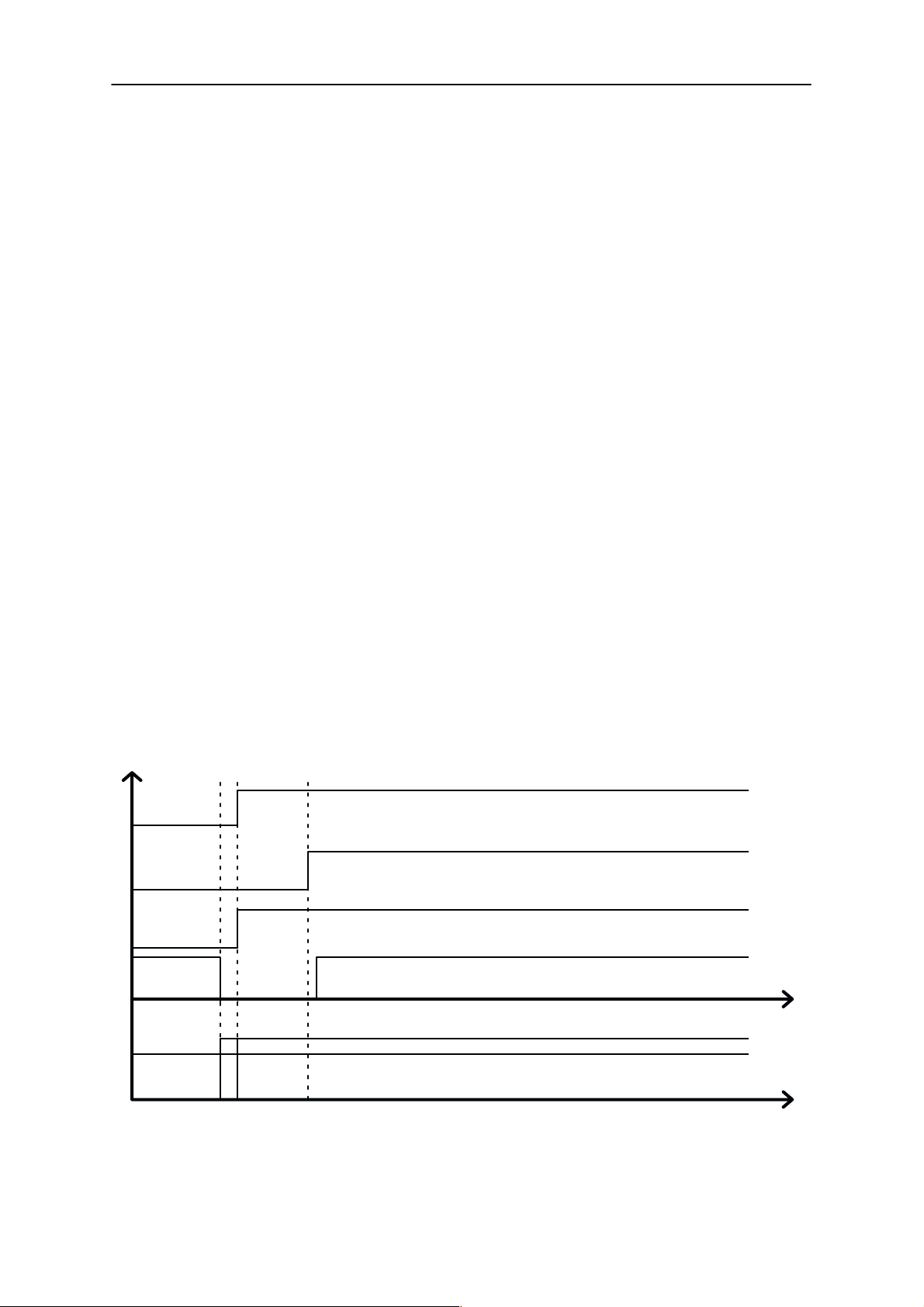

Different PWM Frequencies ( 1Hz and 32 Hz)

When a travel charger (2– wire charger) is used, the power switch is

turned ON and OFF by the PWM input when the PWM rate is 1Hz. When

PWM is HIGH, the switch is ON and the output current Iout = charger current – CHAPS supply current. When PWM is LOW, the switch is OFF and

the output current Iout = 0. To prevent the switching transients inducing

noise in audio circuitry of the phone soft switching is used.

The performance travel charger (3– wire charger) is controlled with PWM

at a frequency of 32Hz. When the PWM rate is 32Hz CHAPS keeps the

power switch continuously in the ON state.

SWITCH

ON ONON OFF OFF

System Module

PWM (1Hz)

SWITCH

PWM (32Hz)

ON

Issue 2 01/00

Page 3–23

Page 24

NSM–1

PAMS

System Module

Battery Identification

Different battery types are identified by a pulldown resistor inside the battery pack. The BSI line inside transceiver has a 100k pullup to VBB. The

MCU can identify the battery by reading the BSI line DC–voltage level

with a CCONT (N100) A/D–converter.

BATTERY

BVOLT

BTEMP

BSI

VBB

2.8V

100k

10k

Technical Documentation

TRANSCEIVER

BSI

CCONT

The battery identification line is used also for battery removal detection.

The BSI line is connected to a SIMCardDetX line of MAD2 (D200). SIMCardDetX is a threshold detector with a nominal input switching level

0.85xVcc for a rising edge and 0.55xVcc for a falling edge. The battery

removal detection is used as a trigger to power down the SIM card before

the power is lost. The BSI contact in the battery pack is made 0.7mm

shorter than the supply voltage contacts so that there is a delay between

battery removal detection and supply power off,

Vcc

0.850.05 Vcc

0.550.05 Vcc

R

s

BGND

10n

SIMCardDetX

MAD

Page 3–24

GND

SIMCARDDETX

S

IGOUT

Issue 2 01/00

Page 25

PAMS

NSM–1

Technical Documentation

Battery Temperature

The battery temperature is measured with a NTC inside the battery pack.

The BTEMP line inside transceiver has a 100k pullup to VREF. The MCU

can calculate the battery temperature by reading the BTEMP line DC–

voltage level with a CCONT (N100) A/D–converter.

BATTERY

BVOLT

BSI

BTEMP

TRANSCEIVER

VREF

100k

10k

System Module

BTEMP

CCONT

R

T

NTC

Supply Voltage Regulators

The heart of the power distrubution is the CCONT. It includes all the voltage regulators and feeds the power to the whole system. The baseband

digital parts are powered from the VBB regulator which provides 2.8V

baseband supply. The baseband regulator is active always when the

phone is powered on. The VBB baseband regulator feeds MAD and memories, COBBA digital parts and the LCD driver in the UI section. There is

a separate regulator for a SIM card. The regulator is selectable between

3V and 5V and controlled by the SIMPwr line from MAD to CCONT. The

COBBA analog parts are powered from a dedicated 2.8V supply VCOBBA. The CCONT supplies also 5V for RF and for flash VPP. The CCONT

contains a real time clock function, which is powered from a RTC backup

when the main battery is disconnected.

BGND

1k

1k

10n

VibraPWM

MAD

MCUGenIO4

Issue 2 01/00

Page 3–25

Page 26

NSM–1

PAMS

System Module

The RTC backup is rechargable polyacene battery, which has a capacity

of 50uAh (@3V/2V) The battery is charged from the main battery voltage

by the CHAPS when the main battery voltage is over 3.2V. The charging

current is 200uA (nominal).

Operating mode Vref RF REG VCOB-

BA

Power off Off Off Off Off Off Pull

Power on On On/Off On On On On/Off

Reset On Off

VR1 On

Sleep On Off On On On On/Off

NOTE:

On On Off Pull

Technical Documentation

VBB VSIM SIMIF

down

down

CCONT includes also five additional 2.8V regulators providing power to

the RF section. These regulators can be controlled either by the direct

control signals from MAD or by the RF regulator control register in

CCONT which MAD can update. Below are the listed the MAD control

lines and the regulators they are controlling.

– TxPwr controls VTX regulator (VR5)

– RxPwr controls VRX regulator (VR2)

– SynthPwr controls VSYN_1 and VSYN_2 regulators (VR4 and VR3)

– VCXOPwr controls VXO regulator (VR1)

CCONT generates also a 1.5 V reference voltage VREF to COBBA,

SUMMA and CRFU3. The VREF voltage is also used as a reference to

some of the CCONT A/D converters.

In additon to the above mentioned signals MAD includes also TXP control

signal which goes to SUMMA power control block and to the power amplifier. The transmitter power control TXC is led from COBBA to SUMMA.

Page 3–26

Issue 2 01/00

Page 27

PAMS

NSM–1

Technical Documentation

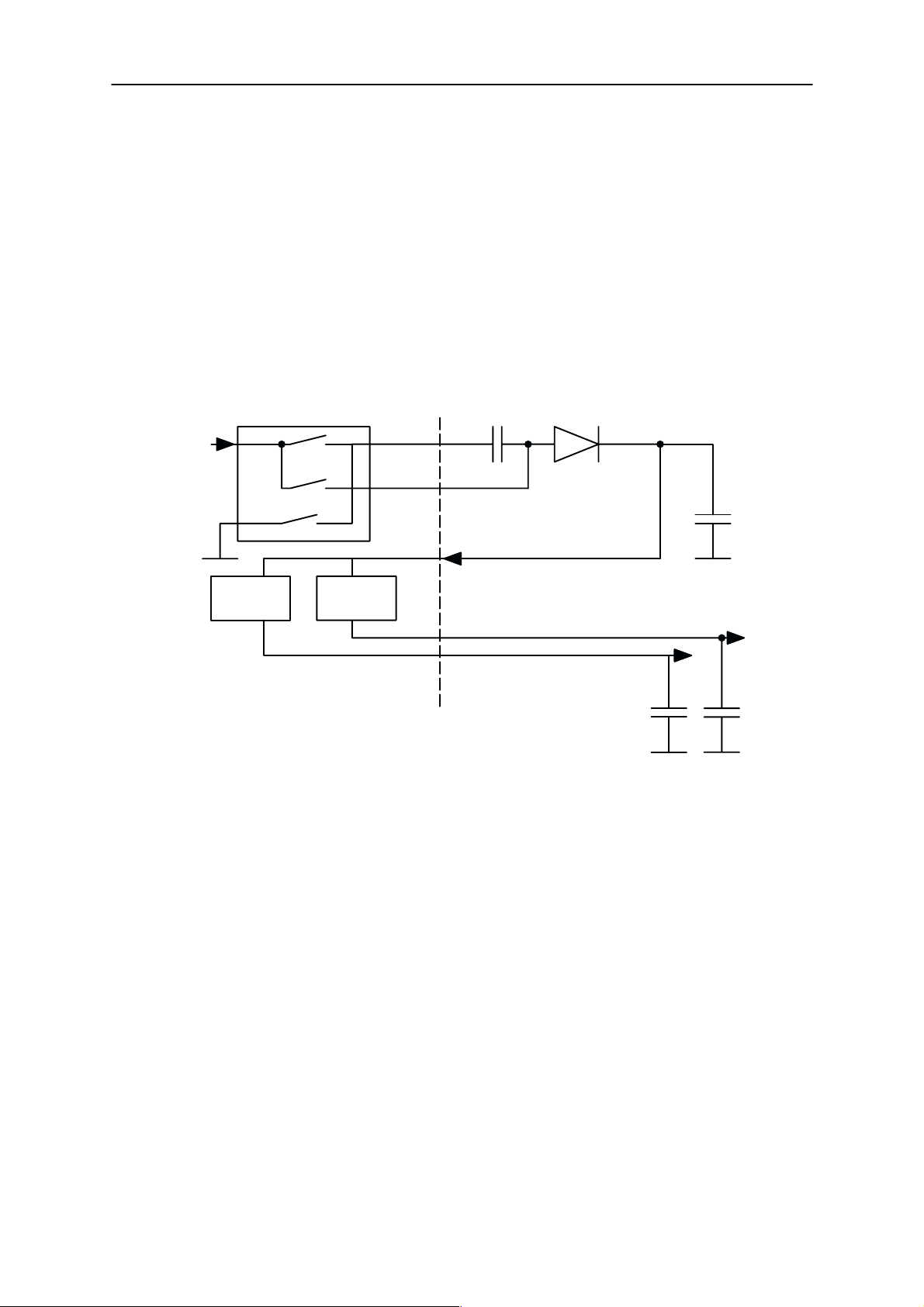

Switched Mode Supply VSIM

There is a switched mode supply for SIM–interface. SIM voltage is selected via serial IO. The 5V SMR can be switched on independently of the

SIM voltage selection, but can’t be switched off when VSIM voltage value

is set to 5V.

NOTE: VSIM and V5V can give together a total of 30mA.

In the next figure the principle of the SMR / VSIM–functions is shown.

CCONT External

VBAT

System Module

V5V_4

V5V_3

V5V_2

Power Up

VSIM

The baseband is powered up by:

1. Pressing the power key, that generates a PWRONX interrupt

2. Connecting a charger to the phone. The CCONT recognizes

3. A RTC interrupt. If the real time clock is set to alarm and the

5V reg

V5V

signal from the power key to the CCONT, which starts the power up procedure.

the charger from the VCHAR voltage and starts the power up

procedure.

phone is switched off, the RTC generates an interrupt signal,

when the alarm is gone off. The RTC interrupt signal is connected to the PWRONX line to give a power on signal to the

CCONT just like the power key.

5/3V

5V

Issue 2 01/00

4. A battery interrupt. Intelligent battery packs have a possibility

to power up the phone. When the battery gives a short (10ms)

voltage pulse through the BTEMP pin, the CCONT wakes up

and starts the power on procedure.

Page 3–27

Page 28

NSM–1

PAMS

System Module

Power up with a charger

When the charger is connected CCONT will switch on the CCONT digital

voltage as soon as the battery voltage exeeds 3.0V. The reset for

CCONT’s digital parts is released when the operating voltage is stabilized

( 50 us from switching on the voltages). Operating voltage for VCXO is

also switched on. The counter in CCONT digital section will keep MAD in

reset for 62 ms (PURX) to make sure that the clock provided by VCXO is

stable. After this delay MAD reset is relased, and VCXO –control

(SLEEPX) is given to MAD. The diagram assumes empty battery, but the

situation would be the same with full battery:

When the phone is powered up with an empty battery pack using the

standard charger, the charger may not supply enough current for standard powerup procedure and the powerup must be delayed.

Power Up With The Power Switch (PWRONX)

Technical Documentation

When the power on switch is pressed the PWRONX signal will go low.

CCONT will switch on the CCONT digital section and VCXO as was the

case with the charger driven power up. If PWRONX is low when the 64

ms delay expires, PURX is released and SLEEPX control goes to MAD. If

PWRONX is not low when 64 ms expires, PURX will not be released, and

CCONT will go to power off ( digital section will send power off signal to

analog parts)

SLEEPX

PURX

CCPURX

PWRONX

12 3

1:Power switch pressed ==> Digital voltages on in CCONT (VBB)

2: CCONT digital reset released. VCXO turned on

3: 62 ms delay to see if power switch is still pressed.

Page 3–28

VR1,VR6

VBB (2.8V)

Vchar

Issue 2 01/00

Page 29

PAMS

NSM–1

Technical Documentation

Power Up by RTC

RTC ( internal in CCONT) can power the phone up by changing RTCPwr to

logical ”1”. RTCPwr is an internal signal from the CCONT digital section.

Power Up by IBI

IBI can power CCONT up by sending a short pulse to logical ”1”. RTCPwr is

an internal signal from the CCONT digital section.

Acting Dead

If the phone is off when the charger is connected, the phone is powered

on but enters a state called ”acting dead”. To the user the phone acts as if

it was switched off. A battery charging alert is given and/or a battery

charging indication on the display is shown to acknowledge the user that

the battery is being charged.

Active Mode

System Module

In the active mode the phone is in normal operation, scanning for channels, listening to a base station, transmitting and processing information.

All the CCONT regulators are operating. There are several substates in

the active mode depending on if the phone is in burst reception, burst

transmission, if DSP is working etc..

Sleep Mode

In the sleep mode, all the regulators except the baseband VBB, VCOBBA,

and the SIM card VSIM regulators are off. Sleep mode is activated by the

MAD after MCU and DSP clocks have been switched off. The voltage regulators for the RF section are switched off and the VCXO power control,

VCXOPwr is set low. In this state only the 32 kHz sleep clock oscillator in

CCONT is running. The flash memory power down input is connected to

the ExtSysResetX signal, and the flash is deep powered down during the

sleep mode.

The sleep mode is exited either by the expiration of a sleep clock counter

in the MAD or by some external interrupt, generated by a charger connection, key press, headset connection etc. The MAD starts the wake up

sequence and sets the VCXOPwr and ExtSysResetX control high. After

VCXO settling time other regulators and clocks are enabled for active

mode.

If the battery pack is disconnect during the sleep mode, the CCONT pulls

the SIM interface lines low as there is no time to wake up the MCU.

Charging

Charging can be performed in any operating mode. The charging algorithm is dependent on the used battery technology. The battery type is in-

Issue 2 01/00

Page 3–29

Page 30

NSM–1

PAMS

System Module

dicated by a resistor inside the battery pack. The resistor value corresponds to a specific battery capacity. This capacity value is related to the

battery technology as different capacity values are achieved by using different battery technology.

The battery voltage, temperature, size and current are measured by the

CCONT controlled by the charging software running in the MAD.

The power management circuitry controls the charging current delivered

from the charger to the battery. Charging is controlled with a PWM input signal, generated by the CCONT. The PWM pulse width is controlled by the

MAD and sent to the CCONT through a serial data bus. The battery voltage

rise is limited by turning the CHAPS switch off when the battery voltage has

reached 4.2V (LiIon) or 5.2V (NiMH, 5V in call mode). Charging current is

monitored by measuring the voltage drop across a 220mohm resistor.

Power Off

The baseband is powered down by:

Technical Documentation

1. Pressing the power key, that is monitored by the MAD, which

starts the power down procedure.

2. If the battery voltage is dropped below the operation limit, either by not charging it or by removing the battery.

3. Letting the CCONT watchdog expire, which switches off all

CCONT regulators and the phone is powered down.

4. Setting the real time clock to power off the phone by a timer.

The RTC generates an interrupt signal, when the alarm is gone

off. The RTC interrupt signal is connected to the PWRONX line

to give a power off signal to the CCONT just like the power key.

The power down is controlled by the MAD. When the power key has been

pressed long enough or the battery voltage is dropped below the limit the

MCU initiates a power down procedure and disconnects the SIM power.

Then the MCU outputs a system reset signal and resets the DSP. If there is

no charger connected the MCU writes a short delay to CCONT watchdog

and resets itself. After the set delay the CCONT watchdog expires, which

activates the PURX and all regulators are switched off and the phone is

powered down by the CCONT.

If a charger is connected when the power key is pressed the phone enters into the acting dead mode.

Watchdog

Page 3–30

The Watchdog block inside CCONT contains a watchdog counter and

some additional logic which are used for controlling the power on and

power off procedures of CCONT. Watchdog output is disabled when

WDDisX pin is tied low. The WD-counter runs during that time, though.

Watchdog counter is reset internally to 32s at power up. Normally it is reset by MAD writing a control word to the WDReg.

Issue 2 01/00

Page 31

PAMS

NSM–1

Technical Documentation

Audio control

The audio control and processing is taken care by the COBBA–GJ, which

contains the audio and RF codecs, and the MAD2, which contains the

MCU, ASIC and DSP blocks handling and processing the audio signals. A

detailed audio specification can be found from document

MICP/N

System

Connector

Bias +

EMC

EMC + Acc.

XMIC

SGND

XEAR

Interf.

EMC

Preamp

MIC2

MIC1

MIC3

HFCM

AuxOut

HF

EAR

Multipl.Premult.

Amp Multipl.

COBBA

Pre

& LP

LP

System Module

MAD

DSP

A

D

D

A

MCU

Buzzer

Driver

Circuit

Buzzer

The baseband supports three microphone inputs and two earphone outputs. The inputs can be taken from an internal microphone, a headset microphone or from an external microphone signal source. The microphone

signals from different sources are connected to separate inputs at the

COBBA–GJ asic. Inputs for the microphone signals are differential type.

The MIC1 inputs are used for a headset microphone that can be connected directly to the system connector. The internal microphone is connected to MIC2 inputs and an external pre–amplified microphone (handset/handfree) signal is connected to the MIC3 inputs. In COBBA there are

also three audio signal outputs of which dual ended EAR lines are used

for internal earpiece and HF line for accessory audio output. The third audio output AUXOUT is used only for bias supply to the headset microphone. As a difference to DCT2 generation the SGND ( = HFCM at COBBA) does not supply audio signal (only common mode). Therefore there

are no electrical loopback echo from downlink to uplink.

The output for the internal earphone is a dual ended type output capable

of driving a dynamic type speaker. The output for the external accessory

and the headset is single ended with a dedicated signal ground SGND.

Input and output signal source selection and gain control is performed inside the COBBA–GJ asic according to control messages from the MAD2.

Keypad tones, DTMF, and other audio tones are generated and encoded

by the MAD2 and transmitted to the COBBA–GJ for decoding.

Issue 2 01/00

Page 3–31

Page 32

NSM–1

PAMS

System Module

External Audio Connections

The external audio connections are presented in figure 16. A headset can

be connected directly to the system connector. The headset microphone

bias is supplied from COBBA AUXOUT output and fed to microphone

through XMIC line. The 330ohm resistor from SGND line to AGND provides a return path for the bias current.

Baseband

HookDet

MAD

HeadDet

1u

Technical Documentation

2.8 V

47k

22k

22k

1u

CCONT

AUXOUT

COBBA

EAD

HFC

M

MIC1

N

MIC1

P

MIC3

N

MIC3

P

2.8 V

47k

47R

1m

10m

H

F

10m

33n

33n

33n

33n

47R

47R

330R

2k2

2k2

2k2

XEAR

SGN

D

XMI

C

Page 3–32

Issue 2 01/00

Page 33

PAMS

NSM–1

Technical Documentation

System Module

Analog Audio Accessory Detection

In XEAR signal there is a 47 kW pullup in the transceiver and 6.8 kW

pull–down to SGND in accessory. The XEAR is pulled down when an

accessory is connected, and pulled up when disconnected. The XEAR is

connected to the HookDet line (in MAD), an interrupt is given due to both

connection and disconnection. There is filtering between XEAR and

HookDet to prevent audio signal giving unwanted interrupts.

External accessory notices powered–up phone by detecting voltage in

XMIC line. In Table 23 there is a truth table for detection signals.

Accessory connected HookDet HeadDet Notes

No accessory connected High High Pullups in the transceiver

Headset HDC–9 with a button switch

pressed

Headset HDC–9 with a button switch re-

leased

Handsfree (HFU–1) Low High XEAR loaded (dc)

Low Low XEAR and XMIC loaded (dc)

High Low *) XEAR unloaded (dc)

Headset Detection

The external headset device is connected to the system connector, from

which the signals are routed to COBBA headset microphone inputs and

earphone outputs. In the XMIC line there is a (47 + 2.2) kW pullup in the

transceiver. The microphone is a low resistancepulldown compared to

the transceiver pullup.

When there is no call going, the AUXOUT is in high impedance state and

the XMIC is pulled up. When a headset is connected, the XMIC is pulled

down. The XMIC is connected to the HeadDet line (in MAD), an interrupt

is given due to both connection and disconnection. There is filtering between the XMIC and the HeadDet to prevent audio signal giving unwanted interrupts (when an accessory is connected).

In the XEAR line there is a 47 kW pullup in the transceiver. The earphone

is a low resistance pulldown compared to the transceiver pullup. When a

remote control switch is open, there is a capacitor in series with the earphone, so the XEAR (and HookDet) is pulled up by the phone. When the

switch is closed, the XEAR (and HookDet) is pulled down via the earphone. So both press and release of the button gives an interrupt.

During a call there is a bias voltage (1.5 V) in the AUXOUT, and the

HeadDet cannot be used. The headset interrupts should to be disabled

during a call and the EAD line (AD converter in CCONT) should be polled

to see if the headset is disconnected.

Issue 2 01/00

Page 3–33

Page 34

NSM–1

PAMS

System Module

Internal Audio Connections

The speech coding functions are performed by the DSP in the MAD2 and

the coded speech blocks are transferred to the COBBA–GJ for digital to

analog conversion, down link direction. In the up link direction the PCM

coded speech blocks are read from the COBBA–GJ by the DSP.

There are two separate interfaces between MAD2 and COBBA–GJ: a

parallel bus and a serial bus. The parallel bus has 12 data bits, 4 address

bits, read and write strobes and a data available strobe. The parallel interface is used to transfer all the COBBA–GJ control information (both the

RFI part and the audio part) and the transmit and receive samples. The

serial interface between MAD2 and COBBA–GJ includes transmit and receive data, clock and frame synchronisation signals. It is used to transfer

the PCM samples. The frame synchronisation frequency is 8 kHz which

indicates the rate of the PCM samples and the clock frequency is 1 MHz.

COBBA is generating both clocks.

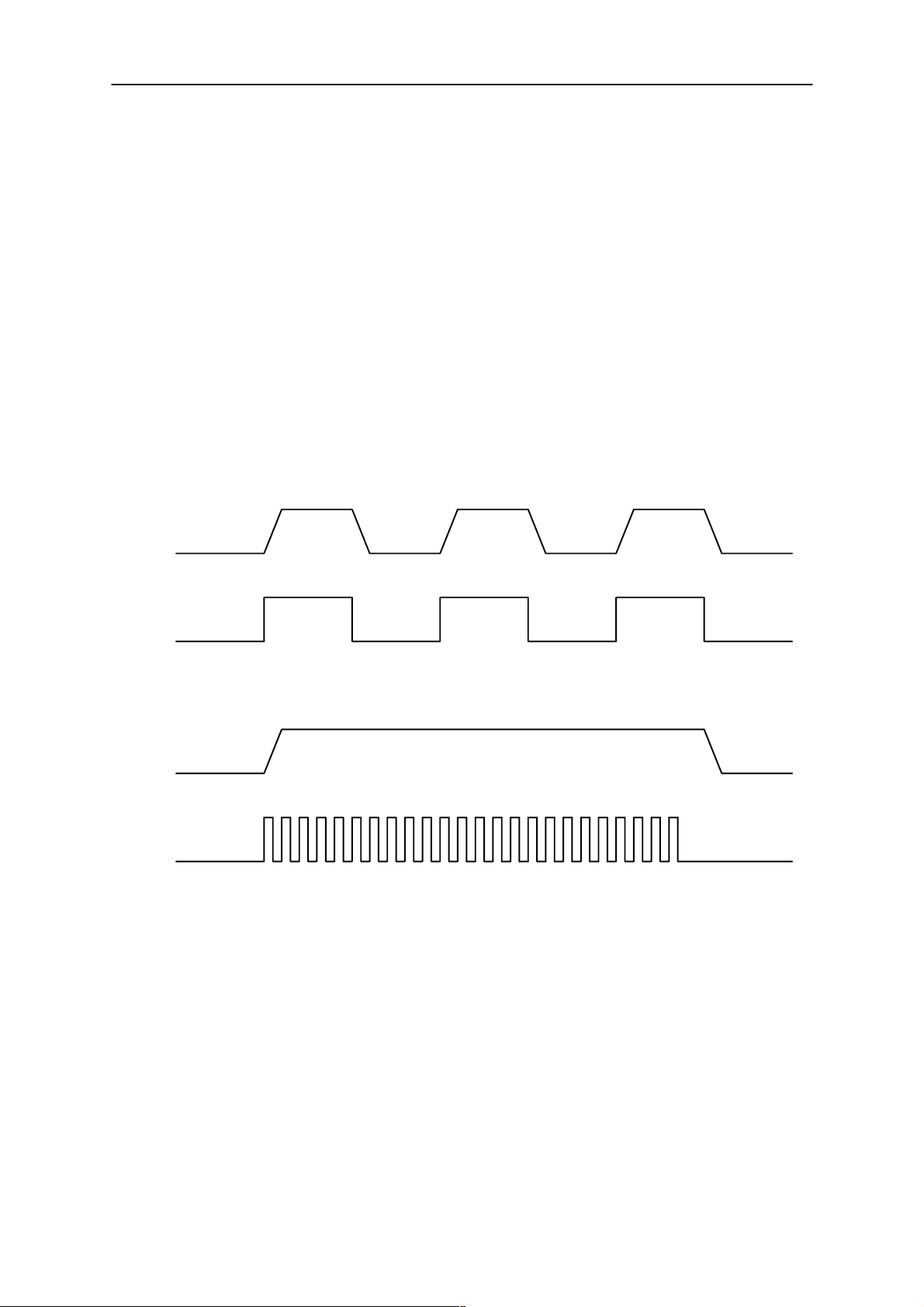

4–wire PCM Serial Interface

Technical Documentation

The interface consists of following signals: a PCM codec master clock

(PCMDClk), a frame synchronization signal to DSP (PCMSClk), a codec

transmit data line (PCMTX) and a codec receive data line (PCMRX). The

COBBA–GJ generates the PCMDClk clock, which is supplied to DSP SIO.

The COBBA–GJ also generates the PCMSClk signal to DSP by dividing

the PCMDClk. The PCMDClk frequency is 1.000 MHz and is generated

by dividing the RFIClk 13 MHz by 13. The COBBA–GJ further divides the

PCMDClk by 125 to get a PCMSClk signal, 8.0 kHz.

PCMDClk

PCMSClk

PCMTxData

PCMRxData

sign extended

15 14 13 12 011 10

sign extended

MSB

MSB

LSB

LSB

Page 3–34

Issue 2 01/00

Page 35

PAMS

NSM–1

Technical Documentation

Alert Signal Generation

A buzzer is used for giving alerting tones and/or melodies as a signal of

an incoming call. Also keypress and user function response beeps are

generated with the buzzer. The buzzer is controlled with a BuzzerPWM

output signal from the MAD. A dynamic type of buzzer must be used

since the supply voltage available can not produce the required sound

pressure for a piezo type buzzer. The low impedance buzzer is connected

to an output transistor that gets drive current from the PWM output. The

alert volume can be adjusted either by changing the pulse width causing

the level to change or by changing the frequency to utilize the resonance

frequency range of the buzzer.

A vibra alerting device is used for giving silent signal to the user of an incoming call. The device is controlled with a VibraPWM output signal from

the MAD2. The vibra alert can be adjusted either by changing the pulse

width or by changing the pulse frequency. The vibra device is not inside

the phone, but in a special vibra battery.

System Module

Digital Control

The baseband functions are controlled by the MAD asic, which consists of

a MCU, a system ASIC and a DSP.

MAD2

MAD2 contains following building blocks:

– ARM RISC processor with both 16–bit instruction set (THUMB mode)

and 32–bit instruction set (ARM mode)

– TI Lead DSP core with peripherials:

– BUSC (BusController for controlling accesses from ARM to API, Sys-

tem Logic and MCU external memories, both 8– and 16–bit memories)

– API (Arm Port Interface memory) for MCU–DSP commu-

nication, DSP code download, MCU interrupt handling vec-

tors (in DSP RAM) and DSP booting

– Serial port (connection to PCM)

– Timer

– DSP memory

– System Logic

Issue 2 01/00

– CTSI (Clock, Timing, Sleep and Interrupt control)

– MCUIF (Interface to ARM via B

USC). Contains MCU Boo-

tROM

– DSPIF (Interface to DSP)

– MFI (Interface to COBBA AD/DA Converters)

Page 3–35

Page 36

NSM–1

PAMS

System Module

The MAD2 operates from a 13 MHz system clock, which is generated

from the 13Mhz VCXO frequency. The MAD2 supplies a 6,5MHz or a

13MHz internal clock for the MCU and system logic blocks and a 13MHz

clock for the DSP, where it is multiplied to 52 MHz DSP clock. The system

clock can be stopped for a system sleep mode by disabling the VCXO

supply power from the CCONT regulator output. The CCONT provides a

32kHz sleep clock for internal use and to the MAD2, which is used for the

sleep mode timing. The sleep clock is active when there is a battery voltage available i.e. always when the battery is connected.

Technical Documentation

– CODER (Block encoding/decoding and A51&A52 ciphering)

– AccIF(Accessory Interface)

– SCU (Synthesizer Control Unit for controlling 2 separate

synthesizer)

– UIF (Keyboard interface, serial control interface for COBBA

PCM Codec, LCD Driver and CCONT)

– SIMI (SimCard interface with enhanched features)

– PUP (Parallel IO, USART and PWM control unit for vibra

and buzzer)

Pin

N:o

1 MCUGenOut5 O Audio 2 0 MCU General

2 MCUGenOut4 O N101 2 0 MCU General

3 LEADGND Lead Ground

4 MCUGenOut3 O 2 0 MCU General

5 VCC IO VCC in

6 MCUGenOut2 O 2 0 MCU General

7 MCUGenOut1 O MCU

8 MCUGenOut0 O 2 1 LoByteSelX

9 Col4 I/O UIF 2 Input program-

Pin Name Pin

Type

Connected

to/from

memory

Drive

req.

mA

Reset

State

2 0 MCU General

Note Explanation

purpose output

purpose output

purpose output

Power

1833c07

purpose output

purpose output

MCU General

in 16–bit

mode

mable pullup

PR0201

purpose output

I/O line for keyboard column 4

port

port

port

port

port

port

Page 3–36

Issue 2 01/00

Page 37

PAMS

NSM–1

Technical Documentation

Pin NamePin

N:o

10 Col3 I/O UIF 2 Input program-

11 GND Ground

12 Col2 I/O UIF 2 Input program-

13 Col1 I/O UIF 2 Input program-

14 Col0 I/O UIF 2 Input program-

15 LCDCSX I/O UIF 2 Input external

Pin

Type

Connected

to/from

Drive

req.

mA

State

mable pullup

PR0201

mable pullup

PR0201

mable pullup

PR0201

mable pullup

PR0201

pullup/down

System Module

ExplanationNoteReset

I/O line for keyboard column 3

I/O line for keyboard column 2

I/O line for keyboard column 1

I/O line for keyboard column 0

serial LCD driver

chip select, par-

allel LCD driver

enable

16 LEADVCC Lead Power

17 Row5LCDCD I/O UIF 2 Input,

pullup

18 VCC Core VCC in

19 Row4 I/O UIF 2 Input,

pullup

20 Row3 I/O UIF 2 Input,

pullup

21 Row2 I/O UIF 2 Input,

pullup

pullup

PR0201

1833c07

pullup

PR0201

pullup

PR0201

pullup

PR0201

Keyboard row5

data I/O , serial

LCD driver com-

mand/data indi-

cator, parallel

LCD driver read/

write select

Power

I/O line for key-

board row 4, par-

allel LCD driver

register selection

control

I/O line for key-

board row 3, par-

allel LCD driver

data

I/O line for key-

board row 2, par-

allel LCD driver

data

22 Row1 I/O UIF 2 Input,

pullup

23 Row0 I/O UIF 2 Input,

pullup

Issue 2 01/00

pullup

PR0201

pullup

PR0201

I/O line for key-

board row 1, par-

allel LCD driver

data

I/O line for key-

board row 0, par-

allel LCD driver

data

Page 3–37

Page 38

NSM–1

PAMS

System Module

Pin NamePin

N:o

24 JTDO O 2 Tri–

25 GND Ground

26 JTRst I Input,

27 JTClk I Input pulldown

28 JTDI I Input,

29 JTMS I Input,

30 VCC IO VCC in

Pin

Type

Connected

to/from

Drive

req.

mA

State

state

pull-

down

pullup

pullup

Technical Documentation

ExplanationNoteReset

JTAG data out

pulldown

PD0201

PD0201

pullup

PR0201

pullup

PR0201

1833c07

JTAG reset

JT AG Clock

JTAG data in

JTAG mode se-

Power

lect

31 CoEmu0 I/O 2 Input,

pullup

32 CoEmu1 I/O 2 Input,

pullup

33 MCUGenIO7 I/O 2 Input,

pull-

down

34 MCUGenIO6 I/O UI 2 Input,

pull-

down

35 LEADGND Lead Ground

36 MCUGenIO5 I/O UI 2 Input,

pull-

down

37 ARMGND ARM Ground

38 MCUAd0 O MCU

MEMORY

39 ARMVCC ARM Power

40 MCUAd1 O MCU

MEMORY

41 MCUAd2 O MCU

MEMORY

2 0 MCU address

2 0 MCU address

2 0 MCU address

pullup

PR0201

pullup

PR0201

pulldown

PD1001

pulldown

PD1001

pulldown

PD1001

DSP/MCU

emulation port 0

DSP/MCU

emulation port 1

General purpose

I/O port

Lights

LCD reset

bus

bus

bus

42 GND Ground

43 MCUAd3 O MCU

MEMORY

44 MCUAd4 O MCU

MEMORY

45 MCUAd5 O MCU

MEMORY

Page 3–38

2 0 MCU address

bus

2 0 MCU address

bus

2 0 MCU address

bus

Issue 2 01/00

Page 39

PAMS

NSM–1

Technical Documentation

Pin NamePin

N:o

46 MCUAd6 O MCU

47 VCC IO VCC in

48 MCUAd7 O MCU

49 MCUAd8 O MCU

50 MCUAd9 O MCU

51 MCUAd10 O MCU

52 GND Ground

53 MCUAd11 O MCU

54 MCUAd12 O MCU

55 MCUAd13 O MCU

56 MCUAd14 O MCU

57 MCUAd15 O MCU

58 MCUAd16 O MCU

59 VCC Core VCC in

60 MCUAd17 O MCU

61 MCUAd18 O MCU

62 MCUAd19 O MCU

63 MCUAd20 O MCU

64 MCUAd21 O MCU

65 ExtMCUDa0 I/O MCU

66 GND Ground

Pin

Type

Connected

to/from

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

Drive

req.

mA

State

2 0 MCU address

1833c07

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

1833c07

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 0 MCU address

2 Input MCU data bus

System Module

ExplanationNoteReset

Power

Power

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

bus

67 ExtMCUDa1 I/O MCU

MEMORY

68 ExtMCUDa2 I/O MCU

MEMORY

Issue 2 01/00

2 Output MCU data bus

2 Output MCU data bus

Page 3–39

Page 40

NSM–1

PAMS

System Module

Pin NamePin

N:o

69 ExtMCUDa3 I/O MCU

70 ExtMCUDa4 I/O MCU

71 ExtMCUDa5 I/O MCU

72 ExtMCUDa6 I/O MCU

73 VCC IO VCC in

74 ExtMCUDa7 I/O MCU

75 MCUGenIO8 I/O 2 Input MCU Data in

76 MCUGenIO9 I/O 2 Input MCU Data in

77 MCUGenIO10 I/O 2 Input MCU Data in

78 MCUGenIO11 I/O 2 Input MCU Data in

79 GND Ground

Pin

Type

Connected

to/from

MEMORY

MEMORY

MEMORY

MEMORY

MEMORY

Drive

req.

mA

State

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

2 Output MCU data bus

Technical Documentation

ExplanationNoteReset

Power

3325c10

General purpose

16–bit mode

16–bit mode

16–bit mode

16–bit mode

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

80 MCUGenIO12 I/O 2 Input MCU Data in

16–bit mode

81 MCUGenIO13 I/O 2 Input MCU Data in

16–bit mode

82 MCUGenIO14 I/O 2 Input MCU Data in

16–bit mode

83 MCUGenIO15 I/O 2 Input MCU Data in

16–bit mode

84 MCURdX O MCU

MEMORY

85 VCC Core VCC in

86 MCUWrX O MCU

MEMORY

87 ROM1SelX O MCU ROM 2 1 ROM chip select

88 RAMSelX O MCU RAM 2 1 RAM chip select

89 ROM2SelX O MCU ROM2 2 1 Extra chip select,

90 MCUGenIO1 I/O 2 Input,

91 DSPXF O 2 1 External flag

2 1 MCU Read

1833c07

2 1 MCU write

pullup

pullup

PR0201

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

General purpose

I/O port

strobe

Power

strobe

can be used as

MCU general

output

General purpose

I/O port

Page 3–40

Issue 2 01/00

Page 41

PAMS

NSM–1

Technical Documentation

Pin NamePin

N:o

92 SCVCC Special cell Pow-

93 RFClk I VCXO Input System clock

94 RFClkGnd Input System clock

95 SIMCardDetX I Input SIM card detec-

96 SCGND Special cell

97 BuzzPWM O BUZZER 2 0 Buzzer PWM

98 LEADVCC LEAD Power

99 VibraPWM O VIBRA 2 0 Vibra PWM con-

100 GND Ground

Pin

Type

Connected

to/from

Drive

req.

mA

State

System Module

ExplanationNoteReset

er

from VCTCXO

reference ground

input

tion

Ground

control

trol

101 MCUGenIO3 I/O EEPROM 2 Input,

pullup

102 MCUGenIO2 I/O EEPROM 2 Input,

pullup

103 EEPROMSelX O MCU EE-

PROM

104 AccTxData I/O 4 Tri–

105 VCC IO VCC in

106 GenDet I Input General purpose

107 HookDet I Input Non–MBUS ac-

108 HeadDet I Input Headset detec-

109 AccRxData I Input Accessory RX

110 GND Ground

2 1 EEPROM chip

State

pullup

PR1001

pullup

PR1001

external

pullup

1833c07

General purpose

I/O port

WP SCL

select, can be

used as MCU

general output

Accessory TX

data, Flash_TX

Power

interrupt

cessory connec-

tion detector

tion interrupt

data, Flash_RX

111 MCUGenIO4 I/O 2 Input,

pull-

down

Issue 2 01/00

pulldown

PD1001

General purpose

I/O port

Page 3–41

Page 42

NSM–1

PAMS

System Module

Pin NamePin

N:o

112 MBUS I/O 2 Input,

113 VCXOPwr O CCONT 2 1 VCXO regulator

114 SynthPwr O CCONT 2 0 Synthesizer reg-

115 VCC Core VCC in

116 GenCCONTCSX O CCONT 2 1 Chip select to

117 LEADGND LEAD Ground

118 GenSDIO I/O CCONT, UIF 2 Input,

Pin

Type

Connected

to/from

Drive

req.

mA

State

exter-

nal

pullup

exter-

nal

pullup/

down

Technical Documentation

ExplanationNoteReset

external

pullup

1833c07

external

pullup/down

depending

on how to

boot

MBUS, Flash

clock

control

ulator control

Power

CCONT

Serial data in/out

119 GenSClk O CCONT, UIF 2 0 Serial clock

120 SIMCardData I/O CCONT 2 0 SIM data

121 GND Ground

122 PURX I CCONT Input Power Up Reset

123 CCONTInt I CCONT Input CCONT interrupt

124 Clk32k I CCONT Input Sleep clock os-

cillator input

125 VCC IO VCC in

1833c07

126 SIMCardClk O CCONT 2 0 SIM clock

127 SIMCardRstX O CCONT 2 0 SIM reset

128 SIMCardIOC O CCONT 2 0 SIM data in/out

129 SIMCardPwr O CCONT 2 0 SIM power con-

130 LEADVCC LEAD Power

131 RxPwr O CCONT 2 0 RX regulator

132 TxPwr O CCONT 2 0 TX regulator

Power

control

trol

control

control

133 TestMode I Input,

pull-

down

134 ExtSysResetX O 2 0 System Reset

Page 3–42

pulldown

PD0201

Test mode select

Issue 2 01/00

Page 43

PAMS

NSM–1

Technical Documentation

Pin NamePin

N:o

135 PCMTxData O COBBA 2 0 Transmit data,

136 VCC IO VCC in

137 PCMRxData I COBBA Input Receive data,

138 PCMDClk I COBBA Input Transmit clock,

139 PCMSClk I COBBA Input Transmitframe

140 COBBADAX I COBBA Input Data available

141 GND Ground

142 COBBAWrX O COBBA 2 1 COBBA write

Pin

Type

Connected

to/from

Drive

req.

mA

State

1833c07

System Module