NEC UPD72850AGK-9EU Datasheet

DATA SHEET

MOS INTEGRATED CIRCUIT

PD72850A

µµµµ

IEEE1394 400Mbps PHY

The µPD72850A is the 3-port physical layer LSI which complies with the P1394a draft 2.0 specifications.

The µPD72850A works up to 400 Mbps. It is an upgrade of NEC's µPD72850.

FEATURES

• The Three-port Physical Layer LSI complies to IEEE P1394a draft 2.0

• Connection debounce

• Arbitration enhancements

• Arbitrated short bus reset

• Ack-accelerated arbitration

• Fly-by concatenation

• Multiple-speed packet concatenation

• Arbitration enhancements and cycle start (controlled by the Link layer)

• Performance optimization via PHY pinging

• Priority arbitration (controlled by the Link layer)

• Data rate: 393.216 / 196.608 / 98.304 Mbps

• Compliant with Suspend/Resume function as defined in P1394a draft 2.1

• 3.3 V single power supply

• Electrical isolated Link interface

• 24.576 MHz crystal clock generation, 393.216 MHz PLL multiplying frequency

• System power management by signaling of node power class information

• Cable power monitor (CPS) is equipped

• Fully interoperable with IEEE1394 std 1394 Link (FireWireTM, i.LINKTM)

• Cable bias and terminal voltage driver supply function (for 3-port each)

• Separate digital power and analog GND

• Enable/Disable port control switch when power supply is powered on

• Support Suspend/Resume Off mode (Compliant with P1394a draft 1.3)

• Number of supported port are selectable

• 1port, 2port, 3port. This selection is only under Suspend/Resume Off mode

• Compliant with MD8405E (FUJIFILM MICRODEVICES CO., LTD)

ORDERING INFORMATION

Part number Package

µ

PD72850AGK-9EU 80-pin plastic TQFP (Fi ne pitch) (12 x 12 mm)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. S14452EJ1V0DS00 (1st edition)

Date Published October 1999 NS CP(K)

Printed in Japan

1999

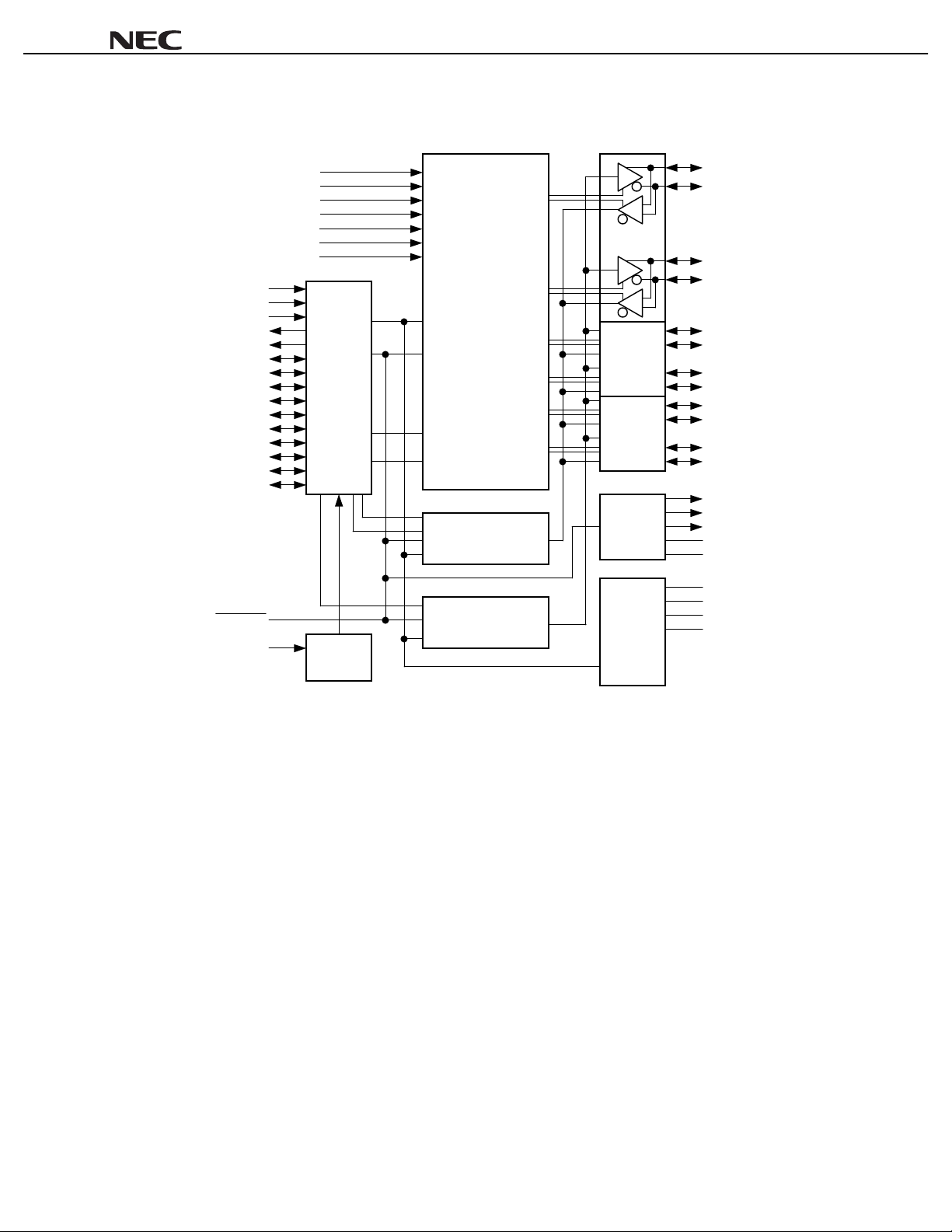

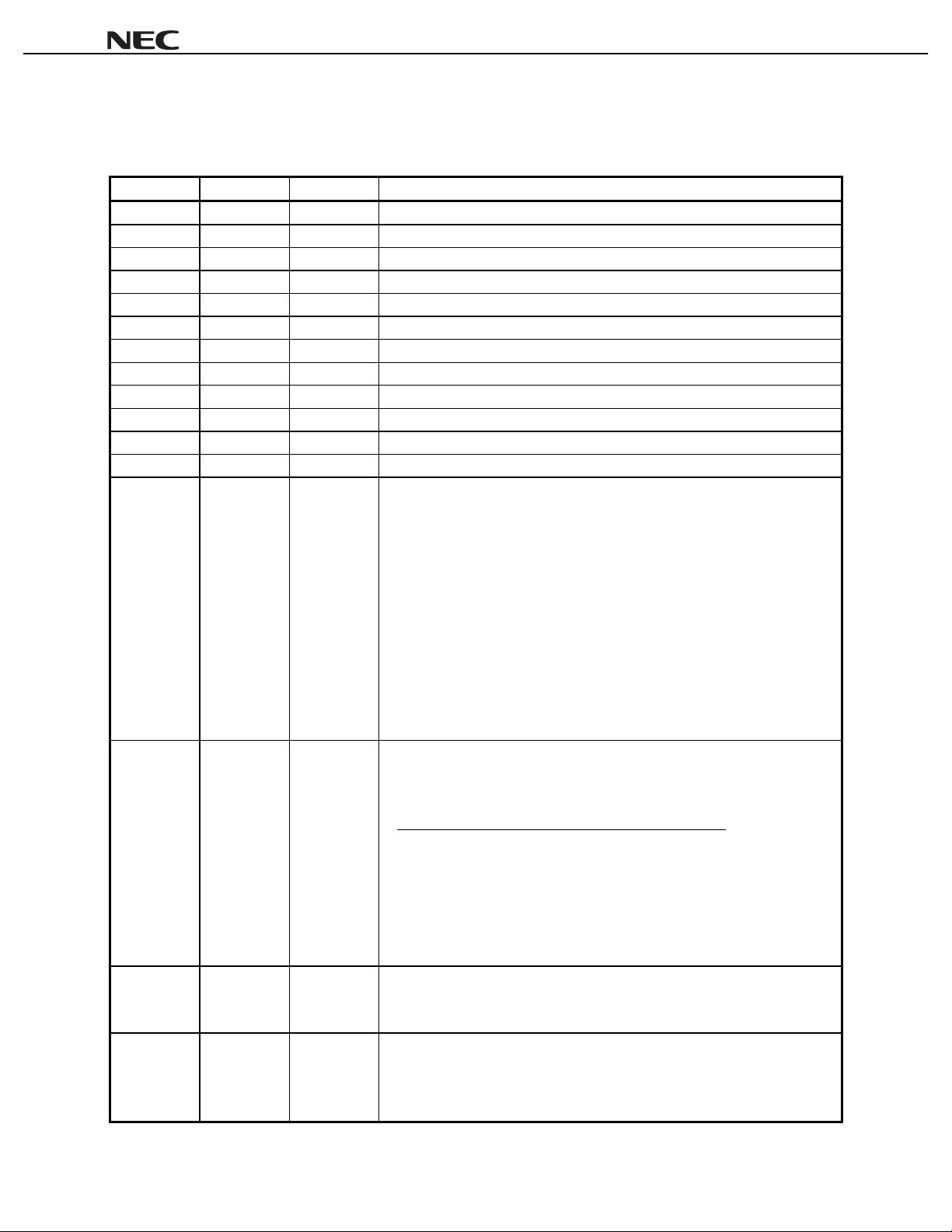

BLOCK DIAGRAM

µµµµ

PD72850A

LREQ

LPS

DIRECT

SCLK

LKON

CTL0

CTL1

D0

D1

D2

D3

D4

D5

D6

D7

RESETB

CPS

CMC

PC0

PC1

PC2

PORTDIS

PSEL

SUS/RES

Link

Interface

I/O

Cable

Power

Status

Arbitration

and Control

State Machine

Logic

Receive Data

Decoder and

Retimer

Transmit Data

Encoder

Cable

Port1

Cable

Port2

Cable

Port3

Voltage

and

Current

Generator

Crystal

Oscillator

PLL

System

and

Transmit

Clock

Generator

TpA0p

TpA0n

TpB0p

TpB0n

TpA1p

TpA1n

TpB1p

TpB1n

TpA2p

TpA2n

TpB2p

TpB2n

TpBias0

TpBias1

TpBias2

R0

R1

XI

XO

FIL0

FIL1

2

Data Sheet S14452EJ1V0DS00

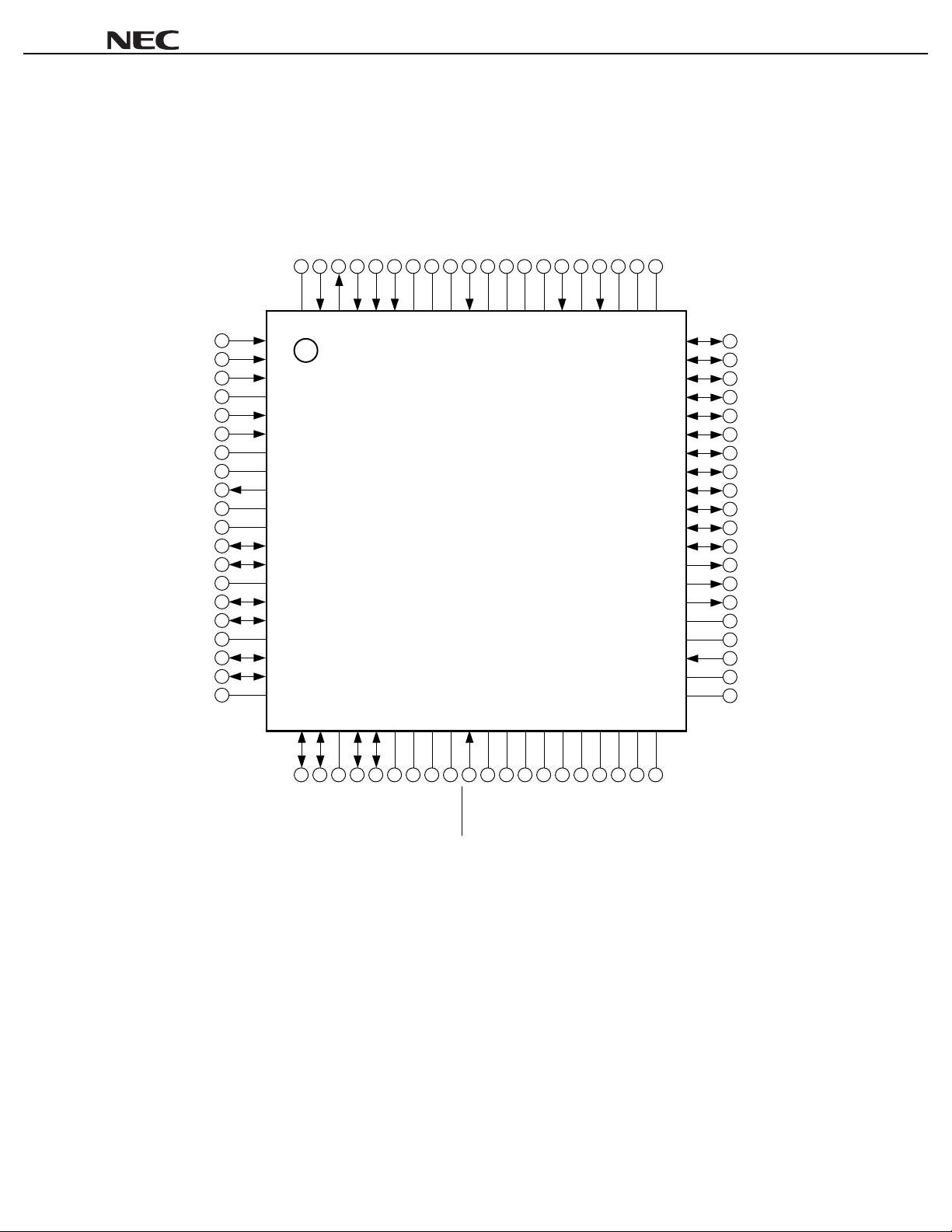

PIN CONFIGURATION (Top View)

• 80-pin plastic TQFP (Fine pitch) (12 x 12 mm)

DVDDPC2

LKON

DIRECT

IC(H)

IC(H)

DGND

AVDDAGND

µµµµ

PD72850A

SUS/RES

AGND

AGND

AGND

AVDDPSEL

AGND

PORTDIS

AVDDAGND

AGND

PC1

PC0

CMC

DGND

LPS

LREQ

DV

DGND

SCLK

DV

DGND

CTL0

CTL1

DV

D0

D1

DGND

D2

D3

DGND

80797877767574737271706968676665646362

1

2

3

4

5

6

DD

7

8

9

DD

10

11

12

13

DD

14

15

16

17

18

19

20

21222324252627282930313233343536373839

61

40

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

TpA0p

TpA0n

TpB0p

TpB0n

TpA1p

TpA1n

TpB1p

TpB1n

TpA2p

TpA2n

TpB2p

TpB2n

TpBias0

TpBias1

TpBias2

DD

AV

AGND

CPS

RI1

RI0

D4

D5

D6

DGND

DDDVDDDVDD

D7

DV

DGND

DD

AV

RESETB

Data Sheet S14452EJ1V0DS00

DD

FIL0

XI

AV

FIL1

AGND

AGND

XO

DD

AV

AGND

3

PIN NAME

AGND : Analog GND

DD

AV

CMC : Configuration Manager Capable

CPS : Cable Power Status

CTL0 : Link Interface Control (bit 0)

CTL1 : Link Interface Control (bit 1)

D0-D7 : Data Input/Output

DGND : Digital GND

Direct : PHY/Link Isolation Barrier Control Input

DD

DV

FIL0 : APLL Filter Ground

FIL1 : APLL Filter

IC(H) : Internally Connected (High Clamped)

LKON : Link-on Signal Output

LPS : Link Power Status Input

LREQ : Link Request Input

PC0-PC2 : Power Class Set Input

PORTDIS : Port Disable

PSEL : Support Number of Port Select

RESETB : Power on Reset Input

RI0 : Reference Power Set, Connect Resistor 0

RI1 : Reference Power Set, Connect Resistor 1

SCLK : Link Control Output Clock

SUS/RES : Suspend/Resume Function Select

TpA0n : First Port Twisted Pair Cable A Negative Phase I/O

TpA0p : First Port Twisted Pair Cable A Positive Phase I/O

TpA1n : Second Port Twisted Pair Cable A Negative Phase I/O

TpA1p : Second Port Twisted Pair Cable A Positive Phase I/O

TpA2n : Third Port Twisted Pair Cable A Negative Phase I/O

TpA2p : Third Port Twisted Pair Cable A Positive Phase I/O

TpB0n : First Port Twisted Pair Cable B Negative Phase I/O

TpB0p : First Port Twisted Pair Cable B Positive Phase I/O

TpB1n : Second Port Twisted Pair Cable B Negative Phase I/O

TpB1p : Second Port Twisted Pair Cable B Positive Phase I/O

TpB2n : Third Port Twisted Pair Cable B Negative Phase I/O

TpB2p : Third Port Twisted Pair Cable B Positive Phase I/O

TpBias0 : First port Twisted Pair Output

TpBias1 : Second Port Twisted Pair Output

TpBias2 : Third Port Twisted Pair Output

XI : Crystal Oscillator Connection XI

XO : Crystal Oscillator Connection XO

: Analog Power

: Digital V

DD

µµµµ

PD72850A

4

Data Sheet S14452EJ1V0DS00

µµµµ

PD72850A

CONTENTS

1. PIN FUNCTIONS.....................................................................................................................................7

1.1 Cable Interface Pins.........................................................................................................................7

1.2 Link Interface Pins...........................................................................................................................8

1.3 Control Pins......................................................................................................................................8

1.4 IC........................................................................................................................................................9

1.5 Power Supply Pins...........................................................................................................................9

1.6 Other Pins.........................................................................................................................................9

2. PHY REGISTERS...................................................................................................................................10

2.1 Complete Structure for PHY Registers........................................................................................10

2.2 Port Status Page (Page 000) .........................................................................................................13

2.3 Vendor ID Page (Page 001) ...........................................................................................................14

3. INTERNAL FUNCTION ..........................................................................................................................15

3.1 Link Interface..................................................................................................................................15

3.1.1 Connection Method....................................................................................................... ........................ 15

3.1.2 LPS (Link Power Status).......................................................................................................................15

3.1.3 LREQ, CTL0,CTL1, and D0-D7 Pins....................................................................................................15

3.1.4 SCLK.....................................................................................................................................................15

3.1.5 LKON....................................................................................................................................................16

3.1.6 Direct ....................................................................................................................................................16

3.1.7 Isolation Barrier..................................................................................................................................... 16

3.2 Cable Interface ...............................................................................................................................18

3.2.1 Connections..........................................................................................................................................18

3.2.2 Cable Interface Circuit .......................................................................................................................... 19

3.2.3 Unused Ports........................................................................................................................................19

3.2.4 CPS.......................................................................................................................................................19

3.3 Suspend/Resume...........................................................................................................................19

3.3.1 Suspend/Resume On Mode (SUS/RES = “H”)......................................................................................19

3.3.2 Suspend/Resume Off Mode (SUS/RES = “L”)...................................................................................... 19

3.4 PLL and Crystal Oscillation Circuit..............................................................................................20

3.4.1 Crystal Oscillation Circuit......................................................................................................................20

3.4.2 PLL .......................................................................................................................................................20

3.5 PC0-PC2, CMC................................................................................................................................20

3.6 RESETB...........................................................................................................................................20

3.7 RI1, RI0............................................................................................................................................20

4. PHY/LINK INTERFACE..........................................................................................................................21

4.1 Initialization of Link Power Status (LPS) and PHY/Link Interface.............................................21

4.2 Link-on Indication..........................................................................................................................22

4.3 PHY/Link Interface Operation (CTL0, CTL1, LREQ, D0-D7) .......................................................23

4.3.1 CTL0,CTL1 ...........................................................................................................................................23

4.3.2 LREQ....................................................................................................................................................23

4.3.3 PHY/Link Interface Timing....................................................................................................................27

4.4 Acceleration Control......................................................................................................................28

4.5 Transmit Status..............................................................................................................................29

Data Sheet S14452EJ1V0DS00

5

µµµµ

PD72850A

4.6 Transmit..........................................................................................................................................30

4.7 Cancel .............................................................................................................................................31

4.8 Receive............................................................................................................................................32

5. CABLE PHY PACKET............................................................................................................................33

5.1 Self_ID Packet ................................................................................................................................33

5.2 Link-on Packet ...............................................................................................................................34

5.3 PHY Configuration Packet ............................................................................................................34

5.4 Extended PHY Packet....................................................................................................................34

5.4.1 Ping Packet........................................................................................................................................... 35

5.4.2 Remote Access Packet.........................................................................................................................35

5.4.3 Remote Reply Packet...........................................................................................................................36

5.4.4 Remote Command Packet....................................................................................................................36

5.4.5 Remote Confirmation Packet................................................................................................................ 37

5.4.6 Resume Packet.....................................................................................................................................37

6. ELECTRICAL SPECIFICATIONS..........................................................................................................38

7. APPLICATION CIRCUIT EXAMPLE......................................................................................................43

7.1 IEEE1394 Interface.........................................................................................................................43

7.2 NEC/FFM Board Sharing...............................................................................................................44

8. PACKAGE DRAWING............................................................................................................................45

9. RECOMMENDED SOLDERING CONDITIONS...................................................................................46

6

Data Sheet S14452EJ1V0DS00

1. PIN FUNCTIONS

1.1 Cable Interface Pins

Name Pin No. I/O Function

TpA0p 60 I / O First port twisted pair cable A positive phase I/ O

TpA0n 59 I / O First port twisted pair cable A negative phase I/O

TpB0p 58 I / O First port twisted pair cable B positive phase I/ O

TpB0n 57 I / O First port twisted pair cable B negative phase I/O

TpA1p 56 I / O Second port twisted pair cabl e A positive phase I/O

TpA1n 55 I / O Second port twisted pair cabl e A negative phase I/O

TpB1p 54 I / O Second port twisted pair cabl e B positive phase I/O

TpB1n 53 I / O Second port twisted pair cabl e B negative phase I/O

TpA2p 52 I / O Third port twisted pair cable A positive phase I/O

TpA2n 51 I / O Third port twisted pair cable A negative phase I/O

TpB2p 50 I / O Third port twisted pair cable B positive phase I/O

TpB2n 49 I / O Third port twisted pair cable B negative phase I/O

PORTDIS 64 I Port disable.

SUS/RES(71pin)=“1”

This selected state will be loaded to Disabled bit which allocated PHY register

Port Status Page when power-on reset.

The PORTDIS pin is ignored except power-on reset.

1: All 3 ports will be disabled.

0: All 3 ports will be enabled.

µµµµ

PD72850A

SUS/RES(71pin)=“0”

Combination with PSEL(66pin) input the supported number of port will be

selected.

Please refer to PSEL.

PSEL 66 I

SUS/RES 71 I Suspend/Resume function select

CPS 43 I Power cable status.

Supported number of Port select (This function will be activated only under

SUS/RES=“0”).

64pin 66pin

1Port(Port0) 0 1

2Port(Port0,1) 1 0

3Port(Port0-2) 0 0

When SUS/RES=“1”, this pi n s houl d be connected to AGND.

1: Suspend/Resume on (P1394a draft 2.1 compliant)

0: Suspend/Resume off (P 1394a draft 1.3 compliant)

Connect to the cable through a 390 kΩ resistor.

0: Cable power fail

1: Cable power on

Data Sheet S14452EJ1V0DS00

7

1.2 Link Interface Pins

Name Pin No. I/O Function

D0 15 I/O Data input/output (bit 0)

D1 16 I/O Data input/output (bit 1)

D2 18 I/O Data input/output (bit 2)

D3 19 I/O Data input/output (bit 3)

D4 21 I/O Data input/output (bit 4)

D5 22 I/O Data input/output (bit 5)

D6 24 I/O Data input/output (bit 6)

D7 25 I/O Data input/output (bit 7)

CTL0 12 I/O Link interface control (bit 0)

CTL1 13 I/O Llink interface control (bit 1)

LREQ 6 I Link request input

SCLK 9 O Link control output clock

LPS 1: 49.152 MHz output

LPS 0: Clamp to 0 (The clock si gnal will be out put within 25

to “0”)

LPS 5 I Link power status input

0: Link power off

1: Link power on (PHY/Link direct connection)

Clock signal of about 300 kHz (if isolation)

LKON 78 O Link-on signal output pin

Link-on signal is 6.144 MHz c l ock output.

Please refer to

Direct 77 I PHY/Link isolation barrier control input

0: Isolation barrier

1: PHY/Link direct connection

4.2 Link-on Indication

µµµµ

PD72850A

µ

sec after change

.

1.3 Control Pins

Name Pin No. I/O Function

PC0 2 I

PC1 1 I

PC2 79 I

CMC 3 I Configuration manager capable setting.

RESETB 30 I Power on reset input.

8

Power class set input

This pin status will be loaded to Pwr_class bit which allocated to PHY register 4H.

IEEE1394-1995 chapter [4.3. 4.1]

This pin status will be loaded to Contender bit which allocated to PHY register 4H.

0: Non contender

1: Contender

µ

Connect to DGND through a 0.1

0: Reset

1: Normal

Data Sheet S14452EJ1V0DS00

F capacitor.

1.4 IC

Name Pin No. I/O Function

IC 75, 76 I Internally Connected (High Clamped)

1.5 Power Supply Pins

Name Pin No. I/O Function

DD

AV

AGND

DD

DV

DGND

31, 36 - Analog power 1 (APLL, OSC)

40, 45 - Analog power 2 (Bias)

63, 67, 73 - Analog power 3 (Cable Interface)

32, 33 - Analog GND1 (PLL, OSC)

39, 44 - Analog GND2 (Bias)

61 - Analog GND3 (Common)

62 - Analog GND4 (Speed signal)

65, 68-70, 72

7, 10, 14,

26-28, 80

4, 8, 11, 17,

20, 23, 29, 74

- Analog GND5 (Port)

- Digital V

- Digital GND

DD

µµµµ

PD72850A

1.6 Other Pins

Name Pin No. I/O Function

TpBias0 48 O First port twisted pair output

TpBias1 47 O Second port twisted pair output

TpBias2 46 O Third port twisted pair output

RI0 41 - Resistor connection pi n0 f or reference current generator.

Please connect to RI1 pi n via 9.1 kΩ resistor.

RI1 42 - Resistor connection pi n1 f or reference current generator.

Please connect to RI0 pi n via 9.1 kΩ resistor.

FIL1 34 - APLL filter (No need to assemble)

FIL0 35 - APLL filter ground (No need to assemble)

XI 37 - Crystal oscillator connection X I

XO 38 - Crystal oscillator connection X O

Data Sheet S14452EJ1V0DS00

9

µµµµ

PD72850A

2. PHY REGISTERS

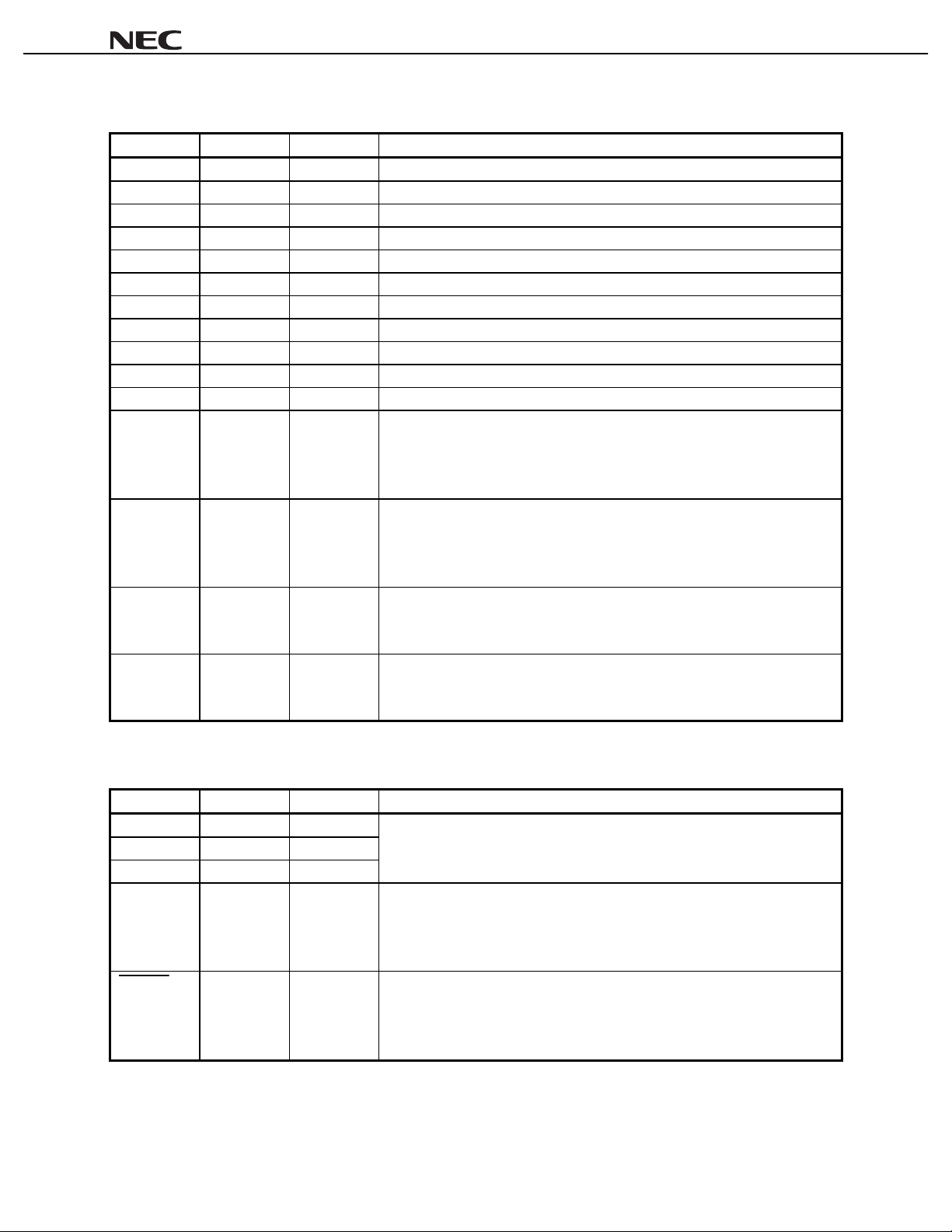

2.1 Complete Structure for PHY Registers

Figure 2-1. Complete Structure of PHY Registers

01234567

0000 Physical_ID R PS

0001 RHB IBR Gap_count

0010 Extended (7) Reserved Total_ports

0011 Max_speed Reserved Delay

0100 Link_active Contender Jitter Pwr_class

0101

0110 Reserved

0111 Page_select Reserved Port_s el ect

1000 Register0 (page_select)

1001 Register1 (page_select)

1010 Register2 (page_select)

1011 Register3 (page_select)

1100 Register4 (page_select)

1101 Register5 (page_select)

1110 Register6 (page_select)

1111 Register7 (page_select)

Resume_int

ISBR Loop Pwr_fail Timeout Port_event Enab_accel Enab_multi

10

Data Sheet S14452EJ1V0DS00

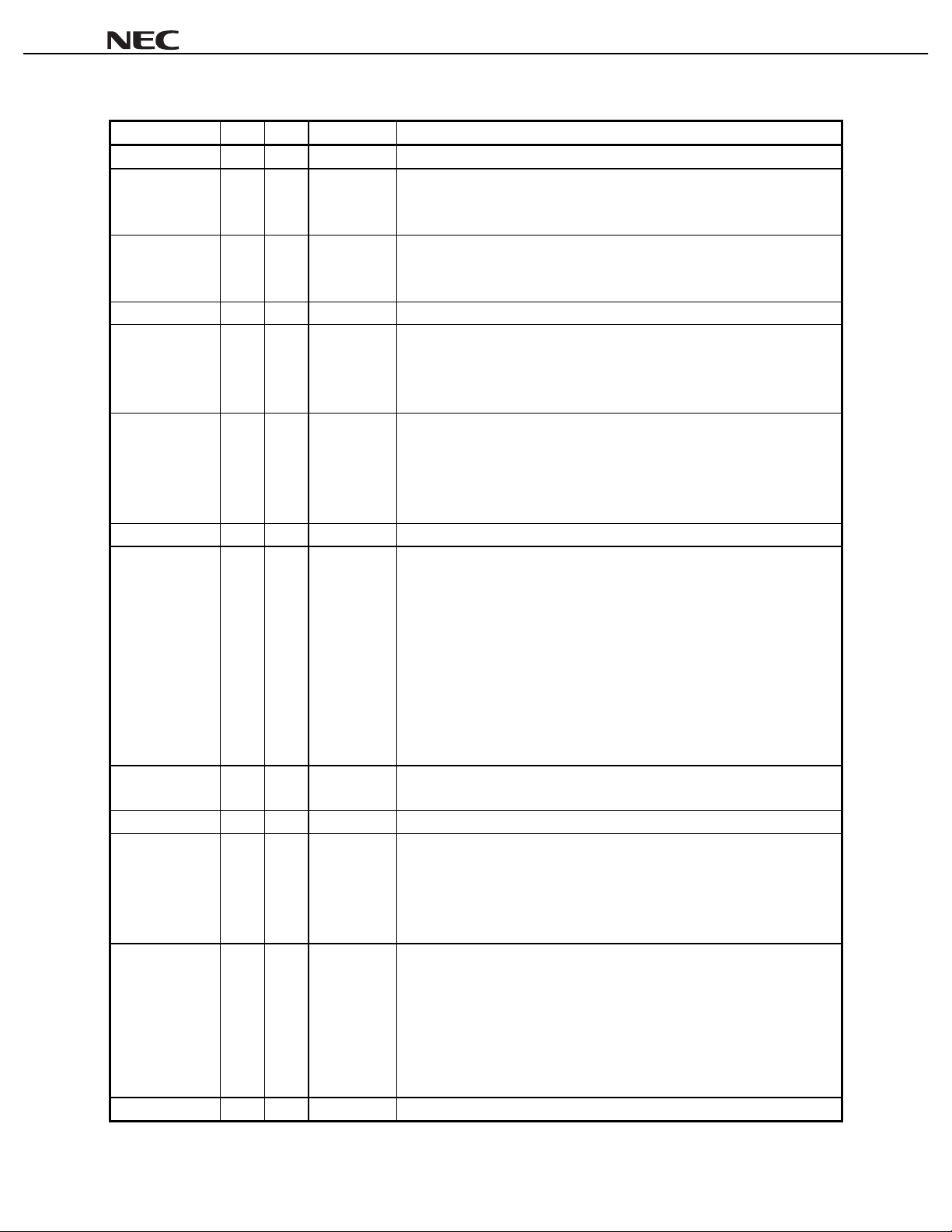

Table 2-1. Bit Field Description (1/2)

Field Size R/W Reset value Description

Physical_ID 6 R 000000 Physical_ID value selected from Self_ID peri od.

R 1 R 0 If this bit is 1, the node is root.

1: Root

0: Not root

PS 1 R Cable power status.

1: Cable power on

0: Cable power off

RHB 1 R/W 0 Root Hold -off bit. If 1, becomes root at the bus reset.

IBR 1 R/W 0 Initiate bus reset.

Setting to 1 begins a long bus reset.

µ

Long bus reset signal duration: 166

Returns to 0 at the beginning of bus reset.

Gap_count 6 R/W 111111 Gap count value.

It is updated by the changes of transmitting and recei ving the PHY

configuration packet Tx/ Rx .

The value is maintained aft er f i rst bus reset.

After the second bus res et i t returns to reset value.

Extended 3 R 111 Shows the extended register map.

Total_ports 4 R 0011 Supported port number.

When SUS/RES(71pin)=“1”

0011 : 3 ports

sec.

µµµµ

PD72850A

When SUS/RES(71pin)=“0”

Combination with PSEL(66pin) input the supported number of port will be

selected. Please ref er t o

0001 : 1 port

0010 : 2 port

0011 : 3 port

Max_speed 3 R 010 Indicate the max i m um speed that this node supports.

010: 98.304, 196.608 and 393.216 Mbps

Delay 4 R 0010 Indicate worst case repeating delay time. 144+(2 x 20)=184 nsec

Link_active 1 R/W 1 Link active.

1 : Enable

0 : Disable

The logical AND status of this bit and LPS pin.

State will be referred to “L bit” of Self-ID Packet#0.

Contender 1 R/W See

Description

Jitter 3 R 010 The difference of repeating time (Max.-Min.). (2+1) x 20=60 nsec

Contender.

“1” indicate this node support bus manager func t i on. This bit will be referred

to “C bit” of Self-ID Packet#0.

The reset data is depending on CMC pin set ting.

CMC pin condition

1: Pull up (Contender)

0: Pull down (Non Contender)

1.1 Cable Interface Pins

.

Data Sheet S14452EJ1V0DS00

11

µµµµ

PD72850A

Table 2-1. Bit Field Description (2/2)

Field Size R/W Reset value Description

Pwr_class 3 R/W See

Description

Resume_int 1 R/W 0 Resume interrupt enable. When s et to 1, if any one port does resume, the

ISBR 1 R/W 0 Initiate short (arbitrated) bus reset.

Loop 1 R/W 0 Loop detection output.

Pwr_fail 1 R/W 0 Power cable disconnect detect.

Timeout 1 R/W 0 Arbitration state machine time-out.

Port_event 1 R/W 0 Set to 1 when the Int _E nabl e bi t in the register map of each port i s 1 and

Enab_accel 1 R/W 0 Enables arbitration acceleration.

Enab_multi 1 R/W 0 Enable multi-speed packet concatenation.

Page_select 3 R/W 000 Select page address between 1000 to 1111.

Port_select 4 R/W 0000 Port Selection.

Reserved - R 000… Reserved. Read as 0.

Power class.

Please refer to IEEE 1394 -1995 [ 4.3.4.1].

This bit will be referred to Pwr field of Self-ID Packet#0.

The reset data will be determined by PC0-PC2 Pin st atus.

Port_event bit becomes 1.

Setting to 1 acquires t he bus and begi ns short bus reset.

µ

Short bus reset signal out put : 1.3

Returns to 0 at the beginning of t he bus reset.

1: Detection

Writing 1 to this bit c l ears it to 0.

Writing 0 has no effect.

It becomes 1 when there is a c hange from 1 to 0 in the CPS bit.

Writing 1 to this bit c l ears it to 0.

Writing 0 has no effect.

Writing 1 to this bit c l ears it to 0.

Writing 0 has no effect.

there is a change in the ports c onnected, Bias, Disabled and Faul t bits.

Set to 1 when the Resume_int bit is 1 and any one port does resume.

Writing 1 to this bit c l ears it to 0.

Writing 0 has no effect.

Ack-acceleration and Fly-by arbitration are enabled.

1: Enabled

0: Disabled

If this bit changes whi l e the bus request is pending, the operat i on i s not

guaranteed.

Setting this bit t o 1 follows multi-speed trans m i ssion.

When this bit is set to 0,the pack et will be transmitted with the same speed

as the first packet.

000: Port Status Page

001: Vendor Definition Page

Others: Unused

Selecting 000 (Port Status Page) with the page select i on s el ects the port.

0000: Port 0

0001: Port 1

0010: Port 2

Others: Unused

sec

12

Data Sheet S14452EJ1V0DS00

µµµµ

PD72850A

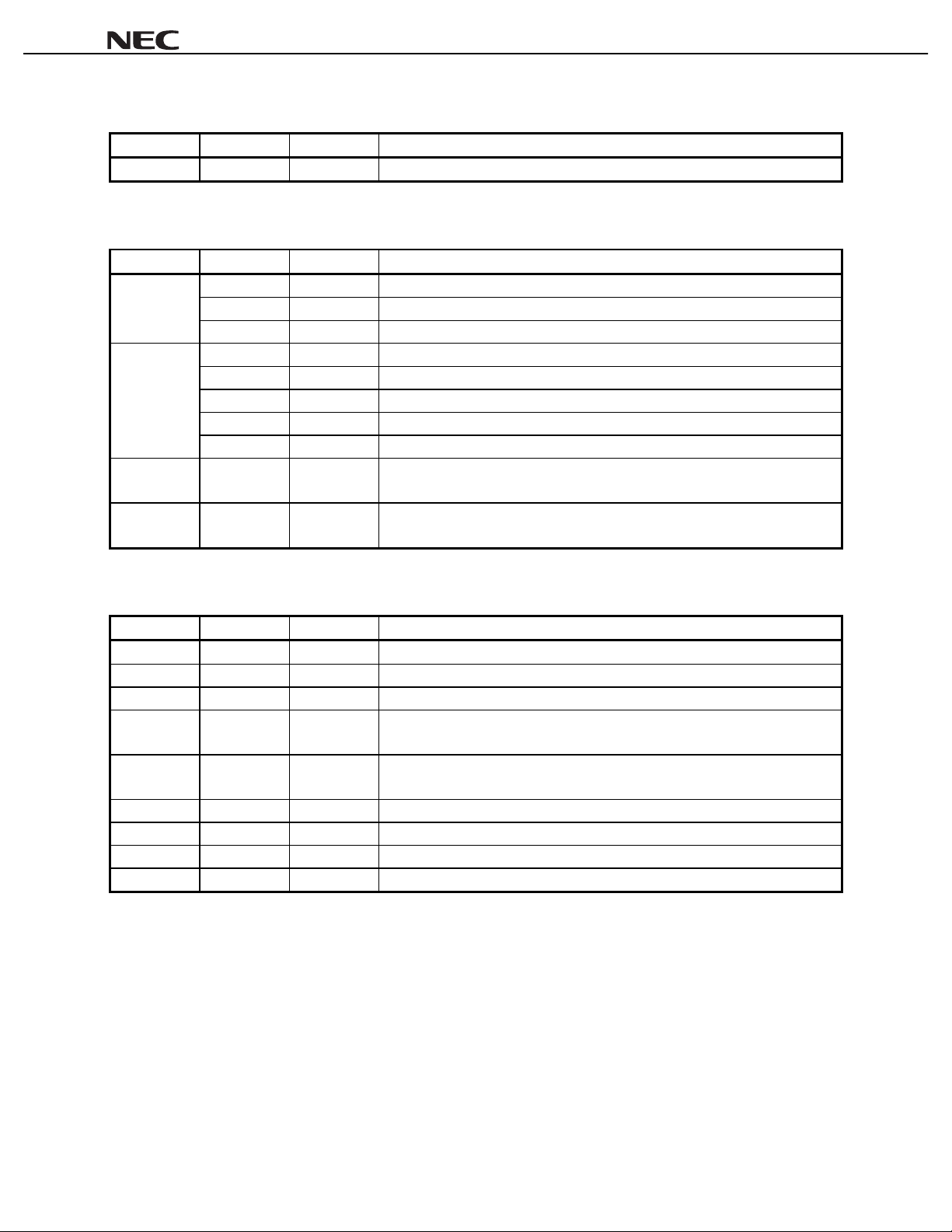

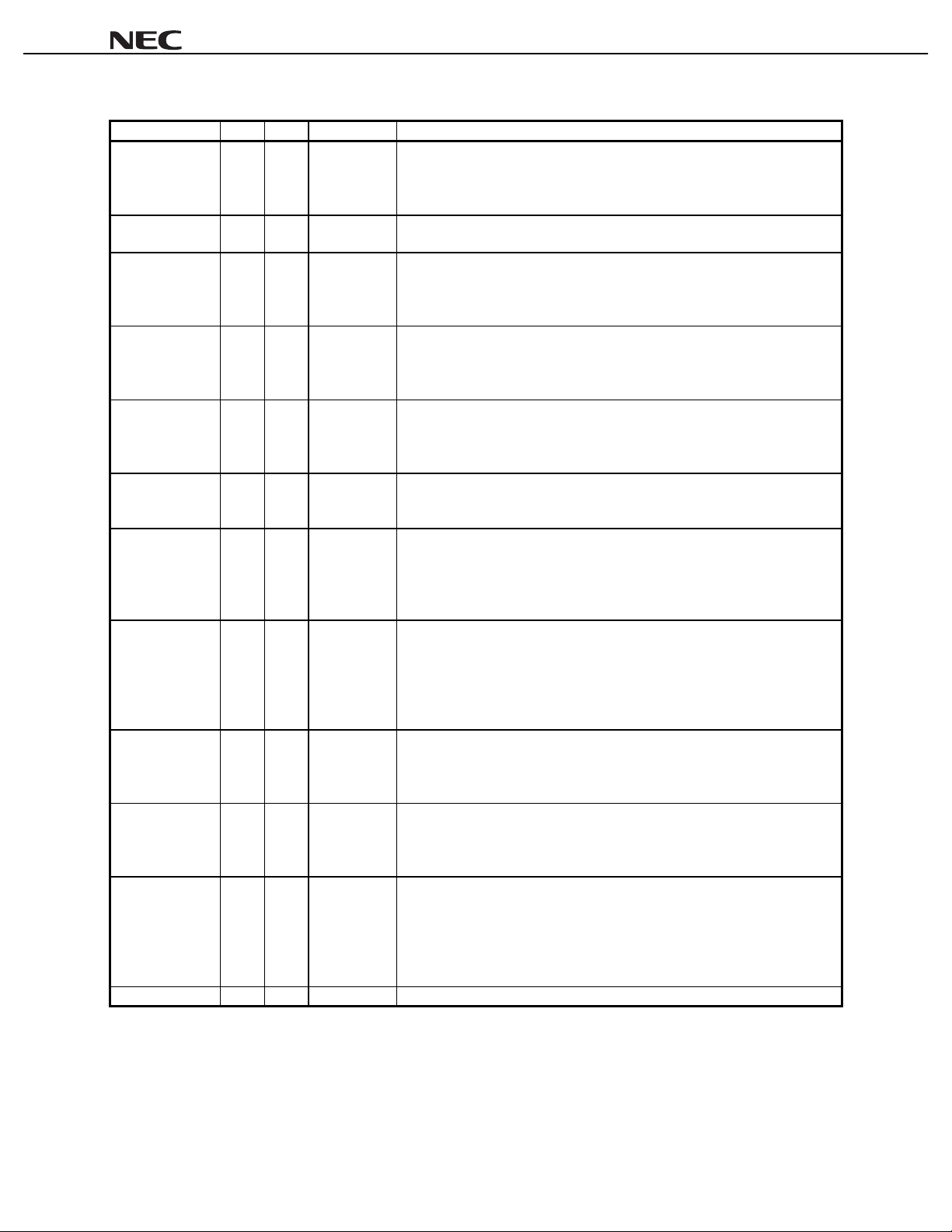

2.2 Port Status Page (Page 000)

Figure 2-2. Port Status Page

01234567

1000 AStat BStat Child Connected Bias Disabled

1001 Negotiated_speed Int_enable Fault Reserved

1010 Reserved

1011 Reserved

1100 Reserved

1101 Reserved

1110 Reserved

1111 Reserved

Table 2-2. Bit Field Description

Field Size R/W Reset value Description

AStat 2 R XX A port status value.

00:---, 10: “0”

01: “1”, 11: “Z”

BStat 2 R XX B port status value.

00:---, 10: “0”

01: “1”, 11: “Z”

Child 1 R Child node status value.

1: Connected to child node

0: Connected to parent node

Connected 1 R 0 Connection status value.

1: Connected

0: Disconnected

Bias 1 R Bias voltage s tatus value.

1: Bias voltage

0: No bias voltage

Disabled 1 R/W See

Description

Negotiated_

Speed

Int_enable 1 R/W 0 The Port_event is set to 1 by a change to 1 of the Connected, Bias , Disable,

Fault 1 R/W 0 Set to 1 if an error occurs during Suspend/Resume.

Reserved - R 000… Reserved. Read as 0.

3 R Shows the maximum data trans fer rate of the node connected to thi s port.

The reset value is set by the PORTDIS pin.

1: Disable

000: 100 Mbps

001: 200 Mbps

010: 400 Mbps

and Fault bits.

Writing 1 to this bit c l ears it to 0.

Writing 0 has no effect.

Data Sheet S14452EJ1V0DS00

13

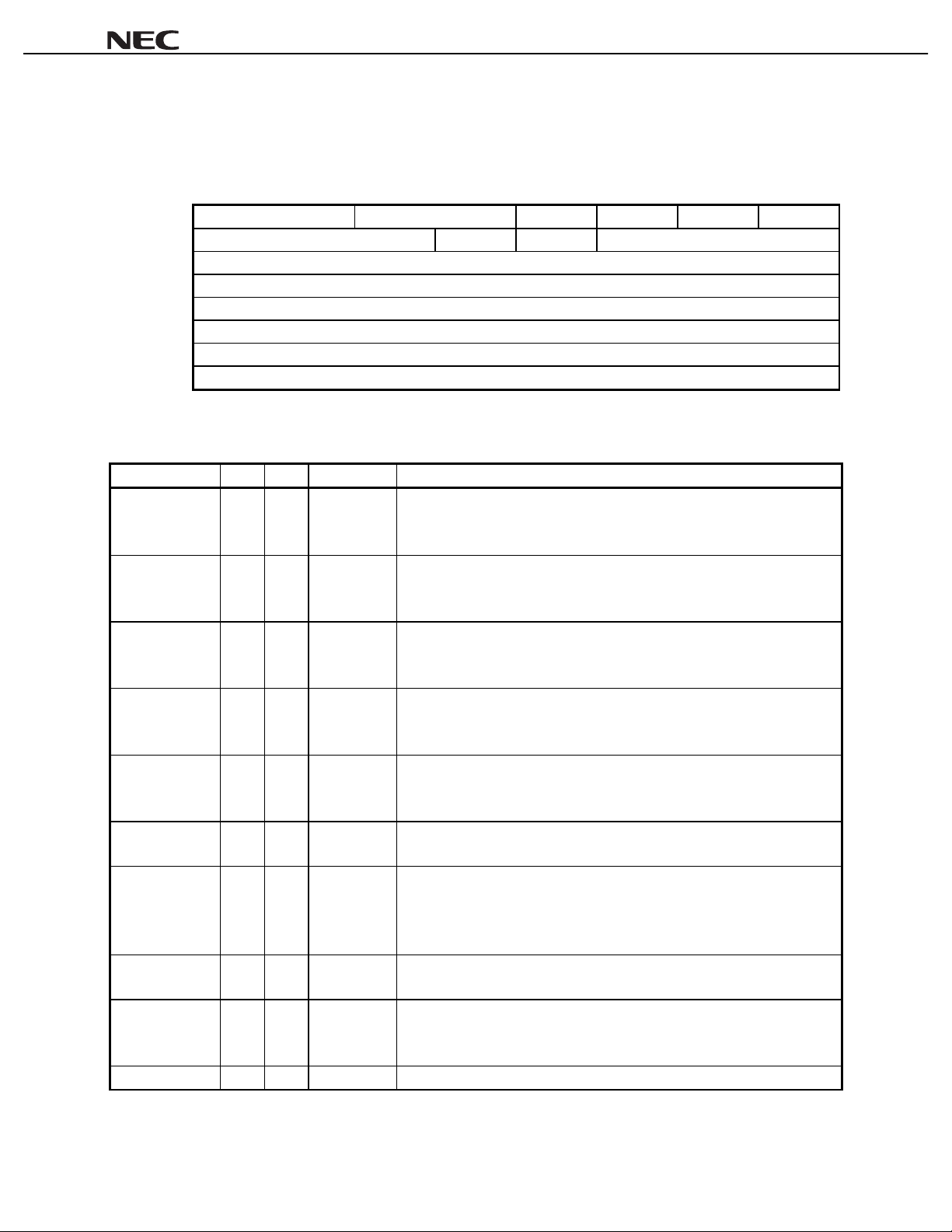

2.3 Vendor ID Page (Page 001)

Figure 2-3. Vendor ID Page

01234567

1000 Compliance_level

1001 Reserved

1010

1011

1100

1101

1110

1111

Table 2-3. Bit Field Description

Field Size R/W Reset value Description

Compliance_level 8 R 00000001 According to IEEE P1394a.

Vendor_ID 24 R 00004CH Company ID Code value, NEC IEEE OUI .

Product_ID 24 R Product code.

Reserved - R 000… Reserved. Read as 0.

Vendor_ID

Product_ID

µµµµ

PD72850A

14

Data Sheet S14452EJ1V0DS00

3. INTERNAL FUNCTION

3.1 Link Interface

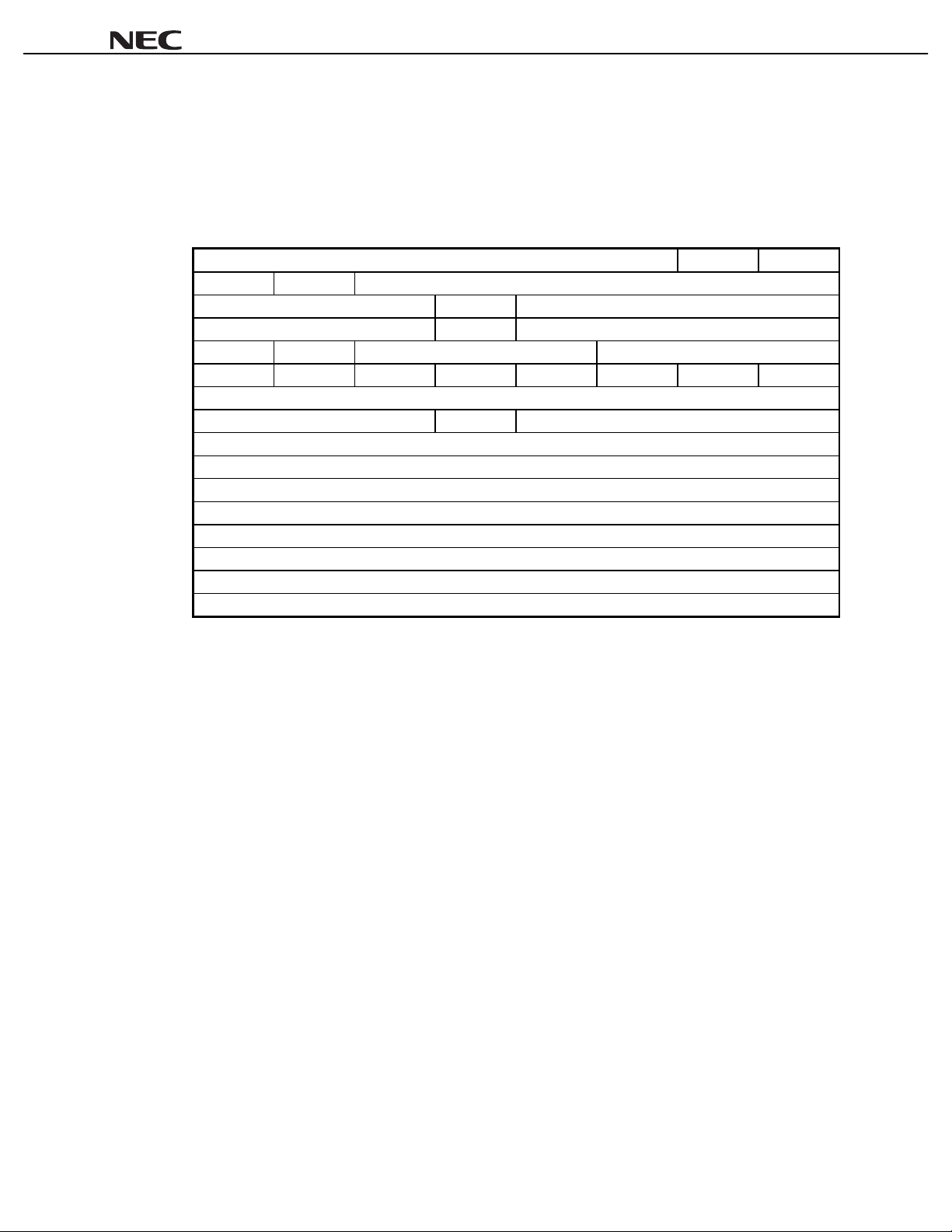

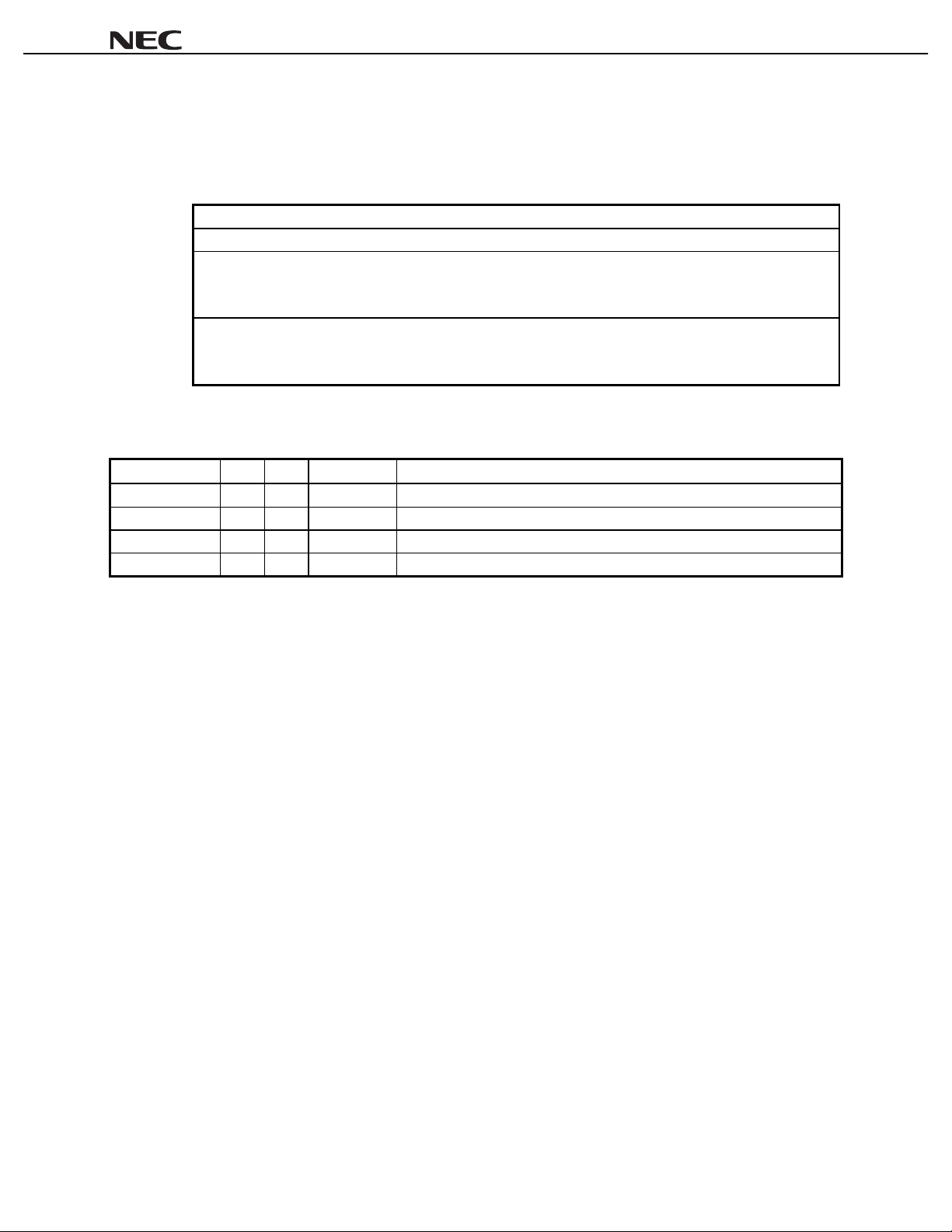

3.1.1 Connection Method

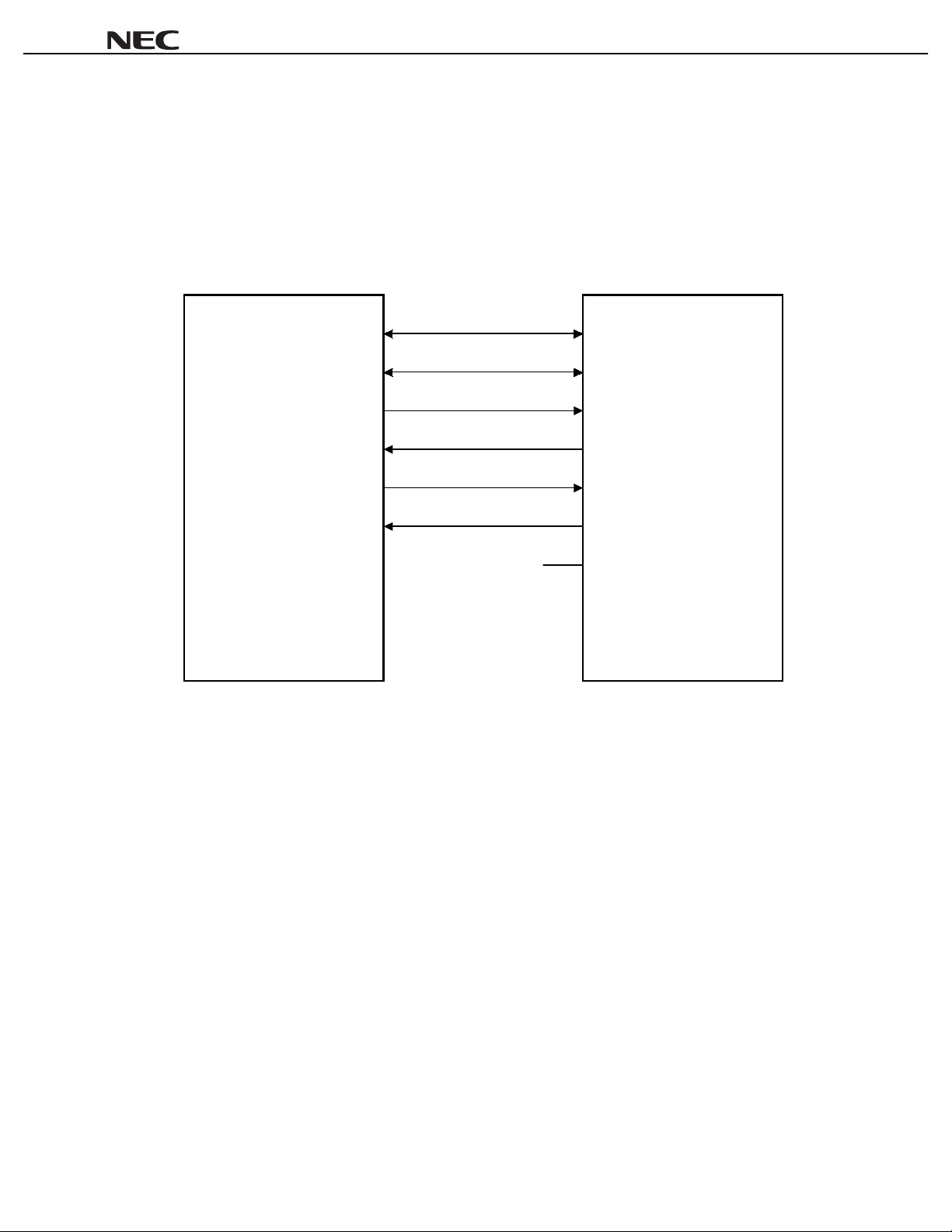

Figure 3-1. PHY/Link Connection Method

D0-D7

CTL0,CTL1

LREQ

SCLK

µµµµ

PD72850A

Link

Note

Clamping to VDD provides direct connection to Link.

Clamping to GND connects through isolation barrier to Link.

The isolation barrier connection circuit is described in

3.1.2 LPS (Link Power Status)

LPS is a function to monitor the On/Off status of the Link power supply. After 1.2

PHY/Link is reset and D and CTL are output Low (when the isolation barrier is Hi-Z). After 2.5 µsec or more, LPS is

Low, moreover, the PHY stops the supply of SCLK and SCLK outputs Low (when the isolation barrier is Hi-Z).

3.1.3 LREQ, CTL0,CTL1, and D0-D7 Pins

LREQ : Indicates that a request is received from Link.

CTL0,CTL1 : Bi-directional pin which controls the functions between the PHY/Link interface.

D0-D7 : Bi-directional pin which controls the data Transfer/Receive status signal, and the speed code

Transfer/Receive status signal.

LPS

LKON

DIRECT

Note

3.1.7 Isolation Barrier.

PHY

µ

PD72850A

sec or more, LPS is Low, the

µ

3.1.4 SCLK

49.152 MHz clock supplied by PHY for the PHY/Link interface synchronization.

Data Sheet S14452EJ1V0DS00

15

Loading...

Loading...