Page 1

©

用户手册

78K0/KE2

8 位单片微控制器

μ

PD78F0531

μ

PD78F0531(A)

μ

PD78F0531(A2)

μ

PD78F0532

μ

PD78F0533

μ

PD78F0534

μ

PD78F0535

μ

PD78F0536

μ

PD78F0537

μ

PD78F0537D

μ

PD78F0537D 具有片上调试功能。

大规模生产时不要使用本产品,因为在使用片上调试功能后,从闪存可重写的次数受到限制这一点来看,它的可靠性不能保

证。NEC Electronics 不接受对于本产品的任何投诉。

文档编号:U17260CA6V0UD00(第六版)

发行日期:2007 年 9 月 N CP(K)

NEC Electronics China 2004

日本印制

μ

PD78F0532(A)

μ

PD78F0533(A)

μ

PD78F0534(A)

μ

PD78F0535(A)

μ

PD78F0536(A)

μ

PD78F0537(A)

μ

PD78F0532(A2)

μ

PD78F0533(A2)

μ

PD78F0534(A2)

μ

PD78F0535(A2)

μ

PD78F0536(A2)

μ

PD78F0537(A2)

Page 2

[备忘录]

用户手册 U17260CA6V0UD

2

Page 3

CMOS设备的注释

① 输入引脚处的电压波形

输入噪音或一个反射波引起的波形失真可能导致错误发生。如果由于噪音等的影响使CMOS设备的输

入电压范围保持在V

从V

(MAX)过渡到VIH (MIN)时的传输期间,要防止散射噪声影响设备。

IL

② 未使用的输入引脚的处理

CMOS设备的输入端保持开路可能导致误操作。如果一个输入引脚未被连接,则由于噪音等原因可能

会产生内部输入电平,从而导致误操作。CMOS设备的操作特性与Bipolar或NMOS设备不同。CMOS设备

的输入电平必须借助上拉或下拉电路固定在高电平或低电平。每一个未使用引脚都应该通过附加电阻连接

到VDD或GND。如果有可能尽量定义为输出引脚。对未使用引脚的处理因设备而异,必须遵循与设备相

关的规定和说明。

③ ESD防护措施

如果MOS设备周围有强电场,将会击穿氧化栅极,从而影响设备的运行。因此必须采取措施,尽可

能防止静电产生。一旦有静电,必须立即释放。对于环境必须有适当的控制。如果空气干燥,应当使用增

湿器。建议避免使用容易产生静电的绝缘体。半导体设备的存放和运输必须使用抗静电容器、抗静电屏蔽

袋或导电材料容器。所有的测试和测量工具包括工作台和工作面必须良好接地。操作员应当佩戴静电消除

手带以保证良好接地。不能用手直接接触半导体设备。对于装配有半导体设备的PW板也应采取类似的静

电防范措施。

④ 初始化之前的状态

在上电时MOS设备的初始状态是不确定的。在刚刚上电之后,具有复位功能的MOS设备并没有被初

始化。因此上电不能保证输出引脚的电平,I/O设置和寄存器的内容。设备在收到复位信号后才进行初始

化。具有复位功能的设备在上电后必须立即进行复位操作。

⑤ 电源开关顺序

在一个设备的内部操作和外部接口使用不同的电源的情况下,按照规定,应先在接通内部电源之后再

接通外部电源。当关闭电源时,按照规定,先关闭外部电源再关闭内部电源。如果电源开关顺序颠倒,可

能会导致设备的内部组件过电压,产生异常电流,从而引起内部组件的误操作和性能的退化。

对于每个设备电源的正确开关顺序必须依据设备的规范说明分别进行判断。

⑥ 电源关闭状态下的输入信号

不要向没有加电的设备输入信号或提供I/O上拉电源。因为输入信号或提供I/O上拉电源将引起电流注

入,从而引起设备的误操作,并产生异常电流,从而使内部组件退化。

每个设备电源关闭时的信号输入必须依据设备的规范说明分别进行判断。

(MAX)和VIH(MIN)之间,设备可能发生错误。在输入电平固定时以及输入电平

IL

用户手册 U17260CA6V0UD

3

Page 4

EEPROM 是 NEC 电子公司的注册商标.

Windows 和 Windows NT 是美国及其它国家微软公司的注册商标.

PC/AT 是 IBM 公司的注册商标.

HP9000 系列 700 和 HP-UX 是 HP 公司的注册商标.

SPARC 工作站是 SPARC 公司的注册商标.

Solaris 和 SunOS 是 Sun 公司的注册商标.

SuperFlash 是 Silicon Storage Technology,Inc(SST 超捷)的注册商标,在包括美国日本的多个国家注册.

用户手册 U17260CA6V0UD

4

Page 5

注意事项:该产品使用的 SuperFlash®技术获得了 Silicon Storage Technology, Inc.公司的授权。

本文档信息发布于 2007 年 7 月。将来可能未经预先通知而更改。在实际进行生产设计时,请参阅各

产品最新的数据表或数据手册等相关资料以获取本公司产品的最新规格。

并非所有的产品和/或型号都向每个国家供应。请向本公司销售代表查询产品供应及其他信息。

未经本公司事先书面许可,禁止复制或转载本文件中的内容。本文件所登载内容的错误,本公司概不

负责。

本公司对于因使用本文件中列明的本公司产品而引起的,对第三者的专利、版权以及其它知识产权的

侵权行为概不负责。本文件登载的内容不应视为本公司对本公司或其他人所有的专利、版权以及其它

知识产权作出任何明示或默示的许可及授权。

本文件中的电路、软件以及相关信息仅用以说明半导体产品的运作和应用实例。用户如在设备设计中

应用本文件中的电路、软件以及相关信息,应自行负责。对于用户或其他人因使用了上述电路、软件

以及相关信息而引起的任何损失,本公司概不负责。

虽然本公司致力于提高半导体产品的质量及可靠性,但用户应同意并知晓,我们仍然无法完全消除出

现产品缺陷的可能。为了最大限度地减少因本公司半导体产品故障而引起的对人身、财产造成损害

(包括死亡)的危险,用户务必在其设计中采用必要的安全措施,如冗余度、防火和防故障等安全设

计。

本公司产品质量分为:

“标准等级”、“专业等级”以及“特殊等级”三种质量等级。

“特殊等级”仅适用于为特定用途而根据用户指定的质量保证程序所开发的日电电子产品。另外,各种

日电电子产品的推荐用途取决于其质量等级,详见如下。用户在选用本公司的产品时,请事先确认产品

的质量等级。

“标准等级”: 计算机,办公自动化设备,通信设备,测试和测量设备,音频·视频设备,家电,加

工机械以及产业用机器人。

“专业等级”: 运输设备(汽车、火车、船舶等),交通用信号控制设备,防灾装置,防止犯罪装

置,各种安全装置以及医疗设备(不包括专门为维持生命而设计的设备)。

“特殊等级: 航空器械,宇航设备,海底中继设备,原子能控制系统,为了维持生命的医疗设备、

用于维持生命的装置或系统等。

除在本公司半导体产品的数据表或数据手册等资料中另有特别规定以外,本公司半导体产品的质量等级

均为“标准等级”。如果用户希望在本公司设计意图以外使用本公司半导体产品,务必事先与本公司销

售代表联系以确认本公司是否同意为该项应用提供支持。

(注)

(1) 本声明中的“本公司”是指日本电气电子株式会社(NEC Electronics Corporation)及其控股公司。

(2) 本声明中的“本公司产品”是指所有由日本电气电子株式会社或为日本电气电子株式会社(定义如上)

开发或制造的产品。

用户手册 U17260CA6V0UD

5

Page 6

引言

读者对象 本手册于适用那些希望了解 78K0/KE2 功能,并设计开发应用系统和程序的工程师。

目标产品如下。

μ

78K0/KE2:

<R>

目的 本手册用于帮助用户了解下面组件中描述的功能。

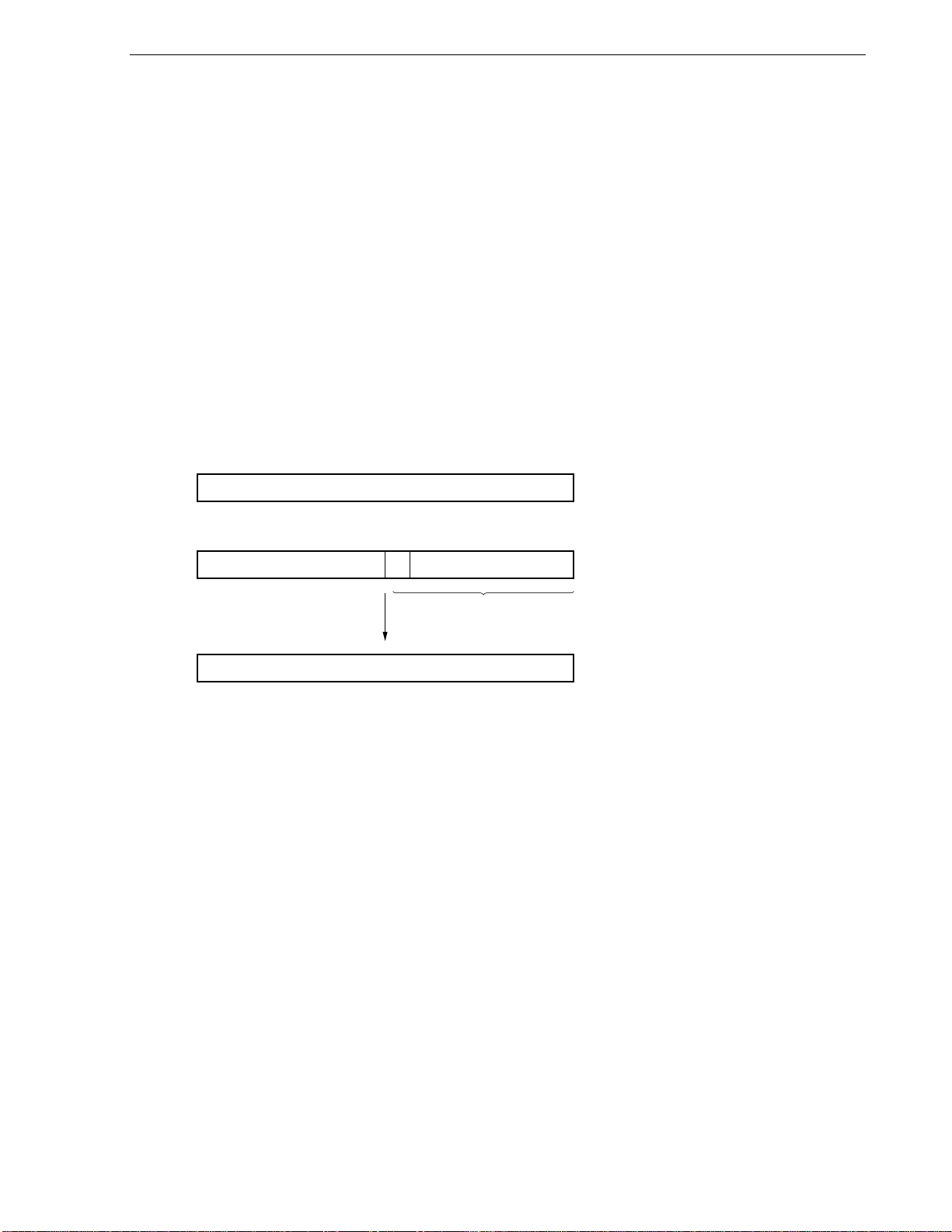

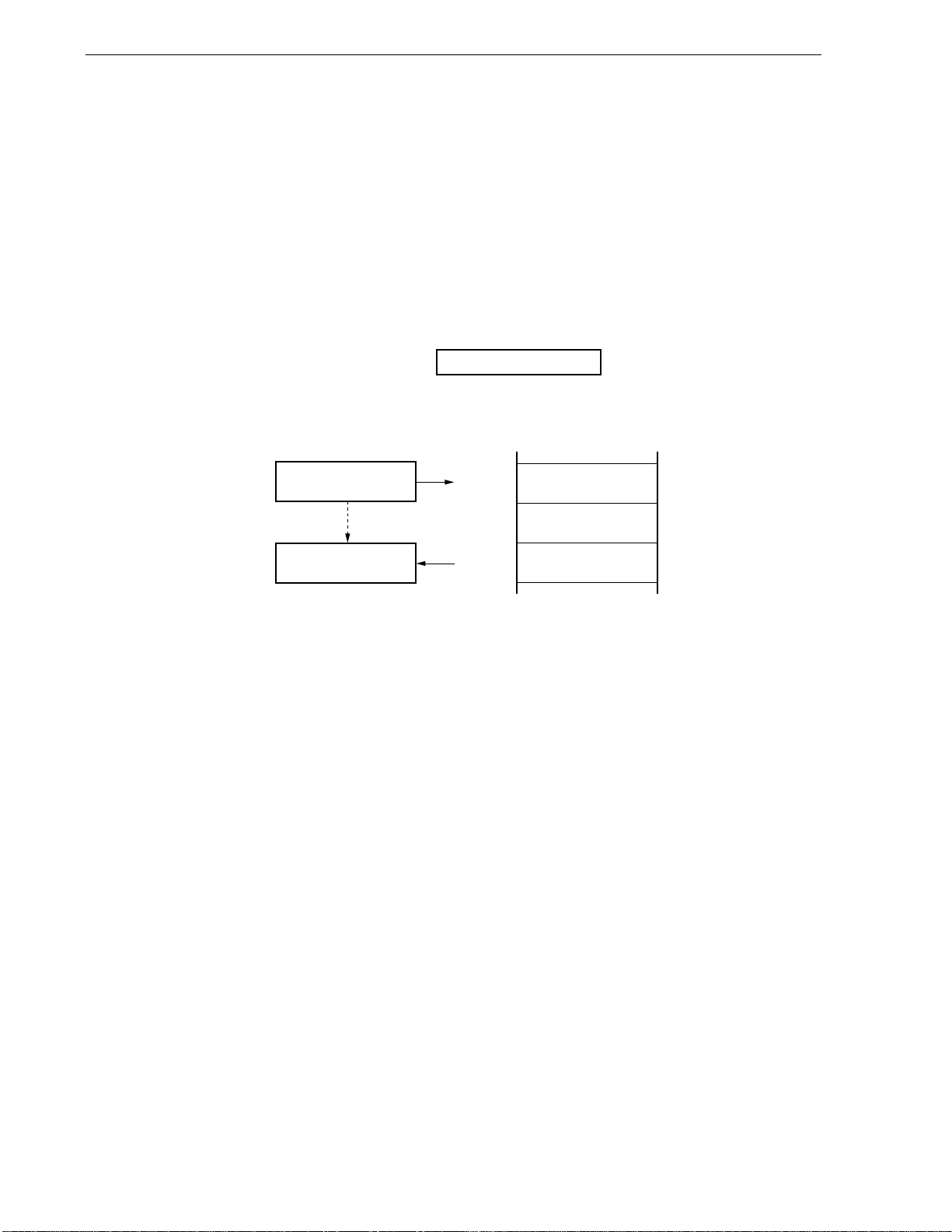

组件 78K0/KE2 手册主要分为两个部分:手册和指令(与 78K/0 系列通用)。

PD78F0531, 78F0532, 78F0533, 78F0534, 78F0535, 78F0536,

78F0537, 78F0537D, 78F0531(A), 78F0532(A), 78F0533(A),

78F0534(A), 78F0535(A), 78F0536(A), 78F0537(A), 78F0531

(A2), 78F0532(A2), 78F0533(A2), 78F0534(A2), 78F0535

(A2), 78F0536(A2), 78F0537(A2)

78K0/KE2

用户手册

(本手册)

78K/0 系列

用户手册

指令

• 引脚功能

• 内部模块功能

• 中断

• 其它内置外设功能

• 电气特性(目标系统)

手册使用方法 在阅读本手册前,读者应掌握电子工程、逻辑电路和微控制器等方面的一般知识。

<R>

• 当把该手册当作(A)和(A2)等级产品的手册使用时:

→ 在标准产品、(A)和(A2)级产品之间仅仅是品质等级不同。阅读如下的产品编

号。

•

μ

PD78F0531→ μPD78F0531(A), μPD78F0531(A2)

•

μ

PD78F0532→ μPD78F0532(A), μPD78F0532(A2)

• μPD78F0533→ μPD78F0533(A), μPD78F0533(A2)

•

μ

PD78F0534→ μPD78F0534(A), μPD78F0534(A2)

•

μ

PD78F0535→ μPD78F0535(A), μPD78F0535(A2)

•

μ

PD78F0536→ μPD78F0536(A), μPD78F0536(A2)

•

μ

PD78F0537→ μPD78F0537(A), μPD78F0537(A2)

• 如果读者要了解产品功能:

→ 请按目录顺序阅读本手册。标识 “<R>” 处是主要修改的地方。在 PDF 文件中可以

使用查找 “<R>” ,来很容易的找到修改的地方。

• CPU 功能

• 指令集

• 指令扩展

用户手册 U17260CA6V0UD

6

Page 7

• 如何解释寄存器格式:

→ 括号中的位名在 RA78K0 中被定义为保留字,并且在 CC78K0 中直接通过

# pragma sfr 定义为一个 sfr 变量。

• 如果读者知道寄存器名字并想验证这个寄存器的详细信息:

→ 可参阅附录 C 寄存器索引。

• 如果读者希望了解 78K/0 系列指令的详细信息:

→ 可参阅 78K/0 系列指令用户手册(U12326E)。

规定 数据规则: 数据的高位部分在左边,低位部分在右边

有效低电平表示法: ××× (在引脚和信号名称上划一条线)

注: 文中用注标注的相关术语的脚注

注意事项: 需要特别关注的信息

备注: 补充信息

数的表示法: 二进制

十进制

十六进制

...

×××× 或 ××××B

...

××××

...

××××H

相关文档 本手册中指出的相关文档可能包括了初级的版本,但未注明。

设备文档

<R>

文档名称 文档编号

78K0/KE2 用户手册 本手册

78K/0 系列指令用户手册

78K0/Kx2 Flash 存储器编程器(编程器) 应用说明

注

78K0/Kx2 Flash 存储器自编程用户手册

78K0/Kx2 EEPROMTM 仿真应用笔记

注

U12326E

U17739E

U17516E

U17517E

注 本手册是针对技术而做的说明。详细问题,请咨询 NEC 电子的销售代表。

开发工具相关文档 (软件)(用户手册)

文档名称 文档编号

RA78K0 Ver. 3.80 汇编包

CC78K0 Ver. 3.70 C 编译器

SM+ 系统仿真器

ID78K0-QB Ver. 2.90 集成调试器 操作

PM+ Ver. 5.20 U16934E

操作

语言

结构化汇编语言

操作

语言

操作

外部用户开放接口

U17199E

U17198E

U17197E

U17201E

U17200E

U17246E

U17247E

U17437E

注意事项 对以上列出的相关文档所做修改恕不另行通知,在设计时请使用每个文档的最新版本。

用户手册 U17260CA6V0UD

7

Page 8

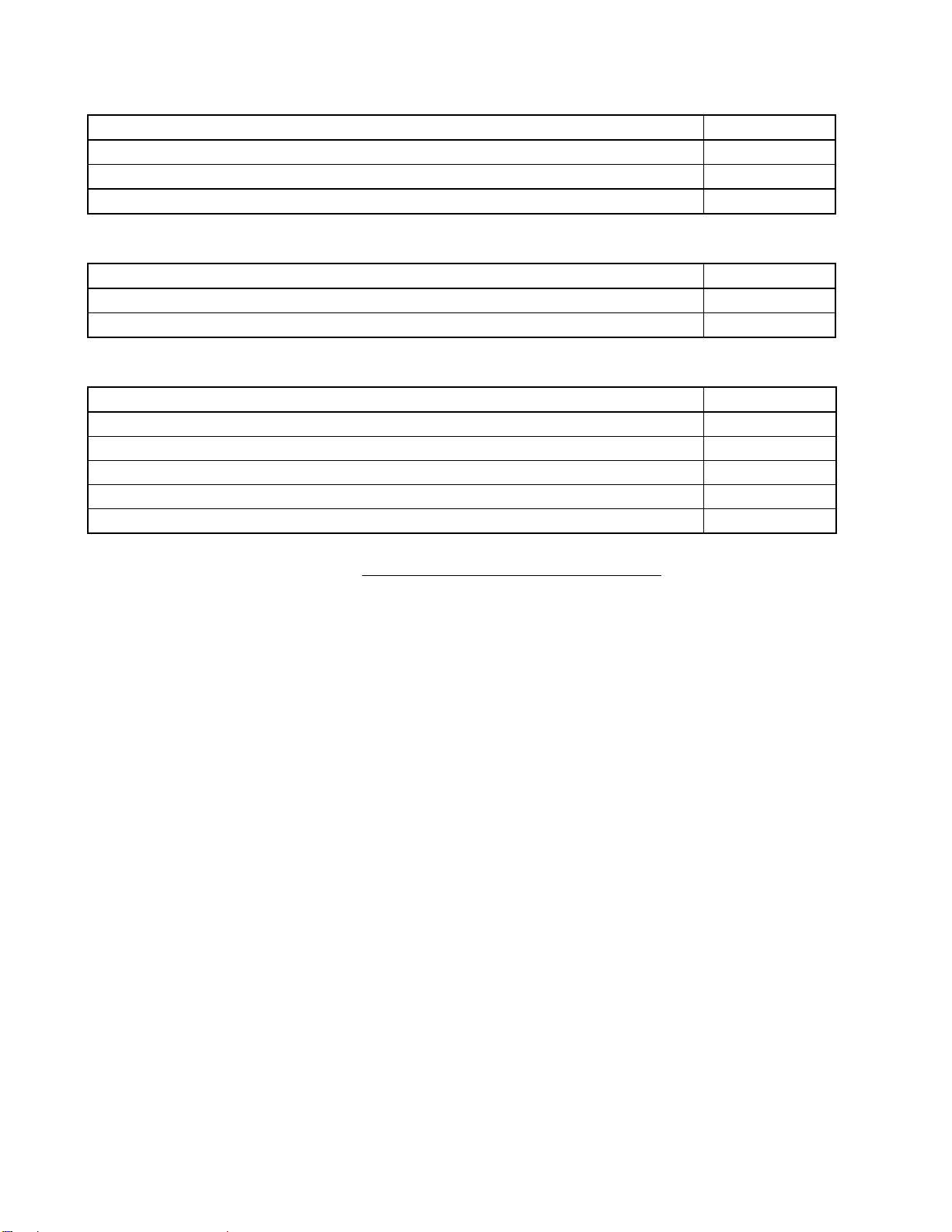

开发工具相关文档 (硬件)(用户手册)

文档名称 文档编号

QB-78K0KX2 在线仿真器

QB-78K0MINI 片上调试仿真器

具有编程功能的 QB-MINI2 片上调试仿真

<R>

与 Flash 存储器编程相关文档 (用户手册)

文档名称 文档编号

PG-FP4 Flash 存储器编程器

PG-FPL3 Flash 存储器编程器

其他文档

文档名称 文档编号

半导体选择指南-产品和封装-

半导体设备安装手册 注

NEC 半导体设备质量等级

NEC 半导体设备可靠性/质量控制系统

半导体设备防静电 ESD 保护指南

注 浏览“半导体设备安装手册”网站 (

http://www.necel.com/pkg/en/mount/index.html ).

注意事项 对以上列出的相关文档所做修改恕不另行通知,在设计时请使用每个文档的最新版本。

U17341E

U17029E

U18371E

U15260E

U17454E

X13769X

C11531E

C10983E

C11892E

8

用户手册 U17260CA6V0UD

Page 9

目录

第一章 概述 .......................................................................................................................................... 17

1.1 特性 ................................................................................................................................................ 17

1.2 应用 ................................................................................................................................................ 18

1.3 订购信息 ......................................................................................................................................... 19

1.4 引脚配置 (俯视图)...................................................................................................................... 22

1.5 78K0/Kx2 系列产品........................................................................................................................ 25

1.6 框图 ................................................................................................................................................ 28

1.7 功能概述 ......................................................................................................................................... 29

第二章 引脚功能 ...................................................................................................................................... 32

2.1 引脚功能列表.................................................................................................................................. 32

2.2 引脚功能描述.................................................................................................................................. 36

2.2.1 P00 ~ P06 (端口 0) ....................................................................................................................36

2.2.2 P10 ~ P17 (端口 1) ....................................................................................................................37

2.2.3 P20 ~ P27 (端口 2) ....................................................................................................................38

2.2.4 P30 ~ P33 (端口 3) ....................................................................................................................38

2.2.5 P40 ~ P43 (端口 4) ....................................................................................................................39

2.2.6 P50 ~ P53 (端口 5) ....................................................................................................................39

2.2.7 P60 ~ P63 (端口 6) ....................................................................................................................39

2.2.8 P70 ~ P77 (端口 7) ....................................................................................................................39

2.2.9 P120 ~ P124 (端口 12) ..............................................................................................................40

2.2.10 P130 (端口 13) ..........................................................................................................................41

2.2.11 P140, P141 (端口 14) ................................................................................................................41

2.2.12 AVREF .............................................................................................................................................41

2.2.13 AVSS...............................................................................................................................................42

2.2.14 RESET...........................................................................................................................................42

2.2.15 REGC ............................................................................................................................................42

2.2.16 VDD 和 EVDD ....................................................................................................................................42

2.2.17 VSS 和 EVSS ....................................................................................................................................42

2.2.18 FLMD0 ...........................................................................................................................................42

2.3 引脚 I/O 电路和未使用引脚的建议连接方式 ................................................................................... 43

第三章 CPU 结构....................................................................................................................................... 47

3.1 存储器空间 ..................................................................................................................................... 47

3.1.1 内部程序存储器空间.........................................................................................................................58

3.1.2 存储器 bank (仅对于

3.1.3 内部数据存储器空间.........................................................................................................................60

3.1.4 特殊功能寄存器 (SFR) 区域 ........................................................................................................61

3.1.5 数据存储器空间寻址.........................................................................................................................61

μ

PD78F0536, 78F0537 和 78F0537D) .......................................................60

3.2 处理器寄存器.................................................................................................................................. 69

3.2.1 控制寄存器.......................................................................................................................................69

3.2.2 通用寄存器.......................................................................................................................................73

3.2.3 特殊功能寄存器 (SFRs)...............................................................................................................74

3.3 指令地址寻址.................................................................................................................................. 79

3.3.1 相对寻址 ..........................................................................................................................................79

用户手册 U17260CA6V0UD

9

Page 10

3.3.2 立即寻址.......................................................................................................................................... 80

3.3.3 表间接寻址 ...................................................................................................................................... 81

3.3.4 寄存器寻址 ...................................................................................................................................... 82

3.4 操作数地址寻址 .............................................................................................................................. 82

3.4.1 隐含寻址.......................................................................................................................................... 82

3.4.2 寄存器寻址 ...................................................................................................................................... 83

3.4.3 直接寻址.......................................................................................................................................... 84

3.4.4 短直接寻址 ...................................................................................................................................... 85

3.4.5 特殊功能寄存器 (SFR) 寻址........................................................................................................ 86

3.4.6 寄存器间接寻址 ............................................................................................................................... 87

3.4.7 基址寻址.......................................................................................................................................... 88

3.4.8 基址变址寻址................................................................................................................................... 89

3.4.9 堆栈寻址.......................................................................................................................................... 90

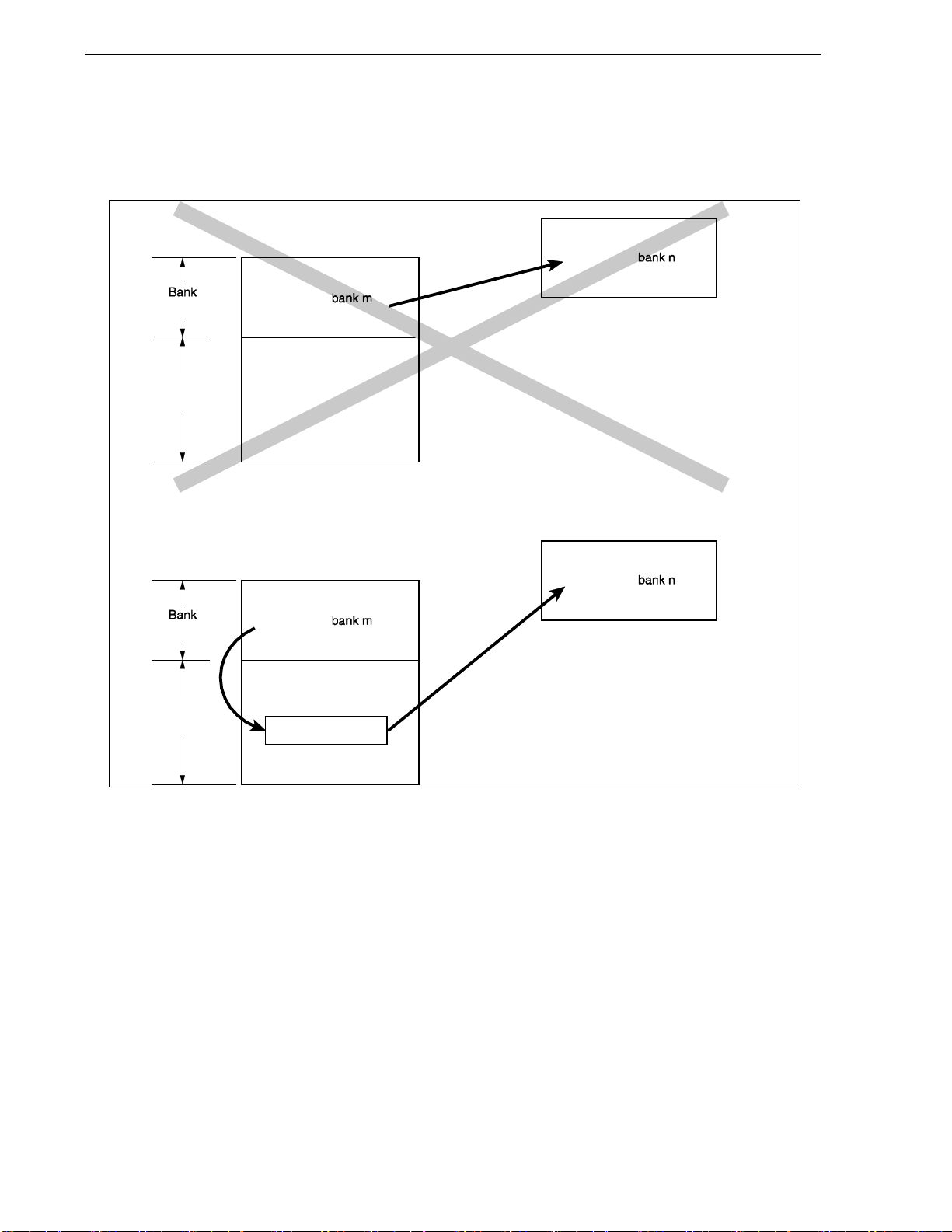

第四章 存储器 BANK 选择功能 (仅适用于

μ

PD78F0536, 78F0537 和 78F0537D).............................. 91

4.1 存储器 Bank ................................................................................................................................... 91

4.2 存储器空间的不同表示 ................................................................................................................... 92

4.3 存储器 Bank 选择寄存器(BANK) .............................................................................................. 93

4.4 选择存储器 Bank............................................................................................................................ 94

4.4.1 存储器 banks 间的关联值 ................................................................................................................ 94

4.4.2 存储器 bank 之间的转移指令........................................................................................................... 96

4.4.3 存储器 bank 之间的子程序调用 ....................................................................................................... 98

4.4.4 通过中断将指令转向存储器 bank 区域........................................................................................... 100

第五章 端口功能....................................................................................................................................... 102

5.1 端口功能 ....................................................................................................................................... 102

5.2 端口配置 ....................................................................................................................................... 104

5.2.1 端口 0 ............................................................................................................................................ 105

5.2.2 端口 1 ............................................................................................................................................ 111

5.2.3 端口 2 ............................................................................................................................................ 116

5.2.4 端口 3 ............................................................................................................................................ 117

5.2.5 端口 4 ............................................................................................................................................ 120

5.2.6 端口 5 ............................................................................................................................................ 121

5.2.7 端口 6 ............................................................................................................................................ 122

5.2.8 端口 7 ............................................................................................................................................ 124

5.2.9 端口 12 .......................................................................................................................................... 125

5.2.10 端口 13 ........................................................................................................................................ 128

5.2.11 端口 14 ........................................................................................................................................ 129

5.3 控制端口功能的寄存器 ................................................................................................................. 130

5.4 端口功能操作 ................................................................................................................................ 135

5.4.1 写入 I/O 端口................................................................................................................................. 135

5.4.2 从 I/O 端口读取.............................................................................................................................. 135

5.4.3 I/O 端口的操作............................................................................................................................... 135

5.5 使用复用功能时端口模式寄存器和输出锁存器的设置 .................................................................. 136

5.6 端口寄存器 n (Pn)的 1 位操作指令的注意事项........................................................................ 139

第六章 时钟发生器................................................................................................................................... 140

6.1 时钟发生器的功能......................................................................................................................... 140

6.2 时钟发生器的配置......................................................................................................................... 141

10

用户手册 U17260CA6V0UD

Page 11

6.3 控制时钟发生器的寄存器.............................................................................................................. 143

6.4 系统时钟振荡器 ............................................................................................................................ 152

6.4.1 X1 振荡器.......................................................................................................................................152

6.4.2 XT1 振荡器 ....................................................................................................................................152

6.4.3 不使用副系统时钟 ..........................................................................................................................155

6.4.4 内部高速振荡器..............................................................................................................................155

6.4.5 内部低速振荡器..............................................................................................................................155

6.4.6 预分频器 ........................................................................................................................................155

6.5 时钟发生器的操作 ........................................................................................................................ 156

6.6 时钟控制 ....................................................................................................................................... 160

6.6.1 高速系统时钟控制 ..........................................................................................................................160

6.6.2 控制内部高速振荡时钟示例............................................................................................................163

6.6.3 控制副系统时钟示例.......................................................................................................................165

6.6.4 控制内部低速振荡时钟示例............................................................................................................167

6.6.5 CPU 和外部硬件所采用的时钟.......................................................................................................167

6.6.6 CPU 时钟状态转换图 .....................................................................................................................168

6.6.7 CPU 时钟切换之前的状况与切换之后的处理..................................................................................173

6.6.8 CPU 时钟和主系统时钟切换所需的时间.........................................................................................174

6.6.9 时钟振荡停止前的状况 ...................................................................................................................175

6.6.10 外部硬件与源时钟 ........................................................................................................................176

第七章 16 位定时器/事件计数器 00 和 01................................................................................................ 177

7.1 16 位定时器/事件计数器 00 和 01 的功能 ..................................................................................... 177

7.2 16 位定时器/事件计数器 00 和 01 的配置 ..................................................................................... 178

7.3 控制 16 位定时器/事件计数器 00 和 01 的寄存器 ......................................................................... 184

7.4 16 位定时器/事件计数器 00 和 01 的操作..................................................................................... 196

7.4.1 间隔定时器的操作 ..........................................................................................................................196

7.4.2 方波输出操作 .................................................................................................................................199

7.4.3 外部事件计数器的操作 ...................................................................................................................202

7.4.4 清零&启动模式(通过 TI00n 引脚有效沿输入进入)下的操作 ....................................................... 206

7.4.5 自由运行定时器操作.......................................................................................................................220

7.4.6 PPG 输出操作................................................................................................................................229

7.4.7 单脉冲输出操作..............................................................................................................................232

7.4.8 脉冲宽度测量操作 ..........................................................................................................................237

7.5 TM0n 的特殊用途......................................................................................................................... 245

7.5.1 TM0n 操作期间重写 CR01n ...........................................................................................................245

7.5.2 LVS0n 和 LVR0n 的设置 ................................................................................................................245

7.6 16 位定时器/事件计数器 00 和 01 注意事项 ................................................................................. 247

第八章 8 位定时器/事件计数器 50 和 51................................................................................................... 251

8.1 8 位定时器/事件计数器 50 和 51 的功能....................................................................................... 251

8.2 8 位定时器/事件计数器 50 和 51 的配置....................................................................................... 251

8.3 控制 8 位定时器/事件计数器 50 和 51 的寄存器 ........................................................................... 254

8.4 8 位定时器/事件计数器 50 和 51 的操作....................................................................................... 259

8.4.1 用作间隔定时器..............................................................................................................................259

8.4.2 用作外部事件计数器.......................................................................................................................261

8.4.3 方波输出操作 .................................................................................................................................262

8.4.4 PWM 输出操作...............................................................................................................................263

8.5 使用 8 位定时器/事件计数器 50 和 51 的注意事项 ....................................................................... 267

用户手册 U17260CA6V0UD

11

Page 12

第九章 8 位定时器 H0 和 H1.................................................................................................................... 268

9.1 8 位定时器 H0 和 H1 的功能......................................................................................................... 268

9.2 8 位定时器 H0 和 H1 的配置 ......................................................................................................... 268

9.3 控制 8 位定时器 H0 和 H1 的寄存器 ............................................................................................. 272

9.4 8 位定时器 H0 和 H1 的操作 ......................................................................................................... 278

9.4.1 间隔定时器/方波输出操作.............................................................................................................. 278

9.4.2 PWM 输出操作 .............................................................................................................................. 281

9.4.3 载波发生器操作 (仅用于 8 位定时器 H1)................................................................................... 287

第十章 钟表定时器................................................................................................................................... 294

10.1 钟表定时器的功能....................................................................................................................... 294

10.2 钟表定时器的配置....................................................................................................................... 295

10.3 控制钟表定时器的寄存器............................................................................................................ 296

10.4 钟表定时器操作 .......................................................................................................................... 298

10.4.1 钟表定时器操作 ........................................................................................................................... 298

10.4.2 间隔定时器操作 ........................................................................................................................... 298

10.5 钟表定时器使用注意事项............................................................................................................ 299

第十一章 看门狗定时器............................................................................................................................ 300

11.1 看门狗定时器的功能 ................................................................................................................... 300

11.2 看门狗定时器的配置 ................................................................................................................... 301

11.3 控制看门狗定时器的寄存器 ........................................................................................................ 302

11.4 看门狗定时器的操作 ................................................................................................................... 303

11.4.1 看门狗定时器操作的控制............................................................................................................. 303

11.4.2 看门狗定时器溢出时间的设置...................................................................................................... 304

11.4.3 看门狗定时器窗口打开周期的设置 .............................................................................................. 305

第十二章 时钟输出/蜂鸣器输出控制器..................................................................................................... 307

12.1 时钟输出/蜂鸣器输出控制器的功能 ............................................................................................ 307

12.2 时钟输出/蜂鸣器输出控制器的配置 ............................................................................................ 308

12.3 控制时钟输出/蜂鸣器输出控制器的寄存器 ................................................................................. 308

12.4 时钟输出/蜂鸣器输出控制器的操作 ............................................................................................ 311

12.4.1 时钟输出操作............................................................................................................................... 311

12.4.2 蜂鸣器输出操作 ........................................................................................................................... 311

第十三章 A/D 转换器 ............................................................................................................................... 312

13.1 A/D 转换器的功能....................................................................................................................... 312

13.2 A/D 转换器的配置....................................................................................................................... 313

13.3 A/D 转换器使用的寄存器............................................................................................................ 315

13.4 A/D 转换器的操作....................................................................................................................... 323

13.4.1 A/D 转换器的基本操作................................................................................................................. 323

13.4.2 输入电压和转换结果.................................................................................................................... 325

13.4.3 A/D 转换器操作模式 .................................................................................................................... 326

13.5 A/D 转换器特征表的阅读方法..................................................................................................... 328

13.6 A/D 转换器使用注意事项............................................................................................................ 330

12

用户手册 U17260CA6V0UD

Page 13

第十四章 串行接口 UART0...................................................................................................................... 334

14.1 串行接口 UART0 的功能 ............................................................................................................ 334

14.2 串行接口 UART0 的配置 ............................................................................................................ 335

14.3 控制串行接口 UART0 的寄存器 ................................................................................................. 338

14.4 串行接口 UART0 的操作 ............................................................................................................ 343

14.4.1 操作停止模式 ...............................................................................................................................343

14.4.2 异步串行接口 (UART)模式 ......................................................................................................344

14.4.3 专用波特率发生器 ........................................................................................................................350

14.4.4 波特率的计算 ...............................................................................................................................351

第十五章 串行接口 UART6...................................................................................................................... 355

15.1 串行接口 UART6 的功能 ............................................................................................................ 355

15.2 串行接口 UART6 的配置 ............................................................................................................ 359

15.3 控制串行接口 UART6 的寄存器 ................................................................................................. 362

15.4 串行接口 UART6 的操作 ............................................................................................................ 371

15.4.1 操作停止模式 ...............................................................................................................................371

15.4.2 异步串行接口(UART)模式 .......................................................................................................372

15.4.3 专用波特率发生器 ........................................................................................................................385

15.4.4 波特率的计算 ...............................................................................................................................387

第十六章 串行接口 CSI10 和 CSI11 ......................................................................................................... 392

16.1 串行接口 CSI10 和 CSI11 的功能............................................................................................... 392

16.2 串行接口 CSI10 和 CSI11 的配置............................................................................................... 393

16.3 控制串行接口 CSI10 和 CSI11 的寄存器 .................................................................................... 396

16.4 串行接口 CSI10 和 CSI11 的操作............................................................................................... 402

16.4.1 操作停止模式 ...............................................................................................................................402

16.4.2 3 线串行 I/O 模式..........................................................................................................................403

第十七章 串行接口 IIC0............................................................................................................................ 415

17.1 串行接口 IIC0 的功能 ................................................................................................................. 415

17.2 串行接口 IIC0 的配置.................................................................................................................. 418

17.3 控制串行接口 IIC0 的寄存器....................................................................................................... 421

2

17.4 I

17.5 I

C 总线模式功能........................................................................................................................ 434

17.4.1 引脚配置 ......................................................................................................................................434

2

C总线定义和控制方法.............................................................................................................. 435

17.5.1 起始条件 ......................................................................................................................................435

17.5.2 地址..............................................................................................................................................436

17.5.3 传送方向指示 ...............................................................................................................................436

17.5.4 应答信号(ACK) ........................................................................................................................437

17.5.5 停止条件 ......................................................................................................................................438

17.5.6 等待..............................................................................................................................................439

17.5.7 取消等待 ......................................................................................................................................441

17.5.8 中断请求 (INTIIC0)产生时序和等待控制..................................................................................441

17.5.9 地址相等的检测方法.....................................................................................................................442

17.5.10 错误检测 .................................................................................................................................... 442

17.5.11 扩展码 ........................................................................................................................................443

17.5.12 仲裁............................................................................................................................................444

17.5.13 唤醒功能 .................................................................................................................................... 445

用户手册 U17260CA6V0UD

13

Page 14

17.5.14 通信预约.................................................................................................................................... 446

17.5.15 其他注意事项............................................................................................................................. 449

17.5.16 通信操作.................................................................................................................................... 451

17.5.17 I

2

C中断请求 (INTIIC0)产生时序 ............................................................................................ 459

17.6 时序图......................................................................................................................................... 480

第十八章 乘法器/除法器 (仅适用于

μ

PD78F0534,78F0535,78F0536,78F0537 和 78F0537D) ......... 487

18.1 乘法器/除法器的功能 .................................................................................................................. 487

18.2 乘法器/除法器的配置 .................................................................................................................. 487

18.3 控制乘法器/除法器的寄存器 ....................................................................................................... 491

18.4 乘法器/除法器的操作 .................................................................................................................. 492

18.4.1 乘法操作...................................................................................................................................... 492

18.4.2 除法操作...................................................................................................................................... 494

第十九章 中断功能................................................................................................................................... 496

19.1 中断类型 ..................................................................................................................................... 496

19.2 中断源及配置 .............................................................................................................................. 496

19.3 控制中断功能的寄存器 ............................................................................................................... 501

19.4 中断服务操作 .............................................................................................................................. 508

19.4.1 可屏蔽的中断响应 ....................................................................................................................... 508

19.4.2 软件中断请求响应 ....................................................................................................................... 510

19.4.3 中断嵌套...................................................................................................................................... 511

19.4.4 保持中断请求............................................................................................................................... 514

第二十章 按键中断功能............................................................................................................................. 515

20.1 按键中断的功能 .......................................................................................................................... 515

20.2 按键中断的配置 .......................................................................................................................... 515

20.3 控制按键中断的寄存器 ............................................................................................................... 516

第二十一章 待机功能 ................................................................................................................................ 517

21.1 待机功能及配置 .......................................................................................................................... 517

21.1.1 待机功能...................................................................................................................................... 517

21.1.2 控制待机功能的寄存器 ................................................................................................................ 517

21.2 待机功能的操作 .......................................................................................................................... 520

21.2.1 HALT 模式................................................................................................................................... 520

21.2.2 STOP 模式 .................................................................................................................................. 525

第二十二章 复位功能 ............................................................................................................................... 531

22.1 确认复位源的寄存器 ................................................................................................................... 539

第二十三章 上电清零电路 ........................................................................................................................ 540

23.1 上电清零电路的功能 ................................................................................................................... 540

23.2 上电清零电路的配置 ................................................................................................................... 541

23.3 上电清零电路的操作 ................................................................................................................... 541

23.4 上电清零电路的注意事项............................................................................................................ 544

第二十四章 低电压检测电路 ..................................................................................................................... 546

24.1 低电压检测电路的功能 ............................................................................................................... 546

24.2 低电压检测电路的配置 ............................................................................................................... 547

14

用户手册 U17260CA6V0UD

Page 15

24.3 控制低电压检测电路的寄存器 .................................................................................................... 547

24.4 低电压检测电路的操作 ............................................................................................................... 550

24.4.1 用于复位 ......................................................................................................................................551

24.4.2 用于中断 ......................................................................................................................................556

24.5 低电压检测电路的注意事项........................................................................................................ 561

第二十五章 选项字节 ................................................................................................................................ 564

25.1 选项字节的功能 .......................................................................................................................... 564

25.2 选项字节的格式 .......................................................................................................................... 566

第二十六章 FLASH 存储器....................................................................................................................... 569

26.1 内部存储器容量切换寄存器........................................................................................................ 569

26.2 内部扩展 RAM 容量切换寄存器.................................................................................................. 571

26.3 用 Flash 编程器写入数据 ........................................................................................................... 572

26.4 编程环境..................................................................................................................................... 575

26.5 通信模式..................................................................................................................................... 575

26.6 在线方式的引脚处理................................................................................................................... 577

26.6.1 FLMD0 引脚.................................................................................................................................577

26.6.2 串行接口引脚 ...............................................................................................................................577

26.6.3 RESET 引脚.................................................................................................................................579

26.6.4 端口引脚 ......................................................................................................................................579

26.6.5 REGC 引脚 ..................................................................................................................................579

26.6.6 其它信号引脚 ...............................................................................................................................579

26.6.7 供电电压 ......................................................................................................................................580

26.7 编程方法..................................................................................................................................... 581

26.7.1 控制 Flash 存储器 ........................................................................................................................581

26.7.2 Flash 存储器编程模式 ..................................................................................................................581

26.7.3 选择通信模式 ...............................................................................................................................582

26.7.4 通信命令 ......................................................................................................................................583

26.8 安全性设置 ................................................................................................................................. 584

26.9 当使用 PG-FP4 时每个命令的执行时间(参考值) ................................................................... 586

26.10 通过自编程进行 Flash 存储器编程........................................................................................... 588

26.10.1 引导交换功能 .............................................................................................................................595

第二十七章 片上调试功能(仅用于

27.1 QB-78K0MINI 或 QB-MINI2 连接

μ

PD78F0537D)............................................................................... 597

μ

PD78F0537D ..................................................................... 597

27.2 QB-78K0MINI 和 QB-MINI2 使用的保留区域 ............................................................................ 599

第二十八章 指令集................................................................................................................................... 600

28.1 操作列表使用规则 ...................................................................................................................... 600

28.1.1 操作数标识符和标识方法 ............................................................................................................. 600

28.1.2 操作栏描述...................................................................................................................................601

28.1.3 标志操作栏的描述 ........................................................................................................................601

28.2 操作列表..................................................................................................................................... 602

28.3 按寻址类型列出指令................................................................................................................... 610

第二十九章 电气特性 (标准产品) ....................................................................................................... 613

第三十章 电气特性((A)级别产品,目标系统).................................................................................... 634

用户手册 U17260CA6V0UD

15

Page 16

第三十一章 电气特性

((A2)级别产品: T

A = −40 ~ +110°C) ................................................................. 654

第三十二章 电气特性

((A2)级别产品: T

A = −40 ~ +125°C) ................................................................. 674

第三十三章 封装图................................................................................................................................... 694

第三十四章 推荐焊接条件 ........................................................................................................................ 702

第三十五章 等待注意事项 ........................................................................................................................ 704

35.1 等待注意事项 .............................................................................................................................. 704

35.2 产生等待的外围硬件 ................................................................................................................... 705

附录 A 开发工具...................................................................................................................................... 706

A.1 软件包 .......................................................................................................................................... 710

A.2 语言处理软件 ............................................................................................................................... 710

A.3 控制软件....................................................................................................................................... 711

A.4 Flash 存储器 写入工具 ................................................................................................................ 712

A.4.1 当使用 flash 存储器编程器 FG-FP4, FL-PR4, PG-FPL3 和 FP-LILE3 ........................................... 712

A.4.2 当使用可写入的片上调试仿真器 QB-MINI2 时 .............................................................................. 712

A.5 调试工具 (硬件) ....................................................................................................................... 713

A.5.1 当使用在线仿真器 QB-78K0KX2 时 .............................................................................................. 713

A.5.2 当使用片上调试仿真器 QB-78K0MINI 时 ...................................................................................... 714

A.5.3 当使用具有编程功能的片上调试仿真器 QB-MINI2 时.................................................................... 714

A.6 调试工具(软件) ........................................................................................................................ 715

附录 B 目标系统设计的注解 ................................................................................................................... 716

附录 C 寄存器索引.................................................................................................................................. 719

C.1 寄存器索引 (按寄存器名称的字母顺序排列)............................................................................ 719

C.2 寄存器索引 (按寄存器符号的字母顺序排列)............................................................................ 723

附录 D 注意事项列表 ............................................................................................................................... 727

附录 E 修订历史...................................................................................................................................... 752

E.1 本版中主要修改之处..................................................................................................................... 752

E.2 以前版本的修订历史..................................................................................................................... 757

16

用户手册 U17260CA6V0UD

Page 17

第一章 概述

1.1 特性

指令最短执行时间可以在高速(0.1s: @高速系统时钟的操作频率为 20 MHz) 和超低速(122s: @子系统

时钟的操作频率为 32.768 kHz)之间改变

通用寄存器: 8 位 32 个寄存器(8 位8 个寄存器4banks)

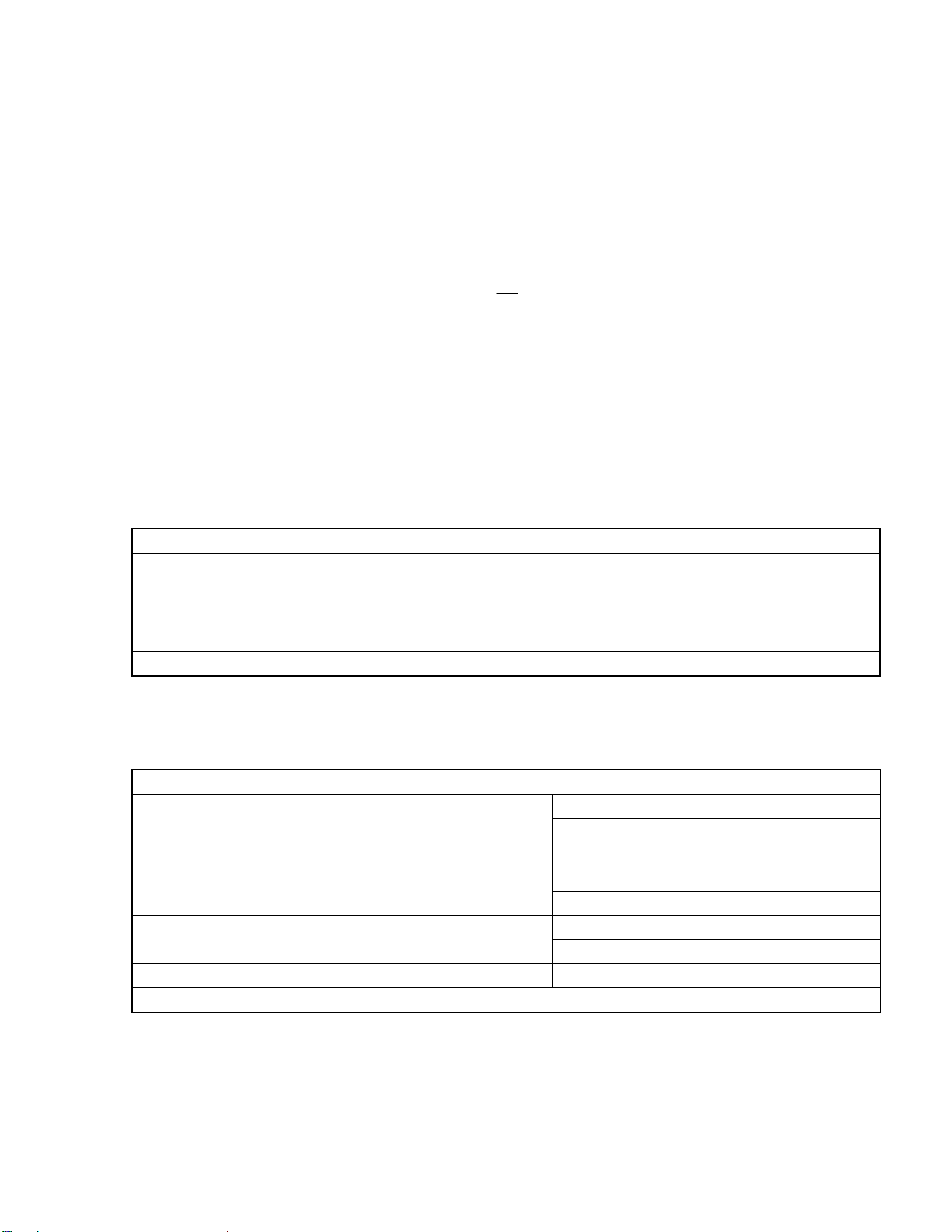

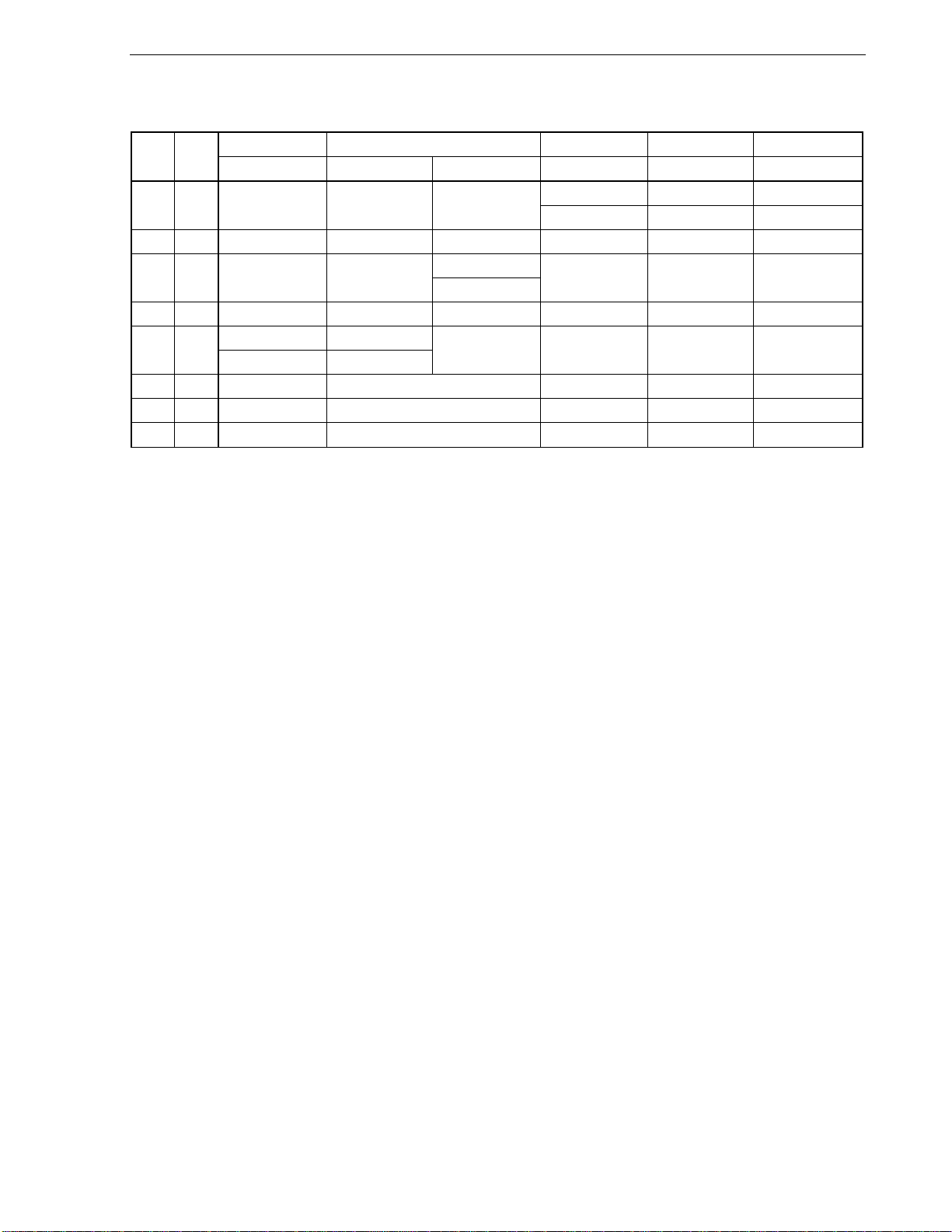

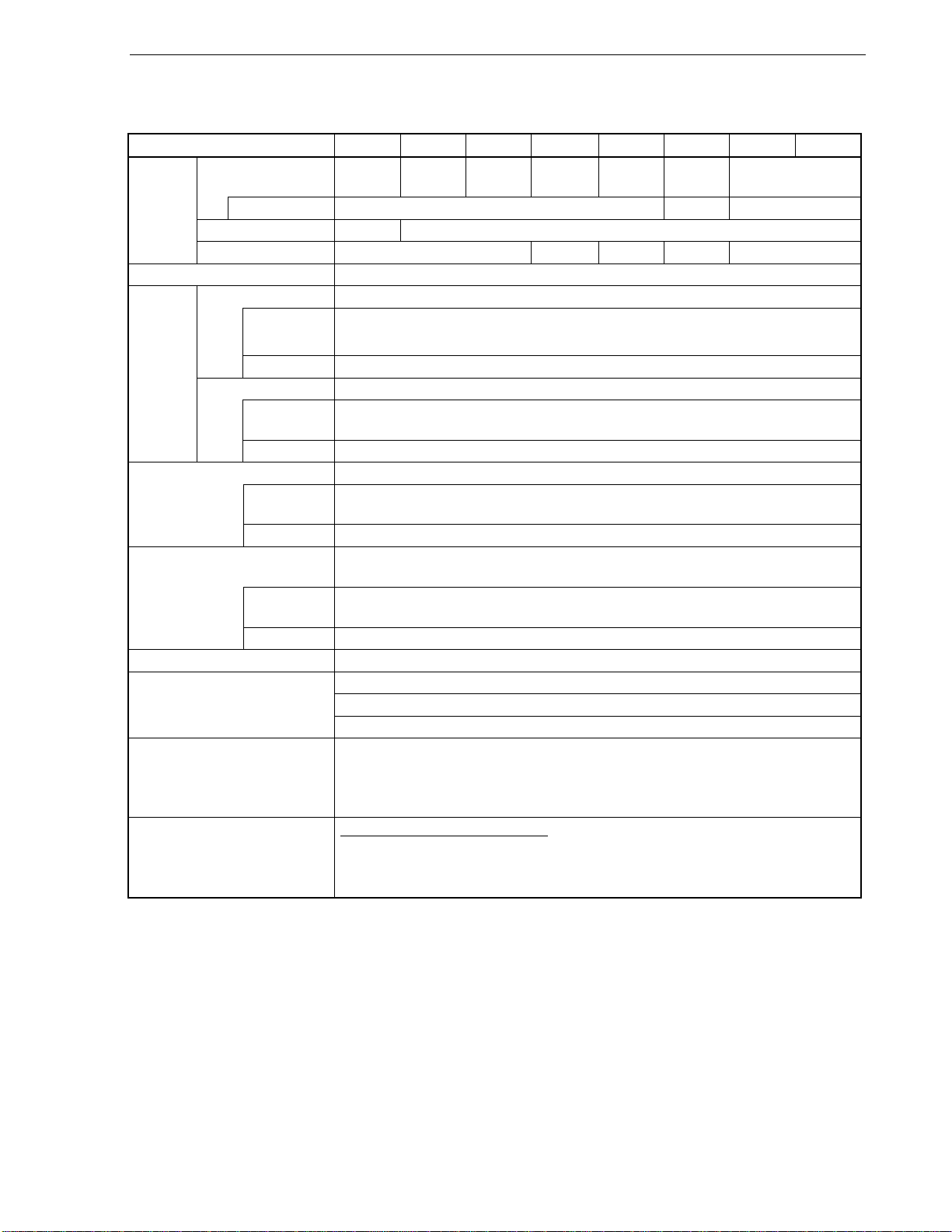

ROM, RAM 的容量

程序存储器

产品型号

PD78F0531 16 KB

PD78F0532 24 KB

PD78F0533 32 KB

PD78F0534 48 KB 1 KB

PD78F0535 60 KB 2 KB

PD78F0536 96 KB 4 KB

PD78F0537, 78F0537D

Flash 存储器

(ROM)

注

内部高速 RAM

768 字节

1 KB

128 KB

数据存储器项目

注

内部扩展 RAM

6 KB

注

注 通过使用内部存储器容量切换寄存器(IMS)和内部扩展 RAM 容量切换寄存器(IXS),可以改变内部

flash 存储器,内部高速 RAM 容量和内部扩展 RAM 的容量。要了解 IMS 和 IXS,请参考 26.1 内部存储

器容量切换寄存器 和 26.2 内部扩展 RAM 容量切换寄存器。

内置单电源 flash 存储器

自编程 (具有启动交换功能)

片上调试功能(仅适用于PD78F0537D)

注

内置上电清零(POC) 电路和低电压检测器(LVI)

内置看门狗定时器 (使用内置的内部低速振荡时钟进行操作)

内置乘法器/除法器(16 位 16 位, 32 位 / 16 位)

(仅适用于PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D)

内置按键中断功能

内置时钟输出/蜂鸣器输出控制器

I/O 端口: 55 (N-ch 漏极开路: 4)

注

PD78F0537D 具有片上调试功能。大规模生产时不要使用本产品,因为在使用片上调试功能后,从 flash 存

储器可重写的次数受到限制这一点来看,它的可靠性不能保证。NEC Electronics 不接受对于本产品的任何投

诉 。

用户手册 U17260CA6V0UD 17

Page 18

第一章 概述

定时器

PD78F0531, 78F0532, 78F0533: 7 通道

PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D:8 通道

16 位定时器/事件计数器: 2 通道

注

8 位定时器/事件计数器: 2 通道

8 位定时器: 2 通道

钟表定时器: 1 通道

看门狗定时器: 1 通道

注PD78F0531, 78F0532, 78F0533:1 通道

串行接口

PD78F0531, 78F0532, 78F0533: 3 通道

PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D: 4 通道

UART (支持 LIN (本地互联网络)-总线): 1 通道

CSI/UART

CSI

注 1

: 1 通道

注 2

: 1 通道

I2C: 1 通道

<R>

<R>

注 1. 选择这些复用功能引脚中的任意一种功能。

2. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D

10 位分辨率 A/D 转换器 (AVREF = 2.3 ~ 5.5 V): 8 通道

供电电压:

标准产品,(A)级产品: VDD = 1.8 ~ 5.5 V

(A2)级产品: VDD = 2.7 ~ 5.5 V

工作环境温度:

标准产品,(A)级产品: TA = – 40 ~ +85C

(A2)级产品: TA = – 40 ~ +110C, TA = – 40 ~ +125C

1.2 应用

汽车设备((A)和(A2)级产品,正在开发中)

车身电子系统控制(电动门窗,无线钥匙的接收等)

用于控制的次级微控制器

汽车音响

AV 设备,家庭音响

PC 外围设备 (键盘等)

家用电器

空调设备

微波炉,电饭煲

工业设备

水泵

自动售货机

FA(工业自动化)

用户手册 U17260CA6V0UD18

Page 19

第一章 概述

<R>

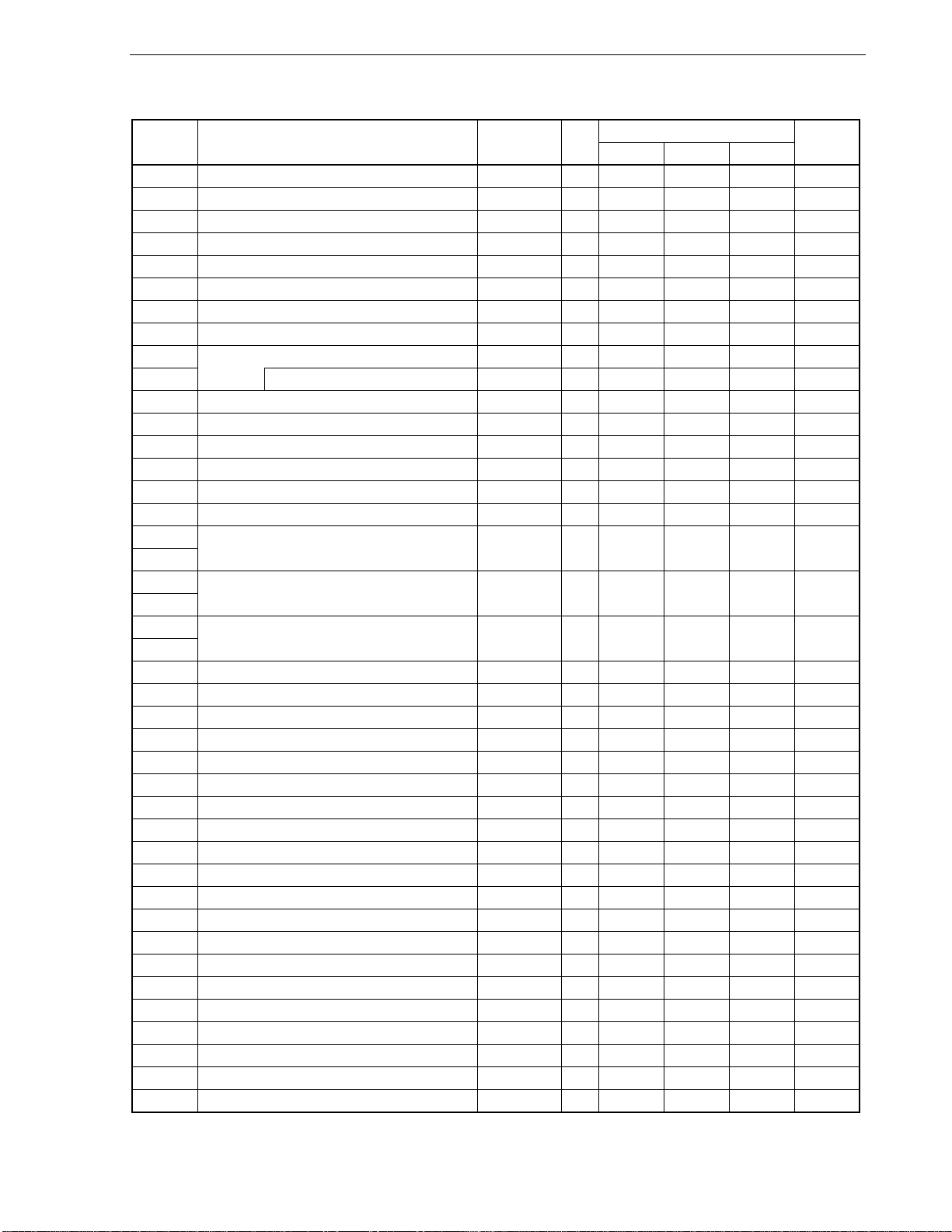

1.3 订购信息

Flash 存储器版本(1/3)

产品型号 封装 质量等级

PD78F0531GB-UEU-A

PD78F0531GC-UBS-A

PD78F0531GK-UET-A 64引脚塑封 LQFP (12x12)

PD78F0531GA-9EV-A 64引脚塑封 TQFP (细脚距) (7x7)

PD78F0531FC-AA1-A

PD78F0532GB-UEU-A

PD78F0532GC-UBS-A

PD78F0532GK-UET-A

PD78F0532GA-9EV-A

PD78F0532FC-AA1-A

PD78F0533GB-UEU-A

PD78F0533GC-UBS-A

PD78F0533GK-UET-A

PD78F0533GA-9EV-A 64引脚塑封 TQFP (细脚距) (7x7) 标准

PD78F0533FC-AA1-A 64引脚塑封 FLGA (5x5) 标准

PD78F0534GB-UEU-A

PD78F0534GC-UBS-A

PD78F0534GK-UET-A

PD78F0534GA-9EV-A

PD78F0534FC-AA1-A 64 引脚塑封 FLGA (5x5) 标准

PD78F0535GB-UEU-A

PD78F0535GC-UBS-A 64 引脚塑封 LQFP (14x14) 标准

PD78F0535GK-UET-A

PD78F0535GA-9EV-A

PD78F0535FC-AA1-A 64 引脚塑封 FLGA (5x5) 标准

PD78F0536GB-UEU-A

PD78F0536GC-UBS-A

PD78F0536GK-UET-A 64 引脚塑封 LQFP (12x12) 标准

PD78F0536GA-9EV-A

PD78F0536FC-AA1-A 64 引脚塑封 FLGA (5x5) 标准

PD78F0537GB-UEU-A

PD78F0537GC-UBS-A

PD78F0537GK-UET-A 64 引脚塑封 LQFP (12x12) 标准

PD78F0537GA-9EV-A

PD78F0537FC-AA1-A

64引脚塑封 LQFP(细脚距) (10x10 ) 标准

64引脚塑封 LQFP (14x14) 标准

64引脚塑封 FLGA (5x5) 标准

64引脚塑封 LQFP (细脚距) (10x10) 标准

64引脚塑封 LQFP (14x14) 标准

64引脚塑封 LQFP (12x12) 标准

64引脚塑封 TQFP (细脚距) (7x7) 标准

64引脚塑封 FLGA (5x5) 标准

64引脚塑封 LQFP (细脚距)(10x10) 标准

64引脚塑封 LQFP (14x14) 标准

64引脚塑封 LQFP (12x12) 标准

64引脚塑封 LQFP (细脚距) (10x10) 标准

64引脚塑封 LQFP (14x14) 标准

64 引脚塑封 LQFP (12x12) 标准

64 引脚塑封 TQFP (细脚距) (7x7) 标准

64 引脚塑封 LQFP (细脚距) (10x10) 标准

64 引脚塑封 LQFP (12x12) 标准

64 引脚塑封 TQFP (细脚距) (7x7) 标准

64 引脚塑封 LQFP (细脚距) (10x10) 标准

64 引脚塑封 LQFP (14x14) 标准

64 引脚塑封 TQFP (细脚距) (7x7) 标准

64 引脚塑封 LQFP (细脚距) (10x10) 标准

64 引脚塑封 LQFP (14x14) 标准

64 引脚塑封 TQFP (细脚距) (7x7) 标准

64 引脚塑封 FLGA (5x5) 标准

标准

标准

备注 在产品型号末尾有-A 的是无铅产品。

如要 了解器件和推荐 应用器 件的质量 等级规 范请参 考 NEC 公司出版 的“ NEC 半 导体器 件质量等级 ” ( 文 档

No.C11531E)

用户手册 U17260CA6V0UD 19

Page 20

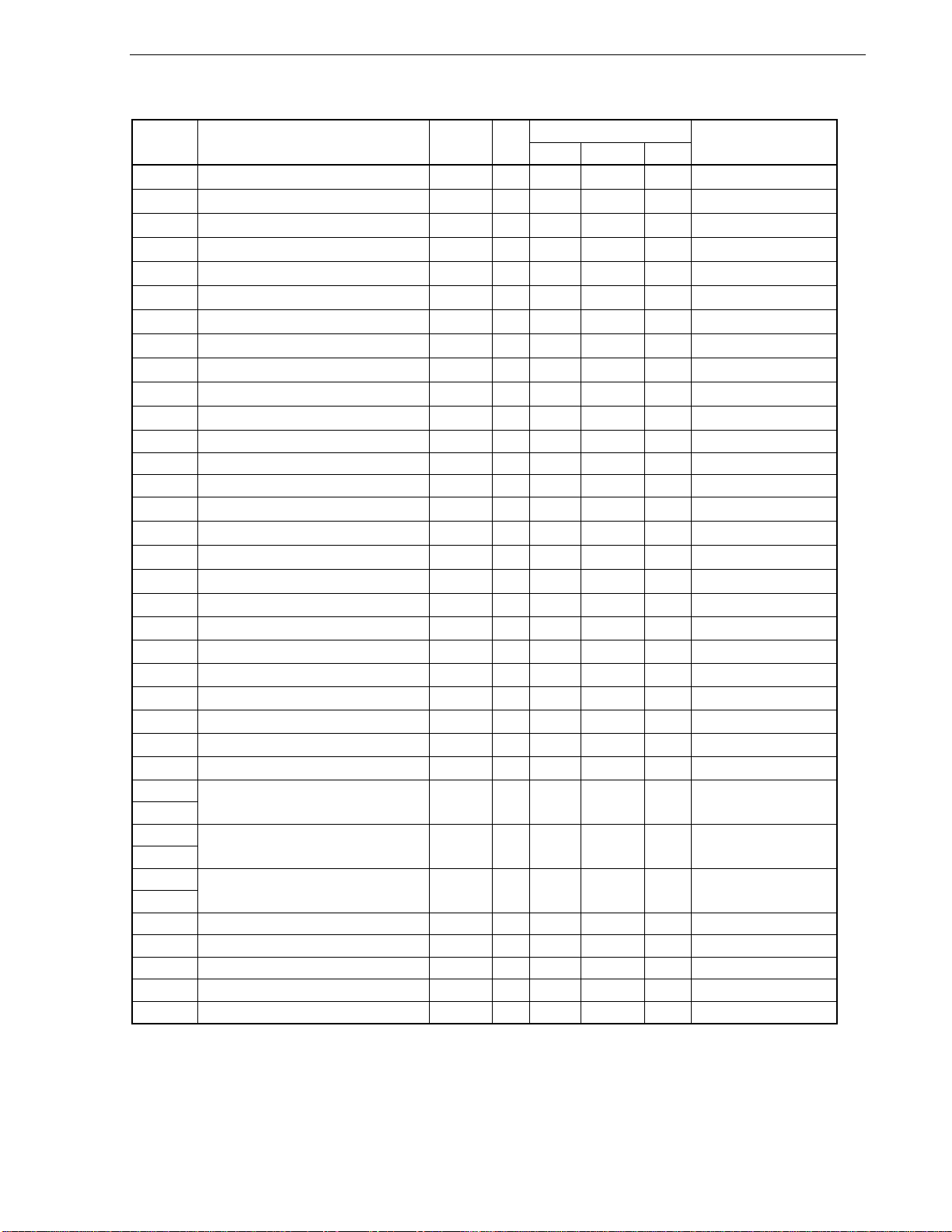

Flash 存储器版本(2/3)

第一章 概述

产品编号 封装 质量等级

PD78F0537DGB-UEU-A

PD78F0537DGC-UBS-A

PD78F0537DGK-UET-A

PD78F0537DGA-9EV-A

PD78F0537DFC-AA1-A

PD78F0531GB(A)-GAH-AX

PD78F0531GC(A)-GAL-AX

PD78F0531GK(A)-GAJ-AX

PD78F0532GB(A)-GAH-AX

PD78F0532GC(A)-GAL-AX

PD78F0532GK(A)-GAJ-AX

PD78F0533GB(A)-GAH-AX

PD78F0533GC(A)-GAL-AX

PD78F0533GK(A)-GAJ-AX

PD78F0534GB(A)-GAH-AX

PD78F0534GC(A)-GAL-AX

PD78F0534GK(A)-GAJ-AX

PD78F0535GB(A)-GAH-AX

PD78F0535GC(A)-GAL-AX

PD78F0535GK(A)-GAJ-AX

PD78F0536GB(A)-GAH-AX

PD78F0536GC(A)-GAL-AX

PD78F0536GK(A)-GAJ-AX

PD78F0537GB(A)-GAH-AX

PD78F0537GC(A)-GAL-AX

PD78F0537GK(A)-GAJ-AX

注1

注1

注1

注1

注1

64引脚塑封 LQFP (细脚距) (10x10) 标准

64引脚塑封 LQFP (14x14) 标准

64引脚塑封 LQFP (12x12) 标准

64引脚塑封 TQFP (细脚距) (7 x7) 标准

64引脚塑封 FLGA (5x5) 标准

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12)

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

注2

64引脚塑封 LQFP (细脚距) (10x10) 专用

注2

64引脚塑封 LQFP (1 4x14) 专用

注2

64引脚塑封 LQFP (1 2x12) 专用

专用

注

PD78F0537D 具有片上调试功能。大规模生产时不要使用本产品,因为在使用片上调试功能后,从 flash 存

储器可重写的次数受到限制这一点来看,它的可靠性不能保证。NEC Electronics 不接受对于本产品的任何投

诉。

备注 在产品型号末尾有-A 和-AX 的是无铅产品。

如要了 解 器 件和推荐应 用 器件的质量等 级 规范请参考 NEC 公司 出 版 的 “ NEC 半导体 器 件 质量等级 ”( 文档

No.C11531E)

用户手册 U17260CA6V0UD20

Page 21

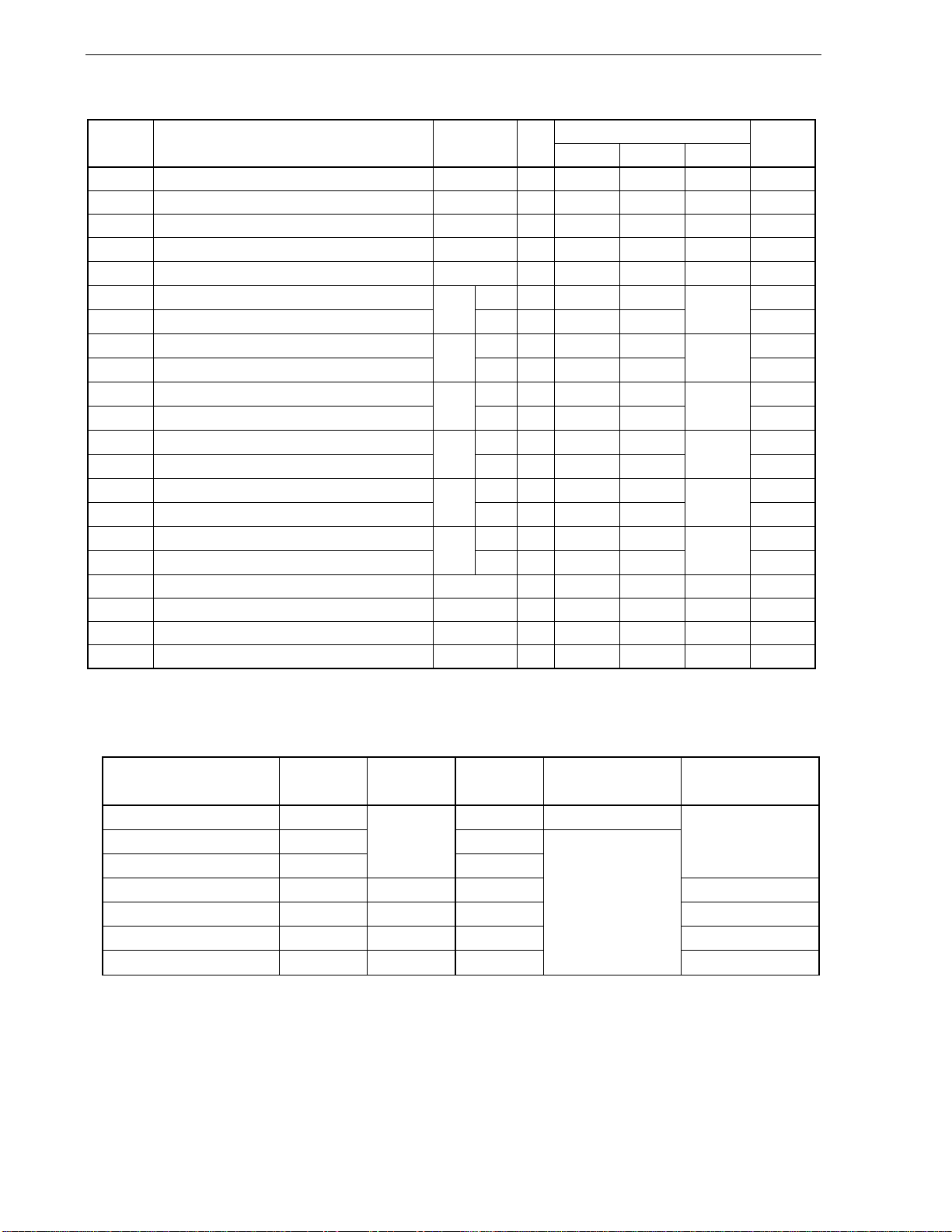

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

<R>

第一章 概述

Flash memory version (3/3)

产品编号 封装 质量等级

PD78F0531GB(A2)-GAH-AX 64引脚塑封LQFP(细脚距)(10x10) 专用

PD78F0531GC(A2)-GAL-AX 64引脚塑封LQFP (14x14) 专用

PD78F0531GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12) 专用

PD78F0532GB(A2)-GAH-AX

PD78F0532GC(A2)-GAL-AX 64引脚塑封LQFP (14x14) 专用

PD78F0532GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12) 专用

PD78F0533GB(A2)-GAH-AX 64 引 脚 塑 封 LQFP ( 细 脚 距 )

PD78F0533GC(A2)-GAL-AX 64引脚塑封LQFP (14x14) 专用

PD78F0533GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12) 专用

PD78F0534GB(A2)-GAH-AX 64

PD78F0534GC(A2)-GAL-AX 64

PD78F0534GK(A2)-GAJ-AX 64

PD78F0535GB(A2)-GAH-AX 64 引 脚 塑 封 LQFP ( 细 脚 距 )

PD78F0535GC(A2)-GAL-AX 64引脚塑封LQFP (14x14)

PD78F0535GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12)

PD78F0536GB(A2)-GAH-AX 64 引 脚 塑 封 LQFP ( 细 脚 距 )

PD78F0536GC(A2)-GAL-AX 64引脚塑封LQFP (14x14) 专用

PD78F0536GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12) 专用

PD78F0537GB(A2)-GAH-AX 64 引 脚 塑 封 LQFP ( 细 脚 距 )

PD78F0537GC(A2)-GAL-AX 64引脚塑封LQFP (14x14) 专用

PD78F0537GK(A2)-GAJ-AX 64引脚塑封LQFP (12x12) 专用

64引脚塑封LQFP (细脚距)(10x10) 专用

10x10)

引 脚 塑 封

10x10)

引脚塑封

引脚塑封

10x10)

10x10)

10x10)

LQFP ( 细 脚 距 )

LQFP (14x14) 专用

LQFP (12x12) 专用

专用

专用

专用

专用

专用

专用

专用

备注 在产品型号末尾有-A 和-AX 的是无铅产品。

如要 了 解 器 件和推荐 应 用 器件 的 质 量 等级规范 请 参 考 NEC 公司 出 版 的 “NEC 半 导 体器件 质 量 等级 ” ( 文 档

No.C11531E)

用户手册 U17260CA6V0UD 21

Page 22

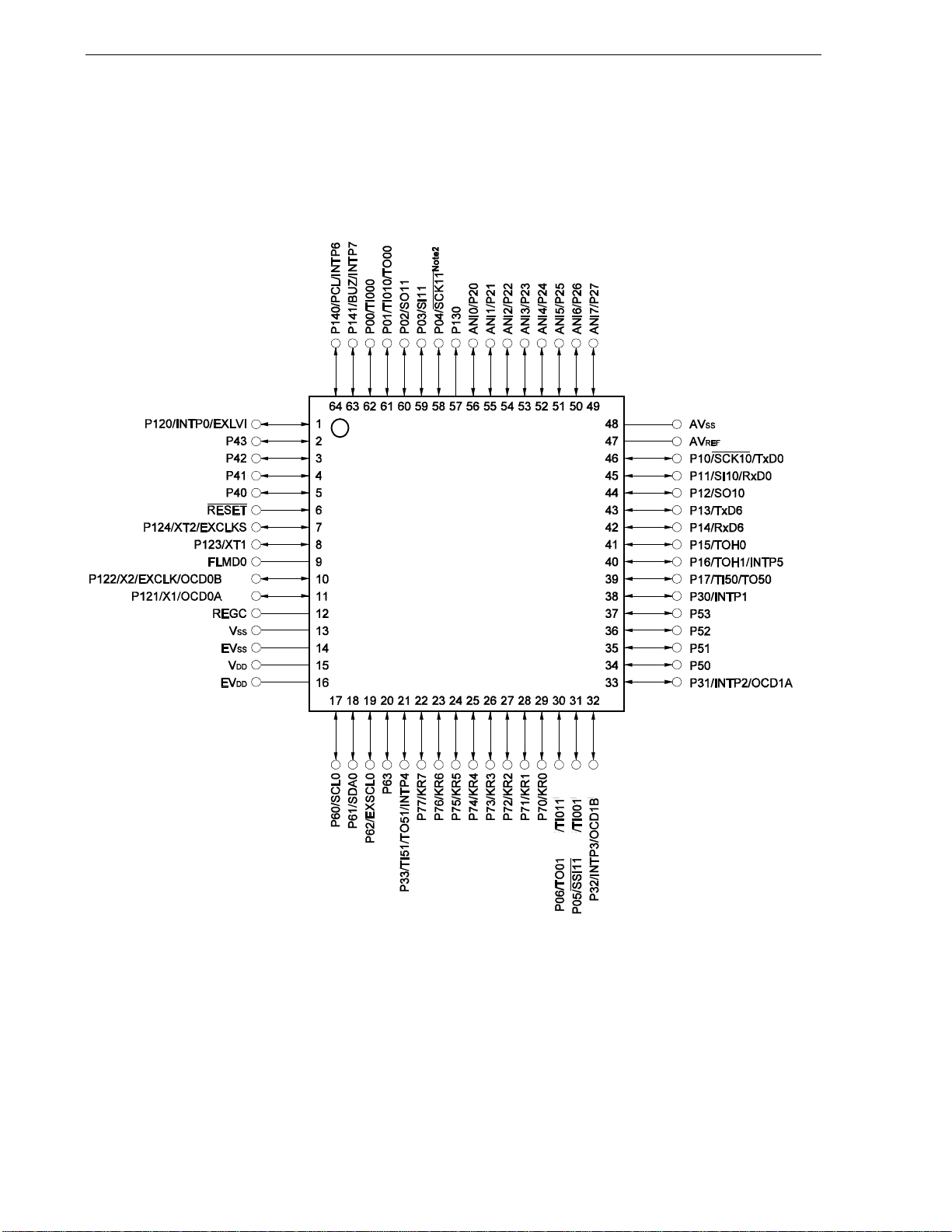

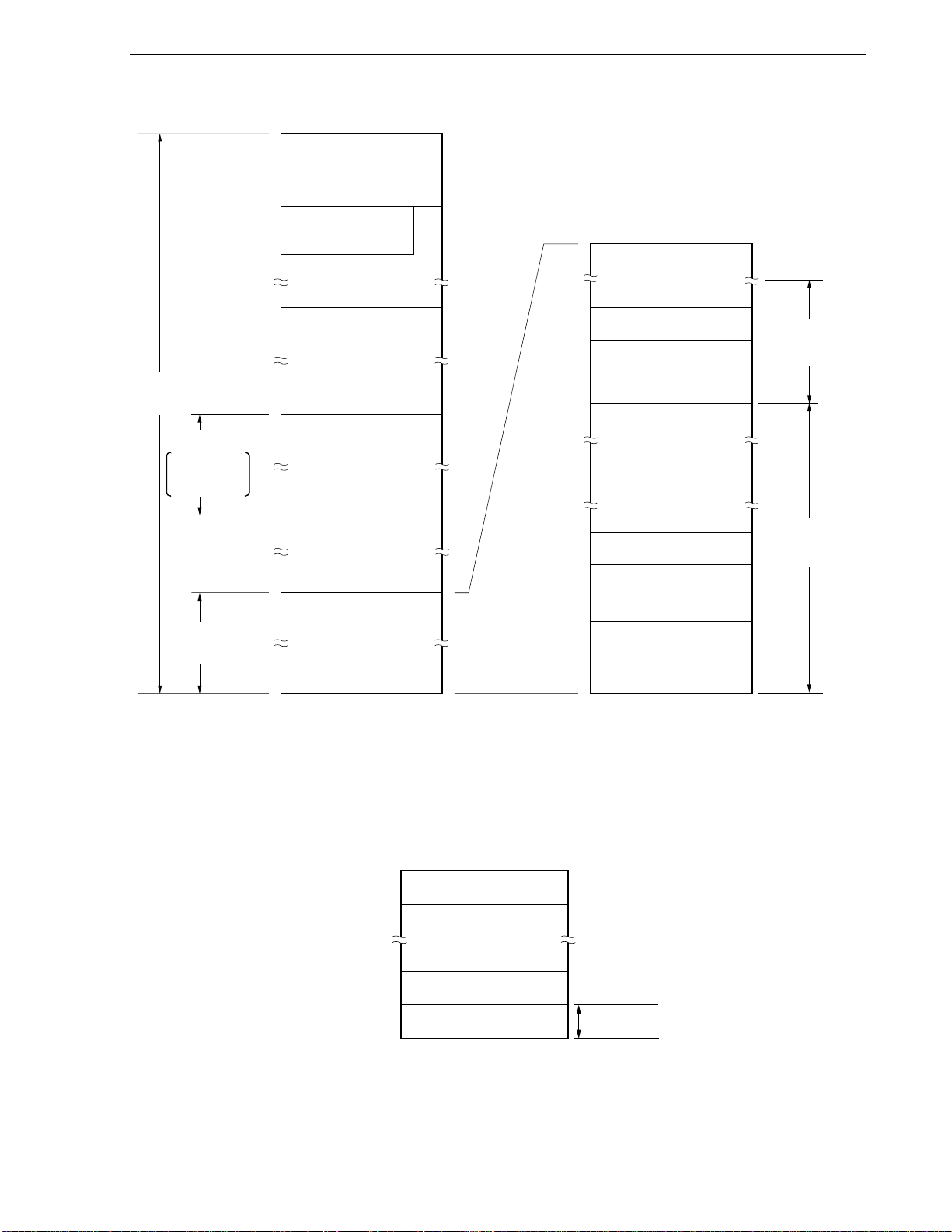

1.4 引脚配置 (俯视图)

1

1

2

2

1

64 引脚塑封 LQFP (细脚距) (10 10)

64 引脚塑封 LQFP (14 14)

64 引脚塑封 LQFP (12 12)

64 引脚塑封 TQFP (细脚距) (7 7)

第一章 概述

注

注

注

注

注 1. 仅适用于PD78F0537D(具有片上调试功能的产品)

2. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D

注意事项 1. 使 AVSS, EVSS 与 VSS 的电位相同。

2. 使 EVDD 与 VDD 的电位相同。

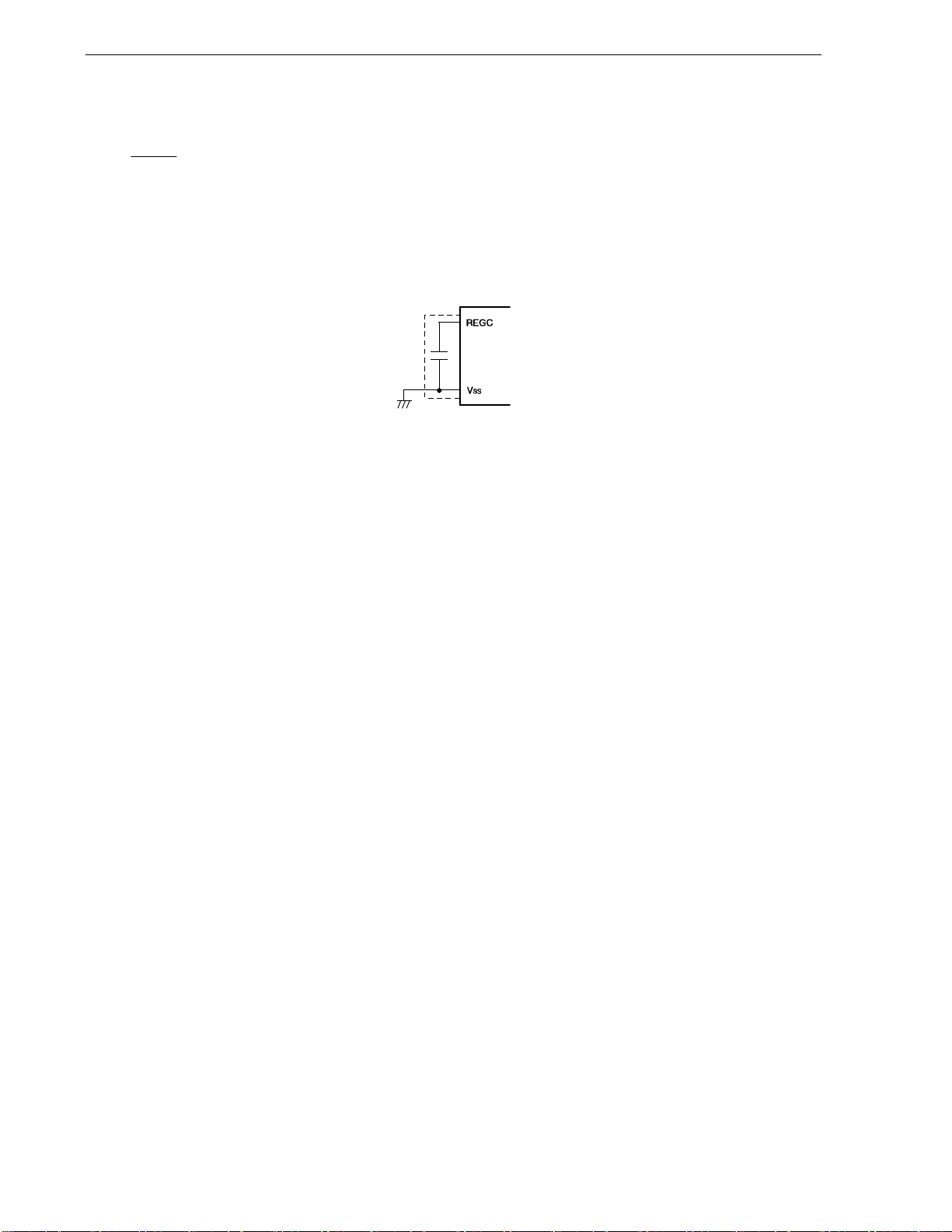

3. 通过一个电容(推荐使用 0.47F ~ 1F)将 REGC 引脚和 VSS 连接到一起。

4. 复位后,ANI0/P20 ~ ANI7/P27 设置为模拟输入模式。

注2注

注

注

注

注

用户手册 U17260CA6V0UD22

Page 23

第一章 概述

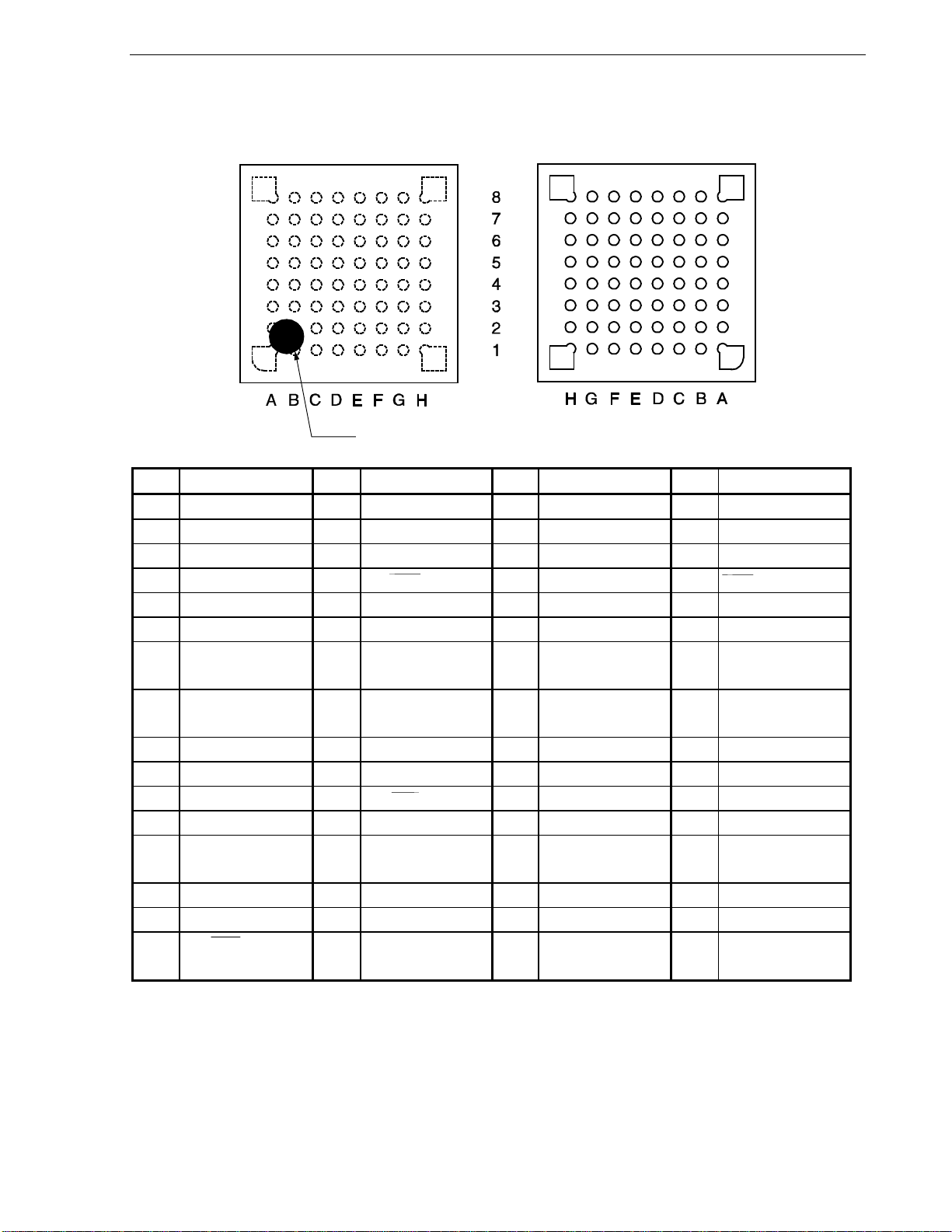

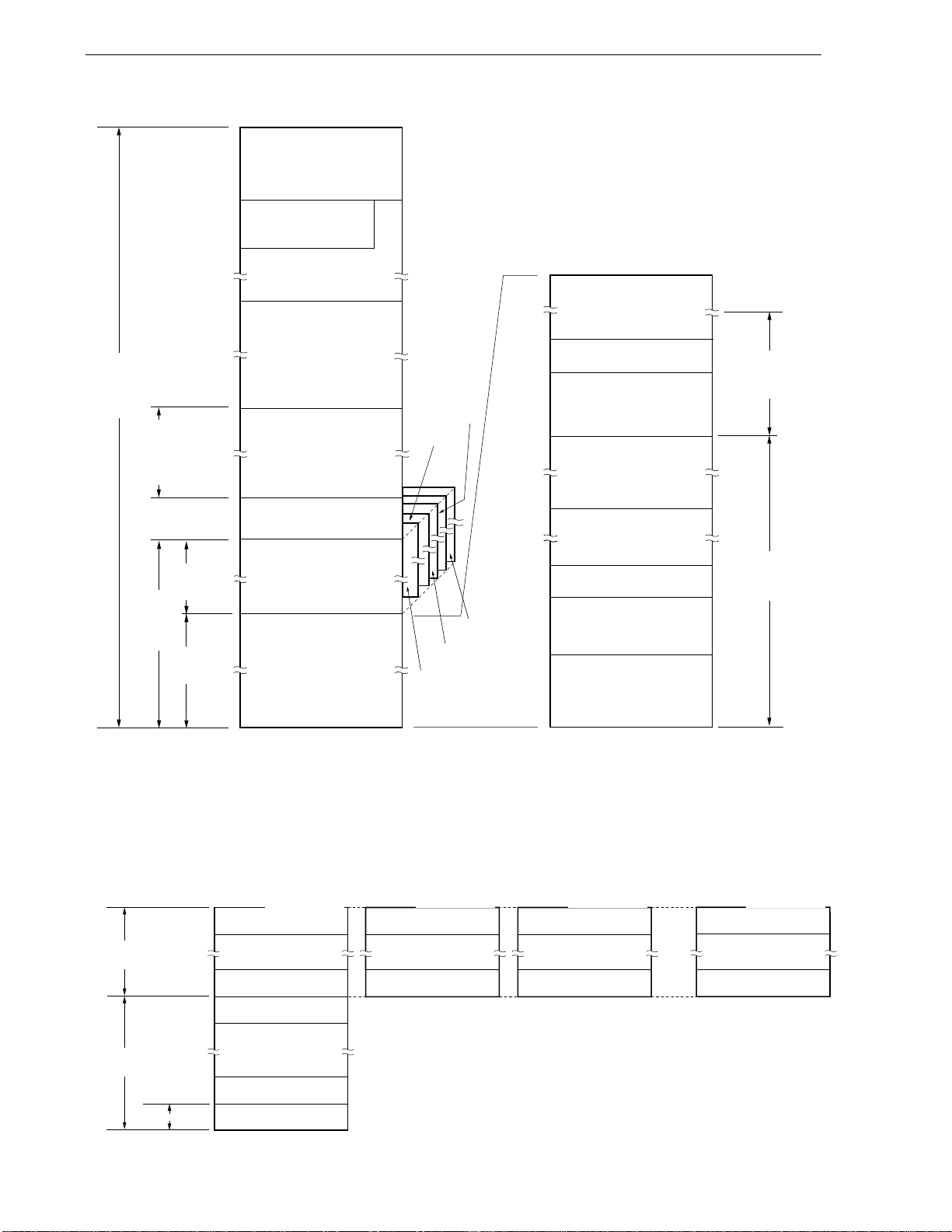

64 引脚塑封 FLGA (5 5)

顶视图 底视图

索引标记

引脚号

.

A1 AVSS C1 ANI4/P24 E1 P130 G1 P141/BUZ/INTP7

A2 AVREF C2 ANI3/P23 E2 ANI0/P20 G2 P140/PCL/INTP6

A3 P11/SI10/RxD0 C3 ANI7/P27 E3 P03/SI11

A4 P13/TxD6 C4 P10/SCK10/TxD0 E4 P42 G4 RESET

A5 P16/TOH1/INTP5 C5 P17/TI50/TO50 E5 P77/KR7 G5 REGC

A6 P53 C6 P30/INTP1 E6 P33/TI51/TO51/INTP4 G6 VSS

A7 P51 C7 P31/INTP2/

A8 P32/INTP3/

B1 ANI5/P25 D1 ANI1/P21 F1 P01/TI010/TO00 H1 P120/INTP0/EXLVI

B2 ANI6/P26 D2 ANI2/P22 F2 P00/TI000 H2 P124/XT2/EXCLKS

B3 P12/SO10 D3 P04/SCK11

B4 P15/TOH0 D4 P72/KR2 F4 P41 H4 FLMD0

B5 P14/RxD6 D5 P70/KR0 F5 P40 H5 P122/X2/EXCLK

B6 P52 D6 P71/KR1 F6 P60/SCL0 H6 P121/X1/OCD0A

B7 P50 D7 P75/KR5 F7 P62/EXSCL0 H7 EVSS

B8 P05/SSI11注2/

OCD1B

TI001

引脚名

注1

注2

引脚号

.

引脚名

引脚号

.

引脚名

注2

引脚号

.

G3 P43

E7 P74/KR4 G7 VDD

注1

OCD1A

C8 P06 /TO01注2/

注2

TI011

注2

E8 P76/KR6 G8 P61/SDA0

F3 P02/SO11

注2

H3 P123/XT1

/OCD0B

D8 P73/KR3 F8 P63 H8 EVDD

引脚名

注1

注1

注 1. 仅适用于PD78F0537D (具有片上调试功能的产品)

2. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D

注意事项 1. 使 AVSS, EVSS 与 VSS 的电位相同。

2. 使 EVDD 与 VDD 的电位相同。

3. 通过一个电容(推荐使用 0.47F ~ 1F)将 REGC 引脚和 VSS 连接到一起。

4. 复位后,ANI0/P20 ~ ANI7/P27 设置为模拟输入模式。

用户手册 U17260CA6V0UD 23

Page 24

引脚标示

第一章 概述

ANI0 ~ ANI7: 模拟输入

AVREF: 模拟参考电压

AVSS: 模拟地

BUZ: 蜂鸣器输出

EVDD: 端口电源

EVSS: 端口地

EXCLK: 外部时钟输入

(主系统时钟)

EXCLKS: 外部时钟输入

(副系统时钟)

EXLVI: 外部电压输入

用于低电压检测器

EXSCL0: 外部串形时钟输入

FLMD0: Flash 编程模式

INTP0 ~ INTP7: 外部中断输入

KR0 ~ KR7: 按键返回

OCD0A

OCD0B

OCD1A

OCD1B

注 1

,

注 1

,

注 1

,

注 1

: 片上调试输入/输出

P00 ~ P06: 端口 0

P10 ~ P17: 端口 1

P20 ~ P27: 端口 2

P30 ~ P33: 端口 3

P40 ~ P43: 端口 4

P50 ~ P53: 端口 5

P60 ~ P63: 端口 6

P70 ~ P77: 端口 7

P120 ~ P124: 端口 12

P130: 端口 13

P140, P141: 端口 14

PCL: 可编程时钟输出

REGC 稳压器电容

RESET: 复位

RxD0, RxD6: 接收数据

SCK10, SCK11注2,

SCL0: 串行时钟输入/输出

SDA0: 串行数据输入/输出

SI10, SI11

注 2

: 串行数据输入

SO10, SO11注2: 串行数据输出

注 2

SSI11

: 串行接口芯片选择输入

TI000, TI010,

TI001注2, TI011注2,

TI50, TI51: 定时器输入

TO00, TO01注2,

TO50, TO51,

TOH0, TOH1: 定时器输出

TxD0, TxD6: 发送数据

VDD: 供电电源

VSS: 地

X1, X2: 晶体振荡器 (主系统时钟)

XT1, XT2: 晶体振荡器(副系统时钟)

注 1. 仅适用于PD78F0537D (具有片上调试功能的产品)

2. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537, 78F0537D

用户手册 U17260CA6V0UD24

Page 25

第一章 概述

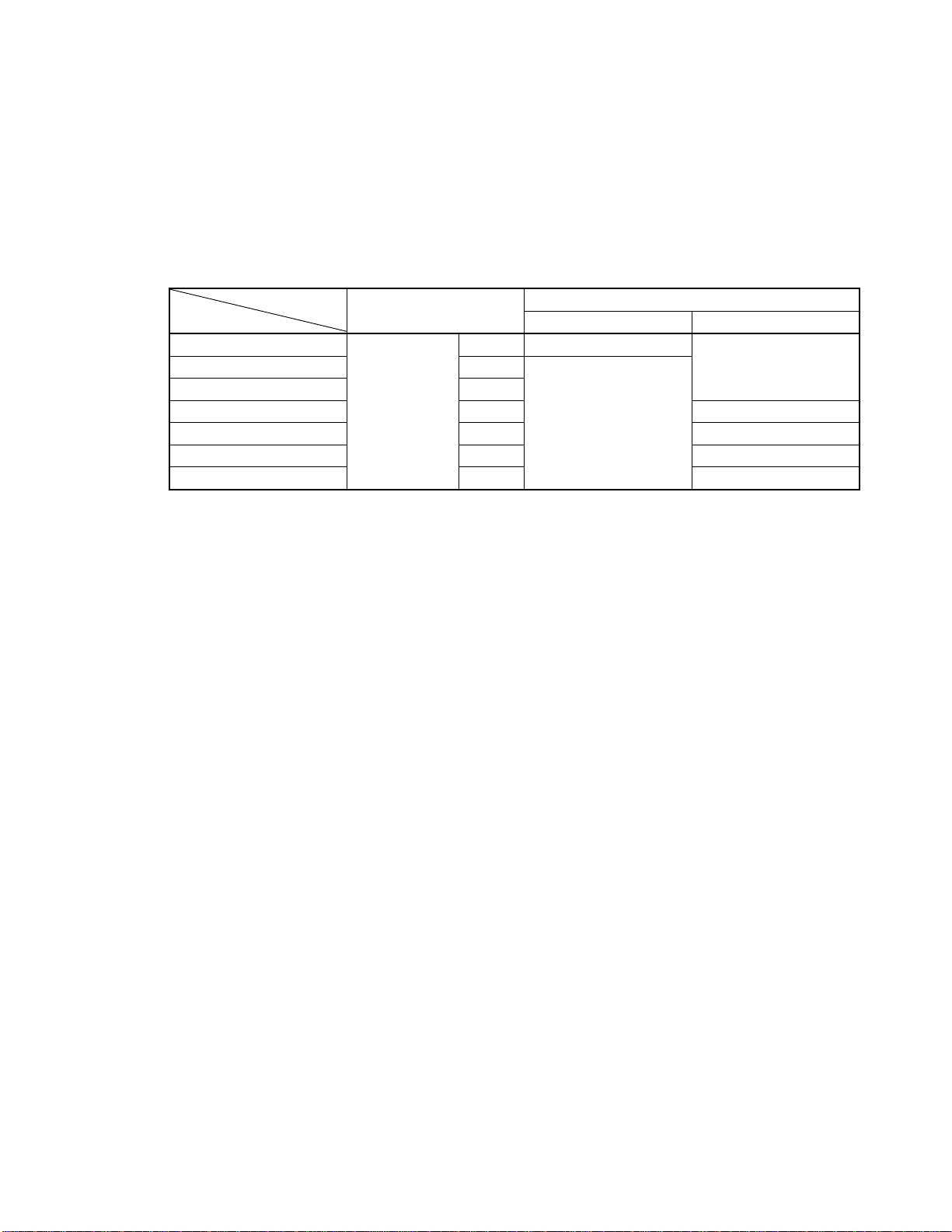

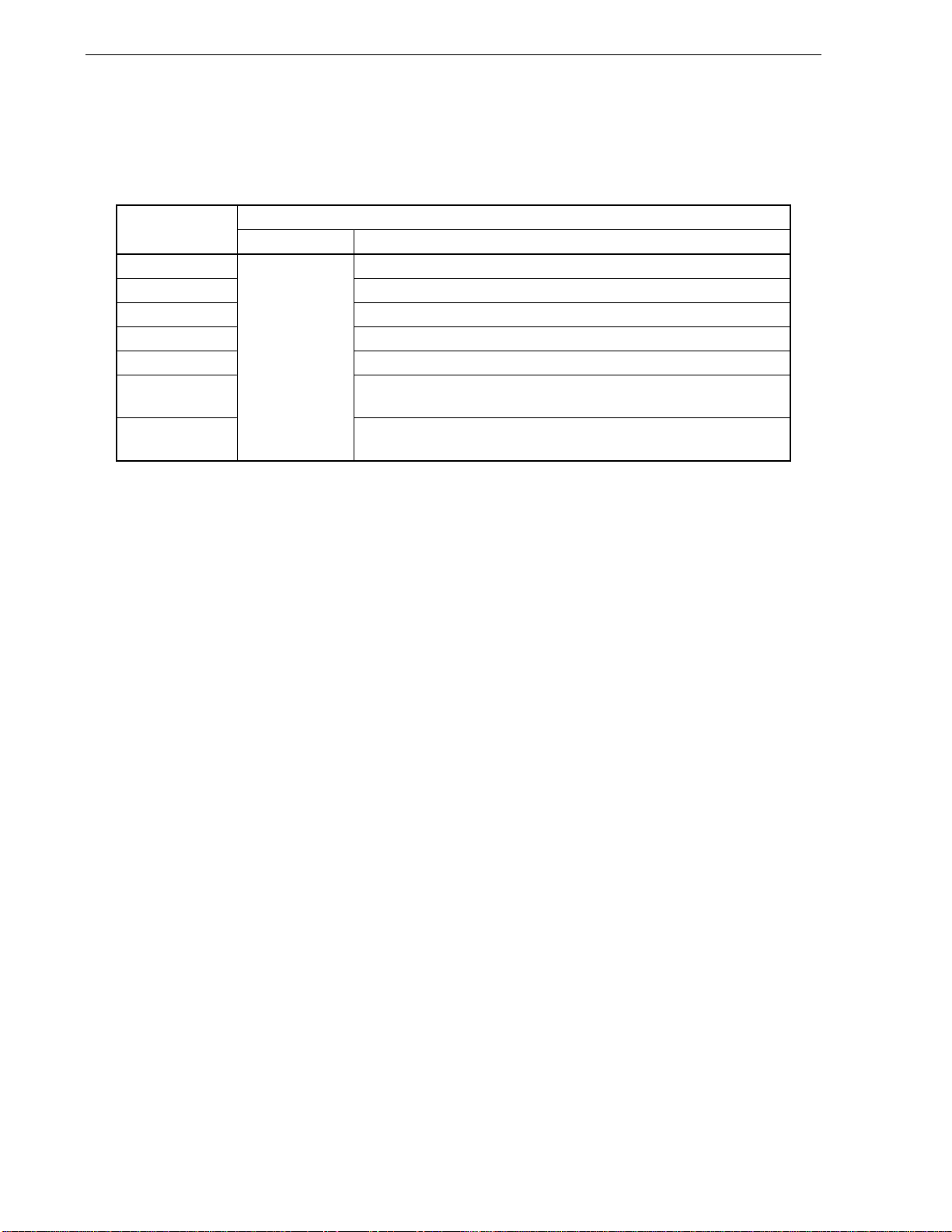

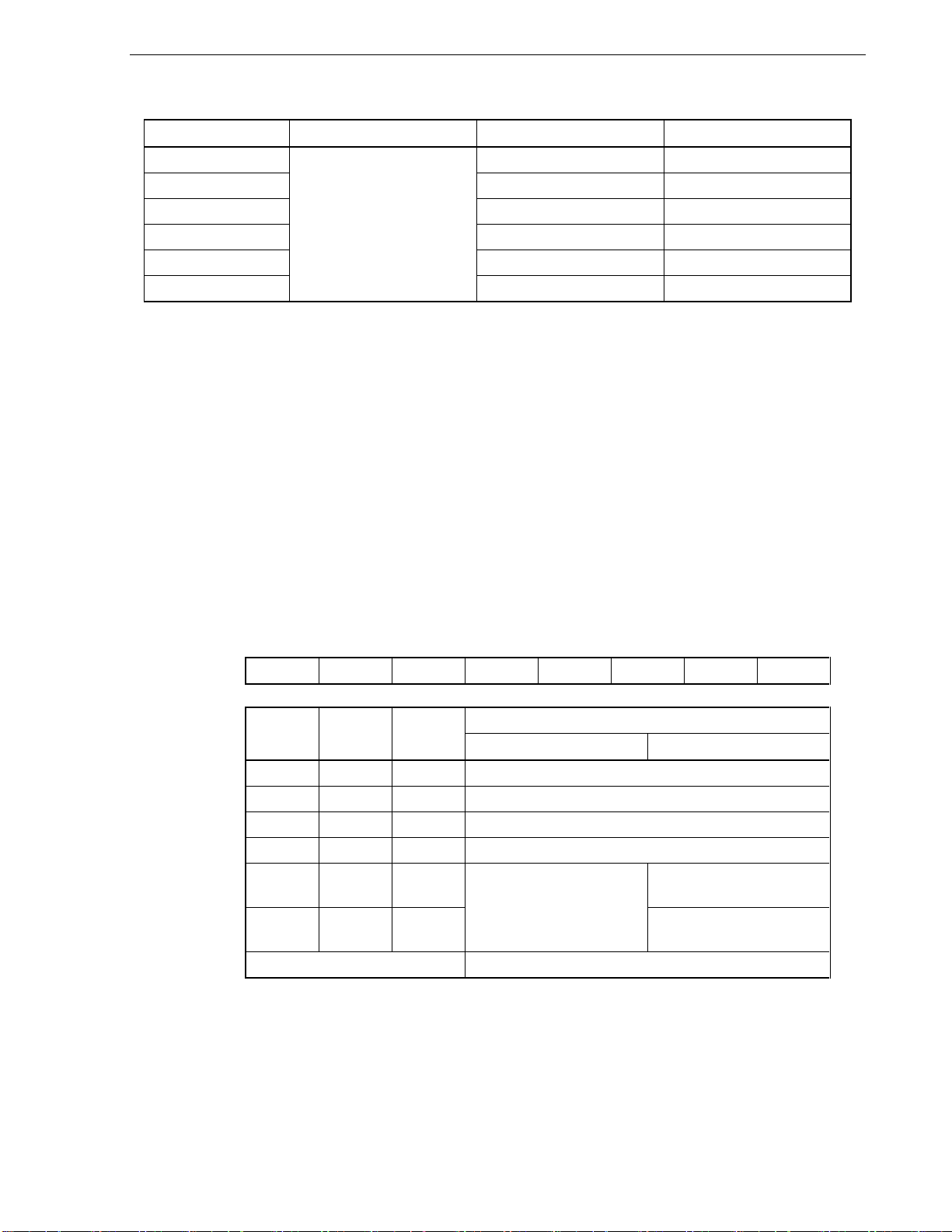

1.5 78K0/Kx2 系列产品

78K0/KB2 78K0/KC2 78K0/KD2 78K0/KE2 78K0/KF2ROM RAM

30/36 引脚 44 引脚 48 引脚 52 引脚 64 引脚 80 引脚

128 KB 7 KB

96 KB 5 KB

60 KB 3 KB

48 KB 2 KB

32 KB 1 KB

24 KB 1 KB

16 KB 768 B

PD78F0503D

PD78F0503

PD78F0502

PD78F0501

注

PD78F0513D

PD78F0513

PD78F0515D

PD78F0515

PD78F0514

注

PD78F0513

PD78F0512

PD78F0511

PD78F0527D

注

PD78F0527

PD78F0526

PD78F0525

PD78F0524

PD78F0523

PD78F0522

PD78F0521

注

PD78F0537D

PD78F0537

PD78F0536

PD78F0535

PD78F0534

PD78F0533

PD78F0532

PD78F0531

8 KB 512 BPD78F0500

注 具有片上调试功能的产品

注

PD78F0547D

PD78F0547

PD78F0546

PD78F0545

PD78F0544

注

用户手册 U17260CA6V0UD 25

Page 26

<R>

第一章 概述

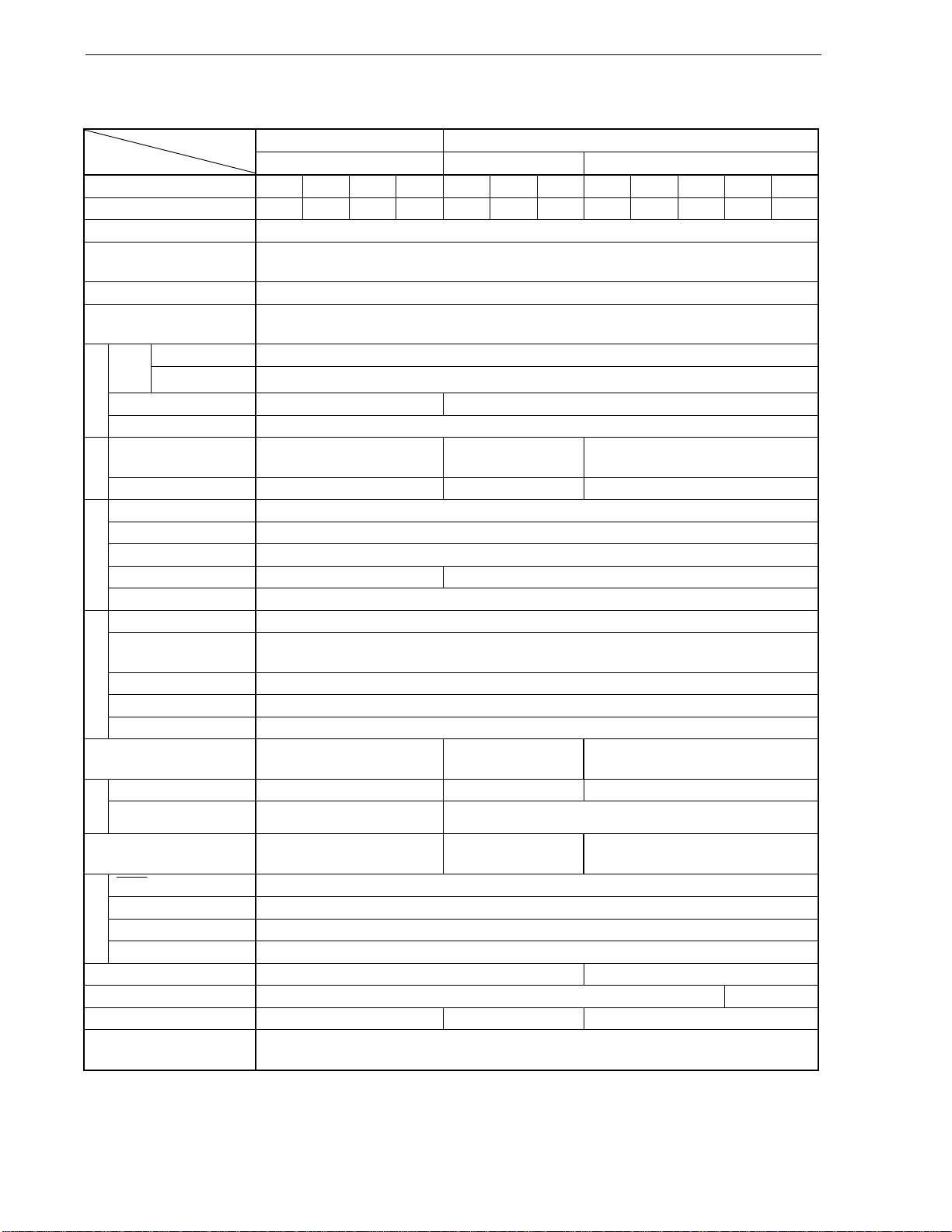

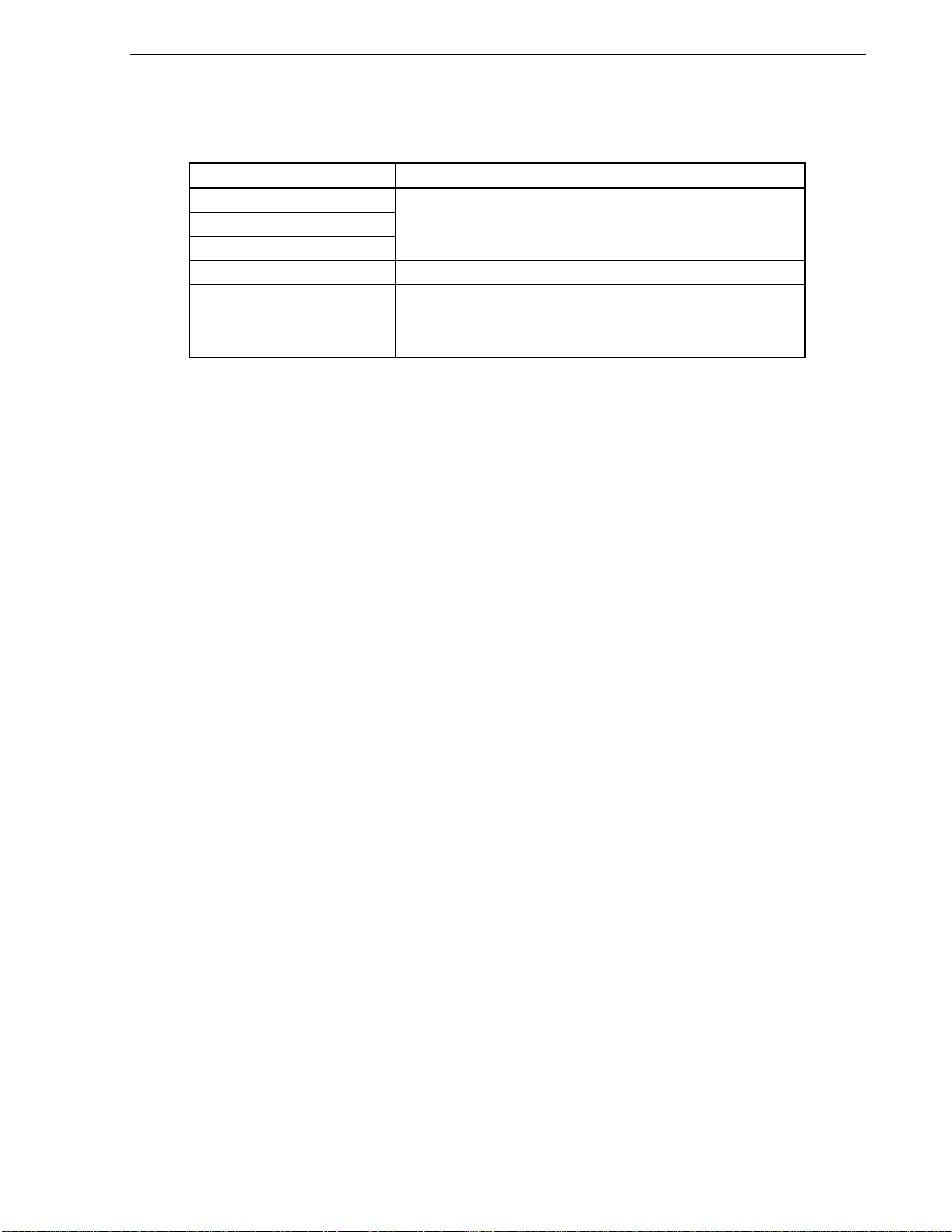

78K0/Kx2 系列的功能列表如下。

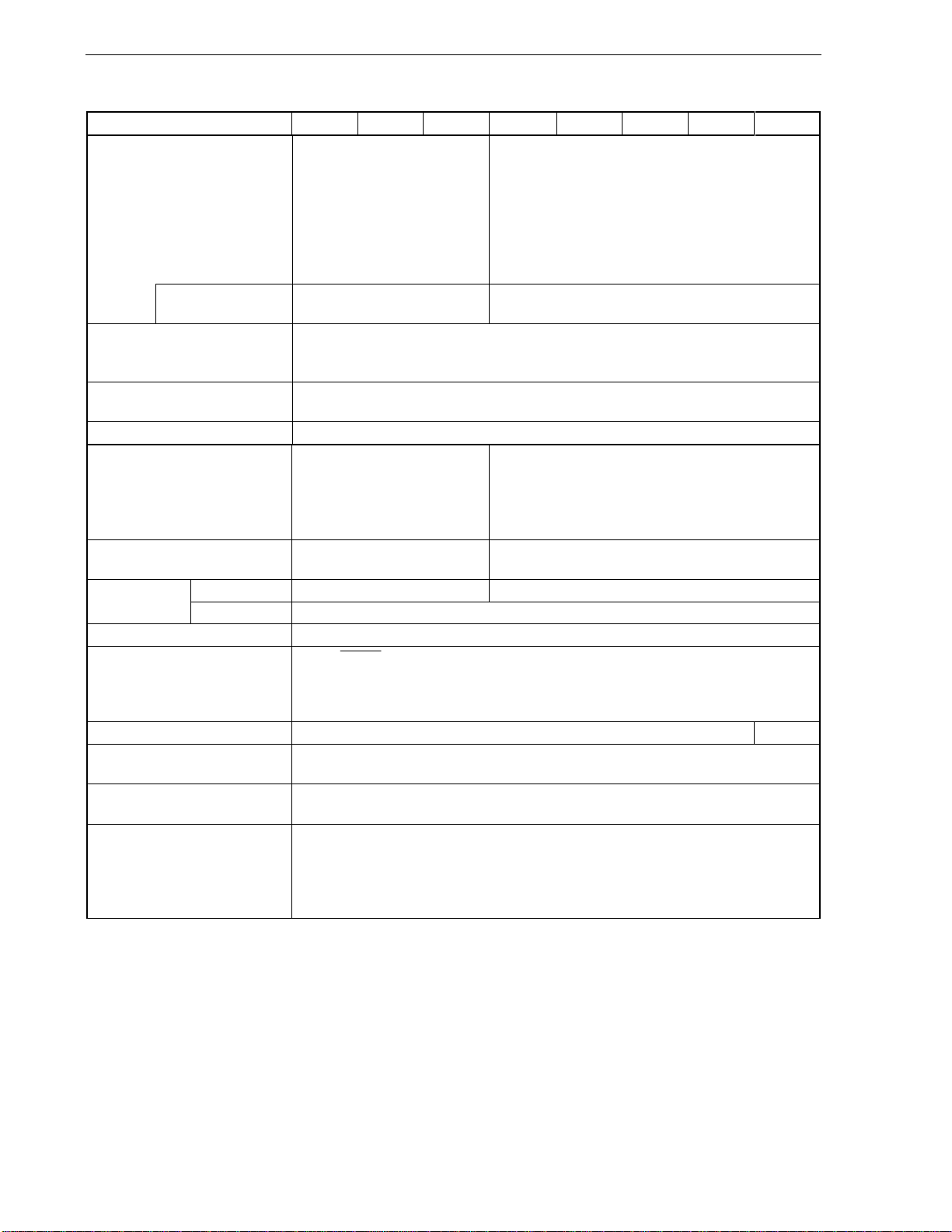

(1/2)

78K0/KB2 78K0/KC2产品型号

项目

Flash 存储器(KB)

RAM (KB) 0.5 0.75 1 1 0.75 1 1 0.75 1 1 2 3

Bank(flash 存储器)

电源电压 标准产品,(A)级产品:VDD = 1.8 ~ 5.5 V

稳压器 提供

最小指令执行时间 0.1s (20 MHz: VDD = 4.0 ~ 5.5 V)/0.2s (10 MHz: VDD = 2.7~ 5.5 V)/

高速系统 20 MHz: VDD = 4.0 ~ 5.5 V/10 MHz: VDD = 2.7~ 5.5 V/ 5 MHz: V DD = 1.8 ~ 5.5 V

时 钟

内部高速振荡 8 MHz (TYP.): VDD = 1.8 ~ 5.5 V

主系统

时钟

副系统

内部低速振荡 240 kHz (TYP.): VDD = 1.8 ~ 5.5 V

合计 23 31 (38 引脚)/

端口

N-ch 开漏(6 V 耐压) 2 4 4

16 位 (TM0) 1 通道

8 位(TM5) 2 通道

8 位(TMH) 2 通道

定时器

钟表 1 通道

看门狗 1 通道

3 线 CSI

自动 发送/接收

3 线 CSI

UART/3 线 CSI

串行接口

支持 LIN 总线的 UART 1 通道

注

I2C 总线 1 通道

10 位 A/D 4 通道 6 通道(38 引脚)/

外部 6 7 8

内部 14 16

中断

30/36 引脚 33/44 引脚 48 引脚

8 16 24 32 16 24 32 16 24 32 48 60

(A2)级产品:VDD = 2.7 ~ 5.5 V

0.4s (5 MHz: VDD = 1.8 ~ 5.5 V)

32.768 kHz (TYP.): VDD = 1.8 ~ 5.5 V

41

37 (44 引脚)

1 通道

8 通道

8 通道(44 引脚)

<R>

按键中断 2 通道(38引脚)/

4 通道

4 通道(44 引脚)

RESET 引脚 提供

POC

复位

LVI 可选择 16 个供电电压的检测级别。

1.59 V 0.15 V (上升到 1.8 V 的时间: 3.6 ms (最大值))

WDT 提供

时钟输出/蜂鸣器输出

仅有时钟输出

乘法器/除法器 提供

片上调试功能 仅适用于PD78F0503D 仅适用于PD78F0513D 仅适用于PD78F0515D

工作环境温度 标准产品,(A)级产品:TA = – 40 ~ +85C

(A2)级产品:TA = – 40 to +110C, TA = – 40 ~ +125C

注 选择这些复用功能引脚中的任意一种功能。

用户手册 U17260CA6V0UD26

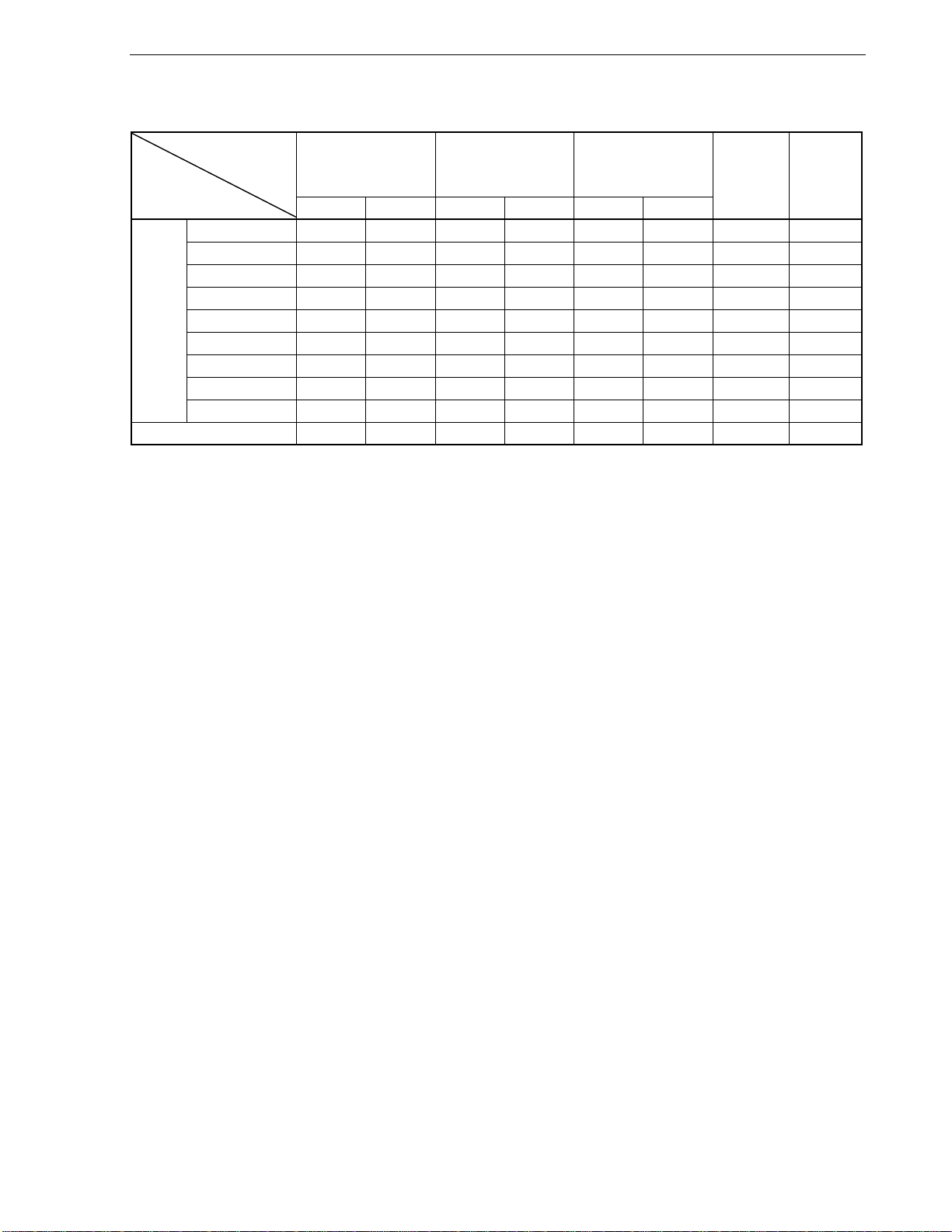

Page 27

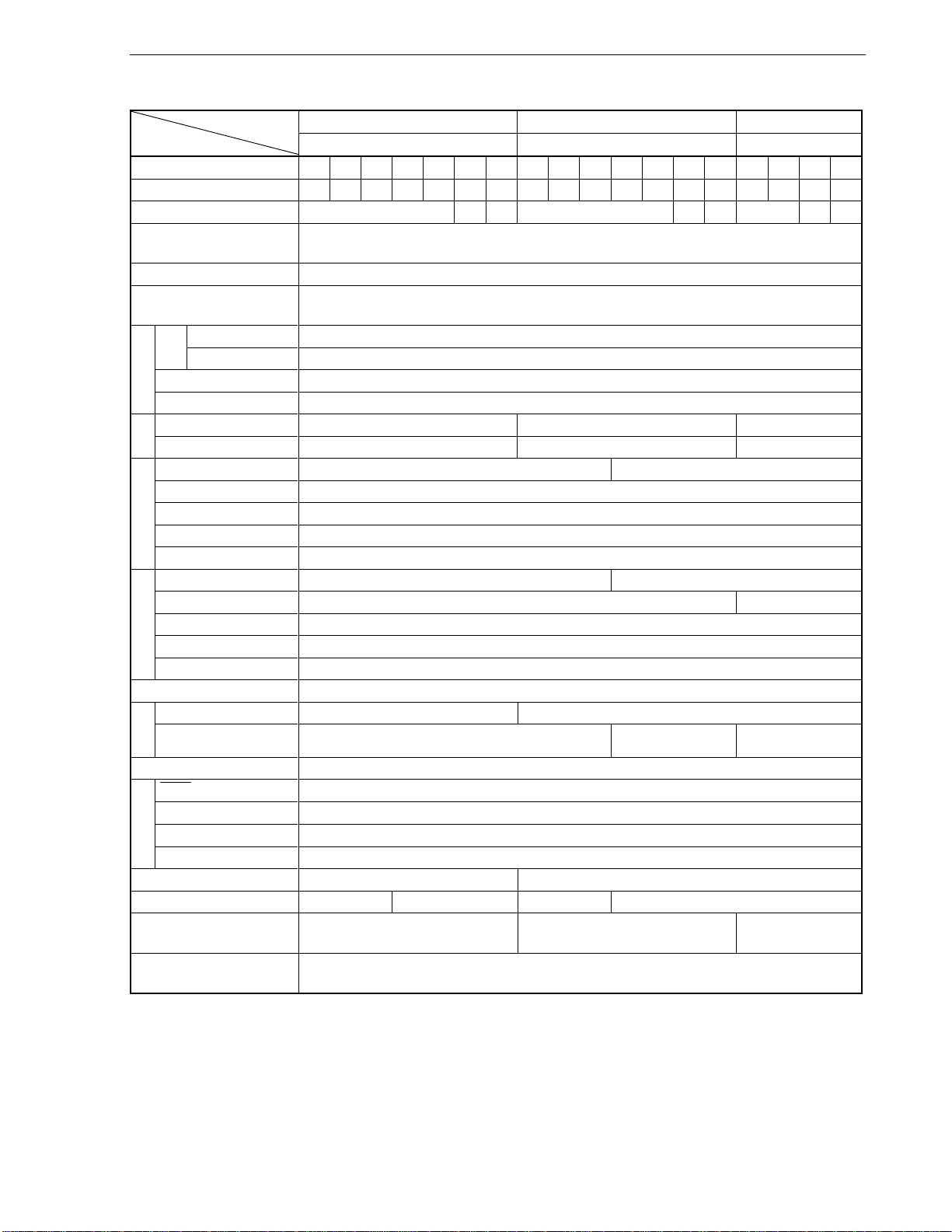

<R>

<R>

第一章 概述

(2/2)

产品型号

项目

flash 存储器(KB)

16 24 32 48 60 96 128 16 24 32 48 60 96 128 48 60 96 128

RAM (KB) 0.75 1 1 2 3 5 7 0.75 1 1 2 3 5 7 2 3 5 7

组(flash 存储器)

供电电压 标准产品,(A)级产品:VDD = 1.8 ~ 5.5 V

稳压器 提供

指令最短执行时间 0.1s (20 MHz: VDD = 4.0 ~ 5.5 V)/0.2s (10 MHz: VDD = 2.7 ~ 5.5 V)/

高速系统时钟 20 MHz: VDD = 4.0 ~ 5.5 V/10 MHz: VDD = 2.7 ~ 5.5 V/ 5 MHz: VDD = 1.8 ~ 5.5 V

时钟

内部高速振荡时钟 8 MHz (TYP.): VDD = 1.8 ~ 5.5 V

主系统

时钟

子系统时钟 32.768 kHz (TYP.): V DD = 1.8 ~ 5.5 V

内部低速振荡时钟 240 kHz (TYP.): VDD = 1.8 ~ 5.5 V

合计 45 55 71

端口

N-ch 开漏 (6 V 耐压)

16 位 (TM0) 1 通道 2 通道

8 位(TM5) 2 通道

8 位(TMH) 2 通道

定时器

钟表 1 通道

WDT 1 通道

3 线 CSI 1 通道

自动收发的 3 线 CSI 1 通道

UART/3 线 CSI

串行接口

支持 LIN 总线的 UART 1 通道

注

I2C 总线 1 通道

10-位 A/D 8 通道

外部

内部 16 19 20

中断

按键中断 8 通道

RESET 引脚 提供

POC

复位

LVI 可选择 16 个供电电压检测级别

WDT

时钟输出/蜂鸣器输出 仅有时钟输出 提供

乘法器/除法器 提供 提供

片上调试功能 仅适用于PD78F0527D 仅适用于PD78F0537D 仅适用于

工作环境温度 标准产品,(A)级产品:TA = – 40 ~ +85C

78K0/KD2 78K0/KE2 78K0/KF2

52 引脚 64 引脚 80 引脚

4 6 4 6 4 6

(A2)级产品:VDD = 2.7 ~ 5.5 V

0.4s (5 MHz: VDD = 1.8 ~ 5.5 V)

4 4 4

1 通道

8 9

1.59 V 0.15 V (上升到 1.8 V 的时间: 3.6 ms (最大值))

提供

PD78F0547D

(A2)级产品:TA = – 40 ~ +110C, TA = – 40 ~ +125C

注 选择这些复用功能引脚中的任意一种功能。

用户手册 U17260CA6V0UD 27

Page 28

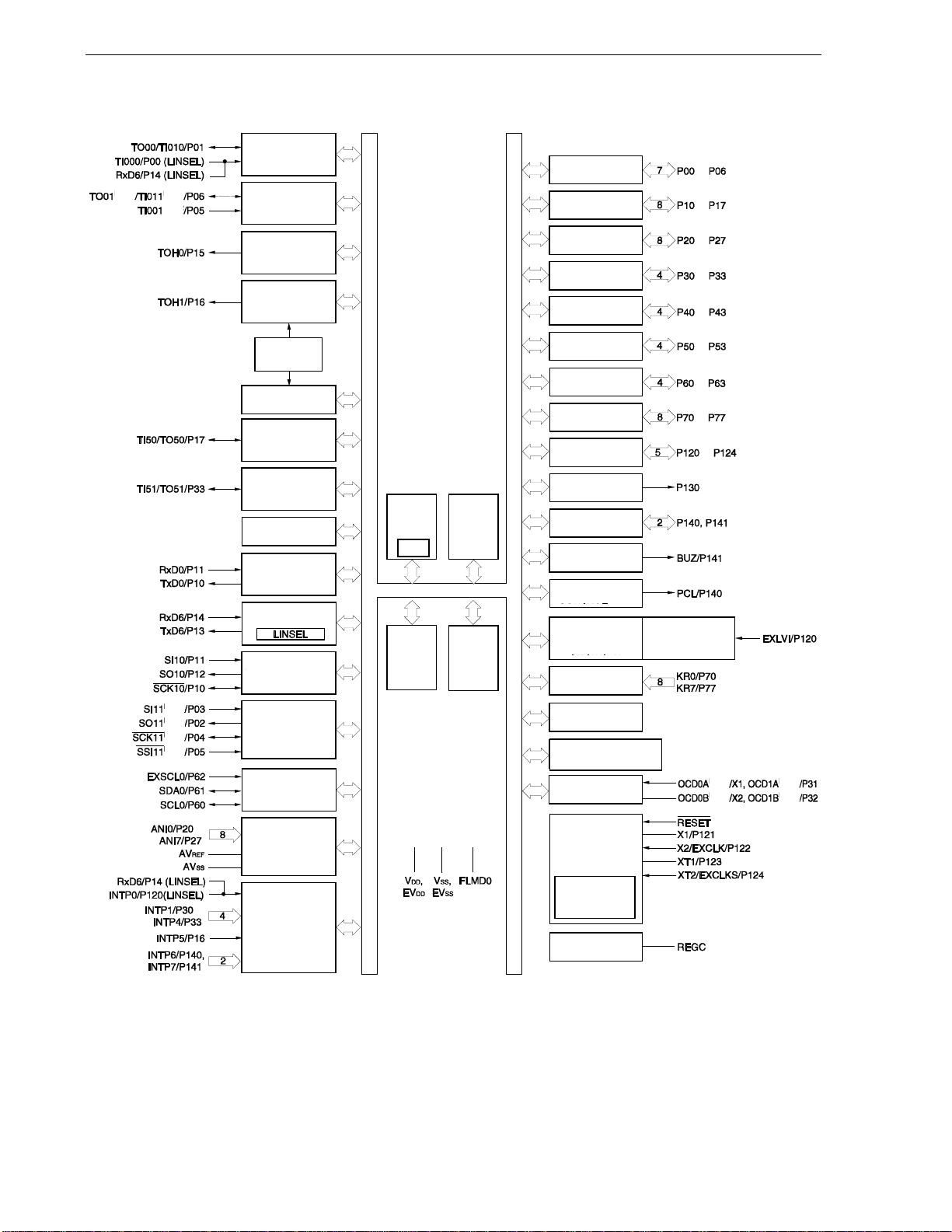

1.6 框图

~

2

3

3

3

3

~

2

注

第一章 概述

16 位定时器/

端口 0

注

注

16 位定时器/

事件计数器 01

端口 1

8位定时器 H0

端口 2

端口 3

8位定时器 H1

内部低速

振荡器

端口 4

端口 5

端口 6

看门狗定时器

端口 7

8位定时器/

事件计数器50

8位定时器/

事件计数器51

钟表定时器

CPU 核

存储器

串行接口

UART0

串行接口UART6

内部

串行接口

CSI10

注

注

注

注

串行接口

注2

CSI11

高速

RAM

内部

扩展

RAM

注

串行接口

端口 12

端口 13

端口 14

蜂鸣器输出

时钟输出控制

上电清零/低

电压指示器

按键返回

复位控制

乘法器&除法器

片上调试

注

控制

注

注

注

注

注

A/D转换

系统控制

内部高速

振荡器

中断控制

电压调节器

注 1. 仅适用于PD78F0536, 78F0537 和 78F0537D。

2. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537 和 78F0537D。

3. 仅适用于PD78F0537D。

用户手册 U17260CA6V0UD28

Page 29

<R>

<R>

<R>

第一章 概述

1.7 功能概述

(1/2)

项目

内部存储

器

Flash 存储器(支持自

注 1

编程)

存储器组

高速 RAM

扩展 RAM

注 2

注 1

注 1

存储器空间

主系统时钟

(振荡频

率)

高速系统时钟 X1 (晶体/陶瓷) 振荡器, 外部主系统时钟输入(EXCLK)

标准产品,

A)级产品

(A2)级产品

内部高速振荡时钟 内部振荡器

标准产品,

(A)级产品

(A2)级产品

副系统时钟 (振荡频率) XT1 (晶体) 振荡器,外部副系统时钟输入 (EXCLKS)

标准产品,

(A)级产品

(A2)级产品 32.768 kHz (典型值): VDD = 2.7 ~ 5.5 V

内部低速振荡时钟(用于 TMH1,

WDT)

标准产品,

(A)级产品

(A2)级产品 240 kHz (典型值): V DD = 2.7 ~ 5.5 V

通用寄存器 8 位 32 个寄存器 (8 位 8 个寄存器 4 组)

指令最短执行时间

指令集 • 8 位操作,16位操作

I/O 端口

注 1. 通过使用内部存储器容量切换寄存器(IMS)和内部扩展 RAM 容量切换寄存器(IXS),可以改变内部 flash

存储器,内部高速 RAM 容量和内部扩展 RAM 的容量。

2. 通过使用存储器 banks 选择寄存器(BANK)可以改变要使用的存储器 banks。

PD78F0531PD78F0532PD78F0533PD78F0534PD78F0535PD78F0536PD78F0537PD78F0537D

16 KB 24 KB 32 KB 48 KB 60 KB 96 KB 128 KB

4 banks 6 banks

768 字节 1 KB

1 KB 2 KB 4 KB 6 KB

64 KB

1 ~ 20 MHz: VDD = 4.0 ~ 5.5 V, 1 ~ 10 MHz: VDD = 2.7 ~ 5.5 V,

1 ~ 5 MHz: VDD = 1.8 ~ 5.5 V

1 ~ 20 MHz: VDD = 4.0 ~ 5.5 V, 1 ~ 10 MHz: VDD = 2.7 ~ 5.5 V

8 MHz (典型值): V DD = 1.8 ~ 5.5 V

8 MHz(典型值):VDD = 2.7 ~ 5.5 V

32.768 kHz (典型值): VDD = 1.8 ~ 5.5 V

内部振荡器

240 kHz (典型值): V DD = 1.8 ~ 5.5 V

0.1s (高速系统时钟: @ fXH = 20 MHz 操作)

0.25s (内部高速振荡时钟: @ fR H = 8 MHz (典型值) 操作)

122s (副系统时钟: @ fSUB = 32.768 kHz 操作)

• 乘/ 除(8 位 8 位, 16 位 8 位)

• 位操作( 置位,复位,测试和布尔操作)

• BCD 调整等。

合计: 55

CMOS I/O: 50

CMOS 输出: 1

N-ch 开漏 I/O (6 V 耐压): 4

用户手册 U17260CA6V0UD 29

Page 30

第一章 概述

项目

定时器 • 16 位定时器/ 事件计数器: 1 通

定时器输出 5 (PWM 输出: 4, PPG 输出:1)6 (PWM 输出: 4, PPG 输出 2)

PD78F0531PD78F0532PD78F0533PD78F0534PD78F0535PD78F0536PD78F0537PD78F0537D

道

• 8 位定时器/事件计数器: 2 通

道

• 8 位定时器: 2 通道

• 钟表定时器 : 1 通道

• 看门狗定时器 : 1 通道

(2/2)

• 16 位定时器/事件计数器: 2 通道

• 8 位定时器/事件计数器: 2 通道

• 8 位定时器: 2 通道

• 钟表定时器: 1通道

• 看门狗定时器: 1通道

时钟输出

蜂鸣器输出

A/D 转换器 10 位分辨率 8 通道 (AVREF = 2.3 ~ 5.5 V))

串行接口 • 支持 LIN 总线的 UART 模式: 1

乘法器/除法器 • 16 位 16 位 = 32 位 (乘法)

内部 16 19中断向量源

外部 9

按键中断 通过检测按键输入引脚(KR0 ~ KR7)的下降沿,产生按键中断 (INTKR)。

复位 • 使用 RESET 引脚复位

片上调试功能 无 提供

供电电压 • 标准产品,(A)级产品:VDD = 1.8 ~ 5.5 V

<R>

工作环境温度 • 标准产品,(A)级产品:TA = – 40 ~ +85C

<R>

封装形式 • 64 引脚塑封 LQFP (细脚距) (10 10)

• 156.25 kHz, 312.5 kHz, 625 kHz, 1.25 MHz, 2.5 MHz, 5 MHz, 10 MHz

(外围硬件时钟: @ fPRS = 20 MHz 操作)

• 32.768 kHz (副系统时钟: @ fSUB = 32.768 kHz 操作)

2.44 kHz, 4.88 kHz, 9.77 kHz, 19.54 kHz

(外围硬件时钟: @ fPRS = 20 MHz 操作)

• 支持 LIN 总线的 UART 模式: 1 通道

通道

• 3 线串行 I/O 模式 /UART 模式注:

1 通道

• I2C 总线模式: 1 通道

• 用看门狗定时器进行内部复位

• 用 POC 进行内部复位

• 用低电压检测电路进行内部复位

• (A2)级产品:VDD = 2.7 ~ 5.5 V

• (A2)级产品:TA = – 40 ~ +110C, TA = – 40 ~ +125C

• 64 引脚塑封 LQFP (14 14)

• 64 引脚塑封 LQFP (12 12)

• 64 引脚塑封 TQFP (细脚距) (7 7)

• 64 引脚塑封 FLGA (5 5)

• 3 线串行 I/O 模式/UART 模式注: 1 通道

• 3 线串行 I/O 模式: 1 通道

• I2C 总线模式: 1 通道

• 32 位 16 位= 32 位,余数 16 位(除法)

注 选择这些复用功能引脚中的任意一种功能。

用户手册 U17260CA6V0UD30

Page 31

定时器概要如下所示

第一章 概述

功能

16 位定时器/

事件计数器 00 和

注 1

01

TM00

TM01

注 1

8 位定时器/

事件计数器 50 和 51

TM50 TM51 TMH0 TMH1

间隔定时器 1 通道 1 通道 1 通道 1 通道 1 通道 1 通道 1 通道

外部事件计数器 1 通道 1 通道 1 通道 1 通道

8 位定时器 H0 和 H1

PPG 输出 1 输出 1 输出

PWM 输出

1 输出 1 输出 1 输出 1 输出

脉冲宽度测量 2 输入 2 输入

方波输出 1 输出 1 输出 1 输出 1 输出 1 输出 1 输出

载波发生器

钟表定时器

看门狗定时器

中断源

2 2 1 1 1 1 1

注 1. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537 和 78F0537D。

2. 对于钟表定时器,钟表定时器功能和间隔定时器功能可同时使用。

3. TM51 和 TMH1 可联合使用,用作载波发生器模式。

1 输出

钟表

定时器

看门狗

定时器

注 2

注 3

注 2

用户手册 U17260CA6V0UD 31

Page 32

第二章 引脚功能

2.1 引脚功能列表

有三种类型的引脚 I/O 缓冲器供电电源: AVREF, EVDD 和 VDD。下表显示了这些供电电源与引脚之间的关系。

表 2 -1. 引脚 I/O 缓冲器供电电源

供电电源 对应的引脚

AVREF P20 ~ P27

EVDD 端口引脚(P20 ~ P27 和 P121 ~ P124 除外)

VDD P121 ~ P124

引脚(端口引脚除外)

(1)端口功能(1/2)

功能名称

P00 TI000

P01 TI010/TO00

I/O

I/O

端口 0。

7 位 I/O 端口。

可以位选输入/输出模式。

P02

通过软件设置,可以定义内置上拉电阻的使用。

P03 SI11

P04

P05 TI001

P06

P10 SCK10/TxD0

P11 SI10/RxD0

P12 SO10

I/O 端口 1。

8 位 I/O 端口。

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

功能 复位后 复用功能

输入端口

注 1

SO11

注 1

注 1

SCK11

注 1

/

注 1

SSI11

注 1

TI011

/

注 1

TO01

输入端口

P13 TxD6

P14 RxD6

P15 TOH0

P16 TOH1/INTP5

P17

P20 ~ P27 I/O 端口 2。

模拟输入 ANI0 ~ ANI7

TI50/TO50

8 位 I/O 端口。

可以位选输入/输出模式。

P30 INTP1

I/O

P31

P32 INTP3/OCD1B

端口 3。

4 位 I/O 端口。

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

P33

输入端口

INTP2/OCD1A

TI51/TO51/INTP4

注 2

注 2

注 1. 仅适用于PD78F0534, 78F0535, 78F0536, 78F0537 和 78F0537D。

2. 仅适用于PD78F0537D

用户手册 U17260CA6V0UD32

Page 33

第二章 引脚功能

(1)端口功能 (2/2)

功能名称 I/O 功能 复位后 复用功能

P40 ~ P43 I/O 端口 4。

4 位 I/O 端口。

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

P50 ~ P53

I/O

端口 5。

4 位 I/O 端口。

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

P60 SCL0

P61 SDA0

P62 EXSCL0

I/O 端口 6 。

4 位 I/O 端口。

P60 ~ P63 输出是 N-ch 漏极开路输出(6V 耐压).

可以位选输入/输出模式。

输入端口

输入端口

输入端口

P63

P70 ~ P77 I/O 端口 7。

输入端口 KR0 ~ KR7

8 位 I/O 端口。

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

P120 INTP0/EXLVI

I/O

P121 X1/OCD0A

端口 12。

5 位 I/O 端口。

可以位选输入/输出模式。

P122

仅对于 P120,通过软件设置,可以定义内置上拉电阻的使用。

输入端口

X2/EXCLK/OCD0B

P123 XT1

P124

P130 输出 端口 13。

输出端口

XT2/EXCLKS

1 位仅输出端口。

P140 PCL/INTP6

I/O

P141

端口 14。

2 位 I/O 端口。

输入端口

BUZ/INTP7

可以位选输入/输出模式。

通过软件设置,可以定义内置上拉电阻的使用。

注 仅适用于PD78F0537D。

注

注

用户手册 U17260CA6V0UD 33

Page 34

第二章 引脚功能