Page 1

DATA SHEET

MOS INTEGRATED CIRCUIT

µ

PD784907, 784908

16-BIT SINGLE-CHIP MICROCONTROLLER

The µPD784907 and µPD784908 are products of the µPD784908 Subseries in the 78K/IV Series. These products

TM

contain various peripheral hardware such as IEBus

serial interface, and interrupt functions, as well as a high-speed, high-performance CPU.

µ

In addition, the

versions, and development tools are also available.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before

designing.

PD78P4908 (one-time PROM product), which is used to evaluate the functions of mask ROM

µ

PD784908 Subseries User's Manual Hardware : U11787E

78K/IV Series User's Manual Instruction : U10905E

controller, ROM, RAM, I/O ports, 8-bit resolution A/D, timers,

FEATURES

•78K/IV Series

•Minimum instruction execution time: 320 ns (at 6.29 MHz)

160 ns (at 12.58 MHz)

•Number of I/O ports: 80

•Timer/counters: 16-bit timer/counter × 3 units

16-bit timer × 1 unit

•Serial interface: 4 channels

UART/IOE (3-wire serial I/O): 2 channels

CSI (3-wire serial I/O): 2 channels

•PWM outputs: 2

•Standby function

HALT/STOP/IDLE mode

•Clock frequency division function

APPLICATIONS

Car audios, etc.

•Watchdog timer: 1 channel

•Clock output function

Selectable from f

CLK, fCLK/2, fCLK/4, fCLK/8, or fCLK/16

•A/D converter: 8-bit resolution × 8 channels

•On-chip IEBus controller

•Watch timer

•Low-power consumption

•Supply voltage: VDD = 4.0 to 5.5 V

(Main clock: f

internal system clock = f

CYK = 79 ns)

f

DD = 3.5 to 5.5 V

V

(Other than above, f

XX = 12.58 MHz,

XX,

CYK = 159 ns)

This document describes the µPD784908 unless otherwise specified.

The information in this document is subject to change without notice.

Document No. U11680EJ2V0DS00 (2nd edition)

Date Published February 1999 N CP(K)

Printed in Japan

The mark shows major revised points.

©

1996

Page 2

µ

PD784907, 784908

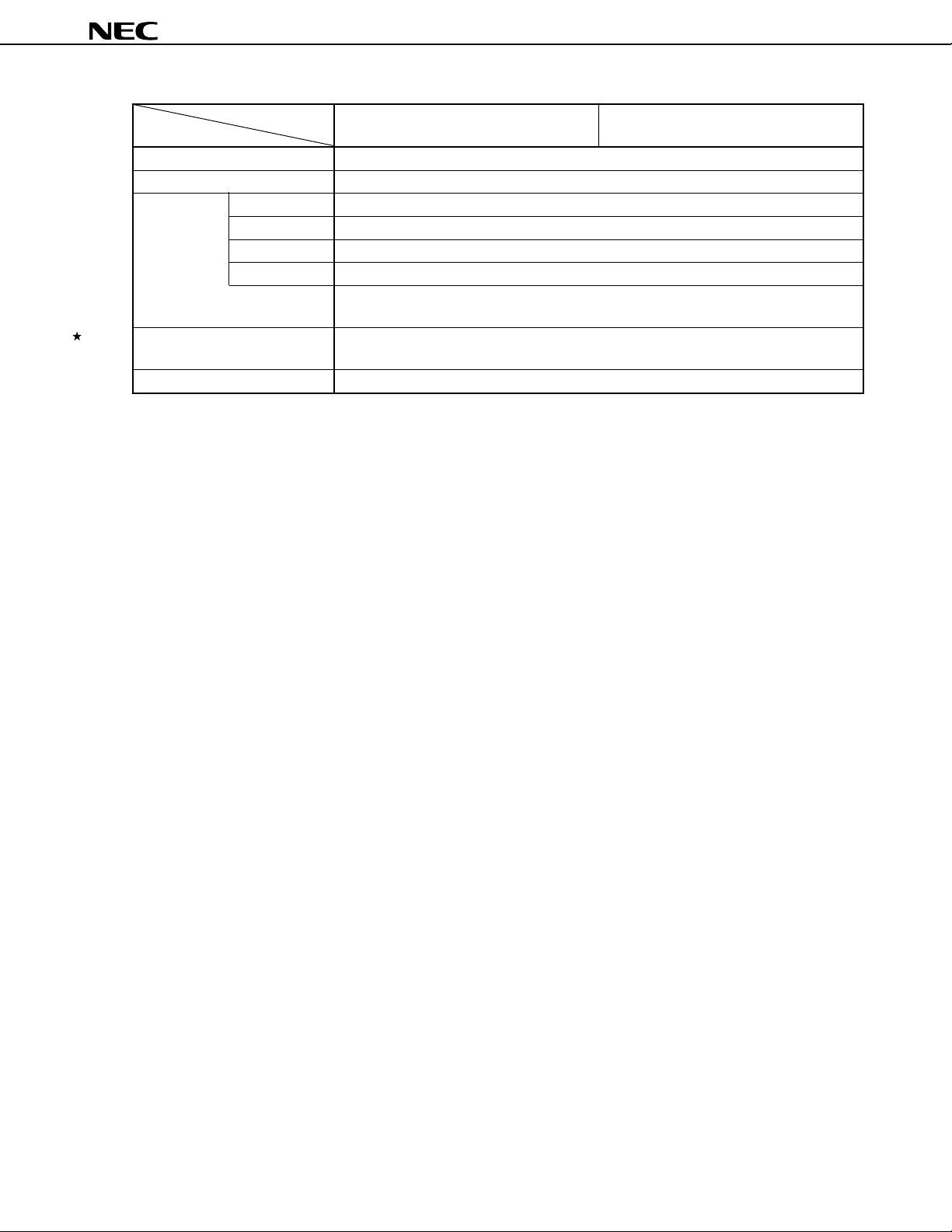

ORDERING INFORMATION

Part number Package Internal ROM Internal RAM

(bytes) (bytes)

µ

PD784907GF-×××-3BA 100-pin plastic QFP (14 × 20 mm) 96 K 3,584

µ

PD784908GF-×××-3BA 100-pin plastic QFP (14 × 20 mm) 128 K 4,352

Remark ××× indicates ROM code suffix.

2

Data Sheet U11680EJ2V0DS00

Page 3

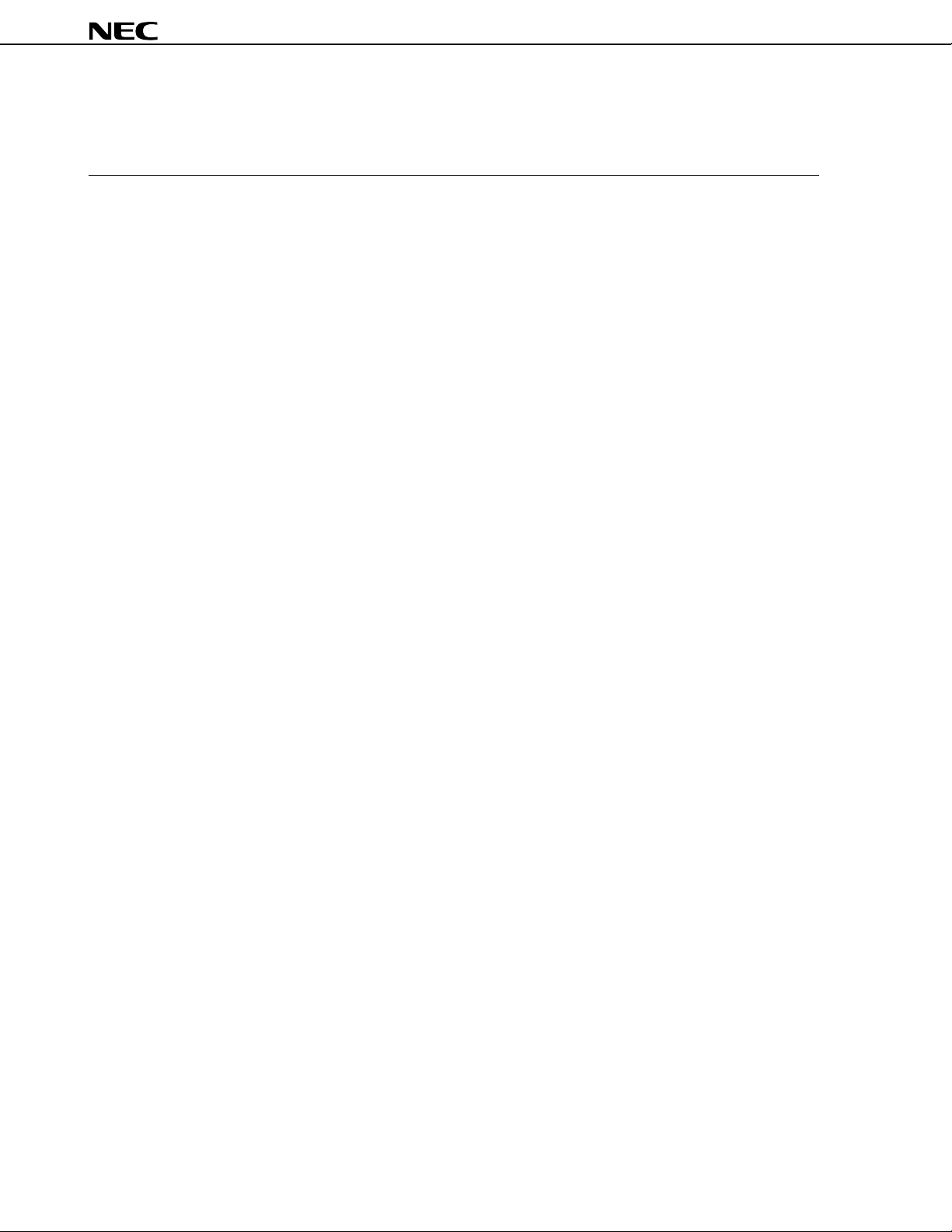

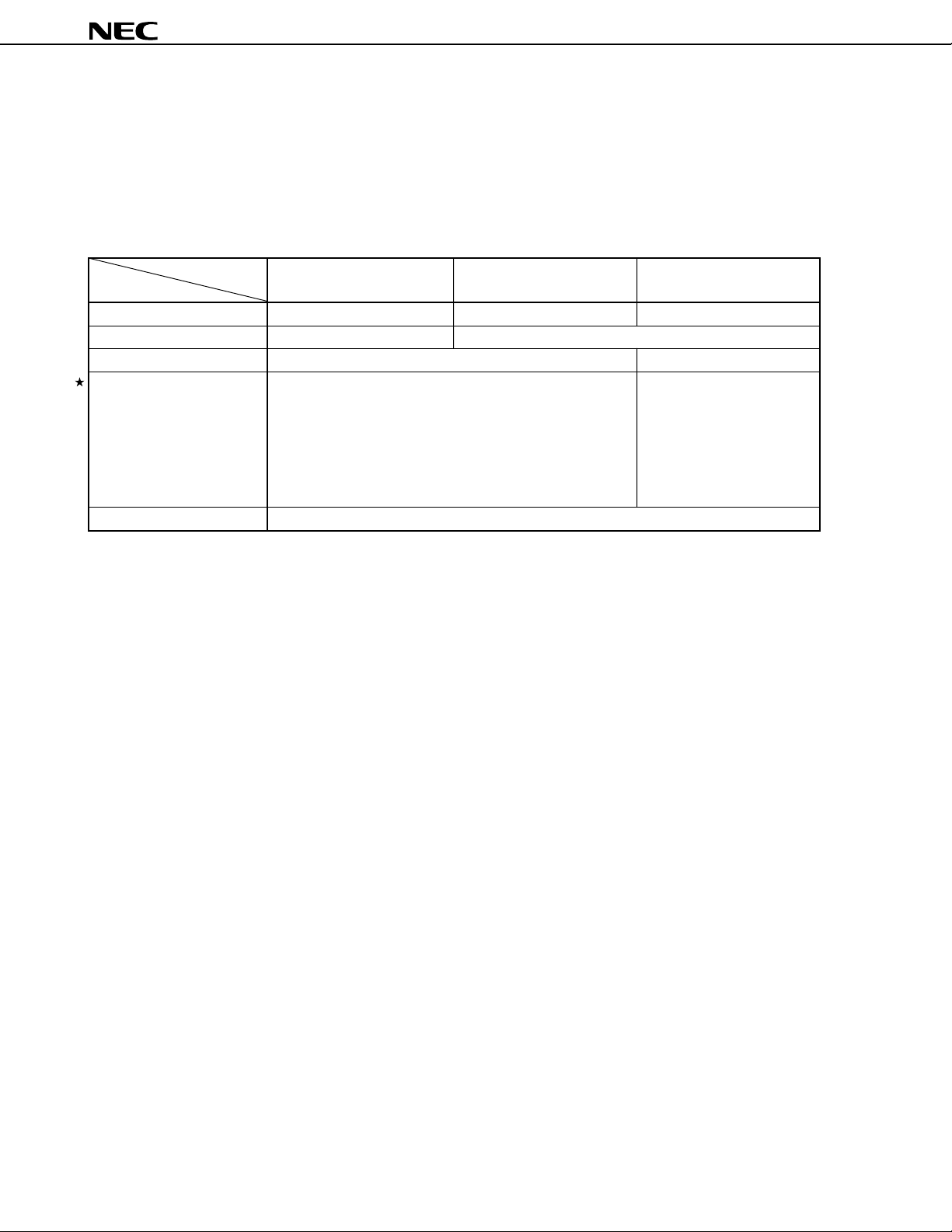

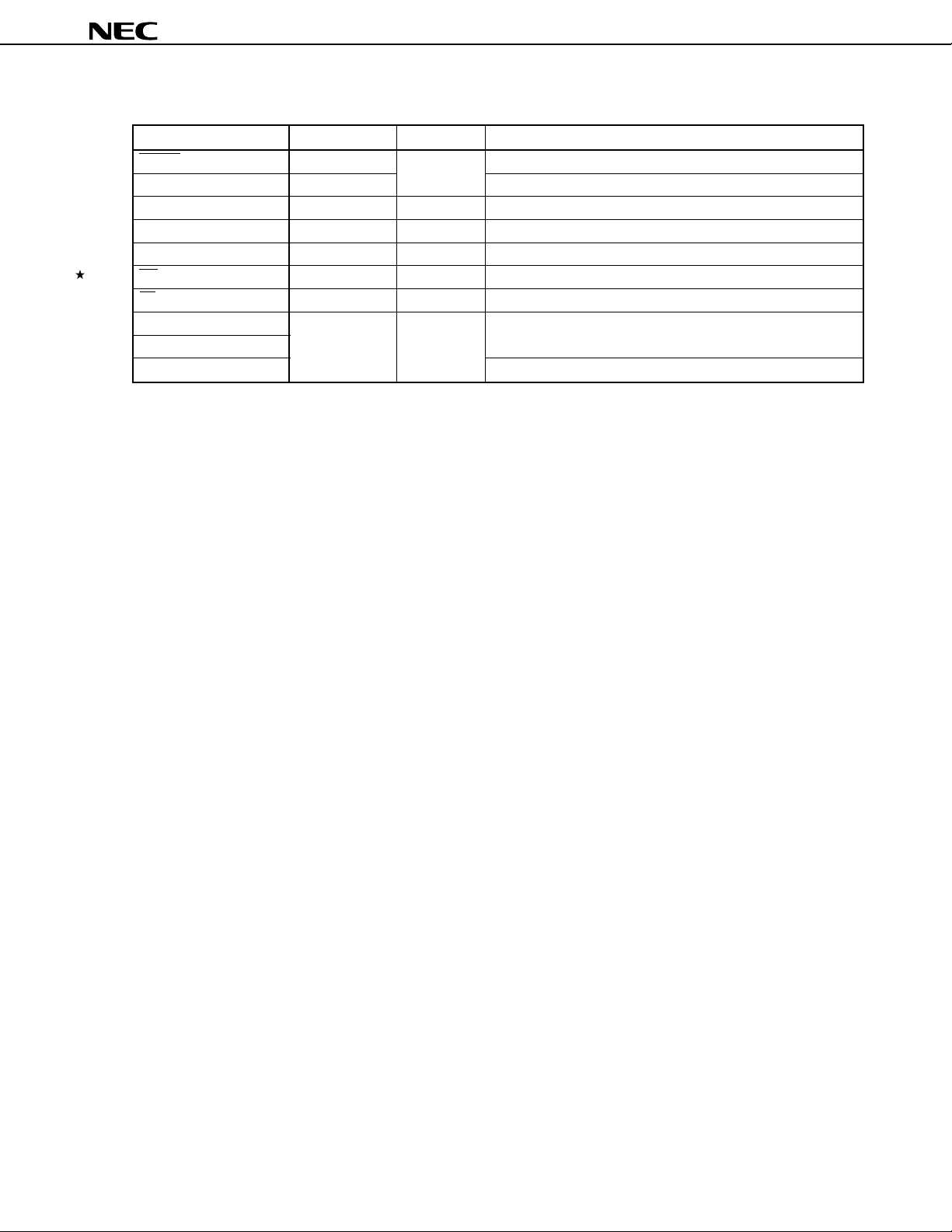

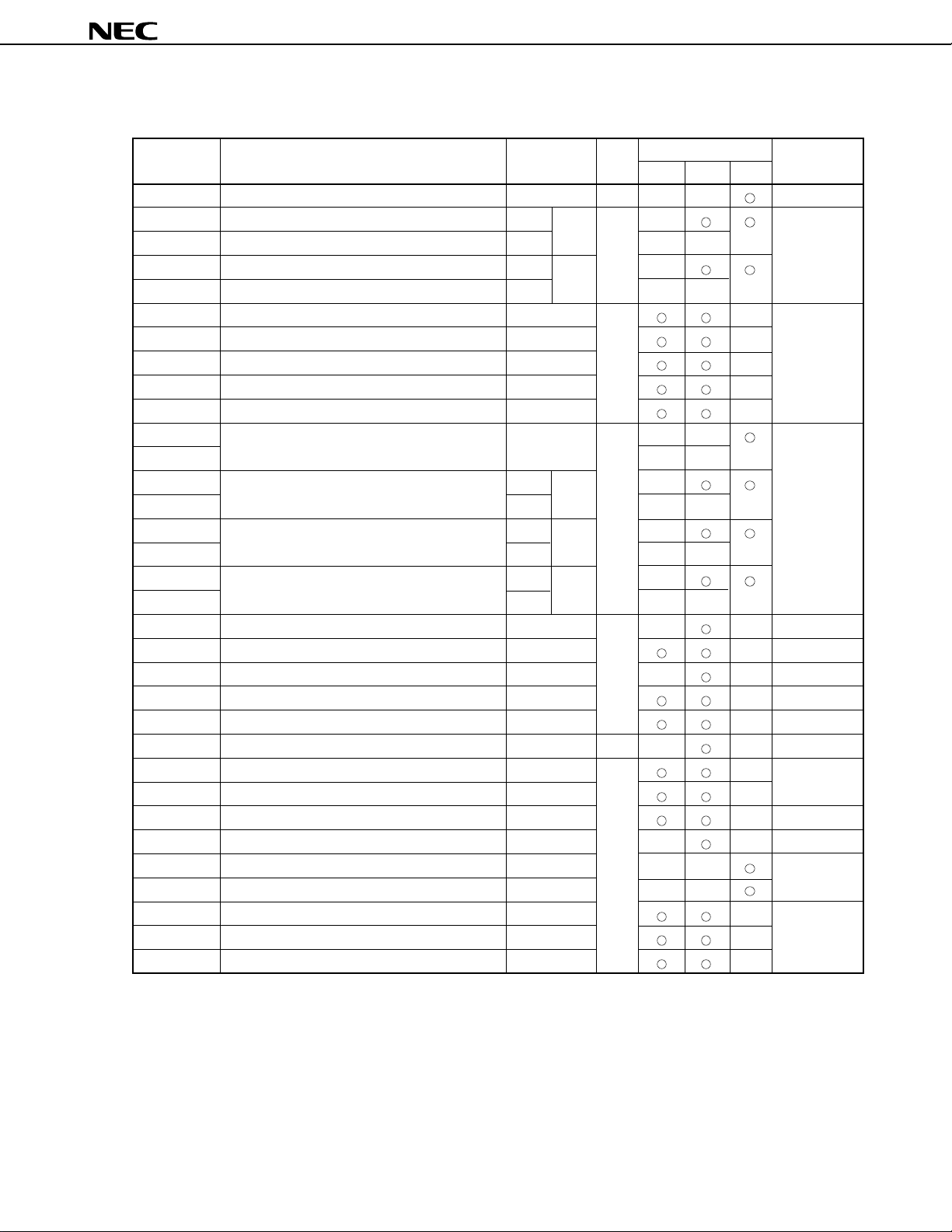

78K/IV SERIES PRODUCT LINEUP

: Under mass production

: Under development

µ

PD784907, 784908

Standard models

PD784026

µ

Enhanced A/D,

16-bit timer,

and power

management

ASSP models

PD784955

µ

For DC inverter control

PD784908

µ

On-chip IEBus

controller

I2C bus supported

PD784038Y

µ

PD784038

µ

Enhanced internal memory capacity,

pin compatible with the PD784026

µ

PD784216Y

µ

PD784216

100 pins,

enhanced I/O and

internal memory capacity

µ

PD784054

µ

PD784046

On-chip 10-bit A/D

PD784938

µ

Enhanced functions of the PD784908,

enhanced internal memory capacity,

ROM correction added

µ

µ

Multi-master I2C bus supported

PD784225Y

µ

PD784225

µ

80 pins,

ROM correction added

Multi-master I2C bus supportedMulti-master I2C bus supported

PD784218Y

µ

PD784218

µ

Enhanced internal memory capacity,

ROM correction added

µ

PD784915

For software servo control,

on-chip analog circuit

for VCR,

enhanced timer

Multi-master I2C bus supported

PD784928Y

µ

PD784928

µ

Enhanced functions of the PD784915

µ

3Data Sheet U11680EJ2V0DS00

Page 4

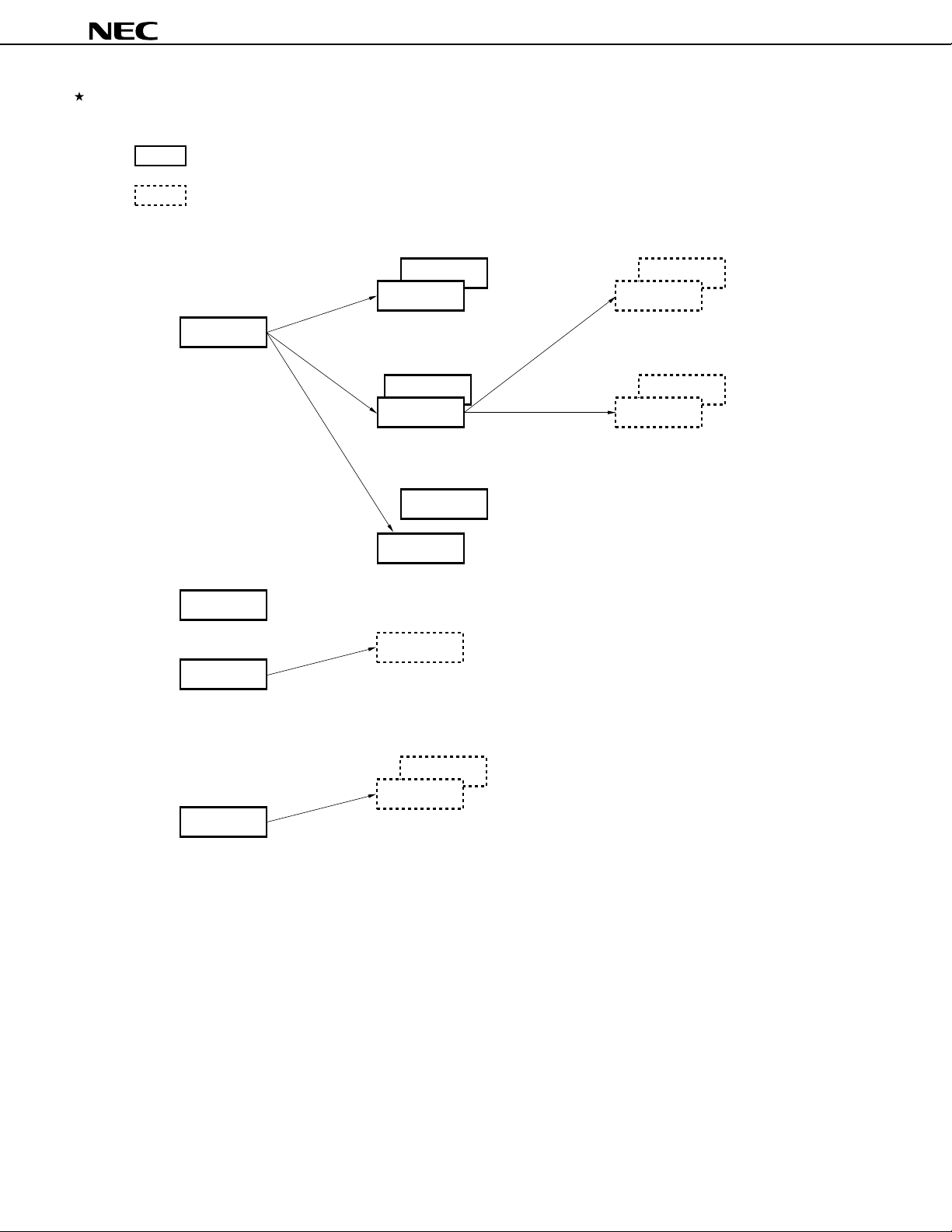

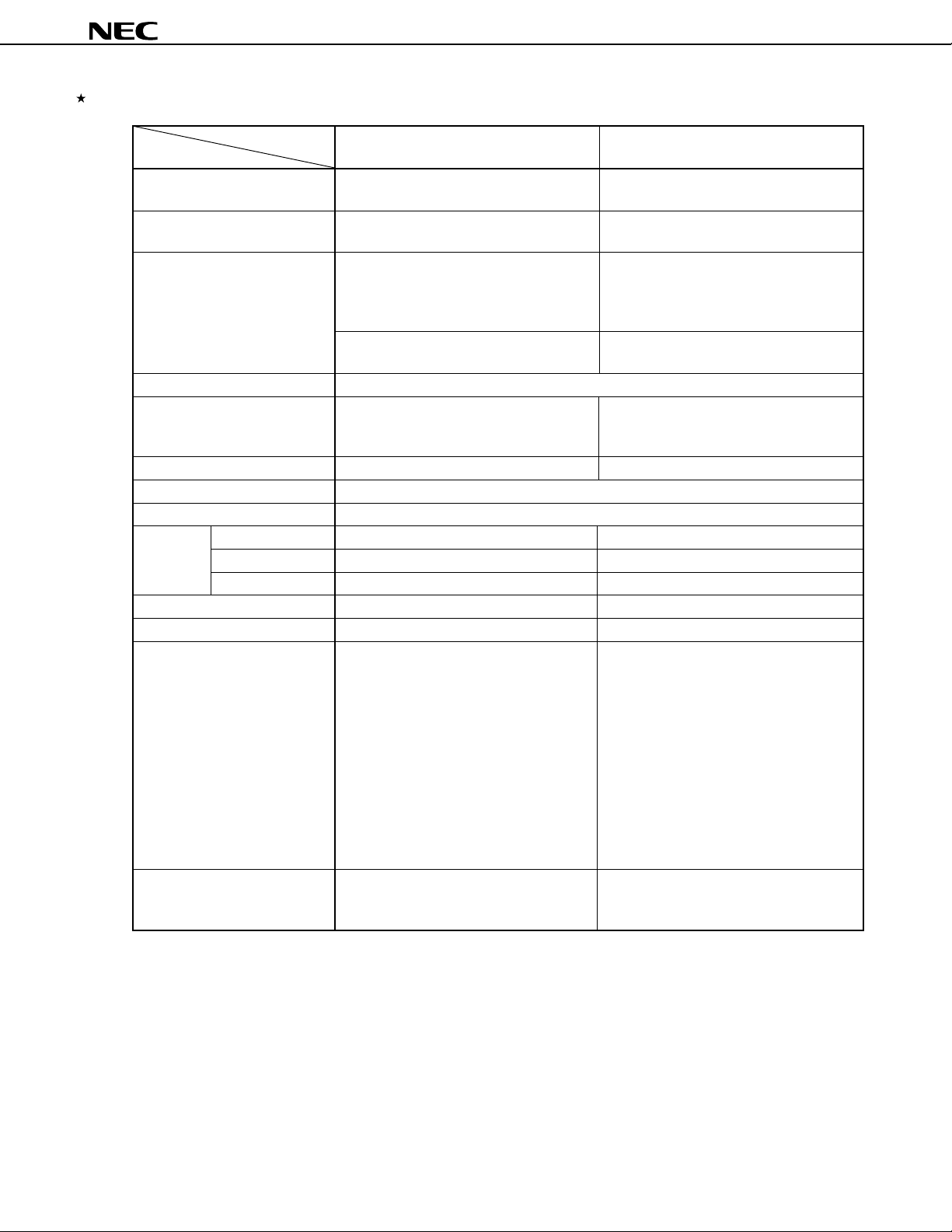

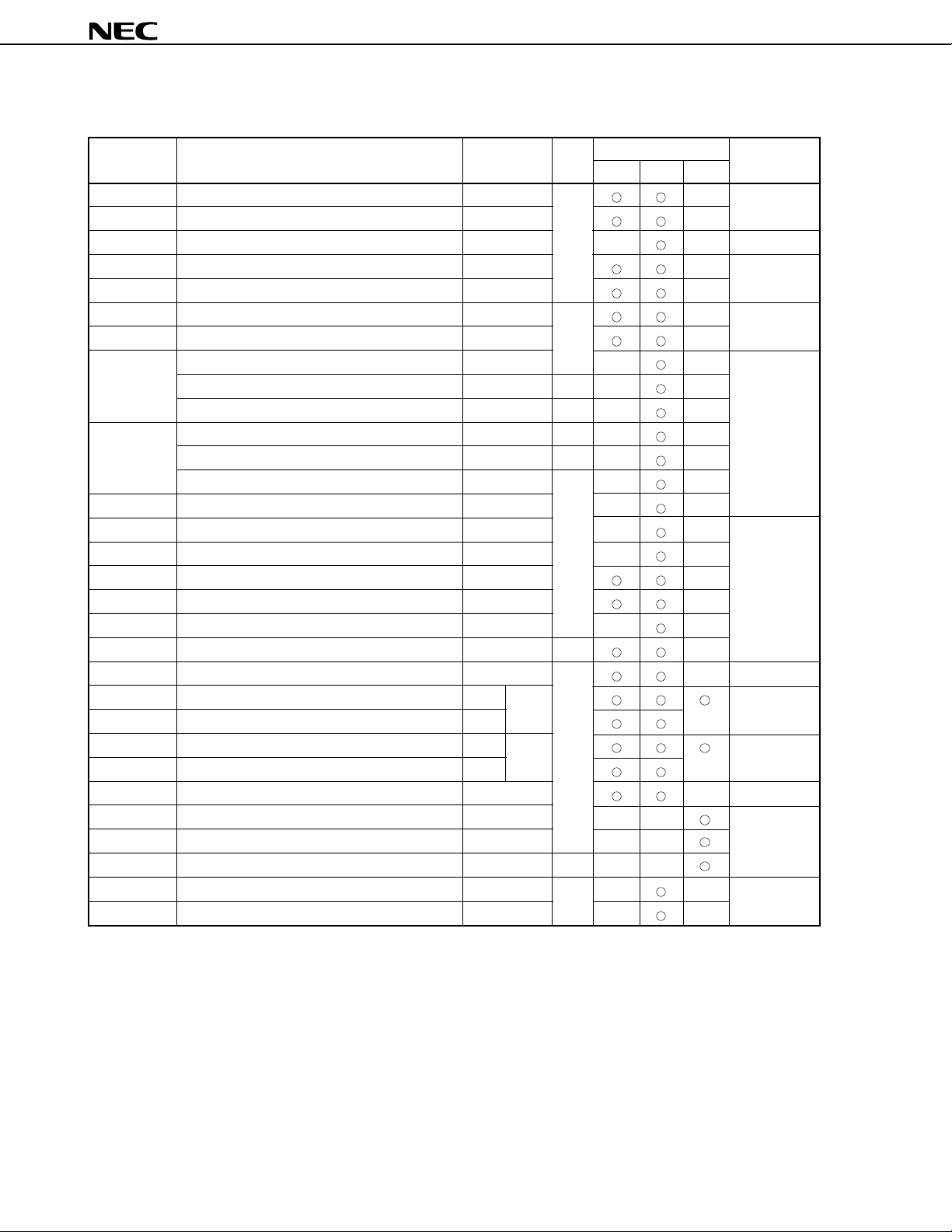

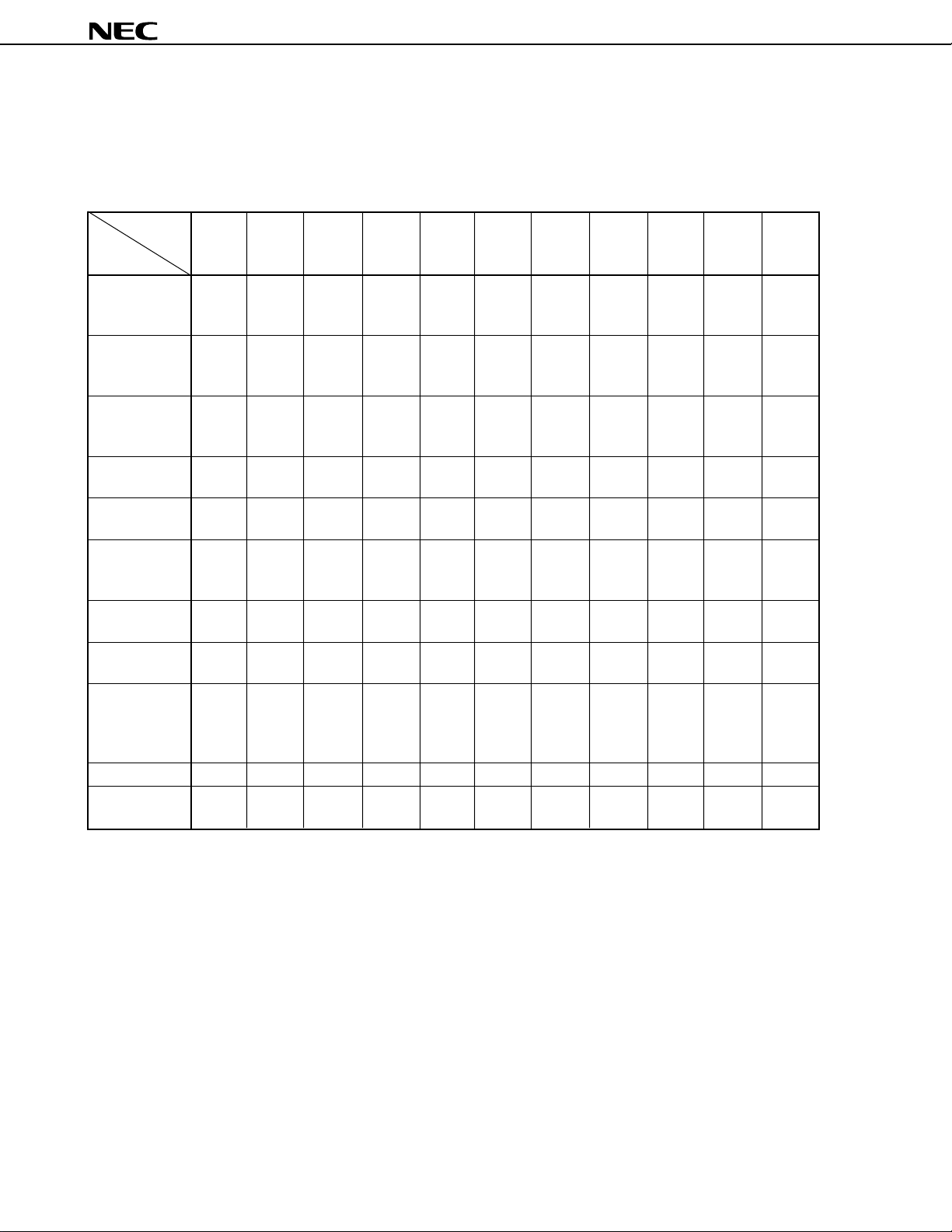

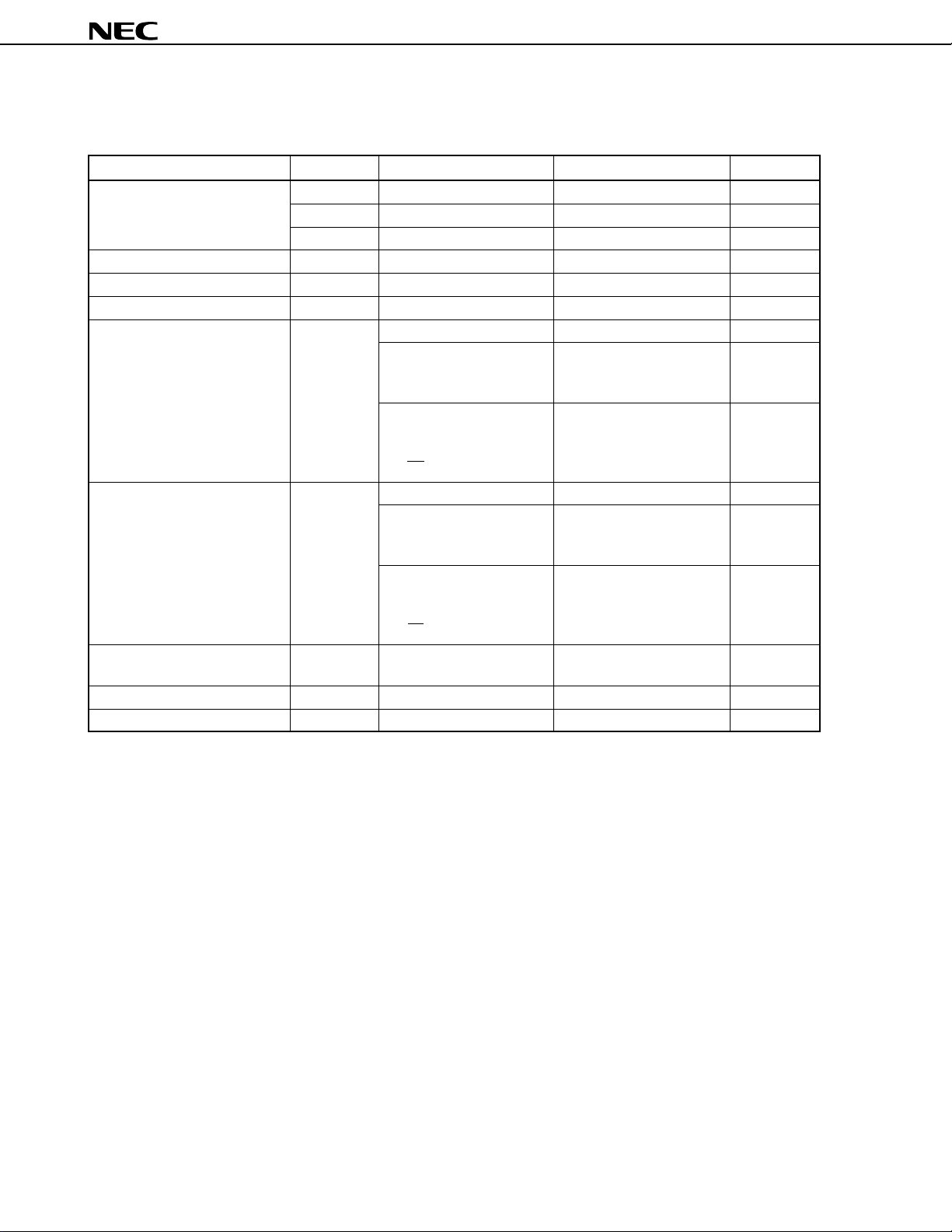

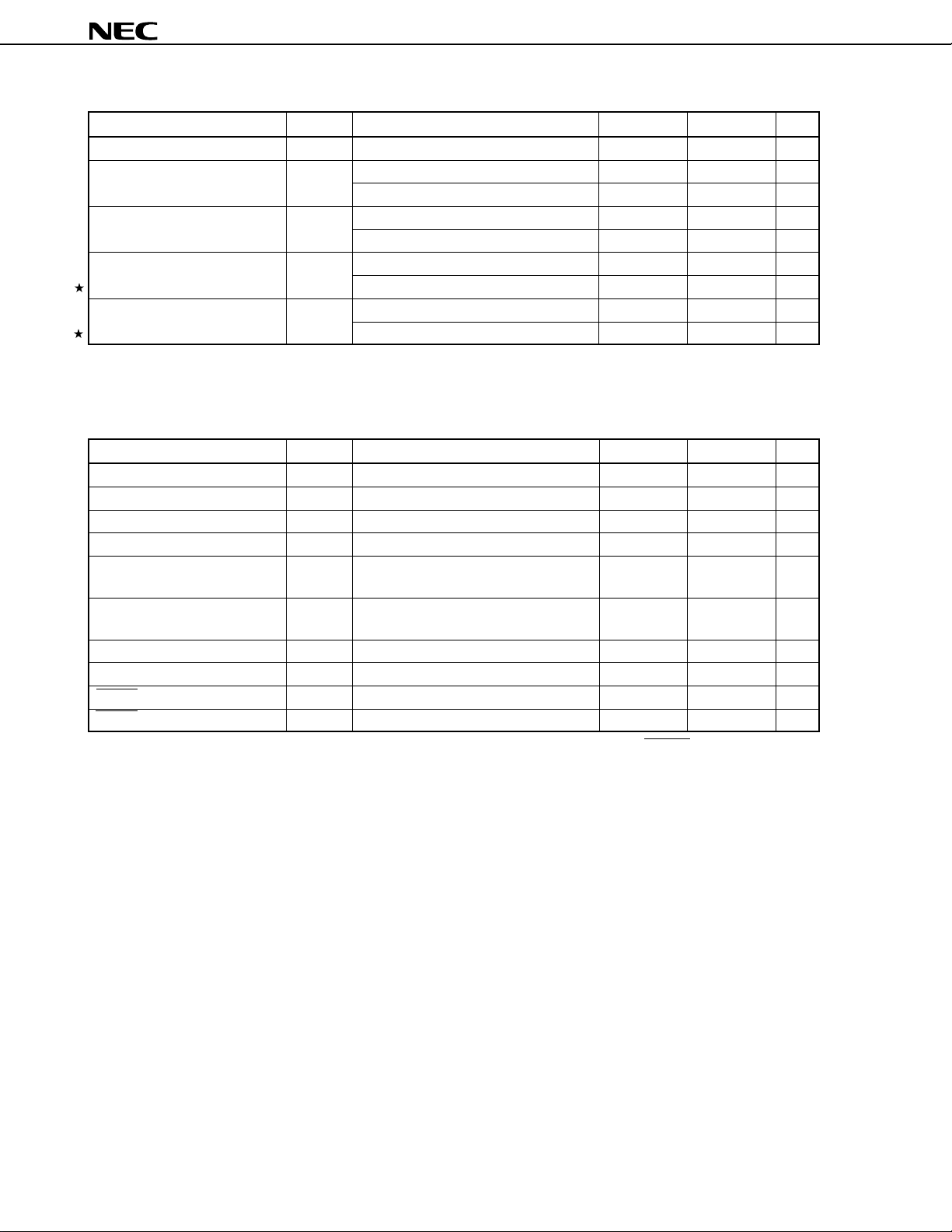

FUNCTIONS

µ

PD784907, 784908

Part Number

Item

Number of basic instructions 113

(mnemonics)

General-purpose register 8 bits × 16 registers × 8 banks, or 16 bits × 8 registers × 8 banks (memory mapping)

Minimum instruction execution 320 ns/636 ns/1.27 µs/2.54 µs (at 6.29 MHz)

time 160 ns/320 ns/636 ns/1.27 µs (at 12.58 MHz)

Internal ROM 96 K 128 K

memory

Memory space 1 Mbyte with program and data spaces combined

I/O ports Total 80

Additional LED direct 24

function drive outputs

Note

pins

Real-time output ports 4 bits × 2, or 8 bits × 1

IEBus controller Incorporated (simplified)

Timer/counter Timer/counter 0: Timer register × 1 Pulse output capability

Watch timer Interrupt requests are generated at 0.5-second intervals. (A watch clock oscillator is

Clock output Selectable from fCLK, fCLK/2, fCLK/4, fCLK/8, or fCLK/16 (can be used as a 1-bit output port)

PWM outputs 12-bit resolution × 2 channels

Serial interface UART/IOE (3-wire serial I/O):2 channels (on-chip baud rate generator)

A/D converter 8-bit resolution × 8 channels

RAM 3,584 bytes 4,352 bytes

Input 8

Input/output 72

Transistor 8

direct drive

N-ch open 4

drain

(16 bits) Capture register × 1 • Toggle output

Timer/counter 1: Timer register × 1 Real-time output port

(16 bits) Capture register × 1

Timer/counter 2: Timer register × 1 Pulse output capability

(16 bits) Capture register × 1 • Toggle output

Timer 3: Timer register × 1

(16 bits) Compare register × 1

incorporated.)

Either the main clock (6.29 MHz/12.58 MHz) or watch clock (32.7 kHz) can be selected

as the input clock.

CSI (3-wire serial I/O): 2 channels

µ

PD784907

Compare register × 2 • PWM/PPG output

Capture/compare register × 1

Compare register × 1

Capture/compare register × 1 • PWM/PPG output

Compare register × 1

µ

PD784908

• One-shot pulse output

Note Additional function pins are included in the I/O pins.

4

Data Sheet U11680EJ2V0DS00

Page 5

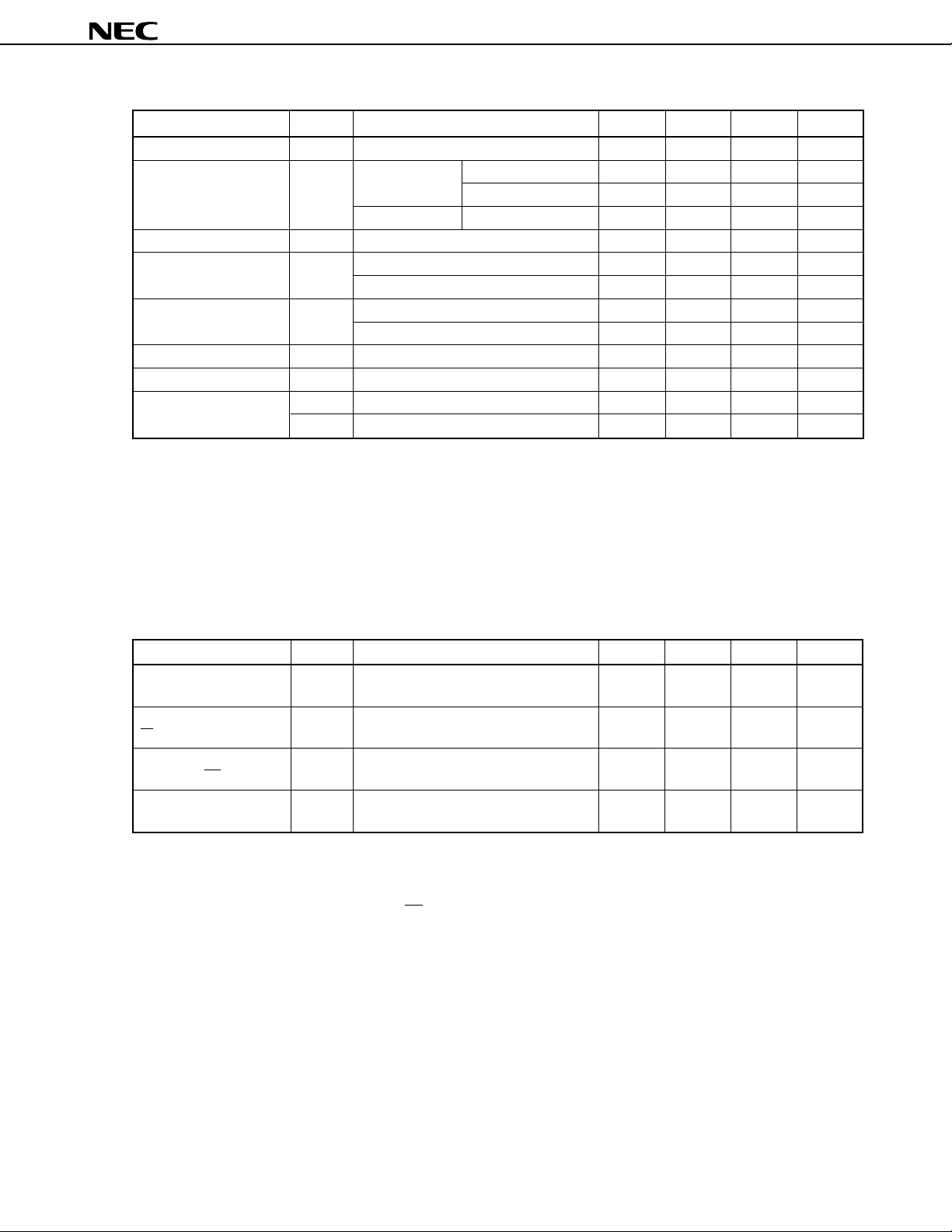

µ

PD784907, 784908

Part Number

Item

Watchdog timer 1 channel

Standby HALT/STOP/IDLE modes

Interrupt Hardware source 27 (20 internal, 7 external (sampling clock variable input: 1))

Software source BRK or BRKCS instruction, operand error

Non-maskable 1 internal, 1 external

Maskable 19 internal, 6 external

4-level programmable priority

3 operation statuses: vectored interrupt, macro service, context switching

Power supply voltage VDD = 4.0 to 5.5 V (Main clock: fXX = 12.58 MHz, internal system clock = fXX, fCYK = 79 ns)

VDD = 3.5 to 5.5 V (other than above, fCYK = 159 ns)

Package 100-pin plastic QFP (14 × 20 mm)

µ

PD784907

µ

PD784908

5Data Sheet U11680EJ2V0DS00

Page 6

µ

PD784907, 784908

CONTENTS

1. DIFFERENCES BETWEEN µPD784908 SUBSERIES PRODUCTS....................................... 8

2. MAJOR DIFFERENCES BETWEEN µPD784908 AND µPD78098 SUBSERIES .................. 9

3. PIN CONFIGURATION (TOP VIEW) ......................................................................................... 10

4. SYSTEM CONFIGURATION EXAMPLE (AUTOMOTIVE CAR AUDIO (TUNER DECK))..... 12

5. BLOCK DIAGRAM ..................................................................................................................... 13

6. PIN FUNCTION........................................................................................................................... 14

6.1 Port Pins............................................................................................................................................ 14

6.2 Non-Port Pins ................................................................................................................................... 16

6.3 Pin I/O Circuits and Recommended Connections of Unused Pins .......................................... 18

7. CPU ARCHITECTURE ............................................................................................................... 2 2

7.1 Memory Space .................................................................................................................................. 22

7.2 CPU Registers .................................................................................................................................. 25

7.2.1 General-purpose registers................................................................................................ 2 5

7.2.2 Control registers ................................................................................................................ 26

7.2.3 Special function registers (SFRs).................................................................................... 27

8. PERIPHERAL HARDWARE FUNCTIONS................................................................................ 33

8.1 Ports................................................................................................................................................... 33

8.2 Clock Generator ............................................................................................................................... 35

8.3 Real-Time Output Port ..................................................................................................................... 38

8.4 Timers/Counters............................................................................................................................... 39

8.5 Watch Timer...................................................................................................................................... 41

8.6 PWM Output (PWM0, PWM1) .......................................................................................................... 42

8.7 A/D Converter ................................................................................................................................... 43

8.8 Serial Interface ................................................................................................................................. 44

8.8.1 Asynchronous serial interface/3-wire serial I/O (UART/IOE) ....................................... 45

8.8.2 Clocked serial interface (CSI)........................................................................................... 47

8.9 Clock Output Function .................................................................................................................... 48

8.10 Edge Detection Function ................................................................................................................ 49

8.11 Watchdog Timer............................................................................................................................... 49

8.12 Simplified IEBus Controller............................................................................................................ 50

9. INTERRUPT FUNCTION............................................................................................................ 53

9.1 Interrupt Source ............................................................................................................................... 53

9.2 Vectored Interrupt............................................................................................................................ 55

9.3 Context Switching............................................................................................................................ 56

9.4 Macro Service ................................................................................................................................... 56

9.5 Examples of Macro Service Applications .................................................................................... 5 7

6

Data Sheet U11680EJ2V0DS00

Page 7

µ

PD784907, 784908

10. LOCAL BUS INTERFACE ......................................................................................................... 59

10.1 Memory Expansion .......................................................................................................................... 59

10.2 Memory Space.................................................................................................................................. 60

10.3 Programmable Wait ......................................................................................................................... 6 1

10.4 Pseudo-Static RAM Refresh Function .......................................................................................... 61

10.5 Bus Hold Function........................................................................................................................... 6 1

11. STANDBY FUNCTION ............................................................................................................... 62

12. RESET FUNCTION..................................................................................................................... 63

13. REGULATOR.............................................................................................................................. 64

14. INSTRUCTION SET .................................................................................................................... 65

15. ELECTRICAL SPECIFICATIONS.............................................................................................. 70

16. PACKAGE DRAWING ................................................................................................................ 8 9

17. RECOMMENDED SOLDERING CONDITIONS ........................................................................ 90

APPENDIX A DEVELOPMENT TOOLS .......................................................................................... 91

APPENDIX B RELATED DOCUMENTS ......................................................................................... 94

7Data Sheet U11680EJ2V0DS00

Page 8

µ

PD784907, 784908

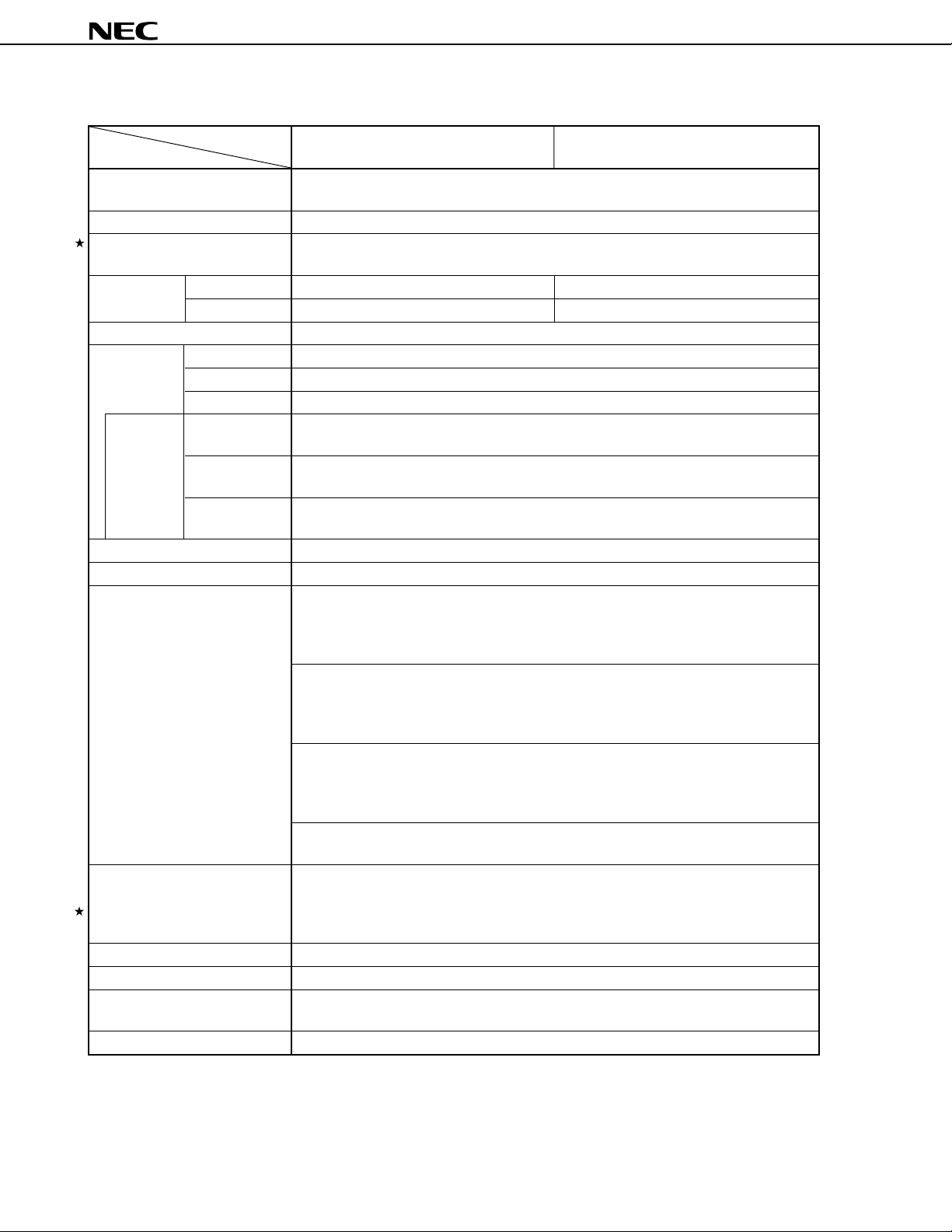

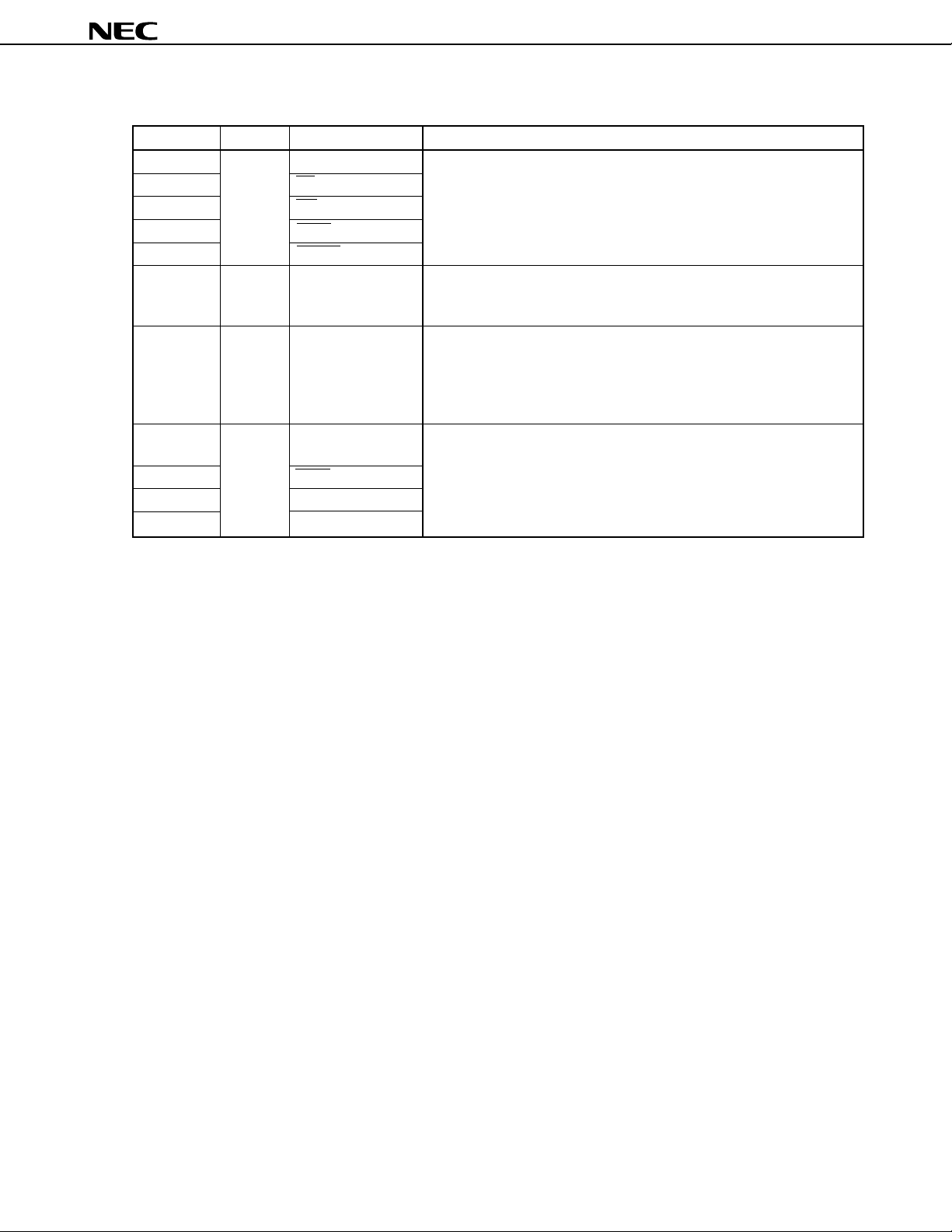

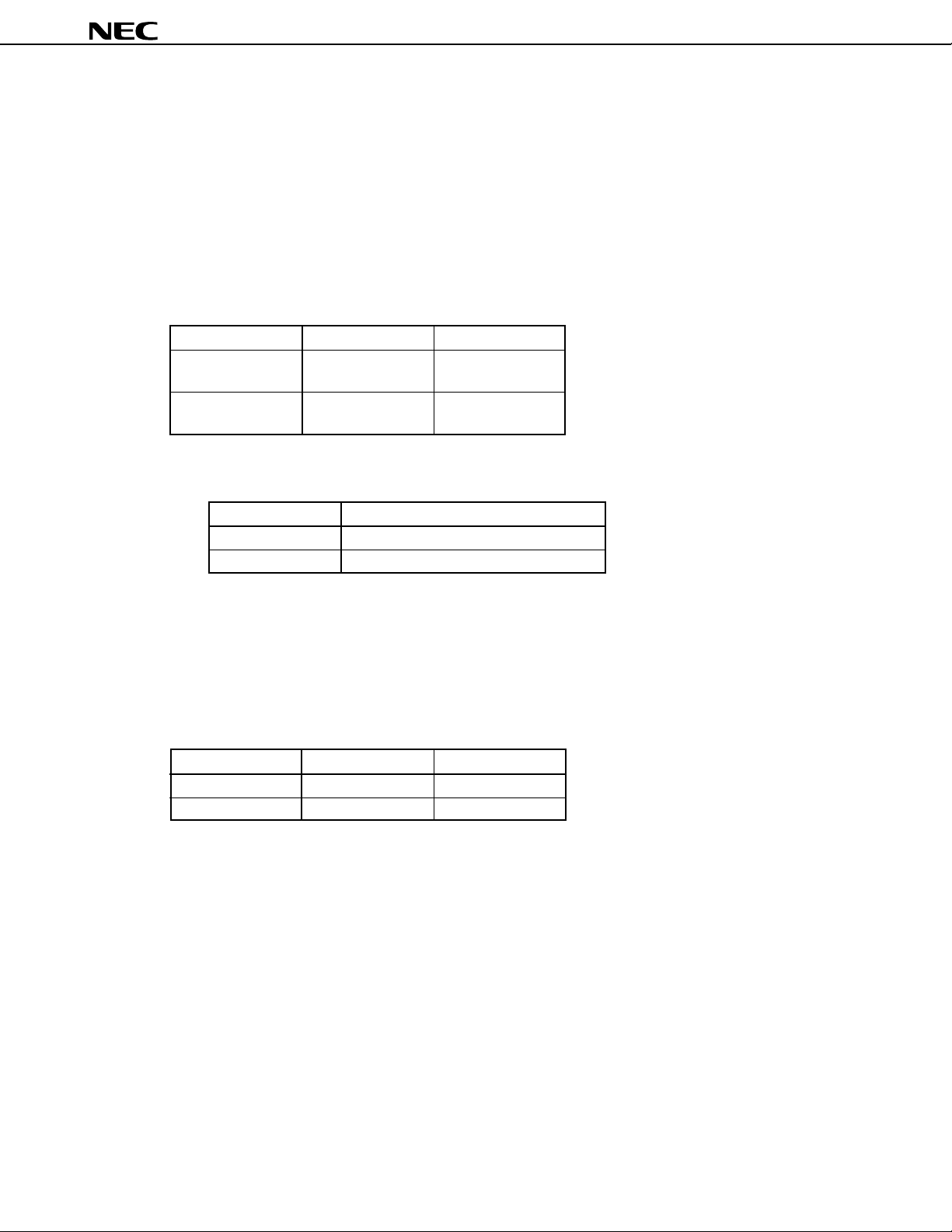

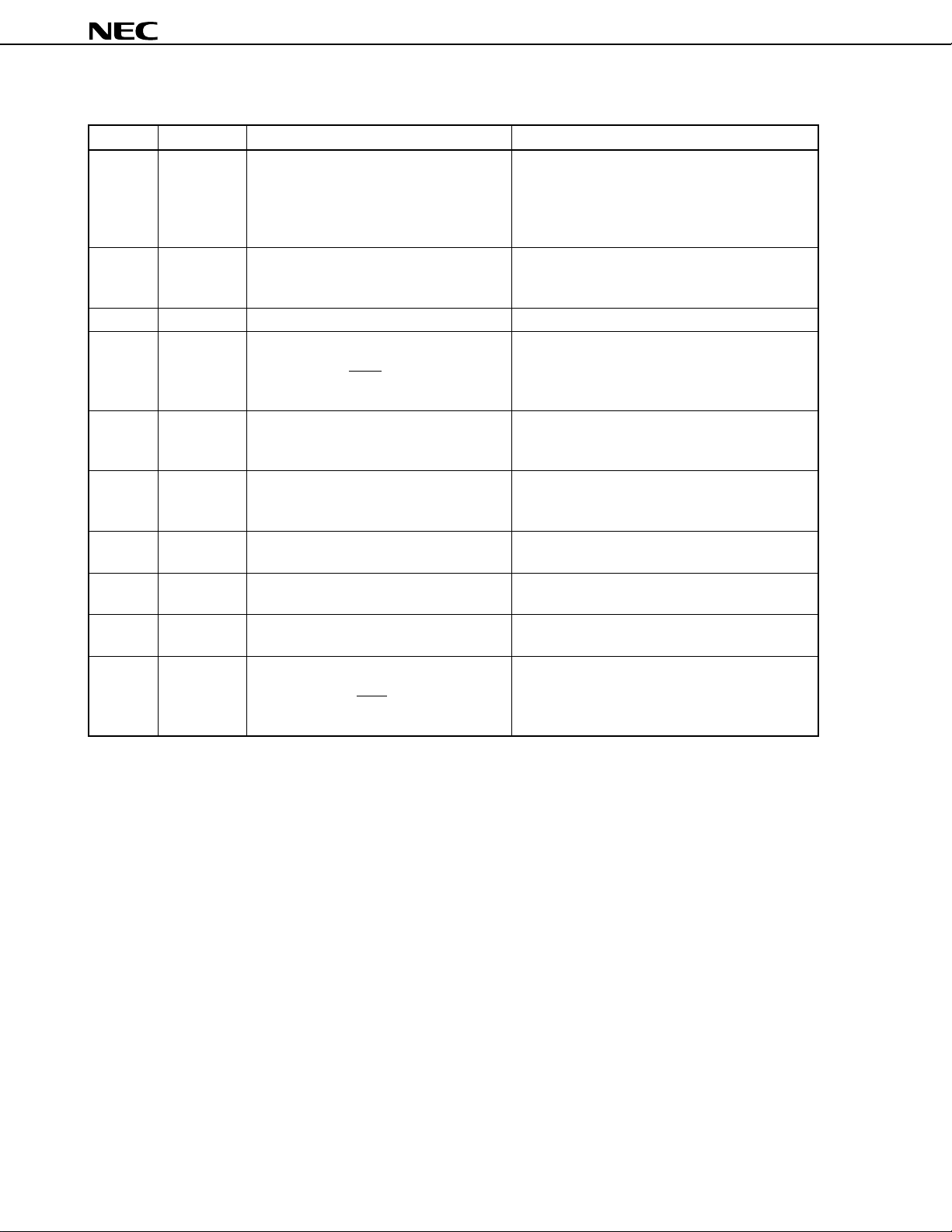

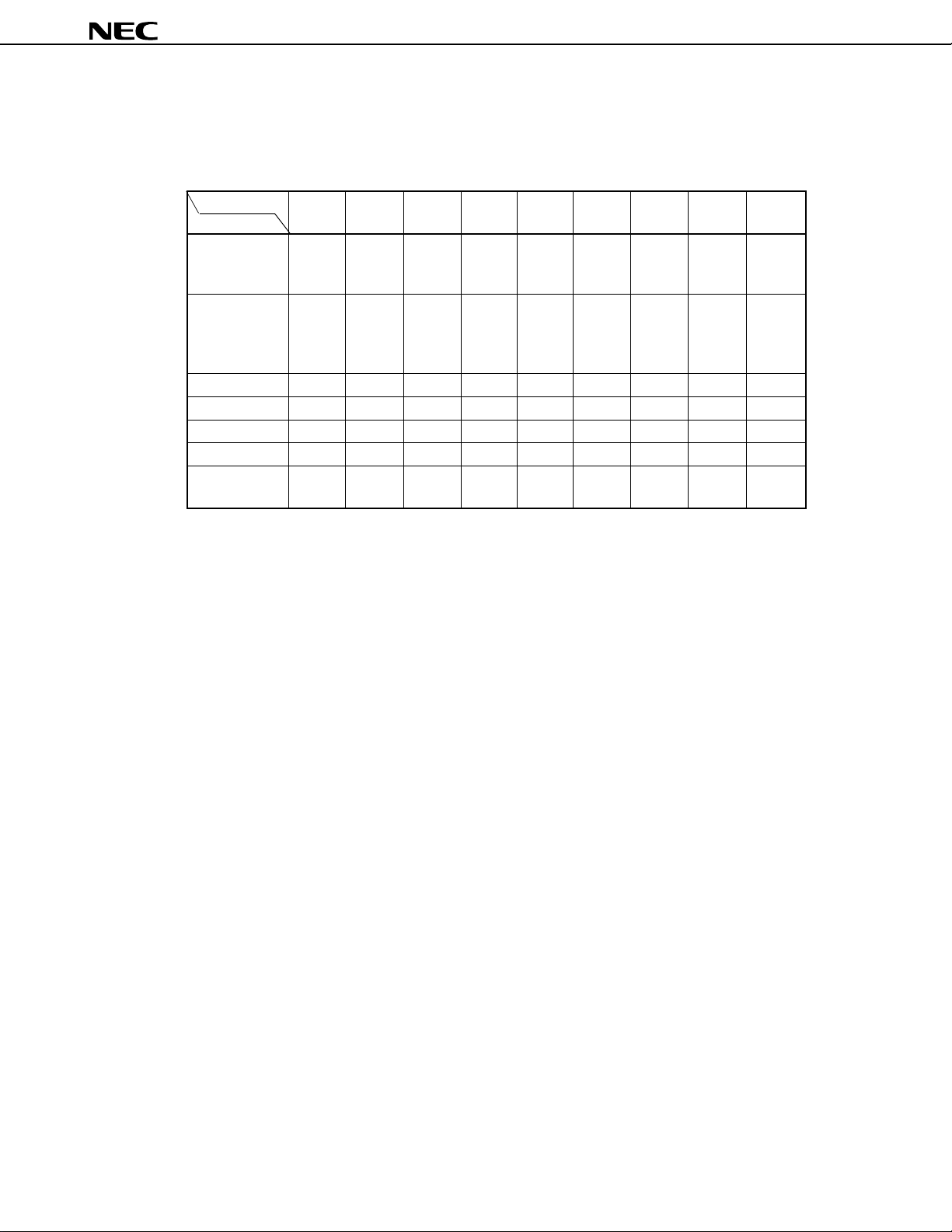

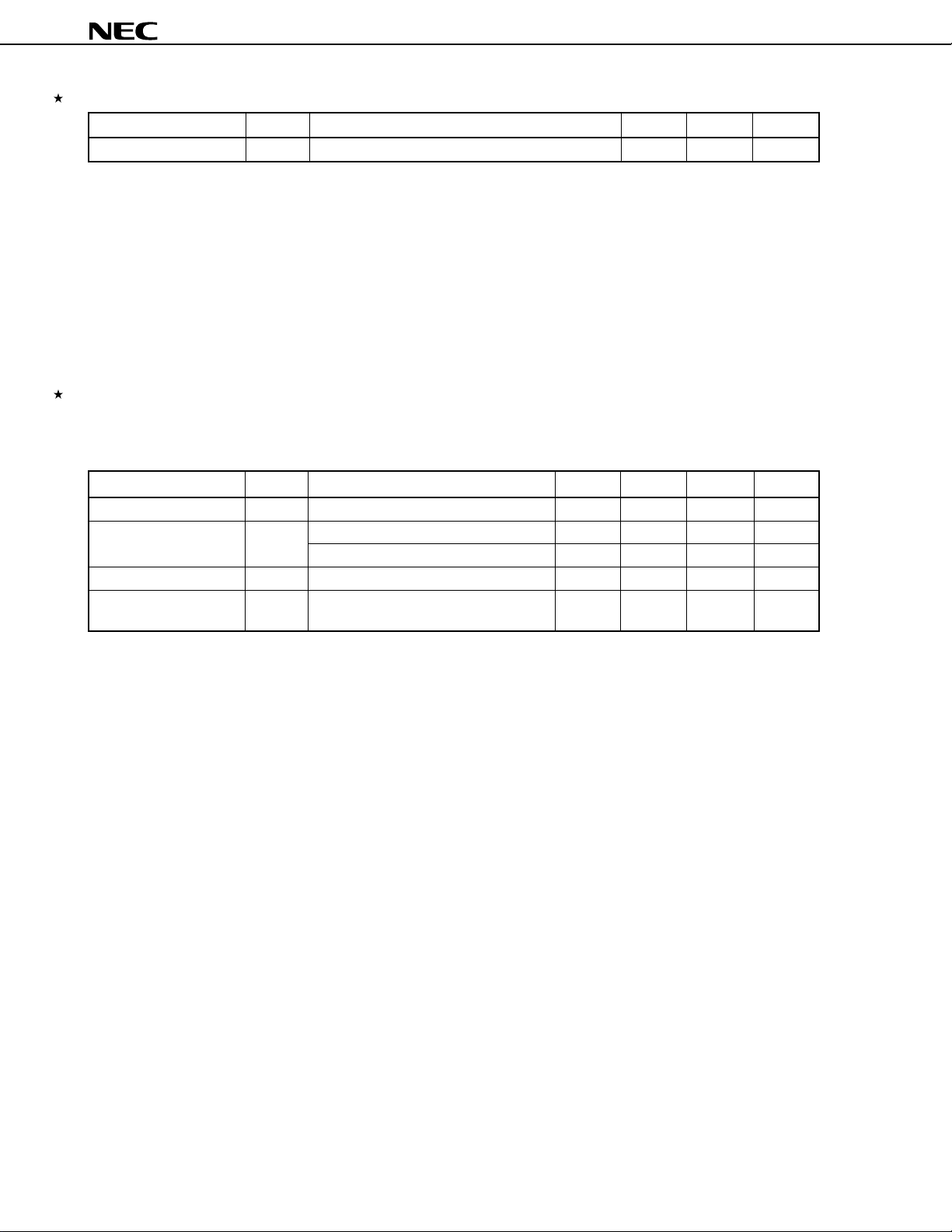

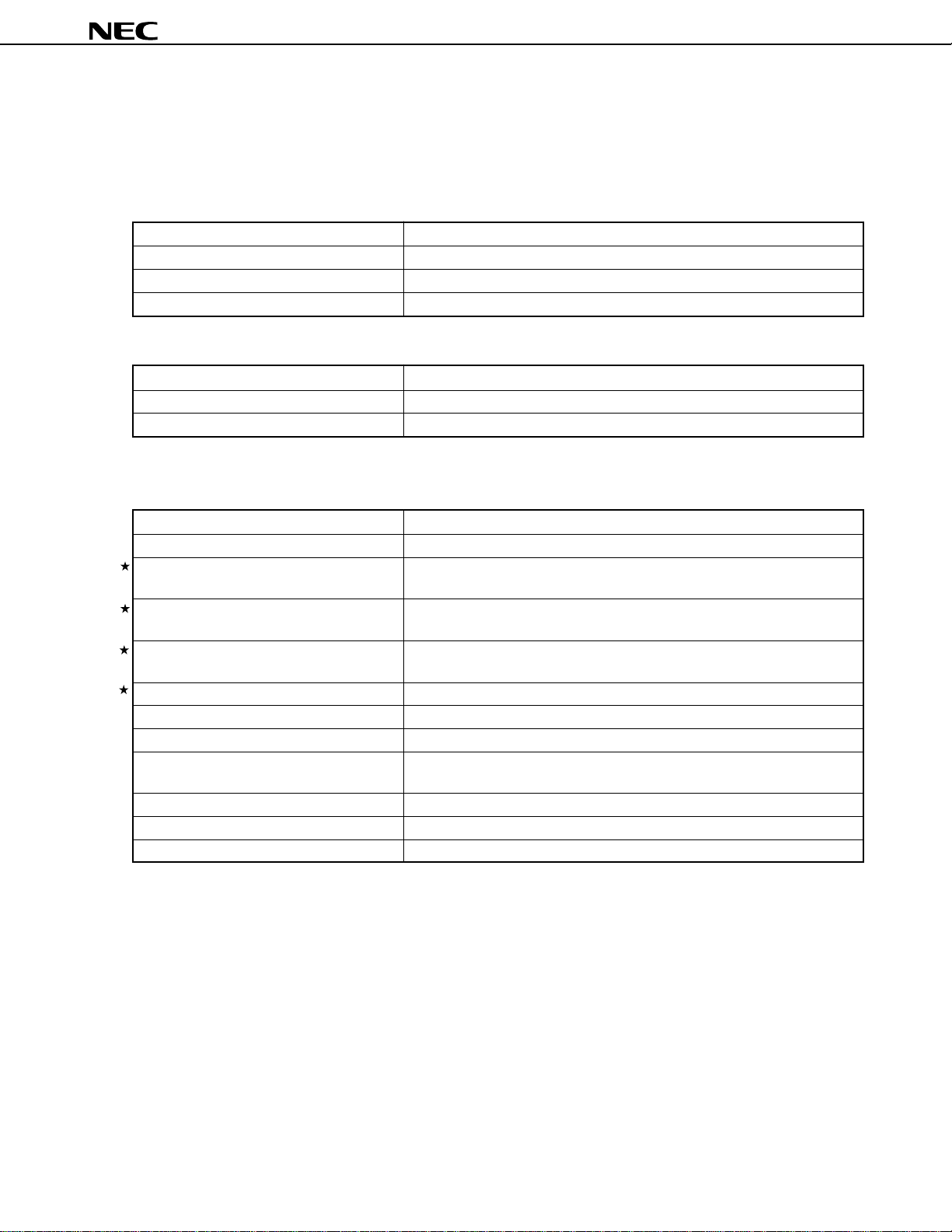

1. DIFFERENCES BETWEEN µPD784908 SUBSERIES PRODUCTS

The only difference between the µPD784907 and µPD784908 is their internal memory capacities.

The µPD78P4908 is produced by replacing the mask ROM in the µPD784907 or µPD784908 with 128-Kbyte one-

time PROM. Table 1-1 shows the differences between these products.

µ

Table 1-1. Differences between the

PD784908 Subseries Products

Part Number

Item

Internal ROM 96 K (mask ROM) 128 K (mask ROM) 128 K (one-time PROM)

Internal RAM 3,584 bytes 4,352 bytes

Regulator Provided None

Power supply voltage VDD = 4.0 to 5.5 V VDD = 4.5 to 5.5 V

(Main clock: fXX = 12.58 MHz, internal system clock = fXX, (Main clock: fXX = 12.58 MHz,

fCYK = 79 ns) internal system clock = fXX,

VDD = 3.5 to 5.5 V fCYK = 79 ns)

(other than above, fCYK = 159 ns) VDD = 4.0 to 5.5 V

Electrical specifications Refer to the data sheet of each product.

µ

PD784907

µ

PD784908

µ

PD78P4908

(other than above,

fCYK = 159 ns)

8

Data Sheet U11680EJ2V0DS00

Page 9

µ

PD784907, 784908

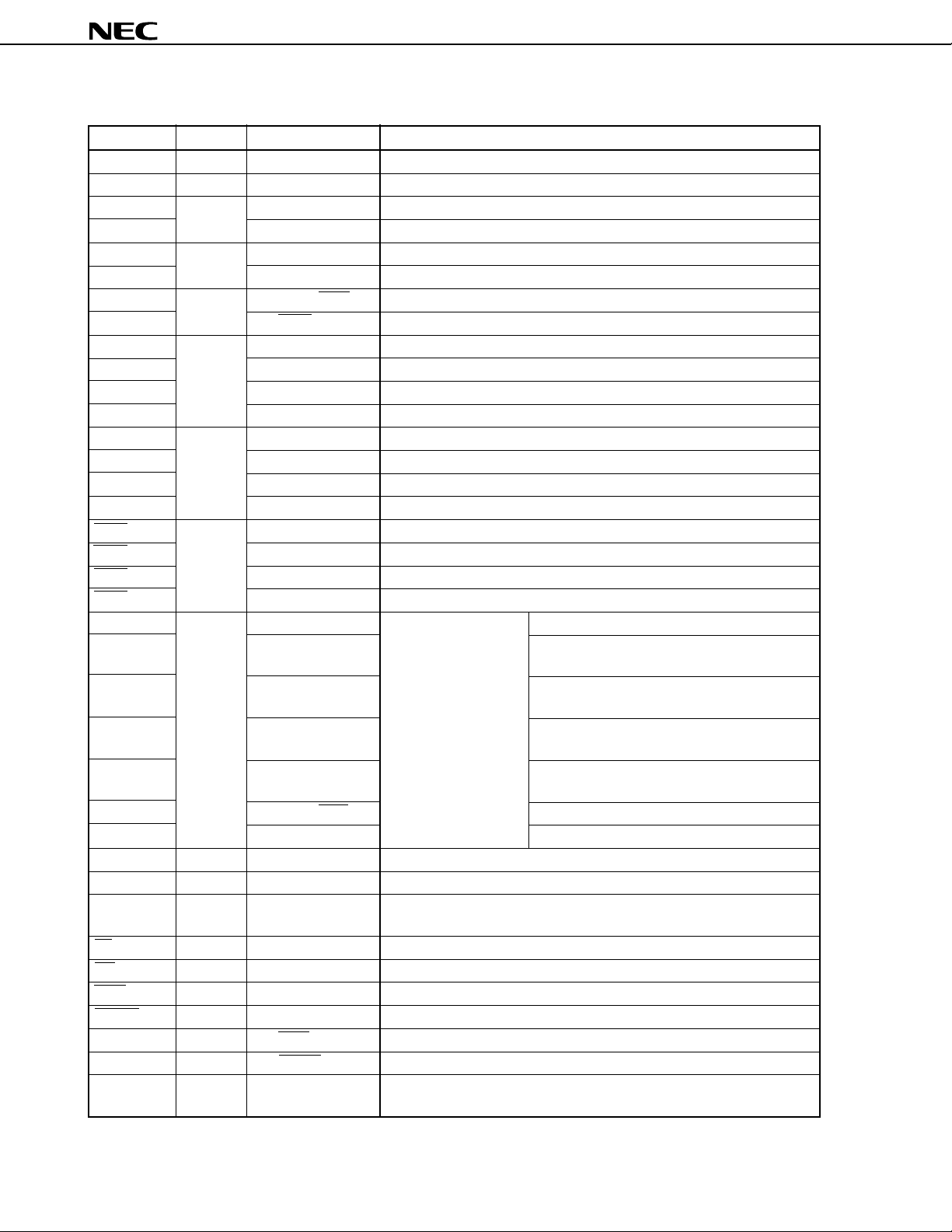

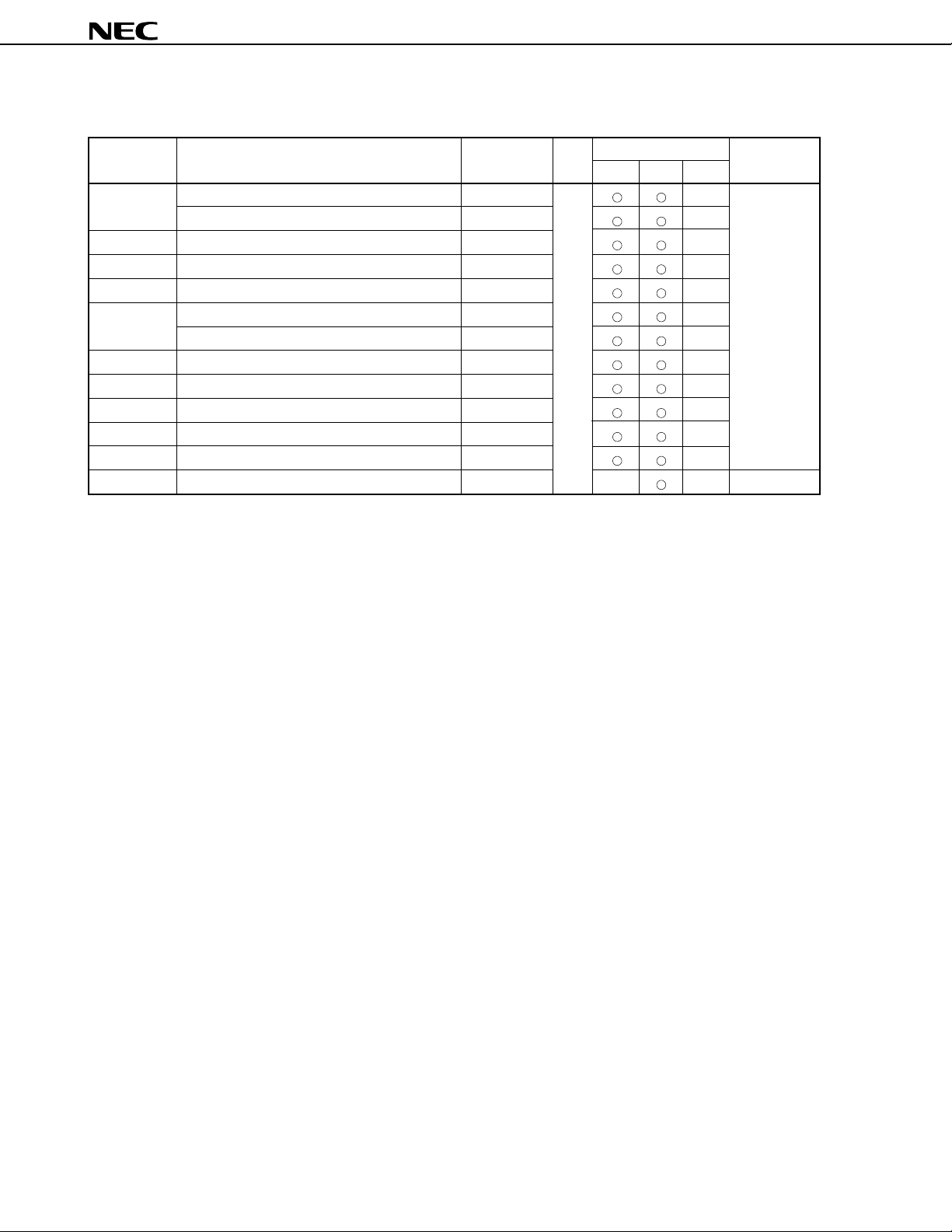

2. MAJOR DIFFERENCES BETWEEN µPD784908 AND µPD78098 SUBSERIES

Series Name

Item

Number of basic instructions 113 63

(mnemonics)

Minimum instruction execution 320/160 ns 480 ns

time (at 6.29/12.58 MHz operation) (at 6.29 MHz operation)

Timer/counter 16-bit timer/counter × 1 16-bit timer/counter × 1

8/16-bit timer/counter × 2 8/16-bit timer/counter × 2

8/16-bit timer × 1 Watch timer

Watch timer

Single clock Dual clock

Watch clock for clock operation

Watchdog timer Provided

Serial interface UART/IOE (3-wire serial I/O): 2 channels UART (3-wire serial I/O): 1 channel

CSI (3-wire serial I/O): 2 channels CSI/SBI (3-wire serial I/O): 1 channel

PWM output 2 None

A/D converter 8-bit resolution × 8 channels

D/A converter None

Interrupt Hardware source 27 23 (two test flags)

Internal 20 14

External 7 7

External extended function Provided (up to 1 Mbyte) None

IEBus controller Incorporated (simplified) Incorporated (complete hardware)

Power supply voltage • Mask ROM version VDD = 2.7 to 6.0 V

VDD = 4.0 to 5.5 V

(Main clock: fXX = 12.58 MHz,

internal system clock = fXX, fCYK = 79 ns)

VDD = 3.5 to 5.5 V

(other than above, fCYK = 159 ns)

• PROM version

VDD = 4.5 to 5.5 V

(Main clock: fXX = 12.58 MHz,

internal system clock = fXX, fCYK = 79 ns)

VDD = 4.0 to 5.5 V

(other than above, fCYK = 159 ns)

Package 100-pin plastic QFP (14 × 20 mm) 80-pin plastic QFP (14 × 14 mm)

µ

PD784908 Subseries

µ

PD78098 Subseries

CSI (3-wire serial I/O): 1 channel

80-pin plastic WQFN (14 × 14 mm):

µ

PD78P098A only

9Data Sheet U11680EJ2V0DS00

Page 10

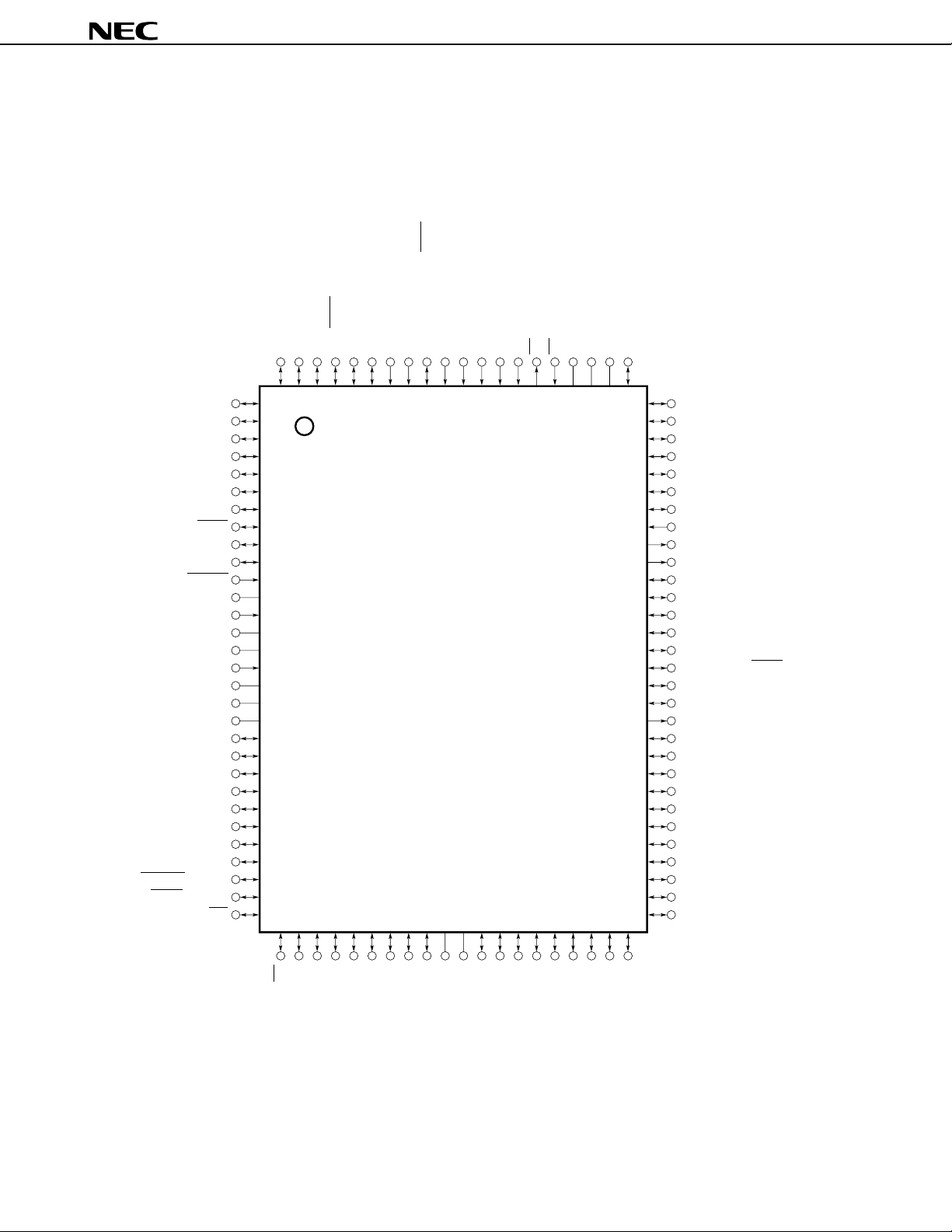

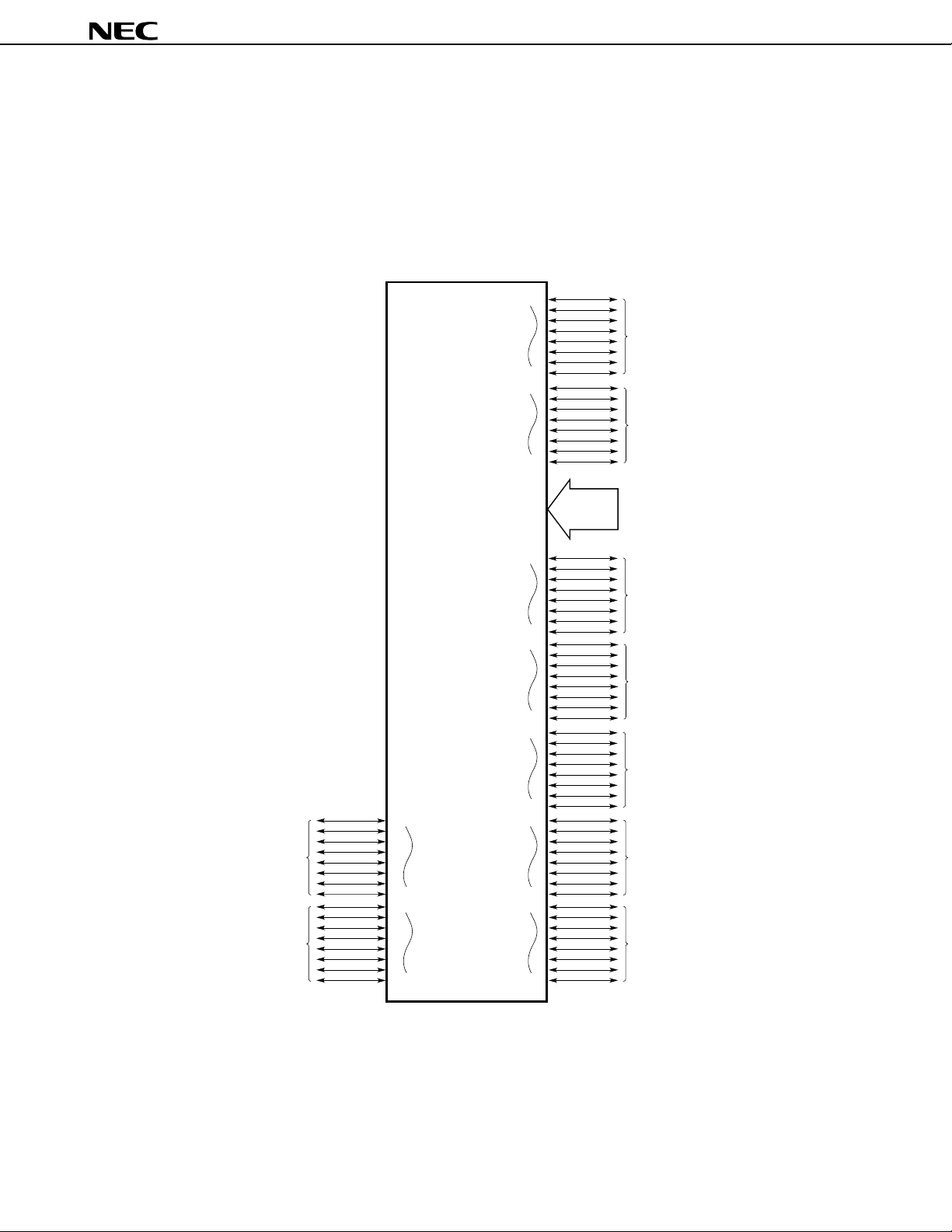

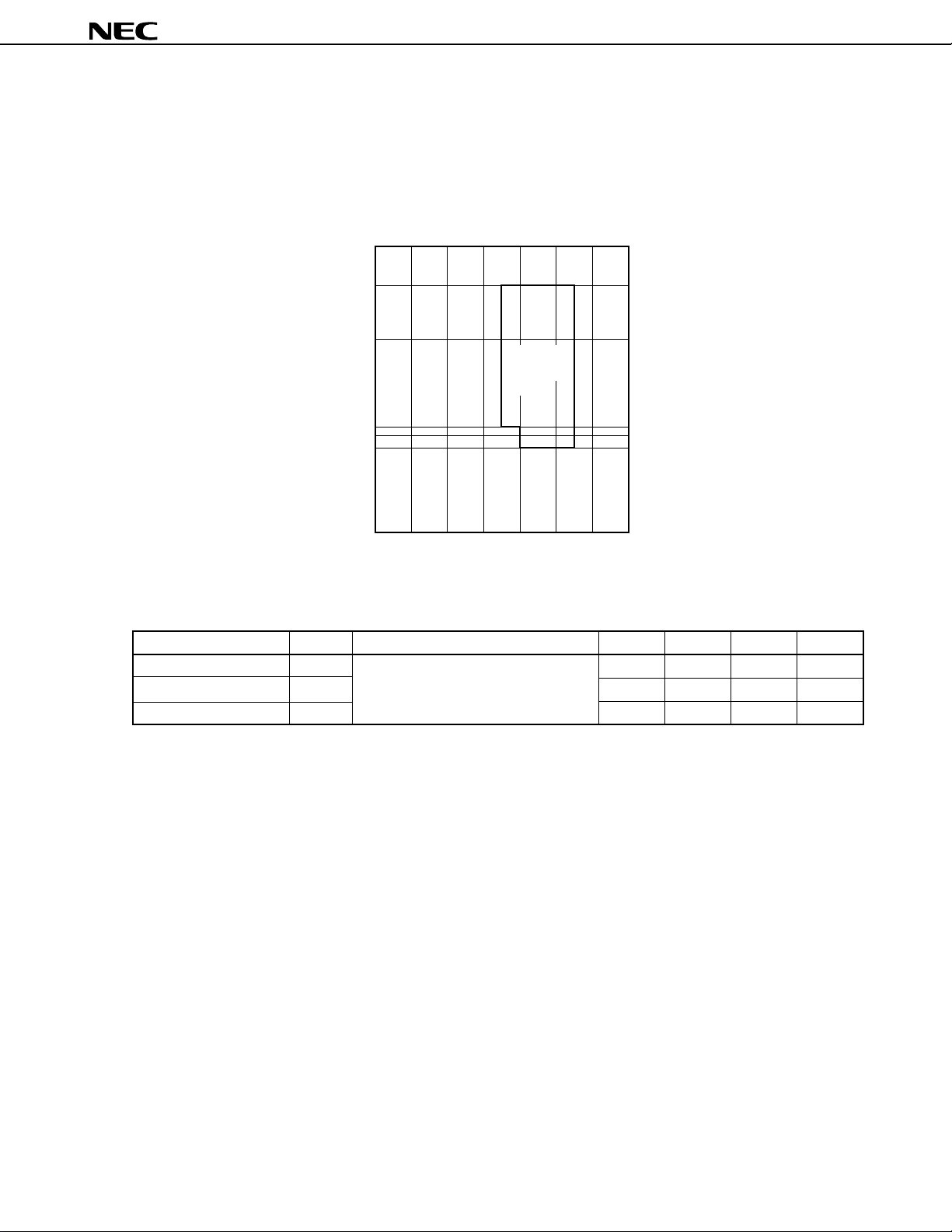

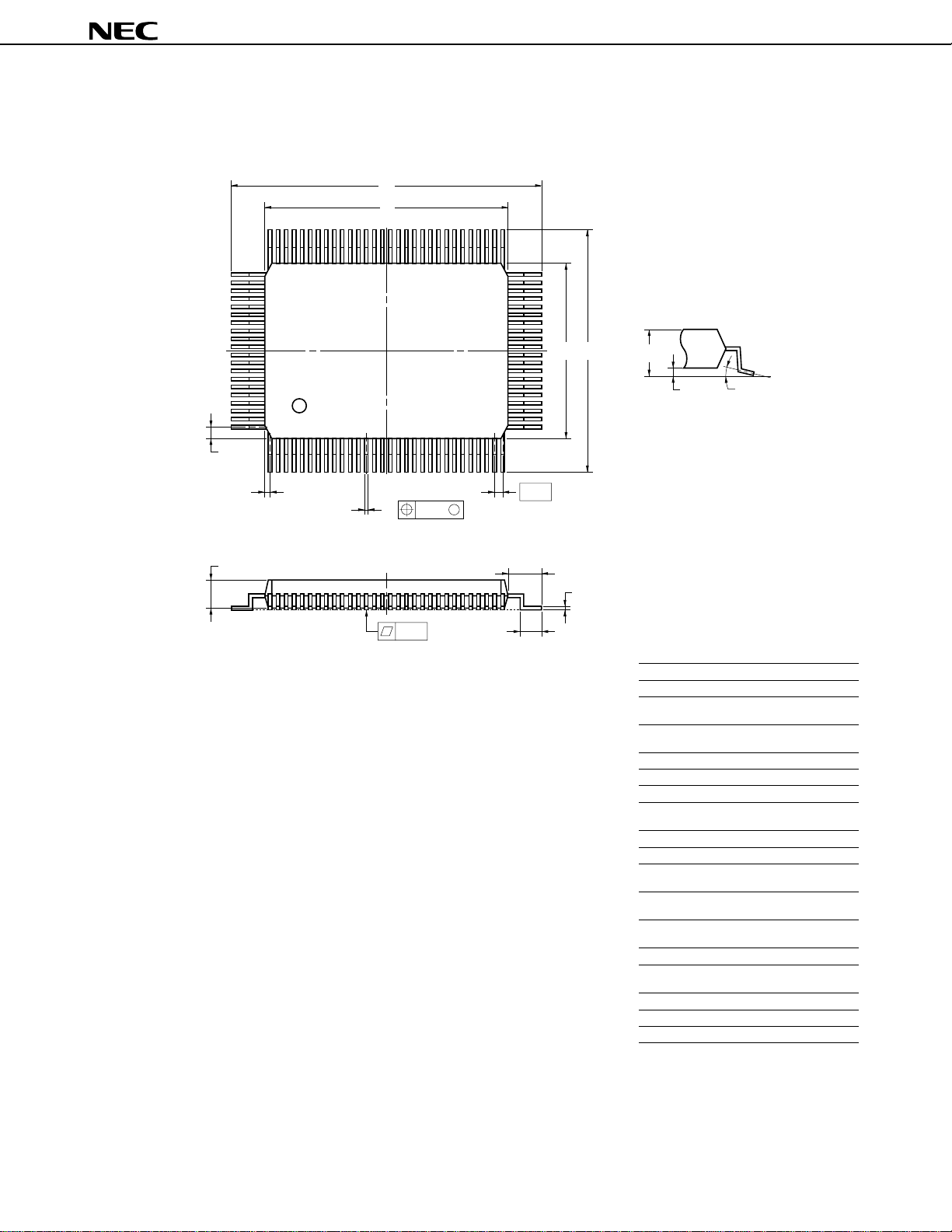

3. PIN CONFIGURATION (TOP VIEW)

• 100-pin plastic QFP (14 × 20 mm)

µ

PD784907GF-×××-3BA

µ

PD784908GF-×××-3BA

P35/TO1

P34/TO099P33/SO0

P32/SCK0

P31/TxD/SO1

100

98

97

96

2P37/TO3

3P100

4P101

5P102

6P103

7P104

8P105/SCK3

9P106/SI3

10P107/SO3

11RESET

12XT2

13XT1

14V

SS

15X2

Note 2

Note 3

16X1

17REGOFF

18REGC

19VDD

20P00

21P01

22P02

23P03

24P04

25P05

26P06

27P07

28P67/REFRQ/HLDAK

29P66/WAIT/HLDRQ

30P65/WR

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50

P30/RxD/SI1

P27/SI094P26/INTP5

95

93

P25/INTP4/ASCK/SCK1

P24/INTP3

P23/INTP2/CI

P22/INTP1

P21/INTP0

P20/NMI87TX86RX85AVSS84AVREF183AVDD82P77/ANI7

92

91

90

89

88

µ

PD784907, 784908

81

80 P76/ANI61P36/TO2

79 P75/ANI5

78 P74/ANI4

77 P73/ANI3

76 P72/ANI2

75 P71/ANI1

74 P70/ANI0

73 TEST

72 PWM1

71 PWM0

70 P17

69 P16

68 P15

67 P14/TxD2/SO2

66 P13/RxD2/SI2

65 P12/ASCK2/SCK2

64 P11

63 P10

62 ASTB/CLKOUT

61 P90

60 P91

59 P92

58 P93

57 P94

56 P95

55 P96

54 P97

53 P40/AD0

52 P41/AD1

51 P42/AD2

Note 1

P64/RD

P63/A19

P62/A18

P61/A17

Notes 1. Connect the TEST pin directly to V

2. Connect the REGOFF pin directly to VSS (select regulator operation).

3. Connect the REGC pin to V

10

SS

V

VDD

P51/A9

P60/A16

P57/A15

P56/A14

P55/A13

P54/A12

SS.

SS via a capacitor of the order of 1

Data Sheet U11680EJ2V0DS00

P53/A11

P52/A10

P50/A8

P47/AD7

P46/AD6

P45/AD5

P44/AD4

µ

F.

P43/AD3

Page 11

µ

PD784907, 784908

A8 to A19: Address bus

AD0 to AD7: Address/data bus

ANI0 to ANI7: Analog input

ASCK, ASCK2: Asynchronous serial clock

ASTB: Address strobe

DD: Analog power supply

AV

AVREF1: Reference voltage

AVSS: Analog ground

CI: Clock input

CLKOUT: Clock output

HLDAK: Hold acknowledge

HLDRQ: Hold request

INTP0 to INTP5: Interrupt from peripherals

NMI: Non-maskable interrupt

P00 to P07: Port 0

P10 to P17: Port 1

P20 to P27: Port 2

P30 to P37: Port 3

P40 to P47: Port 4

P50 to P57: Port 5

P60 to P67: Port 6

P70 to P77: Port 7

P90 to P97: Port 9

P100 to P107: Port 10

PWM0, PWM1: Pulse width modulation output

RD: Read strobe

REFRQ: Refresh request

REGC: Regulator capacitance

REGOFF: Regulator off

RESET: Reset

RX: IEBus receive data

XD, RXD2: Receive data

R

SCK0 to SCK3: Serial clock

SI0 to SI3: Serial input

SO0 to SO3: Serial output

TEST: Test

TO0 to TO3: Timer output

TX: IEBus transmit data

XD, TXD2: Transmit data

T

VDD: Power supply

VSS: Ground

WAIT: Wait

WR: Write strobe

X1, X2: Crystal (main system clock)

XT1, XT2: Crystal (watch)

11Data Sheet U11680EJ2V0DS00

Page 12

µ

PD784907, 784908

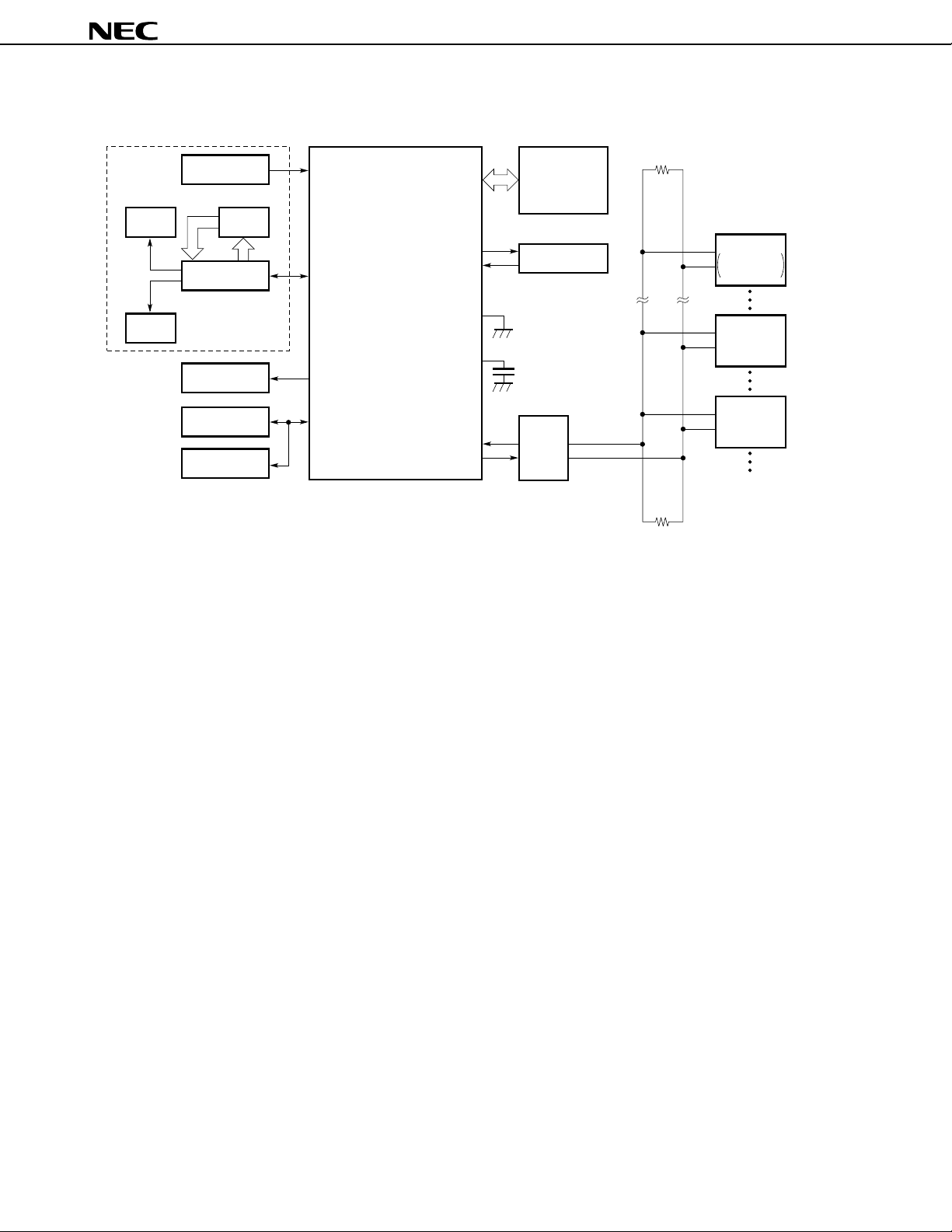

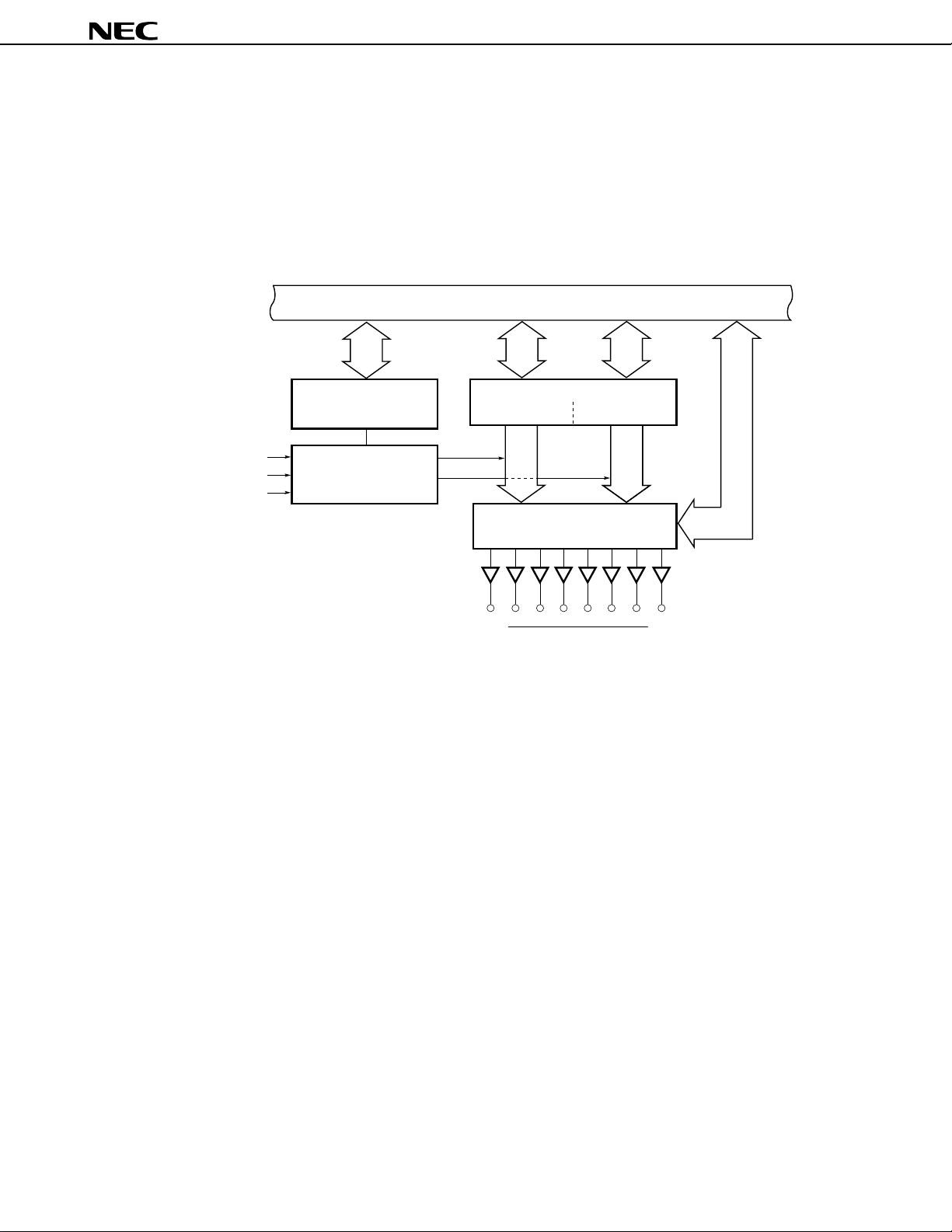

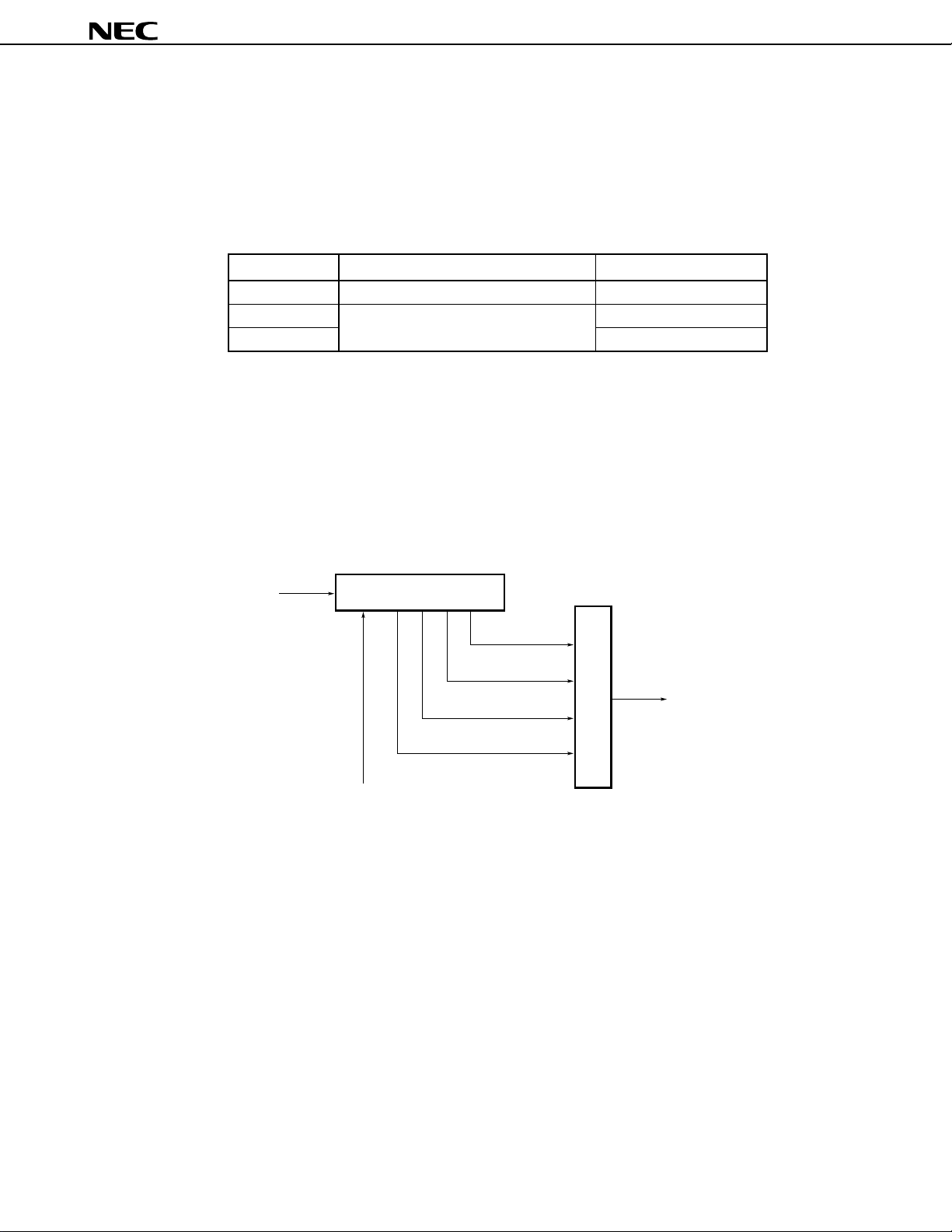

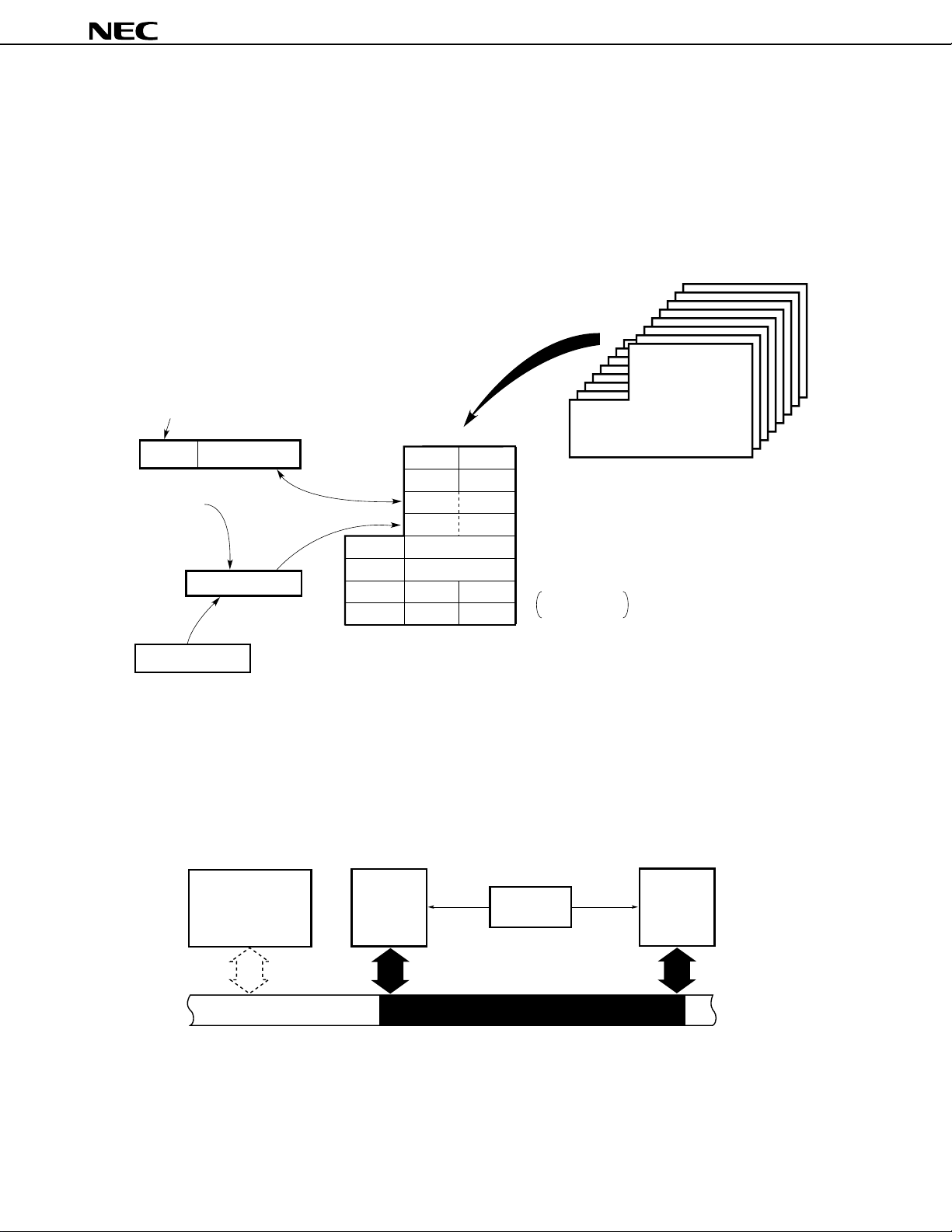

4. SYSTEM CONFIGURATION EXAMPLE (AUTOMOTIVE CAR AUDIO (TUNER DECK))

Front panel PD784908

Remote-controll

FIP

µ

TM

FIP

controller/driver

µ

signal reception

circuit

PC2800A, etc.

Key

matrix

PD16312, etc.

Interrupt input

SIO with automatic

transmission/reception

function

LED

display

Audio control

circuit

Electronic

volume

EEPROM

TM

3-wire serial I/O

µ

General-purpose

port

3-wire serial I/O

IEBus controller

REGOFF

REGC

Cassette deck

unit

Tuner pack

IEBus

driver/

receiver

IEBus

CD unit

CD changer,

one CD, etc.

DSP unit

TV unit

12

Data Sheet U11680EJ2V0DS00

Page 13

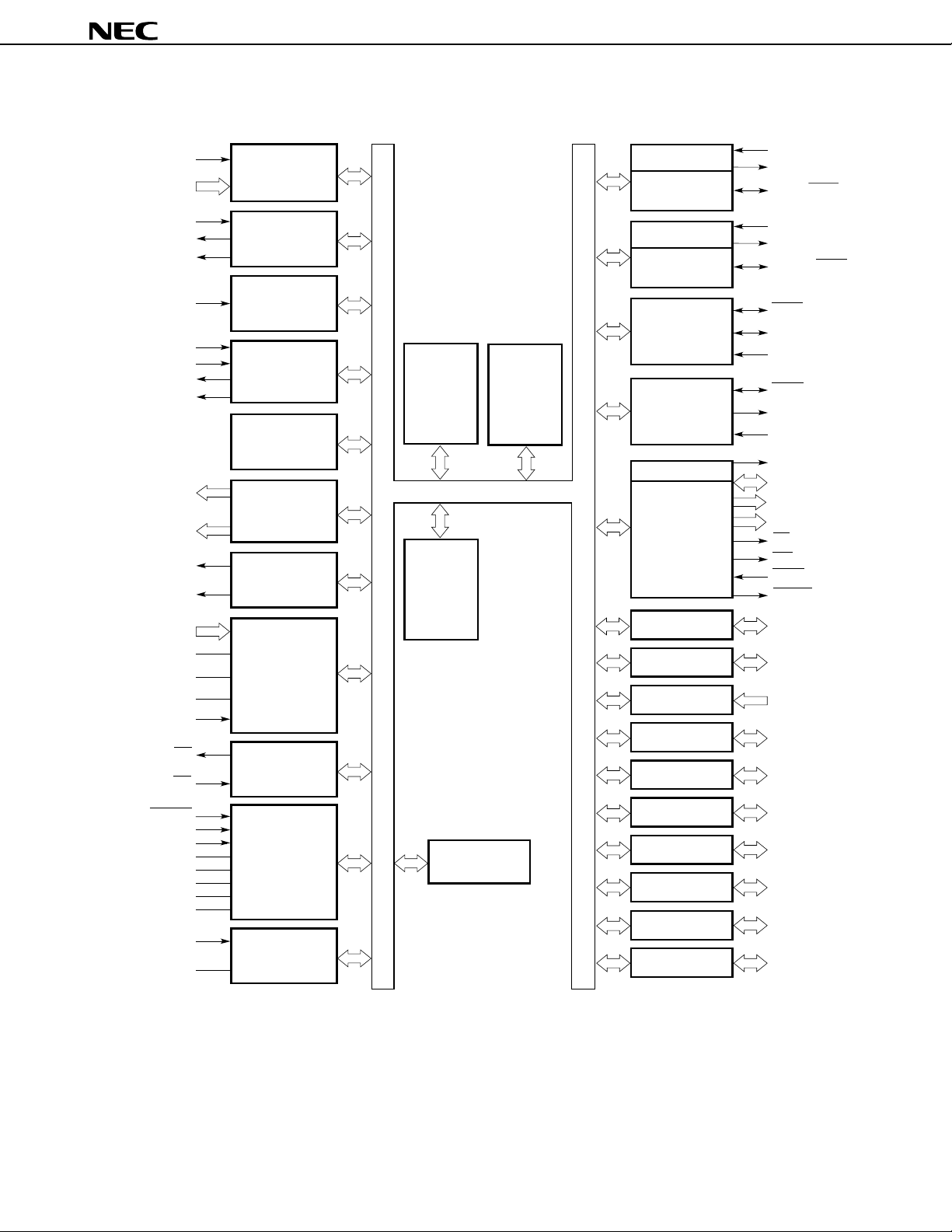

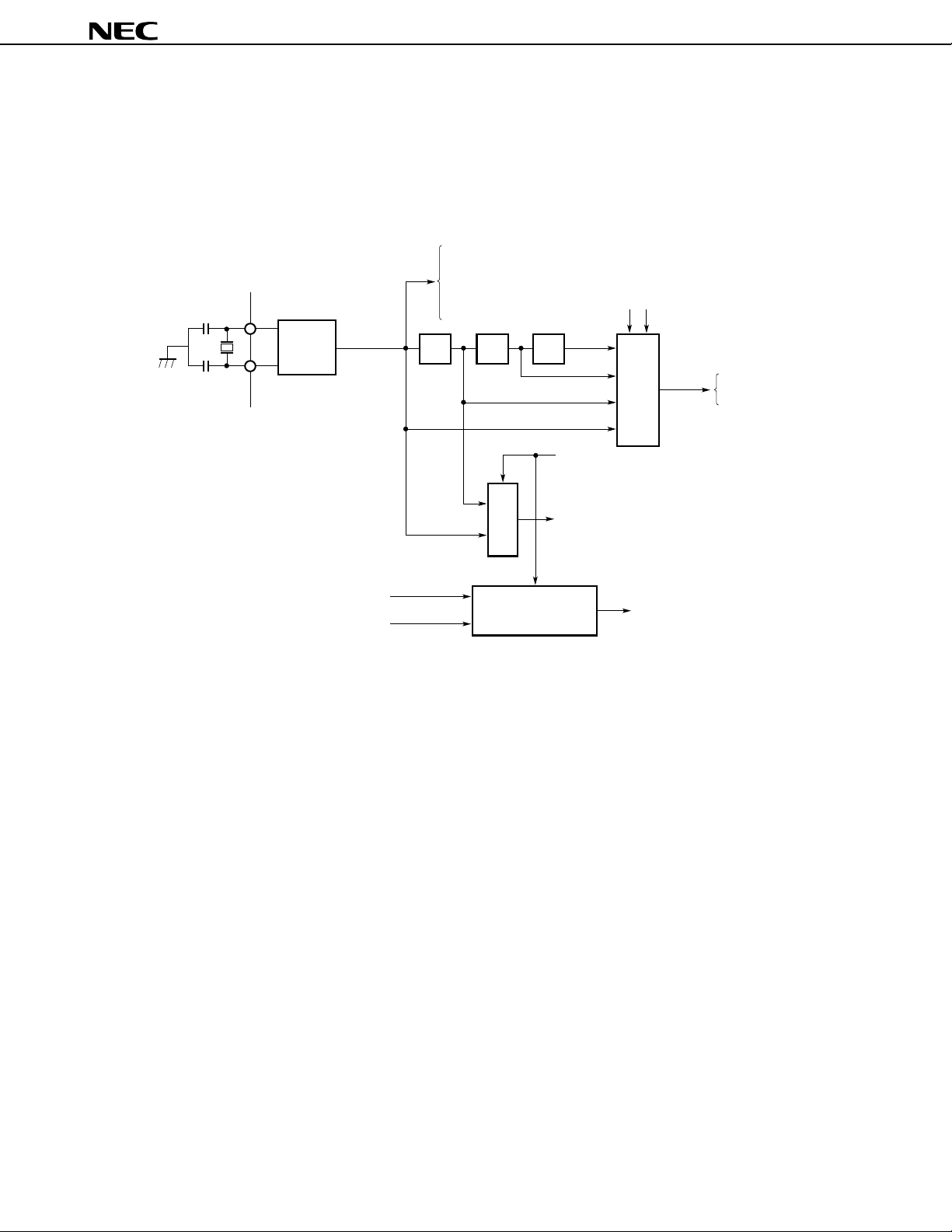

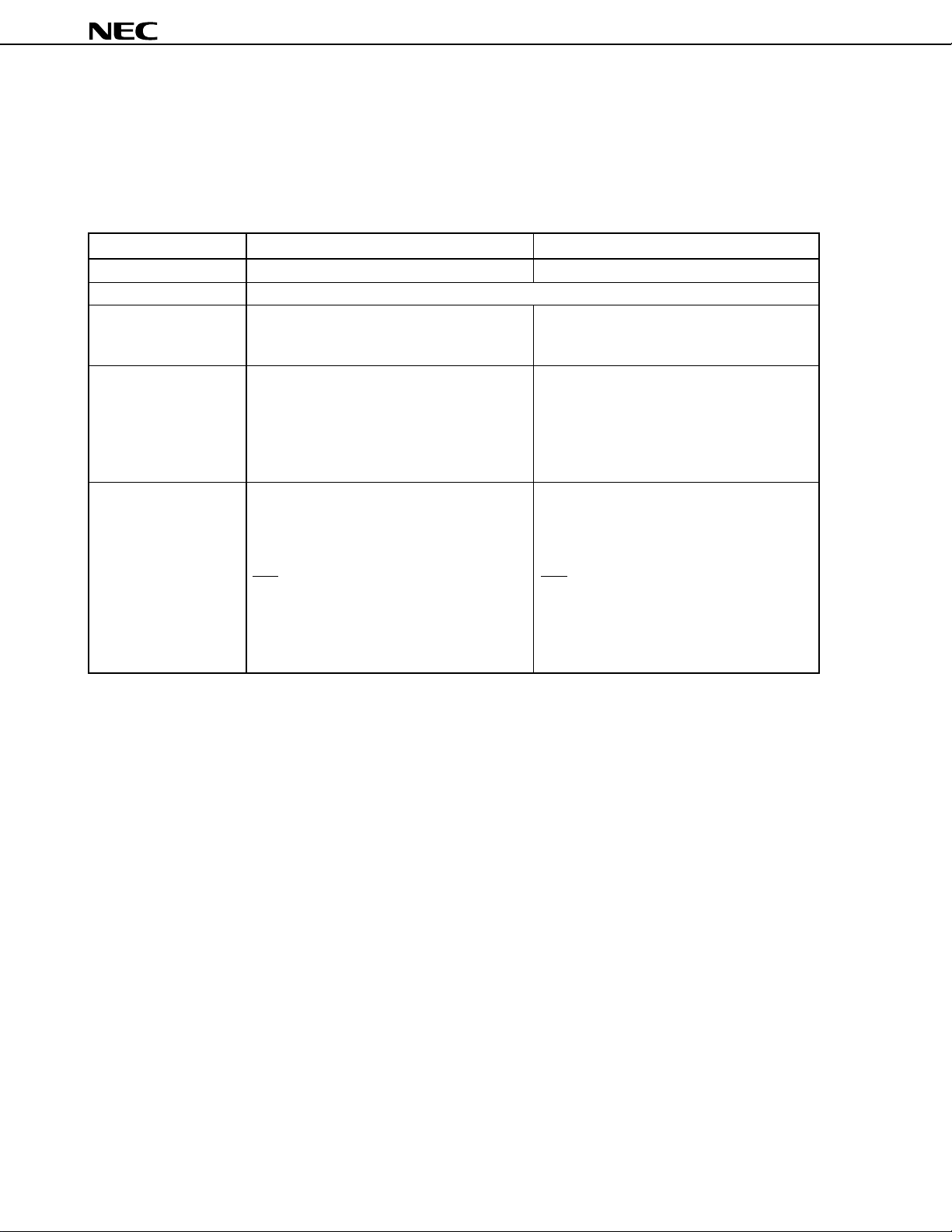

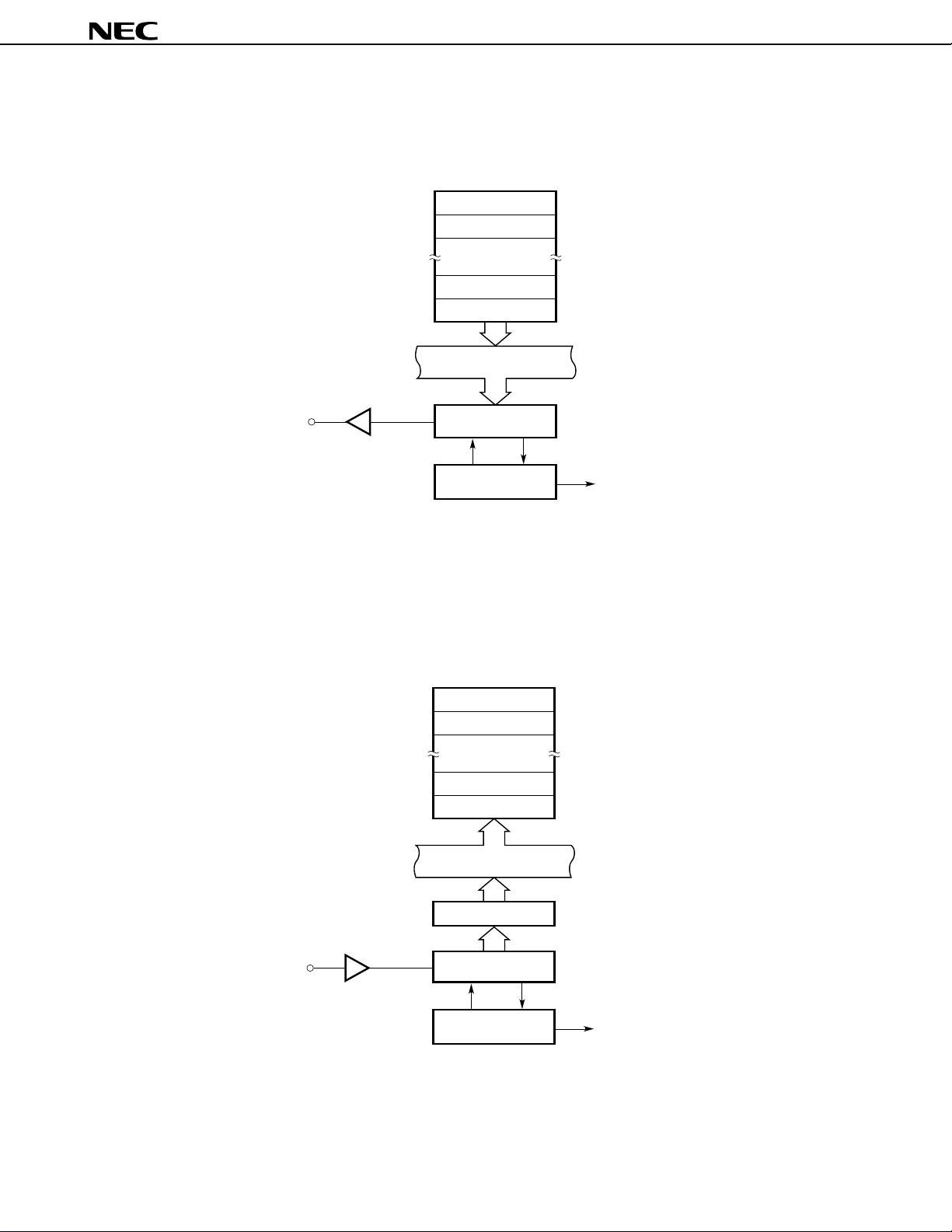

5. BLOCK DIAGRAM

µ

PD784907, 784908

NMI

INTP0 to INTP5

INTP3

TO0

TO1

INTP0

INTP1

INTP2/CI

TO2

TO3

P00 to P03

P04 to P07

PWM0

PWM1

Programmable

interrupt controller

Timer/counter 0

(16 bits)

Timer/counter 1

(16 bits)

Timer/counter 2

(16 bits)

Timer 3

(16 bits)

Real-time output

port

PWM

78K/IV

CPU core

RAM

ROM

UART/IOE2

Baud-rate

generator

UART/IOE1

Baud-rate

generator

Clocked serial

interface

Clocked serial

interface 3

Clock output

Bus interface

RxD/SI1

TxD/SO1

ASCK/SCK1

RxD2/SI2

TxD2/SO2

ASCK2/SCK2

SCK0

SO0

SI0

SCK3

SO3

SI3

ASTB/CLKOUT

AD0 to AD7

A8 to A15

A16 to A19

RD

WR

WAIT/HLDRQ

REFRQ/HLDAK

ANI0 to ANI7

AV

DD

AV

REF1

AV

INTP5

TX

RX

RESET

TEST

X1

X2

REGC

REGOFF

V

V

XT1

XT2

SS

DD

SS

A/D converter

IEBus controller

System control

(regulator)

Watch timer

Watchdog timer

Remark The internal ROM and RAM capacities differ depending on the product.

Port 0

Port 1

Port 2

Port 3

Port 4

Port 5

Port 6

Port 7

Port 9

Port 10

P00 to P07

P10 to P17

P20 to P27

P30 to P37

P40 to P47

P50 to P57

P60 to P67

P70 to P77

P90 to P97

P100 to P107

13Data Sheet U11680EJ2V0DS00

Page 14

6. PIN FUNCTIONS

6.1 Port Pins (1/2)

Pin Name I/O Alternate Function Function

P00 to P07 I/O — Port 0 (P0):

• 8-bit I/O port.

• Can be used as a real-time output port (4 bits × 2).

• Input and output can be specified by 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• Can drive transistors.

P10 I/O —

P11 —

P12 ASCK2/SCK2

P13 RxD2/SI2

P14 TxD2/SO2

P15 to P17 —

P20 Input NMI

P21 INTP0

P22 INTP1

P23 INTP2/CI

P24 INTP3

P25 INTP4/ASCK/SCK1

P26 INTP5

P27 SI0

P30 I/O RxD/SI1

P31 TxD/SO1

P32 SCK0

P33 SO0

P34 to P37 TO0 to TO3

P40 to P47 I/O AD0 to AD7 Port 4 (P4):

P50 to P57 I/O A8 to A15 Port 5 (P5):

Port 1 (P1):

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• Can drive LEDs.

Port 2 (P2):

• 8-bit input port.

• P20 does not function as a general-purpose port (non-maskable interrupt).

However, the input level can be checked by an interrupt service routine.

• The use of on-chip pull-up resistors can be specified by software for pins

P22 to P27 (in 6-bit units).

• The P25/INTP4/ASCK/SCK1 pin functions as the SCK1 output pin by a

CSIM1 specification.

Port 3 (P3):

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• The use of the N-ch open drain can be specified for pins P32 and P33.

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• Can drive LEDs.

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• Can drive LEDs.

µ

PD784907, 784908

14

Data Sheet U11680EJ2V0DS00

Page 15

6.1 Port Pins (2/2)

Pin Name I/O Alternate Function Function

P60 to P63 I/O A16 to A19

P64 RD

P65 WR

P66 WAIT/HLDRQ

P67 REFRQ/HLDAK

P70 to P77 I/O ANI0 to ANI7 Port 7 (P7):

P90 to P97 I/O — Port 9 (P9):

P100 to I/O —

P104

P105 SCK3

P106 SI3

P107 SO3

Port 6 (P6):

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

Port 10 (P10):

• 8-bit I/O port.

• Input and output can be specified in 1-bit units.

• The use of on-chip pull-up resistors can be simultaneously specified by

software for all pins in input mode.

• The use of the N-ch open drain can be specified for pins P105 and P107.

µ

PD784907, 784908

15Data Sheet U11680EJ2V0DS00

Page 16

µ

PD784907, 784908

6.2 Non-Port Pins (1/2)

Pin Name I/O Alternate Function Function

TO0 to TO3 Output P34 to P37 Timer output

CI Input P23/INTP2 Input of a count clock for timer/counter 2

RxD Input P30/SI1 Serial data input (UART0)

RxD2 P13/SI2 Serial data input (UART2)

TxD Output P31/SO1 Serial data output (UART0)

TxD2 P14/SO2 Serial data output (UART2)

ASCK Input P25/INTP4/SCK1 Baud rate clock input (UART0)

ASCK2 P12/SCK2 Baud rate clock input (UART2)

SI0 Input P27 Serial data input (3-wire serial I/O 0)

SI1 P30/RxD Serial data input (3-wire serial I/O 1)

SI2 P13/RxD2 Serial data input (3-wire serial I/O 2)

SI3 P106 Serial data input (3-wire serial I/O 3)

SO0 Output P33 Serial data output (3-wire serial I/O 0)

SO1 P31/TxD Serial data output (3-wire serial I/O 1)

SO2 P14/TxD2 Serial data output (3-wire serial I/O 2)

SO3 P107 Serial data output (3-wire serial I/O 3)

SCK0 I/O P32 Serial clock I/O (3-wire serial I/O 0)

SCK1 P25/INTP4/ASCK Serial clock I/O (3-wire serial I/O 1)

SCK2 P12/ASCK2 Serial clock I/O (3-wire serial I/O 2)

SCK3 P105 Serial clock I/O (3-wire serial I/O 3)

NMI Input P20 External interrupt —

INTP0 P21 request • Input of a count clock for timer/counter 1

• Capture/trigger signal for CR11 or CR12

INTP1 P22 • Input of a count clock for timer/counter 2

• Capture/trigger signal for CR22

INTP2 P23/CI • Input of a count clock for timer/counter 2

• Capture/trigger signal for CR21

INTP3 P24 • Input of a count clock for timer/counter 0

• Capture/trigger signal for CR02

INTP4 P25/ASCK/SCK1 —

INTP5 P26

AD0 to AD7 I/O P40 to P47 Time multiplexing address/data bus (for connecting external memory)

A8 to A15 Output P50 to P57 High-order address bus (for connecting external memory)

A16 to A19 Output P60 to P63 High-order address bus during address expansion (for connecting external

memory)

RD Output P64 Strobe signal output for reading the contents of external memory

WR Output P65 Strobe signal output for writing on external memory

WAIT Input P66/HLDRQ Wait insertion

REFRQ Output P67/HLDAK Refresh pulse output to external pseudo static memory

HLDRQ Input P66/WAIT Input of bus hold request

HLDAK Output P67/REFRQ Output of bus hold response

ASTB Output CLKOUT Latch timing output of time multiplexing address (A0 to A7) (for connecting

external memory)

Input of a conversion start trigger for A/D converter

16

Data Sheet U11680EJ2V0DS00

Page 17

µ

PD784907, 784908

6.2 Non-Port Pins (2/2)

Pin Name I/O Alternate Function Function

CLKOUT Output ASTB Clock output

PWM0 Output — PWM output 0

PWM1 Output — PWM output 1

RX Input — Data input (IEBus)

TX Output — Data output (IEBus)

REGC — — Capacitance connection for stabilizing the regulator output/power supply

when the regulator is stopped. Connect to VSS via a capacitor of order of 1µF.

REGOFF — — Signal for specifying regulator operation

RESET Input — Chip reset

X1 Input — Crystal input for system clock oscillation (A clock pulse can also be input

X2 —

XT1 Input — Watch clock connection

XT2 — —

ANI0 to ANI7 Input P70 to P77 Analog voltage input for A/D converter

AVREF1 — — To apply the reference voltage for A/D converter

AVDD Positive power supply for A/D converter

AVSS GND for A/D converter

VDD Positive power supply

VSS GND

TEST Input Connect directly to V

to the X1 pin.)

SS. (This pin is for IC test.)

Data Sheet U11680EJ2V0DS00

17

Page 18

µ

PD784907, 784908

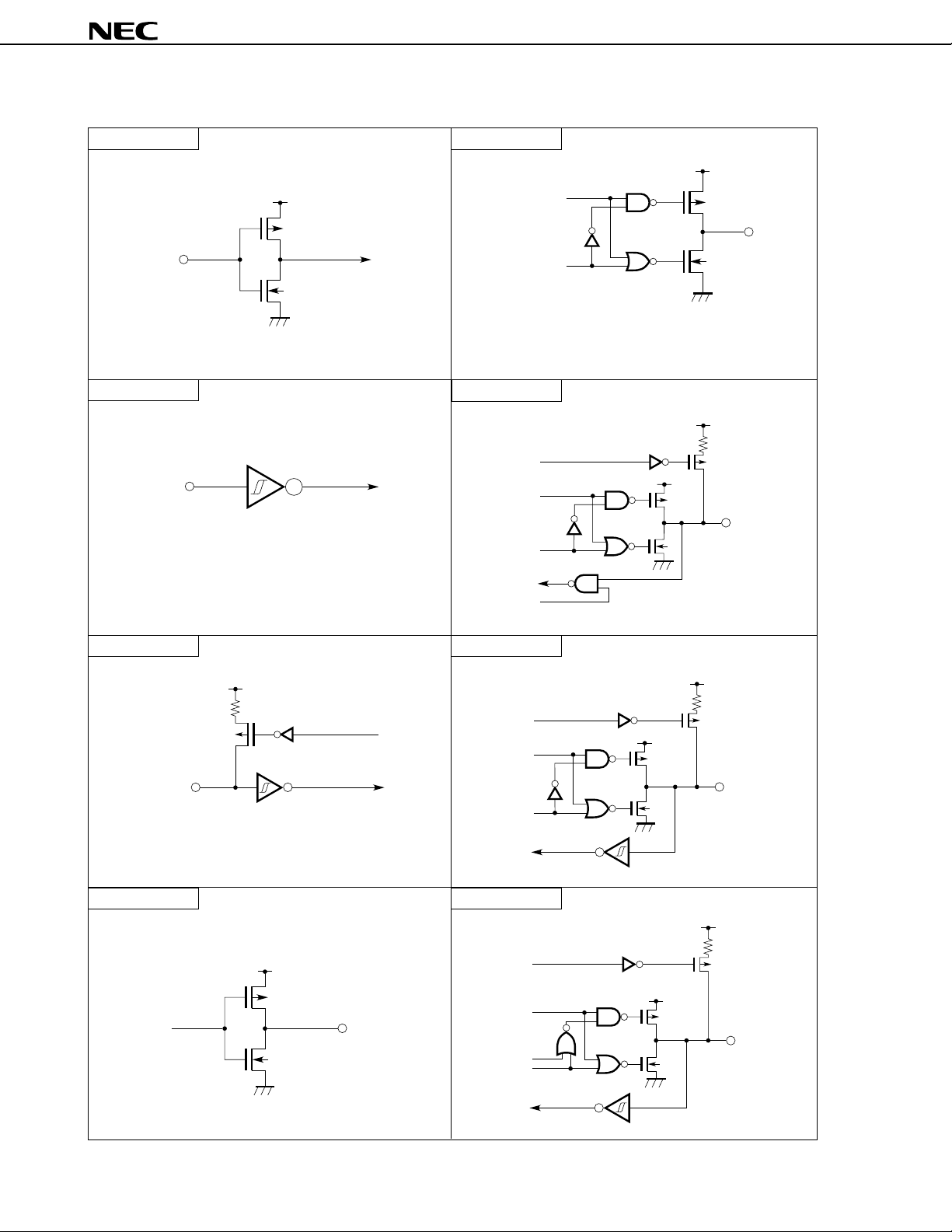

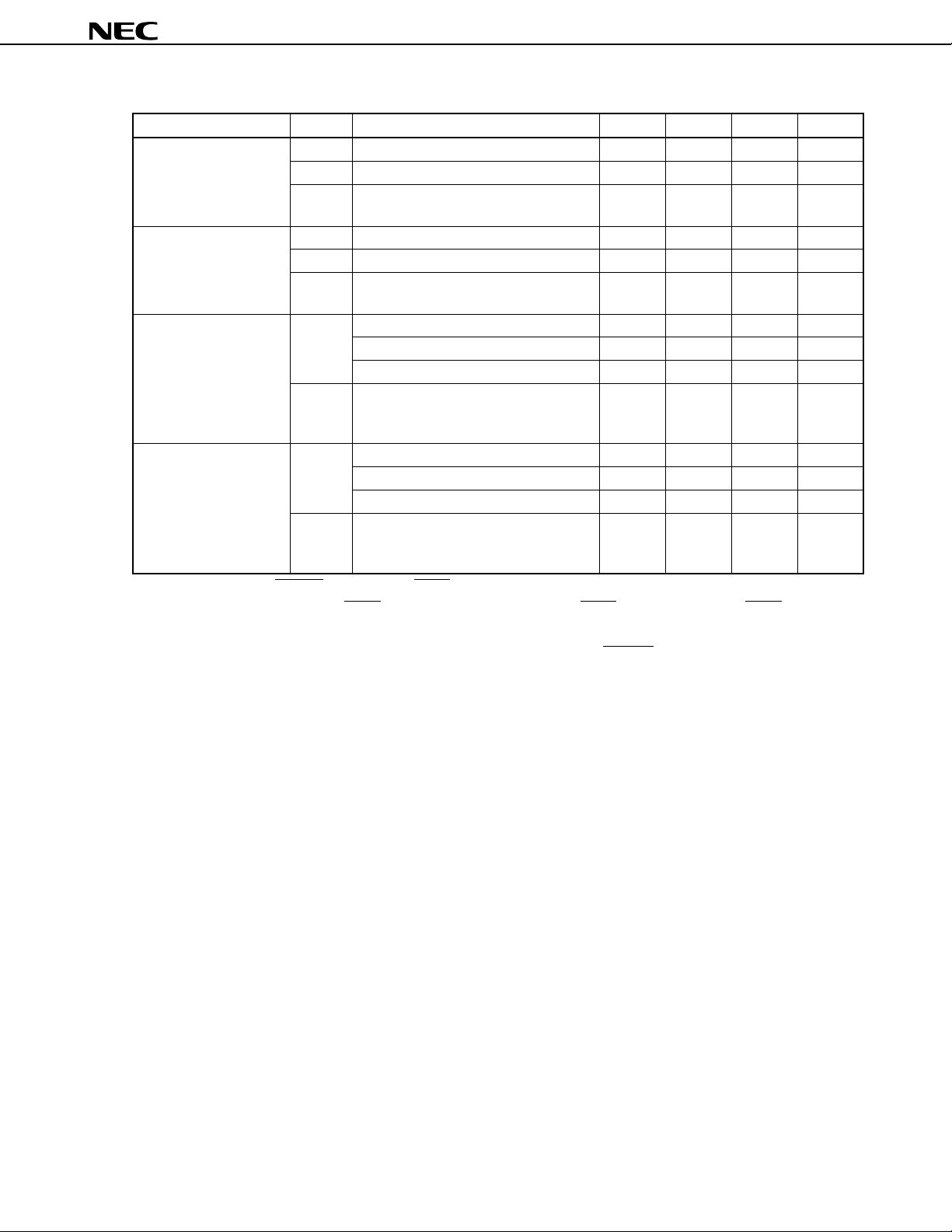

6.3 Pin I/O Circuits and Recommended Connections of Unused Pins

The input/output circuit type of each pin and recommended connections of unused pins are shown in Table 6-1.

For each type of input/output circuit, refer to Figure 6-1.

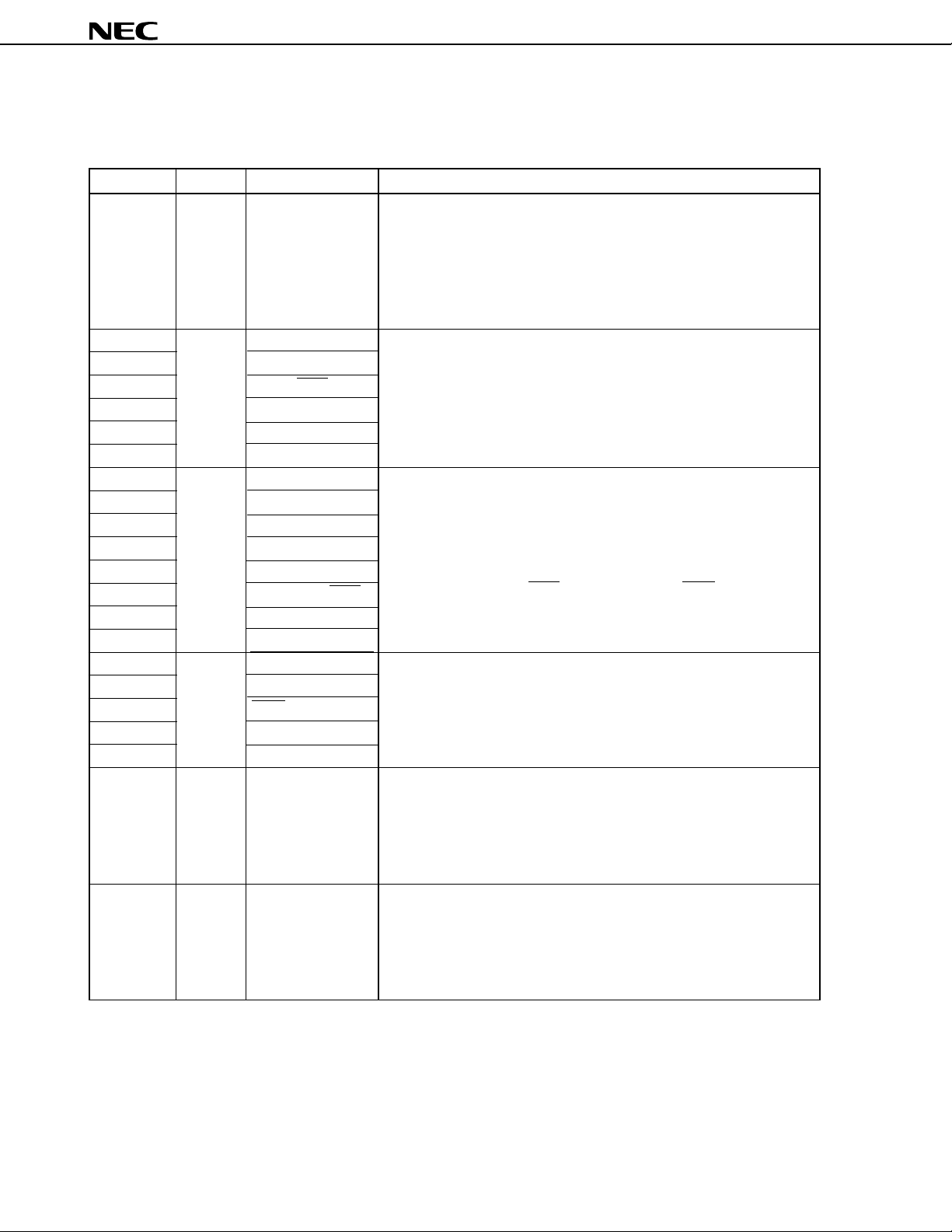

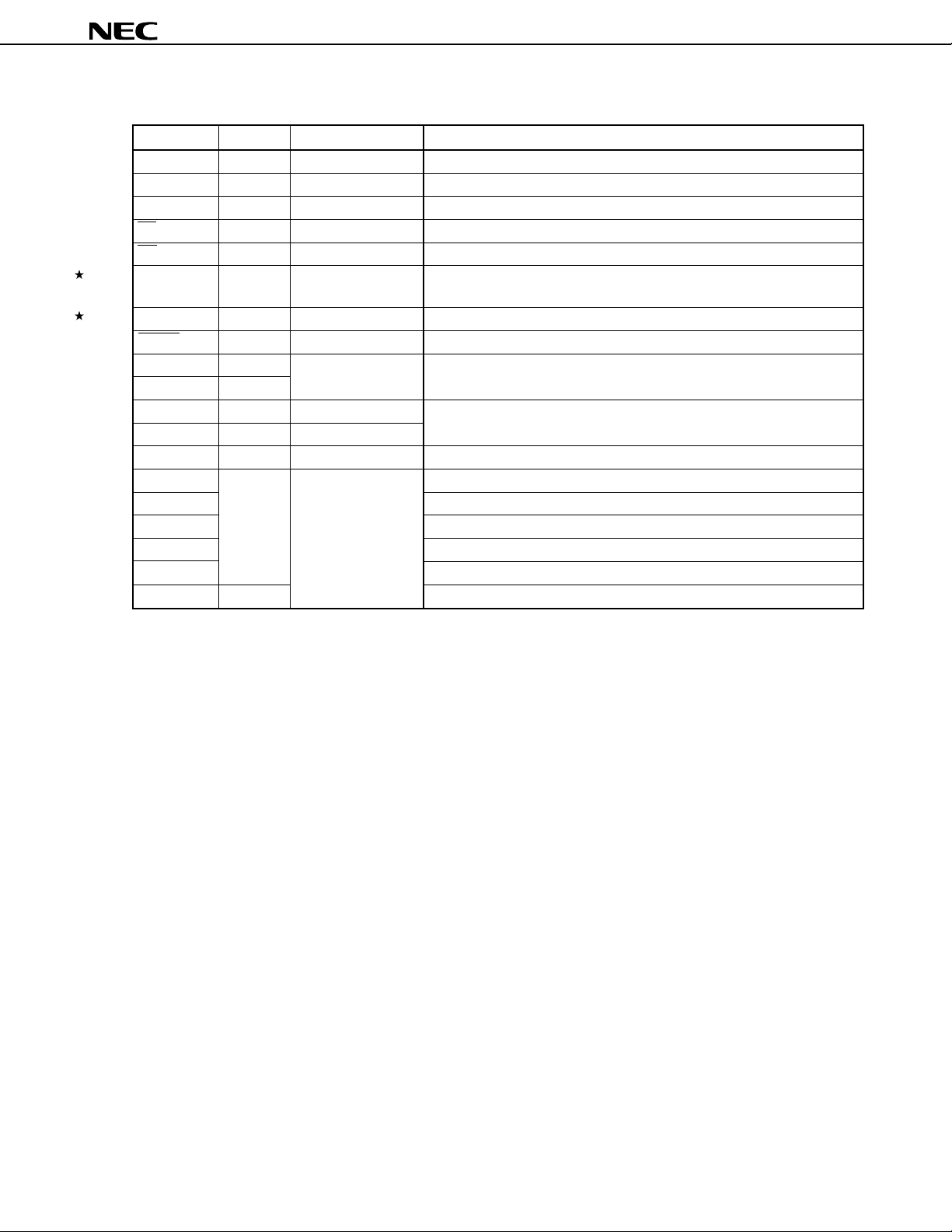

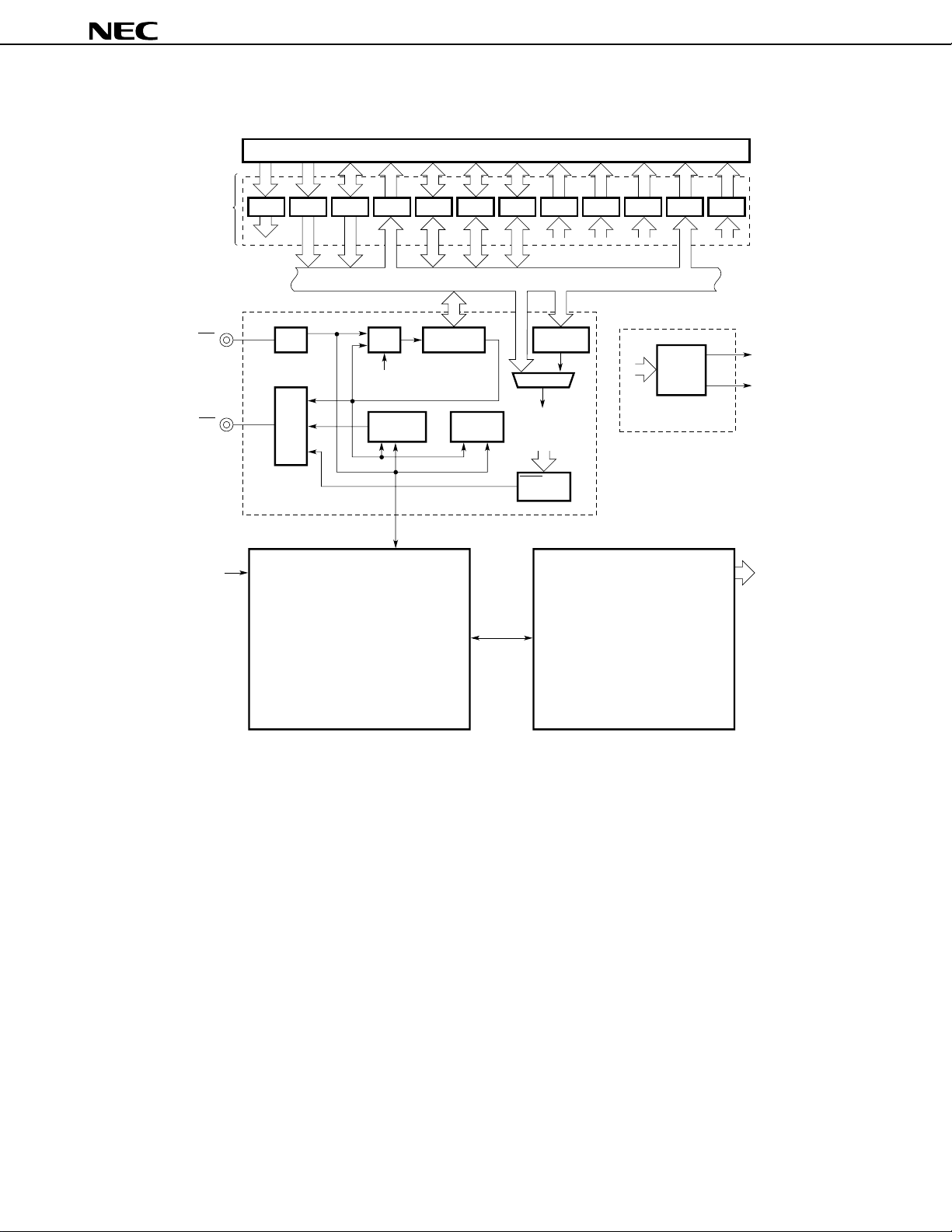

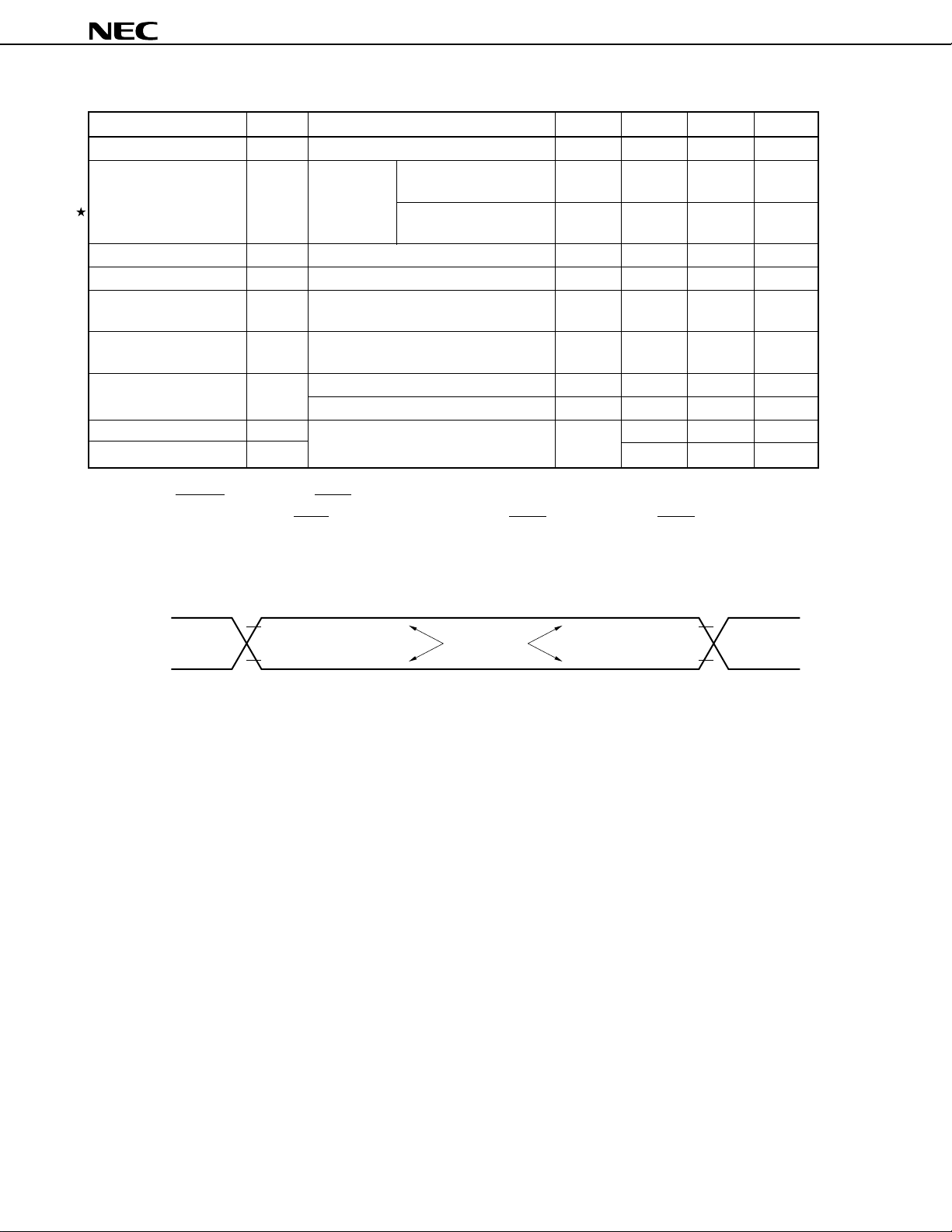

Table 6-1. Types of Pin I/O Circuits and Recommended Connections of Unused Pins (1/2)

Pin Name I/O Circuit Type I/O Recommended Connections of Unused Pins

P00 to P07 5-A I/O Input: Connect to VDD

P10, P11

P12/ASCK2/SCK2 8-A

P13/RxD2/SI2 5-A

P14/TxD2/SO2

P15 to P17

P20/NMI 2 Input Connect to VDD or VSS

P21/INTP0

P22/INTP1 2-A Connect to VDD

P23/INTP2/CI

P24/INTP3

P25/INTP4/ASCK/SCK1 8-A I/O Input: Connect to VDD

P26/INTP5 2-A Input Connect to VDD

P27/SI0

P30/RxD/SI1 5-A I/O Input: Connect to VDD

P31/TxD/SO1

P32/SCK0 10-A

P33/SO0

P34/TO0 to P37/TO3 5-A

P40/AD0 to P47/AD7

P50/A8 to P57/A15

P60/A16 to P63/A19

P64/RD

P65/WR

P66/WAIT/HLDRQ

P67/REFRQ/HLDAK

P70/ANI0 to P77/ANI7 20 I/O Input: Connect to VDD or VSS

P90 to P97 5-A

P100 to P104

P105/SCK3 10-A

P106/SI3 8-A

P107/SO3 10-A

ASTB/CLKOUT 4 Output Leave open

Output:Leave open

Output:Leave open

Output:Leave open

Output:Leave open

18

Data Sheet U11680EJ2V0DS00

Page 19

µ

PD784907, 784908

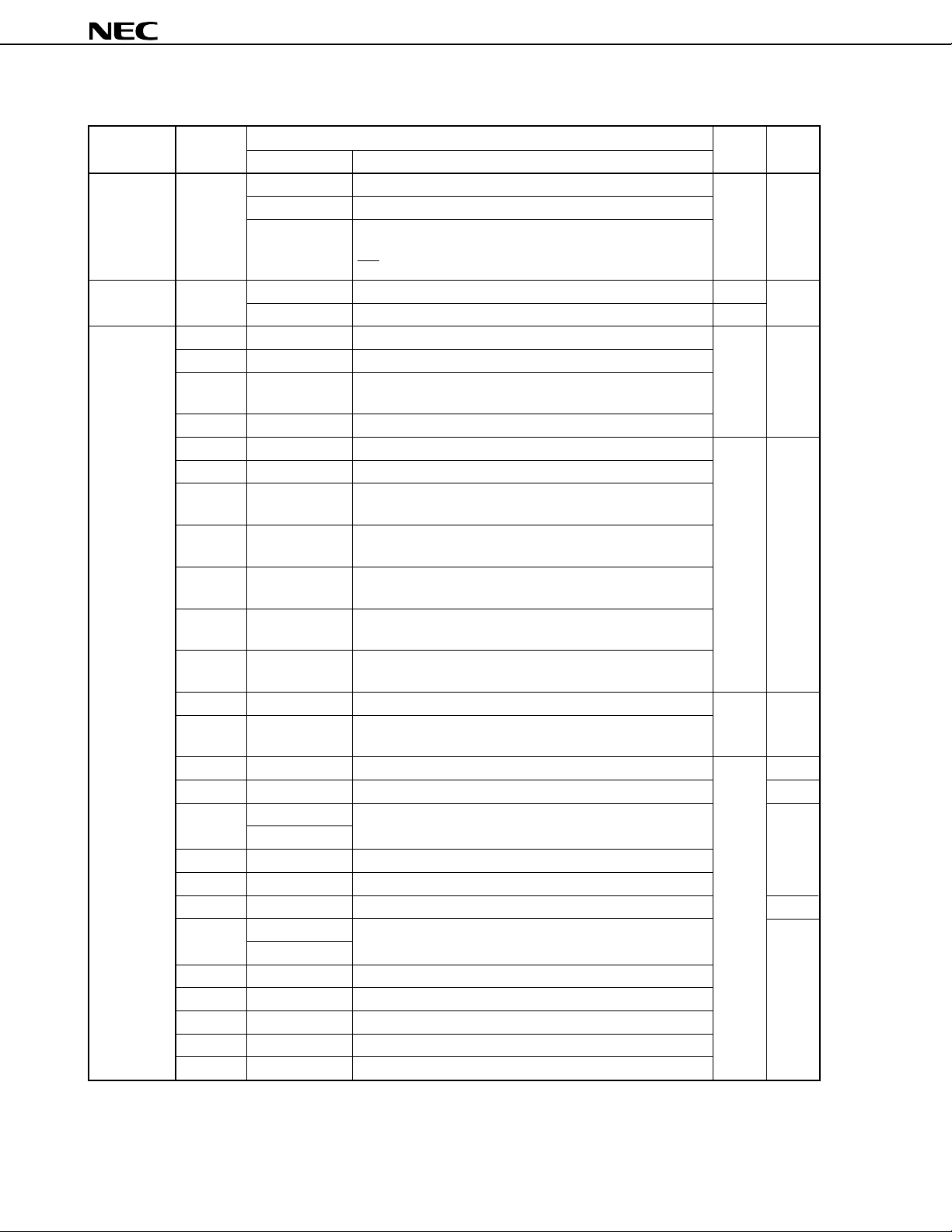

Table 6-1. Types of Pin I/O Circuits and Recommended Connections of Unused Pins (2/2)

Pin Name I/O Circuit Type I/O Recommended Connections of Unused Pins

RESET 2 Input —

TEST 1 Connect directly to VSS

XT2 — — Leave open

XT1 — Input Connect to V SS

PWM0, PWM1 3 Output Leave open

RX 1 Input Connect to VDD or VSS

TX 3 Output Leave open

AVREF1 — — Connect to VSS

AVSS

AVDD Connect to VDD

Caution Connect an I/O pin, whose input/output mode is undefined, to VDD via a resistor of several

10 kΩ (especially if the voltage on the reset input pin rises higher than the low level input at power

on or when the mode is being switched between input and output by software).

Remark Since type numbers are commonly used in the 78K Series, these numbers are not always serial in each

product (some circuits are not included).

Data Sheet U11680EJ2V0DS00

19

Page 20

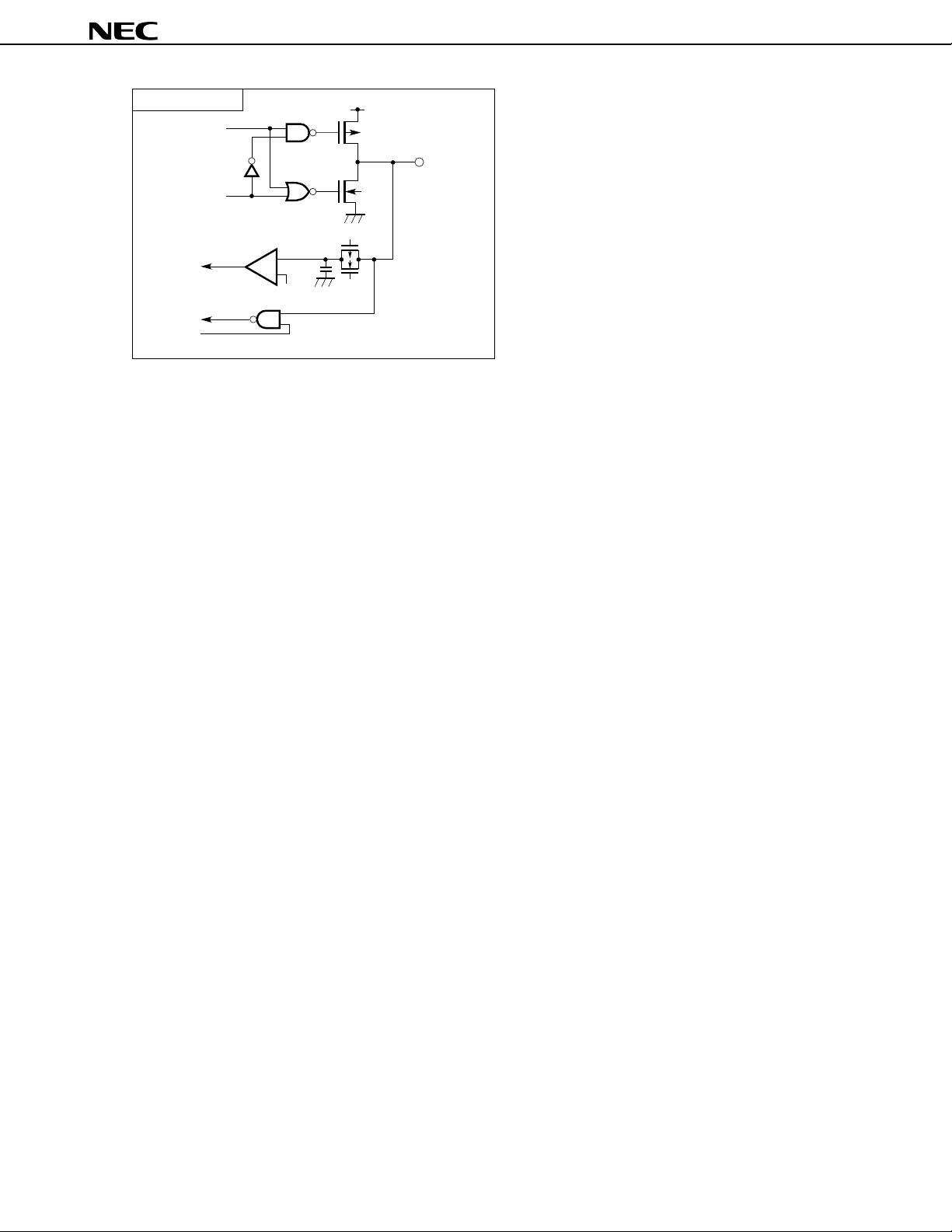

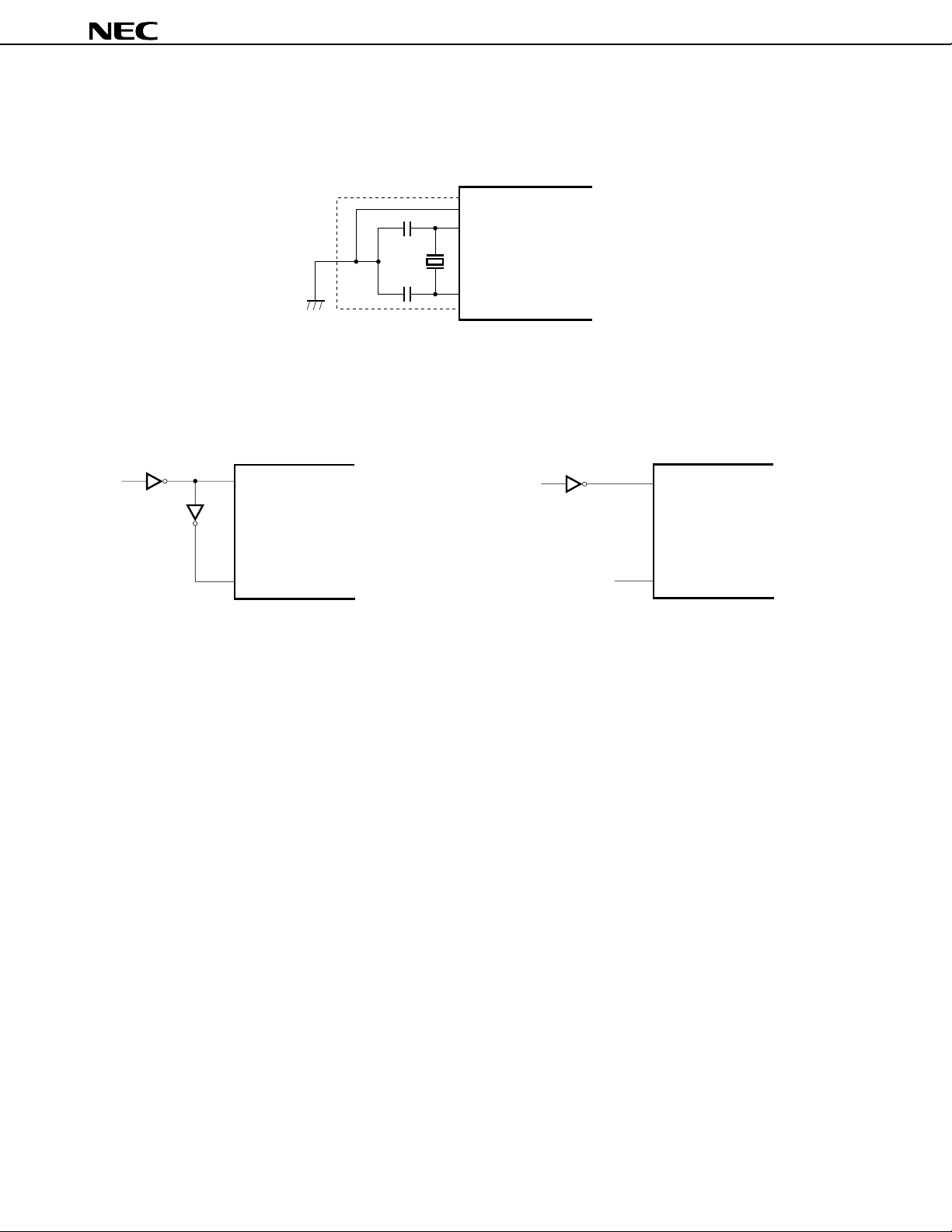

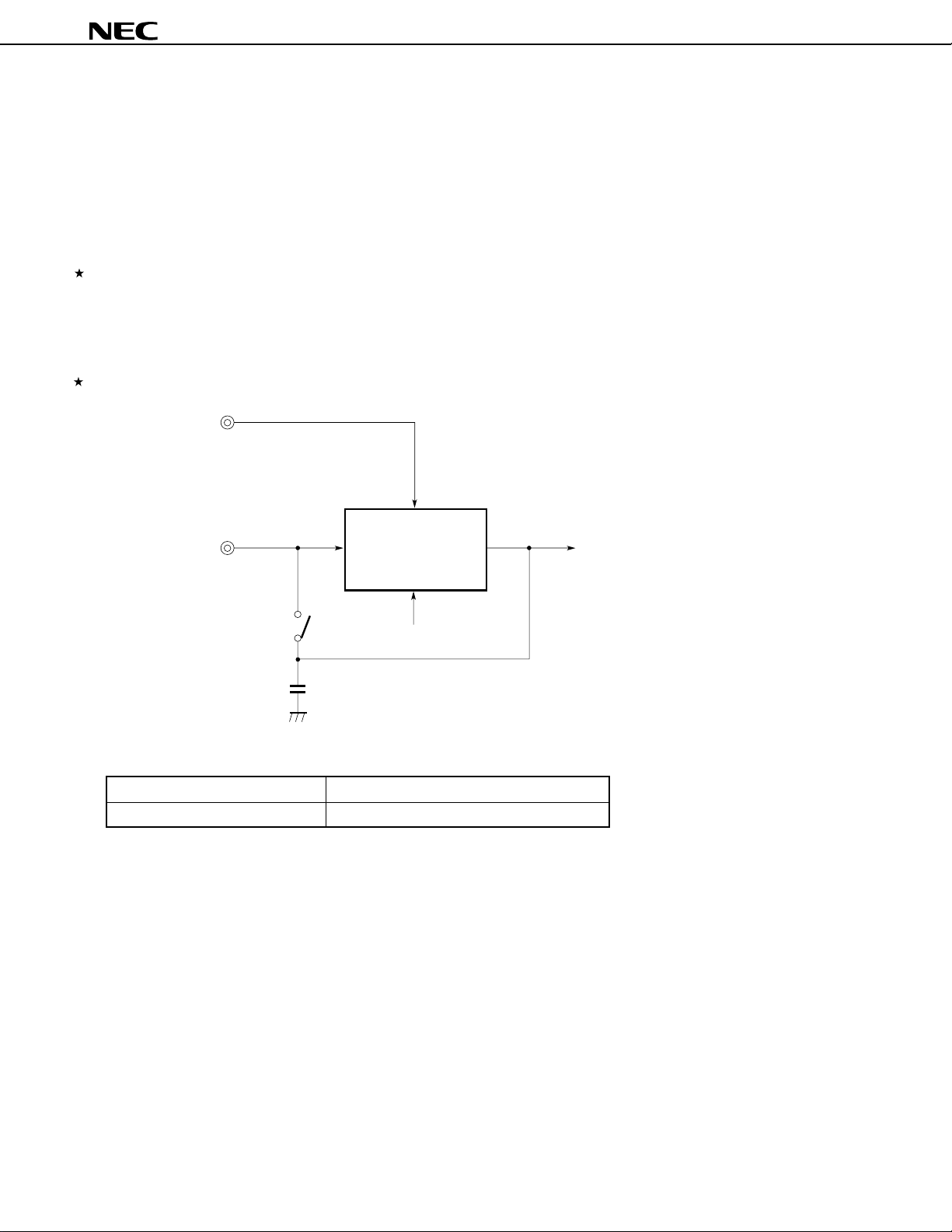

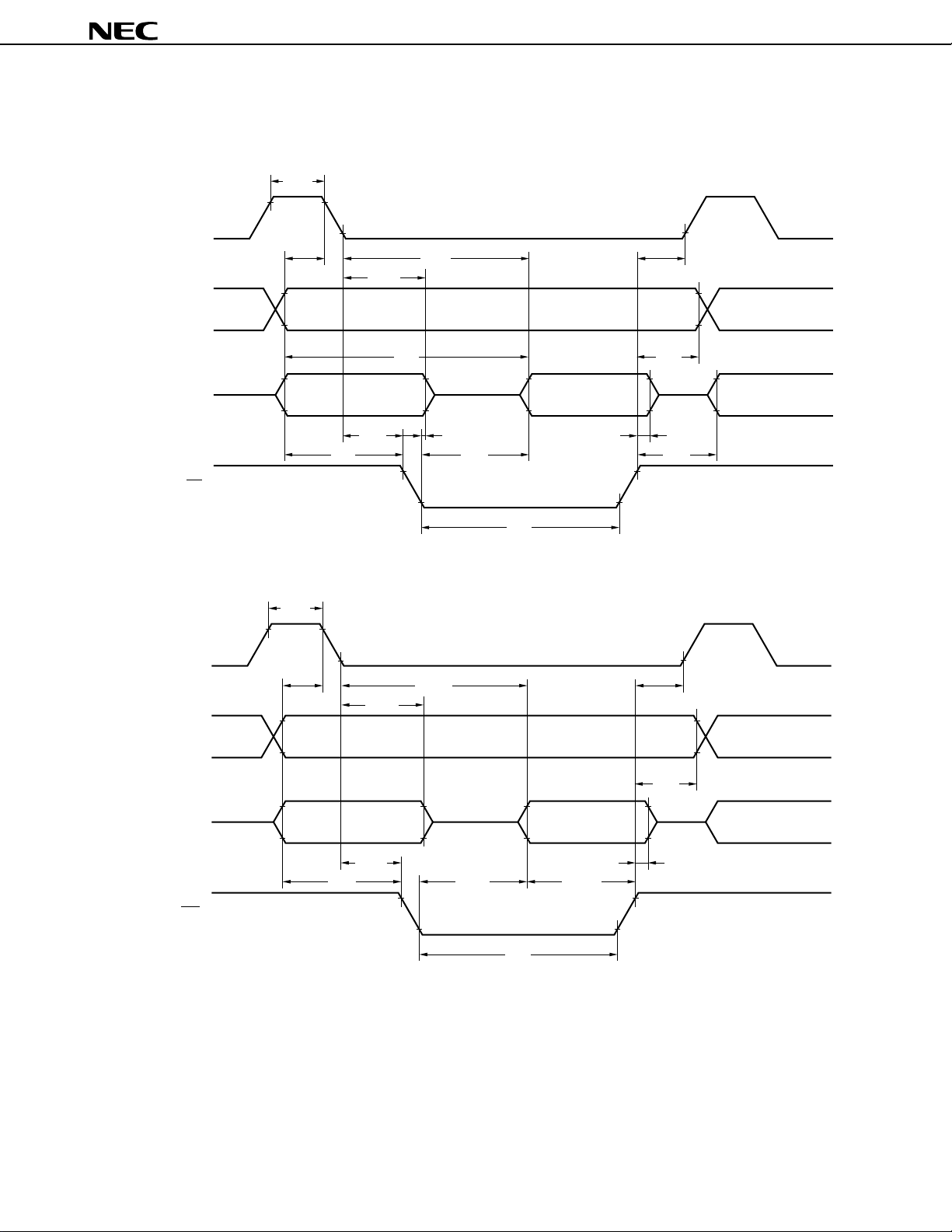

Figure 6-1. I/O Circuits for Pins

Type 1 Type 4

DD

V

P

Data

µ

PD784907, 784908

V

DD

P

OUT

IN

N

Push-pull output which can output high impedance

(both the positive and negative channels are off.)

Type 2

Type 5-A

Pull-up

enable

IN

Schmitt trigger input with hysteresis characteristics

Data

Output

disable

Input

enable

Type 2-A Type 8-A

V

DD

Output

disable

N

V

DD

P

DD

V

P

IN/OUT

N

V

DD

Pull-up

P

Pull-up

enable

enable

Data

IN

Output

disable

Schmitt trigger input with hysteresis characteristics

Type 3 Type 10-A

DD

V

Pull-up

enable

P-ch

Data

Data OUT

Open

N-ch

drain

Output

disable

V

DD

P

IN/OUT

N

P

V

DD

P

V

DD

P

IN/OUT

N

20

Data Sheet U11680EJ2V0DS00

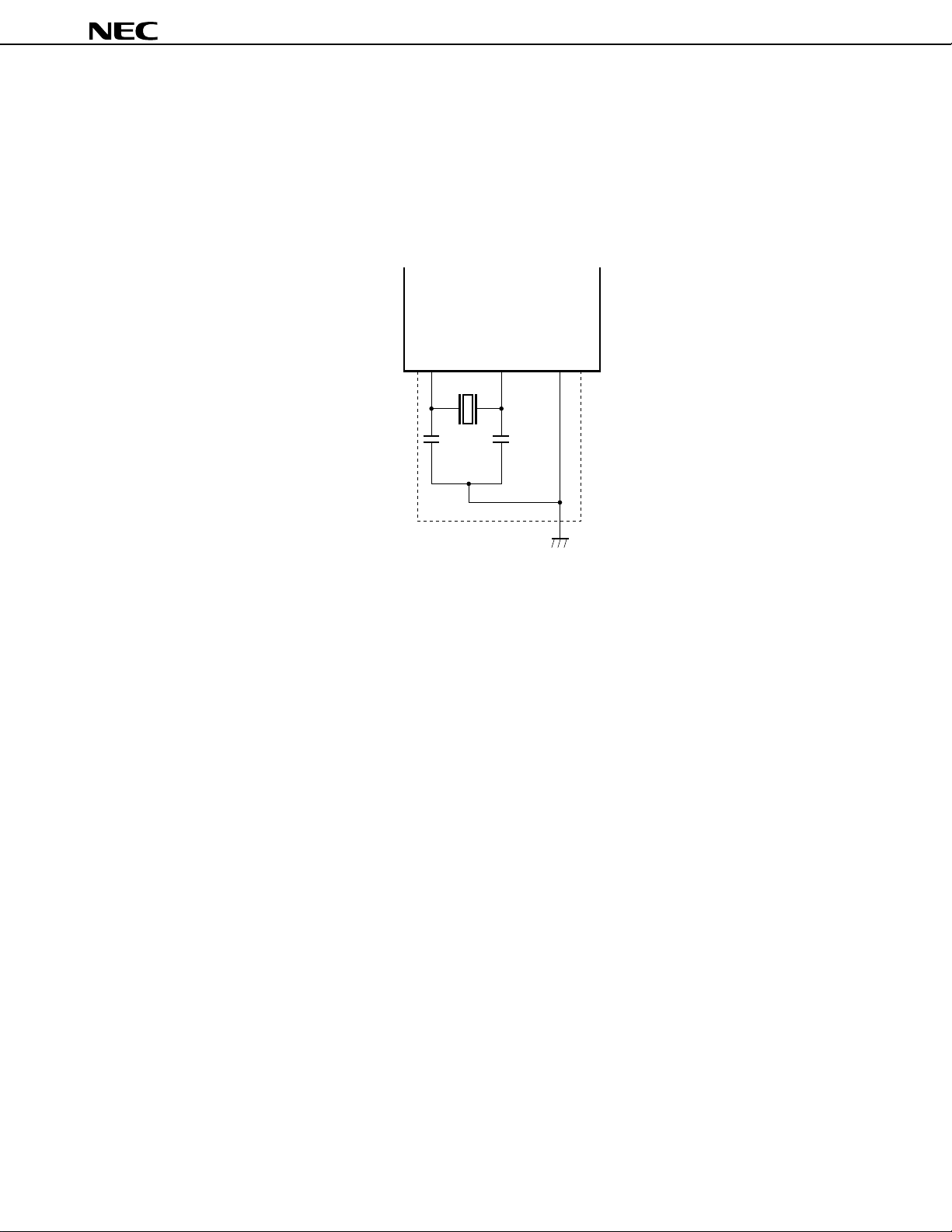

Page 21

Type 20

µ

PD784907, 784908

V

DD

Output

disable

Input

enable

Data

Comparator

(Threshold voltage)

P

IN/OUT

N

+

–

V

REF

P

N

Data Sheet U11680EJ2V0DS00

21

Page 22

µ

PD784907, 784908

7. CPU ARCHITECTURE

7.1 Memory Space

A memory space of 1 Mbyte can be accessed. By using a LOCATION instruction, the mode for mapping internal

data areas (special function registers and internal RAM) can be selected. A LOCATION instruction must always be

executed after a reset, and can be used only once.

(1) When the LOCATION 0 instruction is executed

• Internal memory

The internal data area and internal ROM area are mapped as follows:

Part Number Internal Data Area Internal ROM Area

µ

PD784907 0F100H to 0FFFFH 00000H to 0F0FFH

10000H to 17FFFH

µ

PD784908 0EE00H to 0FFFFH 00000H to 0FDFFH

10000H to 1FFFFH

Caution The following internal ROM areas, existing at the same addresses as the internal data areas,

cannot be used when the LOCATION 0 instruction is executed:

Part Number Unusable Area

µ

PD784907 0F100H to 0FFFFH (3,840 bytes)

µ

PD784908 0EE00H to 0FFFFH (4,608 bytes)

• External memory

The external memory is accessed in external memory expansion mode.

(2) When the LOCATION 0FH instruction is executed

• Internal memory

The internal data area and internal ROM area are mapped as follows:

Part Number Internal Data Area Internal ROM Area

µ

PD784907 FF100H to FFFFFH 00000H to 17FFFH

µ

PD784908 FEE00H to FFFFFH 00000H to 1FFFFH

• External memory

The external memory is accessed in external memory expansion mode.

22

Data Sheet U11680EJ2V0DS00

Page 23

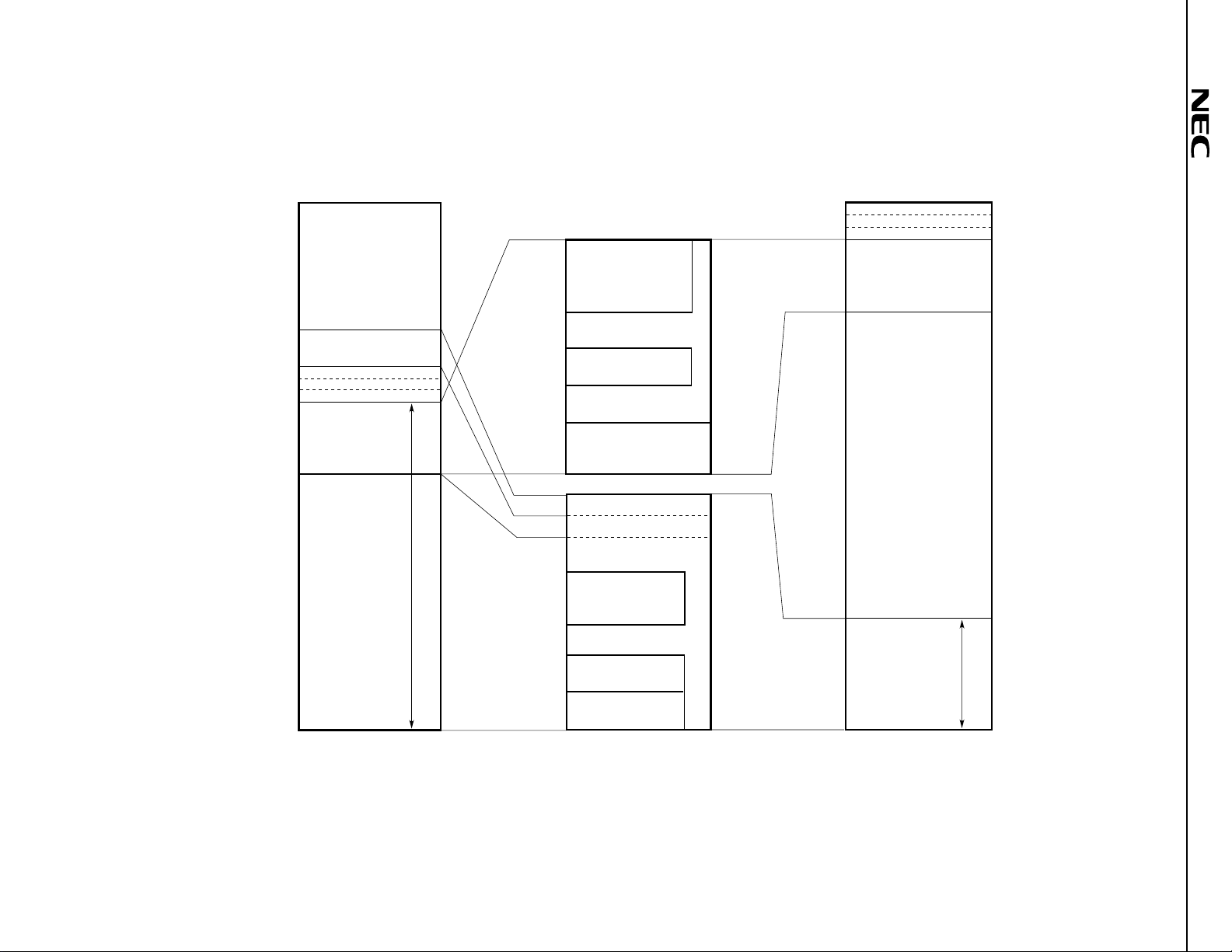

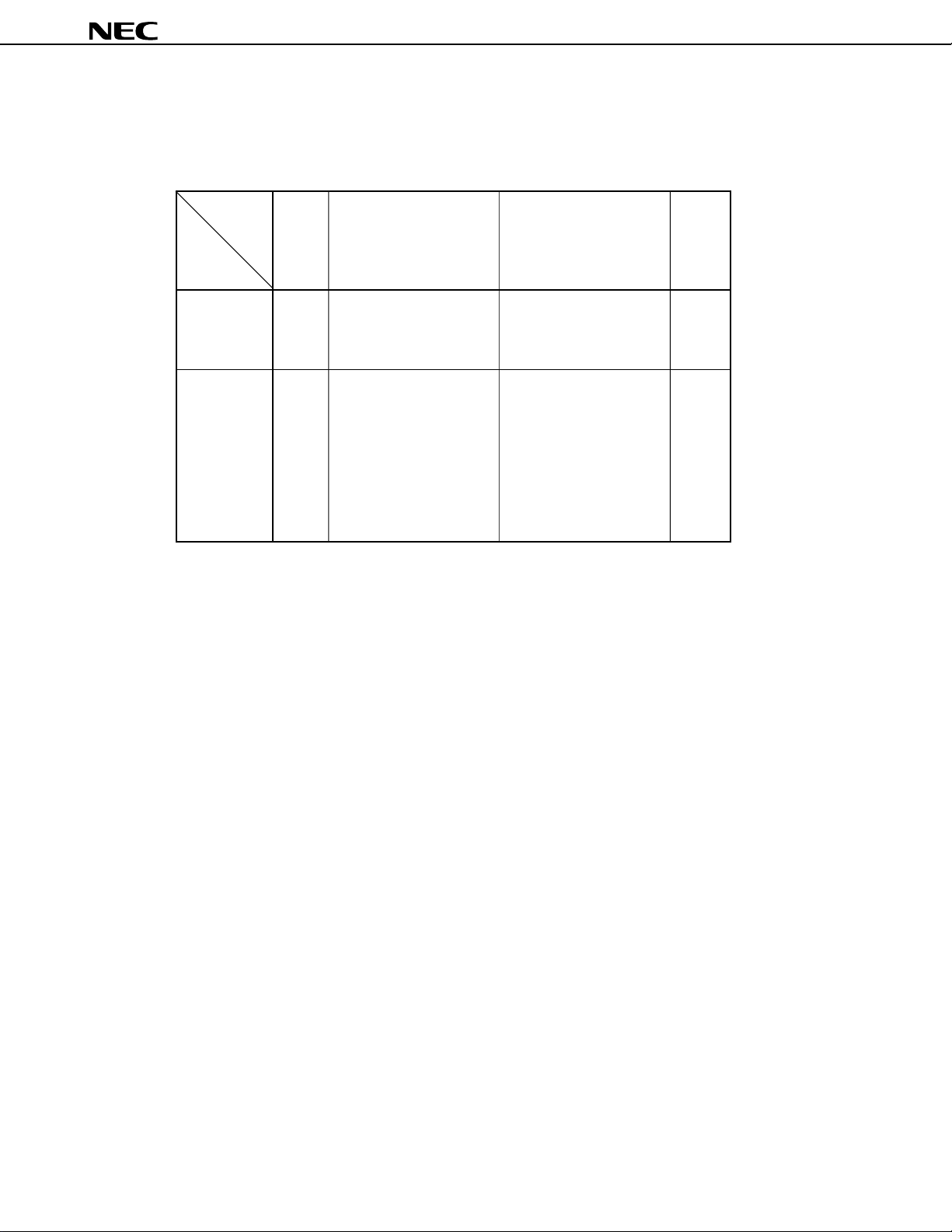

Figure 7-1.

µ

PD784907 Memory Map

Data Sheet U11680EJ2V0DS00

FFFFFH

18000H

1 7FFFH

10000H

0FFFFH

0 FFDFH

0 FFD0H

0FF00H

0FEFFH

0F100H

0F0FFH

00000H

When the LOCATION 0

instruction is executed

External memory

(928 Kbytes)

Note 1

Internal ROM

(32,768 bytes)

Special function registers (SFRs)

Note 1

(256 bytes)

Internal RAM

(3,584 bytes)

Internal ROM

(61,696 bytes)

Note 4

0FEFFH

0FE80H

0FE7FH

0FE39H

0FE06H

0 FD0 0H

0 FCFFH

0F100H

17FFFH

10000H

0F0FFH

01000H

0 0FFFH

00800H

007FFH

00080H

0007FH

00040H

0003FH

00000H

General-purpose

registers (128 bytes)

Macro service control

word area (42 bytes)

Data area (512 bytes)

Program/data area

(3,072 bytes)

Note 2

Program/data area

CALLF entry area

(2 Kbytes)

CALLT table area

(64 bytes)

Vector table area

(64 bytes)

Note 3

FFEFFH

FFE80H

FFE7FH

FFE39H

FFE06H

FFD00H

F FCFFH

FF100H

1 7FFFH

FFFFFH

FFFDFH

FFFD0H

FFF00H

FFEFFH

FF100H

FF0FFH

18000H

1 7FFFH

00000H

When the LOCATION 0FH

instruction is executed

Special function registers (SFRs)

Note 1

(256 bytes)

Internal RAM

(3,584 bytes)

External memory

(946,432 bytes)

Internal ROM

(96 Kbytes)

Note 1

Note 4

µ

PD784907, 784908

23

Notes 1. Accessed in external memory expansion mode.

2. This 3,840-byte area can be used as an internal ROM area only when the LOCATION 0FH instruction is executed.

3. When the LOCATION 0 instruction is executed: 94,464 bytes

When the LOCATION 0FH instruction is executed: 98,304 bytes

4. Base area and entry area based on a reset or interrupt. However, internal RAM is not used as a reset entry area.

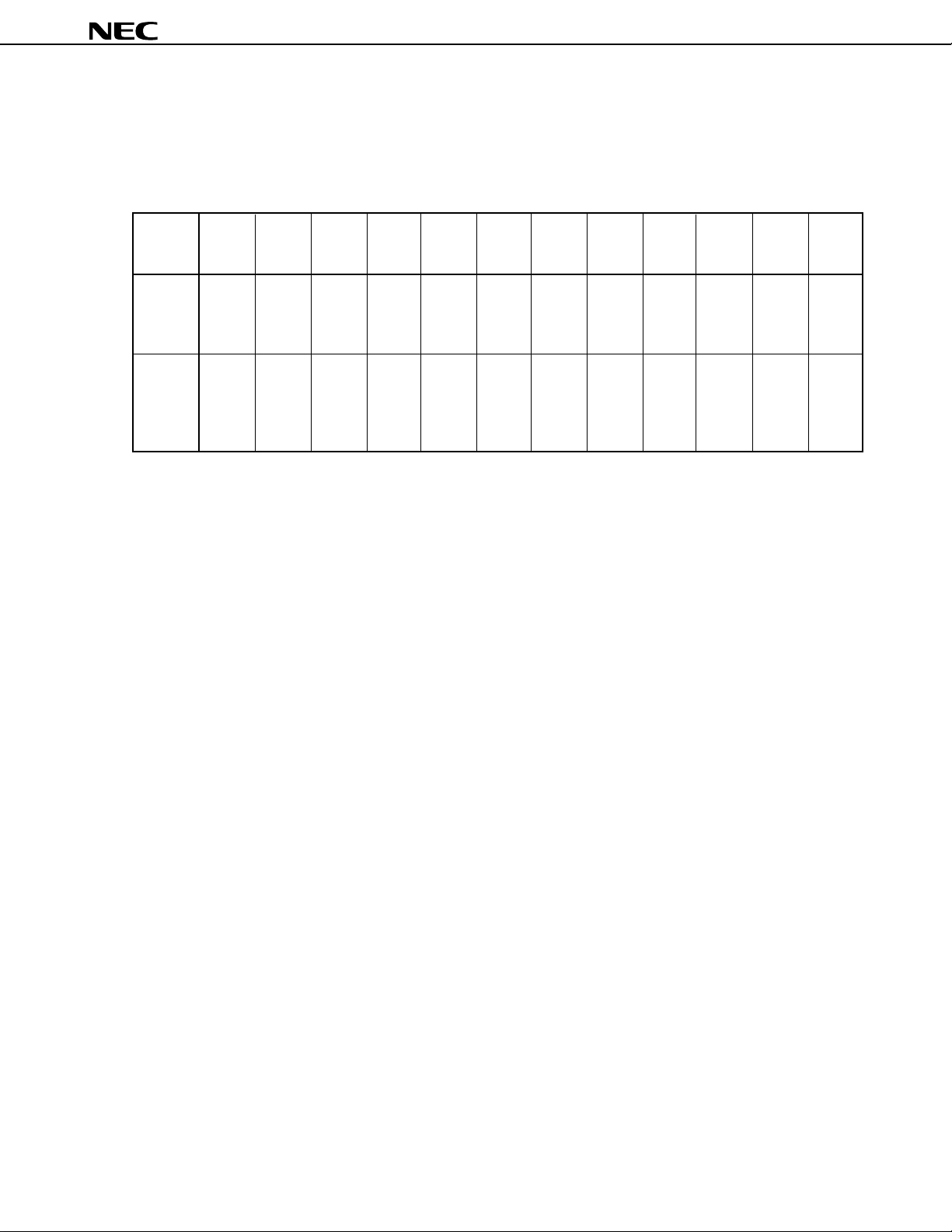

Page 24

24

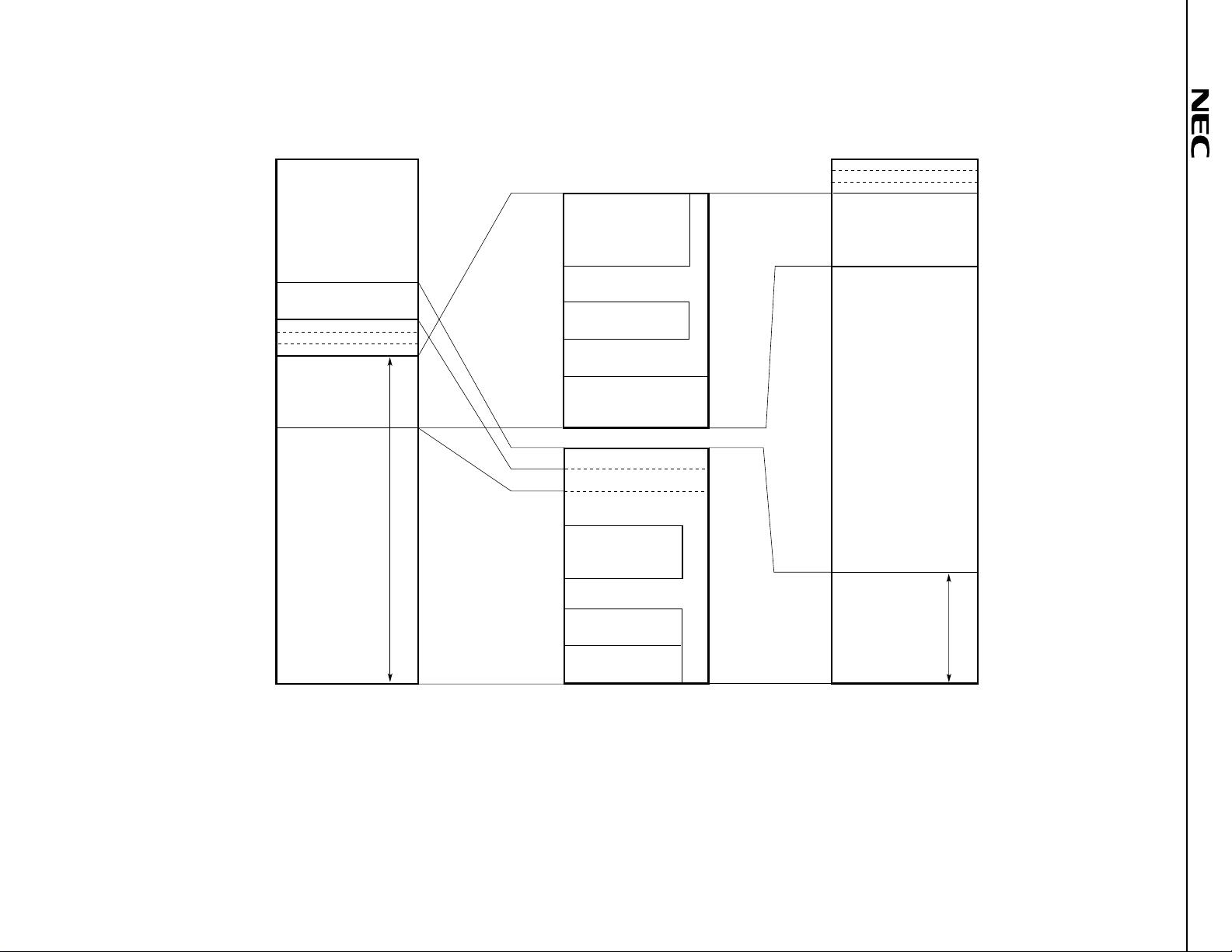

Figure 7-2.

µ

PD784908 Memory Map

Data Sheet U11680EJ2V0DS00

FFFFFH

20000H

1FFFFH

10000H

0FFFFH

0FFDFH

0FFD0H

0FF 00H

0FEFFH

0EE00H

0EDFFH

00000H

When the LOCATION 0

instruction is executed

External memory

(896 Kbytes)

Note 1

Internal ROM

(65,536 bytes)

Special function registers (SFRs)

Note 1

(256 bytes)

Internal RAM

(4,352 bytes)

Internal ROM

(60,928 bytes)

Note 4

0FEFFH

0FE8 0H

0FE7 FH

0FE3 9H

0FE0 6H

0FD00H

0FCFFH

0EE00H

1FFFFH

10000H

0EDFFH

01000H

00FFFH

00800H

007 FFH

00080H

0007FH

00040H

0003FH

00000H

General-purpose

registers (128 bytes)

Macro service control

word area (42 bytes)

Data area (512 bytes)

Program/data area

(3,840 bytes)

Note 2

Program/data area

CALLF entry area

(2 Kbytes)

CALLT table area

(64 bytes)

Vector table area

(64 bytes)

Note 3

FFEFFH

FFE 8 0H

FFE 7 FH

FFE 3 9H

FFE 0 6H

FFD00H

FFCFFH

FEE 0 0 H

1FFFFH

FFFFFH

FFFDFH

FFFD0H

FFF00H

FFEFFH

FEE 0 0 H

FEDFFH

20000H

1FFFFH

00000H

When the LOCATION 0FH

instruction is executed

Special function registers (SFRs)

Note 1

(256 bytes)

Internal RAM

(4,352 bytes)

External memory

(912,896 bytes)

Internal ROM

(128 Kbytes)

Note 1

Note 4

µ

PD784907, 784908

Notes 1. Accessed in external memory expansion mode.

2. This 4,608-byte area can be used as an internal ROM area only when the LOCATION 0FH instruction is executed.

3. When the LOCATION 0 instruction is executed: 126,464 bytes

When the LOCATION 0FH instruction is executed: 131,072 bytes

4. Base area and entry area based on a reset or interrupt. However, internal RAM is not used as a reset entry area.

Page 25

µ

PD784907, 784908

7.2 CPU Registers

7.2.1 General-purpose registers

A set of general-purpose registers consists of sixteen 8-bit general-purpose registers. Two 8-bit general-purpose

registers can be combined to form a 16-bit general-purpose register. Moreover, four 16-bit general-purpose registers,

when combined with an 8-bit register for address extension, can be used as 24-bit address specification registers.

Eight banks of this register set are provided. The user can switch between banks by software or the context switching

function.

General-purpose registers other than the V, U, T, and W registers used for address extension are mapped onto

internal RAM.

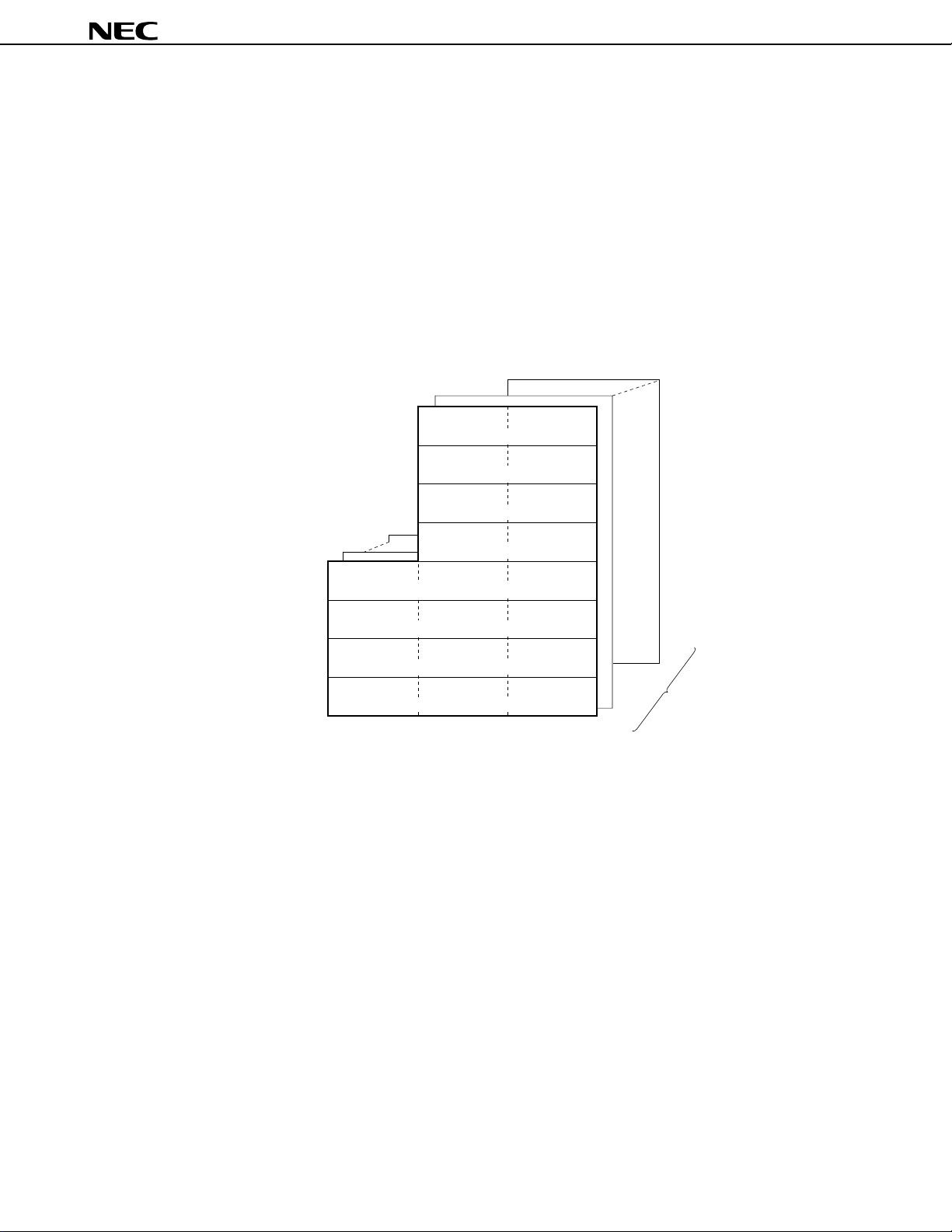

Figure 7-3. General-Purpose Register Format

A (R1) X (R0)

AX (RP0)

B (R3) C (R2)

BC (RP1)

R5 R4

RP2

R7 R6

RP3

V

VVP (RG4)

U

UUP (RG5)

T

TDE (RG6)

W L (R14)

WHL (RG7)

The character strings enclosed in

parentheses represent absolute names.

R9 R8

VP (RP4)

R11 R10

UP (RP5)

D (R13) E (R12)

DE (RP6)

H (R15)

HL (RP7)

8 banks

Caution By setting the RSS bit of PSW to 1, R4, R5, R6, R7, RP2, and RP3 can be used as the X, A, C,

B, AX, and BC registers, respectively. However, this function must be used only when using

programs for the 78K/III series.

Data Sheet U11680EJ2V0DS00

25

Page 26

µ

PD784907, 784908

7.2.2 Control registers

(1) Program counter (PC)

This register is a 20-bit program counter. The program counter is automatically updated by program execution.

Figure 7-4. Format of Program Counter (PC)

19 0

PC

(2) Program Status Word (PSW)

This register holds the CPU state. The program status word is automatically updated by program execution.

Figure 7-5. Format of Program Status Word (PSW)

PSW

PSWH

PSWL

15 14 13 12

UF RBS2 RBS1 RBS0

76543210

S Z RSS

Note

AC IE P/V 0 CY

11 10 9 8

Note This flag is used to maintain compatibility with the 78K/III Series. This flag must be set to 0 when

programs for the 78K/III Series are not being used.

(3) Stack pointer (SP)

This register is a 24-bit pointer for holding the start address of the stack.

The higher 4 bits must be set to 0.

Figure 7-6. Format of Stack Pointer (SP)

23 20 0

SP 0 0 0 0

26

Data Sheet U11680EJ2V0DS00

Page 27

µ

PD784907, 784908

7.2.3 Special function registers (SFRs)

The special function registers are registers with special functions such as mode registers and control registers for

built-in peripheral hardware. The special function registers are mapped onto the 256-byte space between 0FF00H

Note

and 0FFFFH

Note On execution of the LOCATION 0 instruction. FFF00H to FFFFFH when the LOCATION 0FH instruction

Caution Do not access an address in this area where no SFR is allocated, as the

Table 7-1 lists the special function registers (SFRs). The symbols of the table columns are explained below.

• Symbol.................................... Symbol indicating an on-chip SFR. The symbols listed in the table are reserved

• R/W ......................................... Indicates whether the SFR is read-only, write-only, or read/write.

• Bit units for manipulation ....... Indicates the maximum number of bits that can be manipulated whenever an SFR

• After reset............................... Indicates the state of the register when the RESET signal has been input.

.

is executed.

in the deadlock state. The deadlock state can be cleared only by a reset.

words for the NEC assembler (RA78K4). In the C compiler (CC78K4), the

symbols can be used as sfr variables with the #pragma sfr command.

R/W: Read/write

R: Read-only.

W: Write-only.

is manipulated. An SFR that supports 16-bit manipulation can be described in

the sfrp operand. For address specification, an even-numbered address must

be specified.

An SFR that can be manipulated in 1-bit units can be described as the operand

of a bit manipulation instruction.

µ

PD784908 may be placed

Data Sheet U11680EJ2V0DS00

27

Page 28

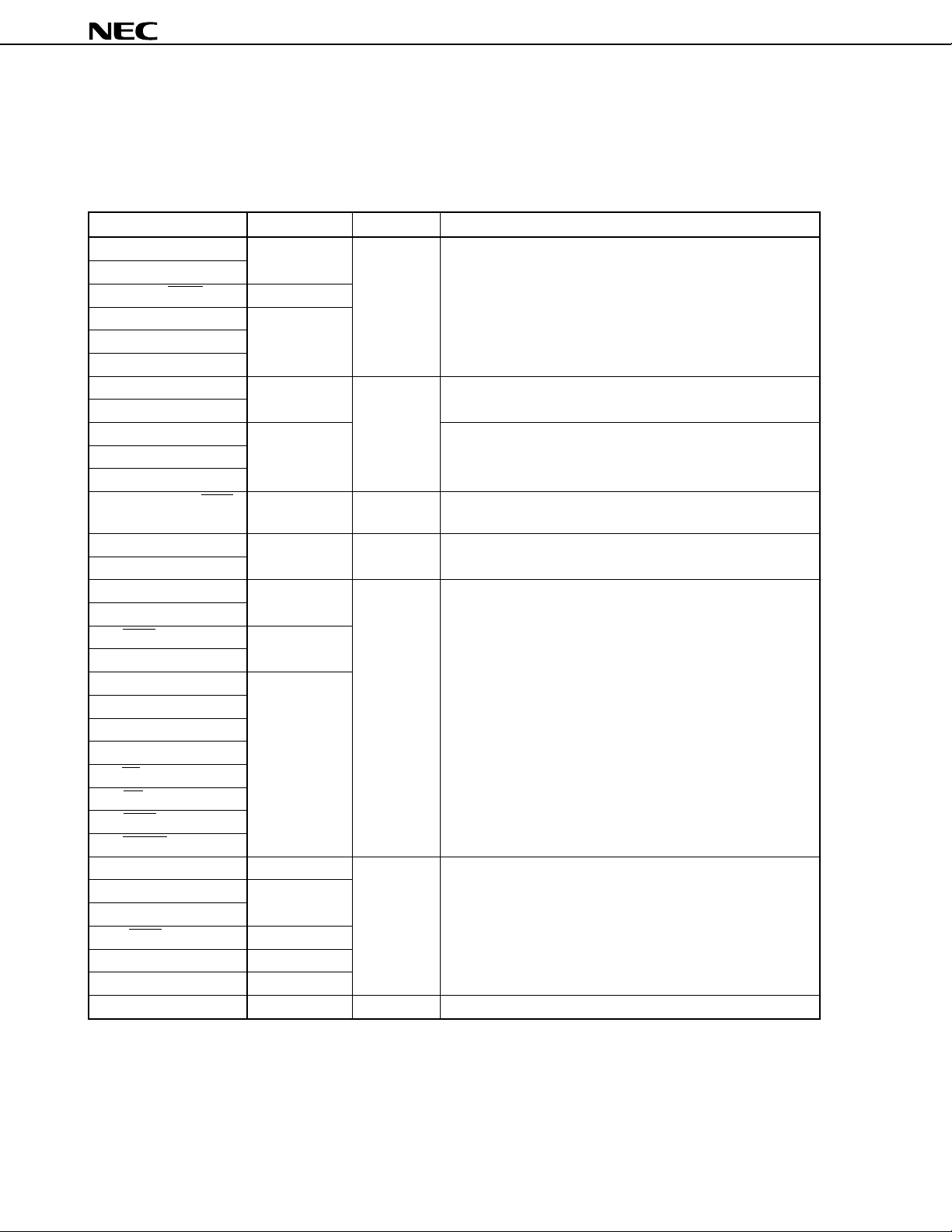

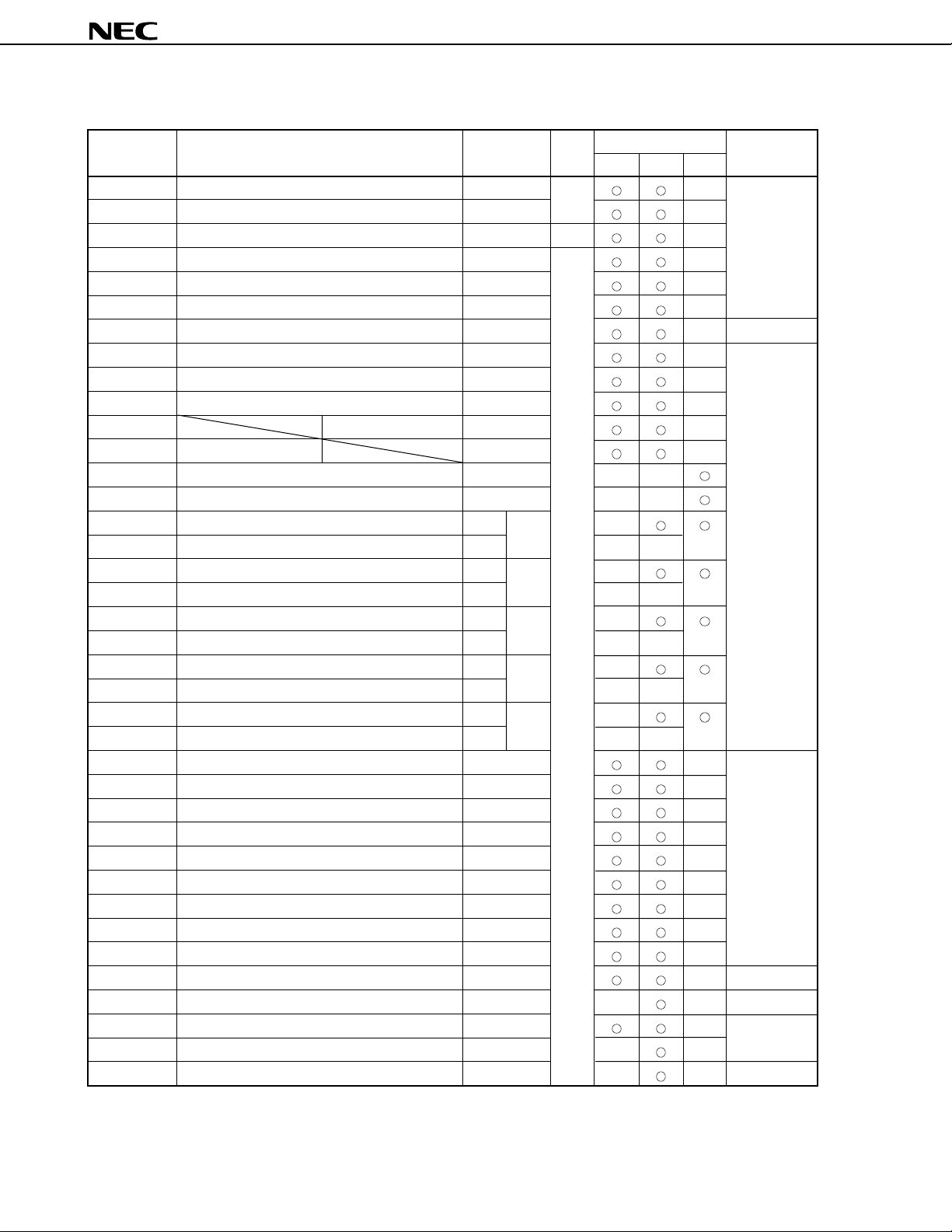

Table 7-1. Special Function Registers (SFRs) (1/5)

µ

PD784907, 784908

Address

0FF00H Port 0 P0 R/W — Undefined

0FF01H Port 1 P1 —

0FF02H Port 2 P2 R —

0FF03H Port 3 P3 R/W —

0FF04H Port 4 P4 —

0FF05H Port 5 P5 —

0FF06H Port 6 P6 — 00H

0FF07H Port 7 P7 — Undefined

0FF09H Port 9 P9 —

0FF0AH Port 10 P10 —

0FF0EH Port 0 buffer register L P0L —

0FF0FH Port 0 buffer register H P0H —

0FF10H Compare register (timer/counter 0) CR00 — —

0FF12H Capture/compare register (timer/counter 0) CR01 — —

0FF14H Compare register L (timer/counter 1) CR10

0FF15H Compare register H (timer/counter 1) — — —

0FF16H Capture/compare register L (timer/counter 1) CR11

0FF17H Capture/compare register H (timer/counter 1) — — —

0FF18H Compare register L (timer/counter 2) CR20

0FF19H Compare register H (timer/counter 2) — — —

0FF1AH Capture/compare register L (timer/counter 2) CR21

0FF1BH Capture/compare register H (timer/counter 2) — — —

0FF1CH Compare register L (timer 3) CR30

0FF1DH Compare register H (timer 3) — — —

0FF20H Port 0 mode register PM0 — FFH

0FF21H Port 1 mode register PM1 —

0FF23H Port 3 mode register PM3 —

0FF24H Port 4 mode register PM4 —

0FF25H Port 5 mode register PM5 —

0FF26H Port 6 mode register PM6 —

0FF27H Port 7 mode register PM7 —

0FF29H Port 9 mode register PM9 —

0FF2AH Port 10 mode register PM10 —

0FF2EH Real-time output port control register RTPC — 00H

0FF30H Capture/compare control register 0 CRC0 — — 10H

0FF31H Timer output control register TOC — 00H

0FF32H Capture/compare control register 1 CRC1 — —

0FF33H Capture/compare control register 2 CRC2 —

Note

Special Function Register (SFR) Name Symbol R/W

CR10W

CR11W

CR20W

CR21W

CR30W

Bit Units for Manipulation

1 bit 8 bits 16 bits

—

—

—

—

—

— 10H

After Reset

Note When the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed, F0000H

is added to each address.

28

Data Sheet U11680EJ2V0DS00

Page 29

µ

Table 7-1. Special Function Registers (SFRs) (2/5)

PD784907, 784908

Address

0FF36H Capture register (timer/counter 0) CR02 R — — 0000H

0FF38H Capture register L (timer/counter 1) CR12

0FF39H Capture register H (timer/counter 1) — — —

0FF3AH Capture register L (timer/counter 2) CR22

0FF3BH Capture register H (timer/counter 2) — — —

0FF41H Port 1 mode control register PMC1 R/W — 00H

0FF43H Port 3 mode control register PMC3 —

0FF4AH Port 10 mode control register PMC10 —

0FF4EH Register L for optional pull-up resistor PUOL —

0FF4FH Register H for optional pull-up resistor PUOH —

0FF50H Timer register 0 TM0 R — — 0000H

0FF51H ——

0FF52H Timer register 1 TM1 TM1W —

0FF53H — — —

0FF54H Timer register 2 TM2 TM2W —

0FF55H — — —

0FF56H Timer register 3 TM3 TM3W —

0FF57H — — —

0FF5CH Prescaler mode register 0 PRM0 R/W — — 11H

0FF5DH Timer control register 0 TMC0 — 00H

0FF5EH Prescaler mode register 1 PRM1 — — 11H

0FF5FH Timer control register 1 TMC1 — 00H

0FF68H A/D converter mode register ADM — 00H

0FF6AH A/D conversion result register ADCR R — — Undefined

0FF6CH A/D current cut selection register IEAD R/W — 00H

0FF6FH Clock timer mode register WM —

0FF70H PWM control register PWMC — 05H

0FF71H PWM prescaler register PWPR — — 00H

0FF72H PWM modulo register 0 PWM0 — — Undefined

0FF74H PWM modulo register 1 PWM1 — —

0FF7DH One-shot pulse output control register OSPC — 00H

0FF80H Clocked serial interface mode register 3 CSIM3 —

0FF82H Clocked serial interface mode register CSIM

Note

Special Function Register (SFR) Name Symbol R/W

CR12W

CR22W

Bit Units for Manipulation

1 bit 8 bits 16 bits

—

—

—

After Reset

Note When the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed, F0000H

is added to each address.

Data Sheet U11680EJ2V0DS00

29

Page 30

Table 7-1. Special Function Registers (SFRs) (3/5)

µ

PD784907, 784908

Address

0FF84H Clocked serial interface mode register 1 CSIM1 R/W — 00H

0FF85H Clocked serial interface mode register 2 CSIM2 —

0FF86H Serial shift register SIO — — Undefined

0FF88H Asynchronous serial interface mode register ASIM — 00H

0FF89H Asynchronous serial interface mode register 2 ASIM2 —

0FF8AH Asynchronous serial interface status register ASIS R —

0FF8BH Asynchronous serial interface status register 2 ASIS2 —

0FF8CH Serial receive buffer: UART0 RXB — — Undefined

0FF8DH Serial receive buffer: UART2 RXB2 R — —

0FF8EH Serial shift register 3: IOE3 SIO3 — —

0FF90H Baud rate generator control register BRGC — — 00H

0FF91H Baud rate generator control register 2 BRGC2 — —

0FFA0H External interrupt mode register 0 INTM0 —

0FFA1H External interrupt mode register 1 INTM1 —

0FFA4H Sampling clock selection register SCS0 — —

0FFA8H In-service priority register ISPR R —

0FFAAH Interrupt mode control register IMC R/W — 80H

0FFACH Interrupt mask register 0L MK0L MK0 FFFFH

0FFADH Interrupt mask register 0H MK0H

0FFAEH Interrupt mask register 1L MK1L MK1 FFFFH

0FFAFH Interrupt mask register 1H MK1H

0FFB0H Bus control register BCR — 00H

0FFB2H Unit address register UAR — — 0000H

0FFB4H Slave address register SAR — —

0FFB6H Partner address register PAR R — —

0FFB8H Control data register CDR R/W — — 01H

0FFB9H Telegraph length register DLR — —

Note

Special Function Register (SFR) Name Symbol R/W

Serial transmission shift register: UART0 TXS W — —

Serial shift register: IOE1 SIO1 R/W — —

Serial transmission shift register: UART2 TXS2 W — —

Serial shift register: IOE2 SIO2 R/W — —

Bit Units for Manipulation

1 bit 8 bits 16 bits

After Reset

Note Applicable when the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed,

F0000H is added to each address.

30

Data Sheet U11680EJ2V0DS00

Page 31

µ

PD784907, 784908

Table 7-1. Special Function Registers (SFRs) (4/5)

Note

Address

0FFBAH Data register DR R/W — — 00H

0FFBBH Unit status register USR R —

0FFBCH Interrupt status register ISR R/W —

0FFBDH Slave status register SSR R — 41H

0FFBEH Success count register SCR — — 01H

0FFBFH Communication count register CCR — — 20H

0FFC0H Standby control register STBC R/W —

0FFC2H Watchdog timer mode register WDM —

0FFC4H Memory expansion mode register MM — 20H

0FFC5H Hold mode register HLDM — 00H

0FFC6H Clock output mode register CLOM —

0FFC7H Programmable wait control register 1 PWC1 — — AAH

0FFC8H Programmable wait control register 2 PWC2 — — AAAAH

0FFCCH Refresh mode register RFM — 00H

0FFCDH Refresh area specification register RFA —

0FFCFH Oscillation stabilization time specification register OSTS — —

0FFD0H to External SFR area — — —

0FFDFH

0FFE0H Interrupt control register (INTP0) PIC0 — 43H

0FFE1H Interrupt control register (INTP1) PIC1 —

0FFE2H Interrupt control register (INTP2) PIC2 —

0FFE3H Interrupt control register (INTP3) PIC3 —

0FFE4H Interrupt control register (INTC00) CIC00 —

0FFE5H Interrupt control register (INTC01) CIC01 —

0FFE6H Interrupt control register (INTC10) CIC10 —

0FFE7H Interrupt control register (INTC11) CIC11 —

0FFE8H Interrupt control register (INTC20) CIC20 —

0FFE9H Interrupt control register (INTC21) CIC21 —

0FFEAH Interrupt control register (INTC30) CIC30 —

0FFEBH Interrupt control register (INTP4) PIC4 —

0FFECH Interrupt control register (INTP5) PIC5 —

0FFEDH Interrupt control register (INTAD) ADIC —

0FFEEH Interrupt control register (INTSER) SERIC —

Special Function Register (SFR) Name Symbol R/W

Bit Units for Manipulation

1 bit 8 bits 16 bits

Note 2

Note 2

— 30H

— 00H

After Reset

Notes 1. When the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed,

F0000H is added to each address.

2. A write operation can be performed only with special instructions MOV STBC,#byte and MOV

WDM,#byte. Other instructions cannot perform a write operation.

Data Sheet U11680EJ2V0DS00

31

Page 32

µ

PD784907, 784908

Table 7-1. Special Function Registers (SFRs) (5/5)

Note

Address

0FFEFH Interrupt control register (INTSR) SRIC R/W — 43H

0FFF0H Interrupt control register (INTST) STIC —

0FFF1H Interrupt control register (INTCSI) CSIIC —

0FFF2H Interrupt control register (INTSER2) SERIC2 —

0FFF3H Interrupt control register (INTSR2) SRIC2 —

0FFF4H Interrupt control register (INTST2) STIC2 —

0FFF6H Interrupt control register (INTIE1) IEIC1 —

0FFF7H Interrupt control register (INTIE2) IEIC2 —

0FFF8H Interrupt control register (INTW) WIC —

0FFF9H Interrupt control register (INTCSI3) CSIIC3 —

0FFFCH Internal memory size switching register

Special Function Register (SFR) Name Symbol R/W

Interrupt control register (INTCSI1) CSIIC1 —

Interrupt control register (INTCSI2) CSIIC2 —

Note 2

IMS — — FFH

Bit Units for Manipulation

1 bit 8 bits 16 bits

After Reset

Notes 1. When the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed,

F0000H is added to each address.

2. A write to this register is meaningful only for the µPD78P4908.

32

Data Sheet U11680EJ2V0DS00

Page 33

µ

PD784907, 784908

8. PERIPHERAL HARDWARE FUNCTIONS

8.1 Ports

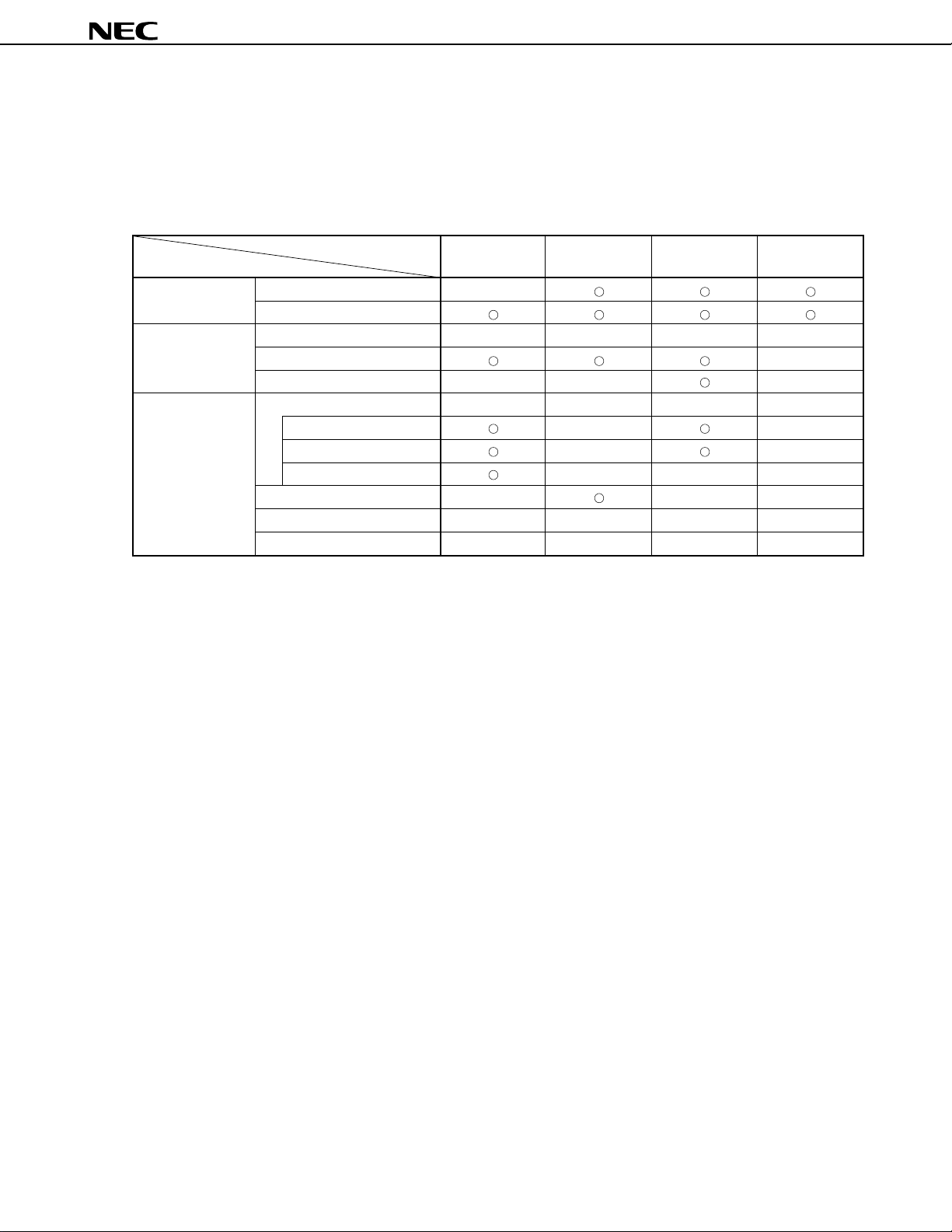

The ports shown in Figure 8-1 are provided to make various control operations possible. Table 8-1 shows the

functions of the ports. When inputting to port 0 to port 6, port 9, and port 10, an on-chip pull-up resistor can be specified

by software.

Figure 8-1. Port Configuration

P00

Port 0

P07

P10

Port 1

P17

Port 9

Port 10

P90

P97

P30

P37

P40

P47

P50

P57

P60

P67

P70P100

Port 2P20 to P27

8

Port 3

Port 4

Port 5

Port 6

Port 7

P107

Data Sheet U11680EJ2V0DS00

P77

33

Page 34

µ

PD784907, 784908

Table 8-1. Port Functions

Port Name Pin Name Function Specification of Pull-up Resistor Connection by Software

Port 0 P00 to P07 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Operable as 4-bit real-time outputs

(P00 to P03, P04 to P07)

• Can drive transistors

Port 1 P10 to P17 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Can drive LEDs

Port 2 P20 to P27 • Input port In 6-bit units (P22 through P27)

Port 3 P30 to P37 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Either pin P32/SCK0 or P33/SO0 can be

set as the N-ch open drain.

Port 4 P40 to P47 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Can drive LEDs

Port 5 P50 to P57 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Can drive LEDs

Port 6 P60 to P67 • Input or output mode can be specified All port pins in input mode

in 1-bit units

Port 7 P70 to P77 • Input or output mode can be specified —

in 1-bit units

Port 9 P90 to P97 • Input or output mode can be specified All port pins in input mode

in 1-bit units

Port 10 P100 to P107 • Input or output mode can be specified All port pins in input mode

in 1-bit units

• Either pin P105/SCK3 or P107/SO3 can

be set as the N-ch open drain.

34

Data Sheet U11680EJ2V0DS00

Page 35

µ

PD784907, 784908

8.2 Clock Generator

A circuit for generating the clock signal required for operation is provided. The clock generator has a frequency

divider. If high-speed operation is not necessary, the internal operating frequency can be lowered by the frequency

divider to reduce the current consumption.

Figure 8-2. Block Diagram of Clock Generator

Clock-synchronized 3-wire serial I/O (CSI)

Asynchronous serial I/O (UART/IOE)

INTP0 noise eliminator

X1

X2

Oscillator

Oscillation settling timer

Timer/counter

XX

f

1/2 1/2 1/2

STBC.7

XX

/8

f

XX

/4

f

f

XX

/2

STBC.4, 5

Selector

f

CLK

CPU

Peripheral circuits

1

0

Selector

Watch clock

Main clock

Watch timer

Note Set bit 7 of the standby control register (STBC) to 1.

Remark f

XX: Oscillator frequency or external clock input frequency

fCLK: Internal operating frequency

Operation clock of the IEBus controller

INTW interrupt signal

Note

Data Sheet U11680EJ2V0DS00

35

Page 36

µ

PD784907, 784908

Figure 8-3. Examples of Using Oscillator

(1) Crystal/ceramic oscillation

µ

PD784908

V

SS

X1

X2

(2) External clock

• When EXTC bit of OSTS = 1 • When EXTC bit of OSTS = 0

PD784908

µ

X1

X1

µ

PD784908

PD74HC04, etc.

µ

X2

Open

X2

Caution When using the clock generator, wire in the area enclosed by the broken lines to avoid adverse

influence from capacitance.

• Keep the wiring length as short as possible.

• Do not cross the wiring with other signal lines.

• Do not route the wiring near a signal line through which a high fluctuating current flows.

• Make the ground point of the oscillator capacitor the same potential as V

SS. Do not ground

the capacitor to a ground pattern in which a high current flows.

• Do not fetch signals from the oscillator.

36

Data Sheet U11680EJ2V0DS00

Page 37

µ

PD784907, 784908

Compared with the main system clock oscillator, the watch clock oscillator, which is a low-gain circuit designed

to reduce current consumption, is more likely to cause noise-induced malfunctions. Therefore, special care should

be taken when using the watch clock oscillator.

The microcontroller can operate normally only when the oscillation is normal and stable. If a high-precision oscillator

frequency is required, consult with the oscillator manufacturer.

Figure 8-4. Notes on Connecting the Oscillator

PD784908

µ

X2

Cautions 1. Place the oscillator as close as possible to pins X1 and X2 (XT1 and XT2).

2. Do not let other signal lines cross that part of the circuit enclosed in broken lines.

X1 V

SS

Data Sheet U11680EJ2V0DS00

37

Page 38

µ

PD784907, 784908

8.3 Real-Time Output Port

The real-time output port outputs data stored in the buffer, synchronized with a timer/counter 1 match interrupt or

external interrupt. Thus, pulse output that is free of jitter can be obtained.

Therefore, the real-time output port is best suited to applications (such as open-loop control over stepping motors)

where an arbitrary pattern is output at arbitrary intervals.

As shown in Figure 8-5, the real-time output port is built around port 0 and the port 0 buffer register (P0H, P0L).

Figure 8-5. Block Diagram of Real-Time Output Port

Internal bus

INTP0 (externally)

INTC10 (from timer/counter 1)

INTC11 (from timer/counter 1)

8

Real-time output port

control register

(RTPC)

Output trigger

control circuit

4

Port 0 buffer register

4

Output latch (P0)

P07

4

8

P0LP0H

4

P00

38

Data Sheet U11680EJ2V0DS00

Page 39

µ

PD784907, 784908

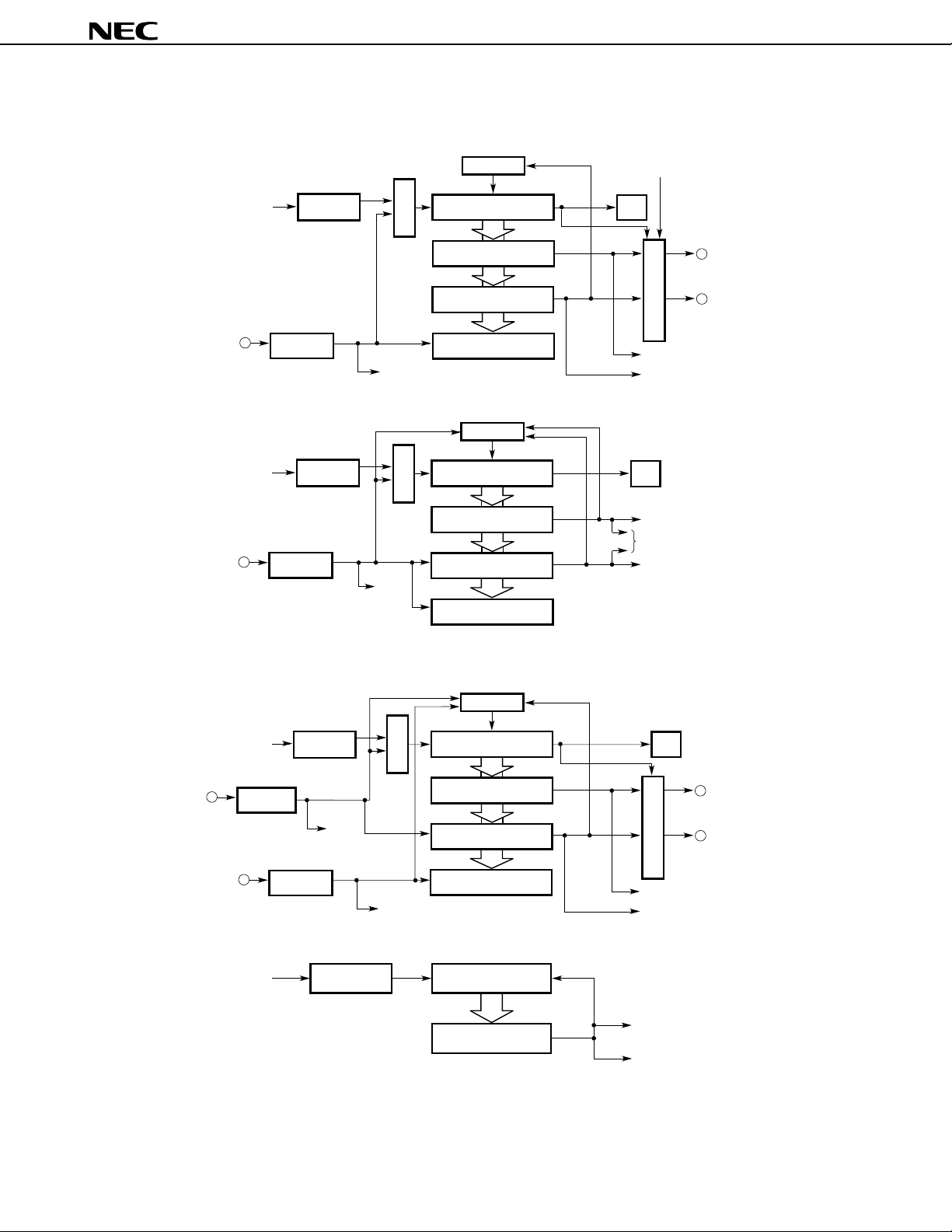

8.4 Timers/Counters

Three timer/counter units and one timer unit are incorporated.

Moreover, because seven interrupt requests are supported, these timers/counters can be used as seven timer/

counter units.

Table 8-2. Timers/Counters Operation

Name Timer/Counter 0 Timer/Counter 1 Timer/Counter 2 Timer 3

Item

Count width 8 bits —

16 bits

Operating mode Interval timer 2 ch 2 ch 2 ch 1 ch

External event counter —

One-shot timer — — —

Function Timer output 2 ch — 2 ch —

Toggle output — —

PWM/PPG output — —

One-shot pulse output

Real-time output — ——

Pulse width measurement 1 input 1 input 2 inputs —

Number of interrupt requests 2221

Note

———

Note The one-shot pulse output function makes the level of a pulse output active by software, and makes the level

of a pulse output inactive by hardware (interrupt request signal).

Note that this function differs from the one-shot timer function of timer/counter 2.

Data Sheet U11680EJ2V0DS00

39

Page 40

Timer/counter 0

Figure 8-6. Timer/Counter Block Diagram

Clear control

µ

PD784907, 784908

Software trigger

fXX/4

INTP3

Timer/counter 1

fXX/4

INTP0

Prescaler

Edge

detection

Prescaler

Event input

Edge

detection

INTP3

INTP0

Timer register 0

Selector

Compare register

Compare register

Capture register

Clear control

Timer register 1

(TM1/TM1W)

Selector

Compare register

(CR10/CR10W)

Capture/compare register

(CR11/CR11W)

Capture register

(CR12/CR12W)

(TM0)

(CR00)

(CR01)

(CR02)

Match

Match

Match

Match

OVF

TO0

TO1

Pulse output control

INTC00

INTC01

OVF

INTC10

To real-time

output port

INTC11

Timer/counter 2

fXX/4

INTP2/CI

INTP1

Edge

detection

Edge

detection

Timer 3

fXX/4

Remark OVF: Overflow flag

Prescaler

INTP2

Prescaler

Selector

INTP1

Clear control

Timer register 2

(TM2/TM2W)

Compare register

(CR20/CR20W)

Capture/compare register

(CR21/CR21W)

Capture register

(CR22/CR22W)

Timer register 3

(TM3/TM3W)

Compare register

(CR30/CR30W)

Match

Match

Clear

Match

OVF

TO2

TO3

Pulse output control

INTC20

INTC21

UART, CSI

INTC30

40

Data Sheet U11680EJ2V0DS00

Page 41

µ

PD784907, 784908

8.5 Watch Timer

As the count clock, either of two types of clock can be input to the watch timer: the main clock (6.29 MHz/12.58

MHz) or the watch clock (32.768 kHz). They can be selected using the control register. The watch clock is input to

the watch timer only. It is not input to the CPU or other peripheral circuits. Therefore, the speed of CPU operation

cannot be slowed by the watch clock.

Note

The watch timer generates interrupt signals (INTW), at 0.5-second intervals

, by dividing the count clock. At

the same time, the watch timer sets the interrupt request flag (WIF) (where WIF refers to bit 7 of the interrupt control

register (WIC)).

By switching modes, the INTW generation interval can be changed to about 1 ms (fast-forward mode: normal

operation speed × 512).

When the main clock is selected as the count clock, the watch timer stops if in STOP or IDLE standby mode, but

continues operating if in HALT standby mode. When the watch clock is selected as the count clock, the watch timer

continues operating regardless of the standby mode. The operation of the watch clock oscillator is controlled by means

of the watch timer mode register (WM).

µ

The watch timer of the

PD784908 does not have a buzzer output function.

Note After the operation is enabled, the time until first INTW generation is not 0.5 s.

Table 8-3. Relationship between Count Clock and Watch Timer Operation

Count Clock Selection Normal Operation Mode Standby Modes

HALT mode STOP mode IDLE mode

Main clock Operable Operable Stopped Stopped

Watch clock Operable Operable Operable Operable

The watch timer consists of a frequency divider which divides the count clock by 3 and a counter which divides

the frequency output from the frequency divider by 214. As the count clock, select the signal obtained by dividing the

internal system clock by 128 or that output by the watch clock oscillator.

Figure 8-7. Watch Timer Block Diagram

WM.3

Reset

Main clock

f

XX

/128

Division

by 3

Watch

clock

oscillator

ON/OFF

0

1

123456789 10111213 14

Counter Counter

0

SEL

SEL SEL

1

WM.2

1

INTW

0

WM.7

WM.6

Data Sheet U11680EJ2V0DS00

Main clock selection: 6.29 MHz

STBC.7

12.58 MHz

41

Page 42

µ

PD784907, 784908

8.6 PWM Output (PWM0, PWM1)

Two channels of PWM (pulse width modulation) output circuitry with a resolution of 12 bits and a repetition frequency

of 24.57 kHz (fCLK = 6.29 MHz) are incorporated. Low or high active level can be selected for the PWM output

channels, independently of each other. This output is best suited to DC motor speed control.

Figure 8-8. Block Diagram of PWM Output Unit

Internal bus

CLK

f

Prescaler

Remark n = 0, 1

(Modulo register)

15 0

PWMn

8-bit

down-counter

1/256

16

8 7 4 3

84

Pulse control

circuit

4-bit counter

8

PWM control register

(PWMC)

Reload

control

Output

control

PWMn (output pin)

42

Data Sheet U11680EJ2V0DS00

Page 43

µ

PD784907, 784908

8.7 A/D Converter

An analog/digital (A/D) converter having 8 multiplexed analog inputs (ANI0 through ANI7) is incorporated.

The successive approximation system is used for conversion. The result of conversion is held in the 8-bit A/D

conversion result register (ADCR). Thus, speedy high-precision conversion can be achieved.

A/D conversion can be started in the following two ways:

• Hardware start: Conversion is started by trigger input (INTP5).

• Software start: Conversion is started by setting the bit of the A/D converter mode register (ADM).

After conversion has started, one of the following modes can be selected:

• Scan mode: Multiple analog inputs are selected sequentially to convert multiple pins.

• Select mode: A single analog input is selected at all times to enable conversion data to be obtained continuously.

ADM is used to specify the above modes, as well as the termination of conversion.

When the result of conversion is transferred to ADCR, an interrupt request (INTAD) is generated. Using this feature,

the results of conversion can be continuously transferred to memory by the macro service.

Cautions 1. For this product, apply the same voltage as the power supply voltage (AV

voltage input pin (AVREF1).

2. When port 7 is used as both an output port and A/D input line, do not manipulate the output

port while A/D conversion is in progress.

Figure 8-9. Block Diagram of A/D Converter

ANI0

ANI1

ANI2

ANI3

ANI4

ANI5

ANI6

ANI7

INTP5

Input selector

Edge

detection

circuit

A/D converter mode

register (ADM)

Sample and hold circuit

Conversion

trigger

Trigger enable

Voltage comparator

Successive

approximation

register (SAR)

Control

circuit

A/D conversion

result register (ADCR)

INTAD

8

Series resistor string

R/2

R

Tap selector

R/2

AV

DD

Connection

control

AV

REF1

AV

SS

DD) to the reference

A/D current cut selection

register (IEAD)

8

Internal bus

Data Sheet U11680EJ2V0DS00

8

43

Page 44

µ

PD784907, 784908

8.8 Serial Interface

Four independent serial interface channels are incorporated.

•

Asynchronous serial interface (UART)/3-wire serial I/O (IOE) × 2

•

Synchronous serial interface (CSI) × 2

• 3-wire serial I/O (IOE)

This makes it possible for communication with an external system and local communication within the system to

be simultaneously executed (see Figure 8-10).

Figure 8-10. Example of Serial Interface

UART + 3-wire serial I/O + 2-wire serial I/O

PD4711A

µ

RS-232-C

driver/receiver

Note Handshake line

PD784908 (master)

µ

[UART]

RxD

TxD

Port

SO1

SI1

SCK1

INTPm

Port

SI0

SO0

SCK0

INTPn

Port

[3-wire serial I/O]

Note

V

DD

Note

[2-wire serial I/O]

Slave

SI

SO

SCK

Port

INT

V

DD

Slave

SB0

SCK0

Port

INT

44

Data Sheet U11680EJ2V0DS00

Page 45

µ

PD784907, 784908

8.8.1 Asynchronous serial interface/3-wire serial I/O (UART/IOE)

Two serial interface channels, from which asynchronous serial interface mode and 3-wire serial I/O mode can be

selected, are provided.

(1) Asynchronous serial interface mode

In this mode, 1-byte data is transferred or received after a start bit.

A baud rate generator is incorporated to enable communication at a wide range of baud rates.

A baud rate can be defined by dividing the frequency of a clock signal input to the ASCK pin.

By using the baud rate generator, a baud rate conforming to the MIDI standard (31.25 kbps) can be obtained.

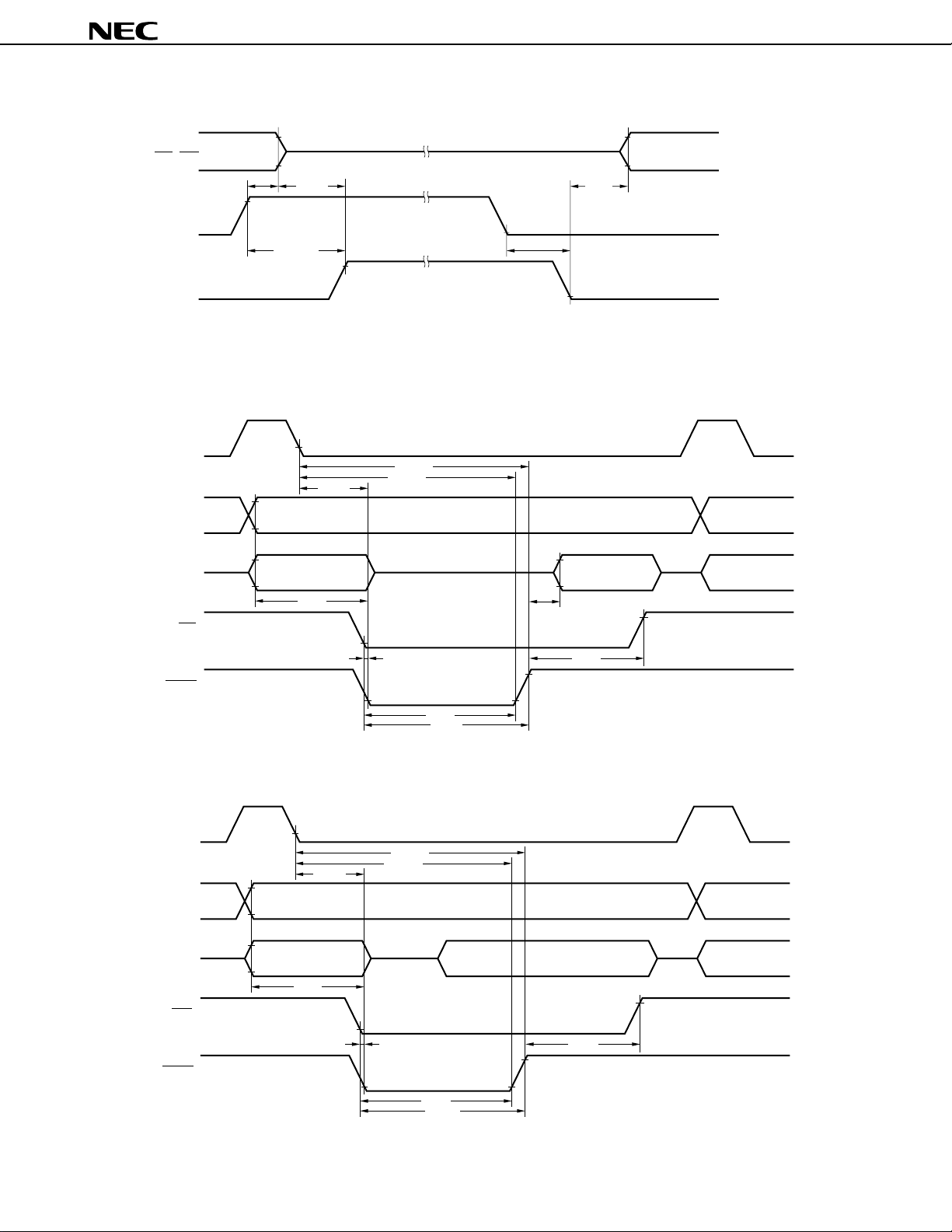

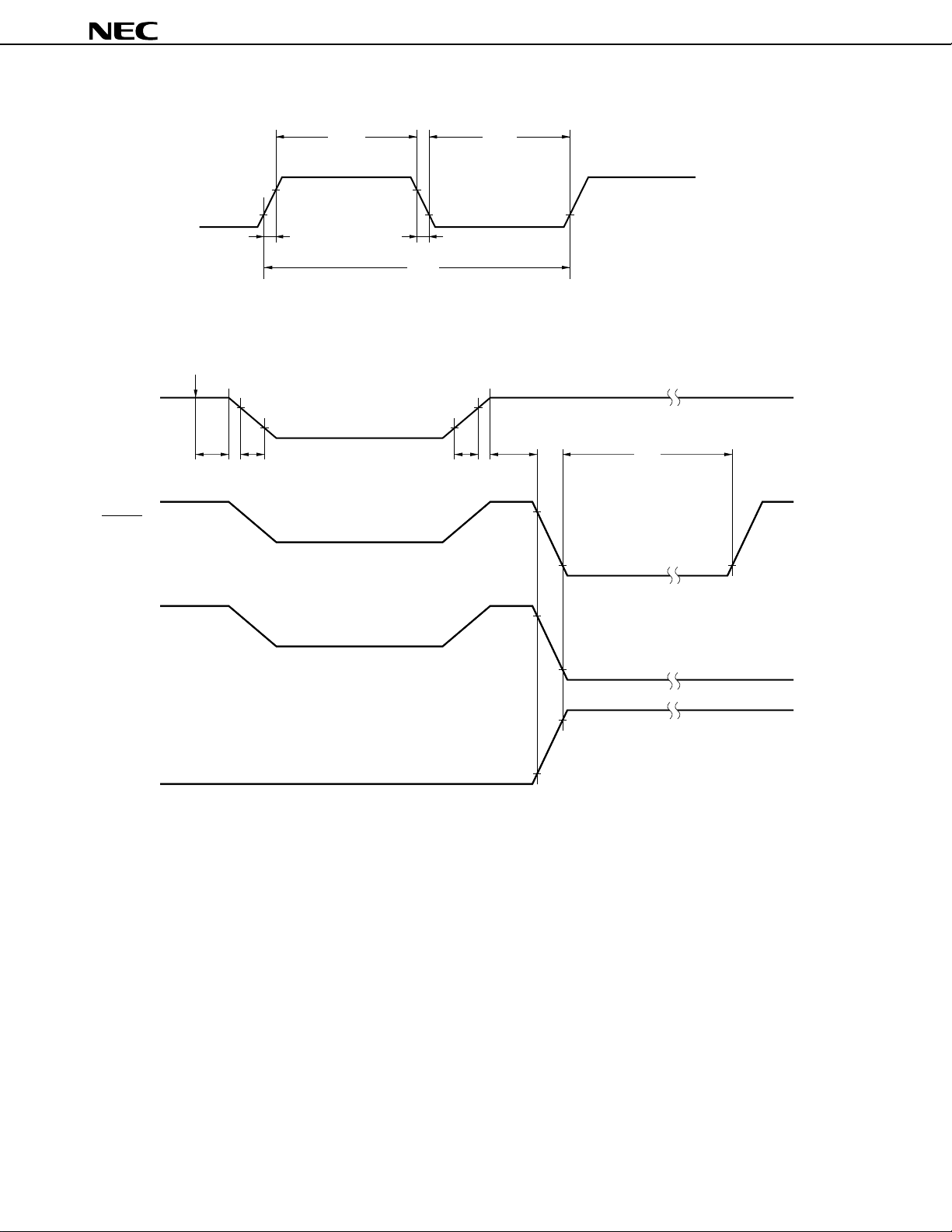

Figure 8-11. Block Diagram of Asynchronous Serial Interface Mode

Internal bus

RxD, RxD2

TxD, TxD2

Baud rate generator

XX

f

ASCK, ASCK2

Selector

1/2

n+1

Receive buffer

Receive

shift register

Reception

control parity

check

1/2m

1/2m

RXB, RXB2

INTSR,

INTSR2

INTSER,

INTSER2

Transmission

shift register

Transmission

control parity

bit addition

TXS, TXS2

INTST, INTST2

Remark f

XX: Oscillating frequency or external clock input frequency

n = 0 to 11

m = 16 to 30

Data Sheet U11680EJ2V0DS00

45

Page 46

µ

PD784907, 784908

(2) 3-wire serial I/O mode

In this mode, the master device makes the serial clock active to start transmission, then transfers 1-byte data

in synchronization with this clock.

This mode is designed for communication with a device incorporating a conventional synchronous serial interface.

Basically, three lines are used for communication: the serial clock line (SCK) and the two serial data lines (SI

and SO). In general, a handshake line is required to check the state of communication.

Figure 8-12. Block Diagram of 3-Wire Serial I/O Mode

Internal bus

Direction control

circuit

SIO1, SIO2

SI1, SI2

Shift register Output latch

SO1, SO2

SCK1, SCK2

Remark f

Serial clock counter

Serial clock

control circuit

XX: Oscillating frequency or external clock input frequency

n = 0 to 11

m = 1, 16 to 30

Interrupt

generator

Selector

1/m 1/2

INTCSI1,

INTCSI2

n+1

f

XX

46

Data Sheet U11680EJ2V0DS00

Page 47

µ

PD784907, 784908

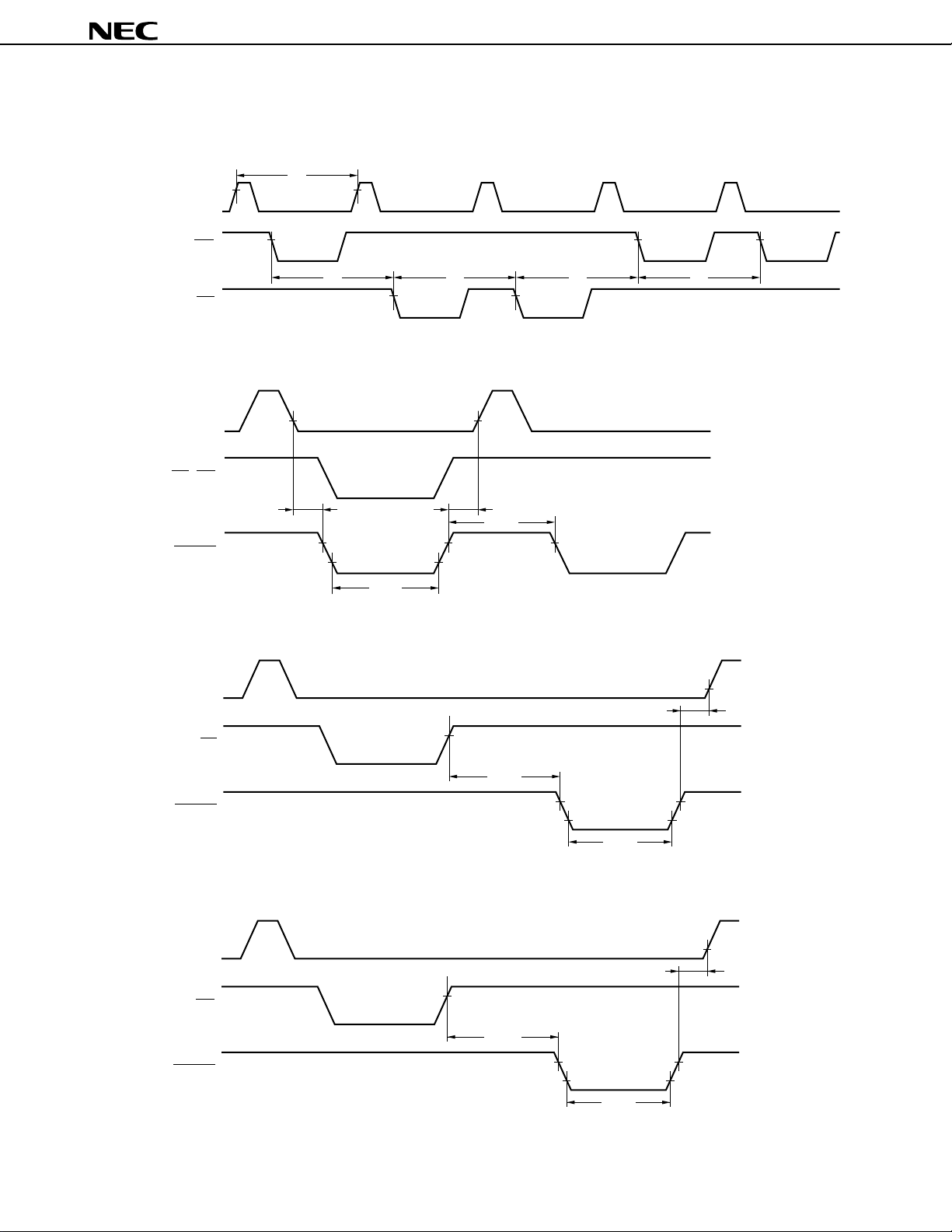

8.8.2 Clocked serial interface (CSI)

With this interface, the master device makes the serial clock active to start transmission, then transfers 1-byte data

in synchronization with this clock.

Figure 8-13. Block Diagram of Clocked Serial Interface

Internal bus

SIn

SIOn register CSIMn register

Selector

SOn

SCKn

Remark f

Serial clock counter

XX: Oscillating frequency or external clock input frequency

n = 0, 3

Selector

INTCSIn

f

XX

/8

f

XX

/16

f

XX

/32

f

XX

/64

f

XX

/128

Data Sheet U11680EJ2V0DS00

47

Page 48

µ

PD784907, 784908

• 3-wire serial I/O mode

This mode is designed for communication with a device incorporating a conventional clocked serial interface.

Basically, three lines are used for communication: the serial clock line (SCKn) and serial data lines (SIn and SOn)

(n = 0, 3).

In general, a handshake line is required to check the state of communication.

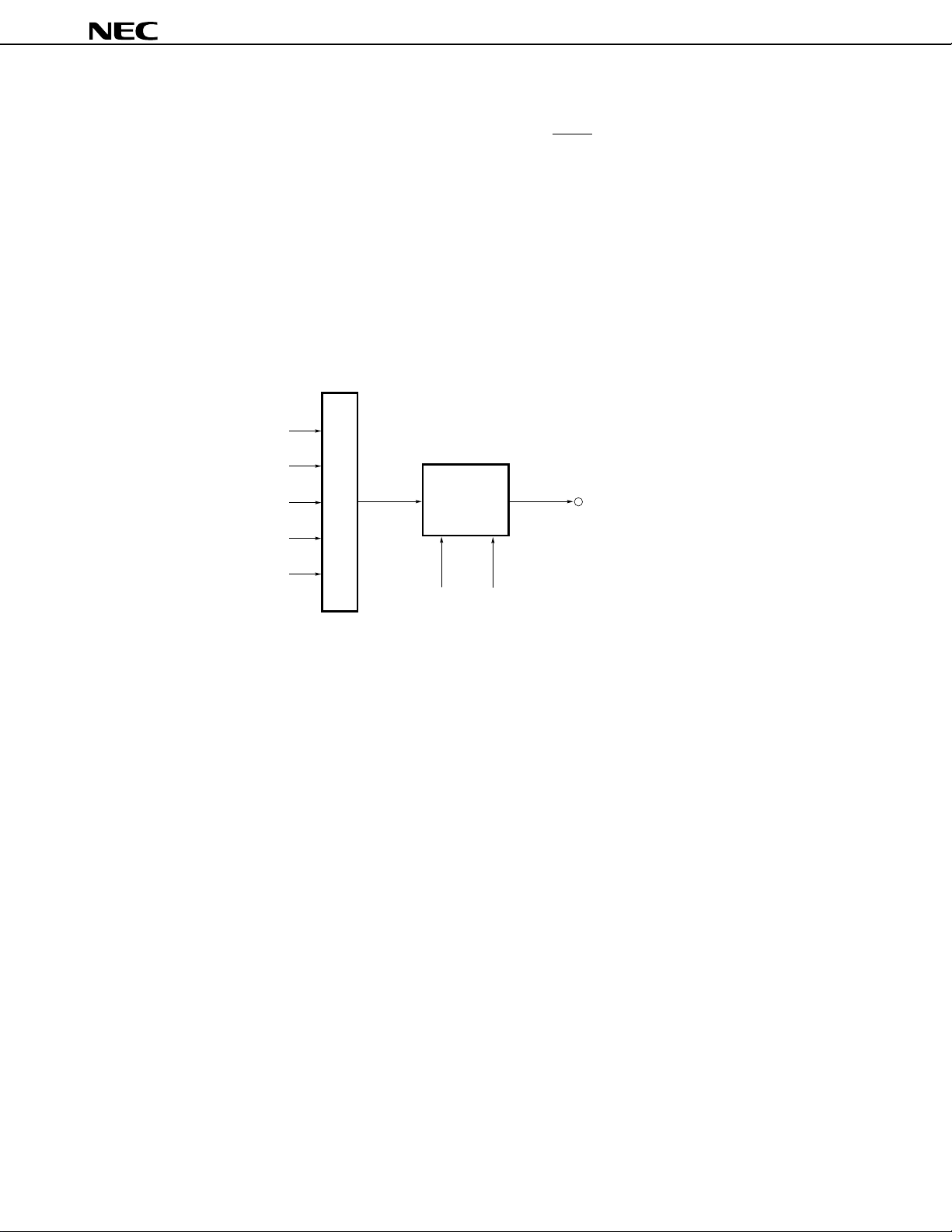

8.9 Clock Output Function

The frequency of the CPU clock signal can be divided and output from the system. Moreover, the port can be used

as a 1-bit port.

The ASTB pin is also used as the CLKOUT pin, so that when this function is used, the local bus interface cannot

be used.

Figure 8-14. Block Diagram of Clock Output Function

f

CLK

f

CLK

/2

CLK

/4

f

Selector

CLK

/8

f

f

CLK

/16

Output control

Enable output Output level

CLKOUT

48

Data Sheet U11680EJ2V0DS00

Page 49

µ

PD784907, 784908

8.10 Edge Detection Function

The interrupt input pins (NMI, INTP0 through INTP5) are used not only to input interrupt requests but also to input

trigger signals to the internal hardware units. Because these pins operate at the edge of the input signal, they have

an edge-detection function incorporated. Moreover, a noise elimination function is also provided to prevent erroneous

edge detection caused by noise.

Table 8-4. Noise Elimination Method of Interrupt Input Pins

Pin Name Detectable Edge Noise Elimination Method

NMI Rising edge or falling edge Analog delay

INTP0 to INTP3 Rising edge or falling edge, or both edges Clock sampling

Note

INTP4, INTP5 Analog delay

Note INTP0 is used for sampling clock selection.

8.11 Watchdog Timer

A watchdog timer is incorporated to detect a CPU runaway. The watchdog timer, if not cleared by software within

a specified interval, generates a non-maskable interrupt request. Furthermore, once watchdog timer operation is

enabled, it cannot be disabled by software. The user can specify whether priority is placed on an interrupt request

based on the watchdog timer or on an interrupt request based on the NMI pin.

Figure 8-15. Block Diagram of Watchdog Timer

f

CLK

Clear signal

Timer

21

f

CLK

/2

20

CLK

/2

f

19

f

CLK

/2

17

f

CLK

/2

Selector

INTWDT

Data Sheet U11680EJ2V0DS00

49

Page 50

µ

PD784907, 784908

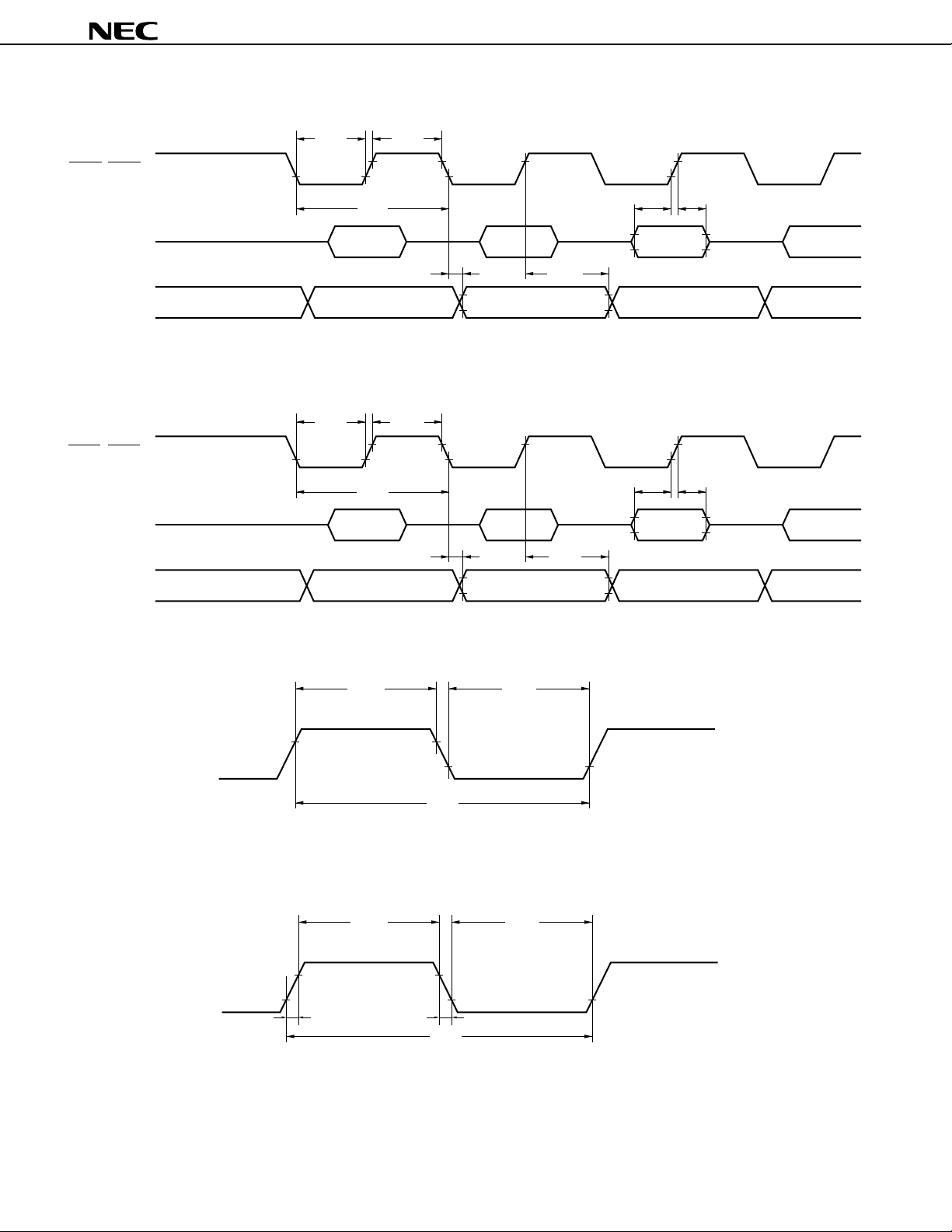

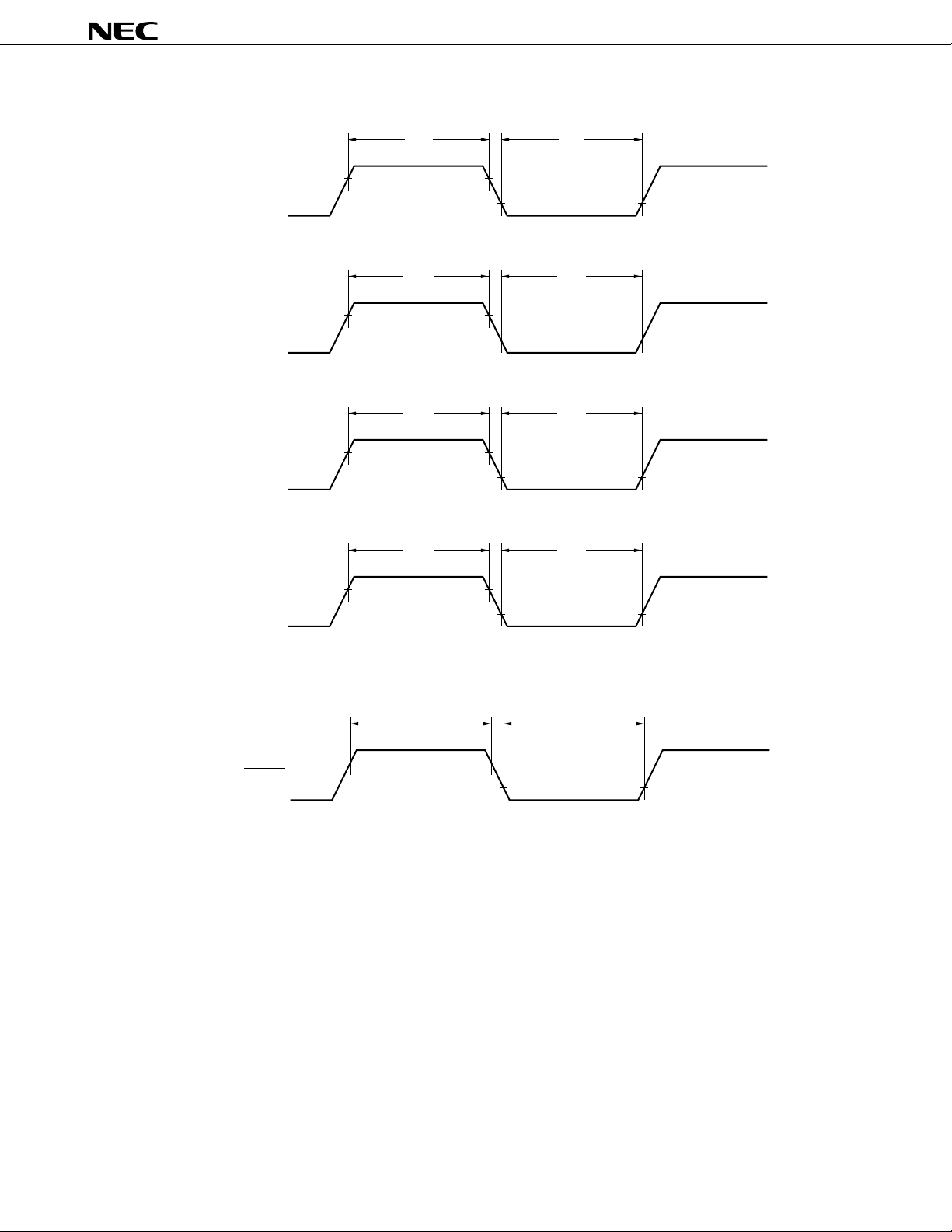

8.12 Simplified IEBus Controller

µ

A newly developed IEBus controller is incorporated into the

PD784908. This IEBus controller has fewer functions

than the IEBus interface function of previous product (incorporated into the 78K/0).

Table 8-5 compares the previous product and the new, simplified IEBus interface.

Table 8-5. Comparisons between Previous Product and Simplified IEBus Interface

Item Previous Product (IEBus Incorporated into 78K/0) Simplified IEBus

Communication mode Modes 0 to 2 Fixed to mode 1