ADC14L020

14-Bit, 20 MSPS, 150 mW A/D Converter

ADC14L020 14-Bit, 20 MSPS, 150 mW A/D Converter

March 2006

General Description

The ADC14L020 is a low power monolithic CMOS analogto-digital converter capable of converting analog input signals into 14-bit digital words at 20 Megasamples per second

(MSPS). This converter uses a differential, pipeline architecture with digital error correction and an on-chip sample-andhold circuit to minimize power consumption while providing

excellent dynamic performance and a 150 MHz Full Power

Bandwidth. Operating on a single +3.3V power supply, the

ADC14L020 achieves 12.0 effective bits at nyquist and consumes just 150 mW at 20 MSPS . The Power Down feature

reduces power consumption to 15 mW.

The differential inputs provide a full scale differential input

swing equal to 2 times V

ended input. Full use of the differential input is recommended for optimum performance. Duty cycle stabilization

and output data format are selectable using a quad state

function pin. The output data can be set for offset binary or

two’s complement.

To ease interfacing to lower voltage systems, the digital

output driver power pins of the ADC14L020 can be connected to a separate supply voltage in the range of 2.4V to

the analog supply voltage.

This device is available in the 32-lead LQFP package and

will operate over the industrial temperature range of −40˚C to

+85˚C. An evaluation board is available to ease the evaluation process.

with the possibility of a single-

REF

Features

n Single +3.3V supply operation

n Internal sample-and-hold

n Internal reference

n Outputs 2.4V to 3.6V compatible

n Duty Cycle Stabilizer

n Power down mode

Key Specifications

n Resolution 14 Bits

n DNL

n SNR (f

n SFDR (f

n Data Latency 7 Clock Cycles

n Power Consumption

n -- Operating 150 mW (typ)

n -- Power Down Mode 15 mW (typ)

= 10 MHz) 74 dB (typ)

IN

= 10 MHz) 93 dB (typ)

IN

±

0.5 LSB (typ)

Applications

n Medical Imaging

n Instrumentation

n Communications

n Digital Video

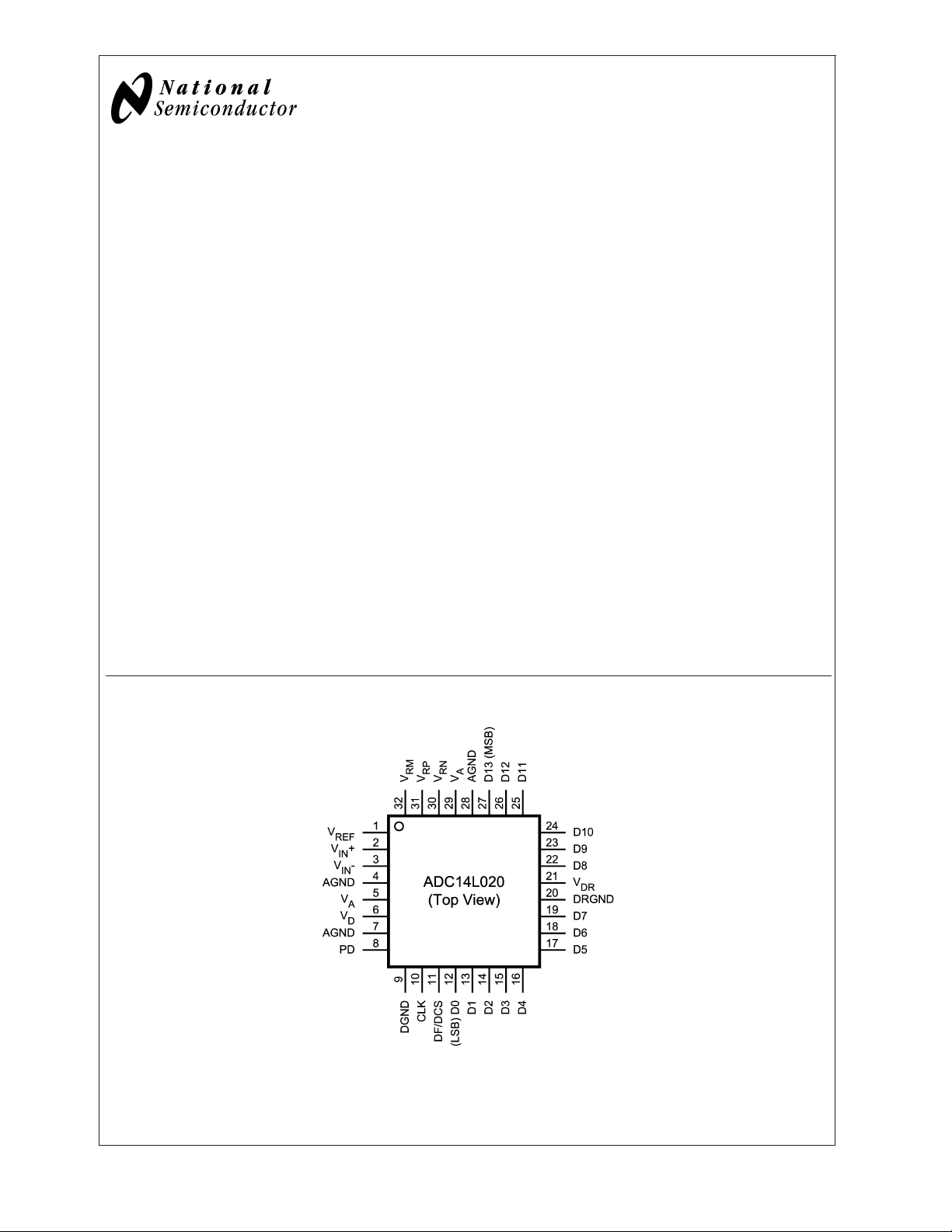

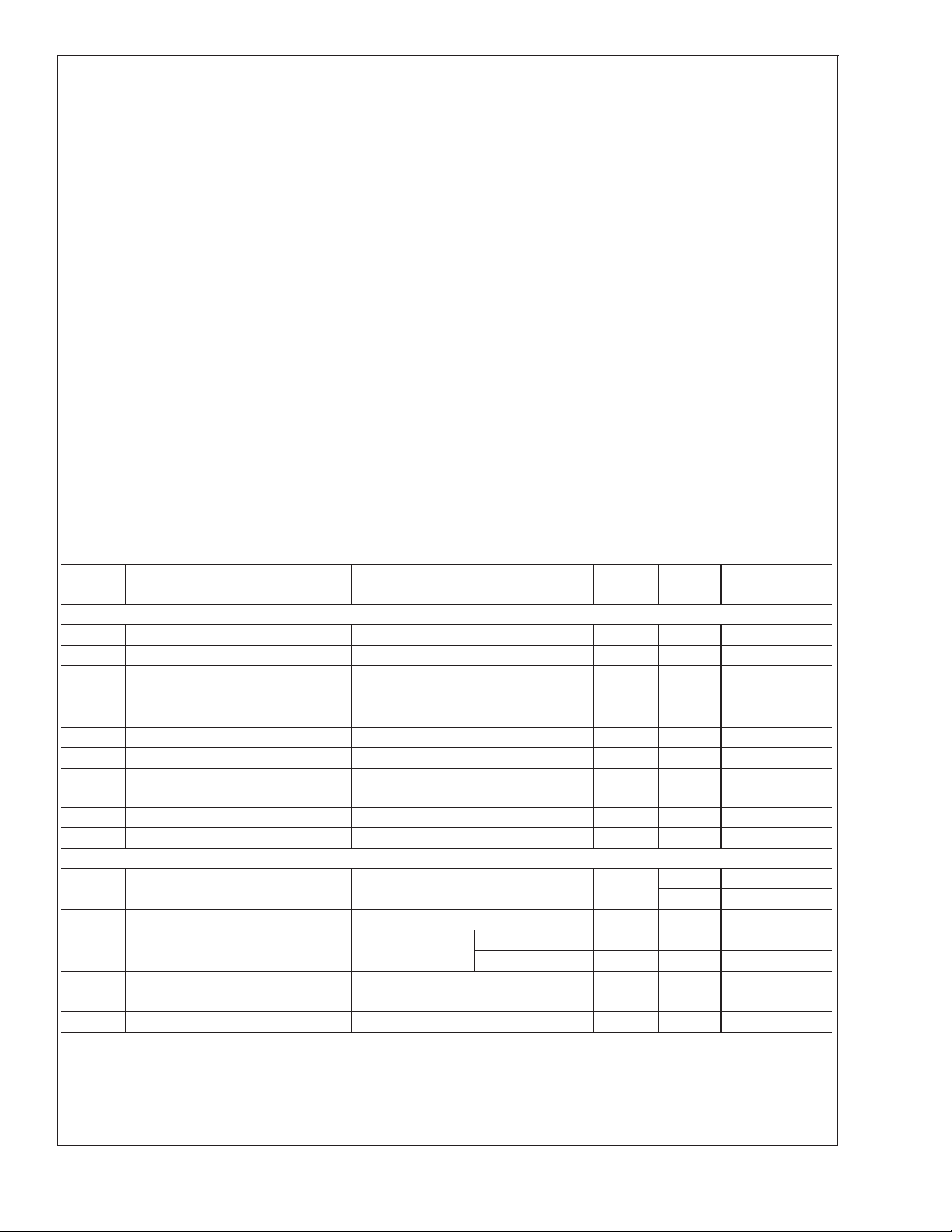

Connection Diagram

20157001

© 2006 National Semiconductor Corporation DS201570 www.national.com

Ordering Information

ADC14L020

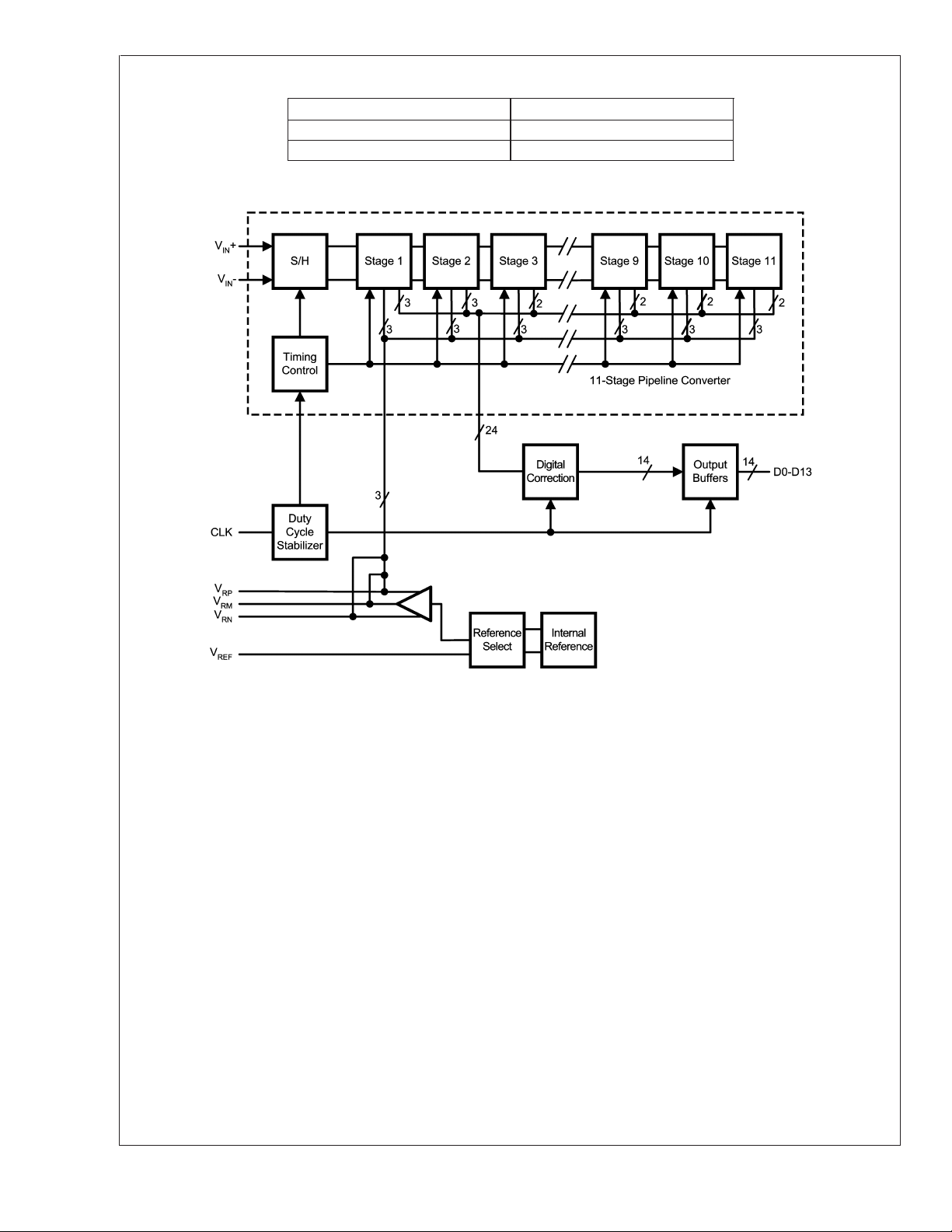

Block Diagram

Industrial (−40˚C ≤ TA≤ +85˚C) Package

ADC14L020CIVY 32 Pin LQFP

ADC14L020EVAL Evaluation Board

20157002

www.national.com 2

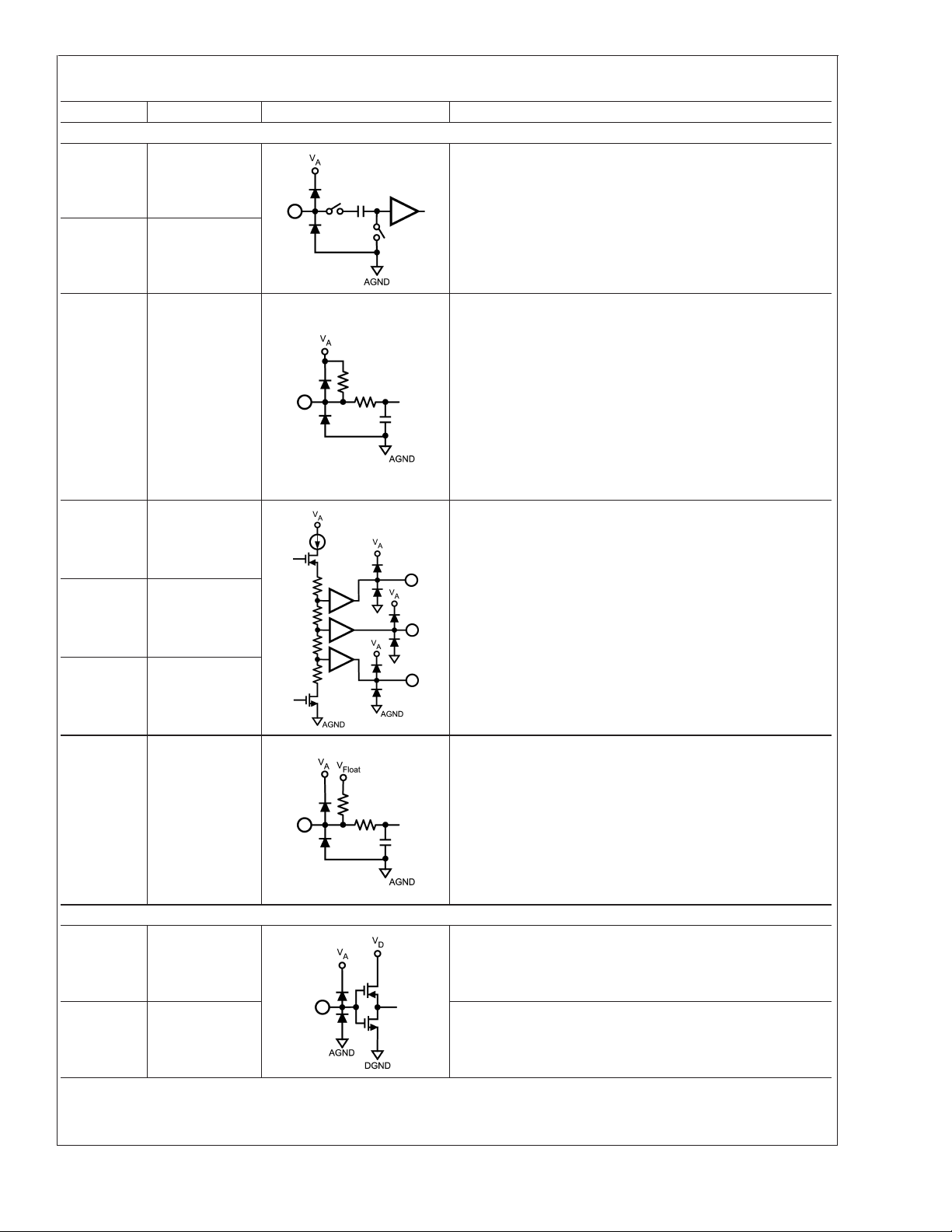

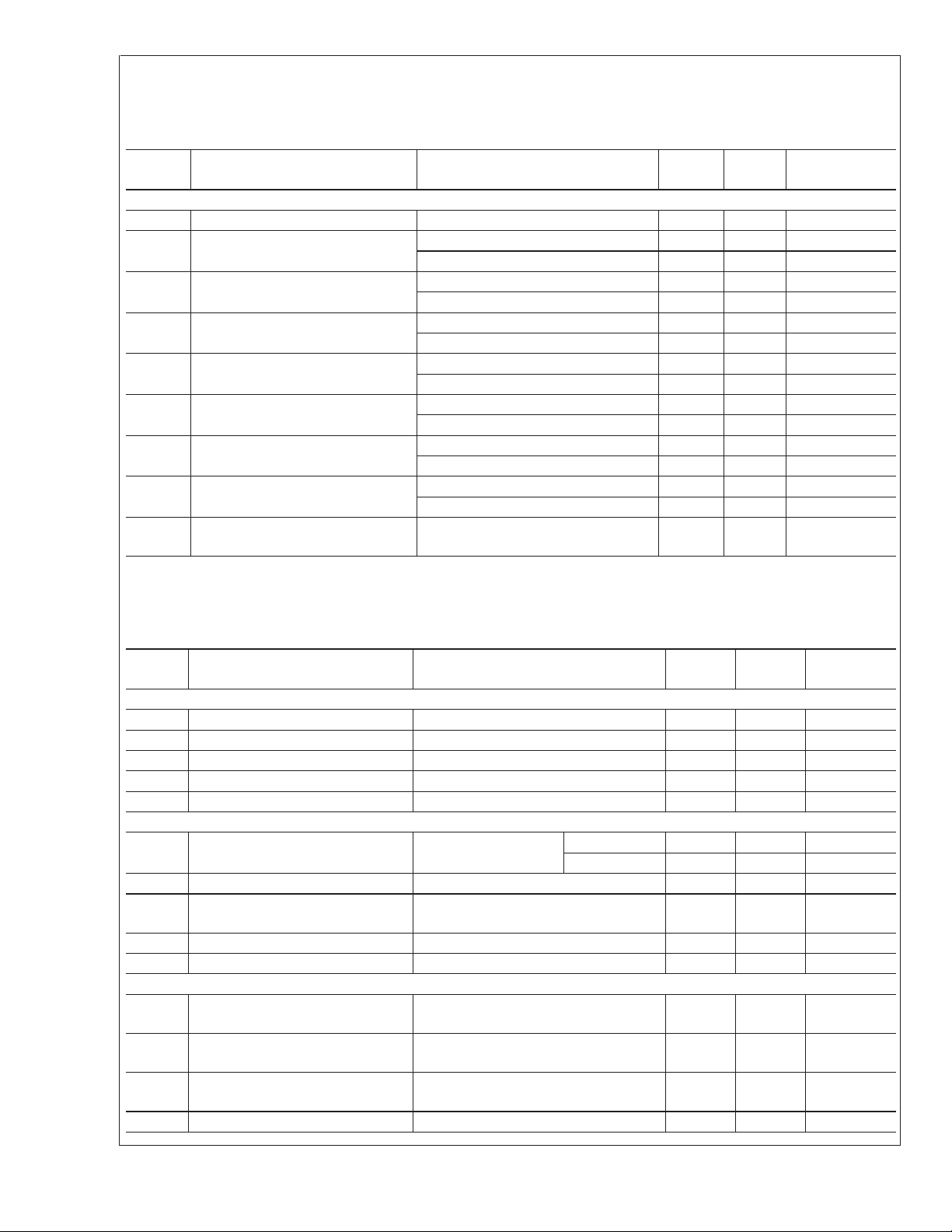

Pin Descriptions and Equivalent Circuits

Pin No. Symbol Equivalent Circuit Description

ANALOG I/O

Differential analog input pins. With a 1.0V reference voltage the

2V

3V

1V

IN

IN

REF

+

−

differential full-scale input signal level is 2.0 V

input pin voltage centered on a common mode voltage, V

The negative input pins may be connected to V

single-ended operation, but a differential input signal is

required for best performance.

This pin is the reference select pin and the external reference

input.

If (V

- 0.3V)<V

A

<

VA, the internal 1.0V reference is

REF

selected.

If AGND

<

<

V

(AGND + 0.3V), the internal 0.5V reference

REF

is selected.

If a voltage in the range of 0.4V to (V

pin, that voltage is used as the reference.

The full scale differential voltage range is2*V

should be bypassed to AGND with a 0.1 µF capacitor when an

external reference is used.

with each

P-P

for

CM

- 0.4V) is applied to this

A

REF.VREF

CM

ADC14L020

.

31 V

32 V

30 V

11 DF/DCS

DIGITAL I/O

10 CLK

RM

RP

These pins should each be bypassed to AGND with a low ESL

(equivalent series inductance) 0.1 µF capacitor. A 10 µF

capacitor should be placed between the V

may be loaded to 1mA for use as a temperature stable

V

RM

and VRN.

RP

1.5V reference. The remaining pins should not be loaded.

may be used to provide the common mode voltage, VCM,

V

RM

for the differential inputs.

RN

This is a four-state pin.

DF/DCS = V

, output data format is offset binary with duty

A

cycle stabilization applied to the input clock

DF/DCS = AGND, output data format is 2’s complement, with

duty cycle stabilization applied to the input clock.

DF/DCS = V

, output data is 2’s complement without duty

RM

cycle stabilization applied to the input clock

DF/DCS = "float", output data is offset binary without duty cycle

stabilization applied to the input clock.

Digital clock input. The range of frequencies for this input is as

specified in the electrical tables with guaranteed performance

at 20 MHz. The input is sampled on the rising edge.

8PD

PD is the Power Down input pin. When high, this input puts the

converter into the power down mode. When this pin is low, the

converter is in the active mode.

www.national.com3

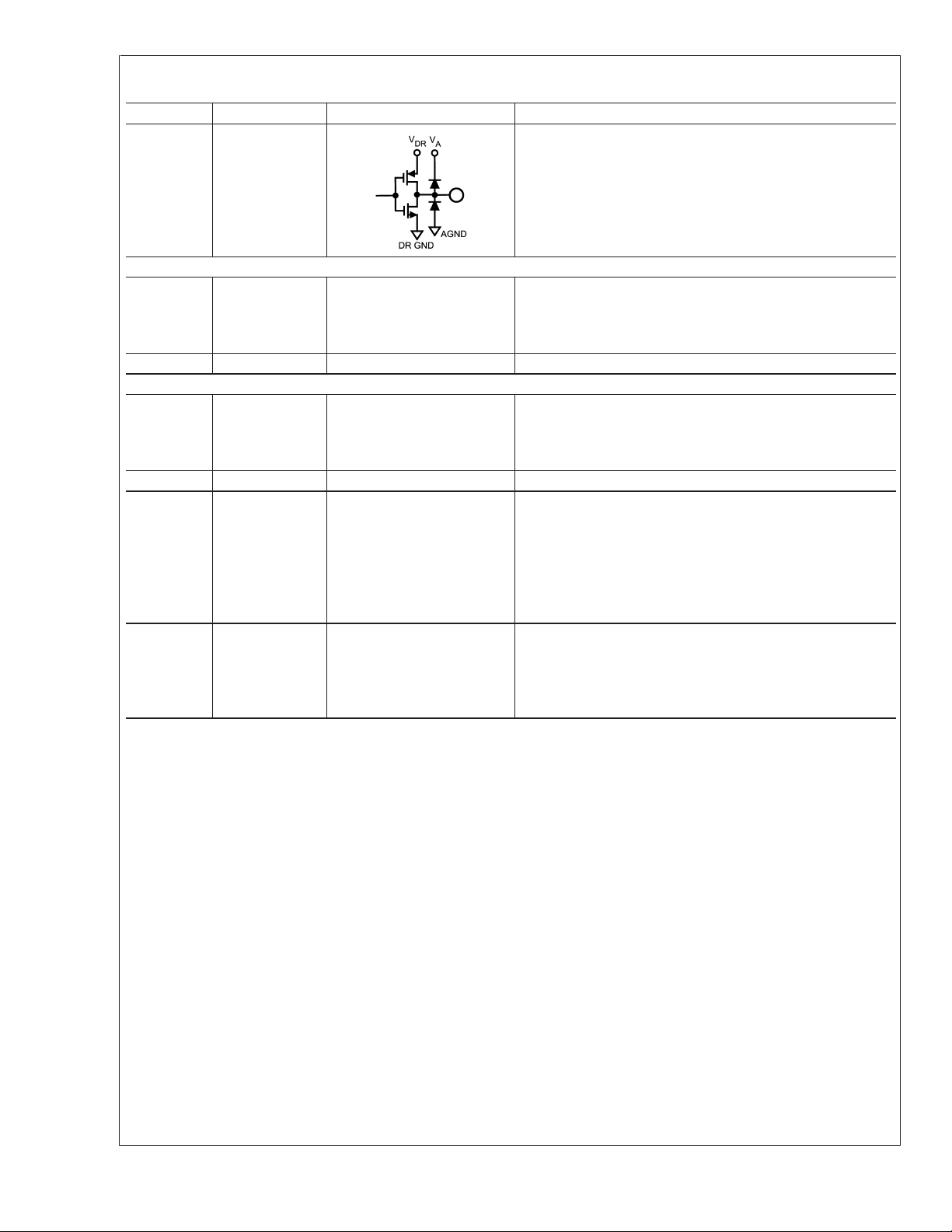

Pin Descriptions and Equivalent Circuits (Continued)

Pin No. Symbol Equivalent Circuit Description

ADC14L020

12-19

22-27

ANALOG POWER

5, 29 V

4, 7, 28 AGND The ground return for the analog supply.

DIGITAL POWER

6V

9 DGND The ground return for the digital supply.

21 V

20 DR GND

D0–D13

A

D

DR

Digital data output pins that make up the 14-bit conversion

result. D0 (pin 12) is the LSB, while D13 (pin 27) is the MSB of

the output word. Output levels are TTL/CMOS compatible.

<

Optimum loading is

10pF.

Positive analog supply pins. These pins should be connected

to a quiet +3.3V source and bypassed to AGND with 0.1 µF

capacitors located close to these power pins, and with a 10 µF

capacitor.

Positive digital supply pin. This pin should be connected to the

same quiet +3.3V source as is V

with a 0.1 µF capacitor located close to the power pin and with

a 10 µF capacitor.

Positive driver supply pin for the ADC14L020’s output drivers.

This pin should be connected to a voltage source of +2.4V to

and be bypassed to DR GND with a 0.1 µF capacitor. If the

V

D

supply for this pin is different from the supply used for V

, it should also be bypassed with a 10 µF capacitor. V

V

D

should never exceed the voltage on VD. All 0.1 µF bypass

capacitors should be located close to the supply pin.

The ground return for the digital supply for the ADC’s output

drivers. These pins should be connected to the system digital

ground, but not be connected in close proximity to the ADC’s

DGND or AGND pins. See Section 5 (Layout and Grounding)

for more details.

and be bypassed to DGND

A

and

A

DR

www.national.com 4

ADC14L020

Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required,

please contact the National Semiconductor Sales Office/

Distributors for availability and specifications.

or V

A

+0.3V)

±

25 mA

±

50 mA

4.2V

D

V

A,VD,VDR

|V

| ≤ 100 mV

A–VD

Voltage on Any Input or Output Pin −0.3V to (V

Input Current at Any Pin (Note 3)

Package Input Current (Note 3)

Package Dissipation at T

= 25˚C See (Note 4)

A

Operating Ratings (Notes 1, 2)

Operating Temperature −40˚C ≤ T

Supply Voltage (V

Output Driver Supply (V

) +3.0V to +3.6V

A,VD

) +2.4V to V

DR

CLK, PD −0.05V to (VD+ 0.05V)

Clock Duty Cycle (DCS On) 20% to 80%

Clock Duty Cycle (DCS Off) 40% to 60%

Analog Input Pins 0V to 2.6V

V

CM

|AGND–DGND| ≤100mV

≤ +85˚C

A

0.5V to 2.0V

ESD Susceptibility

Human Body Model (Note 5) 2500V

Machine Model (Note 5) 250V

Storage Temperature −65˚C to +150˚C

Soldering process must comply with National

Semiconductor’s Reflow Temperature Profile

specifications. Refer to www.national.com/packaging.

(Note 6)

Converter Electrical Characteristics

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA=VD= +3.3V, VDR=

+2.5V, PD = 0V, External V

REF

= +1.0V, f

Stabilizer On. Boldface limits apply for T

Symbol Parameter Conditions

STATIC CONVERTER CHARACTERISTICS

Resolution with No Missing Codes 14 Bits (min)

INL Integral Non Linearity (Note 11)

DNL Differential Non Linearity

PGE Positive Gain Error 0.3

NGE Negative Gain Error 0.3

TC GE Gain Error Tempco −40˚C ≤ T

V

TC

V

OFF

OFF

Offset Error (VIN+=VIN−) -0.06

Offset Error Tempco −40˚C ≤ TA≤ +85˚C 1.5 ppm/˚C

Under Range Output Code 0

Over Range Output Code 16383

REFERENCE AND ANALOG INPUT CHARACTERISTICS

V

CM

V

RM

C

IN

V

REF

Common Mode Input Voltage 1.5

Reference Output Voltage Output load=1mA 1.5 V

VINInput Capacitance (each pin to

GND)

External Reference Voltage (Note

13)

Reference Input Resistance 1 MΩ (min)

= 20 MHz, fIN= 10 MHz at -0.5dBFS, tr=tf= 2 ns, CL= 15 pF/pin, Duty Cycle

CLK

J=TMIN

to T

: all other limits TJ= 25˚C (Notes 7, 8, 9)

MAX

Typical

(Note 10)

±

1.4

±

0.5

≤ +85˚C 2.5 ppm/˚C

A

Limits

(Note 10)

±

3.8 LSB (max)

±

1.0 LSB (max)

±

3.3 %FS (max)

±

3.3 %FS (max)

±

0.85 %FS (max)

0.5 V (min)

2.0 V (max)

VIN= 1.5 Vdc

±

0.5 V

(CLK LOW) 11 pF

(CLK HIGH) 4.5 pF

1.00

0.8 V (min)

1.2 V (max)

Units

(Limits)

D

www.national.com5

Converter Electrical Characteristics (Continued)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA=VD= +3.3V, VDR=

+2.5V, PD = 0V, External V

ADC14L020

Stabilizer On. Boldface limits apply for T

REF

= +1.0V, f

Symbol Parameter Conditions

DYNAMIC CONVERTER CHARACTERISTICS

FPBW Full Power Bandwidth 0 dBFS Input, Output at −3 dB 150 MHz

SNR Signal-to-Noise Ratio

SINAD

Signal-to-Noise Ratio and

Distortion

ENOB Effective Number of Bits

THD Total Harmonic Disortion

H2 Second Harmonic Distortion

H3 Third Harmonic Distortion

SFDR Spurious Free Dynamic Range

IMD Intermodulation Distortion

= 20 MHz, fIN= 10 MHz at -0.5dBFS, tr=tf= 2 ns, CL= 15 pF/pin, Duty Cycle

CLK

J=TMIN

to T

f

= 4.8 MHz and 5.2 MHz,

IN

: all other limits TJ= 25˚C (Notes 7, 8, 9)

MAX

f

= 1 MHz 74 dBc

IN

f

=10 MHz 74 72.3 dBc

IN

f

= 1 MHz 74 dBc

IN

f

= 10 MHz 74 72.2 dBc

IN

f

= 1 MHz 12 Bits

IN

f

= 10 MHz 12 11.7 Bits

IN

f

= 1 MHz -90 dBc

IN

f

= 10 MHz -90 -80 dBc

IN

f

= 1 MHz -97 dBc

IN

f

= 10 MHz -97 -81 dBc

IN

f

= 1 MHz -96 dBc

IN

f

= 10 MHz -96 -81 dBc

IN

f

= 1 MHz 93 dBc

IN

f

= 10 MHz 93 81 dBc

IN

each = −6.5 dBFS

Typical

(Note 10)

Limits

(Note 10)

−76 dBFS

Units

(Limits)

DC and Logic Electrical Characteristics

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA=VD= +3.3V, VDR=

+2.5V, PD = 0V, External V

Boldface limits apply for T

= +1.0V, f

REF

J=TMIN

to T

Symbol Parameter Conditions

CLK, PD DIGITAL INPUT CHARACTERISTICS

V

V

I

I

C

IN(1)

IN(0)

IN(1)

IN(0)

IN

Logical “1” Input Voltage VD= 3.6V 2.0 V (min)

Logical “0” Input Voltage VD= 3.0V 1.0 V (max)

Logical “1” Input Current VIN= 3.3V 10 µA

Logical “0” Input Current VIN= 0V −10 µA

Digital Input Capacitance 5 pF

D0–D13 DIGITAL OUTPUT CHARACTERISTICS

V

V

+I

−I

C

OUT(1)

OUT(0)

SC

SC

OUT

Logical “1” Output Voltage I

Logical “0” Output Voltage I

Output Short Circuit Source

Current

Output Short Circuit Sink Current V

Digital Output Capacitance 5 pF

POWER SUPPLY CHARACTERISTICS

I

A

I

D

I

DR

Analog Supply Current

Digital Supply Current

Digital Output Supply Current

Total Power Consumption PD Pin = DGND, C

= 20 MHz, fIN= 10 MHz, tr=tf= 2 ns, CL= 15 pF/pin, Duty Cycle Stabilizer On.

CLK

: all other limits TJ= 25˚C (Notes 7, 8, 9)

MAX

Typical

(Note 10)

= 2.5V 2.3 V (min)

V

= −0.5 mA

OUT

= 1.6 mA, VDR=3V 0.4 V (max)

OUT

= 0V −10 mA

V

OUT

OUT=VDR

PD Pin = DGND, V

PD Pin = V

REF=VA

D

PD Pin = DGND

PD Pin = V

D,fCLK

PD Pin = DGND, C

PD Pin = V

D,fCLK

=0

DR

V

=3V 2.7 V (min)

DR

10 mA

41

4.5

4.5

=0

= 5 pF (Note 14)

L

0

2.5

0

= 5 pF (Note 15) 150 215 mW (max)

L

Limits

(Note 10)

57 mA (max)

8 mA (max)

(Limits)

Units

mA

mA

mA

mA

www.national.com 6

DC and Logic Electrical Characteristics (Continued)

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA=VD= +3.3V, VDR=

+2.5V, PD = 0V, External V

Boldface limits apply for T

= +1.0V, f

REF

J=TMIN

to T

Symbol Parameter Conditions

Power Down Power Consumption PD Pin = V

PSRR Power Supply Rejection Ratio

= 20 MHz, fIN= 10 MHz, tr=tf= 2 ns, CL= 15 pF/pin, Duty Cycle Stabilizer On.

CLK

: all other limits TJ= 25˚C (Notes 7, 8, 9)

MAX

, clock on 15 mW

D

Rejection of Full-Scale Error with

=3.0V vs. 3.6V

V

A

Typical

(Note 10)

72 dB

Limits

(Note 10)

Units

(Limits)

AC Electrical Characteristics

Unless otherwise specified, the following specifications apply for AGND = DGND = DR GND = 0V, VA=VD= +3.3V, VDR=

+2.5V, PD = 0V, External V

Boldface limits apply for T

= +1.0V, f

REF

J=TMIN

to T

Symbol Parameter Conditions

1

f

CLK

f

CLK

t

CH

t

CL

t

CH

t

CL

t

CONV

t

OD

t

AD

t

AJ

t

PD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is

functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed

specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test

conditions.

Note 2: All voltages are measured with respect to GND = AGND = DGND = 0V, unless otherwise specified.

Note 3: When the input voltage at any pin exceeds the power supplies (that is, V

50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 25 mA to two.

Note 4: The absolute maximum junction temperature (T

junction-to-ambient thermal resistance (θ

for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven

beyond the power supply voltages, or the power supply polarity is reversed). Obviously, such conditions should always be avoided.

Note 5: Human body model is 100 pF capacitor discharged through a 1.5 kΩ resistor. Machine model is 220 pF discharged through 0Ω.

Note 6: Reflow temperature profiles are different for lead-free and non-lead-free packages.

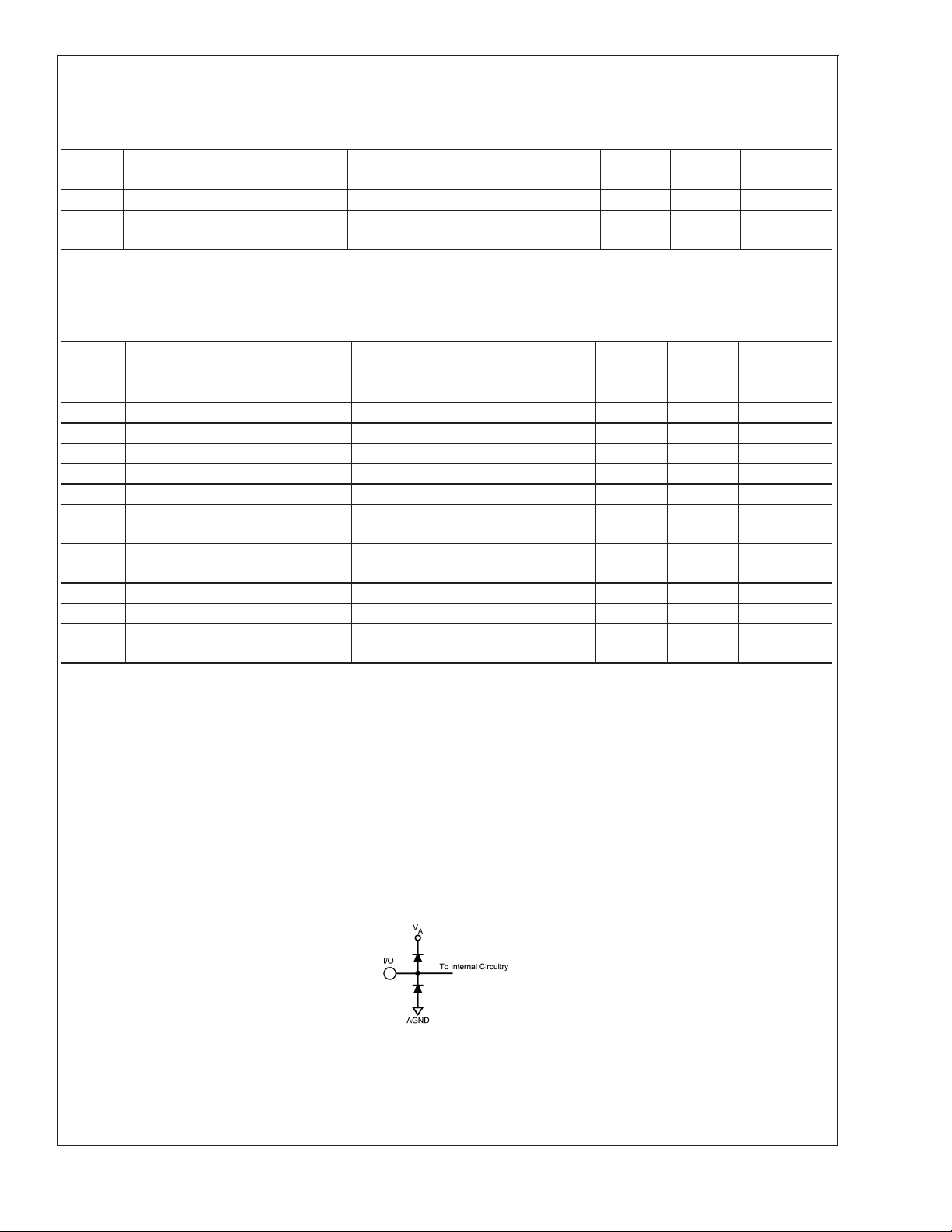

Note 7: The inputs are protected as shown below. Input voltage magnitudes above V

(Note 3). However, errors in the A/D conversion can occur if the input goes above V

input voltage must be ≤+3.4V to ensure accurate conversions.

Maximum Clock Frequency 20 MHz (min)

2

Minimum Clock Frequency 5 MHz

Clock High Time Duty Cycle Stabilizer On 25 10 ns (min)

Clock Low Time Duty Cycle Stabilizer On 25 10 ns (min)

Clock High Time Duty Cycle Stabilizer Off 25 20 ns (min)

Clock Low Time Duty Cycle Stabilizer Off 25 20 ns (min)

Conversion Latency 7

Data Output Delay after Rising

Clock Edge

Aperture Delay 2 ns

Aperture Jitter 0.7 ps rms

Power Down Mode Exit Cycle

), and the ambient temperature, (TA), and can be calculated using the formula PDMAX=(TJmax - TA)/θJA. The values

JA

= 20 MHz, fIN= 10 MHz, tr=tf= 2 ns, CL= 15 pF/pin, Duty Cycle Stabilizer On.

CLK

: all other limits TJ= 25˚C (Notes 7, 8, 9, 12)

MAX

Typical

(Note 10)

Limits

(Note 10)

6 9.6 ns (max)

0.1 µF on pins 30, 31, 32; 10 µF

between pins 30, 31

<

AGND, or V

IN

max) for this device is 150˚C. The maximum allowable power dissipation is dictated by TJmax, the

J

or below GND will not damage this device, provided current is limited per

A

or below GND by more than 100 mV. As an example, if VAis +3.3V, the full-scale

A

>

VA), the current at that pin should be limited to 25 mA. The

IN

280 µs

Units

(Limits)

Clock

Cycles

ADC14L020

20157011

Note 8: To guarantee accuracy, it is required that |VA–VD| ≤ 100 mV and separate bypass capacitors are used at each power supply pin.

Note 9: With the test condition for V

Note 10: Typical figures are at T

Level).

J

= +1.0V (2V

REF

= 25˚C, and represent most likely parametric norms. Test limits are guaranteed to National’s AOQL (Average Outgoing Quality

differential input), the 14-bit LSB is 122.1 µV.

P-P

www.national.com7

Loading...

Loading...