MXIC MX23L6422MC-11, MX23L6422YC-12, MX23L6422MC-12 Datasheet

MX23L6422

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

NC

A0

A1

A2

A3

A4

A5

NC

NC

VCC

D0

D16

D1

D17

VSS

VCC

D2

D18

D3

D19

NC

NC

D4

D20

D5

D21

VSS

VCC

D6

D22

D7

D23

VSS

A6

A7

A8

A9

A10

A11

A12

A13

NC

NC

NC

NC

NC

NC

A20

WORD

OE

CE

NC

VSS

NC

D31/A-1

D15

D30

D14

VSS

VCC

D29

D13

D28

D12

NC

D27

D11

D26

D10

VSS

VCC

D25

D9

D24

D8

VCC

A19

A18

A17

A16

A15

A14

NC

NC

NC

NC

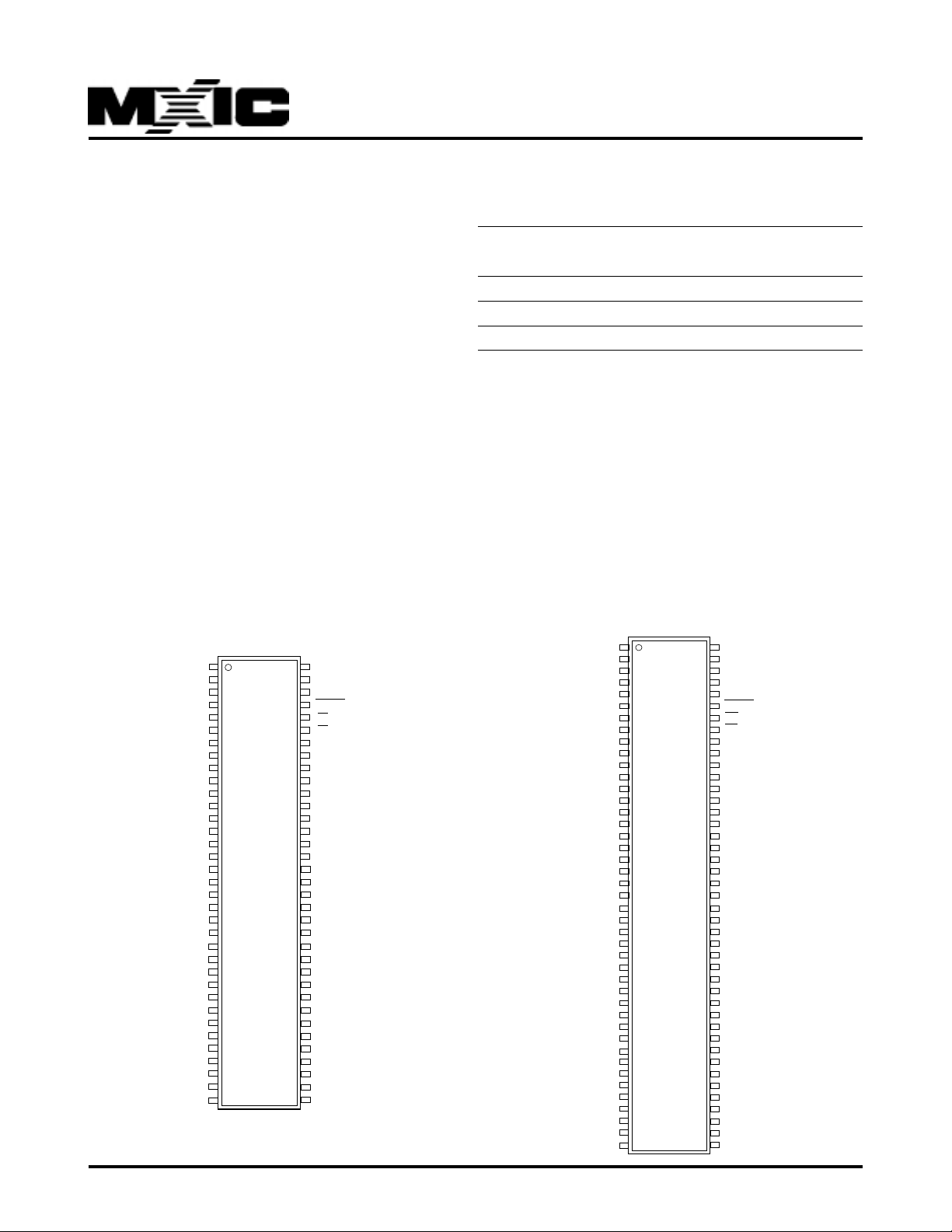

MX23L6422

3.3 Volt 64M-BIT (4M x 16 / 2M x 32) Mask ROM with Page Mode

FEATURES

• Bit organization

- 4M x 16 (byte mode)

- 2M x 32 (double word mode)

• Fast access time

- Random access: 110ns (max.) for 3.15~3.6V

120ns (max.) for 3.0~3.6V

- Page access: 30ns (max.)

• Page Size

- 8 double words per page

• Current

- Operating: 60mA (max.)

- Standby: 20uA (max.)

• Supply voltage

- 3.3V±10%

• Package

- 70 pin SSOP

- 86 pin TSOP(2)

PIN CONFIGURATION

70 SSOP

ORDER INFORMATION

Part No. Access Page Access Package

Time Time

MX23L6422MC-11 110ns 30ns 70 pin SSOP

MX23L6422MC-12 120ns 50ns 70 pin SSOP

MX23L6422YC-12 120ns 50ns 86 pin TSOP

86 TSOP(2)

70

A0

2

A1

3

A2

4

VCC

D16

D17

VSS

VCC

D18

D19

D20

D21

VSS

VCC

D22

D23

VSS

A10

A11

A12

A3

5

A4

6

A5

7

8

D0

9

10

D1

11

12

13

14

D2

15

16

D3

17

18

D4

19

20

D5

D6

D7

A6

A7

A8

A9

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

MX23L6422

P/N:PM0410 REV. 2.7, OCT. 19, 2001

NC

69

NC

68

A20

67

WORD

66

OE

65

CE

64

VSS

63

D31/A-1

62

D15

61

D30

60

D14

59

VSS

58

VCC

57

D29

56

D13

55

D28

54

D12

53

D27

52

D11

51

D26

50

D10

49

VSS

48

VCC

47

D25

46

D9

45

D24

44

D8

43

VCC

42

A19

41

A18

40

A17

39

A16

38

A15

37

A14

36

A13

1

MX23L6422

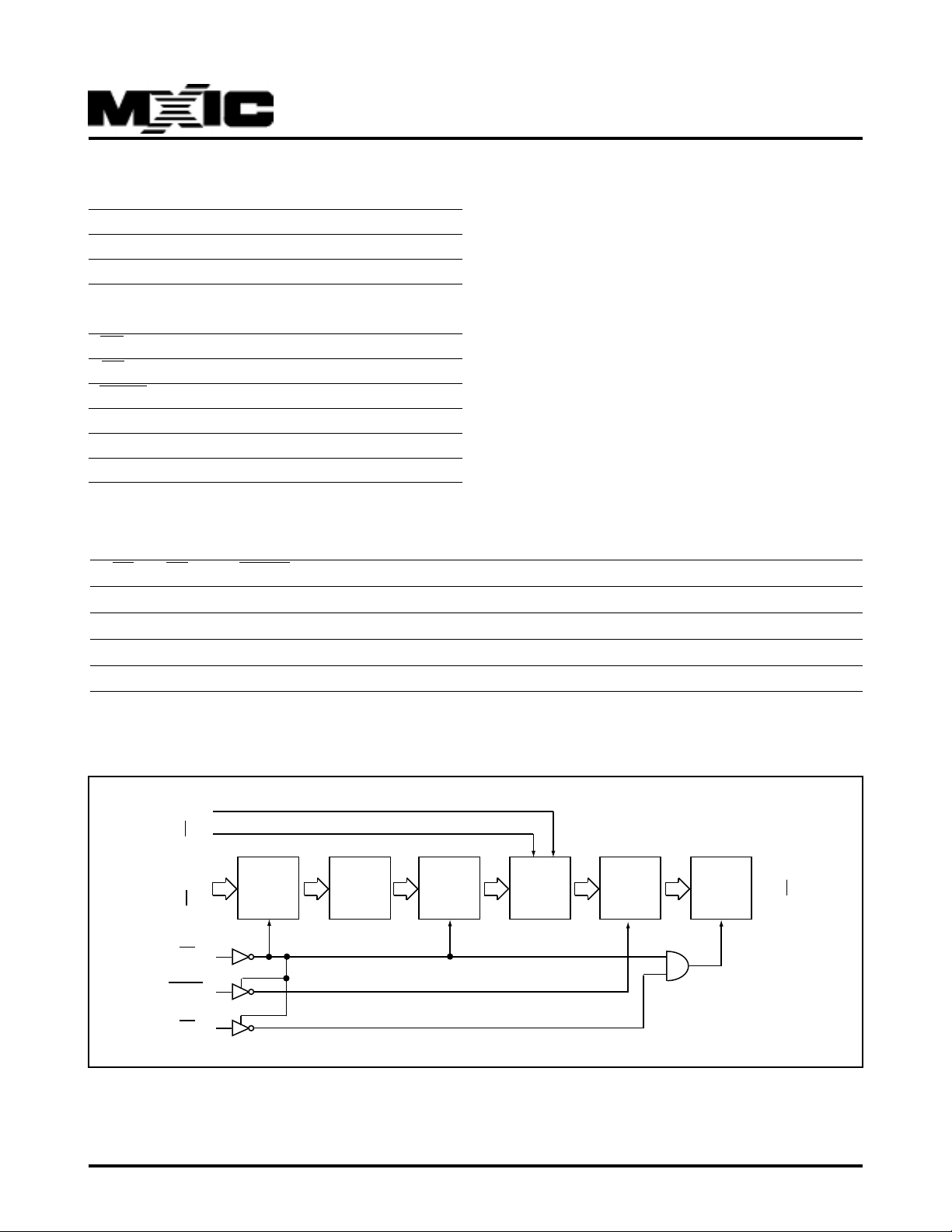

PIN DESCRIPTION

Symbol Pin Function

A0~A20 Address Inputs

D0~D30 Data Outputs

D31/A-1 D31 (Double W ord Mode)/ LSB Address

(Word Mode)

CE Chip Enable Input

OE Output Enable Input

WORD Double Word/ W ord Mode Selection

VC C Po wer Supply Pin

VSS Ground Pin

N C No Connection

MODE SELECTION

CE OE WORD D31/A-1 D0~D15 D16~D31 Mode Po wer

H X X X High Z High Z - Stand-by

L H X X High Z High Z - Active

L L H Output D0~D15 D16~D31 Double W ord Active

L L L Input D0~D15 High Z Word Active

BLOCK DIAGRAM

A0/(A-1)

A2

A3

A20

CE

WORD

OE

Address

Buffer

Memory

Array

Page

Buffer

Page

Decoder

Double

Word/

Word

Output

Buffer

D31/(D15)

D0

P/N:PM0410

REV. 2.7, OCT. 19, 2001

2

Loading...

Loading...