MSI MS-V115 Schematic

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

P621-A00: G98-GB1-64, MXM-I, 256/128MB GDDR2 (32M/16Mx16),

LVDS, HDMI, TV_OUT, VGA, HD Audio, DP option

Table of Contents

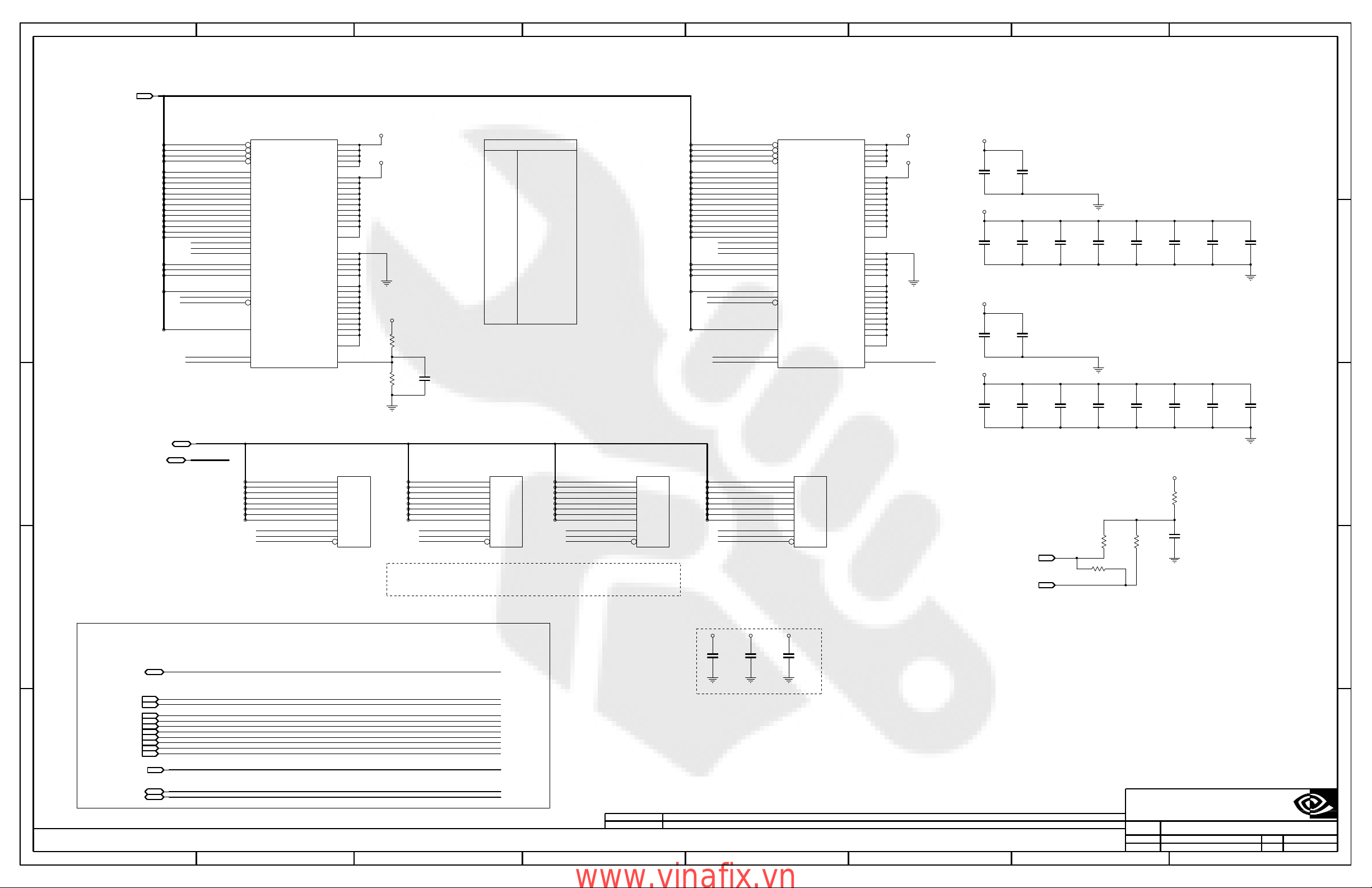

Page 1: PAGE OVERVIEW

Page 2: PCI EXPRESS INTERFACE

Page 3: GPU MEMORY INTERFACE

Page 4: MEMORY LOWER SUB-PARTITION INTERFACE

Page 5: MEMORY UPPER SUB-PARTITION INTERFACE

Page 6: DAC A/B

Page 7: LVDS(LINK A/B), HD AUDIO

Page 8: HDMI, DP

Page 9: MXM CONNECTOR

Page 10: GPIO, JTAG, TEMP SENSOR

Page 11: VBIOS & HDCP ROM, XTAL, SPREAD SPECTRUM, SPDIF

Page 12: NVVDD POWER SUPPLY

Page 13: PEX, FBVDDQ POWER SUPPLY

Page 14: STRAPS

Page 15: Basenet Report

Page 16: Cref Part

Base

SKU0001

SKU0002

SKU0003

SKU9998

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

600-10621-0000-000

600-10621-0001-000

600-10621-0002-000

600-10621-0003-000

600-10621-9998-000

<UNDEFINED?

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

Cancelled 128MB version

NB9M-GE G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

All components

<UNDEFINED?

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

PAGE OVERVIEW

www.vinafix.vn

600-10621-0001-000 A

p621 1 OF 16

Thorsten Freund

13-SEP-2007

BI

1/13 PCI_EXPRESS

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

PEX_IOVDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD_SENSE

GND_SENSE

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

PEX_PLLVDD

RFU

PEX_TERMP

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_RST

RFU

PEX_TX2

PEX_RX0

PEX_RX0

PEX_REFCLK

PEX_REFCLK

PEX_RX1

PEX_RX1

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX5

PEX_TX5

PEX_TX4

PEX_TX4

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_TX3

PEX_TX3

PEX_TX9

PEX_TX9

PEX_TX8

PEX_TX8

PEX_RX7

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX8

PEX_RX8

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX12

PEX_TX12

PEX_TX11

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_TX10

PEX_TX10

PEX_TX11

PEX_RX12

PEX_TX15

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

OUT

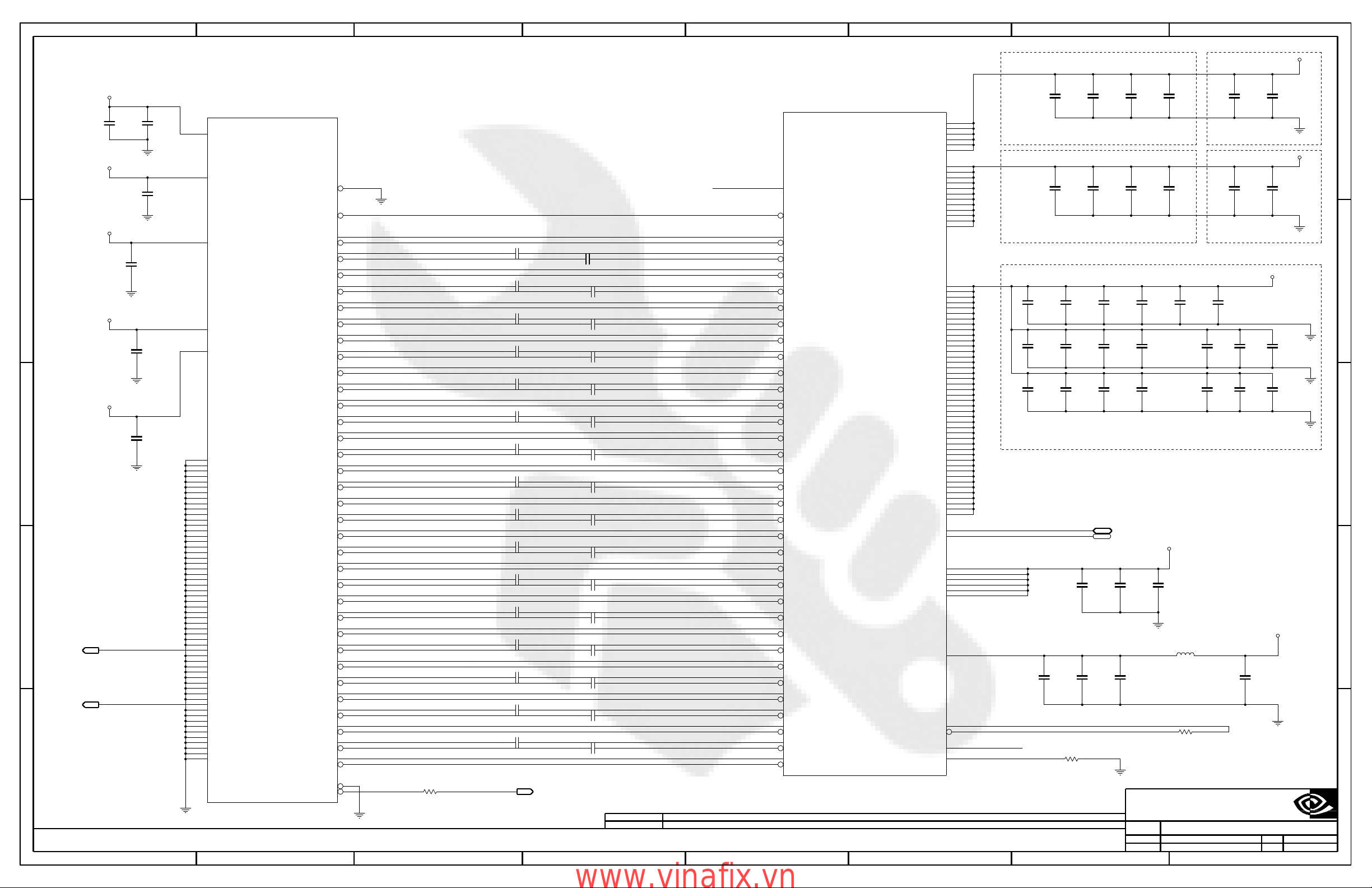

1/2 PCI-Express, Power

PEX_RST

CLK_REQ

PEX_REFCLK

PEX_TX2

PEX_RX2

PEX_RX2

PEX_TX1

PEX_TX1

PEX_RX1

PEX_TX0

PEX_TX0

PEX_RX1

PEX_RX0

PEX_REFCLK

PEX_RX0

PEX_TX2

PEX_RX6

PEX_TX5

PEX_TX5

PEX_RX6

PEX_TX4

PEX_TX4

PEX_RX5

PEX_RX5

PEX_TX3

PEX_RX4

PEX_RX4

PEX_TX3

PEX_RX3

PEX_RX3

PEX_TX9

PEX_TX9

PEX_RX9

PEX_RX9

PEX_TX8

PEX_TX8

PEX_RX8

PEX_RX8

PEX_TX7

PEX_TX7

PEX_RX7

PEX_RX7

PEX_TX6

PEX_TX6

PEX_RX11

PEX_RX10

PEX_RX10

PEX_TX10

PEX_TX10

PEX_RX13

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_RX11

PEX_TX11

PEX_TX11

PEX_RX13

PRSNT2

PRSNT1

PEX_TX15

PEX_RX15

PEX_RX15

PEX_TX15

PEX_TX14

PEX_TX14

PEX_RX14

PEX_RX14

PEX_TX13

PEX_TX13

3V3RUN

(1.5A)

(3.5A)

1V8RUN

(0.5A)

2V5RUN

(4A)

PWR_SRC

(0.5A)

5VRUN

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

OUT

OUT

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

PCI-EXPRESS

PLACE UNDER GPU (near BALLS)

PLACE near GPU

PEX_VDD

3V3_RUN

C2

.1UF

X5R

0402

COMMON

1V8_RUN

C3

.1UF

10V10V

10%10%

X5R

0402

COMMON

GND

CN1

CON_MXM_X16_EDGE

(NPHY,NONPHY)-X16(_SLI)

NONPHY-X16

COMMON

238

G1

G98-630-U1 NB

BGA533

CHANGED

2

C535

.1UF

10V

10%

GND

C531

.1UF

25V

10%

X7R

0603

COMMON

GND

C29

.1UF

10V

10%

X5R

0402

COMMON

GND

C536

.1UF

10V

10%

X5R

0402

COMMON

GND

X5R

0402

COMMON

GND

234

101

104

107

110

113

116

119

122

125

128

131

138

142

146

150

154

158

164

176

182

188

194

199

200

205

206

211

212

218

223

229

235

236

241

1

18

17

20

41

44

47

50

53

56

59

62

65

68

71

74

77

80

83

86

89

92

95

98

7<> 7<

PWR_SRC

2V5_RUN

5V_RUN

HDA_RST*

IFPC_HPD

10<

137

139

135

133

129

127

132

130

123

121

126

124

117

115

120

118

111

109

114

112

105

103

108

106

99

97

102

100

93

91

96

94

87

85

90

88

81

84

82

75

73

78

76

69

67

72

70

63

61

66

64

55

60

58

51

49

54

52

45

43

48

46

42

40

134

38

GND

GND

NET_NAME

PEX_TX0_C

PEX_TX0_C*

PEX_TX1_C

PEX_TX1_C*

PEX_TX2_C

PEX_TX2_C*

PEX_TX3_C

PEX_TX3_C*

PEX_TX4_C

PEX_TX4_C*

PEX_TX5_C

PEX_TX5_C*

PEX_TX6_C

PEX_TX6_C*

PEX_TX7_C

PEX_TX7_C*

PEX_TX9_C

PEX_TX9_C*

PEX_TX10_C

PEX_TX11_C

PEX_TX11_C*

PEX_TX12_C57

PEX_TX12_C*

PEX_TX13_C

PEX_TX13_C*

PEX_TX14_C*

PEX_TX15_C PEX_TX15_C39

PEX_TX15_C*37

PEX_PRSNT2

DIFF_PAIR

PEX_TX0_C

PEX_TX0_C

PEX_TX1_C

PEX_TX1_C

PEX_TX2_C

PEX_TX2_C

PEX_TX3_C

PEX_TX3_C

PEX_TX4_C

PEX_TX4_C

PEX_TX5_C

PEX_TX5_C

PEX_TX6_C

PEX_TX6_C

PEX_TX7_C

PEX_TX7_C

PEX_TX8_CPEX_TX8_C

PEX_TX8_CPEX_TX8_C*79

PEX_TX9_C

PEX_TX9_C

PEX_TX10_C

PEX_TX10_CPEX_TX10_C*

PEX_TX11_C

PEX_TX11_C

PEX_TX12_C

PEX_TX12_C

PEX_TX13_C

PEX_TX13_C

PEX_TX14_CPEX_TX14_C

PEX_TX14_C

PEX_TX15_C

R83

0402

NV_CRITICAL_NET

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

COMMON

5%

NV_IMPEDANCE

100DIFF

100DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF 0402 10V

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF .1UFC545

90DIFF

90DIFF

90DIFF

PEX_PRSNT2_R

C62290DIFF

0402

C611

C601

0402

C593

0402

C587

0402

C57990DIFF

0402

C575

0402

C570

0402

C568

C56690DIFF

0402

C564

0402

C562

0402

C560

0402

C558

0402

C553

0402

0402

.1UF

10V

10%

X5R

COMMON

.1UF

10V0402

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

10V

10%

X5R

COMMON

PEX_RST

14<

NV_CRITICAL_NET

NV_IMPEDANCE

1

1

C612

0402

COMMON

.1UF

10V

10%

X5R

0402 10V

C594

0402

C589

0402

C581

0402

C578

0402

C573

C569

0402

0402

C565

0402

C563

0402

C561

0402

C559

0402

C557

0402 10V

C549

C541

0402

.1UFC602

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V0402

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

.1UF

10%

X5R

COMMON

.1UF

10V0402

10%

X5R

COMMON

.1UF

10V

10%

X5R

COMMON

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF.1UFC567

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

90DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

PCI EXPRESS INTERFACE

www.vinafix.vn

SNN_RFU_AE9

NET_NAME

DIFF_PAIR

PEX_REFCLK

PEX_RCLK

PEX_REFCLK*

PEX_RCLK

PEX_TX0

PEX_TX0

PEX_TX0*

PEX_TX0

PEX_RX0

PEX_RX0

PEX_RX0*

PEX_RX0

PEX_TX1

PEX_TX1

PEX_TX1*

PEX_TX1

PEX_RX1

PEX_RX1

PEX_RX1*

PEX_RX1

PEX_TX2

PEX_TX2

PEX_TX2*

PEX_TX2

PEX_RX2

PEX_RX2

PEX_RX2*

PEX_RX2

PEX_TX3

PEX_TX3

PEX_TX3*

PEX_TX3

PEX_RX3

PEX_RX3

PEX_RX3*

PEX_RX3

PEX_TX4

PEX_TX4

PEX_TX4*

PEX_TX4

PEX_RX4

PEX_RX4

PEX_RX4*

PEX_RX4

PEX_TX5

PEX_TX5

PEX_TX5*

PEX_TX5

PEX_RX5

PEX_RX5

PEX_RX5*

PEX_RX5

PEX_TX6

PEX_TX6

PEX_TX6*

PEX_TX6

PEX_RX6

PEX_RX6

PEX_RX6*

PEX_RX6

PEX_TX7

PEX_TX7

PEX_TX7*

PEX_TX7

PEX_RX7

PEX_RX7

PEX_RX7*

PEX_RX7

PEX_TX8

PEX_TX8

PEX_TX8*PEX_TX8 AB18

PEX_RX8

PEX_RX8

PEX_RX8*

PEX_RX8

PEX_TX9

PEX_TX9

PEX_TX9*

PEX_TX9

PEX_RX9

PEX_RX9

PEX_RX9*

PEX_RX9

PEX_TX10

PEX_TX10

PEX_TX10*

PEX_TX10

PEX_RX10

PEX_RX10

PEX_RX10*

PEX_RX10

PEX_TX11

PEX_TX11

PEX_TX11*

PEX_TX11

PEX_RX11

PEX_RX11

PEX_RX11*

PEX_RX11

PEX_TX12

PEX_TX12

PEX_TX12*

PEX_TX12

PEX_RX12

PEX_RX12

PEX_RX12*

PEX_RX12

PEX_TX13

PEX_TX13

PEX_TX13*

PEX_TX13

PEX_RX13

PEX_RX13

PEX_RX13*

PEX_RX13

PEX_TX14

PEX_TX14

PEX_TX14*

PEX_TX14

PEX_RX14

PEX_RX14

PEX_RX14*

PEX_RX14

PEX_TX15 PEX_TX15 AE25

PEX_TX15*

PEX_TX15

PEX_RX15

PEX_RX15

PEX_RX15*

PEX_RX15

AE9

AD9

AB10

AC10

AD10

AD11

AE12

AF12

AD12

AC12

AG12

AG13

AB11

AB12

AF13

AE13

AD13

AD14

AE15

AF15

AD15

AC15

AG15

AG16

AB14

AB15

AF16

AE16

AC16

AD16

AE18

AF18

AD17

AD18

AG18

AG19

AC18

AF19

AE19

AB19

AB20

AE21

AF21

AD19

AD20

AG21

AG22

AD21

AC21

AF22

AE22

AB21

AB22

AE24

AF24

AC22

AD22

AG24

AF25

AD23

AD24

AG25

AG26

AE26

AF27

AE27

AC9

AD7

AD8

AE7

AF7

AG7

AB13

AB16

AB17

AB7

AB8

AB9

AC13

AC7

AD6

AE6

AF6

AG6

J10

J12

J13

J9

L9

M11

M17

M9

N11

N12

N13

N14

N15

N16

N17

N19

N9

P11

P12

P13

P14

P15

P16

P17

R11

R12

R13

R14

R15

R16

R17

R9

T11

T17

T9

U19

U9

W10

W12

W13

W18

W19

W9

W15

W16

A12

B12

C12

D12

E12

F12

AF10

AE10

AG9

AG10

NVVDD_SENSE

GND_SENSE

PEX_PLLVDDAF9

PEX_TCLK

PEX_TCLK*

SNN_RFU_AG9

PEX_TERMP

C632

.47UF

6.3V

10%

X5R

0402

COMMON

C629

.1UF

16V

10%

X7R

0402

COMMON

PLACE UNDER GPU (near BALLS)

C626

.47UF

6.3V

10%

X5R

0402

COMMON

C619

.1UF

16V

10%

X7R

0402

COMMON

PLACE UNDER GPU (near BALLS)

C596C618

.022UF

6.3V

10%

X5R

0402

COMMON

C627

.1UF

6.3V

10%

X7R

0402

COMMON

C628

.1UF

6.3V

10%

X7R

0402

1

PLACE UNDER GPU

C37

.1UF

6.3V

10%

X7R

0402

COMMON

PLACE UNDER GPU

C35

.01UF

6.3V

10%

X5R

0402

COMMON

R71

0402

C33

.1UF

6.3V

10%

X5R

0402

COMMON

1

1

2.49K

COMMON

1%

TP6

100DIFF

100DIFF

1.1V

16MIL

.022UF

6.3V

10%

X5R

0402

COMMON

C625

.1UF

6.3V

10%

X7R

0402

COMMON

C600

.1UF

6.3V

10%

X7R

0402

PEX_TCLK

PEX_TCLK

C634

1UF

6.3V

10%

X5R

0402

COMMON

C640

1UF

6.3V

10%

X5R

0402

COMMON

PLACE near GPU

C606

1UF 4.7UF 22UF1UF

6.3V

10%

X5R

0402

COMMON

C613 C631

.022UF

6.3V

10%

X5R

0402

COMMON

C592

.1UF

6.3V

10%

X7R

0402

COMMON

C597

.1UF

6.3V

10%

X7R

0402

.022UF

6.3V

10%

X5R

0402

COMMON

3V3_RUN

C620

1UF

6.3V

10%

X5R

0402

COMMON

C610

.47UF

6.3V

10%

X5R

0402

COMMON

C49

10UF

6.3V

20%

X5R

0805

C614

.022UF

6.3V

10%

X5R

0402

COMMON

C609

.1UF

6.3V

10%

X7R

0402

COMMON

C624

.1UF

6.3V

10%

X7R

0402

COMMONCOMMONCOMMON

12<>

C621

.1UF

6.3V

10%

X7R

0402

COMMON

C31

6.3V

10%

X5R

0402

COMMON

GND

10nH

LB3

COMMON

C34

1UF

6.3V

10%

X5R

0402

COMMON

GND

0603

200

R70

COMMON

0402

600-10621-0001-000 A

p621

Thorsten Freund

C616

.022UF

6.3V

10%

X5R

0402

COMMON

C30

4.7UF

6.3V

10%

X5R

0603

COMMON

C537

6.3V

10%

X5R

0603

COMMON

C598

1UF

6.3V

10%

X7R

0603

COMMON

C45

22UF

6.3V

20%

X5R

0805

C36

4.7UF

6.3V

10%

X5R

0603

COMMON

NVVDD

PEX_VDD

GND

C28

22UF

6.3V

20%

X5R

0805

COMMON

GND

PEX_VDD

C32

6.3V

20%

X5R

0805

COMMON

GND

C607

4.7UF

6.3V

10%

X5R

0603

COMMON

C48

47UF

4V

20%

X5R

0805

COMMONCOMMONCOMMONCOMMON

2 OF 16

13-SEP-2007

GND

GND

GND

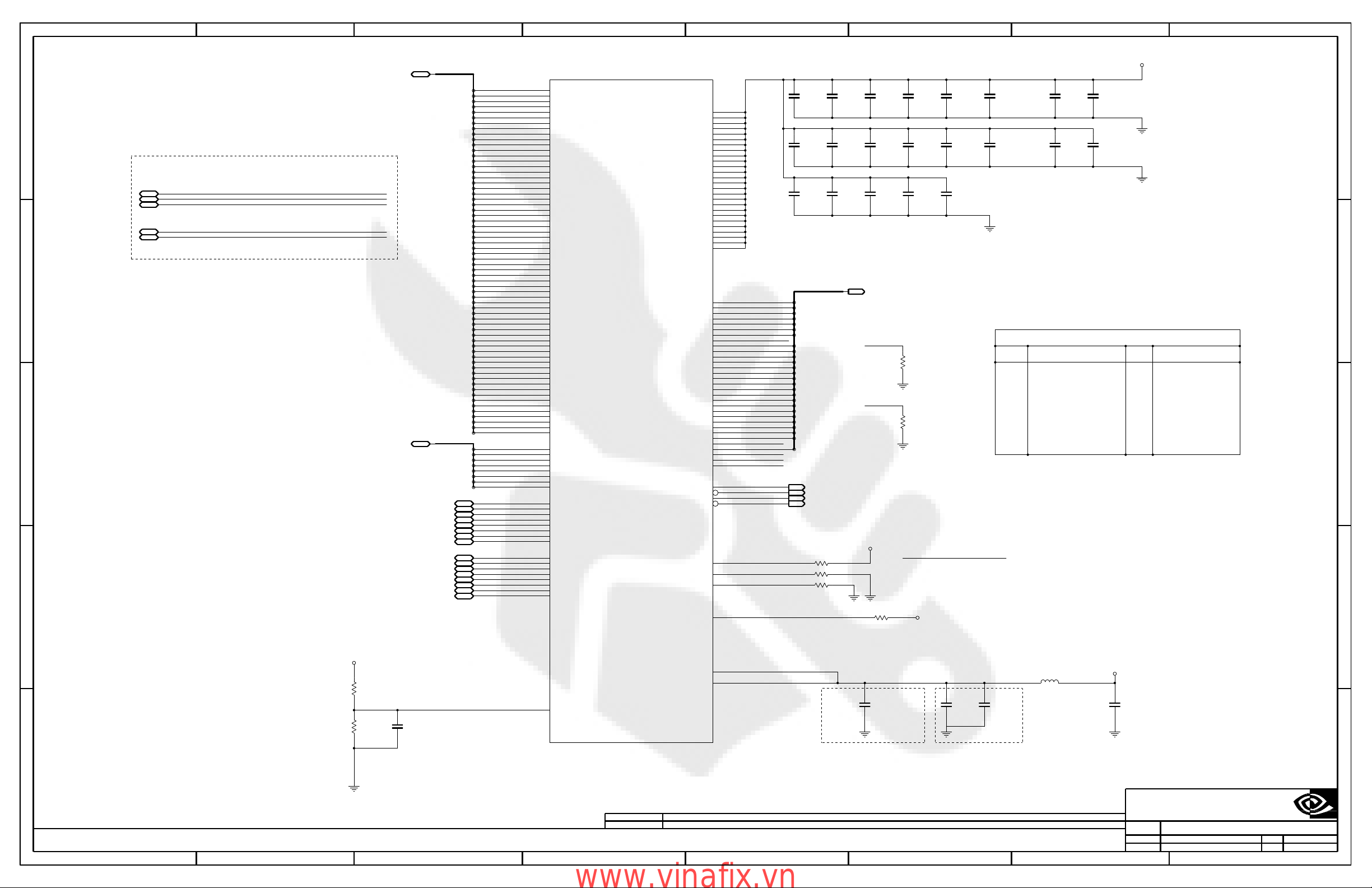

GPU MEMORY INTERFACE

OUT

OUT

OUT

OUT

OUTBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBI

2/13 FRAME_BUFFER

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD19

FBA_CMD18

FBA_CMD17

FBA_CMD16

FBA_CMD15

FBA_CMD14

FBA_CMD13

FBA_CMD12

FBA_CMD11

FBA_CMD10

FBA_CMD9

FBA_CMD8

FBA_CMD7

FBA_CMD6

FBA_CMD5

FBA_CMD4

FBA_CMD3

FBA_CMD2

FBA_CMD1

FBA_CMD0

FBA_CMD20

RFU

RFU

FBA_CMD28

FBA_CMD27

FBA_CMD26

FBA_CMD25

FBA_CMD24

FBA_CMD23

FBA_CMD22

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_CMD21

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

FBA_DEBUG

FB_DLLAVDD

FB_PLLAVDD

FBA_D17

FBA_D16

FBA_D15

FBA_D14

FBA_D13

FBA_D12

FBA_D11

FBA_D10

FBA_D9

FBA_D8

FBA_D7

FBA_D6

FBA_D5

FBA_D4

FBA_D3

FBA_D2

FBA_D1

FBA_D0

FBA_D18

FBA_D38

FBA_D37

FBA_D36

FBA_D35

FBA_D34

FBA_D33

FBA_D32

FBA_D31

FBA_D30

FBA_D29

FBA_D28

FBA_D27

FBA_D26

FBA_D25

FBA_D24

FBA_D23

FBA_D22

FBA_D21

FBA_D20

FBA_D19

FBA_D58

FBA_D57

FBA_D56

FBA_D55

FBA_D54

FBA_D53

FBA_D52

FBA_D51

FBA_D50

FBA_D49

FBA_D48

FBA_D47

FBA_D46

FBA_D45

FBA_D44

FBA_D43

FBA_D42

FBA_D41

FBA_D40

FBA_D39

FBA_D59

FBA_DQS_WP3

FBA_DQS_WP2

FBA_DQS_WP1

FBA_DQS_WP0

FBA_DQM7

FBA_DQM6

FBA_DQM5

FBA_DQM4

FBA_DQM3

FBA_DQM2

FBA_DQM1

FBA_DQM0

FBA_D63

FBA_D62

FBA_D61

FBA_D60

FBA_DQS_WP7

FBA_DQS_WP6

FBA_DQS_WP5

FBA_DQS_WP4

FBA_DQS_RN7

FBA_DQS_RN6

FBA_DQS_RN5

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FB_VREF

BIBIBIBIBIBIBI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

GPU MEMORY CONSTRAINTS

NET

FB_CAL_PD_VDDQ

FB_CAL_PU_GND

FB_CAL_TERM_GND

NET

FB_VREF

FB_PLLAVDD

50OHM

50OHM

50OHM

0.9V

1.1V

G1

G98-630-U1 NB

D21

C22

B22

A22

C24

B25

A25

A26

D22

E22

E24

D24

D26

D27

C27

B27

D16

E16

D17

F18

D20

F20

E21

F21

C16

B18

C18

D18

C19

C21

B21

A21

P22

P24

R23

R24

T23

U24

V24

N25

N26

R25

R26

T25

V26

V25

V27

V22

W22

W23

W24

AA22

AB23

AB24

AC24

W25

W26

W27

AA25

AB25

AB26

AD26

AD27

D23

C26

D19

B19

T24

T26

AA23

AB27

A24

C25

E19

T22

T27

AA24

AA26

B24

D25

E18

A18

R22

R27

Y24

AA27

BGA533

CHANGED

4<> 5<>

FB_VREF

C608

.1UF

10V

10%

X5R

0402

COMMON

FBA_D<63..0>

FBA_DQM<7..0>

4<

4<

4<

4<

5<

5<

5<

5<

4<

4<

4<

4<

5<

5<

5<

5<

FBA_D<0>

0

FBA_D<1>

1

FBA_D<2>

2

FBA_D<3>

3

FBA_D<4>

4

FBA_D<5>

5

FBA_D<6>

6

FBA_D<7>

7

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

FBA_D<14>

14

FBA_D<15>

15

FBA_D<16>

16

FBA_D<17>

17

FBA_D<18>

18

FBA_D<19>

19

FBA_D<20>

20

FBA_D<21>

21

FBA_D<22>

22

FBA_D<23>

23

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

FBA_D<30>

30

FBA_D<31>

31

FBA_D<32>

32

FBA_D<33>

33

FBA_D<34>

34

FBA_D<35>

35

FBA_D<36>

36

FBA_D<37>

37

FBA_D<38> V23

38

FBA_D<39>

39

FBA_D<40>

40

FBA_D<41>

41

FBA_D<42>

42

FBA_D<43>

43

FBA_D<44>

44

FBA_D<45>

45

FBA_D<46>

46

FBA_D<47>

47

FBA_D<48>

48

FBA_D<49>

49

FBA_D<50>

50

FBA_D<51>

51

FBA_D<52>

52

FBA_D<53>

53

FBA_D<54>

54

FBA_D<55>

55

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DQM<0>

0

FBA_DQM<1>

1

FBA_DQM<2>

2

FBA_DQM<3>

3

FBA_DQM<4>

4

FBA_DQM<5>

5

FBA_DQM<6>

6

FBA_DQM<7>

7

FBA_DQS_WP0

FBA_DQS_WP1

FBA_DQS_WP2

FBA_DQS_WP3 A19

FBA_DQS_WP4

FBA_DQS_WP5

FBA_DQS_WP6

FBA_DQS_WP7

FBA_DQS_RN0

FBA_DQS_RN1

FBA_DQS_RN2

FBA_DQS_RN3

FBA_DQS_RN4

FBA_DQS_RN5

FBA_DQS_RN6

FBA_DQS_RN7

16.00 A16

5<> 4<>

NV_CRITICALNV_IMPEDANCE

2

2

2

MIN_LINE_WIDTHVOLTAGE

16.00

16.00

Rtop

Rbot

FBVDDQ

R531

1.05K

1%

0402

COMMON

R530

1.05K

1%

0402

COMMON

VREF = FBVDDQ * Rbot/(Rtop + Rbot)

A13

B13

C13

D13

D14

E13

F13

F14

F15

F16

F17

F19

F22

H23

H26

J15

J16

J18

J19

L19

L23

L26

M19

N22

U22

Y22

FBA_CMD<0>

F26

FBA_CMD<1>

J24

FBA_CMD<2>

F25

FBA_CMD<3>

M23

FBA_CMD<4>

N27

FBA_CMD<5>

M27

FBA_CMD<6>

K26

SNN_FBA_CMD7

J25

FBA_CMD<8>

J27

FBA_CMD<9>

G23

FBA_CMD<10>

G26

FBA_CMD<11>

J23

FBA_CMD<12>

M25

FBA_CMD<13>

K27

FBA_CMD<14>

G25

FBA_CMD<15>

L24

FBA_CMD<16>

K23

FBA_CMD<17>

K24

FBA_CMD<18>

G22

FBA_CMD<19>

K25

FBA_CMD<20>

H22

FBA_CMD<21>

M26

FBA_CMD<22>

H24

FBA_CMD<23>

F27

FBA_CMD<24>

J26

FBA_CMD<25>

G24

SNN_FBA_CMND26

G27

FBA_CMD<27>

M24

SNN_FBA_CMND28

K22

SNN_FBA_RFU_1

J22

SNN_FBA_RFU_2

L22

FBA_CLK0

F24

FBA_CLK0*

F23

FBA_CLK1

N24

FBA_CLK1*

N23

FB_CAL_PD_VDDQ

B15

FB_CAL_PU_GND

A15

FB_CAL_TERM_GND

B16

M22

FB_PLLAVDD

R19

T19

FBA_DEBUG

PLACE UNDER GPU

C604

.022UF

16V

10%

X7R

0402

COMMON

C519

.1UF

10V

10%

X5R

0402

COMMON

C571 C586

4700PF

25V

10%

X7R

0402

COMMON

FBA_CMD<27..0>

0

1

2

3

4

5

6

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

27

4<

4<

5<

5<

24.3

R77

COMMON

0402

1%

30.1

R79

COMMON

0402

1%

60.4

R80

NO STUFF

0402

1%

350OHM

16.00

PLACE NEAR BALLS

C605

.022UF

16V

10%

X7R

0402

COMMON

C595

.1UF

10V

10%

X5R

COMMON

4700PF

25V

10%

X7R

0402

COMMON

GND

C580

.022UF

16V

10%

X7R

0402

COMMON

C508

.1UF

10V

10%

X5R

04020402

COMMON

C591

4700PF

25V

10%

X7R

0402

COMMON

5< 4<

FBA_CMD<11>

CKE PD

FBA_CMD<12>

ODT/RST PD

FBVDDQ

GND

R521

0402

5%

C590

1UF

6.3V

10%

X5R

0402

COMMON

GND

10K

COMMON

GND

GND

R515

10K

5%

0402

COMMON

R516

10K

5%

0402

COMMON

DDR1

50R

50R

ns

C617

.022UF

16V

10%

X7R

0402

COMMON

C603

.1UF

10V

10%

X5R

0402

COMMON

4700PF

25V

10%

X7R

0402

COMMON

FBVDDQ

C584

.022UF

16V

10%

X7R

0402

COMMON

C583

.1UF

10V

10%

X5R

0402

COMMON

C574C582

4700PF

25V

10%

X7R

0402

COMMON

C585

.022UF

16V

10%

X7R

0402

COMMON

C65

.1UF

10V

10%

X5R

0402

COMMON

GND

C41

.1UF

6.3V

10%

X5R

0402

COMMON

DDR3

60R

40R

40R

C43

4.7UF

6.3V

10%

X5R

0603

COMMON

DDR2

40R

40R

ns

GND

PLACE NEAR GPU

FBVDDQ

C504

1UF

6.3V

10%

X5R

COMMON

C588

1UF

6.3V

10%

X5R

COMMON

C54

4.7UF

6.3V

10%

X5R

06030402

COMMON

C534

4.7UF

6.3V

10%

X5R

06030402

COMMON

GND

GND

COMMAND BUS MAPPING DDR2-FBGA84

PEX_VDD

GND

CMD

CMD16

CMD17

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

C47

4.7UF

6.3V

10%

X5R

0603

COMMON

CMD

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

FB[31..0]

A3

A0

A2

A1

-

-

CS1*(BA2)CMD7

CS0*

WE*

BA0

CKE

RST/ODT

A12

RAS*

LB4

BEAD_0603

FB[63..32]

A0

A1

A3

A4

A5

CS1*(BA2)

CS0*

WE*

BA0

CKE

RST/ODT

A2

A12

RAS*

220R@100MHz

COMMON

FB[31..0]

A11

A10

BA1CMD18

A8

A9

A6

A5

A7

A4

CAS*

A13

BA2

RFU0

RFU1

FB[63..32]

A11

A10

BA1

A8

A9

A6

A7

CAS*

A13

BA2

RFU0

RFU1

RFU2RFU2

GND

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

GPU MEMORY INTERFACE

www.vinafix.vn

600-10621-0001-000 A

p621

Thorsten Freund

3 OF 16

13-SEP-2007

C514

IN

IN

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

IN

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

BIBIBIININININININININININBIBI

IN

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

.1UF

6.3V6.3V

X5R

04020402

COMMONCOMMON

C506

.1UF

6.3V

10%

X5R

0402

COMMON

C84

.1UF

6.3V

X5R

0402

COMMON

C74

.1UF

6.3V

X5R

0402

COMMON

GND

C62

.1UF

6.3V

10%

X5R

0402

COMMON

C520

.1UF

6.3V

10%

X5R

0402

COMMON

GND

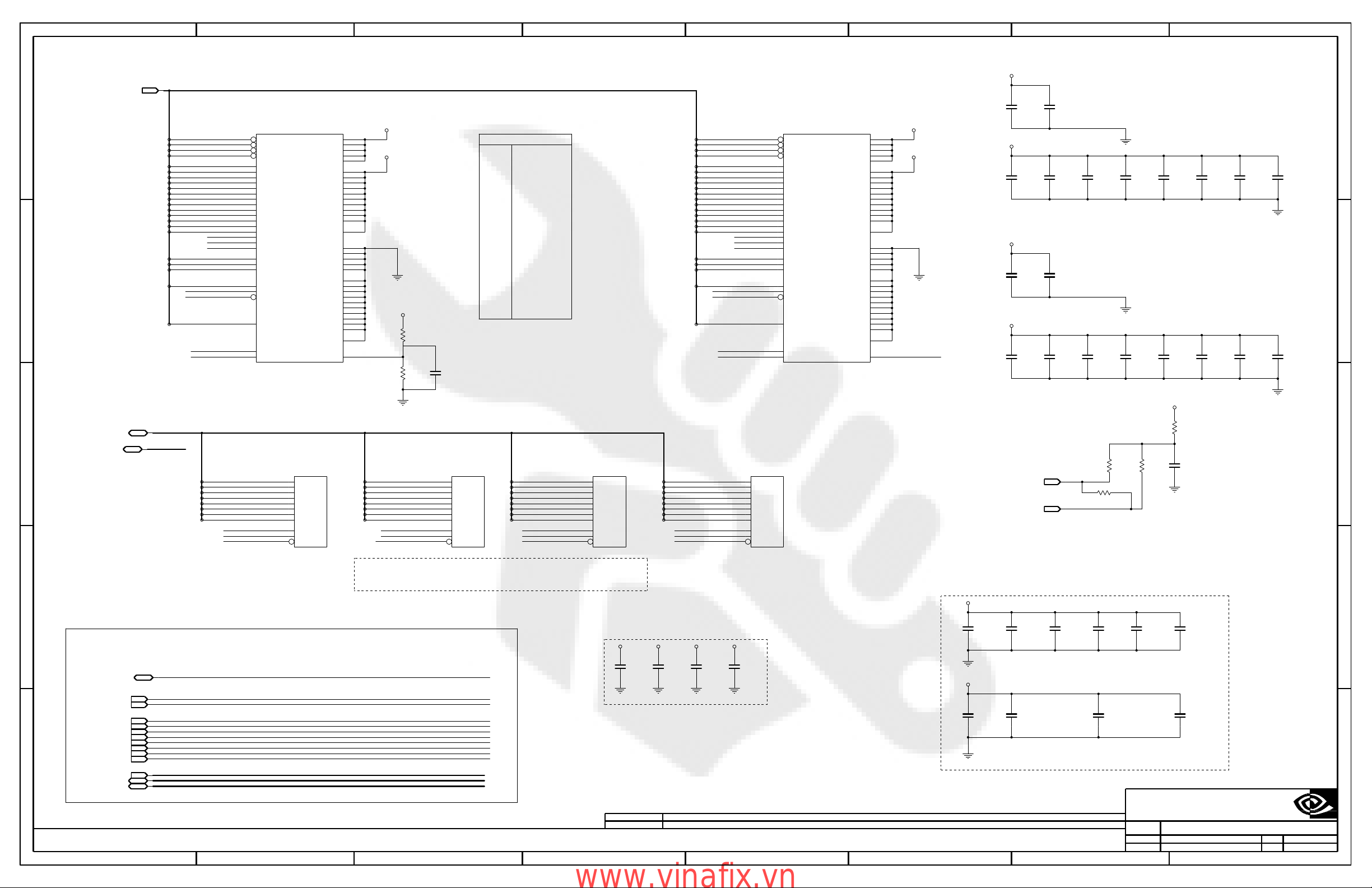

MEMORY LOWER SUB-PARTITION INTERFACE D<31..0>

3> 5< 4<

3<>

4<>

FBA_DQM<3..0>

3<>

4<>

FBA_CMD<27..0>

FBA_CMD<15>

15

FBA_CMD<25>

25

FBA_CMD<9>

9

FBA_CMD<8>

8

FBA_CMD<1>

1

FBA_CMD<3>

3

FBA_CMD<2>

2

FBA_CMD<0>

0

FBA_CMD<24>

24

FBA_CMD<22>

22

FBA_CMD<21>

21

FBA_CMD<23>

23

FBA_CMD<19>

19

FBA_CMD<20>

20

FBA_CMD<17>

17

FBA_CMD<16>

16

FBA_CMD<14>

14

FBA_CMD<10>

10

FBA_CMD<18>

18

FBA_CMD<27>

27

FBA_CMD<11>

11

FBA_CLK0

FBA_CLK0*

FBA_CMD<12>

12

FBA_D<31..0>

SNN_A13_1

SNN_A14_1

SNN_A15_1

SNN_FBA_NC1

SNN_FBA_NC2

0

1

2

3

4

5

6

7

M1

32MX16DDR2-2.5

BGA84

COMMON

K7

L7

K3

L8

M8

M3

M7

N2

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

FBA_D<0>

FBA_D<1>

FBA_D<2>

FBA_D<3>

FBA_D<4>

FBA_D<5>

FBA_D<6>

FBA_D<7> D3

FBA_DQM<0>

FBA_DQS_WP0

FBA_DQS_RN0

M1

32MX16DDR2-2.5

BGA84

COMMON

D9

B9

D7

C8

D1

C2

B1

B3

B7

A8

FBVDDQ

A1

E1

J9

M9

FBVDDQ

R1

A9

C1

C3

C7N8

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

GND

FBVDDQ

R505

1.02K

1%

R1

0402

COMMON

FBA_VREF1J2

R501

1.02K

1%

R2

0402

COMMON

VREF = FBVDDQ * R2/(R1 + R2)

LOWER SUB_PARTITION A

COMMAND BUS MAPPING

Note: CS1* not used

for single rank

C70

.1UF

16V

10%

X5R

0402

COMMON

CMD-ADDR

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD28

CMD29

CMD30 RFU2

A3

A0

A2

A1

NC

NC

NC

CS1*

CS0*

WE*

BA0

CKE

RST/ODT

NC

A12

RAS*

A11

A10

BA1

A8

A9

A6

A5

A7

A4

CAS*

A13

BA2CMD27

RFU0

RFU1

GND

M501

32MX16DDR2-2.5

BGA84

FBA_D<8>

8

FBA_D<9>

9

FBA_D<10>

10

FBA_D<11>

11

FBA_D<12>

12

FBA_D<13>

13

14

FBA_D<15> C8

15

FBA_DQM<1>

FBA_DQS_WP1

FBA_DQS_RN1

COMMON

D1

C2

B1

D3

D7

D9

B9FBA_D<14>

B3

B7

A8

16

19

18

17

20

21

22

23

FBA_D<16>

FBA_D<19>

FBA_D<18>

FBA_D<17>

FBA_D<20>

FBA_D<21>

FBA_D<22>

FBA_D<23>

FBA_DQM<2>

FBA_DQS_WP2

FBA_DQS_RN2

FBA_CMD<15>

15

FBA_CMD<25>

25

FBA_CMD<9>

9

FBA_CMD<8>

8

FBA_CMD<1>

1

FBA_CMD<3>

3

FBA_CMD<2>

2

FBA_CMD<0>

0

FBA_CMD<24>

24

FBA_CMD<22>

22

FBA_CMD<21>

21

FBA_CMD<23>

23

FBA_CMD<19>

19

FBA_CMD<20>

20

FBA_CMD<17>

17

FBA_CMD<16>

16

FBA_CMD<14>

14

FBA_CMD<10>

10

FBA_CMD<18>

18

FBA_CMD<27>

27

FBA_CMD<11>

11

FBA_CLK0

FBA_CLK0* K8

FBA_CMD<12>

12

SNN_FBA_NC4

M501

32MX16DDR2-2.5

BGA84

COMMON

F1

H3

G2

H1

F9

G8

H7

H9

F3

F7

E8

FBA_D<24>

24

FBA_D<25>

25

FBA_D<26>

26

FBA_D<27>

27

FBA_D<28>

28

FBA_D<29>

29

30

FBA_D<31> H3

31

FBA_DQM<3>

FBA_DQS_WP3

SNN_A13_2

SNN_A14_2 R3

SNN_A15_2

M1

32MX16DDR2-2.5

BGA84

COMMON

H9

G8

H7

F9

G2

H1

F1FBA_D<30>

F3

F7

E8FBA_DQS_RN3

M501

32MX16DDR2-2.5

BGA84

COMMON

K7

L7

K3

L8

M8

M3

M7

N2

N3

N7

P2

P8

P3

M2

P7

R2

R8

R7

L2

L3

L1

K2

J8

K9

A2SNN_FBA_NC3

E2

FBVDDQ

FBVDDQ

A1

E1

J9

M9

FBVDDQ

R1

A9

C1

C3

C7N8

C9

E9

G1

G3

G7

G9

FBVDDQ

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

GND

FBVDDQ

FBVDDQ

MEMORY DECOUPLING

C510

4.7UF

6.3V

10%

X5R

0603

COMMON

C509

.1UF

6.3V

10% 10%10%

X5R

0402

C556

4.7UF

6.3V

10%

X5R

0603

COMMON

C76

.1UF

6.3V

0402

COMMONCOMMON

MEMORY DECOUPLING

C53

4.7UF

6.3V

10%

X5R

0603

COMMON COMMON

C57

4.7UF

6.3V

10%

X5R

0603

C79

.1UF

6.3V

X5RX5R

0402

COMMON

GND

GND

C518

.1UF

6.3V

X5R

0402

COMMON

C521

.1UF

10%10% 10% 10% 10%

X5R

J7

C551

FBA_VREF1

J2

.1UF

6.3V

10%

X5R

0402

COMMON

C502

.1UF

6.3V

10%

X5R

COMMON

C507

.1UF

6.3V

10%

X5R

04020402

COMMON

C82

.1UF

6.3V

10%

X5R

0402

COMMON

C512

.1UF

6.3V

10%

X5R

0402

COMMON

FBVDDQ

R89

0

0402

NO STUFF

4< 3>

4< 3>

FBA_CLK0

FBA_CLK0*

R91

0402

1%

FBA_CLK0_TERM

R90

121

1%

0402

COMMON

243

NO STUFF

R92

121

1%

0402

COMMON

GND

5.00

1.8V

C80

.01UF

16V

10%

X7R

0402

COMMON

PLACE close to memorires so as to

Minimize the stub length!!

Single resistor termination to be placed on

same pads as 2 resistor termination

Place vias for both DQS, longest, and shortest

bit of each byte just outside the memory packaged body.

X-cap for CMD BUS

FBVDDQ

Place these caps next to plane transitions

MEMORY CONSTRAINTS

4<>

4<>

4< 3>

4< 3>

4< 3> 5<

NET

FBA_VREF1

NET

FBA_CLK0

FBA_CLK0*

3<>

3<>

3<>

3<>

3<>

3<>

3<>

3<>

3<>

3<>

FBA_DQS_WP0

FBA_DQS_RN0

FBA_DQS_WP1

FBA_DQS_RN1

FBA_DQS_WP2

FBA_DQS_RN2

FBA_DQS_WP3

FBA_DQS_RN3

FBA_CMD<27..0>

FBA_D<31..0>

FBA_DQM<3..0>

DIFFPAIR

FBA_CLK0

FBA_CLK0

FBADQS0

FBADQS0

FBADQS1

FBADQS1

FBADQS2

FBADQS2

FBADQS3

FBADQS3

MIN_LINE_WIDTH

16MIL

CRITICAL

1

1

1

1

1

1

1

1

1

1

2

2

2

VOLTAGE

0.9V

IMPEDANCE

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

50OHM

50OHM

50OHM

www.vinafix.vn

FBVDDQ

GND GND

C513

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

FBVDDQ

C527

.01UF

25V

10%

X7R

0402

COMMON

GND

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

MEMORY LOWER SUB-PARTITION INTERFACE

C547

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

GND

C72

.01UF

25V

10%

X7R

0402

COMMON

GND

FBVDDQ

GND

C69

.01UF

10%

X7R

0402

COMMON

C75

.01UF

25V

10%

X7R

0402

COMMON

C539

.01UF

25V 25V25V

10%

X7R

COMMON

C68

.01UF

25V

10%

X7R

0402

COMMON

C533

.01UF

10%

X7R

04020402

COMMON

C511

.01UF

25V

10%

X7R

0402

COMMON

C51

.01UF

25V

10%

X7R

0402

COMMON

C525

.01UF

10%

X7R

0402

COMMON

C530

.01UF

25V25V

10%

X7R

0402

COMMON

C71

.01UF

25V

10%

X7R

0402

COMMON

600-10621-0001-000 A

p621

Thorsten Freund

4 OF 16

13-SEP-2007

IN

IN

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

IN

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

BIBIBIINININININININININININBI

BI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

MEMORY UPPER SUB-PARTITION INTERFACE D<63..32>

3<> 5<>

15

25

9

8

1

3

13

4

5

6

21

23

19

20

17

16

14

10

18

27

11

12

3<> 5<>

FBA_CMD<27..0>

FBA_CMD<15>

FBA_CMD<25>

FBA_CMD<9>

FBA_CMD<8>

FBA_CMD<1>

FBA_CMD<3>

FBA_CMD<13>

FBA_CMD<4>

FBA_CMD<5>

FBA_CMD<6>

FBA_CMD<21>

FBA_CMD<23>

FBA_CMD<19>

FBA_CMD<20>

FBA_CMD<17>

FBA_CMD<16>

FBA_CMD<14>

SNN_A13_3

SNN_A14_3

SNN_A15_3

FBA_CMD<10>

FBA_CMD<18>

FBA_CMD<27>

FBA_CMD<11>

FBA_CLK1

FBA_CLK1*

FBA_CMD<12>

SNN_FBA_NC5

SNN_FBA_NC6

FBA_DQM<7..4>

FBA_D<63..32>

M2

32MX16DDR2-2.5

BGA84

COMMON

K7

L7

K3

L8

M8

M3

M7

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

32

33

34

35

36

37

38

39

FBA_D<32>

FBA_D<33>

FBA_D<34>

FBA_D<35>

FBA_D<36>

FBA_D<37>

FBA_D<39> D9

FBA_DQM<4>

FBA_DQS_WP4

FBA_DQS_RN4

M502

32MX16DDR2-2.5

BGA84

COMMON

D3

D1

B1

C2

D7

C8

B9FBA_D<38>

B3

B7

A8

A1

E1

J9

M9

R1

A9

C1

C3N2

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

FBVDDQ

FBVDDQ

R502

1.02K

COMMON

FBA_VREF2

R506

1.02K

COMMON

GND

FBVDDQ

1%

0402

1%

0402

R1

R2

VREF = FBVDDQ * R2/(R1 + R2)

GND

40

41

42

43

44

45

46

47

C73

.1UF

16V

10%

X5R

0402

COMMON

FBA_D<40>

FBA_D<41>

FBA_D<42>

FBA_D<43>

FBA_D<44>

FBA_D<45>

FBA_D<46>

FBA_D<47>

FBA_DQM<5>

FBA_DQS_WP5

FBA_DQS_RN5

UPPER SUB_PARTITION A

COMMAND BUS MAPPING

CMD-ADDR

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

Note: CS1* not used

for single rank

M2

32MX16DDR2-2.5

BGA84

COMMON

D7

D9

C8

B9

D3

C2

D1

B1

B3

B7

A8

NC

A0

NC

A1

A3

A4

A5

CS1*

CS0*

WE*

BA0

CKE

RST/ODT

A2

A12

RAS*

A11

A10

BA1

A8

A9

A6

NC

A7

NC

CAS*

A13

BA2

RFU0

RFU1

RFU2

48

49

50

51

52

53

54

55

FBA_D<48>

FBA_D<49>

FBA_D<50>

FBA_D<51>

FBA_D<52>

FBA_D<53>

FBA_D<55> H3

FBA_DQM<6>

FBA_DQS_WP6

M2

32MX16DDR2-2.5

BGA84

COMMON

F9

H9

H7

G8

H1

G2

F1FBA_D<54>

F3

F7

E8FBA_DQS_RN6

FBA_CMD<15>

15

FBA_CMD<25>

25

FBA_CMD<9>

9

FBA_CMD<8>

8

FBA_CMD<1>

1

FBA_CMD<3>

3

FBA_CMD<13>

13

FBA_CMD<4>

4

FBA_CMD<5>

5

FBA_CMD<6>

6

FBA_CMD<21>

21

FBA_CMD<23>

23

FBA_CMD<19>

19

FBA_CMD<20>

20

FBA_CMD<17>

17

FBA_CMD<16>

16

FBA_CMD<14>

14

SNN_A13_4

SNN_A14_4

SNN_A15_4

FBA_CMD<10>

10

FBA_CMD<18>

18

FBA_CMD<27>

27

FBA_CMD<11>

11

FBA_CLK1 J8

FBA_CLK1*

FBA_CMD<12>

12

SNN_FBA_NC7

SNN_FBA_NC8

FBA_D<56>

56

FBA_D<57>

57

FBA_D<58>

58

FBA_D<59>

59

FBA_D<60>

60

FBA_D<61>

61

FBA_D<62>

62

FBA_D<63>

63

FBA_DQM<7>

FBA_DQS_WP7

FBA_DQS_RN7

M502

32MX16DDR2-2.5

BGA84

COMMON

K7

L7

K3

L8

M8

M3

M7

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

K8

K9

A2

E2

M502

32MX16DDR2-2.5

BGA84

COMMON

H3

F1

G2

F9

H1

H9

H7

G8

F3

F7

E8

4< 3> 5<

Place vias for both DQS, longest, and shortest

bit of each byte just outside the memory packaged body.

MEMORY CONSTRAINTS

3>

5<

3>

5<

3<>

3<>

3<>

3<>

3<>

3<>

3<>

3<>

3>

4< 5<

3<>

5<>

3<> 5<>

NET

FBA_VREF2

NET

FBA_CLK1

FBA_CLK1*

FBA_DQS_WP4

FBA_DQS_RN4

FBA_DQS_WP5

FBA_DQS_RN5

FBA_DQS_WP6

FBA_DQS_RN6

FBA_DQS_WP7

FBA_DQS_RN7

FBA_CMD<27..0>

FBA_D<63..32>

FBA_DQM<7..4>

DIFFPAIR

FBA_CLK1

FBA_CLK1

FBADQS4

FBADQS4

FBADQS5

FBADQS5

FBADQS6

FBADQS6

FBADQS7

FBADQS7

MIN_LINE_WIDTH

16MIL

CRITICAL

1

1

1

1

1

1

1

1

1

1

2

2

2

VOLTAGE

0.9V

IMPEDANCE

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

50OHM

50OHM

50OHM

www.vinafix.vn

Place near signal transition area

FBVDDQ

GND

NB9M-GS G98M ?/400MHz, 256MB(64bit) GDDR2 32Mx16 84FBGA, LVDS + HDMI + SD/HD(TV_OUT) + VGA

MEMORY UPPER SUB-PARTITION INTERFACE

C543

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

GND

C554

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

GND

C64

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

A1

E1

J9

M9

FBVDDQ

R1

A9

C1

C3N2

C7

C9

E9

G1

G3

G7

G9

FBVDDQ

FBVDDQ

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

GND

FBVDDQ

J7

FBA_VREF2

J2

FBVDDQ

MEMORY DECOUPLING

C63

4.7UF

6.3V

10%

X5R

0603

COMMON

C503

.1UF

6.3V

10%

X5R

0402

COMMON

C555

4.7UF

6.3V

10%

X5R

0603

COMMON

C77

.1UF

6.3V

10%

X5R

0402

COMMON

MEMORY DECOUPLING

C85

4.7UF

6.3V

10%

X5R

0603

COMMON

C538

.1UF

10%

X5R

0402

COMMON

C59

4.7UF

6.3V

10%

X5R

0603

COMMON

C546

.1UF

6.3V6.3V 6.3V 6.3V 6.3V6.3V 6.3V6.3V

10%

X5R

0402

COMMON

C548

.1UF

6.3V

10%

X5R

0402

COMMON

C516

.1UF

10%

X5R

0402

COMMON

GND

GND

C81

.1UF

6.3V

10%

X5R

0402

COMMON

C529

.1UF

10%

X5R

0402

COMMON

C544

.1UF

6.3V

10%

X5R

0402

COMMON

C528

.1UF

10%

X5R

0402

COMMON

C505

.1UF

6.3V

10%

X5R

0402

COMMON

C517

.1UF

10%

X5R

0402

C67

.1UF

6.3V

10%

X5R

0402

COMMON

C50

.1UF

10%

X5R

0402

COMMONCOMMON

GND

C522

.1UF

6.3V

10%

X5R

0402

COMMON

C515

.1UF

10%

X5R

0402

COMMON

GND

FBVDDQ

R93

0

0402

NO STUFF

GND

1.8V

5.00

C83

.01UF

16V

10%

X7R

0402

COMMON

FBA_CLK1_TERM

R94

R96

121

121

1%

1%

0402

0402

COMMON

R95

0402

1%

COMMON

243

NO STUFF

3> 5<

3> 5<

FBA_CLK1

FBA_CLK1*

PLACE close to memorires so as to

Minimize the stub length!!

Single resistor termination to be placed on

same pads as 2 resistor termination

600-10621-0001-000 A

p621

Thorsten Freund

5 OF 16

13-SEP-2007

Loading...

Loading...