MSI MS-V108 Schematic 0b

5

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

RV630 DDR2-REVISION HISTORY Friday, May 04, 2007

RV630 DDR2-REVISION HISTORY Friday, May 04, 2007

RV630 DDR2-REVISION HISTORY Friday, May 04, 2007

REVISION HISTORY

REVISION HISTORY

REVISION HISTORY

D D

PCB

PCB

Sch

Sch

Sch

Rev

Rev

Rev

C C

PCB

Rev

Rev

Rev

0

00A

Date

Date

Date

07/04/20

Initial design for RV630 DDR2 AGP, BASES ON B236

4

NOTE:

NOTE:

NOTE:

3

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

This schematic represents the PCB, it does not represent any specific SKU.

This schematic represents the PCB, it does not represent any specific SKU.

This schematic represents the PCB, it does not represent any specific SKU.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

For Stuffing options (component values, DNI’s, …) please consult the product specific BOM.

Please contact AMD representative to obtain latest BOM closest to the application desired.

Please contact AMD representative to obtain latest BOM closest to the application desired.

Please contact AMD representative to obtain latest BOM closest to the application desired.

REVISION DESCRIPTION

REVISION DESCRIPTION

REVISION DESCRIPTION

2

Date:Schematic No.

Date:Schematic No.

Date:Schematic No.

1

Rev

Rev

Rev

0

0

0

B B

A A

5

4

3

2

1

www.vinafix.vn

5

4

3

2

1

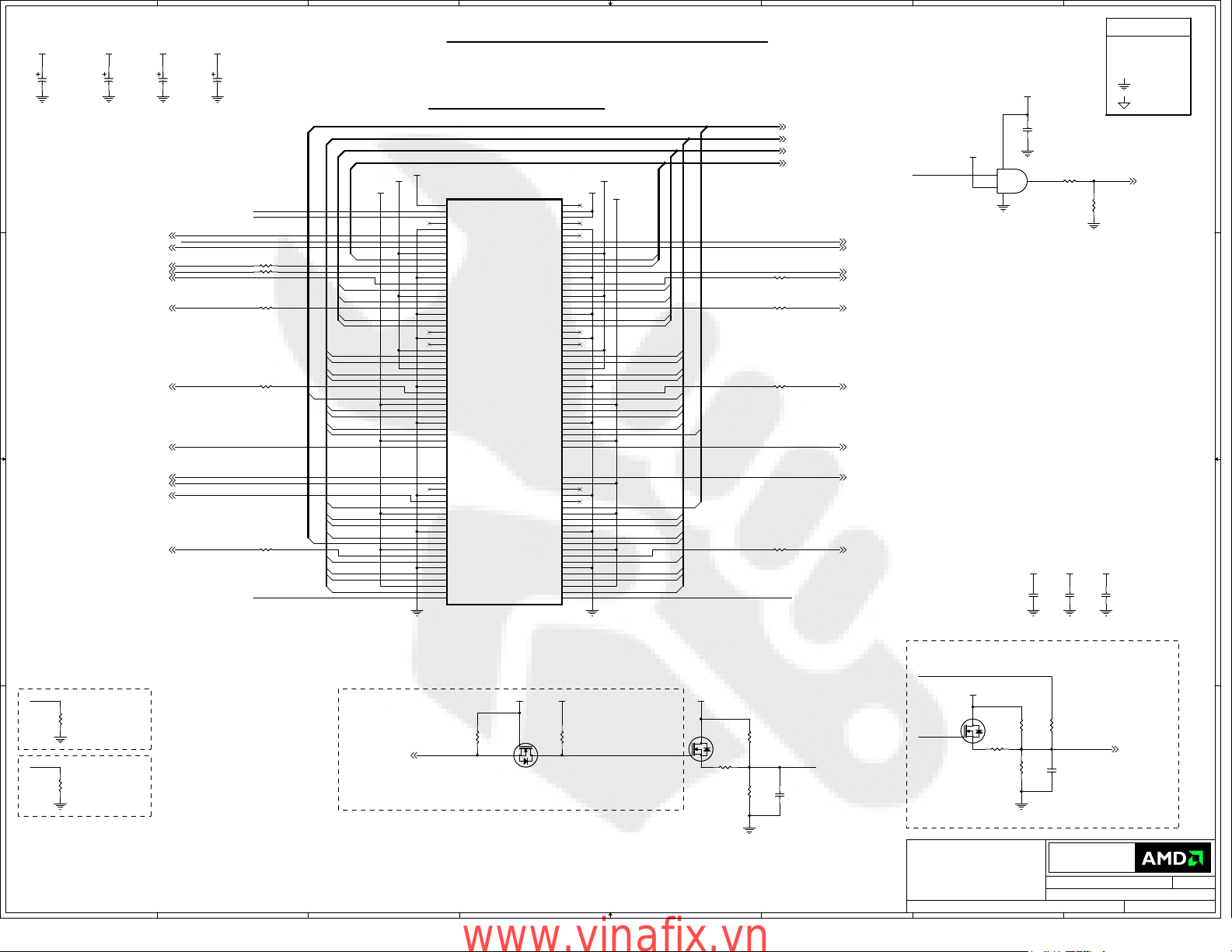

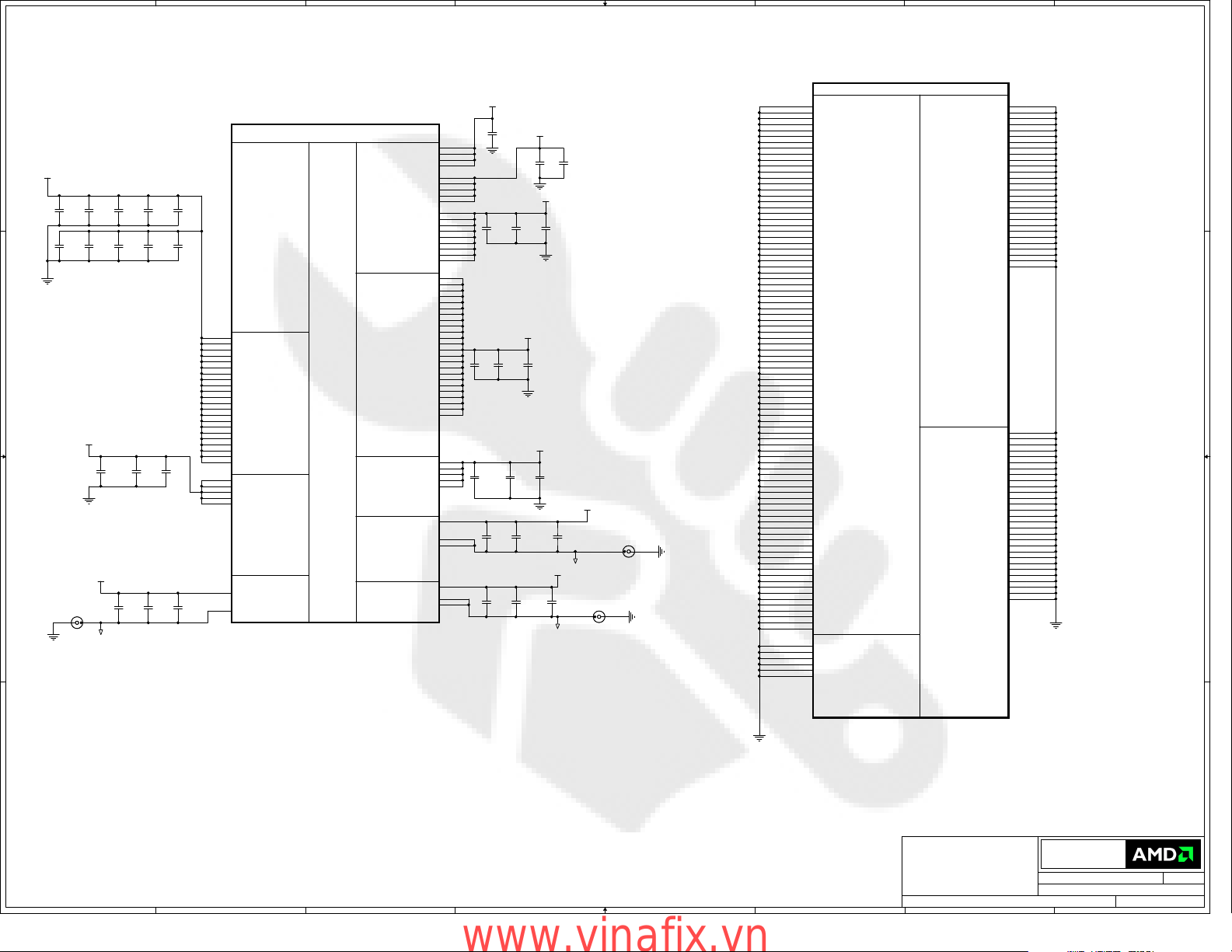

MEMORY CHANNEL A

DDR2 4pcs 16Mx32 (256MB)

D D

Channel A

Channel B

MEMORY CHANNEL B

DDR2 4pcs 16Mx32 (256MB)

TMDS1

Oscillator

Shunt Resistors

Shunt Resistors

XTALIN/OUT

RBG Filters

TVO Filters

RBG Filters

HPD1

Slim-VGA

Connector

TVO

Connector

HPD2

DVI-I

Slim-VGA

Connector

&HDMI

&

DL TMDS1

POWER REGULATORS

From +12V_EXT

+VDDC (MPVDD, VDDCI,

B_VDDC, B_PCIE)

FAN

C C

B B

From +5V_BUS:

+MPVDD

From +MVDD Linear (1.1V):

PCIE_VDDC, DPLL_VDDC

From +3.3V_BUS:

Direct or Linear (1.8V)

VDD_CT, DPLL_PVDD,

TPVDD, T2PVDD,

TXVDDR,

T2XVDDR(LTVDD18),

T2XVDDC(LTVDD33),

AVDD, A2VDD, VDD1DI,

VDD2DI,

PCIE_VDDR, PCIE_PLL,

VDDR3, VDDR4, VDDR5,

+B_VDDC_CT

+3.3V

+5V_BUS

3.3V_BUS

delayed circuit

+12V_BUS

FAN

POWER DELIVERY

Straps

BIOS

Speed control

& temperature

sense

Built-in PWM

INTERRUPT

Temp. Sensing

Dynamic VDDC

GPIO

ROM

Thermal

DDC3

GPIO17

D+/D-

TS_FDO

GPIO15

RV630

CTFb

HPD1

DAC2

CRT2

H/V2Sync

DDC2

XTALIN/OUT

GENERICA

TMDS2

DL TMDS2

HPD2

(GPIO14)

DAC1

CRT1

H/VSync

DDC1

TVO

XTAL

STV/HDTV#_OUT_DET

PCI-Express

SMPS Enable

Circuit

SEFADU HDMI: RH AGP RV630

256MB/512MB DDR2

+3.3V_BUS

+5V_BUS

+12V_BUS

RIALTO

DVI-I ,TVO,HDMI FH

REV 0

AGP 8X/4X

A A

AGP CONNECTOR

5

4

3

2

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV630 DDR2-BLOCK DIAGRAM

RV630 DDR2-BLOCK DIAGRAM

RV630 DDR2-BLOCK DIAGRAM

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

123

of

123

of

123

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

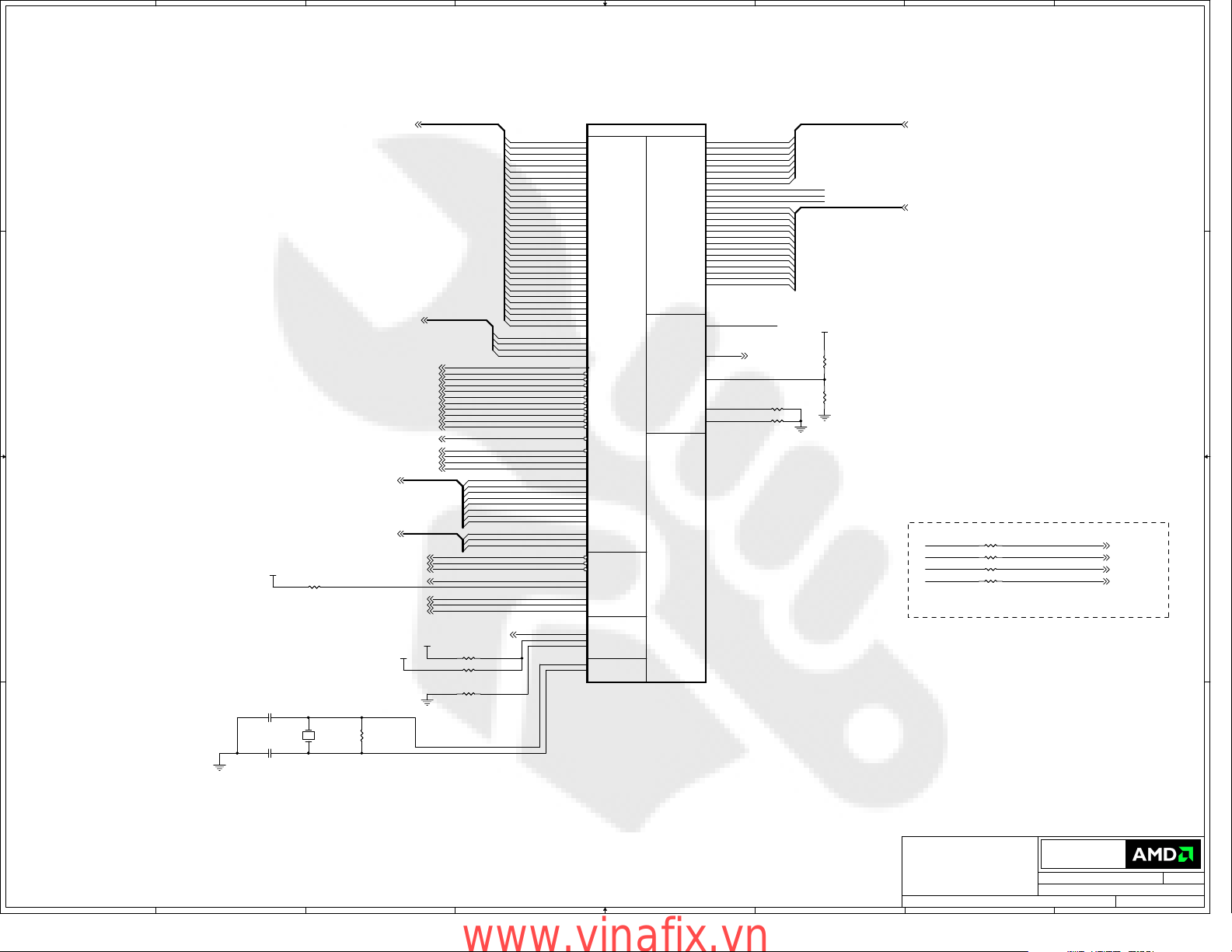

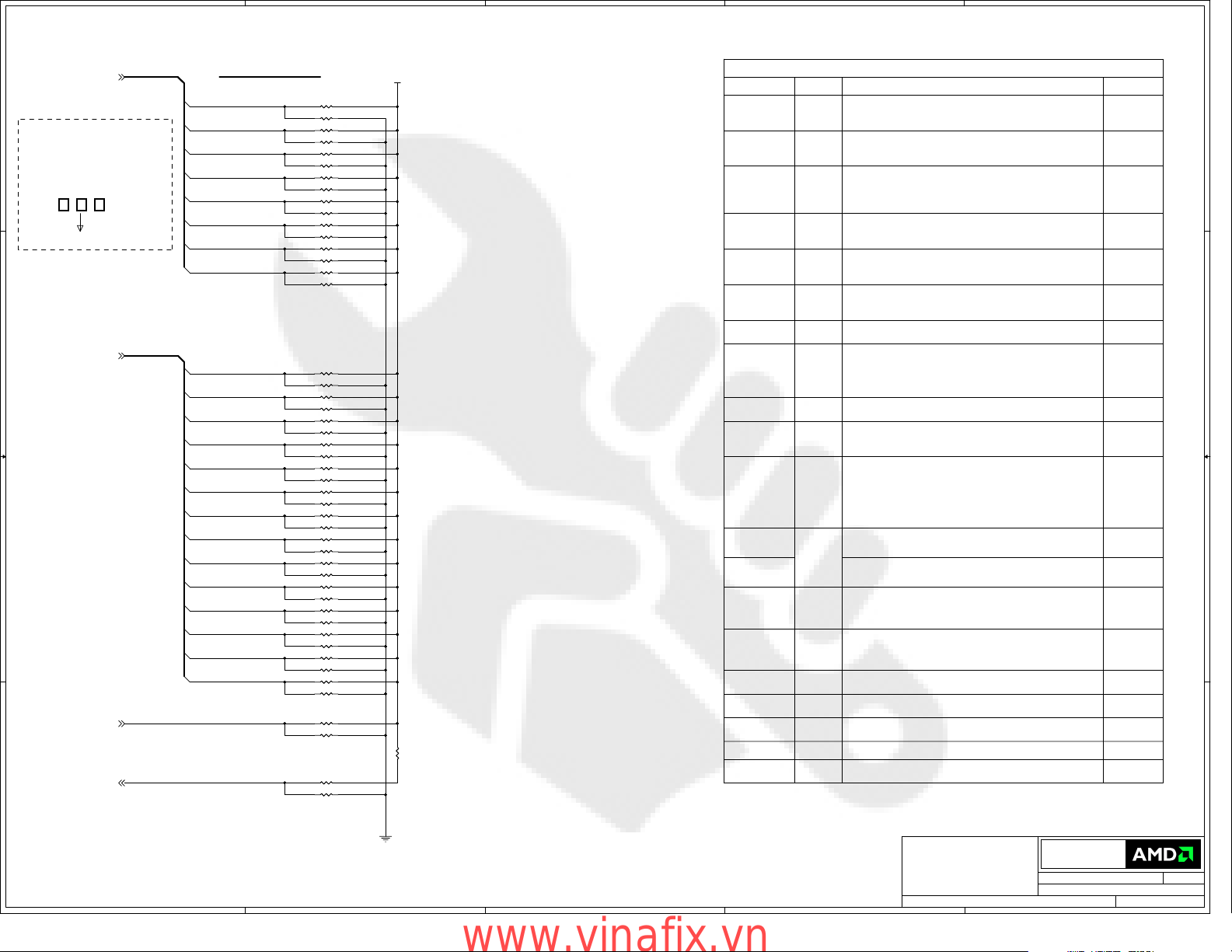

8

LAYOUT NOTE: SOME OF THE CAPS BELOW MAY BE

REMOVED IF SPACE IS AN ISSUE, ASK BEFORE REMOVING

+12V_BUS

C1509

C1509

10uF_20V

10uF_20V

D D

C C

+5V_BUS +3.3V_BUS

C1506

C1506

47uF_6.3V

47uF_6.3V

AGP_INTR#(3)

AGP_GNT#(3)

AGP_MB_8X_DET#(3)

AGP_DBI_HI(3)

AGP_WBF#(3)

AGP_SBSTB#(3)

AGP_ADSTB1#(3)

AGP_FRAME#(3)

C1501

C1501

47uF_6.3V

47uF_6.3V

+VDDQ_BUS

C1508

C1508

100uF_6.3V

100uF_6.3V

AGP_CON_RESET#

7

Use 47uF Tant. 16V 20% D size (P/N 4230047600),

800mR Max. ESR and Max. ripple 430mA @ 100kHz

or

100uF, Alum. 6.3V 20% 6.3mm dia (P/N 4261010700),

440mR Max. ESR and Max. ripple 230mA @ 100kHz

or

47uF, Alum. 6.3V 20% 5mm dia (P/N 4262047600),

760mR Max. ESR and Max. ripple 150mA @ 100kHz

Place C2 on left side of AGP connector

+VDDQ_BUS

AGP_TYPEDET#

AGP_GC_8X_DET#

AGP_ST1

R1509 0RR1509 0R

R1511 0RR1511 0R

R1504 0RR1504 0R

R1501 0RR1501 0R

AGP_MB_8X_DET#_R

AGP_DBI_HI_R

AGP_SBA1

AGP_SBA3

AGP_SBA5

AGP_SBA7

AGP_AD30

AGP_AD28

AGP_AD26

AGP_AD24

AGP_C/BE#3

AGP_AD22

AGP_AD20

AGP_AD18

AGP_AD16

6

+3.3V_BUS

AGP EDGE CONNECTOR

4X/8X AGP BUS

+12V_BUS

MAGP1

MAGP1

A1

12V

A2

TYPEDET#

A3

GC_DET#/RESERVED

A4

USB-

A5

GND

A6

INTA#

A7

RST#

A8

GNT#

A9

VCC3.3

A10

ST1

A11

MB_DET#/RESERVED

A12

DBI_HI/PIPE#

A13

GND#A13

A14

WBF#

A15

SBA1

A16

VCC3.3#A16

A17

SBA3

A18

SB_STB#

A19

GND#A19

A20

SBA5

A21

SBA7

A22

RESERVED

A23

GND#A23

A24

RESERVED#A24

A25

VCC3.3#A25

A26

AD30

A27

AD28

A28

VCC3.3#A28

A29

AD26

A30

AD24

A31

GND#A31

A32

AD_STB1#

A33

C/BE3#

A34

VDDQ1.5

A35

AD22

A36

AD20

A37

GND#A37

A38

AD18

A39

AD16

A40

VDDQ1.5#A40

A41

FRAME#

5

OVRCNT#

5.0V#B3

USB+

GND#B5

INTB#

REQ#

VCC3.3#B9

RBF#

GND#B13

DBI_LO/RESERVED

SBA0

VCC3.3#B16

SBA2

SB_STB

GND#B19

SBA4

SBA6

RESERVED#B22

GND#B23

3.3VAUX

VCC3.3#B25

AD31

AD29

VCC3.3#B28

AD27

AD25

GND#B31

AD_STB1

AD23

VDDQ1.5#B34

AD21

AD19

GND#B37

AD17

C/BE2#

VDDQ1.5#B40

IRDY#

4

AGP_C/BE#[3..0]

AGP_AD[31..0]

AGP_SBA[7..0]

AGP_ST[2..0]

+3.3V_BUS

+5V_BUS

+VDDQ_BUS

B1

B2

5.0V

B3

B4

B5

B6

B7

CLK

B8

B9

B10

ST0

B11

ST2

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

AGP_ST0

AGP_ST2

AGP_SBA0

AGP_SBA2

AGP_SBA4

AGP_SBA6

AGP_AD31

AGP_AD29

AGP_AD27

AGP_AD25

AGP_AD23

AGP_AD21

AGP_AD19

AGP_AD17

AGP_C/BE#2

AGP_DBI_LO_R

AGP_SBSTB_R

AGP_ADSTB1_R

R1500 0RR1500 0R

R1510 0RR1510 0R

R1516 0RR1516 0R

AGP_C/BE#[3..0] (3)

AGP_AD[31..0] (3)

AGP_SBA[7..0] (3)

AGP_ST[2..0] (3)

3

AGP_AGPCLK (3)

AGP_REQ# (3)

AGP_RBF# (3)

AGP_DBI_LO (3)

AGP_SBSTB (3)

AGP_ADSTB1 (3)

AGP_IRDY# (3)

AGP_CON_RESET#

+5V_BUS

2

+5V_BUS

C1500

C1500

100nF

100nF

53

U1501

U1501

1

2

R1519 100RR1519 100R

4

NC7SZ08P5X_NL

NC7SZ08P5X_NL

R1520

R1520

180R

180R

1

SYMBOL LEGEND

DO NOT

DNI

INSTALL

#

ACTIVE

LOW

DIGITAL

GROUND

ANALOG

GROUND

AGP_RESET# (3)

AGP_TRDY#(3)

AGP_STOP#(3)

AGP_PAR(3)

AGP_ADSTB0#(3)

B B

R1508 0RR1508 0R

AGP_VREFGC

AGP_PAR_R

AGP_AD15

AGP_AD13

AGP_AD11

AGP_AD9

AGP_C/BE#0

AGP_AD6

AGP_AD4

AGP_AD2

A46

A47

A48

A49

A50

A51

A52

A53

A54

A55

A56

A57

A58

A59

A60

A61

A62

A63

A64

A65

A66

TRDY#

STOP#

PME#

GND#A49

PAR

AD15

VDDQ1.5#A52

AD13

AD11

GND#A55

AD9

C/BE0#

VDDQ1.5#A58

AD_STB0#

AD6

GND#A61

AD4

AD2

VDDQ1.5#A64

AD0

VREFGC

1.5V_AGP_BUS

1.5V_AGP_BUS

DEVSEL#

VDDQ1.5#B47

PERR#

GND#B49

SERR#

C/BE1#

VDDQ1.5#B52

AD14

AD12

GND#B55

AD10

VDDQ1.5#B58

AD_STB0

GND#B61

VDDQ1.5#B64

VREFCG

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

AD8

B58

B59

B60

AD7

B61

B62

AD5

B63

AD3

B64

B65

AD1

B66

AGP_C/BE#1

AGP_AD14

AGP_AD12

AGP_AD10

AGP_AD8

AGP_AD7

AGP_AD5

AGP_AD3

AGP_AD1AGP_AD0

AGP_ADSTB0_R

AGP_AGPREF

R1505 0RR1505 0R

AGP_DEVSEL# (3)

AGP_ADSTB0 (3)

+12V_BUS

C1505

C1505

100nF

100nF

+5V_BUS

C1507

C1507

100nF

100nF

+3.3V_BUS

C1503

C1503

100nF

100nF

Caps for EMI - install close to AGP connector

UNIVERSAL VREFCG CIRCUIT (4X, 8X)

UNIVERSAL VREFGC CIRCUIT (4X, 8X)

AGP_TYPEDET#

AGP_GC_8X_DET#

A A

R1512

R1512

5.1R

5.1R

R15180RR1518

0R

+12V, TYPEDET#

short protection

for OEM (5.1R)

8

AGP_MB_8X_DET#(3)

7

AGP_MB_8X_DET#

6

R1517

R1517

47K

47K

+3.3V_BUS

1

Q1500

Q1500

5

32

BSN20

BSN20

+12V_BUS

R1503

R1503

20K

20K

TEST

+VDDQ_BUS

1

4

32

Q1501

Q1501

R1514

R1514

324R

324R

402

2N7002E

2N7002E

R1515

R1515

147R

147R

R1513

R1513

100R

100R

AGP_VREFGC

C1502

C1502

10nF

10nF

3

AGP_AGPREF

+VDDQ_BUS

32

TEST

1

Q1502

Q1502

2N7002E

2N7002E

R1502

R1502

147R

147R

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

2

RIALTO

RIALTO

R1506

R1506

R1521

R1521

0R

324R

324R

0R

AGP_AGPREFCG

R1507

R1507

C1504

C1504

100R

100R

10nF

10nF

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

223

223

223

of

of

of

AGP_AGPREFCG (3)

Doc No.

Doc No.

Doc No.

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

1

RevDate:

RevDate:

RevDate:

0

0

0

www.vinafix.vn

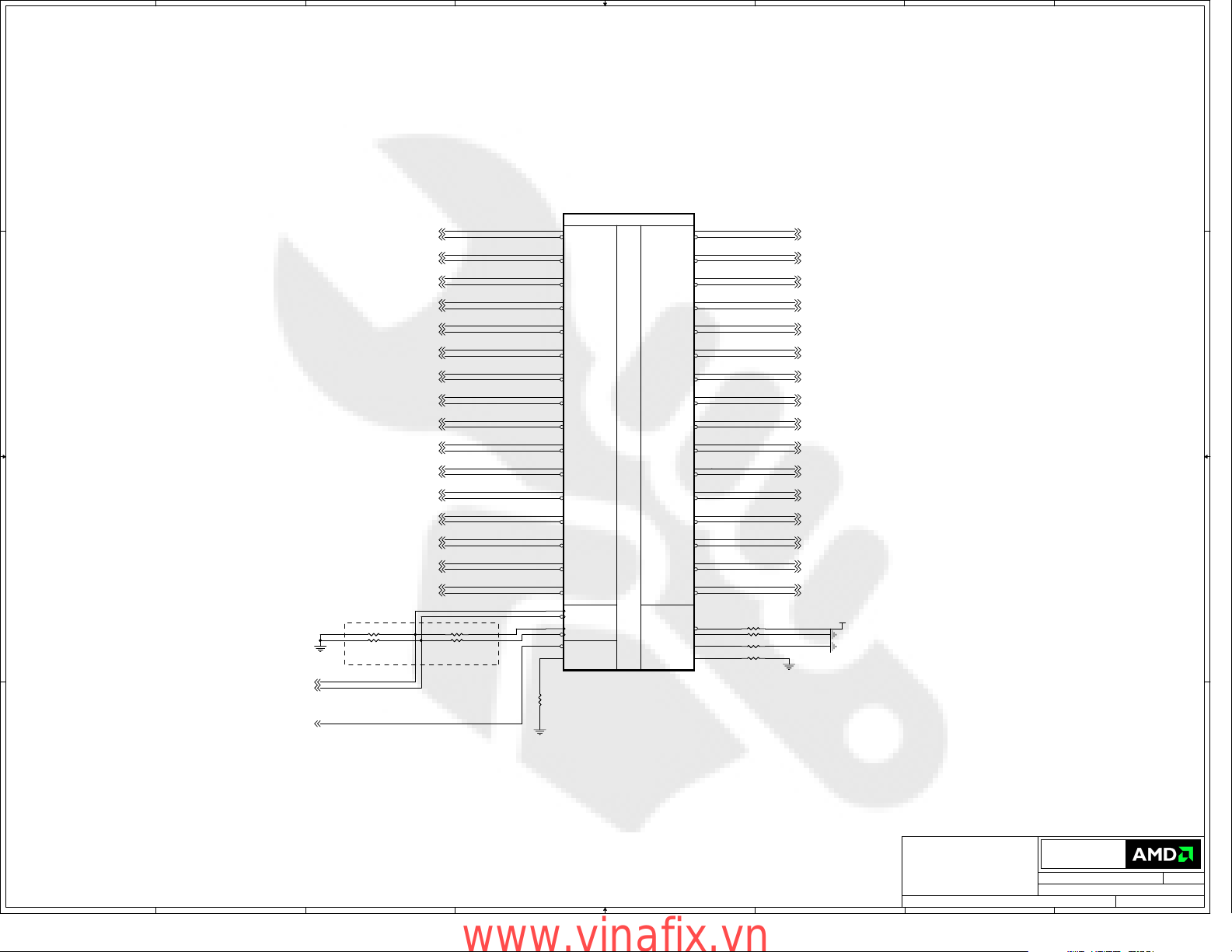

8

7

6

5

4

3

2

1

D D

C C

B B

+VDDQ_BUS

R1529 47RR1529 47R

C1511

C1511

18pF_50V

18pF_50V

C1510

C1510

18pF_50V

18pF_50V

2 1

Y1500

Y1500

25.000MHz

25.000MHz

AGP_AD[31..0](2)

AGP_C/BE#[3..0](2)

AGP_SBA[7..0](2)

AGP_ST[2..0](2)

AGP_ADSTB0#(2)

AGP_ADSTB1#(2)

AGP_AGPREFCG(2)

AGP_MB_8X_DET#(2)

R15321MR1532

1M

AGP_SBSTB#(2)

AGP_DBI_LO(2)

AGP_DBI_HI(2)

+3.3V

AGP_ADSTB0(2)

AGP_ADSTB1(2)

AGP_AGPCLK(2)

AGP_RESET#(2)

AGP_STOP#(2)

AGP_DEVSEL#(2)

AGP_TRDY#(2)

AGP_IRDY#(2)

AGP_FRAME#(2)

AGP_INTR#(2)

AGP_WBF#(2)

AGP_SBSTB(2)

AGP_REQ#(2)

AGP_GNT#(2)

AGP_RBF#(2)

+VDDQ_BUS

AGP_PAR(2)

AGP_SBA[7..0]

AGP_ST[2..0]

AGP_AD[31..0]

AGP_C/BE#[3..0]

R1526 1KR1526 1K

R1593 1KRIALTOR1593 1KRIALTO

R1528 1KR1528 1K

U1500B

U1500B

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

STP_AGPB(6)

A6

A5

B6

B5

C5

C4

C3

D4

E4

F4

F3

G4

G3

H3

H4

J3

F6

F5

G6

H7

H6

J6

J7

K7

L7

M7

M6

M5

N7

N6

P7

P6

E3

J4

G7

J5

AA2

AB3

U6

V5

E7

F7

L4

L3

M3

M4

W4

R7

T6

D2

K6

R3

U4

U3

T4

T3

P4

P3

N4

N3

W3

V4

V3

R4

C2

L6

D6

E6

R5

R6

T7

AA3

AA4

Y3

AA8

AB8

Rialto A11

Rialto A11

AD_0

AD_1

AD_2

AD_3

AD_4

AD_5

AD_6

AD_7

AD_8

AD_9

AD_10

AD_11

AD_12

AD_13

AD_14

AD_15

AD_16

AD_17

AD_18

AD_19

AD_20

AD_21

AD_22

AD_23

AD_24

AD_25

AD_26

AD_27

AD_28

AD_29

AD_30

AD_31

C_BEB_0

C_BEB_1

C_BEB_2

C_BEB_3

PCICLK

RSTB

REQB

GNTB

PAR

STOPB

DEVSELB

TRDYB

IRDYB

FRAMEB

INTAB

WBFB

RBFB

AD_STBF_0

AD_STBF_1

SB_STBF

SBA_0

SBA_1

SBA_2

SBA_3

SBA_4

SBA_5

SBA_6

SBA_7

ST_0

ST_1

ST_2

SB_STBS

AD_STBS_0

AD_STBS_1

AGPVREF

AGPTEST

DBI_LO

DBI_HI

AGP8X_DETB

STP_AGPB

AGP_BUSYB

RSTB_MSK

XTO

XTI

PART 2 OF 4

PART 2 OF 4

PCI / AGPAGP2X

PCI / AGPAGP2X

4X8X

4X8X

AGP

AGP

AGP

Additional

AGP

Additional

CLK

CLK

GPIOMISC

GPIOMISC

NC

NC

GPIO_0

GPIO_1

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

GPIO_24

ROMCSB

REFCLKBYP

VrefG1

PLLTEST

TESTEN

Y9

AB10

AA10

Y10

AA11

Y12

AA12

AB12

W18

Y20

AB20

AA13

AB13

AA14

AB14

AA15

AB15

AA16

AB16

AA17

AB17

AA18

AB18

Y18

AA19

Y19

W20

AB4

W6

Y4

B_GPIO0

B_GPIO1

B_GPIO2

B_GPIO3

B_GPIO4

B_GPIO5

B_GPIO6

B_GPIO7

B_GPIO11

B_GPIO12

B_GPIO13

B_GPIO14

B_GPIO15

B_GPIO16

B_GPIO17

B_GPIO18

B_GPIO19

B_GPIO20

B_GPIO21

B_GPIO22

B_GPIO23

B_GPIO24

B_ROMCS#

REFCLKBYP (6)

R1527 1KR1527 1K

R1533 1KR1533 1K

B_GPIO8

B_GPIO9

B_GPIO10

+3.3V

R1531

R1531

499R

499R

R1530

R1530

499R

499R

B_GPIO[7..0]

B_GPIO[24..11]

B_GPIO[7..0] (6)

B_GPIO[24..11] (6)

B_GPIO8

B_GPIO9

B_GPIO10

B_ROMCS#

R1523 33RR1523 33R

R1522 33RR1522 33R

R1524 33RR1524 33R

R1525 33RR1525 33R

TO SERIAL EEPROM 512K/1M

ROM_SO (12)

SI/A16 (12)

SCK/WEb (12)

CSb (12)

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

8

7

6

5

4

3

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

323

of

323

of

323

Doc No.

Doc No.

Doc No.

1

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

8

D D

7

6

5

4

3

2

1

Rialto ASIC p/n is: 218BAPAGA11F

U1500A

U1500A

W16

W11

W19

R1541

R1541

4.7K

4.7K

U13

T13

T14

R14

R12

P12

P13

N13

N14

M14

M12

L12

L13

K13

K14

J14

J12

H12

H13

G13

G14

F14

F12

E12

E13

D13

D14

C14

C12

B12

B13

A13

V16

Y11

R20

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

PCIE_REFCLKP

PCIE_REFCLKN

RefCLKP

RefCLKN

PERSTB

PCIETEST

Rialto A11

Rialto A11

PETp0_GFXRp0(7)

PETn0_GFXRn0(7)

PETp1_GFXRp1(7)

PETn1_GFXRn1(7)

PETp2_GFXRp2(7)

PETn2_GFXRn2(7)

PETp3_GFXRp3(7)

PETn3_GFXRn3(7)

PETp4_GFXRp4(7)

R1538 49.9RR1538 49.9R

1%

R1540 49.9RR1540 49.9R

1%

PETn4_GFXRn4(7)

PETp5_GFXRp5(7)

PETn5_GFXRn5(7)

PETp6_GFXRp6(7)

PETn6_GFXRn6(7)

PETp7_GFXRp7(7)

PETn7_GFXRn7(7)

PETp8_GFXRp8(7)

PETn8_GFXRn8(7)

PETp9_GFXRp9(7)

PETn9_GFXRn9(7)

PETp10_GFXRp10(7)

PETn10_GFXRn10(7)

PETp11_GFXRp11(7)

PETn11_GFXRn11(7)

PETp12_GFXRp12(7)

PETn12_GFXRn12(7)

PETp13_GFXRp13(7)

PETn13_GFXRn13(7)

PETp14_GFXRp14(7)

PETn14_GFXRn14(7)

PETp15_GFXRp15(7)

PETn15_GFXRn15(7)

R1539 33.2RR1539 33.2R

1%

R1534 33.2RR1534 33.2R

1%

Place the reisitors

close to ASIC

C C

B B

PCIE_REFCLKP(7)

PCIE_REFCLKN(7)

PERST#(7)

PART 1 OF 4

PART 1 OF 4

PCIE TX

PCIE TX

Clock

Clock

V17

PCIE_RX0P

U17

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE RX

PCIE RX

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

R_EXT

U19

T19

T16

R16

R17

P17

P19

N19

N16

M16

M17

L17

L19

K19

K16

J16

J17

H17

H19

G19

G16

F16

F17

E17

E19

D19

D16

C16

C17

B17

AA21

Y21

W21

Y8

1%

R1536 100RR1536 100R

R1535 150RR1535 150R

1%

R1537 10KR1537 10K

1%

R1542 750RR1542 750R

1%

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

GFXTp0_PERp0 (7)

GFXTn0_PERn0 (7)

GFXTp1_PERp1 (7)

GFXTn1_PERn1 (7)

GFXTp2_PERp2 (7)

GFXTn2_PERn2 (7)

GFXTp3_PERp3 (7)

GFXTn3_PERn3 (7)

GFXTp4_PERp4 (7)

GFXTn4_PERn4 (7)

GFXTp5_PERp5 (7)

GFXTn5_PERn5 (7)

GFXTp6_PERp6 (7)

GFXTn6_PERn6 (7)

GFXTp7_PERp7 (7)

GFXTn7_PERn7 (7)

GFXTp8_PERp8 (7)

GFXTn8_PERn8 (7)

GFXTp9_PERp9 (7)

GFXTn9_PERn9 (7)

GFXTp10_PERp10 (7)

GFXTn10_PERn10 (7)

GFXTp11_PERp11 (7)

GFXTn11_PERn11 (7)

GFXTp12_PERp12 (7)

GFXTn12_PERn12 (7)

GFXTp13_PERp13 (7)

GFXTn13_PERn13 (7)

GFXTp14_PERp14 (7)

GFXTn14_PERn14 (7)

GFXTp15_PERp15 (7)

GFXTn15_PERn15 (7)

+B_PCIE

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

8

7

6

5

4

3

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

423

of

423

of

423

Doc No.

Doc No.

Doc No.

1

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

8

D D

CONNECT +VDDC TO +B_VDDC

+VDDC

C1545

C1545

C1535

C1536

C1536

10nF

10nF

C1539

C1539

1uF_6.3V

1uF_6.3V

+3.3V

+B_PVDD

GND_B_PVSS

C1523

C1523

1uF_6.3V

1uF_6.3V

C1535

10nF

10nF

C1544

C1544

1uF_6.3V

1uF_6.3V

C1515

C1515

1uF

1uF

C1524

C1524

1uF_6.3V

1uF_6.3V

10nF

10nF

C1541

C1541

10uF_X6S

10uF_X6S

C1558

C1558

100nF

100nF

C1526

C1526

10nF

10nF

C1537

C1537

10nF

10nF

C1540

C1540

1uF_6.3V

1uF_6.3V

C C

B B

NS1 NS_VIANS1 NS_VIA

1 2

C1542

C1542

10nF

10nF

C1549

C1549

10uF_X6S

10uF_X6S

C1557

C1557

10uF_X6S

10uF_X6S

7

U1500C

U1500C

C11

VDDC_1

F9

VDDC_2

K11

VDDC_3

B11

VDDC_4

K9

VDDC_5

F11

VDDC_6

G10

VDDC_7

G11

VDDC_8

P11

VDDC_9

P10

VDDC_10

L9

VDDC_11

L11

VDDC_12

B9

VDDC_13

F10

VDDC_14

G9

VDDC_15

L10

VDDC_16

P9

VDDC_17

C9

VDDC_18

B10

VDDC_19

C10

VDDC_20

K10

VDDC_21

AB9

VDDCI

U9

VDDR3_1

W8

VDDR3_2

U10

VDDR3_3

V9

VDDR3_4

W9

VDDR3_5

AB5

PVDD

AA5

PVSS

Rialto A11

Rialto A11

PLL

PLL

NC

NC

Core

Core

GPIO

GPIO

AGP

AGP

PART 3 OF 4

PART 3 OF 4

P

P

O

O

W

W

E

E

R

R

6

PCIE_PVDD_12_1

PCIE_PVDD_12_2

PCIE_PVDD_12_3

PCIE_PVDD_12_4

PCIE_VDDR_18_2

PCIE_VDDR_18_3

PCIE_VDDR_18_4

PCIE_VDDR_18_1

PCIE_VDDR_12_1

PCIE_VDDR_12_2

PCIE_VDDR_12_3

PCIE_VDDR_12_4

PCIE_VDDR_12_5

PCI-Express

PCI-Express

PCIE_VDDR_12_6

PCIE_VDDR_12_7

PCIE_VDDR_12_8

PCIE_VDDR_12_9

AGPDIFF

AGPDIFF

Volt COV

Volt COV

OSC

OSC

I/O

I/O

PCIE_PVDD_18

VDDP_1

VDDP_2

VDDP_3

VDDP_4

VDDP_5

VDDP_6

VDDP_7

VDDP_8

VDDP_9

VDDP_10

VDDP_11

VDDP_12

VDDP_13

VDDP_14

VDDP_15

VDDP_16

VDDP_17

VDDP_18

VDDP_19

VDDP_20

VDDP_21

VDDP_22

VDDP_23

VDDP_24

VDD15_1

VDD15_2

VDD15_3

VDD15_4

VDD15_5

VAA_DIO

AGND_DIO_1

AGND_DIO_2

VAA_XTL

AGND_XTL_1

AGND_XTL_2

5

+B_PCIE

+B_PCIE_PVDD_18

C1514

C1514

1uF_6.3V

C1552

C1552

10nF

10nF

C1554

C1554

10nF

10nF

C1520

C1520

10nF

10nF

C1530

C1530

100nF

100nF

C1532

C1532

100nF

100nF

1uF_6.3V

C1553

C1553

10nF

10nF

C1521

C1521

10nF

10nF

+VDDQ_BUS

+B_VDDC_CT

C1556

C1556

10nF

10nF

C1529

C1529

10uF_X6S

10uF_X6S

C1531

C1531

10uF_X6S

10uF_X6S

+B_PCIE

C1560

C1560

1uF_6.3V

1uF_6.3V

GND_XTL

C1512

C1512

10nF

10nF

C1522

C1522

1uF_6.3V

1uF_6.3V

C1555

C1555

1uF_6.3V

1uF_6.3V

+VAA_XTL

C1516

C1516

1uF

1uF

GND_DIO

C1518

C1518

1uF

1uF

C1513

C1513

1uF_6.3V

1uF_6.3V

+VAA_DIO

NS2NS_VIA NS2NS_VIA

NS3NS_VIA NS3NS_VIA

12

F21

A21

B21

E21

A15

A16

A17

A18

A19

W13

Y13

Y14

W12

W14

Y16

W15

Y15

Y17

A4

E2

G2

L2

U2

W2

AB2

G5

K4

B4

T5

W5

B2

N2

E5

D8

E8

C8

H8

J8

M8

N8

R8

A2

B8

U8

A8

T9

V8

AB6

AA6

Y6

AB7

AA7

Y7

4

12

T17

L21

W17

C21

B19

C19

D18

E18

G18

H18

K18

L18

M19

N18

P18

M18

R19

T18

L16

H16

E16

B16

T15

P16

F15

L15

G17

K17

F18

U18

U12

V15

B18

B15

C15

D15

E15

G15

H15

J15

K15

M15

N15

P15

R15

U15

V18

V14

R18

A14

C13

P14

L14

F13

B14

J13

E14

M13

V12

U16

H14

U14

V13

J21

R13

A20

G21

A12

K21

B20

C20

D20

E20

F20

G20

H20

L20

T20

F19

J19

C18

J18

D17

N17

D12

G12

N12

T12

K12

V10

V11

W7

T11

U11

W10

3

U1500D

U1500D

PCIE_VSS_1

PCIE_VSS_2

PCIE_VSS_3

PCIE_VSS_4

PCIE_VSS_5

PCIE_VSS_6

PCIE_VSS_7

PCIE_VSS_8

PCIE_VSS_9

PCIE_VSS_10

PCIE_VSS_11

PCIE_VSS_12

PCIE_VSS_13

PCIE_VSS_14

PCIE_VSS_15

PCIE_VSS_16

PCIE_VSS_17

PCIE_VSS_18

PCIE_VSS_19

PCIE_VSS_20

PCIE_VSS_21

PCIE_VSS_22

PCIE_VSS_23

PCIE_VSS_24

PCIE_VSS_25

PCIE_VSS_26

PCIE_VSS_27

PCIE_VSS_28

PCIE_VSS_29

PCIE_VSS_30

PCIE_VSS_31

PCIE_VSS_32

PCIE_VSS_33

PCIE_VSS_34

PCIE_VSS_35

PCIE_VSS_36

PCIE_VSS_37

PCIE_VSS_38

PCIE_VSS_39

PCIE_VSS_40

PCIE_VSS_41

PCIE_VSS_42

PCIE_VSS_43

PCIE_VSS_44

PCIE_VSS_45

PCIE_VSS_46

PCIE_VSS_47

PCIE_VSS_48

PCIE_VSS_49

PCIE_VSS_50

PCIE_VSS_51

PCIE_VSS_52

PCIE_VSS_53

PCIE_VSS_54

PCIE_VSS_55

PCIE_VSS_56

PCIE_VSS_57

PCIE_VSS_58

PCIE_VSS_59

PCIE_VSS_60

PCIE_VSS_61

PCIE_VSS_62

PCIE_VSS_63

PCIE_VSS_64

PCIE_VSS_65

PCIE_VSS_66

PCIE_VSS_67

PCIE_VSS_68

PCIE_VSS_69

PCIE_VSS_70

PCIE_VSS_71

PCIE_VSS_72

PCIE_VSS_73

PCIE_VSS_74

PCIE_VSS_75

PCIE_VSS_76

PCIE_VSS_77

PCIE_VSS_78

PCIE_VSS_79

PCIE_VSS_80

PCIE_VSS_81

PCIE_VSS_82

PCIE_VSS_83

PCIE_VSS_84

PCIE_VSS_85

PCIE_VSS_86

PCIE_VSS_87

PCIE_VSS_88

PCIE_VSS_89

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

Part 4 of 4

Part 4 of 4

PCI-Express GND

PCI-Express GND

GPIO GND

GPIO GND

CORE GND

CORE GND

AGP GND

AGP GND

2

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSSP_1

VSSP_2

VSSP_3

VSSP_4

VSSP_5

VSSP_6

VSSP_7

VSSP_8

VSSP_9

VSSP_10

VSSP_11

VSSP_12

VSSP_13

VSSP_14

VSSP_15

VSSP_16

VSSP_17

VSSP_18

VSSP_19

VSSP_20

VSSP_21

VSSP_22

VSSP_23

VSSP_24

VSSP_25

VSSP_26

VSSP_27

VSSP_28

VSSP_29

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

1

M9

A10

H11

N11

T8

E10

R9

A9

E11

N10

D10

J11

D11

J9

H9

H10

M10

M11

R10

A11

N9

D9

E9

T10

J10

R11

V7

AA9

L5

D3

H2

K2

P2

T2

C6

B3

D5

H5

K3

K5

N5

U5

Y2

P5

A7

B7

D7

U7

C7

F8

G8

K8

L8

P8

A3

V6

Y5

Rialto A11

Rialto A11

A A

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

8

7

6

5

4

3

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

2

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

523

of

523

of

523

Doc No.

Doc No.

Doc No.

1

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

5

4

3

2

1

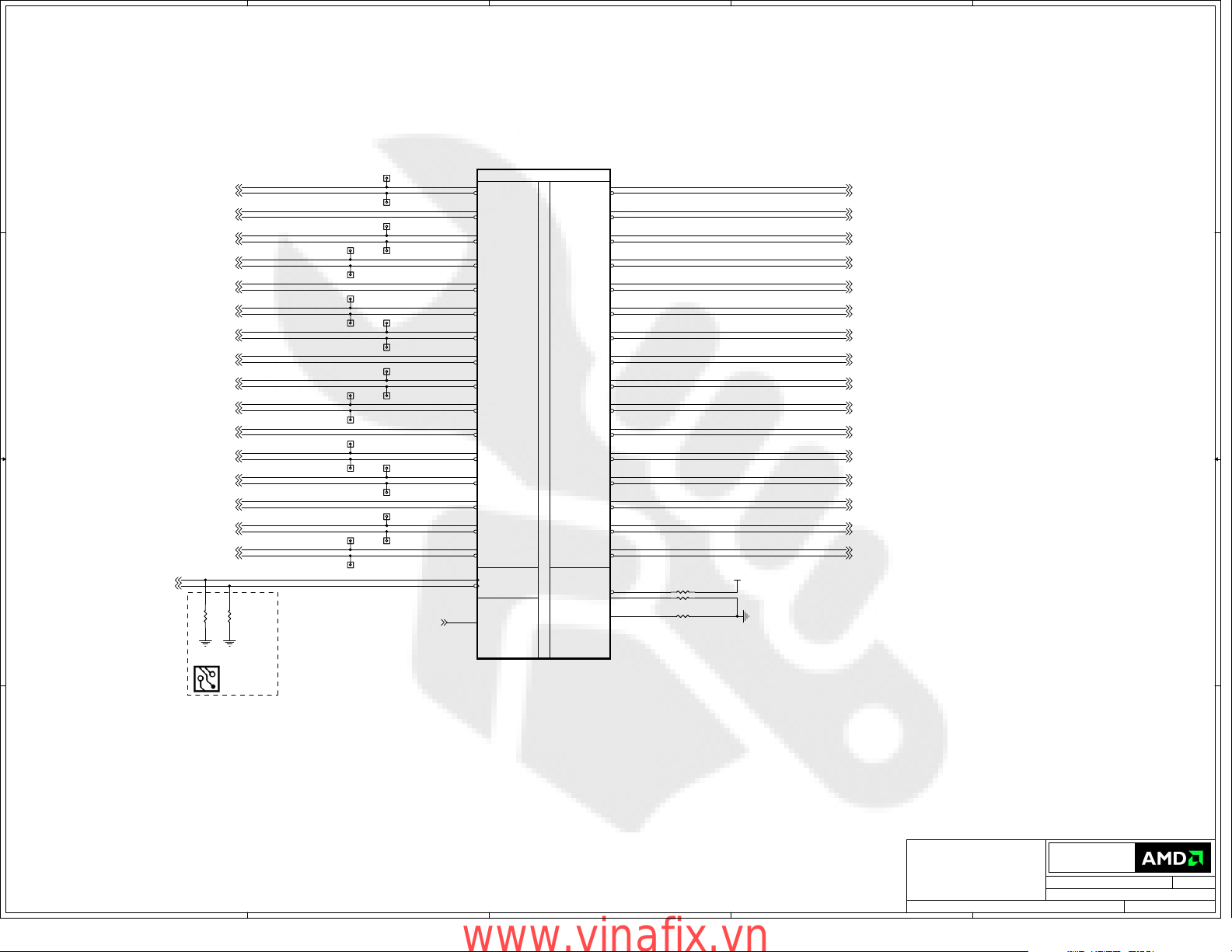

B_GPIO[7..0](3)

D D

Overlap pads to save space

B_GPIO[7..0]

and to prevent assembly of

both resistors.

Layout

High logic voltageGround

Signal

C C

B B

A A

B_GPIO[24..11](3)

REFCLKBYP(3)

B_GPIO[24..11]

STP_AGPB(3)

OPTION STRAPS

B_GPIO0

B_GPIO1

B_GPIO2

B_GPIO3

B_GPIO4

B_GPIO5

B_GPIO6

B_GPIO7

B_GPIO11

B_GPIO12

B_GPIO13

B_GPIO14

B_GPIO15

B_GPIO16

B_GPIO17

B_GPIO18

B_GPIO19

B_GPIO20

B_GPIO21

B_GPIO22

B_GPIO23

B_GPIO24

REFCLKBYP

STP_AGPB

R1543 10KR1543 10K

R1544 10KDNIR1544 10KDNI

R1545 10KR1545 10K

R1546 10KDNIR1546 10KDNI

R1547 10KR1547 10K

R1548 10KDNIR1548 10KDNI

R1549 10KDNIR1549 10KDNI

R1550 10KR1550 10K

R1551 10KDNIR1551 10KDNI

R1552 10KR1552 10K

R1553 10KDNIR1553 10KDNI

R1554 10KR1554 10K

R1555 10KDNIR1555 10KDNI

R1556 10KR1556 10K

R1557 10KDNIR1557 10KDNI

R1558 10KR1558 10K

R1559 10KDNIR1559 10KDNI

R1560 10KR1560 10K

R1561 10KR1561 10K

R1562 10KDNIR1562 10KDNI

R1563 10KDNIR1563 10KDNI

R1564 10KR1564 10K

R1565 10KDNIR1565 10KDNI

R1566 10KR1566 10K

R1567 10KDNIR1567 10KDNI

R1568 10KR1568 10K

R1569 10KDNIR1569 10KDNI

R1570 10KR1570 10K

R1571 10KDNIR1571 10KDNI

R1572 10KR1572 10K

R1573 10KDNIR1573 10KDNI

R1574 10KR1574 10K

R1575 10K

R1575 10K

R1576 10KR1576 10K

DNI

DNI

R1577 10KDNIR1577 10KDNI

R1578 10KR1578 10K

R1579 10KDNIR1579 10KDNI

R1580 10KR1580 10K

R1581 10KDNIR1581 10KDNI

R1582 10KR1582 10K

R1583 10KDNIR1583 10KDNI

R1584 10KR1584 10K

R1585 10KDNIR1585 10KDNI

R1586 10KR1586 10K

R1587 10KDNIR1587 10KDNI

R1588 10KR1588 10K

R1589 10KR1589 10K

R1590 10KDNIR1590 10KDNI

+3.3V

R15910RR1591

0R

PCIE_AGP_Bridge Shared Straps

STRAPS

GPIO(0)PCIE_PTX_PWRS_ENB

PCIE_PTX_DEEMPH_EN PCI Express transmitter de-emphasis enable

PCIE_ICP (1:0)

PCIE_PTX_IEXT GPIO(4)0PCI Express transmitter extra ouptput current

DEBUG_ACCESS 1 - Set the debug bus muxes to bring out debug signals even if registers are inaccessable

PCIE_PPLL_BW GPIO(6) PCI Express PLL bandwidth setting

PCIE_REVERSE_ALL GPIO(7)00 - Don't reverse physical PCIE lanes

PCI_RETRY_ENb

MULTIFUNC

PCIE_FORCE_

COMPLIANCE

PCIE_LINK_TIMEOUT

_OVERRIDE

MOBILE_EN REFCLKBYP

BUS_PCI_CFG_

RETRY_Enb

GPIO(1)

GPIO(3:2)

GPIO(5)

GPIO(13)

GPIO(24, 14)VGA_MONO_MODE(1:0)

GPIO(15)REFCLK_LINK_CONFIG One of the strap bit to encode the combination of:

GPIO(16)

GPIO(18:17)AGPFBSKEW(1:0)

GPIO(20:19)X1CLK_SKEW(1:0)

GPIO(21)BUSCFG Control BUS type, CLK PLL select

GPIO(22)AGP_ONLY

GPIO(23)

STP_AGPB

DESCRIPTIONPIN

PCI Express transmitter power-saving enable bar

0 - 50% Tx output swing for mobile applications

1 - Full output swing

0 - de-emphasis disenable

1 - de-emphasis enable

Charge pump current setting

00 - 5.0uA

01 - 10.0uA

10 - 15.0uA

11 - 20.0uA

0 - no extra current

1 - extra current in output stage

0 - Full PLL bandwidth

1 - Reduces PLL bandwidth

1 - Reverse physical PCIE lanes

If no ROM attached, comtrols chip IDis. If rom attached identifies ROM type

00 - No ROM, CHG_ID=0

01 - 512Kb Serial AT25F512 ROM (Atmel) or AT24F1024 ROM (Atmel)

10 - 512K Serial M25P05A ROM (ST) or PM25LV512 (PMC)

11 - 1M Serial M25P10A ROM (ST) or PM25LV010 (PMC)

0 - Enable all PCI read/write retry, retry cycle 0x3

1 - Disable PCI read/write retry

00 - only VGA controller

01 - only MONO controller

10 - neither VGA/MONO controller

11 - both VGA/MONO controller

SEND_LINK_TRAINING_IMMEDIATELY

MOBILE_EN

AGP_ONLY

....

etc,

For MULTIFUNC, when TESTEN(pin)=0,

0 = 00 - Single function device

1 = 01 - Two function device. No AGP in either function

For PCIE_FORCE_COMPLIANCE, when TESTEN(pin)=1,

0 - Normal operation

1 - Force LC into compliance mode

AGP 1xclock feedback phase adjustment wrt refclk(cpuclk)

00 - refclk slightly earlier than feedback

01 - refclk 1 tap later than feedback

10 - refclk 1 tap earlier than feedback

11 - refclk 2 tap earlier than feedback clock

Clock phase adjustment between x1clk and x2clk

00 - 0 tap delay

01 - 1 tap delay

10 - 2 tap delay

11 - 3 tap delay

1 - for debugging, shut off VPU so the bridge is working in AGP only mode

1 - Timeout is disabled

when internal MOBILE_EN=0 STRAP_BUS_PCI_CFG_RETRY_Enb

DEFAULT

1

1

01

0

0

10GPIO(12:11)ROMIDCFG(1:0)

0

00

0

0

0

00

internal pulldown

00

internal pulldown

0

internal pulldown

00 - normal operation, assume VPU is working

00 - Timeout is active

0

1

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

5

4

3

2

RH AGP RV560 256MB GDDR3 DUAL DL-DVI-I VIVO

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

623

of

623

of

623

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

5

D D

NOTE: some of the PCIE testpoints will

be available trought via on traces.

PETp0_GFXRp0(4)

PETn0_GFXRn0(4)

PETp1_GFXRp1(4)

PETn1_GFXRn1(4)

PETp2_GFXRp2(4)

PETn2_GFXRn2(4)

PETp3_GFXRp3(4)

PETn3_GFXRn3(4)

PETp4_GFXRp4(4)

PETn4_GFXRn4(4)

PETp5_GFXRp5(4)

PETn5_GFXRn5(4)

PETp6_GFXRp6(4)

C C

B B

PCIE_REFCLKP(4)

PCIE_REFCLKN(4)

PETn6_GFXRn6(4)

PETp7_GFXRp7(4)

PETn7_GFXRn7(4)

PETp8_GFXRp8(4)

PETp9_GFXRp9(4)

PETn9_GFXRn9(4)

PETp10_GFXRp10(4)

PETn10_GFXRn10(4)

PETp11_GFXRp11(4)

PETn11_GFXRn11(4)

PETp12_GFXRp12(4)

PETn12_GFXRn12(4)

PETp13_GFXRp13(4)

PETn13_GFXRn13(4)

PETp14_GFXRp14(4)

PETn14_GFXRn14(4)

PETp15_GFXRp15(4)

PETn15_GFXRn15(4)

R14

R14

R13

R13

51R

51R

51R

51R

DNI

DNI

DNI

DNI

TP11

TP11

35mil

35mil

TP12

TP12

35mil

35mil

TP13

TP13

35mil

35mil

TP14

TP14

35mil

35mil

TP19

TP19

35mil

35mil

TP20

TP20

35mil

35mil

TP21

TP21

35mil

35mil

TP22

TP22

35mil

35mil

TP27

TP27

35mil

35mil

TP28

TP28

35mil

35mil

4

U1A

AK33

AH35

AH34

AG35

AG34

AF33

AE33

AE35

AE34

AD35

AD34

AC35

AC34

AB33

AA33

AA35

AA34

AM32

AJ33

AJ35

AJ34

Y35

Y34

W35

W34

V33

U33

U35

U34

T35

T34

R35

R34

AJ31

AJ30

U1A

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

PCIE_RX1N

PCIE_RX2P

PCIE_RX2N

PCIE_RX3P

PCIE_RX3N

PCIE_RX4P

PCIE_RX4N

PCIE_RX5P

PCIE_RX5N

PCIE_RX6P

PCIE_RX6N

PCIE_RX7P

PCIE_RX7N

PCIE_RX8P

PCIE_RX8N

PCIE_RX9P

PCIE_RX9N

PCIE_RX10P

PCIE_RX10N

PCIE_RX11P

PCIE_RX11N

PCIE_RX12P

PCIE_RX12N

PCIE_RX13P

PCIE_RX13N

PCIE_RX14P

PCIE_RX14N

PCIE_RX15P

PCIE_RX15N

Clock

Clock

PCIE_REFCLKP

PCIE_REFCLKN

PERSTB

PART 1 OF 7

PART 1 OF 7

P

P

C

C

I

I

-

E

E

X

X

P

P

R

R

E

E

S

S

S

S

I

I

N

N

T

T

E

E

R

R

F

F

A

A

C

C

E

E

TP7

TP7

35mil

35mil

TP8

TP8

35mil

35mil

TP9

TP9

35mil

35mil

TP10

TP10

35mil

35mil

TP15

TP15

35mil

35mil

TP16

TP16

35mil

35mil

TP17

TP17

35mil

35mil

TP18

TP18

35mil

35mil

TP23

TP23

35mil

35mil

TP24

TP24

35mil

35mil

TP25

TP25

35mil

35mil

TP26

TP26

35mil

35mil

PERST#(4)

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

PCIE_TX2P

PCIE_TX2N

PCIE_TX3P

PCIE_TX3N

PCIE_TX4P

PCIE_TX4N

PCIE_TX5P

PCIE_TX5N

PCIE_TX6P

PCIE_TX6N

PCIE_TX7P

PCIE_TX7N

PCIE_TX8P

PCIE_TX8N

PCIE_TX9P

PCIE_TX9N

PCIE_TX10P

PCIE_TX10N

PCIE_TX11P

PCIE_TX11N

PCIE_TX12P

PCIE_TX12N

PCIE_TX13P

PCIE_TX13N

PCIE_TX14P

PCIE_TX14N

PCIE_TX15P

PCIE_TX15N

Calibration

Calibration

PCIE_CALRN

PCIE_CALRP

PCIE_CALI

3

AG31

AG30

AF31

AF30

AF28

AF27

AD31

AD30

AD28

AD27

AB31

AB30

AB28

AB27

AA31

AA30

AA28

AA27

W31

W30

W28

W27

V31

V30

V28

V27

U31

U30

U28

U27

R31

R30

AG26

AJ27

AK29

R8 2.0KR8 2.0K

R9 1.27KR9 1.27K

R10 2.0KR10 2.0K

+PCIE_VDDC

2

GFXTp0_PERp0 (4)

GFXTn0_PERn0 (4)

GFXTp1_PERp1 (4)

GFXTn1_PERn1 (4)

GFXTp2_PERp2 (4)

GFXTn2_PERn2 (4)

GFXTp3_PERp3 (4)

GFXTn3_PERn3 (4)

GFXTp4_PERp4 (4)

GFXTn4_PERn4 (4)

GFXTp5_PERp5 (4)

GFXTn5_PERn5 (4)

GFXTp6_PERp6 (4)

GFXTn6_PERn6 (4)

GFXTp7_PERp7 (4)

GFXTn7_PERn7 (4)

GFXTp8_PERp8 (4)

GFXTn8_PERn8 (4)PETn8_GFXRn8(4)

GFXTp9_PERp9 (4)

GFXTn9_PERn9 (4)

GFXTp10_PERp10 (4)

GFXTn10_PERn10 (4)

GFXTp11_PERp11 (4)

GFXTn11_PERn11 (4)

GFXTp12_PERp12 (4)

GFXTn12_PERn12 (4)

GFXTp13_PERp13 (4)

GFXTn13_PERn13 (4)

GFXTp14_PERp14 (4)

GFXTn14_PERn14 (4)

GFXTp15_PERp15 (4)

GFXTn15_PERn15 (4)

1

For Tektronix LA only

Place close

to ASIC

A A

5

4

RV630

RV630

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

CONFIDENTIAL & PROPRIETARY TO ADVANCED MICRO DEVICES INC.

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

© 2007 Advanced Micro Devices

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

This AMD Board schematic and design is the exclusive property of AMD,

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

and is provided only to entities under a non-disclosure agreement

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

with AMD for evaluation purposes. Further distribution or disclosure

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

is strictly prohibited. Use of this schematic and design for any purpose

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

other than evaluation requires a Board Technology License Agreement

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

with AMD. AMD makes no representations or warranties of any kind

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

regarding this schematic and design, including, not limited to,

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

any implied warranty of merchantibility or fitness for a particular

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

purpose, and disclaims responsibility forany consequences resulting

from use of the information included herein.

from use of the information included herein.

from use of the information included herein.

Title

Title

Title

RV630 DDR2- ASIC PCIE I/F

RV630 DDR2- ASIC PCIE I/F

3

2

RV630 DDR2- ASIC PCIE I/F

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

Advanced Micro Devices Inc.

1 Commerce Valley Drive East

1 Commerce Valley Drive East

1 Commerce Valley Drive East

Markham, Ontario

Markham, Ontario

Markham, Ontario

Friday, May 04, 2007

Friday, May 04, 2007

Friday, May 04, 2007

Sheet

Sheet

Sheet

of

723

of

723

of

723

1

Doc No.

Doc No.

Doc No.

RevDate:

RevDate:

RevDate:

0

0

0

105-B281xx-00A

105-B281xx-00A

105-B281xx-00A

www.vinafix.vn

Loading...

Loading...