MSI MS-V088 Schematic 30

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

ASSEMBLYNVPNVARIANT

B

1

2

SKU

3

4

5

6

12

13

14

7

8

9

10

11

15

P403-A01 DESIGN -- G84-200, 256 MB DDR2,DVI-I, VGA, HDTV

PAGE SUMMARY:

Page 1: TABLE OF CONTENTS & REVISION HISTORY

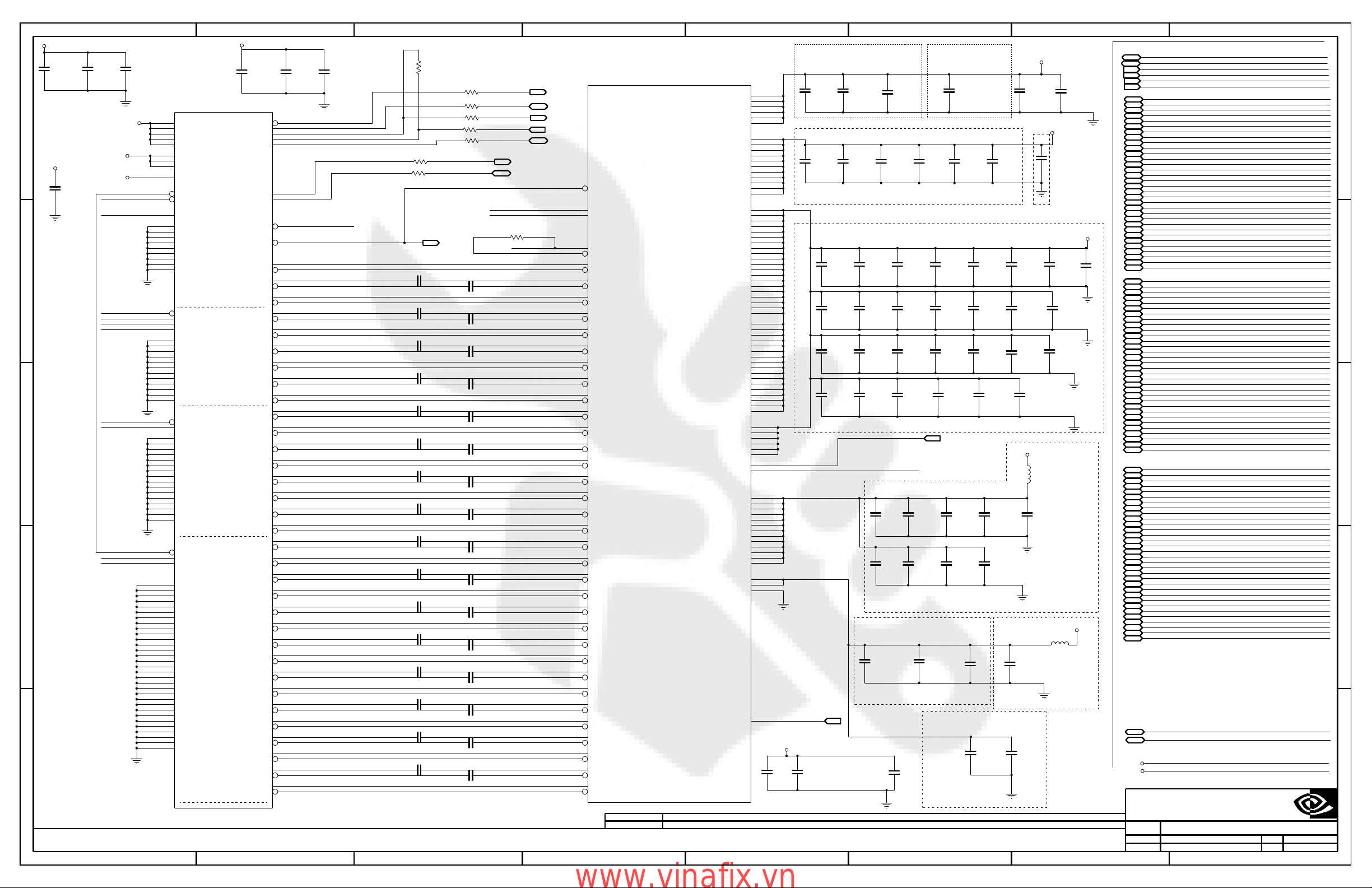

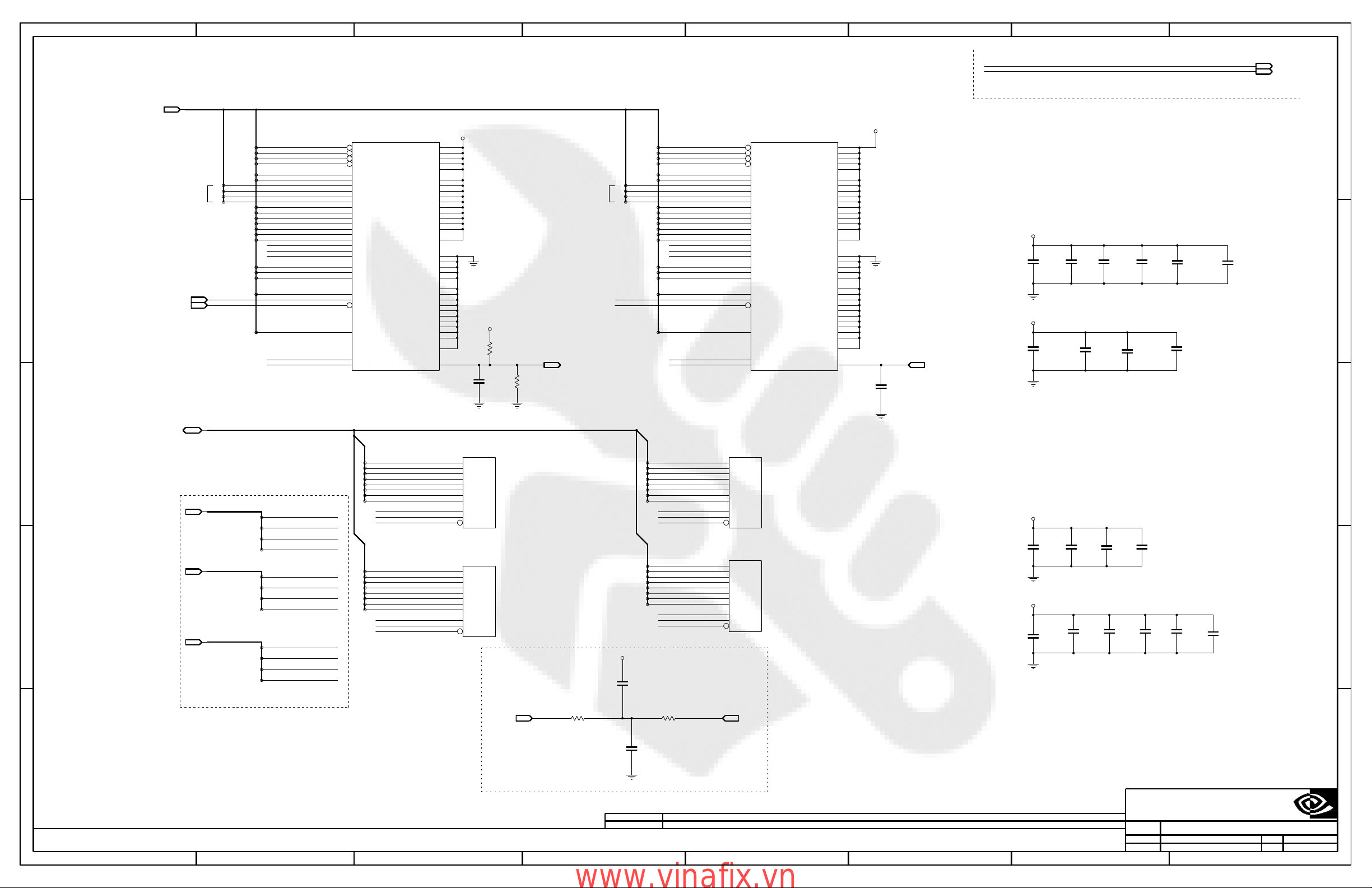

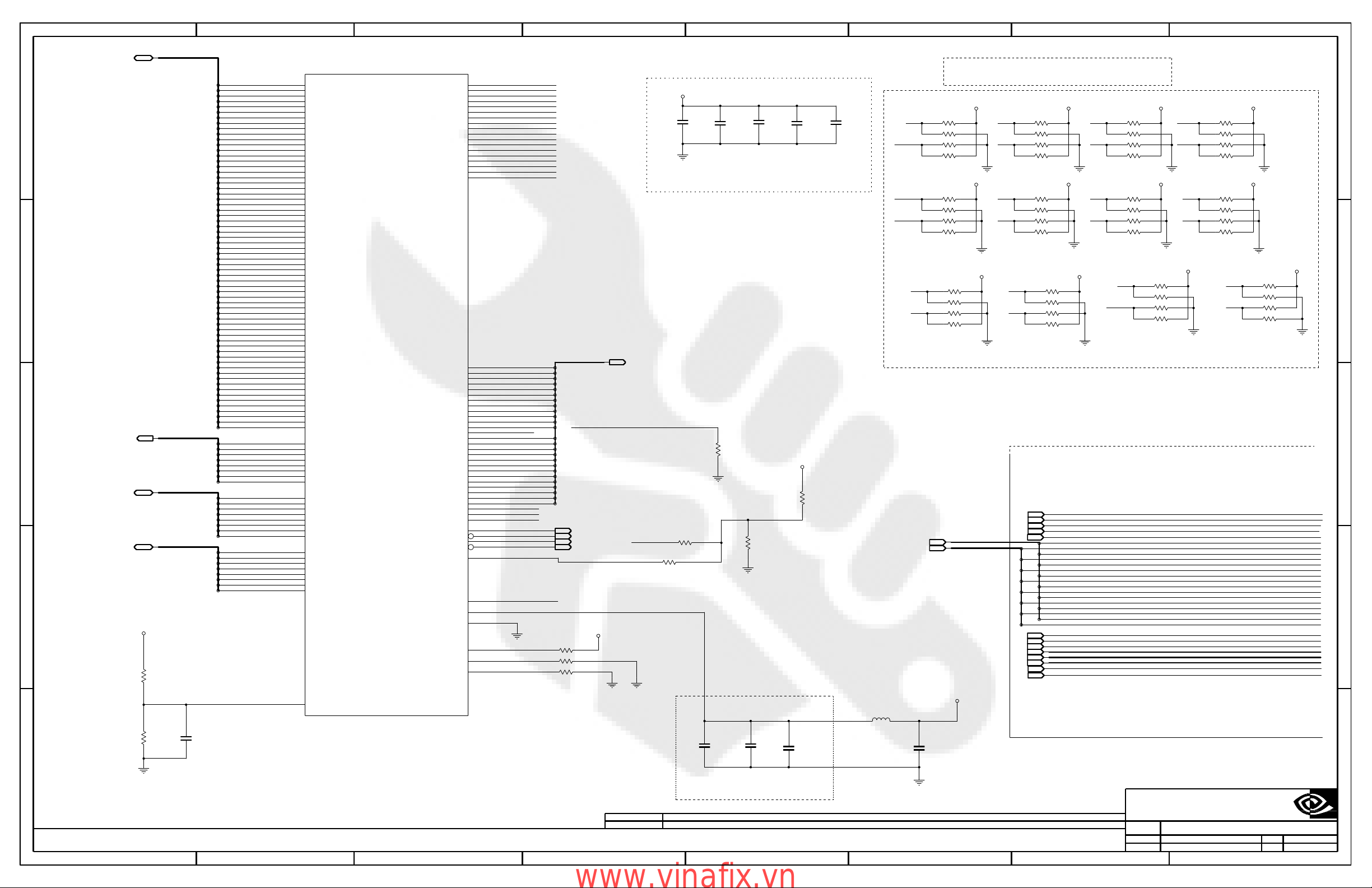

Page 2: PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

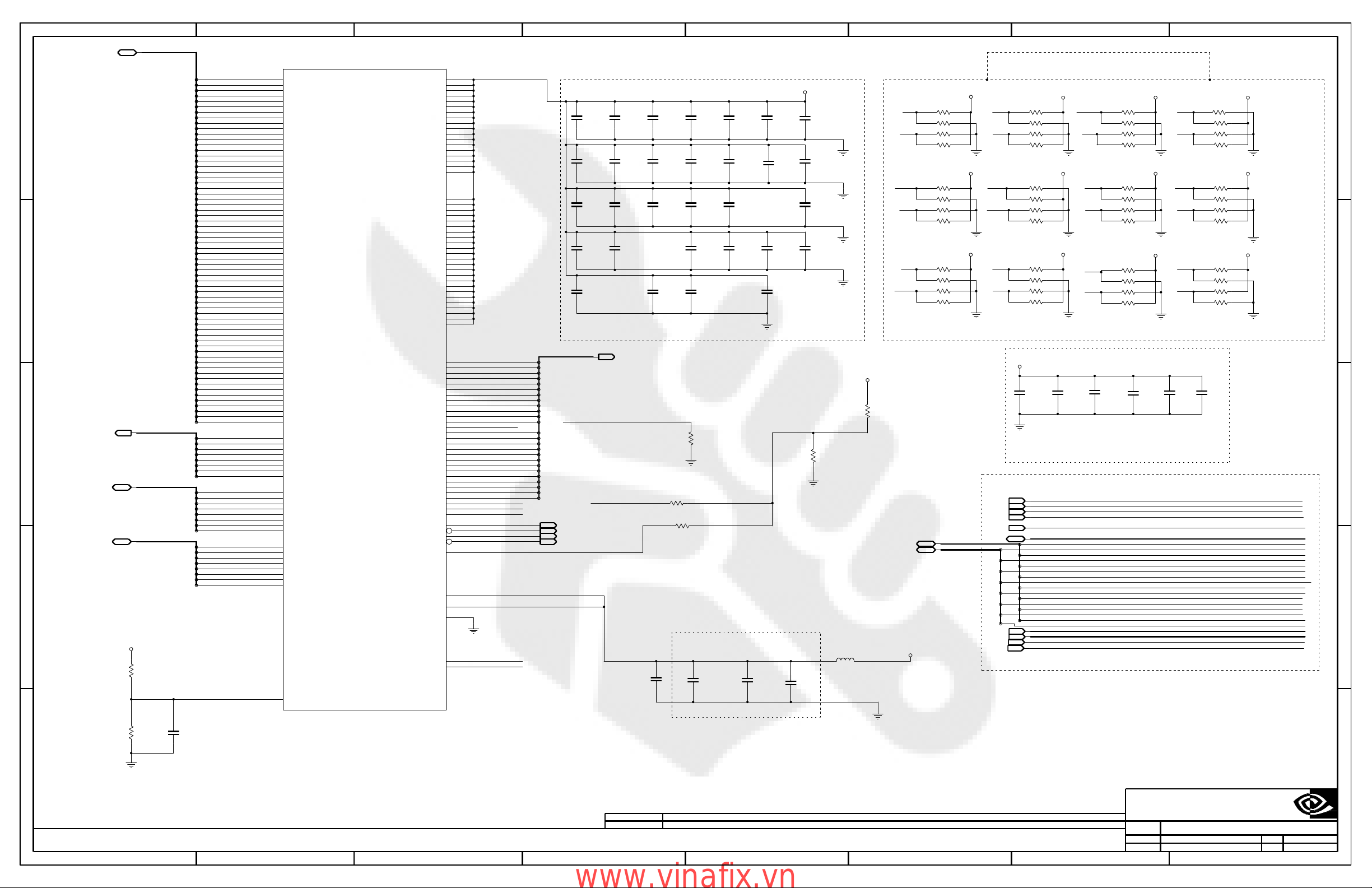

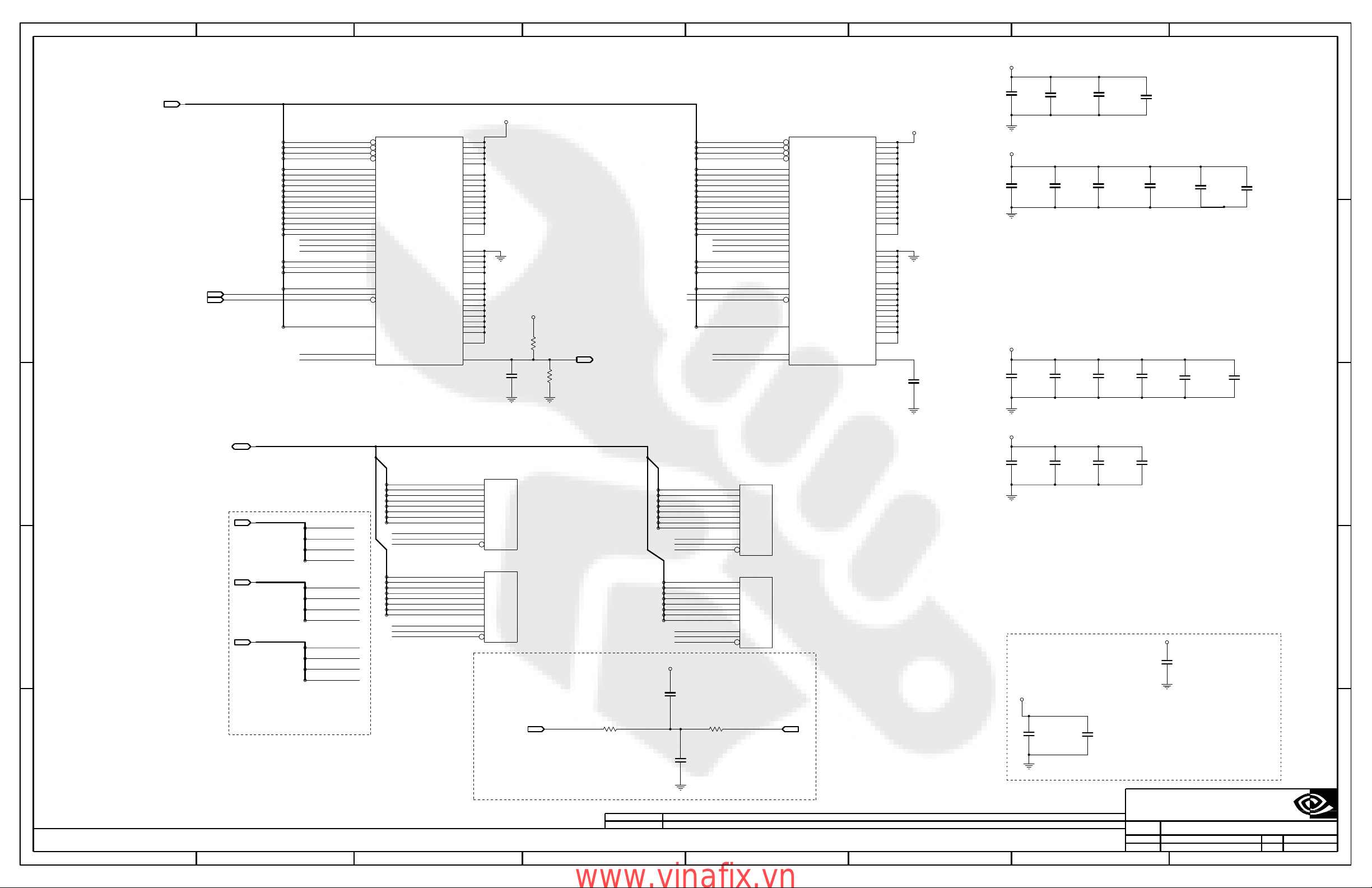

Page 3: FBA MEMORY INTERFACE, GPU FBVDD/Q DECOUPLING CAPS, FBVTT TERMINATION

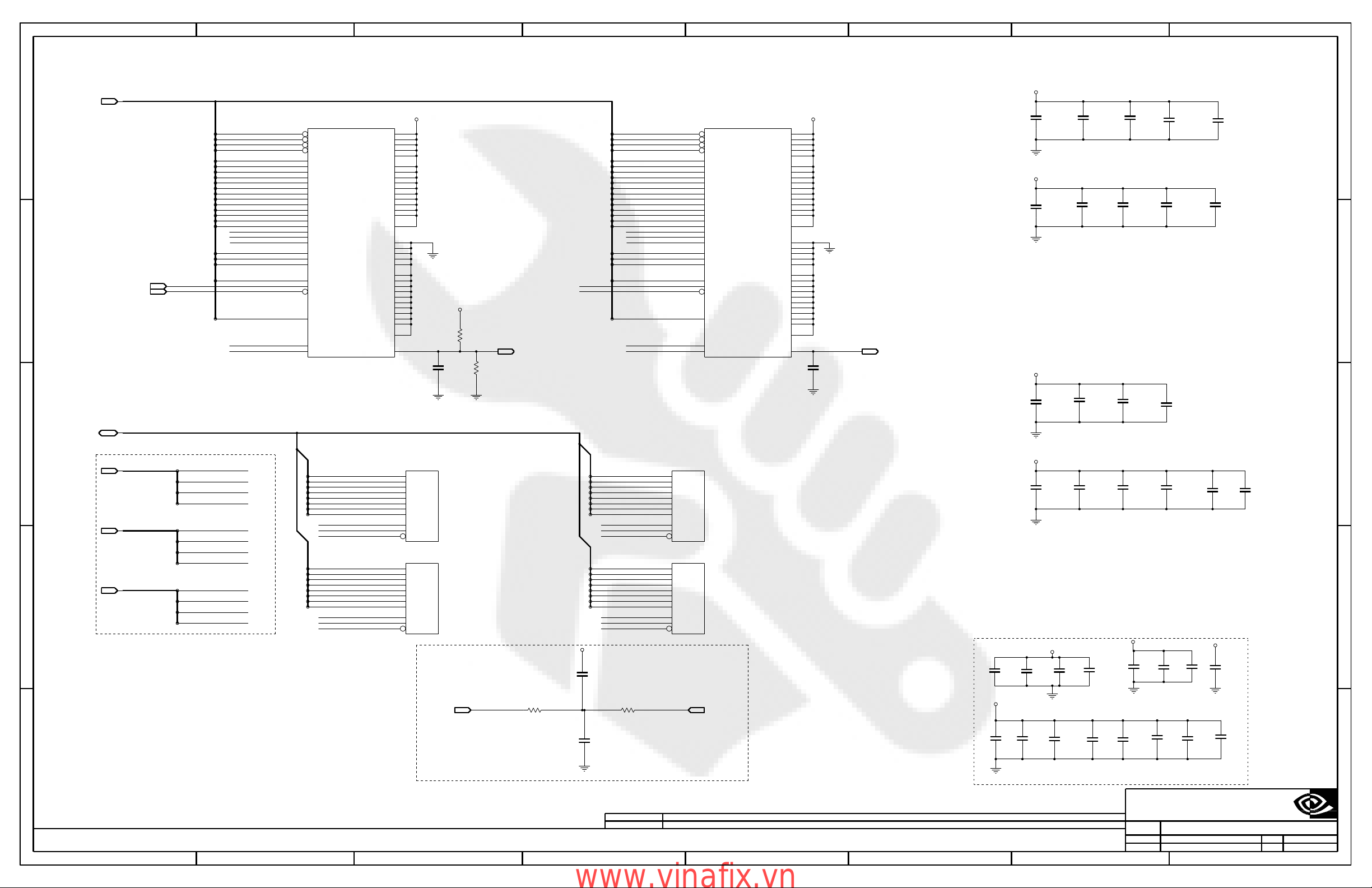

Page 4: FBA 16Mx16 DDR2 MEMORIES, BANK 0..31

Page 5: FBA 16Mx16 DDR2 MEMORIES, 1ST BANK 32..63

Page 6: FBC MEMORY INTERFACE, GPU FBVTT, FBVDDQ

Page 7: FBC 16MX16 DDR2 MEMORIES, 2ND BANK 0..31

Page 8: FBC 16Mx16 DDR2 MEMORIES, 2ND BANK 32..63

Page 9: DACA FILTERS, DACA SYNC BUFFERS & DB15 SOUTH

Page 10: DACC FILTERS, DACC SYNC BUFFERS & DB15 MID

Page 11: TMDS LINK A & PU's, DVI CONNECTOR SOUTH

Page 12: TMDS LINK C

Page 13: MIOA & MIOB

Page 14: DACB FILTERS, SYNC STRIPPER, MINIDIN CONNECTOR NORTH,HDTV HEADER

Page 15: GPU GND CONNECTION, XTAL

Page 16: JTAG, BIOS ROM, HDCP ROM, FAN CONTROL, GPIO

Page 17: SPDIF

Page 18: BIOS STRAPS & MECHANICALS

Page 19: POWER SUPPLY: TMDS IOVDD,5V,A3V3

Page 20: thermal protection and dynamic NVVDD

Page 21: PowerSupplyI: NVVDD, A2V5

Page 22: PowerSupplyIII: FBVDDQ, PLLVDD

BASE

SKU0010

SKU0001

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

TABLE OF CONTENTS & REVISION HISTORY

www.vinafix.vn

600-10403-0000-100

600-10403-0010-100

600-10403-0001-100

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

P403-A00 G86-300 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

<UNDEFINED>

BASE LEVEL GENERIC SCHEMATIC ONLY, COMMON & NO_STUFF ASSEMBLY NOTES AND BOM NOT FINAL

600-10403-0001-100 A

p403_a01

hlu

1 OF 22

11-DEC-2006

3V3_PEX

BIINBIINININBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIBIIN

OUT

OUTBIINBIOUTBIIN

1/14 PCI_EXPRESS

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

VDD

VDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDD

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

PEX_IOVDDQ

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD_LP

VDD_LP

VDD_LP

VDD_LP

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD33

VDD_LP

VDD_LP

VDD_SENSE

GND_SENSE

VDD33

VDD33

PEX_PLLGND

PEX_PLLDVDD

PEX_PLLAVDD

SPDIF

PEX_RST

RFU

RFU

PEX_RX1

PEX_TX1

PEX_TX1

PEX_RX0

PEX_RX0

PEX_TX0

PEX_TX0

PEX_REFCLK

PEX_REFCLK

PEX_TSTCLK_OUT

PEX_TSTCLK_OUT

PEX_RX1

PEX_TX2

PEX_RX4

PEX_RX4

PEX_RX3

PEX_RX3

PEX_TX4

PEX_TX4

PEX_TX3

PEX_TX3

PEX_RX2

PEX_RX2

PEX_TX2

PEX_TX5

PEX_TX5

PEX_RX5

PEX_TX8

PEX_TX8

PEX_RX7

PEX_RX7

PEX_TX7

PEX_TX7

PEX_RX6

PEX_RX6

PEX_TX6

PEX_TX6

PEX_RX5

PEX_RX8

PEX_RX8

PEX_TX9

PEX_TX9

PEX_TX11

PEX_TX11

PEX_RX11

PEX_RX11

PEX_RX10

PEX_RX10

PEX_TX10

PEX_TX10

PEX_RX9

PEX_RX9

PEX_TX12

PEX_TX12

PEX_RX12

PEX_RX12

PEX_TX15

PEX_TX15

PEX_RX14

PEX_RX14

PEX_TX14

PEX_TX14

PEX_RX13

PEX_RX13

PEX_TX13

PEX_TX13

PEX_RX15

PEX_RX15

OUT

END OF X8

END OF X16

END OF X1

END OF X4

TCLK JTAG2

TMS JTAG5

TDO JTAG4

TDI JTAG3

WAKE

SMDAT

SMCLK

PERN0

PERP0

REFCLK

PERST

REFCLK

PETN1

PERP2

PETN0

PERP1

PERN1

PETP0

PETP1

PERN3

PETP3

PETN3

PETP2

PERP3

PETN2

PERN2

PERP4

PERN4

PETN4

PERP5

PETP4

PERN5

PETP5

PETP6

PERN6

PERP6

PETN5

PERP7

PETN6

PERN7

PETN8

PETP8

PERP8

PETN7

PETP7

PERN8

PERN9

PERP9

PERP10

PERN10

PETP10

PETP9

PETN9

PETN10

PETN11

PERP12

PERN12

PERP11

PERN11

PETP11

PETN12

PETP12

PETN13

PERP13

PERN13

PETP13

PERP14

PERN15

PETP15

PETN15

PERN14

PETN14

PETP14

PERP15

TRST* JTAG1+12V

+12V/RSVD

+3V3AUX

+12V

+12V

+12V

+3V3

+3V3

+3V3

PRSNT2

PRSNT1

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

GND

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

C43

.01UF

25V

10%

X7R

0402

COMMON

3V3AUX

GND

Place Close to fingers

C42

.1UF

16V

10%

X7R

0402

COMMON

12V_PEX

3V3_PEX

3V3AUX

PRSNT

SNN_PE_PRSNT2_A

SNN_PE_RSVD2

SNN_PE_PRSNT2_B

SNN_PE_RSVD3

SNN_PE_RSVD4

SNN_PE_RSVD5

SNN_PE_PRSNT2_C

SNN_PE_RSVD6

PRSNT

SNN_PE_RSVD7

SNN_PE_RSVD8

C47

.1UF

16V

10%

X7R

0402

COMMON

C790

10UF

16V

20%

X5R

1206

NO STUFF

GND

10.0

GND

GND

GND

GND

A10

B10

B17

B12

A12

B13

A15

B16

B18

A18

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

B1

B2

A2

A3

B3

B8

A9

A1

B4

A4

B7

NONPHY-X16

CN2

CON_X16

CON_PCIEXP_X16_EDGE

NO STUFF

12V_PEX

C795

.01UF

10%

X7R

0402

COMMON

B9

A5

A6

A7

A8

B5

B6

B11

A11

A13

A14

A16

A17

B14

B15

A21

A22

B19

B20

A25

A26

B23

B24

A29

A30

B27

B28

A35

A36

B33

B34

A39

A40

B37

B38

A43

A44

B41

B42

A47

A48

B45

B46

A52

A53

B50

B51

A56

A57

B54

B55

A60

A61

B58

B59

A64

A65

B62

B63

A68

A69

B66

B67

A72

A73

B70

B71

A76

A77

B74

B75

A80

A81

B78

B79

C796

.1UF

16V25V

10%

X7R

0402

COMMON

PEX_JT_TRST*

PEX_JT_TCLK

PEX_JT_TDI

PEX_JT_TDO

PEX_JT_TMS

SNN_PEX_WAKE*

C40

10UF

16V

20%

X5R

1206

NO STUFF

GND

PEX_RST*

PEX_REFCLK

PEX_REFCLK*

PEX_TXX0

PEX_TXX0*

PEX_RX0

PEX_RX0*

PEX_TXX1

PEX_TXX1*

PEX_RX1

PEX_RX1*

PEX_TXX2

PEX_TXX2*

PEX_RX2

PEX_RX2*

PEX_TXX3

PEX_TXX3*

PEX_RX3

PEX_RX3*

PEX_TXX4

PEX_TXX4*

PEX_RX4

PEX_RX4*

PEX_TXX5

PEX_TXX5*

PEX_RX5

PEX_RX5*

PEX_TXX6

PEX_TXX6*

PEX_RX6

PEX_RX6*

PEX_TXX7

PEX_TXX7*

PEX_RX7

PEX_RX7*

PEX_TXX8

PEX_TXX8*

PEX_RX8

PEX_RX8*

PEX_TXX9

PEX_TXX9*

PEX_RX9

PEX_RX9*

PEX_TXX10

PEX_TXX10*

PEX_RX10

PEX_RX10*

PEX_TXX11

PEX_TXX11*

PEX_RX11

PEX_RX11*

PEX_TXX12

PEX_TXX12*

PEX_RX12

PEX_RX12*

PEX_TXX13

PEX_TXX13*

PEX_RX13

PEX_RX13*

PEX_TXX14

PEX_TXX14*

PEX_RX14

PEX_RX14*

PEX_TXX15

PEX_TXX15*

PEX_RX15

PEX_RX15*

PEX_I2CS_SCL

PEX_I2CS_SDA

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

COMMON

0

5%

0402

0.05R_MAX

R575

RP501

0402X4

0.05R_MAX

RP501

0402X4

RP501

0402X4

0.05R_MAX

0402X4

R572

0.05R_MAX

0

R28

NO STUFF

0402

5%

0

R29

NO STUFF

0402

5%

20.4C<

.1UF

C740

16V

040210%

X7RCOMMON

.1UF

C724

16V

040210%

X7R

.1UF

C710

16V

0402

10%

X7R

.1UF

C692

16V

0402

10%

X7RCOMMON

.1UF

C677

16V

0402

10%

X7R

.1UF

C657

16V

0402

10%

X7R

.1UF

C641

16V

040210%

X7RCOMMON

.1UF

C631

16V

0402X7R 10%COMMON

C612

.1UF

C620

16V

040210%

X7R

.1UF

C611

16V

0402

10%

X7R

C597

.1UF

C601

16V

0402

10%

X7RCOMMON

.1UF

C600

16V

0402

10%

X7R

.1UF

C593

16V

0402

10%

X7R

C592

.1UF

C594

16V

040210%

X7R

C580

.1UF

C581

16V

0402

10%

X7R

C573

.1UF

C575

16V

0402

10%

X7RCOMMON

16X PCIe Interface

JTAG_TRST*

1

4

3

2

0402

I2CS_SCL

I2CS_SDA

C730

C716

0402

C702

0402

C684

0402

C668

0402

C651

0402

C634

0402

C623

C605

0402

0402

C596

0402

C586

0402

0402

0402

7

5%

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

.1UF

0

8

NO STUFF

JTAG_TCLK

0

5

NO STUFF

JTAG_TDI

0

6

NO STUFF

JTAG_TDO

0RP501

NO STUFF

JTAG_TMS

0

NO STUFF

2.1G<

2.1G<

SNN_PEXCAPD_VDDQ

SNN_PEXCALPD_GND

0402 COMMON

10%

10%

10%

10%

10%

10%

10%

10%

10%

10%

5%

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R0402 16V 10% COMMON

X7R

COMMON10%

X7R

COMMON

X7R COMMON

X7R

COMMON10%

X7R COMMON

X7R

COMMON

X7R

COMMON10%

X7R COMMON

PEX_TEST_PLLCLK_OUT

PEX_TEST_PLLCLK_OUT_N

16V0402

16V

16V

16V

16V

16V

16V

16V0402

16V

16V

16V

16V

16V0402

16V

16V

16.1E>

16.1E<>

200R533

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

16.2A<

16.2A<>

16.2A<

16.2A>

16.2A<>

U_GPU_G3_BGA820-NV43-U-A1NA-A

G1

G84-200-A1

BGA820

COMMON

AH15

AG12

AH13

AM12

AM11

AH14

AJ14

AJ15

AK15

AK13

AK14

AH16

AG16

AM14

AM15

AG17

AH17

AL15

AL16

AG18

AH18

AK16

AK17

AK18

AJ18

AL17

AL18

AJ19

AH19

AM18

AM19

AG20

AH20

AK19

AK20

AG21

AH21

AL20

AL21

AK21

AJ21

AM21

AM22

AJ22

AH22

AK22

AK23

AG23

AH23

AL23

AL24

AK24

AJ24

AM24

AM25

AJ25

AH25

AK25

AK26

AH26

AG26

AL26

AL27

AK27

AJ27

AM27

AM28

AJ28

AH27

AL28

AL29

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

PCI EXPRESS 16X, NVVDD DECOUPLING CAPS,PEX_IOVDD/Q DECOUPLING CAPS

AD23

AF23

AF24

AF25

AG24

AG25

AC16

AC17

AC21

AC22

AE18

AE21

AE22

AF12

AF18

AF21

AF22

K16

K17

N13

N14

N16

N17

N19

P13

P14

P16

P17

P19

R16

R17

T13

T14

T15

T18

T19

U13

U14

U15

U18

U19

V16

V17

W13

W14

W16

W17

W19

Y13

Y14

Y16

Y17

Y19

Y20

P20

T20

T23

U20

U23

W20

N20

M21

AC11

AC12

AC24

AD24

AE11

AE12

H7

J7

K7

L10

L7

L8

M10

AF15

AE15

AE16

J6

600mA

NVVDD_SENSE

SNN_GND_SENSE

GND

SPDIF

NVVDD

C670

10UF

6.3V

20%

X5R

0805

COMMON

Place near balls

C671

.022UF

16V

10%

X7R

0402

COMMON

C663

.022UF

16V

10%

X7R

0402

COMMON

VDD33

PEX_PLL_VDD

C705

.1UF

16V

10%

X7R

0402

COMMON

www.vinafix.vn

VALUES TBD

C654

.022UF

16V

10%

X7R

0402

COMMON

C625

.022UF

16V

10%

X7R

0402

COMMON

C707

1UF

6.3V

10%

0402

COMMON

C652

4.7UF

6.3V

10%

X5R

0603

COMMON

C704

.1UF

16V

10%

X7R

0402

COMMON

C639

1UF

6.3V

10%

X5R

COMMON

17.1F<

C614

.022UF

16V

10%

X7R

0402

COMMON

VALUES TBD

Place near balls

C636

.01UF

25V

10%

X7R

0402

COMMON

Place near balls

C674

.1UF

16V

10%

X7RX5R

0402

COMMON

C683

.1UF

16V

10%

X7R

0402

COMMON

C658

.1UF

16V

10%

X7R

0402

COMMON

C688

.1UF

16V

10%

X7R

04020402

COMMON

C690

1UF

6.3V

10%

X5R

0402

COMMON

C662

1UF

6.3V

10%

X5R

0402

COMMON

C686

.1UF

16V

10%

X7R

0402

COMMON

C691

.1UF

16V

10%

0402

COMMON

Place near balls

C703C736

4700PF

.1UF

25V

16V

10%

10%

X7R

X7R

0402

0402

COMMONCOMMON

C711

C708

1UF

.1UF

6.3V

16V

10%

10%

X5RX7R

0402

0402

COMMON

COMMON

Place near balls

C693

.1UF

10%

16V

X7R

0402

COMMON

17.3F>

C653

.1UF

16V

10%

X7R

0402

COMMON

GND

Place Close to GPU

C604

1UF

6.3V

10%

X5R

0402

COMMON

C650

1UF

6.3V

10%

X5R

0402

COMMON

C629

.1UF

16V

10%

X7R

0402

COMMON

C659

.1UF

16V

10%

X7R

0402

COMMON

C660

1UF

6.3V

10%

0402

COMMON

21.1F<

C694

.01UF

25V

10%

X7R

0402

COMMON

21.2G<

C718

.022UF

16V

10%

X7R

0402

COMMON

C749

1UF

6.3V

10%

X5R

0402

COMMON

C665

1UF

6.3V

10%

X5R

0402

COMMON

C638

.1UF

16V

10%

X7R

0402

COMMON

C666

.1UF

16V

10%

X7R

0402

COMMON

C656

1UF

6.3V

10%

X5R

0402

COMMON

C645

.01UF

25V

10%

X7R

0402

COMMON

C678

.01UF

25V

10%

X7R

0402

COMMON

Place near balls

C680

4700PF

25V

X7R

0402

COMMON

Place Close to GPU

C640

1UF

6.3V

10%

X5R

0402

COMMON

C712

1UF

6.3V

10%

X5R

0402

COMMON

C701

1UF

6.3V

10%

X5R

0402

COMMON

C642

4.7UF

6.3V

10%

X5R

0603

COMMON

C706

4.7UF

6.3V

10%

X5RX7R X5RX5R

0603

COMMON

A3V3

C616

.022UF

16V

10%

X7R

0402

COMMON

C725

GND

.022UF

16V

10%

X7R

0402

COMMON

GND

Place Near BGA

C667

1UF

6.3V

10%

X5R

0402

COMMON

C685

470PF

50V

10%

10%

X7R

0402

COMMON

GND

PEX1V2

C609

1UF

6.3V

10%

X5R

0402

COMMON

C681

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

C689

1UF

6.3V

10%

0402

COMMON

LB505

180R@100MHz

COMMON

BEAD_0603

300 mA

C626

1UF

6.3V

10%

X5R

0402

COMMON

180R@100MHz

LB502

BEAD_0603

GND

PEX1V2

C648

4.7UF

6.3V

10%

X5R

0603

COMMON

C676

10UF

6.3V

20%

X5R

0805

COMMON

C699

4.7UF

6.3V

10%

X5R

0603

COMMON

COMMON

16.1E<>

C673

1UF

6.3V

10%

X5R

0402

COMMON

GND

GND

PEX1V2

PEX_REFCLK

PEX_REFCLK*

2.1C>

16.1E>

2.1C<>

GND

NVVDD

C695

4.7UF

6.3V

10%

X5R

0603

COMMON

GND

GND

12V_PEX

3V3_PEX

I2CS_SCL

I2CS_SDA

PEX_I2CS_SCL

PEX_I2CS_SDA

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

PEX_TXX0

PEX_TXX0*

PEX_TXX1

PEX_TXX1*

PEX_TXX2

PEX_TXX2*

PEX_TXX3

PEX_TXX3*

PEX_TXX4

PEX_TXX4*

PEX_TXX5

PEX_TXX5*

PEX_TXX6

PEX_TXX6*

PEX_TXX7

PEX_TXX7*

PEX_TXX8

PEX_TXX8*

PEX_TXX9

PEX_TXX9*

PEX_TXX10

PEX_TXX10*

PEX_TXX11

PEX_TXX11*

PEX_TXX12

PEX_TXX12*

PEX_TXX13

PEX_TXX13*

PEX_TXX14

PEX_TXX14*

PEX_TXX15

PEX_TXX15*

PEX_RX0

PEX_RX0*

PEX_RX1

PEX_RX1*

PEX_RX2

PEX_RX2*

PEX_RX3

PEX_RX3*

PEX_RX4

PEX_RX4*

PEX_RX5

PEX_RX5*

PEX_RX6

PEX_RX6*

PEX_RX7

PEX_RX7*

PEX_RX8

PEX_RX8*

PEX_RX9

PEX_RX9*

PEX_RX10

PEX_RX10*

PEX_RX11

PEX_RX11*

PEX_RX12

PEX_RX12*

PEX_RX13

PEX_RX13*

PEX_RX14

PEX_RX14*

PEX_RX15

PEX_RX15*

NET

NET

12V_PEX

3V3_PEX

p403_a01

hlu

NV_CRITICALNET

PEX_PLL_VDD

NV_PLLAVDD

NV_SOURCE_POWER

12V

3.3V

NV_IMPEDENCE

100DIFF

1

1

50OHM

2

50OHM

2

50OHM

2

50OHM

2

1

100DIFF

100DIFF

1

100DIFF

1

1

100DIFF

100DIFF

1

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

100DIFF

1

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

100DIFF

1

1

100DIFF

100DIFF

1

1

100DIFF

1

100DIFF

100DIFF

1

100DIFF

1

100DIFF

1

1

100DIFF

100DIFF

1

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

100DIFF

1

1

100DIFF

1

100DIFF

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

100DIFF

1

1 100DIFF

100DIFF

1

100DIFF1

1 100DIFF

1 100DIFF

1 100DIFF

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

VOLTAGE

1.20000V

1.20000V

12V

3.3V

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF1

100DIFF

MAX_CURRENTVOLTAGE

MIN_LINE_WIDTH

10.0

10.0

5.5A

600-10403-0001-100 A

2 OF 22

DIFFPAIR

PEX_REFCLK

PEX_REFCLK100DIFF

PEX_TX0

PEX_TX0

PEX_TX1

PEX_TX1

PEX_TX2

PEX_TX2

PEX_TX3

PEX_TX3

PEX_TX4

PEX_TX4

PEX_TX5

PEX_TX5

PEX_TX6

PEX_TX6

PEX_TX7

PEX_TX7

PEX_TX8

PEX_TX8

PEX_TX9

PEX_TX9

PEX_TX10

PEX_TX10

PEX_TX11

PEX_TX11

PEX_TX12

PEX_TX12

PEX_TX13

PEX_TX13

PEX_TX14

PEX_TX14

PEX_TX15

PEX_TX15

PEX_TXX0

PEX_TXX0

PEX_TXX1

PEX_TXX1

PEX_TXX2

PEX_TXX2

PEX_TXX3

PEX_TXX3

PEX_TXX4

PEX_TXX4

PEX_TXX5

PEX_TXX5

PEX_TXX6

PEX_TXX6

PEX_TXX7

PEX_TXX7

PEX_TXX8

PEX_TXX8

PEX_TXX9

PEX_TXX9

PEX_TXX10

PEX_TXX10

PEX_TXX11

PEX_TXX11

PEX_TXX12

PEX_TXX12

PEX_TXX13

PEX_TXX13

PEX_TXX14

PEX_TXX14

PEX_TXX15

PEX_TXX15

PEX_RX0

PEX_RX0

PEX_RX1

PEX_RX1

PEX_RX2

PEX_RX2

PEX_RX3

PEX_RX3

PEX_RX4

PEX_RX4

PEX_RX5

PEX_RX5

PEX_RX6

PEX_RX6

PEX_RX7

PEX_RX7

PEX_RX8

PEX_RX8

PEX_RX9

PEX_RX9

PEX_RX10

PEX_RX10

PEX_RX11

PEX_RX11

PEX_RX12

PEX_RX12

PEX_RX13

PEX_RX13

PEX_RX14

PEX_RX14

PEX_RX15

PEX_RX15

MIN_WIDTH

35.0

25.03.0A

11-DEC-2006

INININININBIBIBIININININOUT

OUT

OUT

OUT

OUT

BI

2/14 FBA

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDD

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBVDDQ

FBA_CMD0

FBA_CMD2

FBA_CMD3

FBVDDQ

FBA_CMD1

FBA_CMD4

FBA_CMD5

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD11

FBA_CMD13

FBA_CMD15

FBA_CMD16

FBA_CMD19

FBA_CMD21

FBA_CMD22

FBA_CMD24

FBA_CMD25

FBA_CMD20

FBA_CMD17

FBA_CMD14

FBA_CMD10

FBA_CMD6

FBA_CMD12

FBA_CMD18

FBA_CMD23

FBA_CMD26

FBA_DEBUG

FBA_CLK0

FBA_PLLAVDD

H_PLLAVDD

FBA_CLK1

FBA_CLK1

FBA_CLK0

FBA_CMD28

FBA_CMD27

NC1

NC2

FBA_PLLGND

FBAD10

FBAD11

FBAD12

FBAD13

FBAD14

FBAD15

FBAD0

FBAD1

FBAD2

FBAD3

FBAD4

FBAD5

FBAD6

FBAD7

FBAD8

FBAD9

FBAD16

FBAD17

FBAD18

FBAD19

FBAD20

FBAD21

FBAD22

FBAD23

FBAD24

FBAD25

FBAD26

FBAD27

FBAD28

FBAD29

FBAD30

FBAD31

FBAD32

FBAD33

FBAD34

FBAD35

FBAD36

FBAD44

FBAD47

FBAD49

FBAD51

FBAD37

FBAD38

FBAD39

FBAD40

FBAD41

FBAD42

FBAD43

FBAD45

FBAD46

FBAD48

FBAD50

FBAD52

FBAD53

FBAD54

FBAD55

FBAD56

FBAD57

FBAD58

FBAD59

FBAD60

FBAD61

FBAD62

FBAD63

FBADQM0

FBADQM1

FBADQM2

FBADQM3

FBADQM4

FBADQM5

FBADQM6

FBADQM7

FBADQS_WP0

FBADQS_WP1

FBADQS_WP2

FBADQS_WP3

FBADQS_WP4

FBADQS_WP5

FBADQS_WP6

FBADQS_WP7

FBADQS_RN0

FBADQS_RN1

FBADQS_RN2

FBADQS_RN3

FBADQS_RN4

FBADQS_RN7

FBADQS_RN6

FBADQS_RN5

FB_VREF1

OUTBIBI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

5.3A< 4.3A<

5.4A< 4.4A<

5.4A< 4.4A<

3.4F<> 5.3A<> 4.3A<>

3.4F<

3.4F<>

3.4F<>

FBVDDQ

NO STUFF

1K

1%

0402

R524

NO STUFF

1K

1%

0402

R523

GND

FBAD<63..0>

FBADQM<7..0>

FBADQS<7..0>

FBADQSN<7..0>

C589

.047UF

16V

10%

X7R

0402

COMMON

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

FBAD<0>

FBAD<1>

FBAD<2>

FBAD<3>

FBAD<4>

FBAD<5>

FBAD<6>

FBAD<7>

FBAD<8>

FBAD<9>

FBAD<10>

FBAD<11>

FBAD<12>

FBAD<13>

FBAD<14>

FBAD<15>

FBAD<16>

FBAD<17>

FBAD<18>

FBAD<19>

FBAD<20>

FBAD<21>

FBAD<22>

FBAD<23>

FBAD<24>

FBAD<25>

FBAD<26>

FBAD<27>

FBAD<28>

FBAD<29>

FBAD<30> E28

FBAD<31>

FBAD<32>

FBAD<33>

FBAD<34>

FBAD<35>

FBAD<36>

FBAD<37>

FBAD<38>

FBAD<39>

FBAD<40> AM30

FBAD<41>

FBAD<42>

FBAD<43>

FBAD<44>

FBAD<45>

FBAD<46>

FBAD<47>

FBAD<48>

FBAD<49>

FBAD<50>

FBAD<51>

FBAD<52>

FBAD<53>

FBAD<54>

FBAD<55>

FBAD<56>

FBAD<57>

FBAD<58>

FBAD<59>

FBAD<61>

FBAD<62>

FBAD<63>

FBADQM<0>

FBADQM<1>

FBADQM<2>

FBADQM<3>

FBADQM<4>

FBADQM<5>

FBADQM<6>

FBADQM<7>

FBADQS<0>

FBADQS<1>

FBADQS<2>

FBADQS<3>

FBADQS<4>

FBADQS<5>

FBADQS<6>

FBADQS<7>

FBADQSN<0>

FBADQSN<1>

FBADQSN<2>

FBADQSN<3>

FBADQSN<4>

FBADQSN<5>

FBADQSN<6>

FBADQSN<7>

N27

M27

N28

L29

K27

K28

J29

J28

P30

N31

N30

N32

L31

L30

J30

L32

H30

K30

H31

F30

H32

E31

D30

E30

H28

H29

E29

J27

F27

E27

F28

AD29

AE29

AD28

AC28

AB29

AA30

Y28

AB30

AF30

AJ31

AJ30

AJ32

AK29

AM31

AL30

AE32

AE30

AE31

AD30

AC31

AC32

AB32

AB31

AG27

AF28

AH28

AG28

AG29FBAD<60>

AD27

AF27

AE28

M29

M30

G30

F29

AA29

AK30

AC30

AG30

L28

K31

G32

G28

AB28

AL32

AF32

AH30

M28

K32

G31

G27

AA28

AL31

AF31

AH29

E32FB_VREF1

G1

G84-200-A1

BGA820

COMMON

A12

A18

A21

A24

A27

A3

A30

A6

A9

AA32

AD32

AG32

AK32

C32

F32

J32

M32

R32

AA25

AA26

AB25

AB26

G11

G12

G15

G18

G21

G22

H11

H12

H15

H18

H21

H22

L25

L26

M25

M26

R25

R26

V25

V26

PLACE BELOW GPU

C585

4700PF

25V

10%

X7R

0402

COMMON

C745

4700PF

25V

10%

X7R

0402

COMMON

C607

4700PF

25V

10%

X7R

0402

COMMON

C624

1UF

6.3V

10%

X5R

0402

COMMON

C582

4700PF

25V

10%

X7R

0402

COMMON

C606

.022UF

16V

10%

X7R

0402

COMMON

C613

.022UF

16V

10%

X7R

0402

COMMON

C753

.022UF

16V

10%

X7R

0402

COMMON

C588

.022UF

16V

10%

X7R

0402

COMMON

C587

1UF

6.3V

10%

X5R

0402

COMMON

C664

.1UF

16V

10%

X7R

0402

COMMON

C644

.1UF

16V

10%

X7R

0402

COMMON

C583

.1UF

16V

10%

X7R

0402

COMMON

C722

4700PF

25V

10%

X7R

0402

COMMON

C618

4700PF

25V

10%

X7R

0402

COMMON

C698

4700PF

25V

10%

X7R

0402

COMMON

C637

4700PF

25V

10%

X7R

0402

COMMON

C591

.1UF

16V

10%

X7R

0402

COMMON

C635

.022UF

16V

10%

X7R

0402

COMMON

C687

.022UF

16V

10%

X7R

0402

COMMON

C590

.022UF

16V

10%

X7R

0402

COMMON

C608

.022UF

16V

10%

X7R

0402

COMMON

C628

.1UF

16V

10%

X7R

0402

COMMON

C765

1UF

6.3V

10%

X5R

0402

COMMON

C627

1UF

6.3V

10%

X5R

0402

COMMON

C661

1000PF

16V

10%

X7R

0402

COMMON

FBVDDQ

C584

1UF

6.3V

10%

X5R

0402

COMMON

C619

.1UF

16V

10%

X7R

0402

COMMON

C672

4.7UF

6.3V

10%

X5R

0603

CHANGED

C630

1UF

6.3V

10%

X5R

0402

COMMON

GND

GND

GND

GND

FBA CMD/ADDR TERMINATIONS:

FBACMD<22>

FBACMD<1>

FBACMD<9>

FBACMD<10>

FBACMD<19>

FBACMD<20>

RP13

0402X4

RP13

0402X4

RP23

0402X4

RP23

0402X4

RP21

0402X4

RP21

0402X4

RP15

0402X4

RP15

0402X4

RP16

0402X4

RP16

0402X4

RP14

0402X4

RP14

0402X4

1

+/-5%

2

+/-5%

2

+/-5%

1

+/-5%

1

+/-5%

2

+/-5%

2

+/-5%

1

+/-5%

1

+/-5%

2

+/-5%

3

+/-5%

4

+/-5%

150

8

COMMON

150

7

COMMON

150

7

COMMON

150

8

COMMON

150

8

COMMON

150

7

COMMON

150

7

COMMON

150

8

COMMON

150

8

COMMON

150

7

COMMON

150

6

COMMON

150

5

COMMON

DDR2 OPERATION:

1) During initialization CKE and ODT low

2) Runtime .. CKE high and ODT operated by FBACMD<12> state machine

3) No termination rpak for FBACMD<11> or FBACMD<12> pins

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBACMD<24>

FBACMD<3>

FBACMD<5>

FBACMD<14>

FBACMD<21>

FBACMD<0>

RP20

0402X4

RP20

0402X4

RP16

0402X4

RP16

0402X4

RP19

0402X4

RP19

0402X4

RP22

0402X4

RP22

0402X4

RP17

0402X4

RP17

0402X4

RP13

0402X4

RP13

0402X4

1

+/-5%

2

+/-5%

3

+/-5%

4

+/-5%

2

+/-5%

1

+/-5%

3

+/-5%

4

+/-5%

1

+/-5%

2

+/-5%

3

+/-5%

4

+/-5%

8

7

6

5

7

8

6

5

8

7

6

5

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

150

COMMON

FBVDDQ

FBACMD<6>

FBACMD<4>

GND

FBVDDQ

FBACMD<15>

FBACMD<16>

GND

FBVDDQ

FBACMD<23>

FBACMD<2>

GND

RP18

0402X4

RP18

0402X4

RP18

0402X4

RP18

0402X4

RP17

0402X4

RP17

0402X4

RP24

0402X4

RP24

0402X4

RP14

0402X4

RP14

0402X4

RP20

0402X4

RP20

0402X4

2

+/-5%

1

+/-5%

4

+/-5%

3

+/-5%

4

+/-5%

3

+/-5%

2

+/-5%

1

+/-5%

1

+/-5%

2

+/-5%

3

+/-5%

4

+/-5%

150

7

COMMON

150

8

COMMON

150

5

COMMON

150

6

COMMON

150

5

COMMON

150

6

COMMON

150

7

COMMON

150

8

COMMON

150

8

COMMON

150

7

COMMON

150

6

COMMON

150

5

COMMON

FBVDDQ

GND

FBVDDQ

GND

FBVDDQ

GND

FBACMD<13>

FBACMD<8>

FBACMD<17>

FBACMD<18>

FBACMD<25>

FBACMD<7>

RP19

0402X4

RP19

0402X4

RP23

0402X4

RP23

0402X4

RP15

0402X4

RP15

0402X4

RP21

0402X4

RP21

0402X4

RP24

0402X4

RP24

0402X4

RP22

0402X4

RP22

0402X4

3

+/-5%

4

+/-5%

3

+/-5%

4

+/-5%

4

+/-5%

3

+/-5%

3

+/-5%

4

+/-5%

4

+/-5%

3

+/-5%

1

+/-5%

2

+/-5%

150

6

COMMON

150

5

COMMON

150

6

COMMON

150

5

COMMON

150

5

COMMON

150

6

COMMON

150

6

COMMON

150

5

COMMON

150

5

COMMON

150

6

COMMON

150

8

COMMON

150

7

COMMON

FBVDDQ

FBVDDQ

FBVDDQ

GND

GND

GND

GND

P32

U27

P31

U30

Y31

W32

W31

T32

V27

T28

T31

U32

W29

W30

T27

V28

V30

U31

R27

V29

T30

W28

R29

R30

P29

U28

Y32

Y30

V32

P28

R28

Y27

AA27

AC27

G23

G25

G24

D31

D32

GND

FBACMD<0>

FBACMD<1>

FBACMD<2>

FBACMD<3>

FBACMD<4>

FBACMD<5>

FBACMD<6>

FBACMD<7>

FBACMD<8>

FBACMD<9>

FBACMD<10>

FBACMD<11>

FBA_RST

FBACMD<13>

FBACMD<14>

FBACMD<15>

FBACMD<16>

FBACMD<17>

FBACMD<18>

FBACMD<19>

FBACMD<20>

FBACMD<21>

FBACMD<22>

FBACMD<23>

FBACMD<24>

FBACMD<25>

SNN_FBA_CMD<26>

SNN_FBA_CMD<27>

SNN_FBA_CMD<28>

FBACLK0

FBACLK0*

FBACLK1

FBACLK1*

FBA_DEBUG

SNN_FBA_NC1

SNN_FBA_NC2

0

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

18

19

20

21

22

23

24

25

FBACMD<25..0>

3.3F<

4.5C< 4.2A< 3.3F<

4.2A< 3.3F<

4.5E<

5.2A< 5.5C<

5.5E< 5.2A< 3.3F<

CKE

FBACMD<11>

5.1A< 4.1A< 3.4F<

PD REQUIRED FOR INITIALIZATION OF DDR2

R79

10K

5%

0402

COMMON

GND

FBA_RST

R616

0402

R617

0402

5%

0

NO STUFF

5%

0

COMMON

PLACE close to balls

FBA_PLLAVDD

C835

.01UF

25V

10%

X7R

0402

COMMON

C621

.01UF

25V

10%

X7R

0402

COMMON

FBACMD<12>

R516

10K

5%

0402

COMMON

PD REQUIRED FOR INITIALIZATION OF DDR2

GND

LB501

C622

.1UF

16V

10%

X7R

0402

COMMON

C617

1UF

6.3V

10%

X5R

0402

COMMON

BEAD_0603

R513

10K

0402

NO STUFF

180R@100MHz

COMMON

FBVDDQ

5%

5.4A<

5.4A<

FBVDDQ

GND

C503

.01UF

25V

10%

X7R

C504

.01UF

25V

10%

X7R

COMMONCOMMON

PLACE CLOSE TO

C505

.01UF

25V

10%

X7R

0402

COMMON

C746

.01UF

25V

10%

X7R

0402

COMMON

C506

.01UF

25V

10%

X7R

0402

C501

1UF

6.3V

10%

X5R

04020402 0402

COMMONCOMMON

TERMINATION RISISTORS

DIFFPAIRNET

FBACLK0

FBACLK0

FBACLK1

FBACLK1

FBADQS0

FBADQS0

FBADQS1

FBADQS1

FBADQS2

FBADQS2

FBADQS3

FBADQS3

FBADQS4

FBADQS4

FBADQS5

FBADQS5

FBADQS6

FBADQS6

FBADQS7

FBADQS7

12.0

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

100DIFF

50OHM

56OHM

50OHM

50OHM

50OHM

4.4A<

4.4A<

3.3A<>

3.4A<>

PEX1V2

4.5C< 4.2A< 3.4D>

3.4D> 5.5C< 5.2A<

FBADQS<7..0>

FBADQSN<7..0>

3.2D> 4.1A<

5.1A<

3.2D>

4.1A<

5.1A<

3.2D>

4.1A<

5.1A<

4.5E<

3.4D>

4.2A<

5.5E<

3.4D>

5.2A<

5.3A<>

4.3A<>

3.1A<>

5.3A<

3.3A>

4.3A<

FBACLK0

FBACLK0*

FBACLK1

FBACLK1*

FBA_PLLAVDD

FBAD<63..0>

FBADQS<0>

0

FBADQSN<0>

0

FBADQS<1>

1

FBADQSN<1>

1

FBADQS<2>

2

FBADQSN<2>

2

FBADQS<3>

3

FBADQSN<3>

3

FBADQS<4>

4

FBADQSN<4>

4

FBADQS<5>

5

FBADQSN<5>

5

FBADQS<6>

6

FBADQSN<6>

6

FBADQS<7>

7

7

FBADQSN<7>

FBADQM<7..0>

FBACMD<25..0>

FBA_RST

FBA_DEBUG

GND

NV_CRITICAL_NETNV_IMPEDANCEMIN_LINE_WIDTH

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

FBA MEMORY INTERFACE, GPU FBVDD/Q DECOUPLING CAPS, FBVTT TERMINATION

www.vinafix.vn

600-10403-0001-100 A

p403_a01

hlu

3 OF 22

11-DEC-2006

OUT

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

OUT

IN

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

IN

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

INININ

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

INBIIN

IN

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

FBA MEMORY 1st bank 0..31

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

3.2D> 3.4F< 5.1A<

3.1A<> 3.4F<> 5.3A<>

3.3A> 3.4F< 5.3A<

3.3A<> 3.4F<> 5.4A<

3.4A<> 3.4F<> 5.4A<

FBACMD<25..0>

USED ONLY FOR 1GB DEVICES ---->

3.3F<

3.4D>

4.5C<

3.3F<

3.4D>

4.5E<

FBAD<63..0>

FBADQM<7..0>

FBADQS<7..0>

FBADQSN<7..0>

FBACLK0

FBACLK0*

0

1

2

3

0

1

2

3

0

1

2

3

FBADQM<0>

FBADQM<1>

FBADQM<2>

FBADQM<3>

FBADQS<0>

FBADQS<1>

FBADQS<2>

FBADQS<3>

FBADQSN<0>

FBADQSN<1>

FBADQSN<2>

FBADQSN<3>

15

25

9

8

1

3

2

0

24

22

21

23

19

20

17

16

14

SNN_U8_FBAA<13>

SNN_U8_FBAA<14>

SNN_U8_FBAA<15>

10

18

7

11

FBACMD<12>

12

SNN_U8_A2

SNN_U8_E2

FBACMD<15>

FBACMD<25>

FBACMD<9>

FBACMD<8>

FBACMD<1>

FBACMD<3>

FBACMD<2>

FBACMD<0>

FBACMD<24>

FBACMD<22>

FBACMD<21>

FBACMD<23>

FBACMD<19>

FBACMD<20>

FBACMD<17>

FBACMD<16>

FBACMD<14>

FBACMD<10>

FBACMD<18>

FBACMD<7>

FBACMD<11>

M6

16MX16DDR2-2.5

BGA84

CHANGED

K7

L7

K3

L8

M8

M3

M7

N2

N8

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

FBAD<0>

FBAD<1>

FBAD<2>

FBAD<3>

FBAD<4>

FBAD<5>

FBAD<6>

FBAD<7>

FBADQM<0>

FBADQS<0>

FBADQSN<0>

FBAD<8>

FBAD<9>

FBAD<10>

FBAD<11>

FBAD<12>

FBAD<13>

FBAD<14>

FBAD<15>

FBADQM<1>

FBADQS<1>

FBADQSN<1>

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9N3

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

M6

16MX16DDR2-2.5

BGA84

CHANGED

D1

C2

B1

D3

C8

B9

D7

D9

B3

B7

A8

M6

16MX16DDR2-2.5

BGA84

CHANGED

H3

H1

G2

F1

H7

G8

H9

F9

F3

F7

E8

FBVDDQ

VREF_B

3.4D>

M5

16MX16DDR2-2.5

BGA84

CHANGED

FBACMD<15>

15

FBACMD<25>

25

FBACMD<9>

9

FBACMD<8>

8

FBACMD<1>

1

FBACMD<3>

3

FBACMD<2>

2

FBACMD<0>

0

FBACMD<24>

24

FBACMD<22>

22

FBACMD<21>

21

FBACMD<23>

23

FBACMD<19>

19

FBACMD<20>

20

FBACMD<17>

17

FBACMD<16>

16

FBACMD<14>

14

SNN_U7_FBAA<13>

SNN_U7_FBAA<14>

SNN_U7_FBAA<15>

FBACMD<10>

10

FBACMD<18>

18

FBACMD<7>

GND

FBVDDQ

R504

1K

1%

0402

COMMON

C515

.047UF

16V

10%

X7R

0402

COMMON

GND

3.3F<

4.2A<

USED ONLY FOR 1GB DEVICES ---->

R505

1K

1%

0402

COMMON

GND

FBACLK0

4.2F> 5.1H>

R73

0402

1%

60.4

CHANGED

FBVDDQ

FBACLK_C0

FBACLK0

FBACLK0*

GND

7

11

12

16

FBAD<16>

17

FBAD<17>

18

FBAD<18>

19

FBAD<19>

20

FBAD<20>

21

FBAD<21>

22

FBAD<22>

23

FBAD<23>

FBADQM<2>

FBADQS<2>

FBADQSN<2>

24

FBAD<24>

25

FBAD<25>

26

FBAD<26>

27

FBAD<27>

28

FBAD<28>

29

FBAD<29>

30

FBAD<30>

31

FBAD<31>

FBADQM<3>

FBADQS<3>

FBADQSN<3>

C85

.01UF

25V

10%

X7R

0402

COMMON

R76

0402

C75

.01UF

25V

10%

X7R

0402

COMMON

SNN_U7_A2

SNN_U7_E2

60.4

CHANGED

1%

FBACMD<11>

FBACMD<12>

FBACLK0*

K7

L7

K3

L8

M8

M3

M7

N2

N8

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

M5

16MX16DDR2-2.5

BGA84

CHANGED

F1

H3

H1

H7

G2

F9

H9

G8

F3

F7

E8

M5

16MX16DDR2-2.5

BGA84

CHANGED

D1

C2

D3

B1

D9

D7

C8

B9

B3

B7

A8

3.4D> 3.3F<

4.2A<

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

FBA 16Mx16 DDR2 MEMORIES, BANK 0..31

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9N3

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

FBVDDQ

VREF_B

GND

C517

.047UF

16V

10%

X7R

0402

COMMON

www.vinafix.vn

FBVDDQ

C523

1UF

6.3V

10%

X5R

0402

COMMON

C534

4.7UF

6.3V

10%

X5R

0603

CHANGED

C540

.01UF

25V

10%

X7R

0402

COMMON

C560

.1UF

16V

10%

X7R

0402

COMMON

C559

1UF

6.3V

10%

X5R

0402

COMMON

C554

1UF

6.3V

10%

X5R

0402

COMMON

C549

.01UF

25V

10%

X7R

0402

COMMON

GND

FBVDDQ

C552

.1UF

16V

10%

X7R

0402

COMMON

GND

GND

C522

.01UF

25V

10%

X7R

0402

COMMON

C539

.1UF

16V

10%

X7R

0402

COMMON

5.1H>

4.2C>

FBVDDQ

FBVDDQ

GND

C561

1UF

6.3V

10%

X5R

0402

COMMON

GND

FBVDDQ

C548

1UF

6.3V

10%

X5R

0402

GND

Place plane decoupling caps near DQS-DQM pairs.

FBVDDQ

C682

.1UF

16V

10%

X7R

0402

COMMON

C655

.01UF

25V

10%

X7R

0402

COMMON

GND

C697

.1UF

16V

10%

X7R

0402

COMMON

C84

.1UF

16V

10%

X7R

0402

COMMON

C57

.1UF

16V 16V

10%

X7R

0402

COMMON

C62

.1UF

10%

X7R

0402

COMMON

C541

.1UF

16V

10%

X7R

0402

COMMON

C524

.01UF

25V

10%

X7R

0402

COMMONCOMMON

C63

.1UF

16V

10%

X7R

0402

COMMON

C571

.1UF

16V

10%

X7R

0402

COMMON

C538

.01UF

25V

10%

X7R

0402

COMMON

C521

.01UF

25V

10%

X7R

0402

COMMON

FBVDDQ

GND

C80

.1UF

16V

10%

X7R

0402

COMMON

C700

.01UF

25V

10%

X7R

0402

COMMON

C530

.1UF

16V

10%

X7R

0402

COMMON

C82

.1UF

16V

10%

X7R

0402

COMMON

C535

4.7UF

6.3V

10%

X5R

0603

CHANGED

C526

.01UF

25V

10%

X7R

0402

COMMON

C83

.1UF

16V

10%

X7R

0402

COMMON

C508

.1UF

16V

10%

X7R

0402

COMMON

FBVDDQ

GND

C525

1UF

6.3V

10%

X5R

0402

COMMON

C788

.01UF

25V

10%

X7R

0402

COMMON

C81

.1UF

16V

10%

X7R

0402

COMMON

C547

.1UF

16V

10%

X7R

0402

COMMON

600-10403-0001-100 A

p403_a01

hlu

4 OF 22

11-DEC-2006

OUT

OUT

IN

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

OUT

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

IN

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

IN

2/2

DQ<6>

DQ<5>

DQ<4>

DQ<3>

DQ<0>

DQ<1>

DQ<2>

DQ<7>

DQM

DQS

DQS

1/2

VDD

VDD

VDD

VDD

VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDL

VDDQ

VSS

VSS

VSS

VSS

VSS

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

Vref

VSSL

A<0>

A<3>

A<4>

A<2>

A<1>

CS

RAS

WE

CAS

A<5>

A<11>

A<9>

NC/A<13>

A<10>

A<12>

NC/A<14>

A<6>

A<7>

A<8>

NC/A<15>

NC/BA<2>

BA<1>

BA<0>

CKE

CLK

CLK

ODT

NC

NC

INININBIINININ

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

FBA MEMORY 1st bank 32..63

PLACE ALL DISCRETE COMPONENTS AS NEAR AS POSSIBLE TO MEMORY

VREF_A 12.0

MIN_LINE_WIDTHNAME

VREF_B 12.0

5.3F<

5.3D>

4.2F>

4.2C>

3.4D>

3.4D>

3.3A<> 3.4F<> 4.4A<

3.4A<> 3.4F<> 4.4A<

3.1A<>

3.3A>

3.3F<

3.3F<

FBACMD<25..0>

13

4

5

6

FBACLK1

FBACLK1*

FBAD<63..0>

FBADQM<7..0>

FBADQS<7..0>

FBADQSN<7..0>

FBACMD<15>

15

FBACMD<25>

25

FBACMD<9>

9

8

FBACMD<1>

1

FBACMD<3>

3

FBACMD<13> M7

FBACMD<4>

FBACMD<5>

FBACMD<6>

FBACMD<21>

21

FBACMD<23>

23

FBACMD<19>

19

FBACMD<20>

20

FBACMD<17>

17

FBACMD<16>

16

FBACMD<14>

14

SNN_U10_FBAA<13>

SNN_U10_FBAA<14>

SNN_U10_FBAA<15>

FBACMD<10>

10

FBACMD<18>

18

FBACMD<7>

7

FBACMD<11>

11

FBACMD<12>

12

SNN_U10_A2

SNN_U10_E2

FBADQM<4>

4

FBADQM<5>

5

FBADQM<6>

6

FBADQM<7>

7

FBADQS<4>

4

FBADQS<5>

5

FBADQS<6>

6

FBADQS<7>

7

FBADQSN<4>

4

FBADQSN<5>

5

FBADQSN<6>

6

FBADQSN<7>

7

M8

16MX16DDR2-2.5

BGA84

CHANGED

K7

L7

K3

L8FBACMD<8>

M8

M3

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

FBAD<32>

FBAD<33>

FBAD<34>

FBAD<35>

FBAD<36>

FBAD<37>

FBAD<38>

FBAD<39>

FBADQM<4>

FBADQS<4>

FBADQSN<4>

FBAD<40>

FBAD<41>

FBAD<42>

FBAD<43>

FBAD<44>

FBAD<45>

FBAD<46>

FBAD<47>

FBADQM<5>

FBADQS<5>

FBADQSN<5>

A1

E1

J9

M9

R1

A9

C1

C3

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

J2

D1

D3

C2

B1

D7

B9

D9

C8

B3

B7

A8

F1

H9

G8

F9

H7

H1

G2

H3

F3

F7

E8

FBVDDQ

GND

FBVDDQ

VREF_A

GND

3

M7

16MX16DDR2-2.5

BGA84

CHANGED

M8

16MX16DDR2-2.5

BGA84

CHANGED

C518

.047UF

16V

10%

X7R

0402

COMMON

R506

1K

1%

0402

COMMON

3.3F< 3.4D>

5.2A<

SUBPARTITION BITS ---->

R511

1K

1%

0402

COMMON

GND

FBACLK1

2

M7

16MX16DDR2-2.5

BGA84

CHANGED

F1

G2

H3

H1

F9

H7

H9

G8

F3

F7

E8

M8

16MX16DDR2-2.5

BGA84

CHANGED

D1

D9

B1

C2

D3

C8

B9

D7

B3

B7

A8

K7

L7

K3

L8

M8

M3

N2

N8

N3

N7

P2

P8

P3

M2

P7

R2

R8

R3

R7

L2

L3

L1

K2

J8

K8

K9

A2

E2

USED ONLY FOR 1GB DEVICES ---->

FBACLK1

FBACLK1*

5.3F< 5.1H>

FBVDDQ

FBACLK_C1

60.4

R74

CHANGED

0402

1%

13

4

5

6

C86

.01UF

25V

10%

X7R

0402

COMMON

GND

FBACMD<15>

15

FBACMD<25>

25

FBACMD<9>

9

FBACMD<8>

8

FBACMD<1>

1

FBACMD<3>

3

FBACMD<13>

FBACMD<4>

FBACMD<5>

FBACMD<6>

FBACMD<21>

21

FBACMD<23>

23

FBACMD<19>

19

FBACMD<20>

20

FBACMD<17>

17

FBACMD<16>

16

FBACMD<14>

14

SNN_U9_FBAA<13>

SNN_U9_FBAA<14>

SNN_U9_FBAA<15>

FBACMD<10>

10

FBACMD<18>

18

FBACMD<7>

7

FBACMD<11>

11

FBACMD<12>

12

SNN_U9_A2

SNN_U9_E2

FBAD<48>

48

FBAD<49>

49

FBAD<50>

50

FBAD<51>

51

FBAD<52>

52

FBAD<53>

53

FBAD<54>

54

FBAD<55>

55

FBADQM<6>

FBADQS<6>

FBADQSN<6>

FBAD<56>

56

FBAD<57>

57

FBAD<58>

58

FBAD<59>

59

FBAD<60>

60

FBAD<61>

61

FBAD<62>

62

FBAD<63>

63

FBADQM<7>

FBADQS<7>

FBADQSN<7>

FBACLK1*

60.4

R78

CHANGED

0402

1%

C78

.01UF

25V

10%

X7R

0402

COMMON

P403-A00 G84-200 450/400MHz 256MB 16Mx16 BGA84 GDDR2 DVI-I-DL+VGA+HDTV-Out

FBA 16Mx16 DDR2 MEMORIES, 1ST BANK 32..63

www.vinafix.vn

M7

16MX16DDR2-2.5

BGA84

CHANGED

5.2A<

3.3F<

3.4D>

4.1A< 3.2D> 3.4F<

SUBPARTITION BITS ---->

USED ONLY FOR 1GB DEVICES ---->

5.5C<

5.5E<

4.3A<> 3.4F<>

4.3A< 3.4F<

FBVDDQ

A1

E1

J9

M9

R1

A9

C1M7

C3

C7

C9

E9

G1

G3

G7

G9

J1

A3

E3

J3

N1

GND

P9

A7

B2

B8

D2

D8

E7

F2

F8

H2

H8

J7

GND

VREF_A

C516

.047UF

16V

10%

X7R

0402

COMMON

5.3D> 5.1H>

J2

FBVDDQ

GND

FBVDDQ

GND

C542

1UF

6.3V

10%

X5R

0402

C544

.01UF

25V

10%

X7R

0402

COMMON

C556

1UF

6.3V

10%

X5R

0402

COMMONCOMMON

C555

1UF

6.3V

10%

X5R

0402

COMMON

C527

.01UF

25V

10%

X7R

0402

COMMON

C536

.1UF

16V

10%

X7R

0402

COMMON

C532

.1UF

16V

10%

X7R

0402

COMMON

C543

.1UF

16V

10%

X7R

0402

COMMON

C551

.1UF

16V

10%

X7R

0402

COMMON

C528

4.7UF

6.3V

10%

X5R

0603

CHANGED

FBVDDQ

C537

1UF

16V

10%

X5R

0603

COMMON

C533

4.7UF

6.3V

10%

X5R

0603

CHANGED

C553

6.3V

10%

X5R

0402

COMMON

C550

.1UF1UF

16V

10%

X7R

0402

COMMON

C546

.1UF

16V

10%

X7R

0402

COMMON

GND

FBVDDQ

GND

C520

.1UF

16V

10%

X7R

0402

COMMON

1UF

6.3V

10%

X5R

0402

COMMON

C545

1UF

6.3V

10%

X5R

0402

COMMON

C557

.01UFC558

25V

10%

X7R

0402

COMMON

C531

.01UF

25V

10%

X7R

0402

COMMON

600-10403-0001-100 A

p403_a01

hlu

5 OF 22

11-DEC-2006

INININININININININININININININ

OUT

OUT

OUT

OUT

OUT

BI

3/14 FBC

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBVTT

FBC_CMD0

FBC_CMD4

FBC_CMD3

FBC_CMD2

FBC_CMD1

FBC_CMD5

FBC_CMD6

FBC_CMD7

FBC_CMD8

FBC_CMD9

FBC_CMD10

FBC_CMD11

FBC_CMD12

FBC_CMD13

FBC_CMD14

FBC_CMD15

FBC_CMD16

FBC_CMD17

FBC_CMD18

FBC_CMD19

FBC_CMD20

FBC_CMD21

FBC_CMD22

FBC_CMD23

FBC_CMD24

FBC_CMD25

FBC_CMD26

FBC_PLLAVDD

FBC_PLLVDD

FBC_DEBUG

FBC_CLK1

FBC_CLK1

FBC_CLK0

FBC_CLK0

FBC_CMD28

FBC_CMD27

FBCAL_TERM_GND

FBCAL_PU_GND

FBCAL_PD_VDDQ

FBC_PLLGND

FBCD10

FBCD11

FBCD12

FBCD13

FBCD14

FBCD15

FBCD0

FBCD1

FBCD2

FBCD3

FBCD4

FBCD5

FBCD6

FBCD7

FBCD8

FBCD9

FBCD16

FBCD17

FBCD18

FBCD19

FBCD20

FBCD21

FBCD22

FBCD23

FBCD24

FBCD25

FBCD26

FBCD27

FBCD28

FBCD29

FBCD30

FBCD31

FBCD32

FBCD33

FBCD34

FBCD35

FBCD36

FBCD37

FBCD38

FBCD39

FBCD40

FBCD41

FBCD42

FBCD43

FBCD44

FBCD45

FBCD46

FBCD47

FBCD48

FBCD49

FBCD50

FBCD51

FBCD52

FBCD53

FBCD54

FBCD55

FBCD56

FBCD57

FBCD58

FBCD59

FBCD60

FBCD61

FBCD62

FBCD63

FBCDQM0

FBCDQM1

FBCDQM2

FBCDQM3

FBCDQM4

FBCDQM5

FBCDQM6

FBCDQM7

FBCDQS_WP0

FBCDQS_WP1

FBCDQS_WP2

FBCDQS_WP3

FBCDQS_WP4

FBCDQS_WP5

FBCDQS_WP6

FBCDQS_WP7

FBCDQS_RN0

FBCDQS_RN1

FBCDQS_RN2

FBCDQS_RN3

FBCDQS_RN4

FBCDQS_RN7

FBCDQS_RN6

FBCDQS_RN5

FB_VREF2

OUTBIBI

2

3

4

5

1

HGF

DATE

PAGE

NVIDIA CORPORATION

2701 SAN TOMAS EXPRESSWAY

SANTA CLARA, CA 95050, USA

NAME

ID

NV_PN

D E

PAGE DETAIL

ASSEMBLY

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

CB

2

1

A

5

4

3

HFD GEBA C

8.3B<

8.4B<

8.4B<

6.3A<>

6.4A<>

GND

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

0402X4

C768

1UF

6.3V

10%

X7R

0603

NO STUFF

DDR2 OPERATION:

1) During initialization CKE and ODT low

2) Runtime .. CKE high and ODT operated by debug state machine

3) No termination rpak for CKE or DEBUG pins

RP1

RP1

RP7

RP7

RP4

RP4

RP6

RP6

1

+/-5%

2

+/-5%

2

+/-5%

1

+/-5%

4

+/-5%

3

+/-5%

2

+/-5%

1

+/-5%

150

8

COMMON

150

7

COMMON

150

7

COMMON

150

8

COMMON

150

5

COMMON

150

6

COMMON

150

7

COMMON

150