A B C

Dell Controlled Print

D

REVISIONS

1

2

3

REV

A00-00

A01-00

A02-00

A03-00

ECO161177

ECO168386

ECO168401

ECO173798

DESCRIPTIONECO DATE

RELEASE FOR P1355 TO J9621 CAPACITOR CHANGE

TABLE OF CONTENTS

Page 1.

Page 2.

Page 3.

Page 4.

Page 5.

Page 6.

Page 7.

Page 8.

Page 9.

Page 10.

Page 11.

Page 12.

Page 13.

Page 14.

Page 15.

Page 16.

Page 17.

Page 18.

Page 19.

Page 20.

Page 21.

Page 22.

Page 23.

Page 24.

Page 25.

Page 26.

Page 27.

Page 28.

Page 29.

Page 30.

Page 31.

Page 32.

Page 33.

Page 34.

Page 35.

Page 36.

Page 37.

Page 38.

Page 39.

Page 40.

Page 41.

Page 42.

Page 43.

Page 44.

Page 45.

Page 46.

Page 47.

Page 48.

Page 49.

Page 50.

Page 51.

Page 52.

Page 53.

Page 54.

Page 55. FWH

Page 56.

Page 57.

Page 58.

Page 59.

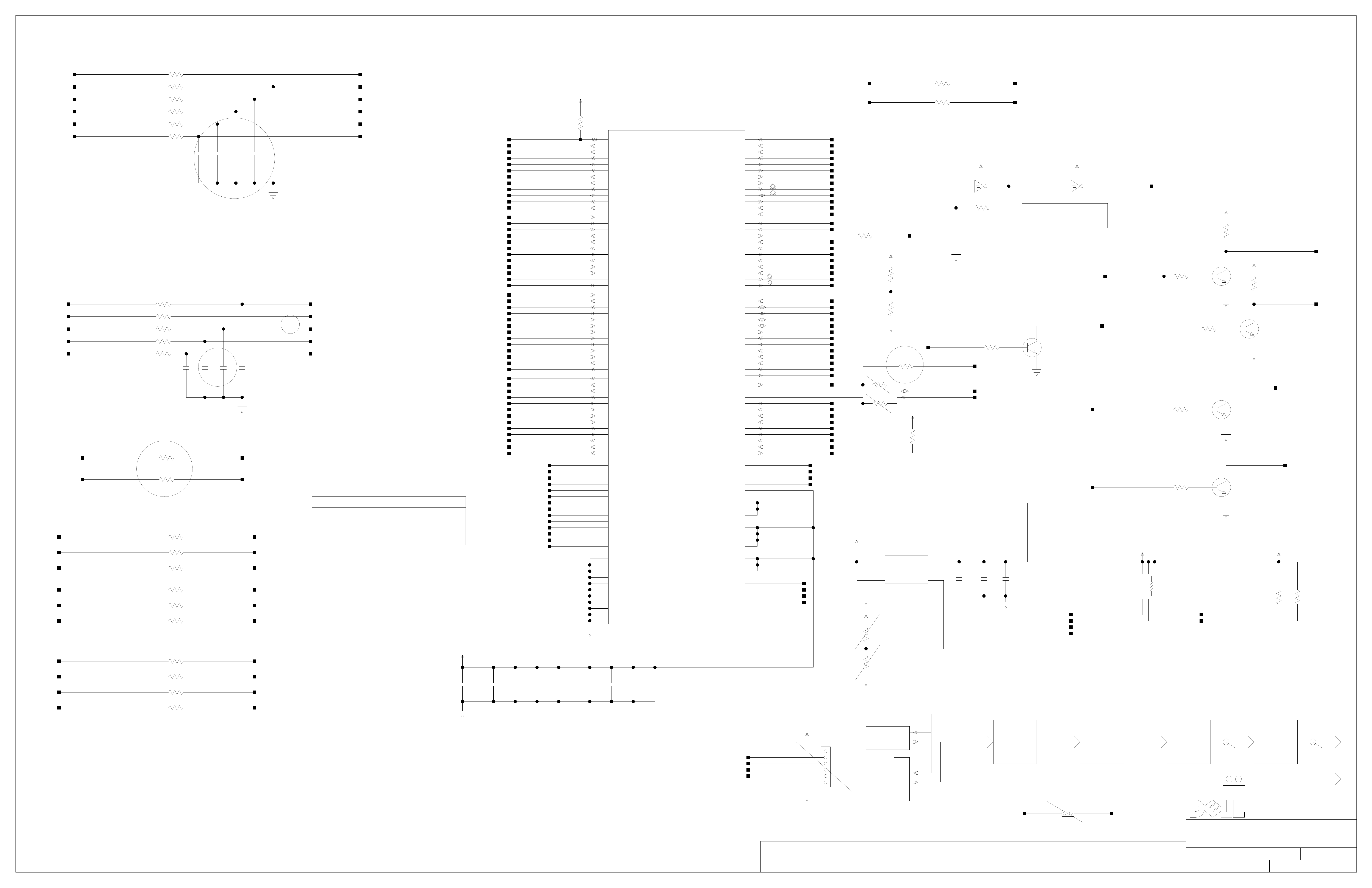

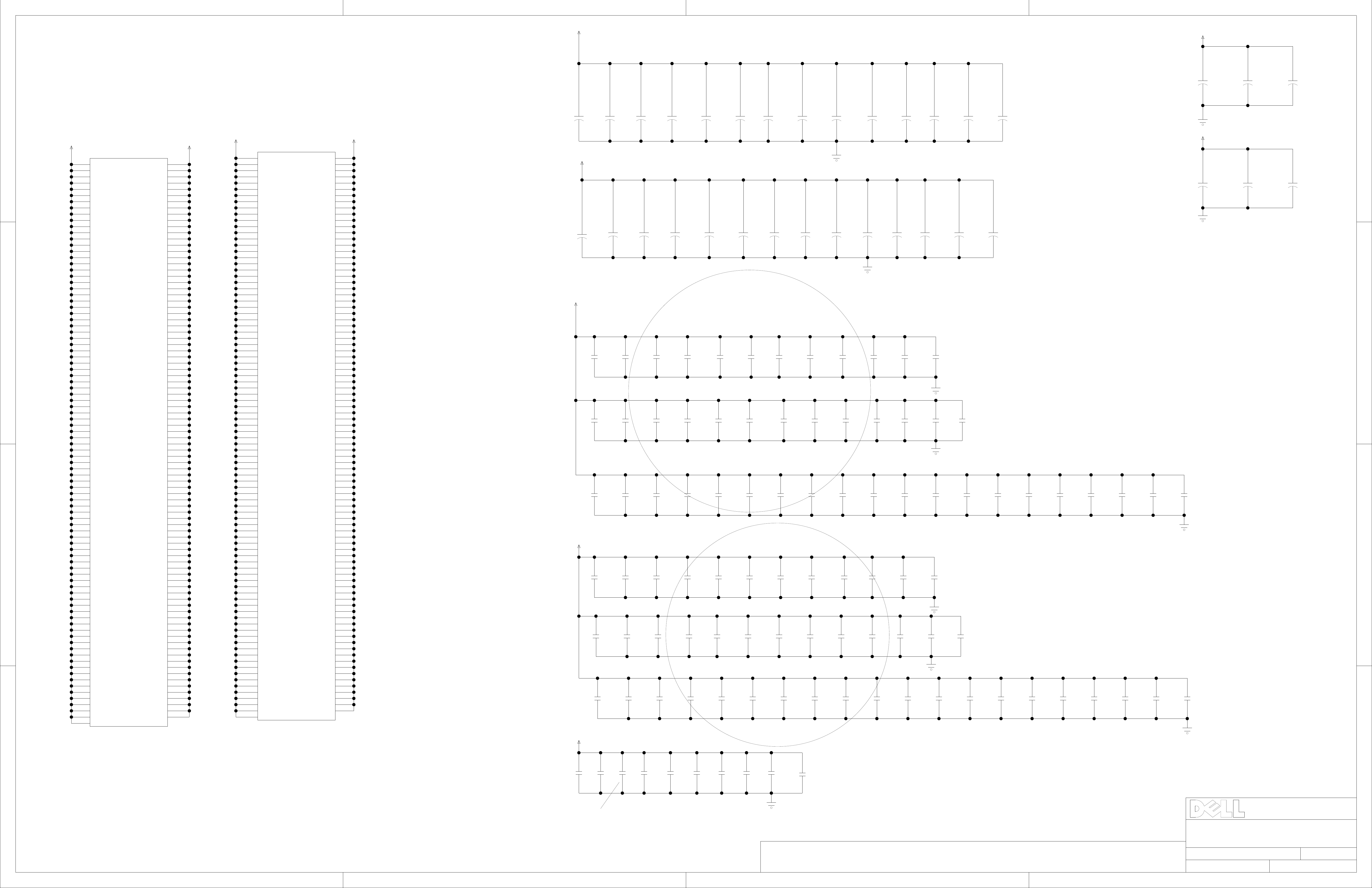

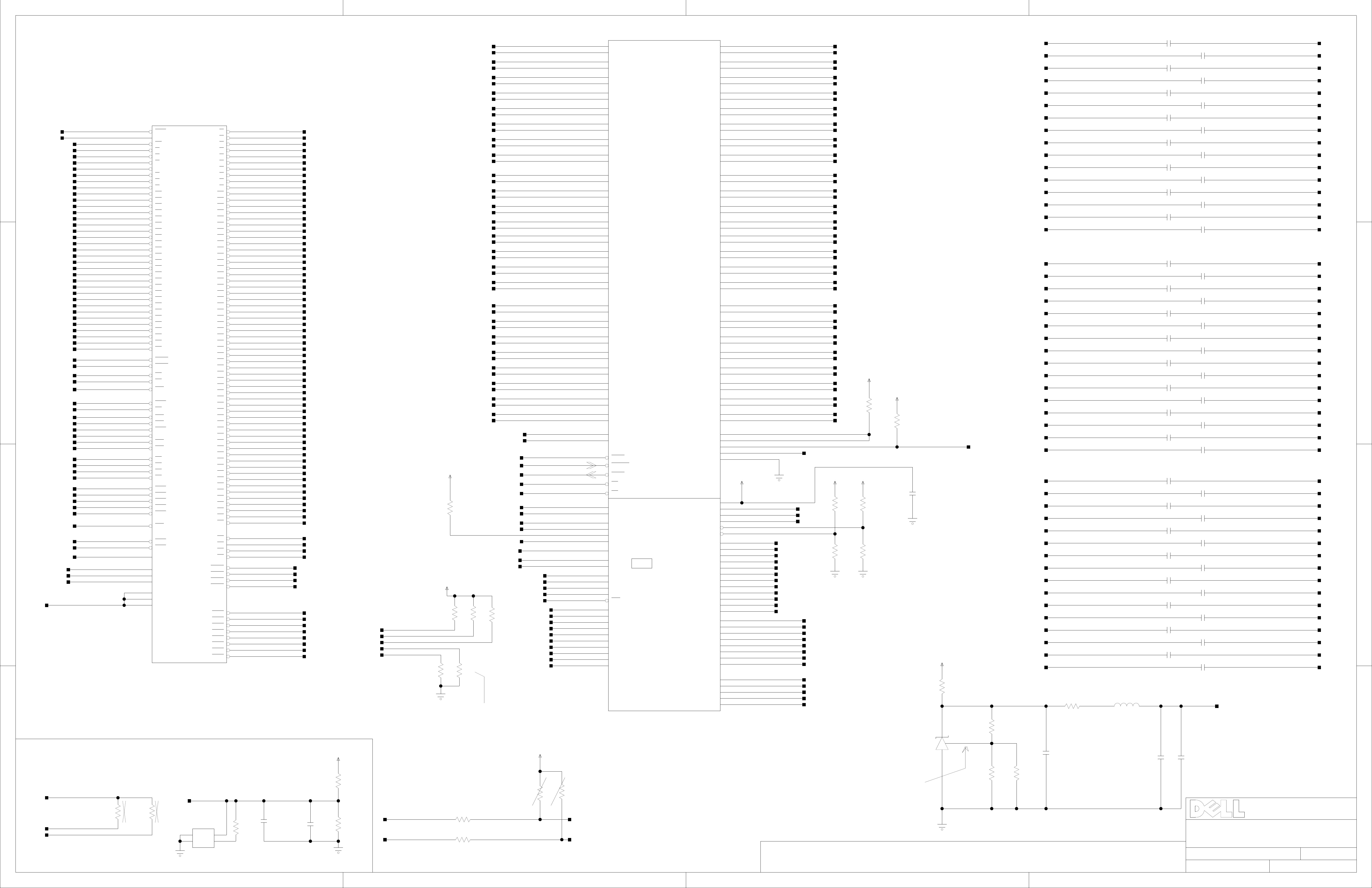

BLOCK DIAGRAM

CLOCK DIAGRAM

Clock Synth.

Differential Buffer DB800

System CPLD

Voltage Regulators

VRD

VRD

VRD

---blank--Processors

Processors

Processors

---blank--ITP 32 & Level Translation Circuits

MCH, memory

MCH, GTL, Exp, Hub-link

MCH, power

Decoupling Caps

DDR2

DDR2

DDR2, routing diagram

DDR2, VRef

Gigabit Ethernet

Gigabit Ethernet

Gigabit Ethernet

PXH

PXH

PXH

PXH

Connectors

Connectors

ICH5

ICH5

Keyboard, Mouse, COM Ports, I2C MUX/Table

Radeon Video

Radeon Video

Radeon Video

Radeon Video

Super I/O, 373

Battery / Intrusion Detect / RAID Key / VAux Pwrgood

Fans and fan LED's

Parallel Port / ID Button / Rear Cyclops / Speaker

BMC

BMC

BMC

BMC

BMC, Serial Port Muxing

BMC - Serial Port MUXing Diagram

RAC

1.2V Vtt generation

Fan PWM Controllers

MicroVu

VAux reset

USB / Buttons

Spares / Coupons / Hardware

PCI bus p/u's / PCI Debug Slot

Debug Features

06/23/2004RELEASE FOR PRODUCTION

10/21/2004RELEASE Q4/2004 BLOCK

12/17/2004

APPROVED

JIM HUNT

JIM HUNT

1

2

3

4

1U PWA assembly

2U/5U PWA assembly

P# D8266

P# H1754

XLBOM Build Options

1U, Production

2U/5U Production

0

1

21U, Debug

2U/5U Debug

EXPORT RESTRICTION:

THE EXPORT OF THE INFORMATION, SCHEMATICS AND OTHER TECHNICAL DATA CONTAINED IN THIS DOCUMENT

IS CONTROLLED BY THE U.S. GOVERNMENT. THE EXPORT, DEEMED EXPORT OR OTHER TRANSFER OF THIS DATA

TO CERTAIN COUNTRIES AND INDIVIDUALS IS RESTRICTED. ANY TRANSFER, EXPORT OR REEXPORT, MUST BE

IN COMPLIANCE WITH THE U.S. EXPORT ADMINISTRATION REGULATIONS.

3

PWB/Silk Color

Red White

Blue x01

White

x00

Clear White x02

Green Yellow x03

White x03Green

Green White a00

Big Bend, Kobuk, Corvette

PWA: H1754

PWB:

SCHEM:

ASSY DWG:

THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS

AND CONTAINS CONFIDENTIAL AND TRADE SECRET INFORMATION. THIS

ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC.,

EXCEPT AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY

OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN

WHOLE OR IN PART AND MUST BE RETURNED TO DELL INC.

UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE

OF THE LOAN. NEITHER THIS ITEM NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED

FOR SUCH USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE

LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

D1656

D1660

D1657

PROPRIETARY NOTE

UNIPLANAR

aka LINDY PLANAR

DRAWN

Uniplanar Team:

DESIGNED

CHECKED

APPROVED

-Shawn Dube

APPROVED

-Jinsaku Masuyama

APPROVED

-Garnett Thompson

APPROVED

-TJ Thompson

RELEASED

XLBOM Build option table

0 Production Build

9 Prototype Build

A CURRENT ISSUE OF THIS DRAWING MUST

INCLUDE A COPY OF THE FOLLOWING

ECO'S:

ECO

ECO

ECO

ECO

ECO

ECO

ECO

ECO

TITLE

SCHEM,PLN,SV,PE2800/2850/1850

DWG NO.

DATE

DATE

DATE

DATE

DATE

DATE

DATE

DATE

INC.

D1660

DATE

12/16/2004 1 OF 60

4

ROUND ROCK,TEXAS

REV.

A03-00

SHEET

DCBA

B D

CA

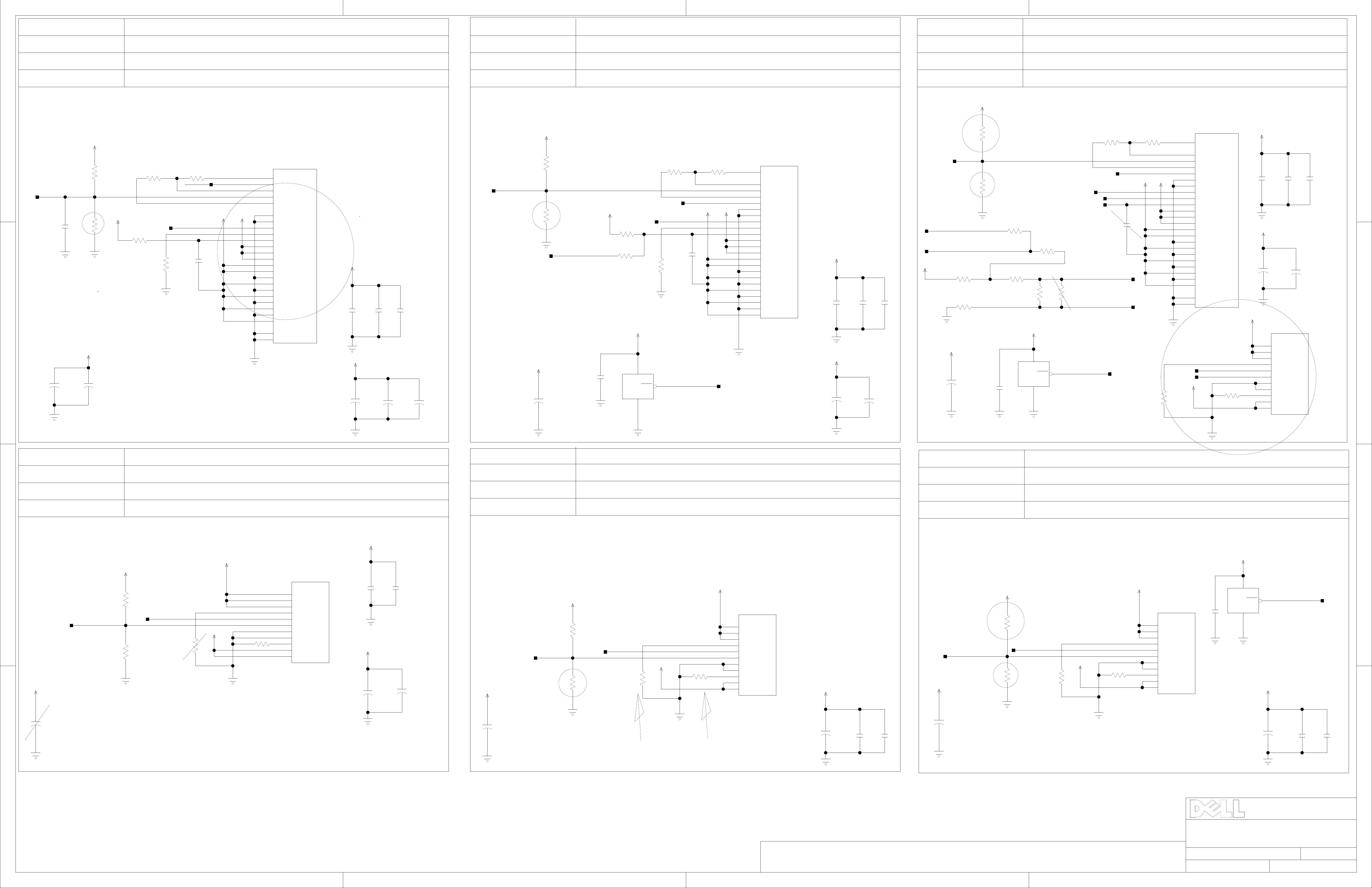

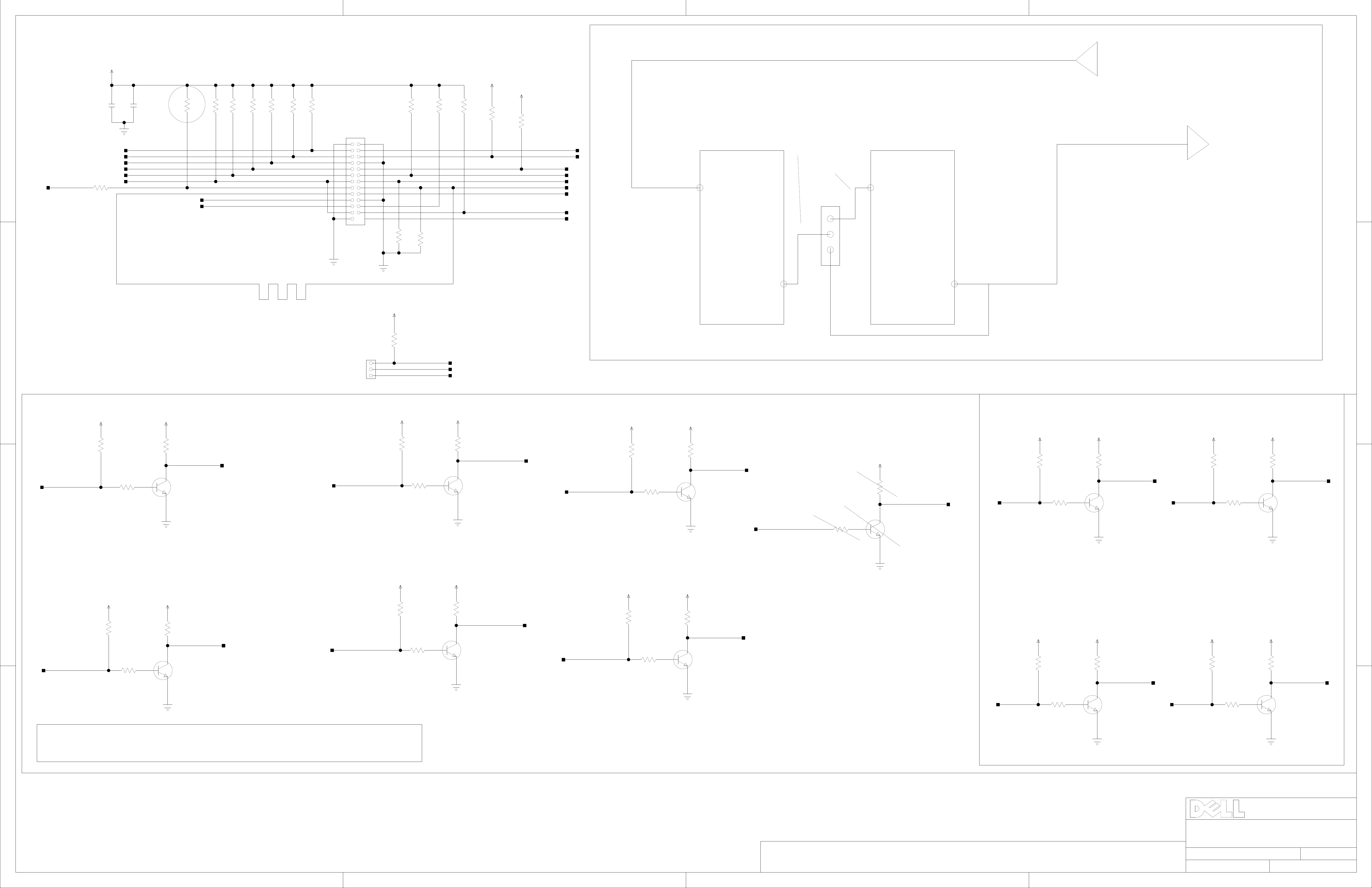

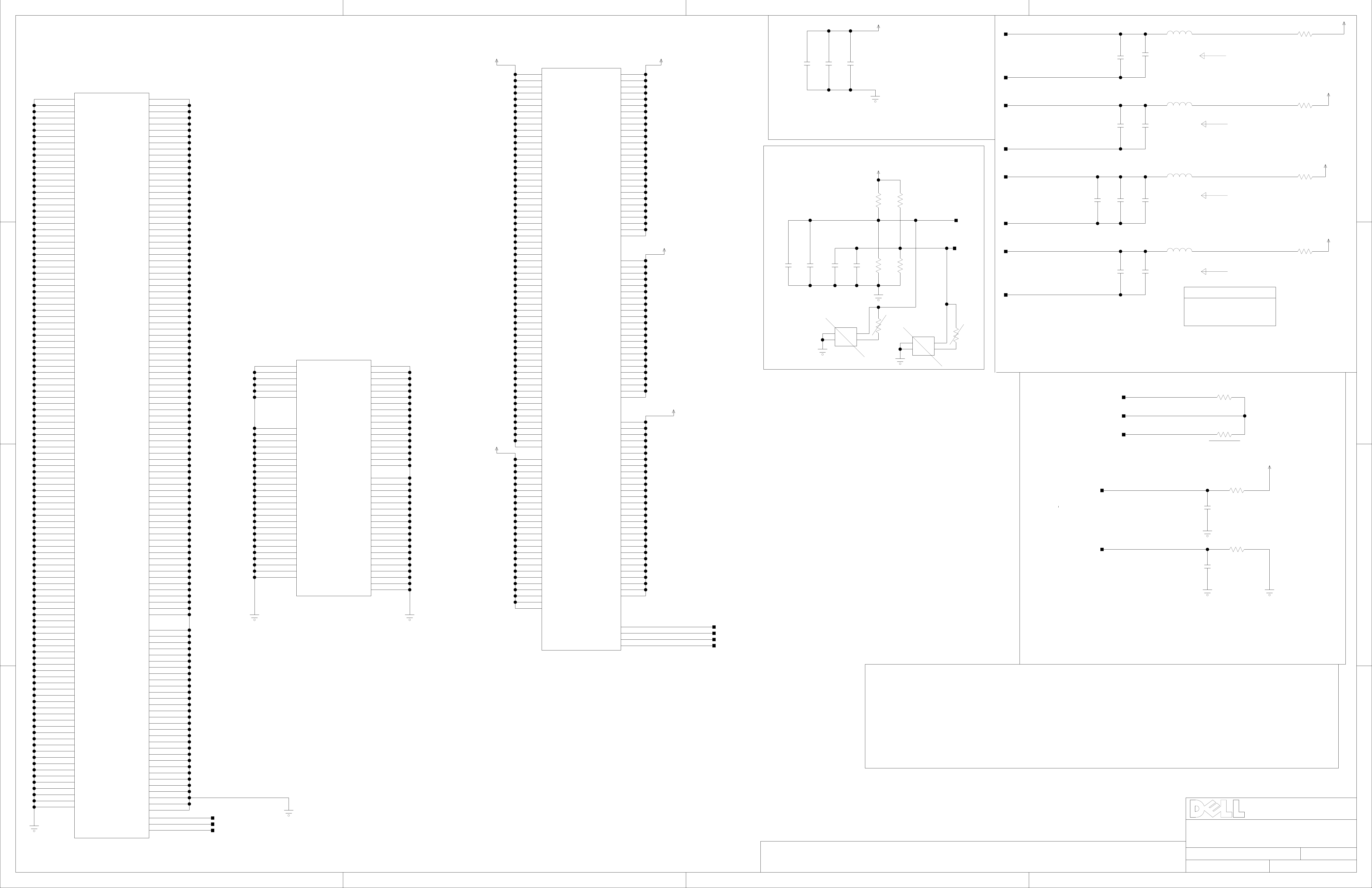

CLOCK DISTRIBUTION

BLOCK DIAGRAM

12-16-2004_19:50

1

1

2

2

3

3

4 4

INC.

ROUND ROCK,TEXAS

TITLE

SCHEM,PLN,SV,PE2800/2850/1850

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

D1660

12/16/2004

REV.

A03-00

SHEET

2 OF 60

DC

A B

B D

V_3P3_CLK

3

21

CA

12-16-2004_19:50

1

+3.3V

1 2

C1093

BLM18BD601SN1

BLM18BD601SN1

0.1uF 16V

L103

L105

R1476

R1420

21

4,35

4,35

21

V_3P3_CLK

3

21

21

1 2

C1094

0.1uF 16V

C1209

C1103

10uF 6.3V

1 2

0.1uF 16V

1 2

C1102

C1101

0.1uF 16V

1 2

0.1uF 16V

1 2

C1100

C1104

0.1uF 16V

1 2

0.1uF 16V

1 2

C1099

1 2

C1098

0.1uF 16V

C1096

0.1uF 16V

1 2

0.1uF 16V

1 2

C1097

0.1uF 16V

ICH_SEG2_SDA

ICH_SEG2_SCL

0-5%

R1421

1 2

0-5%

ICH_SEG2_409_SDA

ICH_SEG2_409_SCL

4.7K

NP*

R1477

4.7K

1 2

NP*

3

ECAD Note:

VCC routing should be from plane, through high-f cap, to pin

3

1

2

3

U1084

300 ohm, 25%, 300mA, 1206

Vishay ILB1206RK301V

KOA CZB2BFL-301P

3

May need to tune caps during UT

V_3P3_CLK

C757

21

0.1uF 16V

50V-10%

27pF

x03_tj_121503

NP

2 1

C1090

R606

21

2.2-5%

X10

1 2

14.31818MHz

R947

2 1

1M-5%

X

50V-10%

C756

27pF

21

0.1uF 16V

12

C759

C1091

21

+3.3V

1 2

C1105

0.1uF 16V

10uF 6.3V

x00_tj_050503

SUB*_U1084

L129

1 2

ILB_1206

300OHM, 300 mA

5

CK_FSB

5

1 2

C1092

V_3P3_CLK_VDD48

CK_FSA

V_3P3_CLK_VDDA

C758

1 2

0.1uF 16V

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MIL

10uF 6.3V

R1419

21

0-5%

R1002

R1022

1 2

0-5%

4,5,59

12

475-1%

IREF = 2.32mA

x02_sd

21

R46

PROPAGATION_DELAY=L:S::1000

NET_PHYSICAL_TYPE=50MIL

5,59

4.7K

R1008

1 2

CK_VTT_PWRGD_N

CK_PWRDWN_N

21

C1326

X

0.1uF 16V

NP*

4.7K

R1018

1 2

NP*

R1007

x00_tj_051203

R1475

4.7K

1 2

3

3

21

1K-1%

C778

1 2

PART_NUMBER=79015

4.7K

21

C779

PART_NUMBER=79015

CK_XTAL_IN

CK_XTAL_OUT

CK_FSA_R

CK_FSB_R

CK_IREF

ICH_SEG2_409_SDA

ICH_SEG2_409_SCL

C777

1000pF

50V-10%

1000pF

50V-10%

PART_NUMBER=79015

C780

21

1000pF

50V-10%

3

10

16

24

55

34

42

48

36

1000pF

1 2

PART_NUMBER=79015

50V-10%

4

5

51

56

52

35

21

30

28

6

11

17

25

39

33

53

45

54

x00_tj_052003

CK409B

VDD_REF

VDD_PCI_1

VDD_PCI_2

VDD_3V66

VDD_ANLG

VDD_48MHZ

VDD_CPU_1

VDD_CPU_2

VDD_SRC

XTALIN

XTALOUT

FS_A

FS_B

IREF

VTT_PWRGD

PWR_DOWN

SDATA

SCLK

GND_REF

GND_PCI_1

GND_PCI_2

GND_3V66

GND_SRC

GND_48MHZ

GND_IREF

GND_CPU

GND_ANLG

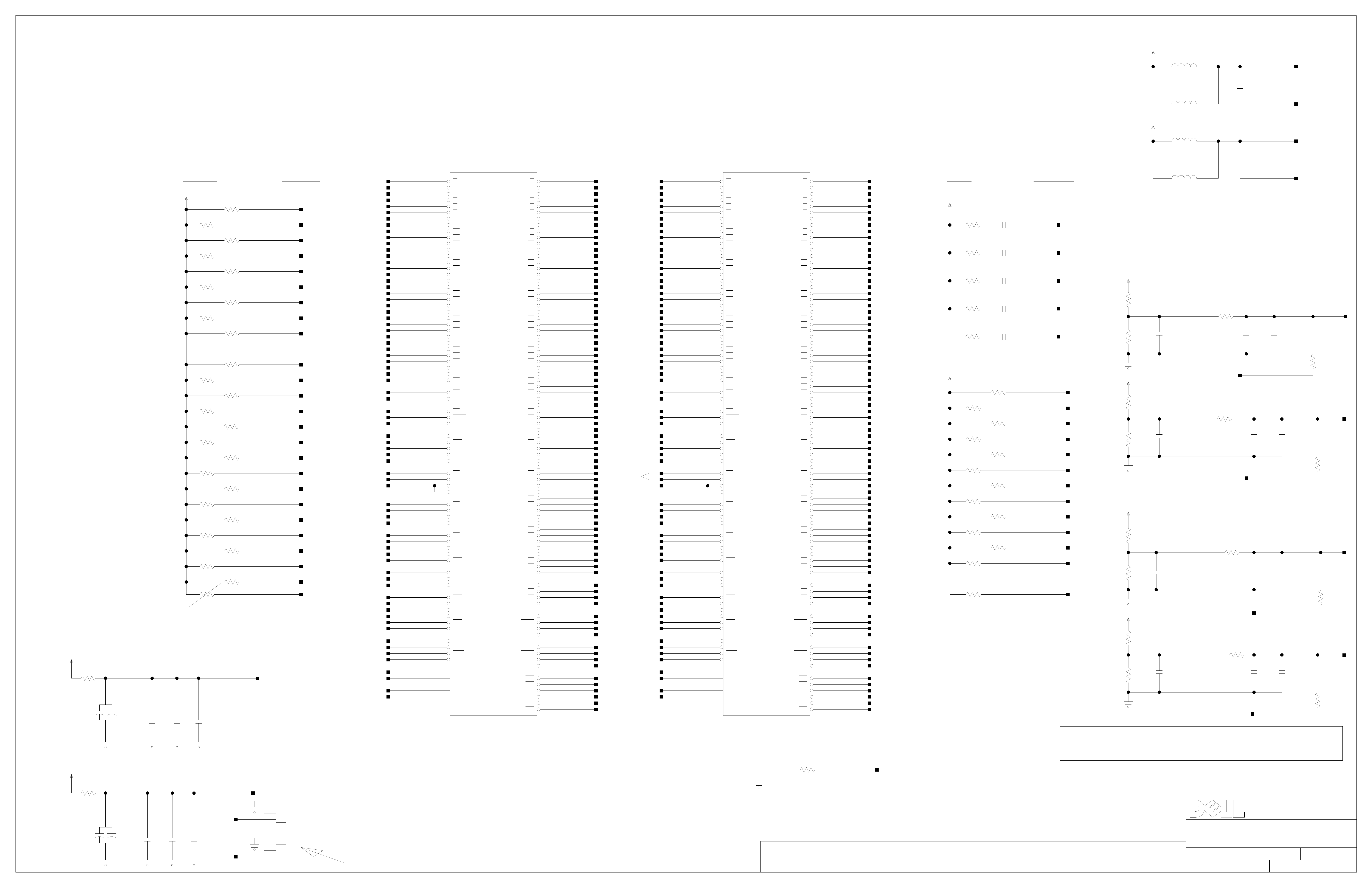

CK409 - TSSOP56

SMBus address = D2h

SUB*_W7296

x00c4_tj_090304

REF0

REF1

PCI_F0

PCI_F1

PCI_F2

PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

USB

DOT

SRC_P

SRC_N

3V66_0

3V66_1

3V66_2

3V66_3

3V66_4/VCH

CPU_P0

CPU_N0

CPU_P1

CPU_N1

CPU_P2

CPU_N2

CPU_P3

CPU_N3

1

2

7

8

9

12

13

14

15

18

19

20

31

32

38

37

22

23

26

27

29

41

40

44

43

47

46

50

49

CK_14M_ICHS_R

CK_14M_SIO_R

CK_33M_ICHS_R

CK_33M_SIO_R

CK_33M_FWH_R

CK_33M_SLOT3_R

CK_33M_PCI0_DEBUG_R

CK_33M_BMC_R

CK_33M_CPLD_R

CK_33M_DBG_LPC_R

CK_33M_VIDEO_R

CK_33M_RAC_R

CK_48M_USB_ICHS_R

CK_48M_SIO_R

CK_66M_MCH_R

CK_66M_ICH_R

CK_66M_3V66_2

CK_66M_LAI_R

CK_167M_CPU1_P_R

CK_167M_CPU1_N_R

CK_167M_CPU2_P_R

CK_167M_CPU2_N_R

CK_167M_MCH_P_R

CK_167M_MCH_N_R

CK_167M_ITP_P_R

CK_167M_ITP_N_R

CK_100M_DB800_P_R

CK_100M_DB800_N_R

1 2

R1017

21

1K-1%

R1417

1K-1%

R956

1 2

33-5%

R957

1 2

33-5%

R1361

1 2

33-5%

+3.3V

NP*

R593

1K-1%

R964

CK_14M_ICHS

CK_14M_SIO

33

40

33-5%

R955

33-5%

R954

33-5%

R1362

1 2

33-5%

R949

33-5%

R1416

21

21

21

21

21

CK_33M_ICHS

CK_33M_SIO

CK_33M_FWH

CK_33M_SLOT1

CK_33M_PCI0_DEBUG

55

33

40

x00_tj_051503

31

58

2

1K-1%

R1363

33-5%

R959

21

NC_CK_48M_SIO

R962

21

33-5%

R963

21

33-5%

21

CK-409 support

Place close to ICH

21

R1429

1 2

33-5%

21

R1712

49.9-1%

CK_100M_DB800_P

CK_100M_DB800_N

49.9-1%

33-5%

R965

33-5%

R966

33-5%

R967

33-5%

CK_48M_USB_ICHS

R960

33-5%

R961

21

R952

33-5%

21

R968

33-5%

21

R969

33-5%

21

R1036

21

21

21

21

21

49.9-1%

33

4

4

21

R1039

49.9-1%

21

21

21

R1038

49.9-1%

21

R1364

1 2

33-5%

R1366

33-5%

R1367

1 2

33-5%

33-5%

R38

NP*

21

21

21

CK_33M_BMC

CK_33M_CPLD

CK_33M_SMARTVU

CK_33M_VIDEO

CK_33M_RAC

CK_66M_MCH

CK_66M_ICH

CK_167M_CPU1_P

CK_167M_CPU1_N

CK_167M_CPU2_P

CK_167M_CPU2_N

CK_167M_MCH_P

CK_167M_MCH_N

44

5,59

59

36

50

To CPLD and Mictor header

17

33

11

11

11

11

17

17

3

Spread spectrum Controlled through I2C

CK409B / CK409 Operation

FSA

FSB SPEEDFSB

All clk _R nets have a hidden prop-delay max of 500mil

R1473

1 2

4.7K

POP01

R1474

4.7K

POP01

CPU_STOP#

PCI_STOP#

Pop 33ohm, 49.9ohm if CK409B used

NP01

Populate with CK409B (ITP diferential pair)

Differential pair routing guideline:

6 mil traces / 14 mil spacing

Spacing to other traces: 5W

NP01

R950

33-5%

R1034

1 2

R1040

49.9-1%

49.9-1%

CK_167M_ITP_P

CK_167M_ITP_N

15

15

R1037

49.9-1%

R951

21

33-5%

21

NP01

R1035

49.9-1%

21

R1033

49.9-1%

NP01

0

1

0

10

0

11

100 MHz

200 MHz

133 MHz

166 MHz

4 4

ROOM=CLOCK1

Freq. latched on VTT_PWRGD

INC.

ROUND ROCK,TEXAS

TITLE

SCHEM,PLN,SV,PE2800/2850/1850

DWG NO.

D1660

DATE

12/16/2004

REV.

A03-00

SHEET

3 OF 60

subsys done

Clock CK409B

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

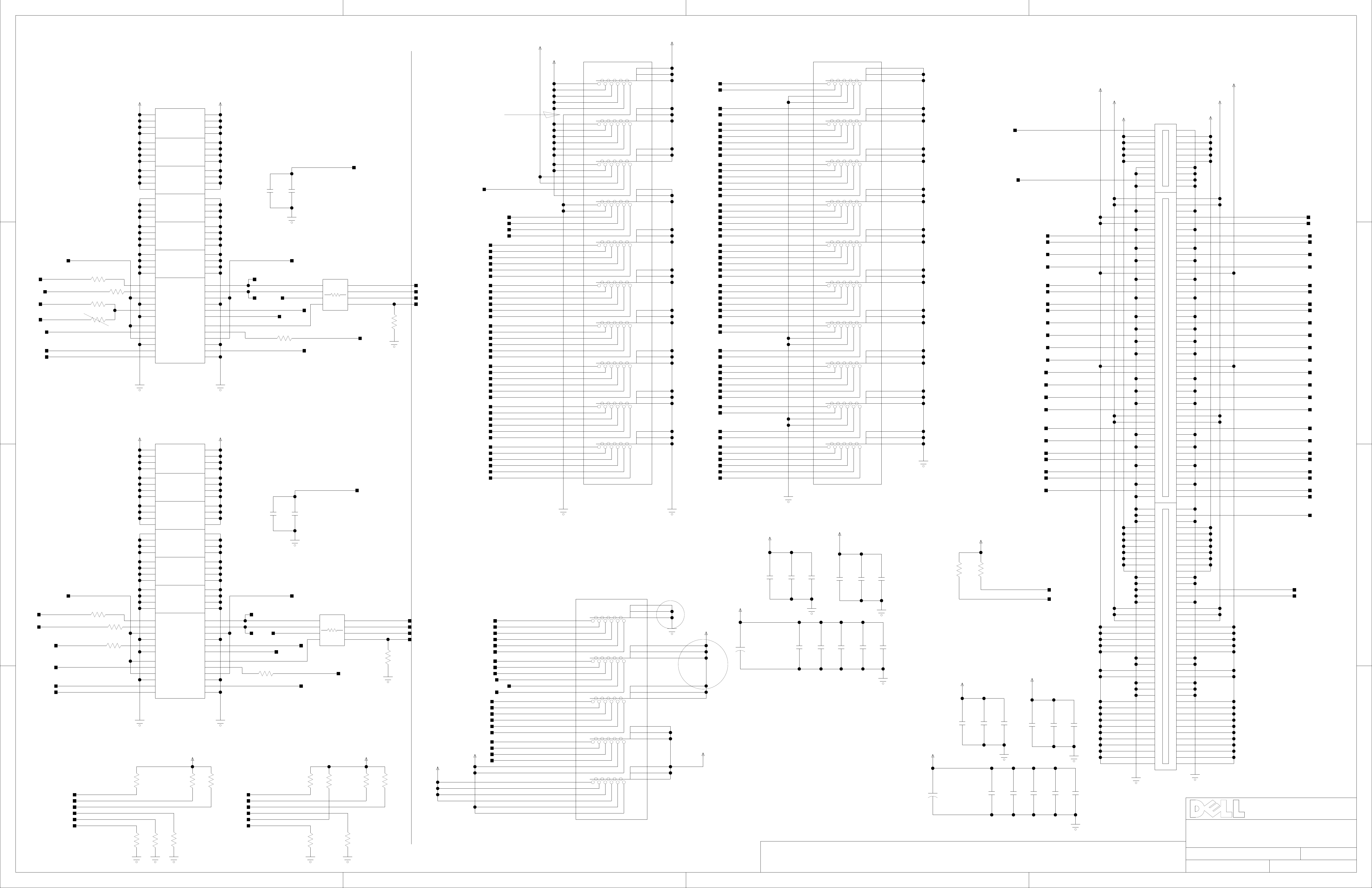

A B

DC

B D

CA

12-16-2004_19:50

1

3,35

3,35

ICH_SEG2_SDA

ICH_SEG2_SCL

R1423

0-5%

R1422

1 2

0-5%

4

21

ICH_SEG2_800_SDA

ICH_SEG2_800_SCL

V_3P3_SRC

21

R1479

4.7K

NP*

R1478

1 2

1

4.7K

NP*

4

4

2

3

V_3P3_SRC

4

DB800_OE0

4

DB800_OE4

4

DB800_OE5

4

4,31

4,31

x00_sd_051703

SLOT7_PWRGD

SLOT6_PWRGD

21

R111

NP

R100

X

1 2

21

R112

8.2K-5%

NP

21

R101

1K-1%

X

R113

8.2K-5%

1 2

NP

R103

1K-1%

X

1 2

21

R114

8.2K-5%

NP

21

R105

1K-1%

X

4

R115

8.2K-5%

1 2

NP

R107

1K-1%

X

1 2

V_3P3_SRC

8.2K-5%1K-1%

4

V_3P3_SRC

21

R592

+3.3V

1 2

C1114

R996

R591

8.2K-5%

1 2

0.1uF 16V

x00_tj_051203

21

10K-1%

21

R590

8.2K-5%

L108

BLM18BD601SN1

L107

BLM18BD601SN1

R999

10K-1%

1 2

8.2K-5%

21

21

R998

1 2

NP*

1 2

C1111

21

R997

10K-1%

X

C1327

21

0.1uF 16V

0.1uF 16V

NP

R1480

X

10K-1%

1 2

3,5,59

21

C1210

4.7K

x00_sd_051703

10uF 6.3V

1 2

C1110

CK_100M_DB800_N

3

CK_100M_DB800_P

3

ICH_SEG2_800_SCL

4

ICH_SEG2_800_SDA

4

CK_PWRDWN_N

DB800_OE0

4

DB800_OE4

4

DB800_OE5

4

4,31

4,31

SLOT7_PWRGD

SLOT6_PWRGD

1 2

C1109

0.1uF 16V

SRC_BYPASS/PLL

SRC_PLL_LOW_BW

SRC_STOP_N

SRC_DIV2_N

NC_SRC_LOCK

C1108

0.1uF 16V

1 2

0.1uF 16V

1 2

C1112

0.1uF 16V

1 2

C1113

C784

0.1uF 16V

PART_NUMBER=79015

DB800

5

SRC_IN

4

SRC_IN

23

SCLK

24

SDATA

22

BYPASS/PLL

28

PLL_BW

27

SRC_STOP

1

SRC_DIV2

26

PWRDWN

45

LOCK

6

OE_0

14

OE_1

15

OE_2

7

OE_3

43

OE_4

35

OE_5

36

OE_6

44

OE_7

3

GND_3

10

GND_10

18

GND_18

25

GND_25

32

GND_32

40

OE_INV/GND

47

GNDA

ICS9DB108

SMBus address = DCh

21

1000pF

50V-10%

x00_tj_051203

C786

1000pF

1 2

PART_NUMBER=79015

50V-10%

DIF_0

DIF_0

DIF_1

DIF_1

DIF_2

DIF_2

DIF_3

DIF_3

DIF_4

DIF_4

DIF_5

DIF_5

DIF_6

DIF_6

DIF_7

DIF_7

IREF

VDD_2

VDD_11

VDD_19

VDD_31

VDD_39

VDDA

8

9

12

13

16

17

20

21

30

29

34

33

38

37

42

41

46

2

11

19

31

39

48

Note: If clock ordering changes, BIOS requirements must change

V_3P3_SRC

CK_100M_SATA_P_R

CK_100M_SATA_N_R

CK_100M_MCH_P_R

CK_100M_MCH_N_R

CK_100M_PXH_PLANAR_P_R

CK_100M_PXH_PLANAR_N_R

CK_100M_DOBSON_P_R

CK_100M_DOBSON_N_R

CK_100M_PXH_P_R

CK_100M_PXH_N_R

CK_100M_EXP_LAI_P_R

CK_100M_EXP_LAI_N_R

CK_100M_SLOT1_P_R

CK_100M_SLOT1_N_R

CK_100M_SLOT2_P_R

CK_100M_SLOT2_N_R

R1003

1 2

475-1%

V_3P3_SRC

DB800_VDDA

21

0.1uF 16V

C1202

10uF 6.3V

4

4

x00_tj_050103

SUB*_U1084

1 2

ILB_1206

300OHM, 300 mA

C1107

12

L130

IREF = 2.32mA

+3.3V

0.1uF 16V

12

NP

1 2

33-5%

R977

1 2

33-5%

R980

1 2

33-5%

R975

1 2

33-5%

1 2

33-5%

1 2

33-5%

R1368

33-5%

R1370

33-5%

C1106

R976

R973

R971

X

NP

21

21

R978

1 2

X

33-5%

R979

1 2

33-5%

R981

1 2

33-5%

R974

1 2

33-5%

R972

1 2

33-5%

R970

1 2

33-5%

R1369

33-5%

R1371

21

33-5%

2

CK_100M_SATA_P

CK_100M_SATA_N

CK_100M_MCH_P

CK_100M_MCH_N

CK_100M_PXH_PLANAR_P

CK_100M_PXH_PLANAR_N

CK_100M_DOBSON_P

CK_100M_DOBSON_N

CK_100M_PXH_P

CK_100M_PXH_N

CK_100M_EXP_SPARE_P

CK_100M_EXP_SPARE_N

CK_100M_SLOT7_P

21

CK_100M_SLOT7_N

CK_100M_SLOT6_P

CK_100M_SLOT6_N

33

33

17

17

27

27

31

31

31

31

31

31

31

31

31

31

3

R1051

1 2

49.9-1%

R1052

1 2

R1050

1 2

49.9-1%

49.9-1%

R1049

1 2

R1048

1 2

49.9-1%

49.9-1%

R1047

1 2

R1046

1 2

49.9-1%

49.9-1%

R1045

1 2

R1044

1 2

49.9-1%

49.9-1%

R1043

1 2

R1042

1 2

49.9-1%

49.9-1%

R1041

1 2

21

R1434

49.9-1%

R1433

49.9-1%

21

21

R1432

49.9-1%

49.9-1%

21

R1431

49.9-1%

PROPAGATION_DELAY=L:S::500

NET_PHYSICAL_TYPE=50MIL

U1084

300 ohm, 25%, 300mA, 1206

Vishay ILB1206RK301V

KOA CZB2BFL-301P

1U Prod 2U/5U Prod 1U Proto 2U/5U Proto

SATAOE0

XXXX

OE1 MCH

X X X X

OE2

Planar PXH

X X X X

OE3

Dobson

X X

4 4

OE4

OE5

PXH

LAI

X X

ROOM=CLOCK2

X X

OE6

Slot1 ***Note--BIOS should disable for 2U

X X

OE7

Slot2

***Note--BIOS should disable for 2U

DB800 Differential buffer

INC.

ROUND ROCK,TEXAS

TITLE

subsys done

A B

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

SCHEM,PLN,SV,PE2800/2850/1850

DWG NO.

D1660

DATE

12/16/2004

DC

REV.

A03-00

SHEET

4 OF 60

1

2

3

5,59

5,59

5,59

5,59

5,59

5,59

46

SYSTEM_PWRGOOD_PXH_R

5

5

5

5

5

5,59

PCI_RST_RAC_N_R

5

PCI_RST_MCH_N_R

5

PCI_RST_PLANAR_N_R

5

PCI_RST_RISER_N_R

5

PCI_RST_BACKPLANE_N_R

5

SHIFTY_RISER_CLK_R

PROPAGATION_DELAY=L:S::2000

SHIFTY_RISER_LATCH_R

PROPAGATION_DELAY=L:S::2000

SHIFTY_RISER_DATA_DN_R

PROPAGATION_DELAY=L:S::2000

SHIFTY_BCKPLN_CLK_R

PROPAGATION_DELAY=L:S::2200

SHIFTY_BCKPLN_LATCH_R

PROPAGATION_DELAY=L:S::2200

SHIFTY_BCKPLN_DATA_DN_R

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_CLK_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_LATCH_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_DATA_DN_R

5

PROPAGATION_DELAY=L:S::2200

SHIFTY_BMC_DATA_UP_R

PROPAGATION_DELAY=L:S::2200

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_NIC_R

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_FETS_R

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_BACKPLANE_R

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_RISER_R

PROPAGATION_DELAY=L:S::2000

SYSTEM_PWRGOOD_CHIPSET_R

PROPAGATION_DELAY=L:S::2000

PROPAGATION_DELAY=L:S::2000

PROPAGATION_DELAY=L:S::2000

PROPAGATION_DELAY=L:S::2000

PROPAGATION_DELAY=L:S::2000

PROPAGATION_DELAY=L:S::2000

PCI_RST_PLANAR_N_R

5

PROPAGATION_DELAY=L:S::2000

PCI_RST_PLANAR_N_R

5

PROPAGATION_DELAY=L:S::2000

1 2

x03_GT_012604

1 2

33-5%

33-5%

1 2

33-5%

1 2

33-5%

33-5%

R6016

1 2

33-5%

R6017

1 2

33-5%

R1541

R1542

R1543

R1545

R1544

R1546

R6003

R6004

R6002

R6005

33-5%

1 2

33-5%

1K-5%

1 2

33-5%

33-5%

1 2

33-5%

R1381

R1377

21

R1378

R1379

R1380

21

50V-10%

470pF

33-5%

1 2

33-5%

33-5%

1 2

33-5%

33-5%

1 2

33-5%

33-5%

1 2

33-5%

33-5%

1 2

33-5%

R129

21

R1376

R1353

R1375

R1374

21

R1373

50V-10%

470pF

50V-10%

21

C1345

x03_GT_012604

x03b_GT_012204

PCI_RST_PXH_N

PCI_RST_DEBUG_N

21

SHIFTY_RISER_CLK

SHIFTY_RISER_LATCH

21

SHIFTY_RISER_DATA_DN

SHIFTY_BCKPLN_CLK

21

SHIFTY_BCKPLN_LATCH

SHIFTY_BCKPLN_DATA_DN

21

SHIFTY_BMC_CLK

SHIFTY_BMC_LATCH

21

SHIFTY_BMC_DATA_DN

SHIFTY_BMC_DATA_UP

point-to-point, no cap needed

50V-10%

470pF

21 C900

470pF

21 C1341

point-to-point, no cap needed

point-to-point, no cap needed

50V-10%

470pF

21

C1346

50V-10%

470pF

50V-10%

470pF

21

C1347

50V-10%

21 C1342

21

470pF

C1349

27

58,59

50V-10%

470pF

21 C1343

31

31

31

32

32

32

46

46

46

5

21 C1344

PCI_RST_RAC_N

PCI_RST_MCH_N

PCI_RST_SIO_FWH_N

PCI_RST_RISER_N

PCI_RST_BACKPLANE_N

x02_sd

SYSTEM_PWRGOOD_PXH

SYSTEM_PWRGOOD_NIC

SYSTEM_PWRGOOD_FETS

SYSTEM_PWRGOOD_BACKPLANE

SYSTEM_PWRGOOD_RISER

SYSTEM_PWRGOOD_CHIPSET

50

17

x03b_GT_012204

40,55

31

32

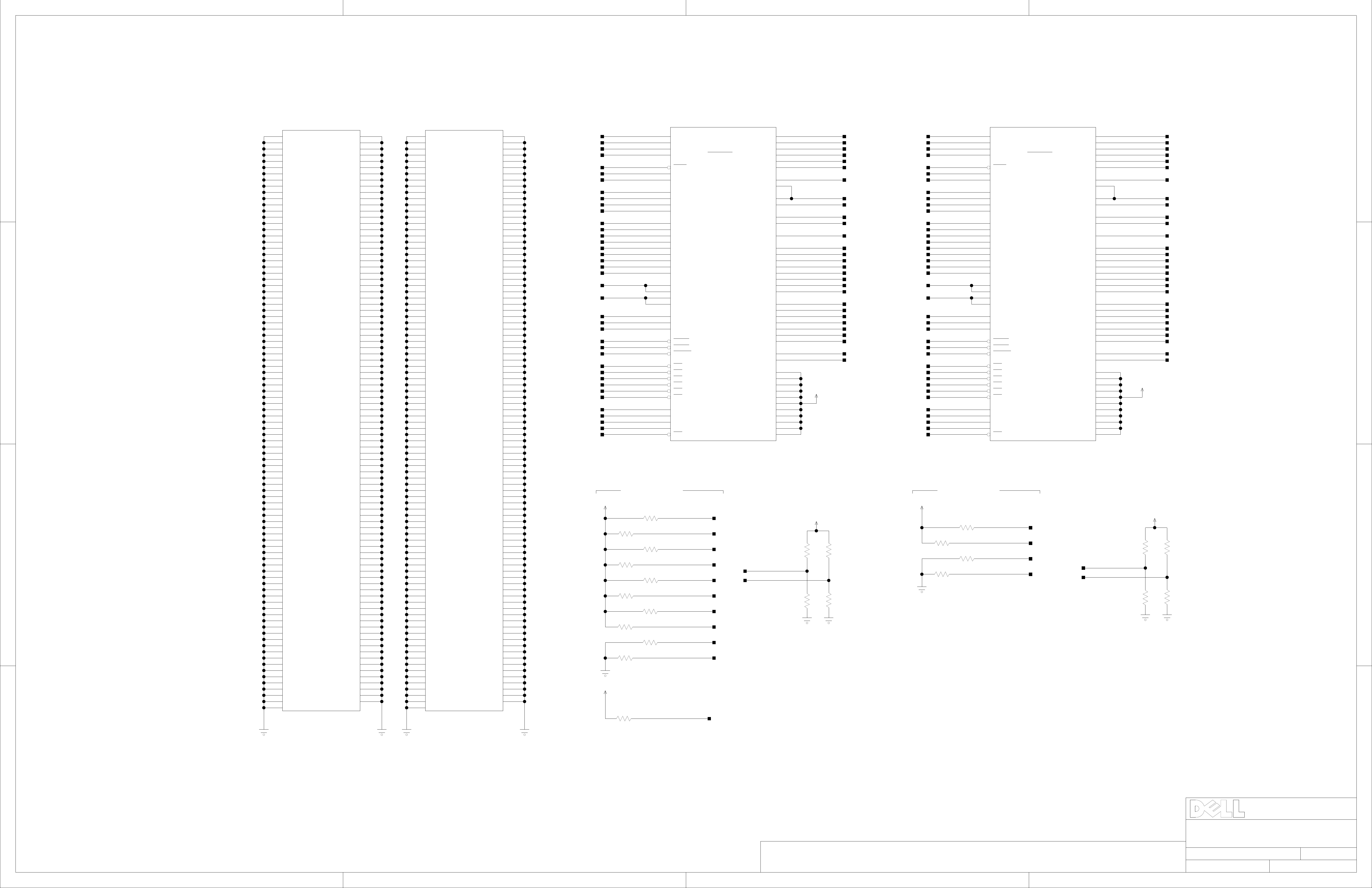

PROG-PART SPEC 14967

DISK PROG

BLANK PART

27,28

24,25

24,35,41

32

31

17,33

B D

todo check ich_pme will be driven or floated high in time

x02_tj_092203

+3.3V_AUX

1K-5%

SYSTEM_PWRGOOD_ESM

SYSTEM_PWRGOOD_NIC_R

5

SYSTEM_PWRGOOD_FETS_R

5

SYSTEM_PWRGOOD_BACKPLANE_R

5

SYSTEM_PWRGOOD_RISER_R

5

SYSTEM_PWRGOOD_CHIPSET_R

SYSTEM_PWRGOOD_PXH_R

5

PCI_RST_MCH_N_R

5

PCI_RST_PLANAR_N_R

5

PCI_RST_RISER_N_R

5

PCI_RST_BACKPLANE_N_R

5

PCI_RST_RAC_N_R

5

BACKPLANE_PRES_N

RISER_PRES_N

SHIFTY_RISER_DATA_UP

CK_FSA

3

SHIFTY_RISER_DATA_DN_R

SHIFTY_RISER_CLK_R

SHIFTY_RISER_LATCH_R

CK_FSB

3

BUF_CK_CPLD

5

CK_33M_CPLD

INTRUSION_COVER_VAUX_N

41

CK_32K_VAUX_SYSCPLD

33

SHIFTY_BMC_DATA_UP

5

SHIFTY_BMC_DATA_DN_R

5

CPLD_DDR2_RESET

3.3VAUX_PWRGOOD

41

H2_PROCHOT_3V

15

H1_PROCHOT_3V

15

H2_THERMTRIP_3V

H1_THERMTRIP_3V

H2_IERR_3V

H1_IERR_3V

ITP_DBR_N

15

SHIFTY_BMC_CLK_R

5

SHIFTY_BMC_LATCH_R

5

ICH_THRMTRIP

5

SHIFTY_BCKPLN_CLK_R

SHIFTY_BCKPLN_LATCH_R

SHIFTY_BCKPLN_DATA_DN_R

SHIFTY_BCKPLN_DATA_UP

5V_PWRGOOD

5V_RISER_PWRGOOD

6

RISER_PWRGOOD

DC2DC_CPUVTT_EN

DC2DC_1V5_EN

DC2DC_1V8_EN

DC2DC_3V3_EN

DC2DC_5V_EN

21

0.1uF 16V

C13

1 2

C14

0.1uF 16V

NC_SC_NC18

NC_SC_NC20

NC_SC_NC31

NC_SC_NC33

NC_SC_NC34

NC_SC_NC42

NC_SC_NC44

NC_SC_NC46

NC_SC_NC48

NC_SC_NC66

NC_SC_NC75

NC_SC_NC106

NC_SC_NC107

NC_SC_NC114

0.1uF 16V

C16

21

P3975SYSTEM_CPLD

P3976

1Y852

x00_sd_051903

x00_sd_051903

just for dumbview

just for dumbview

+3.3V_AUX

22uF 6.3V

C742

21

44,46,50

5,59

5,32,46

5,31

31,59

5,59

5,59

5,59

3,59

x03b_sd

5,59

15,46

15,46

15,46

15,46

5,59

5,59

5,59

32,59

6,59

31,59

6,51,59

6,59

6,59

6,59

6,42,59

0.1uF 16V

1 2

C15

1 2

R1382

1uF 6.3V

21

17

16

15

14

13

12

11

10

9

7

6

5

19

21

22

23

24

25

26

28

30

32

35

38

4

3

2

143

140

138

136

134

133

132

131

130

129

39

40

41

43

45

49

50

51

52

53

54

56

57

18

20

31

33

34

42

44

46

48

66

75

106

107

114

29

36

47

62

72

89

90

99

108

123

144

1uF 6.3V

C277

IO_1_1

IO_1_2

IO_1_3

IO_1_4

IO_1_5

IO_1_6

IO_1_11

IO_1_12

IO_1_13

IO_1_14

IO_1_15_GTS1

IO_1_16_GTS0

IO_2_1

IO_2_2

IO_2_3

IO_2_4

IO_2_5

IO_2_6

IO_2_11

IO_2_12

IO_2_13_GCK0

IO_2_14_GCK1

IO_2_15_CDRST

IO_2_16_GCK2

IO_3_1

IO_3_2_GTS3

IO_3_3_GTS2

IO_3_4_GSR

IO_3_5

IO_3_6

IO_3_7

IO_3_11

IO_3_12

IO_3_13

IO_3_14

IO_3_15

IO_3_16

IO_4_1_DGE

IO_4_2

IO_4_3

IO_4_4

IO_4_5

IO_4_6

IO_4_7

IO_4_11

IO_4_12

IO_4_13

IO_4_14

IO_4_15

IO_4_16

NC_18

NC_20

NC_31

NC_33

NC_34

NC_42

NC_44

NC_46

NC_48

NC_66

NC_75

NC_106

NC_107

NC_114

GND_29

GND_36

GND_47

GND_62

GND_72

GND_89

GND_90

GND_99

GND_108

GND_123

GND_144

1uF 6.3V

1 2

C278

21

1uF 6.3V

C279

SYSTEM_CPLD

XC2C128 TQFP144

SUB*_P3975

256 macrocell flavor

1 2

C659

IO_5_1

IO_5_2

IO_5_3

IO_5_4

IO_5_5

IO_5_6

IO_5_7

IO_5_11

IO_5_12

IO_5_13

IO_5_14

IO_5_15

IO_5_16

IO_6_1

IO_6_2

IO_6_3

IO_6_4

IO_6_5

IO_6_6

IO_6_11

IO_6_12

IO_6_13

IO_6_14

IO_6_15

IO_6_16

IO_7_1

IO_7_2

IO_7_3

IO_7_4

IO_7_5

IO_7_6

IO_7_7

IO_7_11

IO_7_12

IO_7_13

IO_7_14

IO_7_15

IO_7_16

IO_8_1

IO_8_2

IO_8_3

IO_8_4

IO_8_5

IO_8_6

IO_8_11

IO_8_12

IO_8_13

IO_8_14

IO_8_15

IO_8_16

TCK

TDI

TDO

TMS

VCC_JTAG

VCC_1

VCC_37

VCC_84

VCCIO1_27

VCCIO1_55

VCCIO1_73

VCCIO1_93

VCCIO2_109

VCCIO2_127

VCCIO2_141

NC_135

NC_137

NC_139

NC_142

94

95

96

97

98

100

101

102

103

104

105

110

111

92

91

88

87

86

85

83

82

81

80

79

78

112

113

115

116

117

118

119

120

121

124

125

126

128

77

76

74

71

70

69

68

64

61

60

59

58

67

63

122

65

8

1

37

84

27

55

73

93

109

127

141

135

137

139

142

CPLD_TCK

CPLD_TDI

CPLD_TD1

CPLD_TMS

NC_SC_NC135

NC_SC_NC137

NC_SC_NC139

NC_SC_NC142

PS1_PWRGOOD

PS2_PWRGOOD

DEBUG_JUMPER_1

DEBUG_JUMPER_0

DEBUG_LED_3

DEBUG_LED_2

DEBUG_LED_1

DEBUG_LED_0

ICH_PWRBTN_N

ICH_PME_N

PFAULT_LATCH_N_R

PFAULT_RESET

RISER_EXP_PME_N

VRD1_THERMTRIP_N

PCI_RST_ICH_N

VCORE_EN_R VCORE_EN

VCORE1_PWRGOOD

VCORE2_PWRGOOD

CPLD_H_FORCEPR

VRD2_THERMTRIP_N

ICH_PWR_ON_REQ

RESET_BTN_N

PS1_ENABLE_N

PS2_ENABLE_N

B_1U_2U5U

LPC_LFRAME_N

LPC_LAD3

LPC_LAD2

LPC_LAD1

LPC_LAD0

CPLD_H_VID_PWRGOOD_N

PME_NIC_CPLD_N

H2_CPU_PRES_N

H1_CPU_PRES_N

H2_VTT_EN

H1_VTT_EN

RISER_PCI_PME_N

CK_VTT_PWRGD_N

DC2DC_5V_RISER_EN

H1_BSEL0_3V_N

H1_BSEL1_3V_N

H2_BSEL0_3V_N

H2_BSEL1_3V_N

CPU_VTT_PWRGOOD

1V5_PWRGOOD

1V8_PWRGOOD

3V3_PWRGOOD

CK_PWRDWN_N

5,40,46

5,40

46

5,31,32,40,46

CA

44,46

31,59

31,59

59

59

59

59

59

59

33,41,44,56,59

33

5

5

x03b_sd

31

9,46

33,59

7,59

8,59

5

9,46

33,40,41,44,59

56

31,59

31,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

33,40,44,55,59

5,59

28

5,12,46

5,12,46

5,12

5,12

31

3,59

6

15

15

15

15

6,51

6,59

6,59

6,59

3,4,59

33-5%

x02_sd

x03b_sd

+3.3V_AUX

+3.3V_AUX

PFAULT_LATCH_N_R

5

x00_sd_52903 - removed 2 leds

1 2

R1790

1 2

21

R1791

PROPAGATION_DELAY=L:S::2000

PFAULT_RESET_R

PROPAGATION_DELAY=L:S::2500

21

R1865

+3.3V_AUX

1 2

8.2K-5%

8.2K-5%

R1920

0-5%

R1921

0-5%

2

8.2K-5%8.2K-5%

NP*

NP*

R1769

R1770

21

1 2

NP*

21

NP*

GND

TPS72118DBV

7,8,59

NP13

NP02

R6021

0-5%

+3.3V

1 2

33-5%

U64

x02_sd

1 2

ICH_THRMTRIP

5

X04_GT_032904

I2C_SEG2_VAUX_SDA

I2C_SEG2_VAUX_SCL

R1922

51

OUTIN

43

NCEN

R6006

33-5%

R6007

21

33-5%

21

C559

1000pF

PART_NUMBER=79015

SHUNT_1V5_N

NET_PHYSICAL_TYPE=PWR

+1.8V_AUX

0.1uF 16V

C1624

21

PFAULT_LATCH_N

+3.3V_AUX

142U38

1

R575

1 2

100-1%

50V-10%

1 2

2.7K-5%

28

44,45,59

44,45,59

10V-10%

1uF

21

PFAULT_RESET

R92

0.1uF 16V

C1625

21

44,46

5

Q104

3904

1

C1626

+3.3V_AUX

CK_CPLD

3

RC = 0.1 us

F = 2.0MHz

ICH_THRMTRIP_N

3

2

todo....need to check that 3904 has drive strength and gain

x00_tj_042803

5,12,46

5,12,46

5,12

5,12

ROOM=SYSCPLD

144U38

VHC14VHC14

5,59

5,59

H2_CPU_PRES_N

H1_CPU_PRES_N

H2_VTT_EN

H1_VTT_EN

CPLD_H_VID_PWRGOOD_N

CPLD_H_FORCEPR

5

BUF_CK_CPLD

CPLD_DDR2_RESET

33

+3.3V_AUX

7

8

RN87

2

1

12-16-2004_19:50

1

5

todo, consider slew rate limiting

+1.8V

1 2

R1439

1 2

2.7K-5%

R1438

2.7K-5%

R426

1 2

2.7K-5%

301-1%

Q66

3904

1

R583

21

2.7K-5%

Q65

3904

21

1

Q84

3904

1

3

2

3

2

3

2

R1359

301-1%

Q11

3904

1

H_VTT_PWRGOOD

+1.8V

R1

21

3

2

H_FORCEPR_N

DDR2_RESET_N_1

DDR2_RESET_N_2

12

+3.3V_AUX

20,21

20,21

2

11,12

3

5

6

4.7K

21

R1835

4.7K

4.7K

4

3

5,32,46

5,31

BACKPLANE_PRES_N

RISER_PRES_N

x00_sd_052203

x00_tj_052903

R1834

1 2

+3.3V_AUX

J14

1

5,40,46

5,32,40

5,40

4 4

5,31,32,40,46

CPLD_TCK

CPLD_TDO

CPLD_TDI

CPLD_TMS

2

3

4

5

6

SIO

Header

CPLD_TDI CPLD_TD1 CPLD_TD2

CPLD JTAG Chain

Planar ESM Riser Backplane

CPLD_TD3

Gated by ~SPG Gated by ~SPG

Jumper

NP*

CPLD_TD0

CPLD_BYPASS

p/u for TCK at SIO

31,46

CPLD_TD2

1 2

NP*

CPLD_TDO

5,32,40

INC.

ROUND ROCK,TEXAS

TITLE

SCHEM,PLN,SV,PE2800/2850/1850

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

subsys done

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

DWG NO.

DATE

D1660

12/16/2004

REV.

A03-00

SHEET

5 OF 60

A B

DC

B D

CA

12-16-2004_19:51

1

2

TYPE

INPUT

OUTPUT

DESTINATION

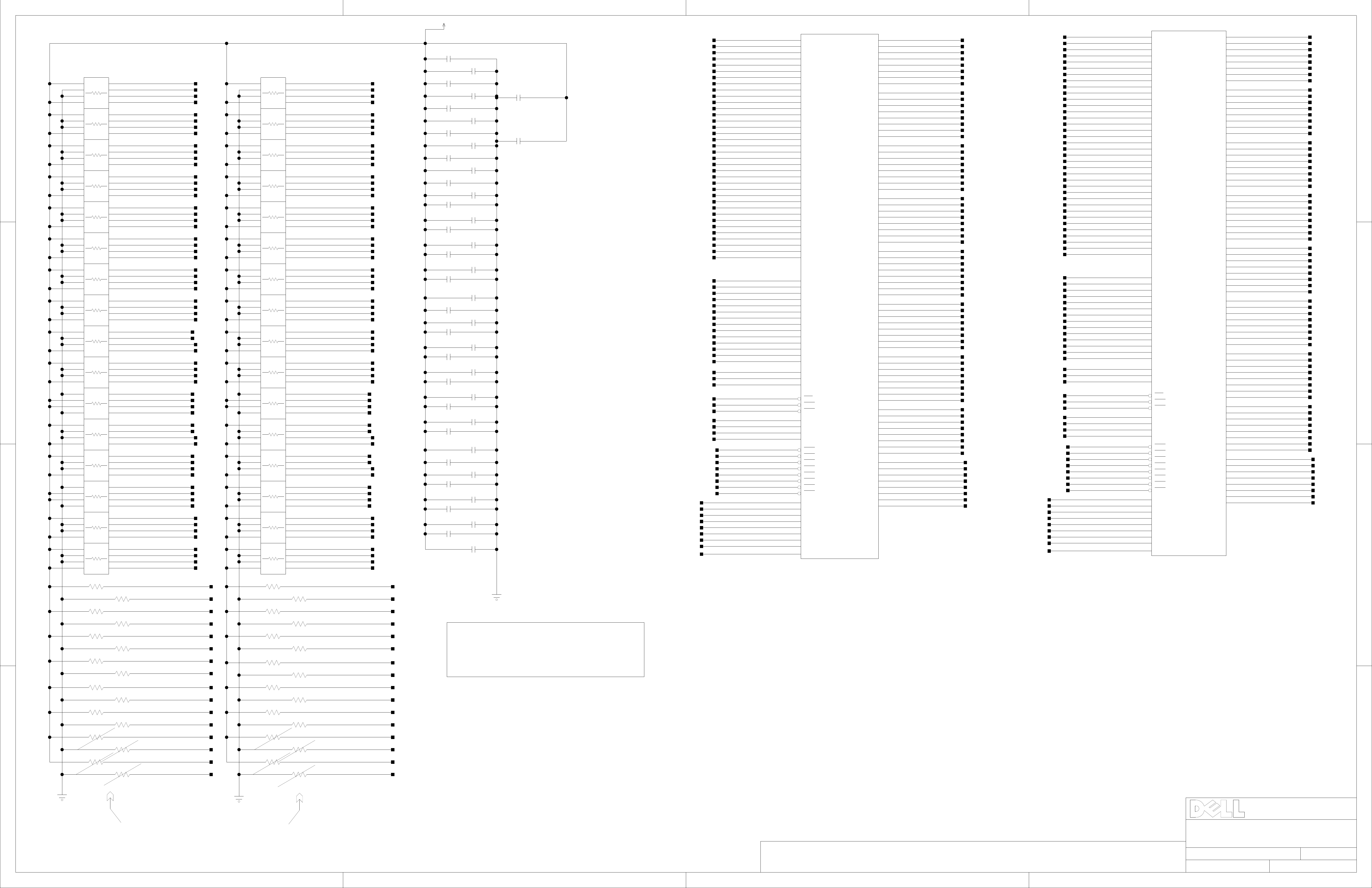

ROOM=DC2DC_1P8V

+12V

R73

8.2K-5%

1 2

C1805

12

+

1V8_PWRGOOD

1 2

0.1uF 16V

270uF

16V-20%

R132

1 2

+12V

+

2 1

X04_GT_031904

+1.8V

3.01K-1%

C606

270uF

16V-20%

5,59

Enable is driven to required state

from CPLD at all times.

C605

70W VERTICAL

+12V

+1.8V

DDR II, MCH

+1.8V DC2DC

x04_tj_031904

SUB=SUB*_0K260

R290

1 2

422-1%

442-1%

DC2DC_1V8_EN

C588

NP

1 2

R463

1 2

0-5%

R546

0-5%

5,59

R547

0-5%

1 2

NC_DC2DC_1P8V_2

+1.8V

21

1000pF

50V-10%

PART_NUMBER=79015

+12V

DC2DC_1P8V

1

+RS

2

RSVD

3

-RS

4

PWRGD

5

PWRGD_SET

K

7

VSS_0

8

VSS_1

9

OUTEN

10

-SENCE

11

+SENSE

12

12V_IN_0

13

12V_IN_1

14

12V_IN_2

15

VOUT_0

16

VOUT_1

17

VSS_2

18

VOUT_2

19

VSS_3

20

VOUT_3

21

VSS_4

22

VOUT_4

23

VSS_5

24

VOUT_5

MH1

GND_MH1

MH2

GND_MH2

DC/DC CONVERTER

MOD., 24 PIN, 72W, VERTICAL

x00_gt_062603

+1.8V

16V-10%

4.7uF

21

+1.8V

12

C268

C600

+

16V-10%

4.7uF

680uF

6.3V-20%

C601

21

C269

25V-20%

.1uF

21

x00_tj_051203

x02_tj_121503

12

+

680uF

C611

C270

6.3V-20%

TYPE

INPUT

OUTPUT

DESTINATION

ROOM=DC2DC_3P3V

100W HORIZONTAL

+12V

+3.3V

RISER's

TYPE

INPUT

OUTPUT

DESTINATION

ROOM=DC2DC_5V

+12V

100W VERTICAL

+12V

+5V

BACKPLANE

+5V DC2DC

1

DC2DC_5V

+RS

K

-RS

PWRGD

RSVD_1

RSVD_2

VSS_0

VSS_1

OUTEN

-SENCE

+SENSE

12V_IN_0

12V_IN_1

12V_IN_2

VOUT_0

VOUT_1

VSS_2

VOUT_2

VSS_3

VOUT_3

VSS_4

VOUT_4

VSS_5

VOUT_5

GND_MH1

GND_MH2

DC/DC CONVERTER

MOD. 073_20821_03

VCC

16V-10%

4.7uF

VCC

C271

VCC

NP

C604

21

12

+

DC2DC_5V_1U

16V-10%

4.7uF

680uF

6.3V-20%

x00_tj_051203

25V-20%

C607

.1uF

21

12

+

C272

C620

21

680uF

6.3V-20%

2

+12V

R74

8.2K-5%

1 2

todo should this really be NC? -shawn

5,6,59

X04_GT_031904

3V3_PWRGOOD

R133

3.01K-1%

1 2

3P3V_RISER_SENSE

31

x00_sd_051703

Enable is driven to required state

from CPLD at all times.

RISER

+3.3V DC2DC

R1572

1 2

21.5K-1%

+3.3V

5,59

R1580

21

2-1%

R1430

1 2

2-1%

+3.3V

DC2DC_3V3_EN

21

R301

0-5%

NC_DC2DC_3P3V_6

+3.3V

C1501

1 2

1000pF

50V-10%

PART_NUMBER=79015

NP

R1488

10K-1%

21

+12V

DC2DC_3P3V

1

+RS

K

3

-RS

4

PWRGD

5

PWRGD_SET

6

RESERVED

7

VSS_7

8

VSS_8

9

OUTEN

10

-SENSE

11

+SENSE

12

12VIN_12

13

12VIN_13

14

12VIN_14

15

VCC_15

16

VCC_16

17

VSS_17

18

VCC_18

19

VSS_19

20

VCC_20

21

VSS_21

22

VCC_22

23

VSS_23

24

VCC_24

100W-25A DC-DC

MOD.-25 pin, HORIZONTAL

+3.3V

16V-10%

4.7uF

21

C602

16V-10%

4.7uF

21

25V-20%

C603

x00_tj_051203

.1uF

C619

21

X04_GT_031904

5,6,59

X04_GT_031904

SENSE_5V_BACKPLANE_1U

32

SENSE_5V_BACKPLANE_2U5U

32

VCC

1 2

5V_PWRGOOD

R1752

20-1%

R562

0-5%

R75

1 2

Enable is driven to required state

from CPLD at all times.

R134

1.5K-5% 4.75K-1%

1 2

x03b_sd

NP13

R1750

1 2

0-5%

R1751

1 2

20-1%

R273

0-5%

21

511-1%

VCC

1 2

R274

10K-1%

21

x03_sd_sense

21

R275

5,6,42,59

NP*

DC2DC_5V_SENSE_GND

R462

12

0-5%

NC_DC2DC_5V_6

DC2DC_5V_EN

DC2DC_5V_SENSE_GND

6

DC2DC_5V_SENSE

6

C590

NP

DC2DC_5V_SENSE

21

1000pF

6

6

R466

1 2

0-5%

VCC

50V-10%

+12V

1

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

MH1

MH2

SUB=SUB*_G6740

BACKPLANE

1

VCC_1

+12V

U24

+12V

1 2

C1627

12

+

680uF

6.3V-20%

C1568

+

270uF

2 1

16V-20%

X00_GT_052203

0.1uF 16V

VCC

GND

DS1818

2

RESET

3

SUB=SUB*_Y1351

1

3V3_PWRGOOD

5,6,59

+3.3V

4V-20%

820uF

x04b_tj_032404

12

+

1 2

C287

+

4V-20%

820uF

+

1 2

C288

C610

270uF

16V-20%

1 2

C1650

0.1uF 16V

Sub to DS1811R-5 (+5V, 5% part)

DS1818

2

VCC

GND

3

U59

RESET

1

SUB=SUB*_1F826

5V_PWRGOOD

5,6,59

NP

R1848

X

1 2

5,6,42,59

5,6,59

309-1%

+12V

DC2DC_5V_EN

5V_PWRGOOD

NP

R1849

1 2

X

0-5%

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

X

12VIN_10

11

12VIN_11

40W-15A DC-DC

SIP11

X00_GT_061203

3

TYPE

INPUT

OUTPUT

DESTINATION

ROOM=DC2DC_CPU_VTT

Enable is driven to required state

from CPLD at all times.

+12V

NP

R1137

X

1 2

CPU_VTT_PWRGOOD

NP

R1148

X

1 2

ECAD: Place 1 560uF cap by each CPU

+12V

NP

16V-20%

270uF

5,51

x04b_tj_032404

1 2

C138

+

40W VERTICAL

+12V

+1.2V

CPU1, CPU2, MCH

8.2K-5%2.7K-5%

5,51,59

DC2DC_CPUVTT_EN

NP*

R543

1 2

x02_tj_091903

+12V

27.4K-1%

& one by regulator

+CPU_VTT

CPU VTT

R225

NP*

1 2

26.7-1%

X

NP

DC2DC_CPUVTT

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

X

12VIN_10

11

12VIN_11

40W-15A DC-DC

SIP11

+CPU_VTT

.1uF

C349

2 1

+

2 1

10V-10%

+CPU_VTT

16V-10%

C591

560uF

4V-20%

4.7uF

21

C350

C608

+

2 1

560uF

4V-20%

TYPE

40W HORIZONTAL

INPUT +12V

OUTPUT

DESTINATION

+1.5V

MCH, ICH5

ROOM=DC2DC_1P5V

Enable is driven to required state

from CPLD at all times.

+12V

R77

8.2K-5%

1 2

5,59

1V5_PWRGOOD

R136

3.01K-1%

1 2

Substitute from 3.92K to 3.74K to tweak 1.5V to 1.514V

x03_tj_010904

x03b_tj_012604

+12V

16V-20%

270uF

5,59

X04_GT_031904

1 2

+

C1566

DC2DC_1V5_EN

R70

1 2

+12V

3.74K-1%

+1.5V DC2DC

+1.5V

R1489

21

26.7K-1%

SUB*_5N443

Substitute 26.1K, 1%

DC2DC_1P5V

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

MOD.-13 pin, HORIZONTAL

+1.5V

4V-20%

820uF

TYPE

INPUT

OUTPUT

DESTINATION

40W HORIZONTAL

+12V

+5V

MCH, ICH5

ROOM=DC2DC_RISER5V

5V DC2DC

Enable is driven to required state

+5.0V Riser

from CPLD at all times.

U34

+5.0V Riser

+12V

DC2DC_RISER5V

1 2

C1651

X04_GT_031904

5,6

+12V

16V-20%

270uF

+

1 2

C1497

+

10V-10%

.1uF

2 1

16V-10%

C1575

4.7uF

C1585

21

5V_RISER_PWRGOOD

X04_GT_031904

1 2

C1569

R76

1 2

5

R135

1 2

4.75K-1%

DC2DC_5V_RISER_EN

1.5K-5%

R32

+12V

309-1%

1 2

R106

1 2

0-5%

1

VCC_1

2

VCC_2

3

VCC_3

4

TRIM

5

OUTEN

6

PWRGD

7

VSS_7

8

VSS_8

9

PWRGD_SET

10

12VIN_10

11

12VIN_11

40W-15A DC-DC

MOD.-13 pin, HORIZONTAL

Sub to DS1811R-5 (+5V, 5% part)

0.1uF 16V

VCC

GND

DS1818

2

3

RESET

+5.0V Riser

1

5V_RISER_PWRGOOD

SUB=SUB*_1F826

12

+

C633

680uF

6.3V-20%

10V-10%

.1uF

2 1

16V-10%

C1576

5,6

4.7uF

C1586

21

3

4 4

INC.

ROUND ROCK,TEXAS

TITLE

DC2DC REGULATORS

SCHEM,PLN,SV,PE2800/2850/1850

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

subsys done

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

A B

DWG NO.

DATE

DC

D1660

12/16/2004

REV.

A03-00

SHEET

6 OF 60

B D

+12V +12V

SUB=SUB*_J9621

CA

12-16-2004_20:22

SUB=SUB*_J9621

1

7

7

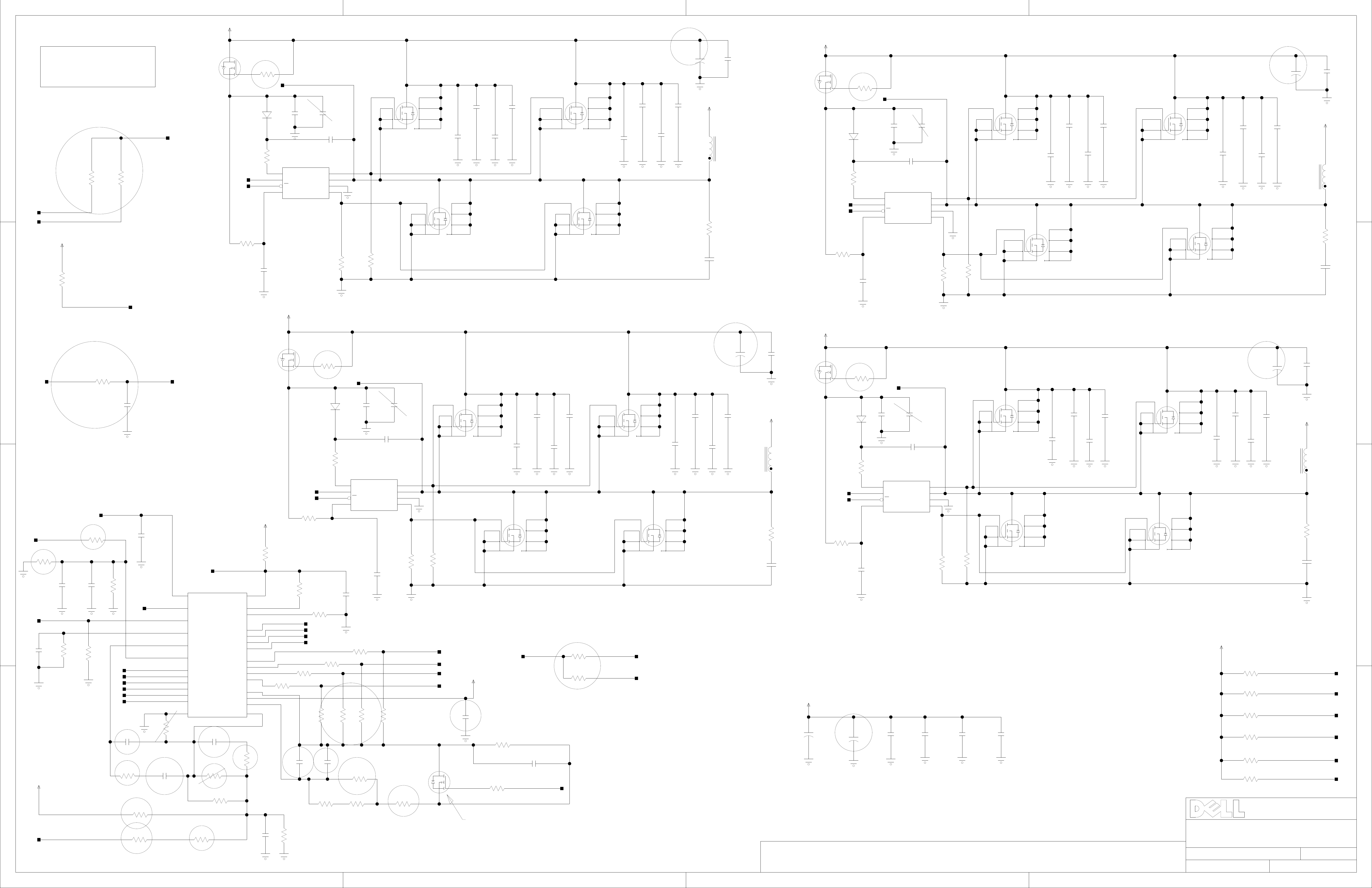

VRD BOM Changes:

X02_TJ_081803

VRD1_PWM3A

VRD1_PWM4A

+3.3V

8.2K-5%

R4502

21

X02_TJ_081803

VCORE1_PWRGOOD

21

R1972

220K

21

R1973

VRD1_VCC

220K

5,7,59

7

X03_GT_011804

X02_TJ_110503

x00c4_tj_090804

SUB*_16155

Q86

3

FT2N7002LT1

1

2

7

7

SUB=SUB*_G7300

5.1-5%

2 1

R260

R1985

1 2

1K-5%

1N914

2-1%

VRD1_PWM1A

DRV1_OD

.22uF 25V

20%

X03_GT_012604

1 3

D9

R240

21

1

2

3

4

C484

21

.22uF 25V

20%

BST

IN

OD

VCC

Phase 1

ROOM = VRD1_PHASE1

1 2

50V-10%

C491

VRD1_DRV1

ADP3418

VRD1_PHASE1B_SENSE

7

x03_sd

1000pF

C852

NP*

21

C466

21

.1uF

25V-20%

8

DRVH

7

SW

6

PGND

5

DRVL

R433

VRD1_UGATE1

VRD1_LGATE1

4.7K

1 2

R451

1 2

4.7K

Q41

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

Q21

4

3

2

1

9

D

G

S

NC

FDS7066SN3

SUB*_T1564

25V-20%

.1uF

21

.22uF 25V

1 2

20%

5

6

7

8

PKG_TYPE=SO8_P9DR_FRCHLD

C488

25V-20%

C1680

.1uF

16V-10%

4.7uF

C1682

21

21

C1681

Q24

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

Q20

4

3

2

1

FDS7066SN3

D

G

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

9

D

S

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

25V-20%

.1uF

C489

21

A03_121704_GT

C1683

21

25V-20%

.1uF

C336

16V-10%

4.7uF

C1684

21

SUB*_16155

12

16V-10%

+

560uF

4V-20%

4.7uF

2 1

C303

X02_TJ_110503

Q88

3

FT2N7002LT1

1

2

R1986

1 2

1K-5%

Phase 2

ROOM = VRD1_PHASE2

VRD1_PHASE2B_SENSE

7

A03_121704_GT

C343

16V-10%

12

+

560uF

4V-20%

4.7uF

2 1

C308

X03_GT_012604

21

C1685

+CPU_VID1

0.6uH, 27Amp

Q36

9

D

G

S

NC

5

6

7

8

20%

16V-10%

.22uF 25V

1 2

C581

4.7uF

2 1

C1686

25V-20%

.1uF

25V-20%

.1uF

2 1

C1687

2 1

C1688

SUB=SUB*_N1453

1N914

.22uF 25V

1 2

20%

1 3

D11

C579

C471

50V-10%

1000pF

21

x03_sd

C853

NP*

4

3

2

1

21

FDS7096N3

L3

2-1%

12

7

7

R244

21

VRD1_PWM2A

DRV1_OD

1

BST

2

IN

3

OD

4

VCC

.1uF

25V-20%

VRD1_PHASE2

DRVH

SW

PGND

DRVL

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

8

7

6

5

Q27

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

C580

21

4.7uF

2 1

C1689

25V-20%

.1uF

25V-20%

.1uF

2 1

C1690

2 1

C1691

1

+CPU_VID1

L2

0.6uH, 27Amp

1 2

SUB=SUB*_N1453

SUB=SUB*_G7300

ADP3418

Q26

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

R163

C281

3-5%

1 2

1 2

.001UF

50V-10%

R152

C276

Q37

4

3

2

3-5%

VRD1_LGATE2

5.1-5%

1 2

2 1

1

R258

.22uF 25V

1 2

.001UF

50V-10%

20%

C482

21

R434

1 2

4.7K

R454

1 2

4.7K

FDS7066SN3

9

D

G

S

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

+12V

+12V

SUB=SUB*_J9621

SUB=SUB*_J9621

2

DRV1_OD_R

7

PWM Control Circuitry

ROOM = VRD1_CTRL

X04_GT_031904

H1_VSSSENSE

12

VRD1_VSSSENSE_MID

3

x00_sd_061603 - providing sensing

0-5%

R1851

21

SUB=SUB*_4053P

SUB=SUB*_75EEC

R304

1 2

1K-5%

DRV1_OD_R

7

X04_GT_031904

C1728

1 2

5,8,59

R1820

1 2

0-5%

VRD1_VSSSENSE

50V-10%

1000pF

1uF

25V-10%

VCORE_EN

C1727

21

R1980

220K

100-5%

X03_GT_011804

21

C1807

1 2

R1846

21

5,7,59

DRV1_OD

x03b_GT_012204

27pF

50V-10%

21

C462

VCORE1_PWRGOOD

.1uF

7

25V-20%

15

7

11

10

12

VRD1_VCC

EN

PWRGD

ILIMIT

DELAY

X02_TJ_110503

VRD1_CTRL

SUB*_16155

+12V

1 2

10-5%

RAMPADJ

R13

VCC

RT

PWM1

Q87

3

FT2N7002LT1

2

28

14

13

27

26

1

7

7

5.1-5%

2 1

R261

1 2

487K-1%

R271

VRD1_PWM1A

VRD1_PWM2A

R1987

1 2

1K-5%

X03_GT_012604

1 3

1N914

1 2

2-1%

VRD1_PWM3A

DRV1_OD

R299

1 2

200K-1%

.22uF 25V

20%

D7

R243

SUB=SUB*_G7300

16V-10%

.47uF

21

7

50V-10%

C490

21

C467

.1uF

25V-20%

VRD1_DRV3

C9

Phase 3

ROOM = VRD1_PHASE3

x03_sd

1000pF

21

1

2

3

4

C854

NP*

21

VRD1_PHASE3B_SENSE

7

BST

IN

OD

VCC

DRVH

SW

PGND

DRVL

ADP3418

.22uF 25V

1 2

20%

C483

X00_GT_062103

Redraw Only- NEED INDEPENDENT CHECK before MODEM!

A03_121704_GT

C338

12

+

16V-10%

4.7uF

2 1

C305

A03_121704_GT

C337

SUB*_16155

12

+

X02_TJ_110503

560uF

4V-20%

Q89

3

FT2N7002LT1

1

2

R1988

1 2

1K-5%

Phase 4

ROOM = VRD1_PHASE4

VRD1_PHASE4B_SENSE

7

X03_GT_012604

.22uF 25V

Q38

4

3

2

1

9

D

G

S

NC

5

6

7

8

.22uF 25V

16V-10%

1 2

20%

4.7uF

C481

2 1

C1692

25V-20%

.1uF

25V-20%

2 1

C1693

.1uF

2 1

C1694

FDS7096N3

SUB*_N1930

PKG_TYPE=SO8_P9DR_FRCHLD

8

VRD1_UGATE3

Redraw Only- NEED INDEPENDENT CHECK before MODEM!

Q39

4

3

2

1

9

G

S

FDS7096N3

D

SUB*_N1930

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

C487

21

4.7uF

2 1

C1695

25V-20%

.1uF

25V-20%

2 1

C1696

.1uF

2 1

C1697

+CPU_VID1

L1

1 2

SUB=SUB*_N1453

0.6uH, 27Amp

1N914

D10

31

1 2

7

7

2-1%

VRD1_PWM4A

DRV1_OD

R236

SUB=SUB*_G7300

20%

1

VRD1_UGATE4

BST

2

IN

3

OD

4

VCC

21

7

50V-10%

C578

C465

1 2

.1uF

25V-20%

VRD1_DRV4

ADP3418

1000pF

21

DRVH

PGND

DRVL

C855

x03_sd

SW

NP*

8

7

6

5

VRD1_LGATE4

6

5

VRD1_LGATE3

R457

1 2

4.7K

R437

4.7K

1 2

Q40

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

Q25

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

R171

C282

5.1-5%

12

R257

3-5%

1 2

21

.001UF

50V-10%

.22uF 25V

20%

C8

21

21

R430

4.7K

21

R428

4.7K

Q34

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

4

3

2

1

FDS7066SN3

.22uF 25V

20%

Q33

G

SUB*_T1564

16V-10%

1 2

9

D

S

NC

PKG_TYPE=SO8_P9DR_FRCHLD

4.7uF

C485

5

6

7

8

2 1

C1698

25V-20%

.1uF

25V-20%

.1uF

C1699

12

C1700

12

Q35

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

Q32

4

3

2

1

9

D

G

S

NC

FDS7066SN3

SUB*_T1564

16V-10%

4.7uF

.22uF 25V

20%

C486

21

5

6

7

8

PKG_TYPE=SO8_P9DR_FRCHLD

2 1

C1701

25V-20%

.1uF

25V-20%

.1uF

C1702

12

C1703

12

FDS7066N3 is local. Waiting on library symbol.

16V-10%

560uF

4V-20%

2 1

4.7uF

C302

+CPU_VID1

L4

1 2

21

R153

21

C280

SUB=SUB*_N1453

0.6uH, 27Amp

3-5%

.001UF

50V-10%

2

3

VID Termination

R303

0-5%

75K-1%

1 2

4700pF

7

7

7

1 2

21

75K-1%

R291

21

X04_GT_031904

C710

1 2

29.4K-1%

R306

1 2

0-5%15.8K-1%

R315

0-5%

R85

75K-1%

R286

21

X04_GT_031904

R314

21

0-5%

75K-1%

R284

21

R81

75K-1%

X04_GT_031904

R285

21

NP

21

VRD1_PHASE1B_SENSE

VRD1_PHASE2B_SENSE

VRD1_PHASE3B_SENSE

VRD1_PHASE4B_SENSE

X04_GT_031904

3

D

1

X

2

G

S

7

VRD1_PWM1A

7

7

7

+CPU_VID1

7

X04_GT_032204

1 2

C6007

.01uF 16V

R407

1 2

0-5%

C334

NP

1 2

21

X

X

ALT_LLINE

7,8

2N7002

NP

Q7

.047uF

16V-10%

R484

4.7K

If this FET is populated, you must verify Vgs(th) is met!

X03_GT_011904

R1717

NP

1 2

68K-5%

R1718

NP

68K-5%

GPO_ALT_LLINE_N

33

X

21

X

VRD1_PWM3A

VRD1_PWM4A

U61

7

7

+3.3V_AUX

14

13

VHC14

x00_sd_052903

12

ALT_LLINE

7,8

x04b_tj_032404

Input Filtering

+12V

A03_121704_GT

SUB=SUB*_J9621

C582

12

C725

12

+

560uF

x04b_tj_032404

4V-20%

C2

.1uF

1 2

50V-20%

+

270uF

16V-20%

C3

21

.1uF

SUB=SUB*_4053P

50V-20%

C21

1uF

1 2

25V-10%

C12

1 2

SUB=SUB*_4053P

INTEGRATED VRD 10.1 VOLTAGE

REGULATOR FOR PROC_1

PROPRIETARY NOTE: THIS ITEM IS THE PROPERTY OF DELL INC. ROUND ROCK, TEXAS AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS ITEM MAY NOT BE TRANSFERRED FROM THE CUSTODY OF DELL INC. EXCEPT

AS AUTHORIZED BY DELL INC., AND THEN ONLY BY WAY OF LOAN FOR LIMITED PURPOSES. IT MUST NOT BE REPRODUCED IN WHOLE

OR IN PART AND MUST BE RETURNED TO DELL INC. UPON REQUEST AND IN ALL EVENTS UPON COMPLETION OF THE PURPOSE OF THE

LOAN. NEITHER THIS ITEM OR THE INFORMATION IT CONTAINS MAY BE USED BY OR DISCLOSED TO PERSONS NOT HAVING A NEED FOR SUCH

USE OR DISCLOSURE CONSISTENT WITH THE PURPOSE OF THE LOAN WITHOUT THE PRIOR WRITTEN CONSENT OF DELL INC.

1uF

25V-10%

+CPU_VTT

R28

1 2

499-1%

R27

1 2

499-1%

R26

1 2

499-1%

R25

1 2

499-1%

R16

1 2

499-1%

R15

1 2

499-1%

INC.

ROUND ROCK,TEXAS

TITLE

SCHEM,PLN,SV,PE2800/2850/1850

DWG NO.

D1660

DATE

12/16/2004

SHEET

H1_VID0

H1_VID1

H1_VID2

H1_VID3

H1_VID4

H1_VID5

7 OF 60

7,12

7,12

7,12

7,12

7,12

7,12

REV.

A03-00

CSSUM

CSREF

CSCOMP

300-5%

NP

50V-10%

1000pF

X

PWM2

25

PWM3

24

PWM4

23

SW1

22

SW2

21

SW3

20

SW4

17

16

18

8

FB

X04_GT_031904

NP

C1810

100-5%

21

X

50V-10%

1 2

R1992

VRD1_PWM3A

VRD1_PWM4A

R310

1 2

0-5%

1 2

2700pF

SUB*_1U388

R147

C720

50V-10%

21

THERMISTOR

.047uF 25V

1 2

20%

C714

4 4

+CPU_VID1

1 2

249K-1%

R255

1 2

127K-1%

R233

X04_GT_031904

7,12

7,12

7,12

7,12

7,12

7,12

C300

100pF 50V

R250

2 1

10.7K-1% 680pF 50V

X04_GT_031904

H1_VID0

H1_VID1

H1_VID2

H1_VID3

H1_VID4

H1_VID5

12

X04_GT_031904

100K-1%

21

C708

12

VRD1_VSSSENSE

R289

NP*

X04_GT_032204

NP

(1.33K)

SUB=NP

9

COMP

7

FBRTN

5

VID0

4

VID1

3

VID2

2

VID3

1

VID4

6

VID5

19

GND

C479

12

680pF 50V

R278

1 2

1.3K-1%

R288

1 2

ADP3168

SUB*_H5002

X04_GT_031904

X

NP

R305

X

X04_GT_031904

SUB*_X5828

1 2

R311

X

12

H1_VCCSENSE

1 2

1K-5%

R1821

1 2

VRD1_VCCSENSE

X04_GT_031904

100K-1%

R6019

1 2

0-5% 0-5%

X04_GT_031904

X04_GT_031904

A B

DC

+12V

B D

CA

SUB=SUB*_J9621

1

8

8

VRD BOM Changes:

VRD2_PWM3A

VRD2_PWM4A

+3.3V

8.2K-5%

X02_TJ_081803

R1970

R4503

21

21

220K

X02_TJ_081803

21

R1971

VRD2_VCC

220K

+12V

Q92

3

FT2N7002LT1

2

SUB=SUB*_J9621

A03_121704_GT

C440

C1715

12

+

Phase 2

R1990

1

1 2

1K-5%

X03_GT_012604

VRD2_PHASE2B_SENSE

8

.22uF 25V

20%

1 3

1N914

2-1%

D38

R249

ROOM = VRD2_PHASE2

x03_sd

C857

NP*

21

1 2

50V-10%

C650

C478

.1uF

25V-20%

1000pF

Q52

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

1 2

C652

4.7uF

2 1

C1710

25V-20%

.1uF

25V-20%

.1uF

2 1

C1711

2 1

C1712

Q47

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

21

16V-10%

4.7uF

C651

2 1

C1713

25V-20%

.1uF

25V-20%

.1uF

2 1

C1714

2 1

560uF

4V-20%

16V-10%

4.7uF

2 1

+CPU_VID2

C333

1

.1uF

C1708

A03_121704_GT

2 1

C1709

12

+

C344

+CPU_VID2

0.6uH, 27Amp

16V-10%

560uF

4V-20%

12

4.7uF

L17

2 1

C326

SUB=SUB*_N1453

SUB*_16155

X02_TJ_110503

Q90

SUB*_16155

X02_TJ_110503

8

3

FT2N7002LT1

1

2

R1989

1 2

1K-5%

1N914

2-1%

VRD2_PWM1A

X03_GT_012604

8

1 3

D25

20%

R247

21

1

BST

2

ROOM = VRD2_PHASE1

VRD2_PHASE1B_SENSE

.22uF 25V

1 2

VRD2_DRV1

C648

50V-10%

1000pF

DRVH

Phase 1

x03_sd

C856

NP*

21

C476

21

.1uF

25V-20%

8

VRD2_UGATE1

7

Q70

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

1 2

C624

4.7uF

2 1

C1704

25V-20%

.1uF

25V-20%

.1uF

2 1

C1705

2 1

C1706

Q44

4

3

2

1

9

G

S

FDS7096N3

D

SUB*_N1930

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

1 2

C646

4.7uF

2 1

C1707

25V-20%

.1uF

25V-20%

2 1

L16

x00c4_tj_090804

8

DRV2_OD

8

SUB=SUB*_G7300

5.1-5%

2 1

R264

.22uF 25V

20%

C599

21

IN

3

OD

4

VCC

ADP3418

SW

PGND

DRVL

6

5

VRD2_LGATE1

Q43

4

3

2

1

9

D

G

S

NC

5

6

7

8

FDS7066SN3

SUB*_T1564

Q42

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

NC

5

6

7

8

R172

3-5%

1 2

5.1-5%

2 1

PKG_TYPE=SO8_P9DR_FRCHLD

C283

1 2

R263

.001UF

50V-10%

R487

1 2

4.7K

R494

1 2

4.7K

PKG_TYPE=SO8_P9DR_FRCHLD

21

VRD2_PWM2A

8

DRV2_OD

8

SUB=SUB*_G7300

.22uF 25V

20%

C595

21

VRD2_DRV2

1

BST

2

IN

3

OD

4

VCC

ADP3418

DRVH

SW

PGND

DRVL

8

7

6

5

Q56

9

D

G

S

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

R490

1 2

VRD2_LGATE2

4.7K

R495

1 2

4

3

2

1

FDS7066SN3

4.7K

Q46

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

R179

C285

0.6uH, 27Amp

1 2

3-5%

1 2

1 2

.001UF

SUB=SUB*_N1453

50V-10%

VCORE2_PWRGOOD

5,8,59

+12V

A03_121704_GT

SUB=SUB*_J9621

2

+12V

Q91

2

SUB=SUB*_J9621

3

H2_VSSSENSE

12

R318

1 2

1K-5%

SUB=SUB*_4053P

8

DRV2_OD_R

8

X04_GT_031904

X04_GT_031904

C1729

DRV2_OD_R

X03_GT_011804

R1981

21

DRV2_OD

220K

x03b_GT_012204

21

C1808

27pF

50V-10%

PWM Control Circuitry

ROOM = VRD2_CTRL

0-5%

21

VCORE_EN

C1730

1 2

100-5%

R1847

C473

5,8,59

21

.1uF

VCORE2_PWRGOOD

VRD2_VSSSENSE

1uF

1 2

5,7,59

1 2

50V-10%

1000pF

25V-10%

R1822

PART_NUMBER=79015

25V-20%

SUB*_16155

X02_TJ_110503

8

3

FT2N7002LT1

1

2

R6018

1 2

1K-5%

1N914

2-1%

X03_GT_012604

8

1 3

D12

20%

1 2

R248

Phase 3

ROOM = VRD2_PHASE3

VRD2_PHASE3B_SENSE

.22uF 25V

C647

21

50V-10%

1000pF

C477

.1uF

25V-20%

x03_sd

C858

NP*

21

21

Q62

4

3

2

1

9

G

S

FDS7096N3

SUB*_N1930

D

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

1 2

16V-10%

4.7uF

C594

2 1

C1732

25V-20%

.1uF

25V-20%

.1uF

2 1

C1722

2 1

C1723

Q63

4

3

2

1

9

G

S

FDS7096N3

D

SUB*_N1930

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

C623

21

4.7uF

2 1

C1724

25V-20%

.1uF

25V-20%

.1uF

2 1

C1725

2 1

12

C424

C1726

+

VRD2_DRV3

15

11

10

EN

PWRGD

ILIMIT

VRD2_VCC

8

VRD2_CTRL

VCC

RAMPADJ

RT

28

14

13

27

+12V

10-5%

1 2

R14

487K-1%

VRD2_PWM1A

VRD2_PWM2A

8

8

SUB=SUB*_G7300

5.1-5%

2 1

R267

1 2

R272

R300

1 2

200K-1%

8

VRD2_PWM3A

DRV2_OD

16V-10%

.47uF

1

BST

2

IN

3

OD

4

VCC

ADP3418

.22uF 25V

1 2

20%

C598

C11

21

DRVH

SW

PGND

DRVL

8

7

6

5

VRD2_UGATE3

VRD2_LGATE3

R500

1 2

4.7K

R493

1 2

4.7K

Q67

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

Q45

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

16V-10%

560uF

4V-20%

2 1

4.7uF

C328

+CPU_VID2

L5

1 2

R182

1 2

21

C299

SUB*_16155

X02_TJ_110503

0.6uH, 27Amp

3-5%

.001UF

SUB=SUB*_N1453

50V-10%

Q93

3

FT2N7002LT1

1

2

5.1-5%

R262

R1991

1 2

1K-5%

X03_GT_012604

20%

1N914

D34

31

1 2

8

8

2-1%

VRD2_PWM4A

DRV2_OD

R246

SUB=SUB*_G7300

12

.22uF 25V

20%

C10

21

.22uF 25V

C649

21

1

BST

2

IN

3

OD

4

VCC

Phase 4

ROOM = VRD2_PHASE4

VRD2_PHASE4B_SENSE

8

50V-10%

1000pF

VRD2_DRV4

ADP3418

x03_sd

C859

21

C475

1 2

.1uF

25V-20%

NP*21

DRVH

SW

PGND

DRVL

8

7

6

5

21

R486

VRD2_LGATE4

R485

4.7K

Q50

4

3

2

1

9

G

S

FDS7096N3

D

SUB*_N1930

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

1 2

16V-10%

4.7uF

C617

2 1

C1716

25V-20%

.1uF

25V-20%

.1uF

C1717

12

12

C1718

Q51

4

3

2

1

9

G

S

FDS7096N3

D

SUB*_N1930

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

.22uF 25V

20%

16V-10%

C618

21

4.7uF

A03_121704_GT

2 1

C1719

25V-20%

.1uF

25V-20%

.1uF

C1720

12

12

C425

C1721

12

+

16V-10%

560uF

4V-20%

2 1

4.7uF

C309

+CPU_VID2

L18

SUB=SUB*_N1453

0.6uH, 27Amp

1 2

VRD2_UGATE4

Q49

4

3

2

1

9

D

G

S

NC

5

6

7

8

21

FDS7066SN3

4.7K

SUB*_T1564

PKG_TYPE=SO8_P9DR_FRCHLD

Q48

4

3

2

1

9

D

G

S

FDS7066SN3

SUB*_T1564

5

6

7

8

NC

PKG_TYPE=SO8_P9DR_FRCHLD

R178

C284

21

3-5%

21

.001UF

50V-10%

3

VID Termination

R316

0-5%

1 2

8

8

8

R350

1 2

21

75K-1%

0-5%

R298

75K-1%

21

C721

50V-10%

SUB*_1U388

1 2

4700pF

C711

R148

21

15.8K-1% 0-5%

THERMISTOR

R349

0-5%

21

75K-1%

R295

R293

21

X04_GT_031904

R87

1 2

29.4K-1%

R332

1 2

21

75K-1%

21

X04_GT_031904

X04_GT_031904

VRD2_PHASE1B_SENSE

VRD2_PHASE2B_SENSE

VRD2_PHASE3B_SENSE

VRD2_PHASE4B_SENSE

R294

R86