5

4

3

2

1

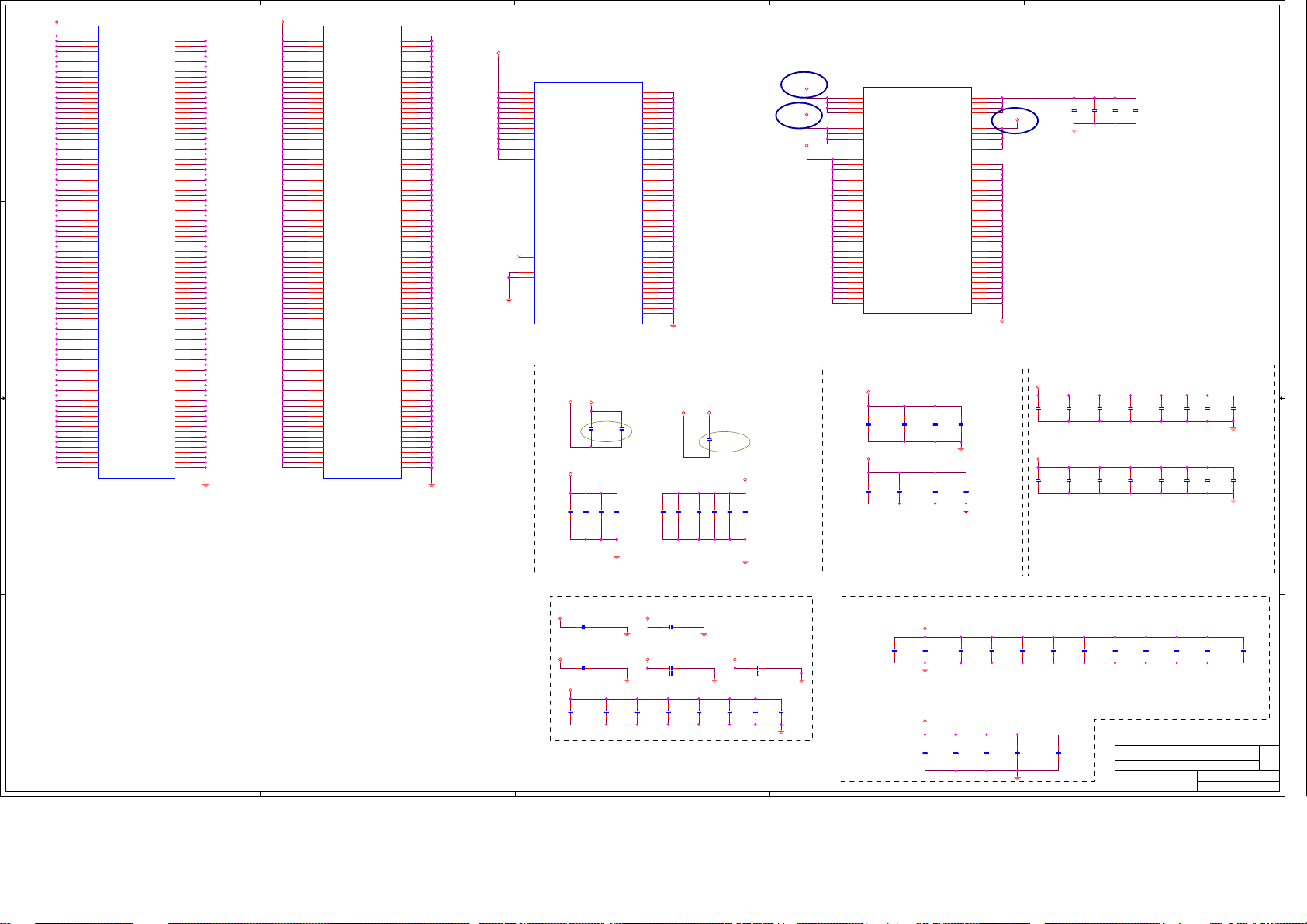

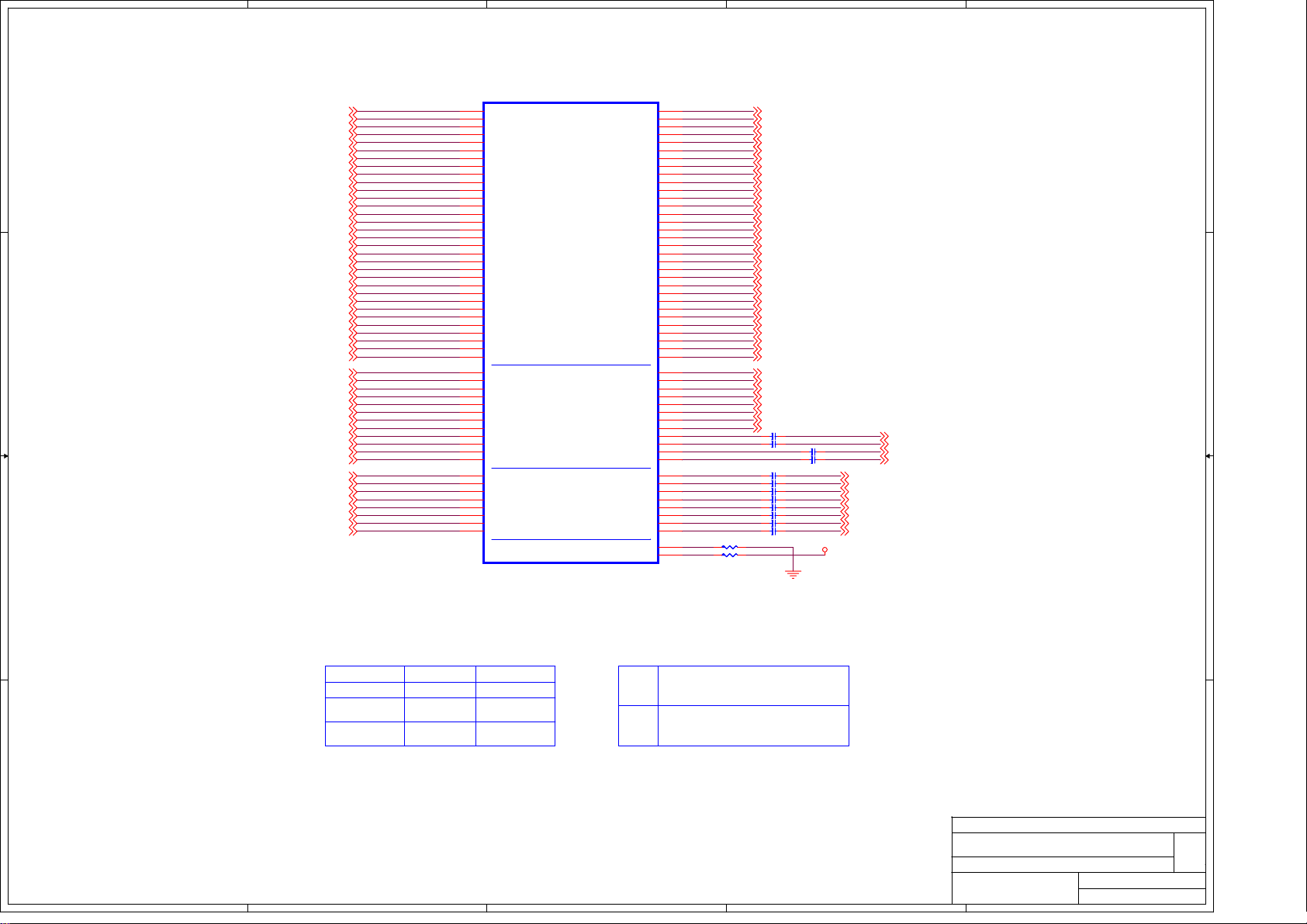

MSI

D D

CPU

System Chipset

MS-7599

Ver:3.1

AMD M3 Phenom/Athlon 64 FX AM3

AMD RX780/RX880

ATI SB810/850

Title Page

Cover Sheet 1

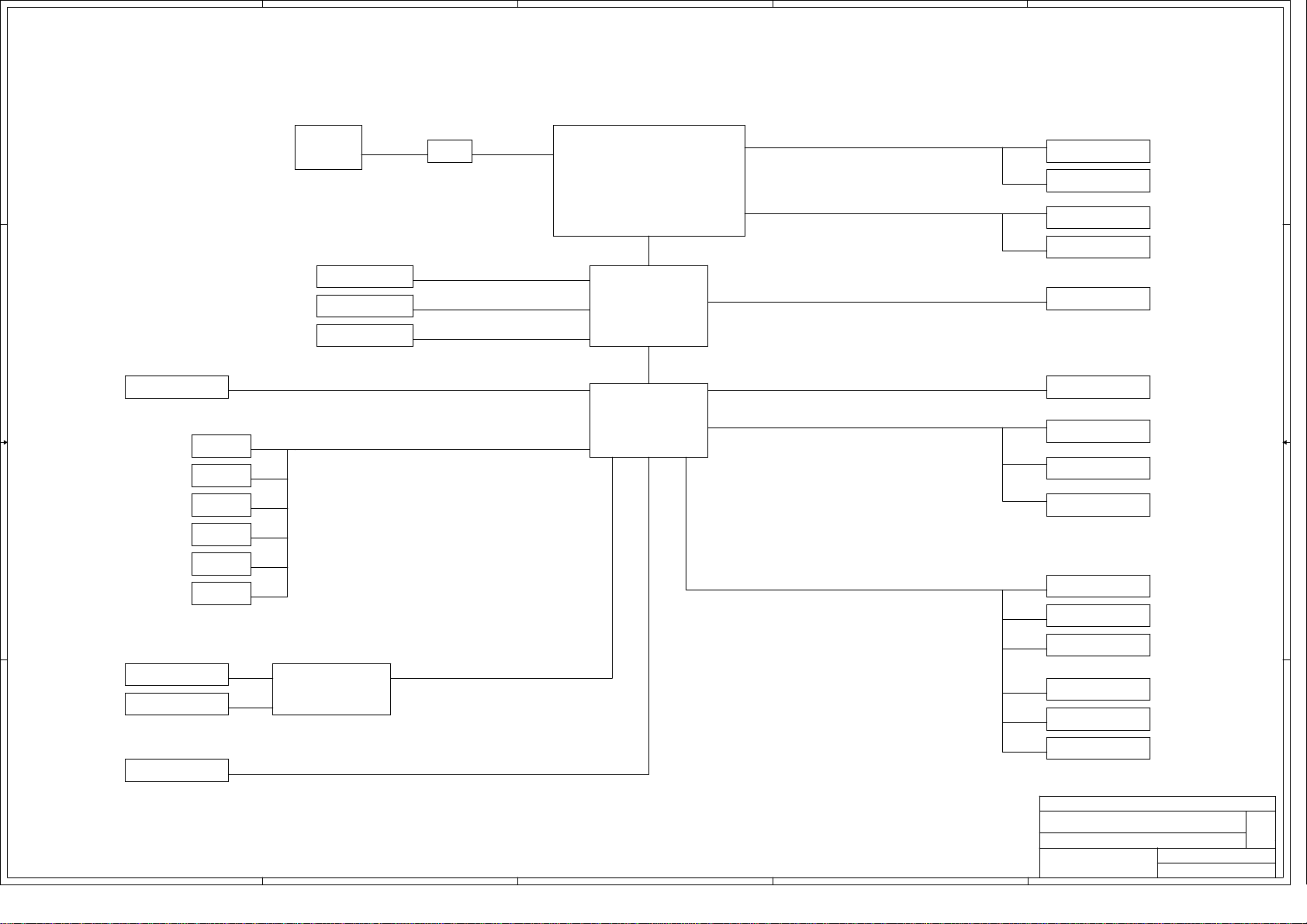

Block Diagram

AMD AM3 941

System Memory

2

3-5

6-7

ATI RX780/RX880 8-12

CLOCK GENERATOR RTM880N-793 13

On Board Chip

FINTEK Super I/O -- F71889ED

LAN -- RTL8111DL

HD Codec --ALC892

C C

BIOS -- SPI ROM 8M

Main Memory

DDR III X 4 (Max 8GB)

Expansion Slots

PCI-E X 16*1

PCI-E X 4 *1

PCI-E X 1 *1

PCI 2.2 Slot X 3

B B

PWM

Controller--Intersil ISL6323 4+1 Phase

Vcore 4 Phase (MOS HIGHX2 LOWX2)

Vnb 1 Phase (MOS HIGHX1 LOWX2)

ATI SB810/850 14-18

PCI Slot 1,2,3

19

PCI-E X16 Slot 2 20-21

PCI-EX4 Slot and PCI-EX1 Slot

LAN RTL8111DL

HD Audio - ALC892

IDE&FAN

UPI ACPI

USB connectors

I/O F71889ED / FDD

ATX Connector&Front Panel& KB

PWM - ISL6323A

VCC_DDR&1P1V_CORE

MANUAL PARTS

JMB368 IDE

NEC720200 USB3.0

POWER MAP

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35POWER OK MAP

Clock Generator

Controller--RTM880N-793

Clock Map

RESET MAP&Power Sequence

36

37

38

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

Cover Sheet

Cover Sheet

Cover Sheet

1

MS-7599

MS-7599

MS-7599

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, March 04, 2010

Thursday, March 04, 2010

Thursday, March 04, 2010

Sheet

Sheet

Sheet

Rev

Rev

Rev

10

10

10

138

138

138

of

of

of

5

4

3

2

1

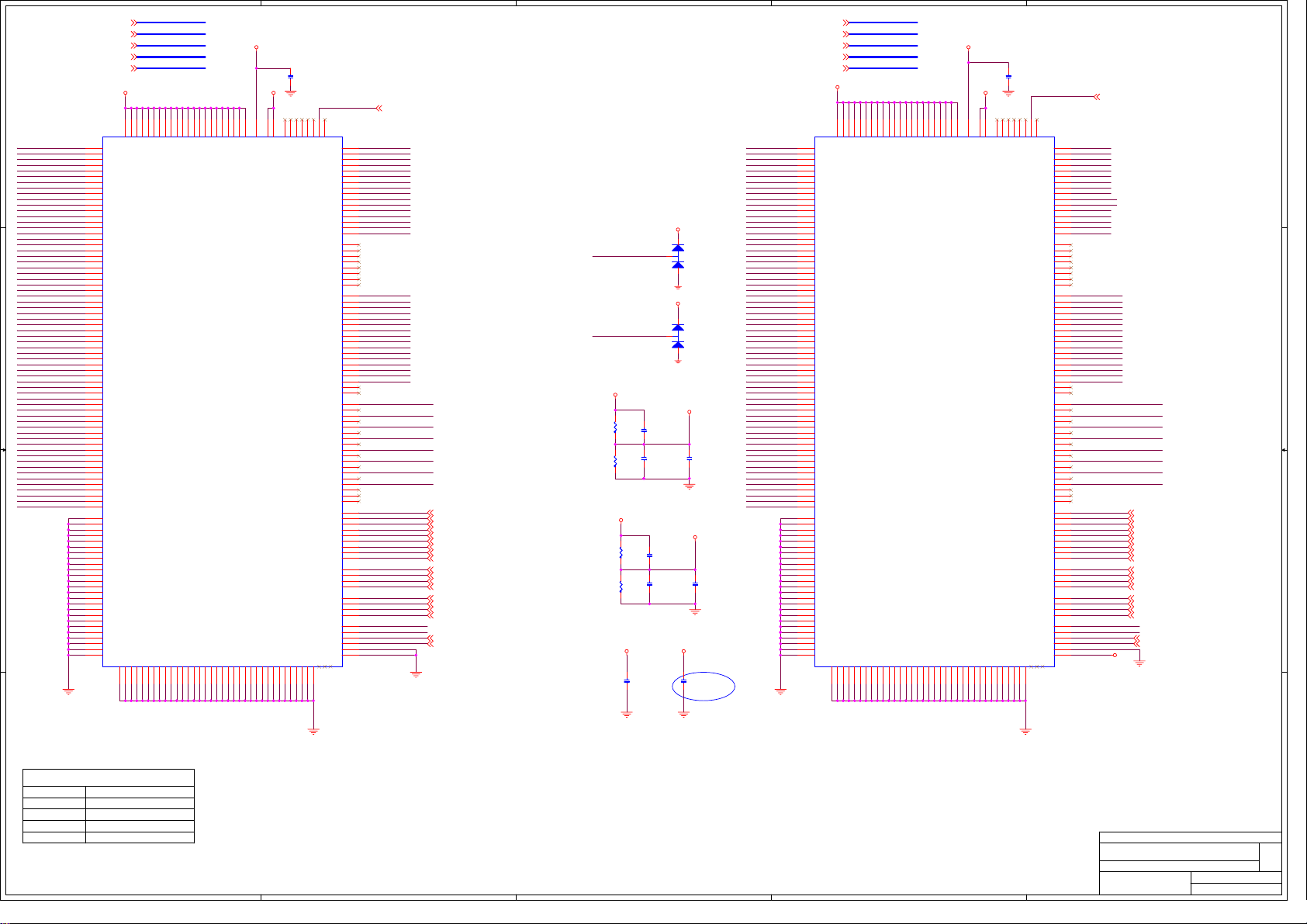

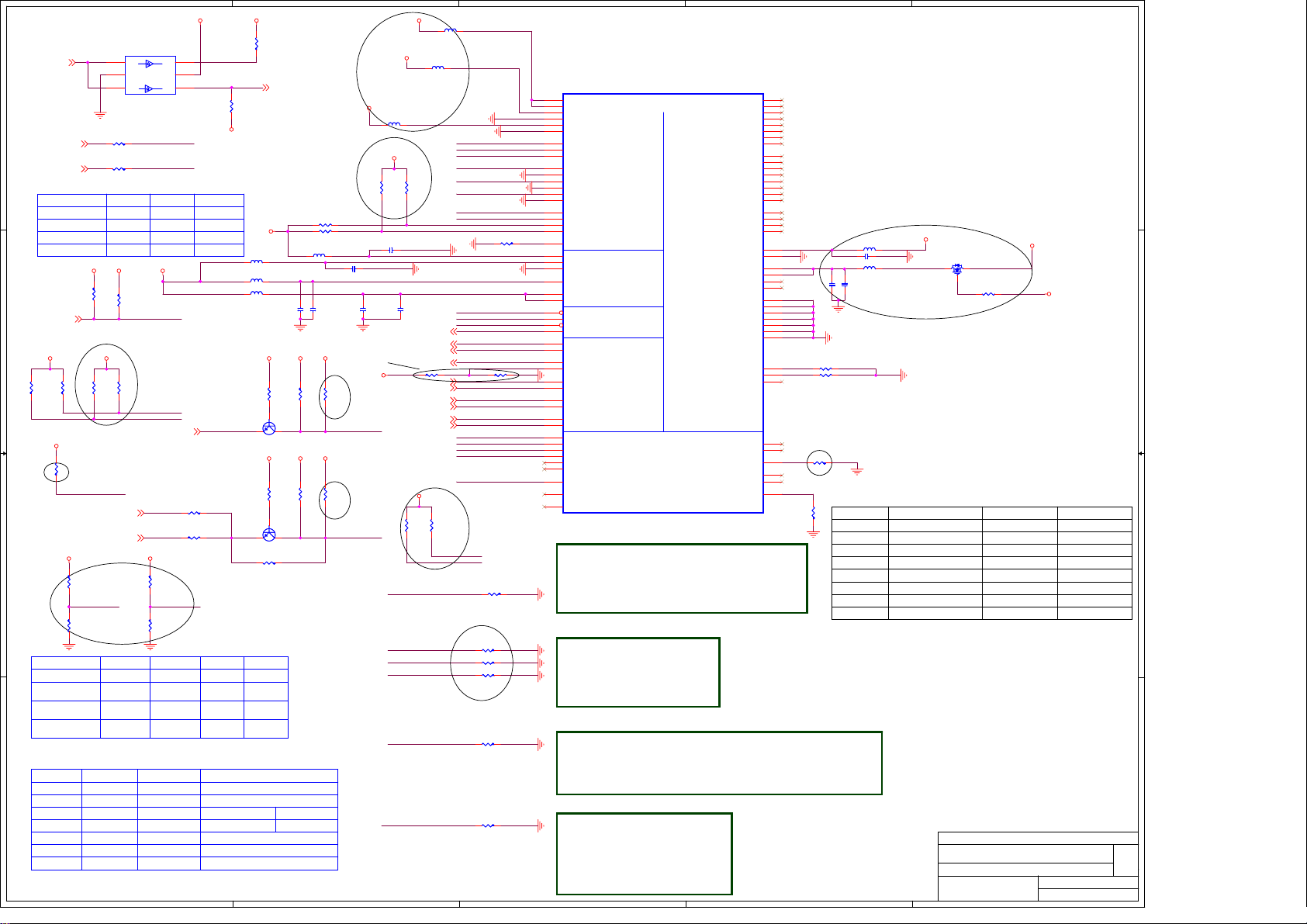

BLOCK DIAGRAM

D D

POWER

SUPPLY

CONNECTOR

VREG

SOCKET 940

K9

128-BIT 333/400MHZ

DDR SDRAM CONN 0

DDR SDRAM CONN 1

DDR SDRAM CONN 2

HT 16X16 2.6GHZ(HT3)

PEX X16

PEX X1

C C

PRIMARY IDE

SATA CONN

SATA CONN

SATA CONN

SATA CONN

B B

FLOPPY CONN SIO

PS2/KBRD CONN

SATA CONN

SATA CONN

LPC SUPER I/O

F71882

PEX X1

ATA 133

INTEGRATED SATA 1/2

PCI EXPRESS

PCI EXPRESS

PCI EXPRESS

LPC BUS 33MHZ

ATI

RX780

ALINK *4

ATI

SB700/750

PCI EXPRESS LAN-RTL8111C

AZAILIA

PCI 33MHZ

DDR SDRAM CONN 3

Realtek ALC 888

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

BACK PANEL CONN

USB2 PORTS 0-1X12 USB2.0 (SB700/750)

USB2 PORTS 2-3

USB2 PORTS 4-5

FRONT PANEL HDR

USB2 PORTS 6-7

USB2 PORTS 8-9

USB2 PORTS 10-11

A A

8MB SPI FLASH

5

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

4

3

2

http://www.msi.com.tw

Block Diagram

Block Diagram

Block Diagram

MS-7599

MS-7599

MS-7599

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Tuesday, March 02, 2010

2

2

2

Rev

Rev

Rev

10

10

10

38

38

38

of

of

of

5

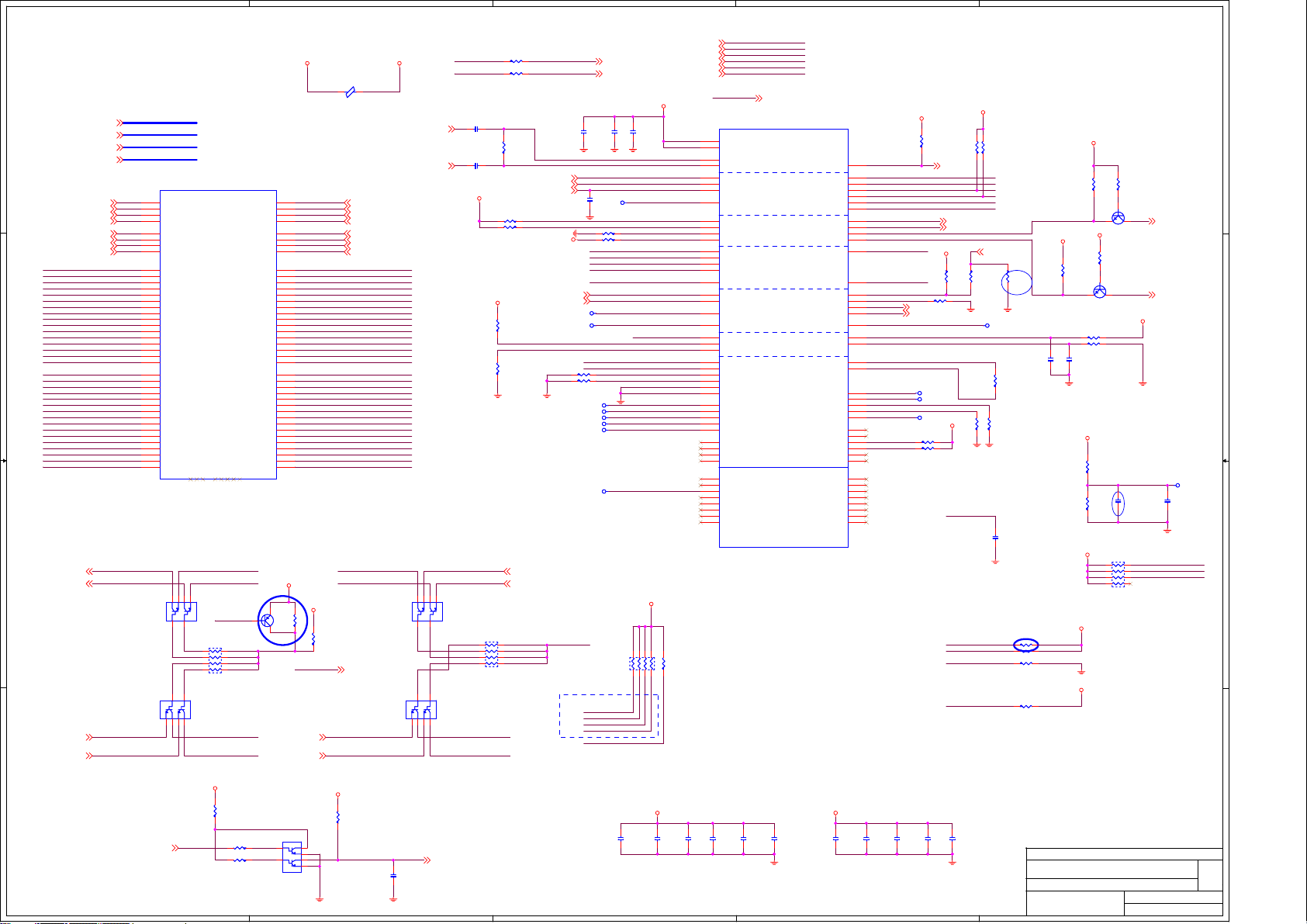

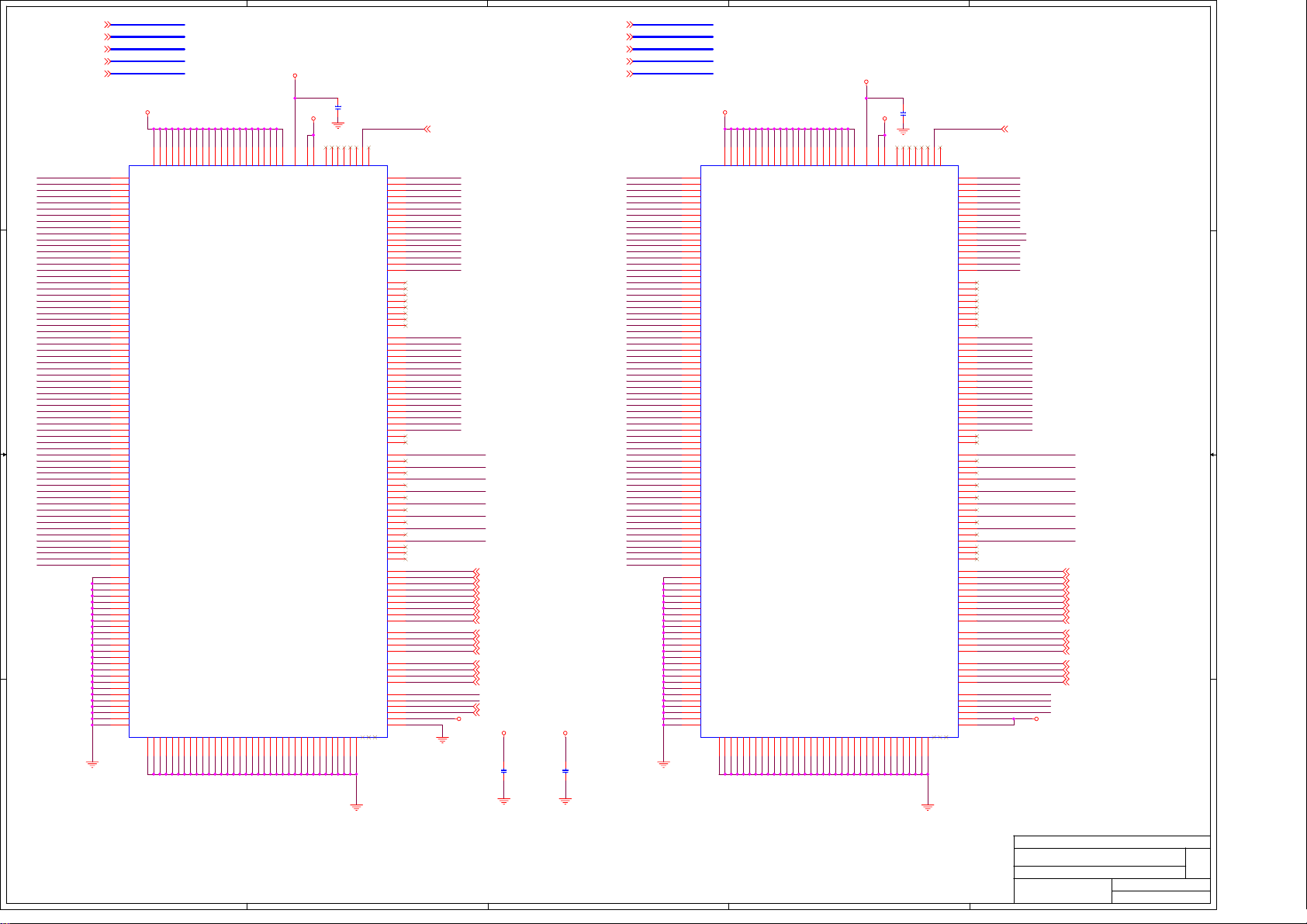

D D

C C

HT_CADIN_H[15..0]8

HT_CADIN_L[15..0]8

HT_CADOUT_H[15..0]8

HT_CADOUT_L[15..0]8

HT_CLKIN_H18

HT_CLKIN_L18

HT_CLKIN_H08

HT_CLKIN_L08

HT_CTLIN_H18

HT_CTLIN_L18

HT_CTLIN_H08

HT_CTLIN_L08

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

CPU1A

CPU1A

N6

L0_CLKIN_H1

P6

L0_CLKIN_L1

N3

L0_CLKIN_H0

N2

L0_CLKIN_L0

V4

L0_CTLIN_H1

V5

L0_CTLIN_L1

U1

L0_CTLIN_H0

V1

L0_CTLIN_L0

U6

L0_CADIN_H15

V6

L0_CADIN_L15

T4

L0_CADIN_H14

T5

L0_CADIN_L14

R6

L0_CADIN_H13

T6

L0_CADIN_L13

P4

L0_CADIN_H12

P5

L0_CADIN_L12

M4

L0_CADIN_H11

M5

L0_CADIN_L11

L6

L0_CADIN_H10

M6

L0_CADIN_L10

K4

L0_CADIN_H9

K5

L0_CADIN_L9

J6

L0_CADIN_H8

K6

L0_CADIN_L8

U3

L0_CADIN_H7

U2

L0_CADIN_L7

R1

L0_CADIN_H6

T1

L0_CADIN_L6

R3

L0_CADIN_H5

R2

L0_CADIN_L5

N1

L0_CADIN_H4

P1

L0_CADIN_L4

L1

L0_CADIN_H3

M1

L0_CADIN_L3

L3

L0_CADIN_H2

L2

L0_CADIN_L2

J1

L0_CADIN_H1

K1

L0_CADIN_L1

J3

L0_CADIN_H0

J2

L0_CADIN_L0

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_H0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

HT LINK

HT LINK

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

112233445566778

L0_CTLOUT_L1

L0_CTLOUT_L0

8

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

CPU output pin:TDO,DBRDY ;OTHERS :INPUT

IMC_TDI

B B

IMC_TDI16

IMC_DBRDY16

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

IMC_TDO16

IMC_TCK16

IMC_DBRDY

IMC_TDO

IMC_TCK

Q38

Q38

Q37

Q37

4

CPU_TDO

CPU_DBRDY

4

6

1

3

IMC_HDTEL

5

2

RN4

RN4

1

2

3

4

5

6

7

8

8P4R-10KR0402

8P4R-10KR0402

5

2

6

1

3

CPU_TDI

CPU_TCK

B

+1.8V_S0

Q79

Q79

C E

P-PMBS3906

P-PMBS3906

+1.8V_S0_CTL

IMC_DBREQ_L16

VCC_DDR

R720

R720

R721

R721

X_0R

X_0R

X_0R

X_0R

IMC_HDTEL

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

IMC_TMS16

4

VDDA25VDDA_25

L1

L1

80L2A-100_0805-RH

80L2A-100_0805-RH

CPU_CLK13

CPU_CLK#13

HT_CLKOUT_H1 8

HT_CLKOUT_L1 8

HT_CLKOUT_H0 8

HT_CLKOUT_L0 8

HT_CTLOUT_H1 8

HT_CTLOUT_L1 8

HT_CTLOUT_H0 8

HT_CTLOUT_L0 8

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

LDT_RST#

CPU_TRST_L IMC_TRST_L

Q41

NN-CMKT3904_SOT363-6-RH

NN-CMKT3904_SOT363-6-RH

IMC_DBREQ_L

IMC_TMS

Q41

IMC_HDTEL 16,27

Q40

Q40

4

6

1

3

5

2

5

2

4

6

1

3

THERM_SIC

THERM_SID

C93

C93

C3900p50X

C3900p50X

C95

C95

C3900p50X

C3900p50X

VCC_DDR

IMC_CRST_L

1

3

5

7

CPU_DBREQ_L

CPU_TMS

R159 0R0402R159 0R0402

R156 0R0402R156 0R0402

R126

R126

169R1%

169R1%

R157 1KR0402R157 1KR0402

R153 1KR0402R153 1KR0402

VCC_DDR

R155

R155

39.2R1%

39.2R1%

R145

R145

39.2R1%

39.2R1%

IMC_CRST_L 16

IMC_TRST_L 16

RN5

RN5

2

4

6

8

8P4R-10KR0402

8P4R-10KR0402

THERM_SIC_R

THERM_SID_R

C84

C84

C4.7u16Y1206

C4.7u16Y1206

CPUCLKIN

CPUCLKIN#

LDT_PWRGD14

LDT_STOP#10,14

LDT_RST#10,14

C162

C162

X_C1000p50X

X_C1000p50X

THERM_SIC

THERM_SID

VCC_DDR

COREFB+29

COREFB-29

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

R122 300R0402R122 300R0402

R123 300R0402R123 300R0402

+1.8V_S0_CTL

CPU internal pull up

3

THERM_SIC_R 27

THERM_SID_R 27

C87

C87

C0.22u16X

C0.22u16X

LDT_PWRGD

LDT_STOP#

LDT_RST#

TP18TP18

R142 0R0402R142 0R0402

R158 X_1KR0402R158 X_1KR0402

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

COREFB+

COREFB-

TP1TP1

M_VDDIO_PWRGD

TP13TP13

CPU_VDDR_SENSE

CPU_TEST25_H

CPU_TEST25_L

TP8TP8

TP9TP9

TP12TP12

TP7TP7

TP14TP14

TP11TP11

RN3

RN3

X_8P4R-1KR0402

X_8P4R-1KR0402

CPU_TRST_L

CPU_TDI

CPU_TCK

CPU_TMS

CPU_DBREQ_L

C91

C91

C3300p50X0402

C3300p50X0402

CPU_PRESENT_L

CPU_M_VREF

CPU_TEST19

CPU_TEST18

CPU_TEST17

CPU_TEST16

CPU_TEST15

CPU_TEST14

CPU_TEST12

CPU_RSVD3

VCC_DDR

7

8

VDDA25

CPU_SA0

ALERT_L

135

246

R124

R124

300R0402

300R0402

VID0/VFIXEN29

VID3/SVC29

VID2/SVD29

VID1/SEL29

AL10

AJ10

AH10

AH11

AJ11

VID529

VID429

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AK4

AL4

AL9

A5

G2

G1

F3

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AH7

AJ6

C18

C20

F2

G24

G25

H25

L25

L26

CPU_HOT

VDDA_1

VDDA_2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

SA0

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

M_VDDIO_PWRGD

VDDR_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

CPU_HOT 14

CPU1D

CPU1D

MISC.

MISC.

INT. MISC.

INT. MISC.

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

CORE_TYPE

SVC/VID3

SVD/VID2

PVIEN/VID1

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

VID5

VID4

VID0

TDO

2

CPU_CORE_TYPE

G5

D2

D1

C1

E3

E2

E1

AG9

AG8

AK7

AL7

AK10

B6

AK11

AL11

G4

G3

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

VID5

VID4

VID3/SVC

VID2/SVD

VID1/SEL

VID0/VFIXEN

THERMDC_CPU

THERMDA_CPU

CPU_HOT

CPU_TDO

CPU_DBRDY

CPU_PSI_L

HTREF1

HTREF0

CPU_TEST29_H

CPU_TEST29_L

CPU_TEST24

CPU_TEST23

CPU_TEST22

CPU_TEST21

CPU_TEST20

CPU_TEST27

CPU_TEST26

VCC_DDR

R109

R109

1KR0402

1KR0402

CPU_CORE_TYPE 29

VCC_DDR

R163

R163

0R0402

0R0402

V_NB 29

V_GND 29

TP17TP17

TP15TP15

TP16TP16

VCC_DDR

R164 X_300R0402R164 X_300R0402

R150 300R0402R150 300R0402

VCC_DDR

R113

R113

300R0402

300R0402

THERMDC_CPU 27

THERMDA_CPU 27

R162

R162

R161

R161

X_0R0402

X_0R0402

0R0402

0R0402

R118

R118

80.6R1%

80.6R1%

R143

R143

300R0402

300R0402

CPU_DBREQ_L

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

M_VDDIO_PWRGD

R116

R116

300R0402

300R0402

VCC_DDR_FB 30

R231

R231

X_0R0402

X_0R0402

TP10TP10

C141

C141

C1000p50X0402

C1000p50X0402

R144

R144

300R0402

300R0402

C169

C169

X_C0.1u25Y

X_C0.1u25Y

R160 10KR0402R160 10KR0402

R111 510R0402R111 510R0402

R110 510R0402R110 510R0402

R106 1KR0402R106 1KR0402

CPU_THRIP_L#

VCC_DDR

R147

R147

300R0402

300R0402

R151 44.2R1%R151 44.2R1%

R152 44.2R1%R152 44.2R1%

VCC_DDR

VCC_DDR

C142

C142

C1000p50X0402

C1000p50X0402

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

1

R175

R175

300R0402

300R0402

B

R177

R177

4.7KR0402

4.7KR0402

B

Q35

Q35

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

CE

R119

R119

15R1%

15R1%

CPU_M_VREF

R117

R117

15R1%

15R1%

C1u6.3X50402-HF

C1u6.3X50402-HF

RN2

RN2

1

3

5

7

8P4R-300R-RH

8P4R-300R-RH

R169

R169

4.7KR0402

4.7KR0402

Q34

Q34

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

CE

CPU_THRIP# 16

TALERT# 13,15,27

1P2V_HT

C88

C92

C92

2

4

6

8

C88

C1000p50X

C1000p50X

LDT_PWRGD

LDT_RST#

LDT_STOP#

TP2TP2

VCC5_SB

A A

LDT_PWRGD14

5

4.7KR0402

4.7KR0402

R28

R28

R35 4.7KR0402R35 4.7KR0402

R9 4.7KR0402R9 4.7KR0402

Q2Q2

2

5

VCC3

R29

R29

4.7KR0402

4.7KR0402

C4.7u10Y0805

6

1

3

4

4

PWROK_PWM 29

C5

C5

X_C100p50N0402

X_C100p50N0402

C4.7u10Y0805

1P2V_HT 1P2V_HT

C150

C150

C147

C156

C156

C138

C138

C0.22u16X

C0.22u16X

3

C144

C144

C0.22u16X

C0.22u16X

C147

X_C0.22u16X

X_C0.22u16X

X_C0.22u16X

X_C0.22u16X

C153

C153

C4.7u10Y0805

C4.7u10Y0805

C336

C336

C4.7u10Y0805

C4.7u10Y0805

C185

C185

C4.7u10Y0805

C4.7u10Y0805

2

C182

C182

C0.22u16X

C0.22u16X

C357

C357

X_C0.22u16X

X_C0.22u16X

C175

C175

X_C0.22u16X

X_C0.22u16X

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

AM3 HT I/F,CTRL&DEBUG

AM3 HT I/F,CTRL&DEBUG

AM3 HT I/F,CTRL&DEBUG

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7599

MS-7599

MS-7599

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Sheet

Sheet

Sheet

338

338

338

Rev

Rev

Rev

10

10

10

of

of

of

5

4

3

2

1

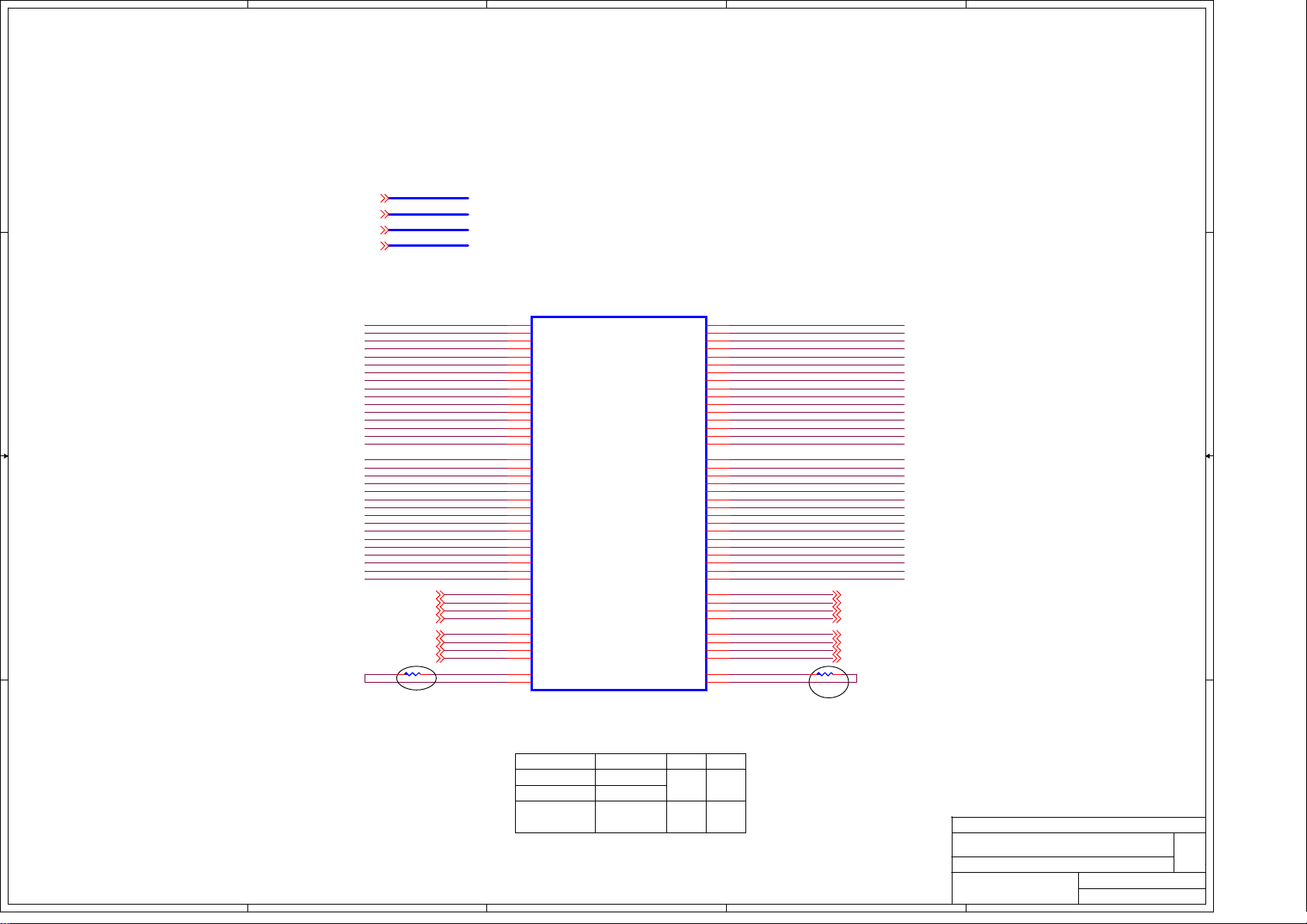

MEM_MA_DQS_L[7..0]6,7 MEM_MB_DQS_L[7..0]6,7

MEM_MA_DQS_H[7..0]6,7

MEM_MA_DM[7..0]6,7

MEM_MA_ADD[15..0]6,7

D D

MEM_MA1_CLK_H17

MEM_MA1_CLK_L17

MEM_MA0_CLK_H06

MEM_MA0_CLK_L06

MEM_MA1_CLK_H07

MEM_MA1_CLK_L07

MEM_MA0_CLK_H16

MEM_MA0_CLK_L16

MEM_MA0_CS_L16

MEM_MA0_CS_L06

MEM_MA0_ODT16

MEM_MA0_ODT06

MEM_MA1_CS_L17

C C

B B

A A

MEM_MA1_CS_L07

MEM_MA1_ODT17

MEM_MA1_ODT07

MEM_MA_RESET#6,7

MEM_MA_CAS_L6,7

MEM_MA_WE_L6,7

MEM_MA_RAS_L6,7

MEM_MA_BANK26,7

MEM_MA_BANK16,7

MEM_MA_BANK06,7

MEM_MA_CKE16,7

MEM_MA_CKE06,7

MEM_MA_DATA[63..0]6,7

MEM_MA1_CLK_H1

MEM_MA1_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA1_CLK_H0

MEM_MA1_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT1

MEM_MA0_ODT0

MEM_MA1_CS_L1

MEM_MA1_CS_L0

MEM_MA1_ODT1

MEM_MA1_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_L[7..0] MEM_MB_DQS_L[7..0]

MEM_MA_DQS_H[7..0]

MEM_MA_DM[7..0]

MEM_MA_ADD[15..0]

MEM_MA_DATA[63..0]

CPU1B

CPU1B

AG21

MA_CLK_H7

AG20

MA_CLK_L7

AE20

MA_CLK_H6

AE19

MA_CLK_L6

U27

MA_CLK_H5

U26

MA_CLK_L5

V27

MA_CLK_H4

W27

MA_CLK_L4

W26

MA_CLK_H3

W25

MA_CLK_L3

U24

MA_CLK_H2

V24

MA_CLK_L2

G19

MA_CLK_H1

H19

MA_CLK_L1

G20

MA_CLK_H0

G21

MA_CLK_L0

AC25

MA0_CS_L1

AA24

MA0_CS_L0

AE28

MA0_ODT1

AC28

MA0_ODT0

AD27

MA1_CS_L1

AA25

MA1_CS_L0

AE27

MA1_ODT1

AC27

MA1_ODT0

E20

MA_RESET_L

AB25

MA_CAS_L

AB27

MA_WE_L

AA26

MA_RAS_L

N25

MA_BANK2

Y27

MA_BANK1

AA27

MA_BANK0

L27

MA_CKE1

M25

MA_CKE0

M27

MA_ADD15

N24

MA_ADD14

AC26

MA_ADD13

N26

MA_ADD12

P25

MA_ADD11

Y25

MA_ADD10

N27

MA_ADD9

R24

MA_ADD8

P27

MA_ADD7

R25

MA_ADD6

R26

MA_ADD5

R27

MA_ADD4

T25

MA_ADD3

U25

MA_ADD2

T27

MA_ADD1

W24

MA_ADD0

AD15

MA_DQS_H7

AE15

MA_DQS_L7

AG18

MA_DQS_H6

AG19

MA_DQS_L6

AG24

MA_DQS_H5

AG25

MA_DQS_L5

AG27

MA_DQS_H4

AG28

MA_DQS_L4

D29

MA_DQS_H3

C29

MA_DQS_L3

C25

MA_DQS_H2

D25

MA_DQS_L2

E19

MA_DQS_H1

F19

MA_DQS_L1

F15

MA_DQS_H0

G15

MA_DQS_L0

AF15

MA_DM7

AF19

MA_DM6

AJ25

MA_DM5

AH29

MA_DM4

B29

MA_DM3

E24

MA_DM2

E18

MA_DM1

H15

MA_DM0

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MEM CHA

MEM CHA

MA_DATA11

MA_DATA10

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

W30

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

1KR0402

1KR0402

MEM_MA_EVENT_L

R140

R140

MEM_MA_EVENT_L 6,7

MEM_MB_DQS_H[7..0]6,7

MEM_MB_DM[7..0]6,7

MEM_MB_ADD[15..0]6,7

MEM_MB_DATA[63..0]6,7

MEM_MB1_CLK_H17

MEM_MB1_CLK_L17

MEM_MB0_CLK_H06

MEM_MB0_CLK_L06

MEM_MB1_CLK_H07

MEM_MB1_CLK_L07

MEM_MB0_CLK_H16

MEM_MB0_CLK_L16

MEM_MB0_CS_L16

MEM_MB0_CS_L06

MEM_MB0_ODT16

MEM_MB0_ODT06

MEM_MB1_CS_L17

MEM_MB1_CS_L07

MEM_MB1_ODT17

MEM_MB1_ODT07

MEM_MB_RESET#6,7

MEM_MB_CAS_L6,7

MEM_MB_WE_L6,7

MEM_MB_RAS_L6,7

MEM_MB_BANK26,7

MEM_MB_BANK16,7

MEM_MB_BANK06,7

MEM_MB_CKE16,7

MEM_MB_CKE06,7

MEM_MB_DQS_H[7..0]

MEM_MB_DM[7..0]

MEM_MB_ADD[15..0]

MEM_MB_DATA[63..0]

MEM_MB1_CLK_H1

MEM_MB1_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB1_CLK_H0

MEM_MB1_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT1

MEM_MB0_ODT0

MEM_MB1_CS_L1

MEM_MB1_CS_L0

MEM_MB1_ODT1

MEM_MB1_ODT0

MEM_MB_RESET#MEM_MA_RESET#

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AL19

AL18

W29

W28

W31

AE30

AC31

AF31

AD29

AE29

AB31

AG31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

U31

U30

Y31

Y30

V31

A18

A19

C19

D19

B19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

CPU1C

CPU1C

MB_CLK_H7

MB_CLK_L7

MB_CLK_H6

MB_CLK_L6

MB_CLK_H5

MB_CLK_L5

MB_CLK_H4

MB_CLK_L4

MB_CLK_H3

MB_CLK_L3

MB_CLK_H2

MB_CLK_L2

MB_CLK_H1

MB_CLK_L1

MB_CLK_H0

MB_CLK_L0

MB0_CS_L1

MB0_CS_L0

MB0_ODT1

MB0_ODT0

MB1_CS_L1

MB1_CS_L0

MB1_ODT1

MB1_ODT0

MB_RESET_L

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK2

MB_BANK1

MB_BANK0

MB_CKE1

MB_CKE0

MB_ADD15

MB_ADD14

MB_ADD13

MB_ADD12

MB_ADD11

MB_ADD10

MB_ADD9

MB_ADD8

MB_ADD7

MB_ADD6

MB_ADD5

MB_ADD4

MB_ADD3

MB_ADD2

MB_ADD1

MB_ADD0

MB_DQS_H7

MB_DQS_L7

MB_DQS_H6

MB_DQS_L6

MB_DQS_H5

MB_DQS_L5

MB_DQS_H4

MB_DQS_L4

MB_DQS_H3

MB_DQS_L3

MB_DQS_H2

MB_DQS_L2

MB_DQS_H1

MB_DQS_L1

MB_DQS_H0

MB_DQS_L0

MB_DM7

MB_DM6

MB_DM5

MB_DM4

MB_DM3

MB_DM2

MB_DM1

MB_DM0

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MEM CHB

MEM CHB

MB_DATA10

MB_DATA9

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_EVENT_L

VCC_DDRVCC_DDR

R139

R139

1KR0402

1KR0402

MEM_MB_EVENT_L 6,7

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

AM3 DDR MEMORY I/F

AM3 DDR MEMORY I/F

AM3 DDR MEMORY I/F

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7599

MS-7599

MS-7599

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Sheet

Sheet

Sheet

438

438

438

Rev

Rev

Rev

10

10

10

of

of

of

VCCP

H11

D D

C C

B B

H23

J12

J14

J16

J18

J20

J22

J24

K11

K13

K15

K17

K19

K21

K23

L10

L12

L14

L16

L18

L20

L22

M11

M13

M15

M17

M19

M21

M23

N10

N12

N14

N16

N18

N20

N22

P11

P13

P15

P17

P19

P21

P23

R10

R12

R14

R16

R18

R20

R22

T11

T13

CPU1E

CPU1E

B3

VDD_1

C2

VDD_2

C4

VDD_3

D3

VDD_4

D5

VDD_5

E4

VDD_6

E6

VDD_7

F5

VDD_8

F7

VDD_9

G6

VDD_10

G8

VDD_11

H7

VDD_12

VDD_13

VDD_14

J8

VDD_15

VDD_16

VDD_17

VDD_18

VDD_19

VDD_20

VDD_21

VDD_22

K7

VDD_23

K9

VDD_24

VDD_25

VDD_26

VDD_27

VDD_28

VDD_29

VDD_30

VDD_31

L4

VDD_32

L5

VDD_33

L8

VDD_34

VDD_35

VDD_36

VDD_37

VDD_38

VDD_39

VDD_40

VDD_41

M2

VDD_42

M3

VDD_43

M7

VDD_44

M9

VDD_45

VDD_46

VDD_47

VDD_48

VDD_49

VDD_50

VDD_51

VDD_52

N8

VDD_53

VDD_54

VDD_55

VDD_56

VDD_57

VDD_58

VDD_59

VDD_60

P7

VDD_61

P9

VDD_62

VDD_63

VDD_64

VDD_65

VDD_66

VDD_67

VDD_68

VDD_69

R4

VDD_70

R5

VDD_71

R8

VDD_72

VDD_73

VDD_74

VDD_75

VDD_76

VDD_77

VDD_78

VDD_79

T2

VDD_80

T3

VDD_81

T7

VDD_82

T9

VDD_83

VDD_84

VDD_85

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

5

VSS_1

VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

POWER/GND1

POWER/GND1

VSS_52

VSS_53

VSS_54

VSS_55

VSS_56

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_63

VSS_64

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

A3

A7

A9

A11

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

VCCP

T15

T17

T19

T21

T23

U8

U10

U12

U14

U16

U18

U20

U22

V9

V11

V13

V15

V17

V19

V21

V23

W4

W5

W8

W10

W12

W14

W16

W18

W20

W22

Y2

Y3

Y7

Y9

Y11

Y13

Y15

Y17

Y19

Y21

Y23

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AC4

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC20

AC22

AD2

AD3

AD7

AD9

AD11

AD23

AE10

AE12

AF7

AF9

AF11

AG4

AG5

AG7

AH2

AH3

CPU1F

CPU1F

VDD_86

VDD_87

VDD_88

VDD_89

VDD_90

VDD_91

VDD_92

VDD_93

VDD_94

VDD_95

VDD_96

VDD_97

VDD_98

VDD_99

VDD_100

VDD_101

VDD_102

VDD_103

VDD_104

VDD_105

VDD_106

VDD_107

VDD_108

VDD_109

VDD_110

VDD_111

VDD_112

VDD_113

VDD_114

VDD_115

VDD_116

VDD_117

VDD_118

VDD_119

VDD_120

VDD_121

VDD_122

VDD_123

VDD_124

VDD_125

VDD_126

VDD_127

VDD_128

VDD_129

VDD_130

VDD_131

VDD_132

VDD_133

VDD_134

VDD_135

VDD_136

VDD_137

VDD_138

VDD_139

VDD_140

VDD_141

VDD_142

VDD_143

VDD_144

VDD_145

VDD_146

VDD_147

VDD_148

VDD_149

VDD_150

VDD_151

VDD_152

VDD_153

VDD_154

VDD_155

VDD_156

VDD_157

VDD_158

VDD_159

VDD_160

VDD_161

VDD_162

VDD_163

VDD_164

VDD_165

VDD_166

VDD_167

VDD_168

VDD_169

VDD_170

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

4

M12

VSS_86

M14

VSS_87

M16

VSS_88

M18

VSS_89

M20

VSS_90

M22

VSS_91

N4

VSS_92

N5

VSS_93

N7

VSS_94

N9

VSS_95

N11

VSS_96

N13

VSS_97

N15

VSS_98

N17

VSS_99

N19

VSS_100

N21

VSS_101

N23

VSS_102

P2

VSS_103

P3

VSS_104

P8

VSS_105

P10

VSS_106

P12

VSS_107

P14

VSS_108

P16

VSS_109

P18

VSS_110

P20

VSS_111

P22

VSS_112

R7

VSS_113

R9

VSS_114

R11

VSS_115

R13

VSS_116

R15

VSS_117

R17

VSS_118

R19

VSS_119

R21

VSS_120

R23

VSS_121

T8

VSS_122

T10

VSS_123

T12

VSS_124

T14

VSS_125

T16

VSS_126

T18

VSS_127

T20

VSS_128

T22

VSS_129

U4

VSS_130

U5

VSS_131

U7

VSS_132

U9

VSS_133

U11

VSS_134

U13

VSS_135

POWER/GND2

POWER/GND2

U15

VSS_136

U17

VSS_137

U19

VSS_138

U21

VSS_139

U23

VSS_140

V2

VSS_141

V3

VSS_142

V10

VSS_143

V12

VSS_144

V14

VSS_145

V16

VSS_146

V18

VSS_147

V20

VSS_148

V22

VSS_149

W7

VSS_150

W9

VSS_151

W11

VSS_152

W13

VSS_153

W15

VSS_154

W17

VSS_155

W19

VSS_156

W21

VSS_157

W23

VSS_158

Y8

VSS_159

Y10

VSS_160

Y12

VSS_161

Y14

VSS_162

Y16

VSS_163

Y18

VSS_164

Y20

VSS_165

Y22

VSS_166

AA4

VSS_167

AA5

VSS_168

AA7

VSS_169

AA9

VSS_170

VCCP_NB

A4

A6

B5

B7

C6

C8

D7

D9

E8

E10

F9

F11

G10

G12

B2

H20

AE7

CPU1G

CPU1G

VDDNB_1

VDDNB_2

VDDNB_3

VDDNB_4

VDDNB_5

VDDNB_6

VDDNB_7

VDDNB_8

VDDNB_9

VDDNB_10

VDDNB_11

VDDNB_12

VDDNB_13

VDDNB_14

NP/RSVD

NP/VSS1

NP/VSS2

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

POWER/GND3

POWER/GND3

FOR EMI

VCC_DDR

VCCP

C2.2u6.3X5

C2.2u6.3X5

VCC_DDR

C121

C121

C135

C135

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C0.1u25Y0402-RH

BOTTOM

C567

C567

C117

C117

C146

C146

C0.1u25Y0402-RH

C0.1u25Y0402-RH

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C590

C590

C2.2u6.3X5

C2.2u6.3X5

3

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

VCCP

VCCP_NB

C103

C103

X_C2.2u6.3X5

X_C2.2u6.3X5

VCC_DDR

C151

C151

C119

C119

C180p50N0402

C180p50N0402

C137

C137

C134

C134

C139

C139

C115

C115

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

1P2V_HT

CPU_VDDR

VCC_DDR

M24

M26

M28

M30

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

X_C0.22u16X

X_C0.22u16X

CPU1H

CPU1H

AJ1

VLDT_A_1

AJ2

VLDT_A_2

AJ3

VLDT_A_3

AJ4

VLDT_A_4

A12

VDDR_1

B12

VDDR_2

C12

VDDR_3

D12

VDDR_4

VDDIO_1

VDDIO_2

VDDIO_3

VDDIO_4

P24

VDDIO_5

P26

VDDIO_6

P28

VDDIO_7

P30

VDDIO_8

T24

VDDIO_9

T26

VDDIO_10

T28

VDDIO_11

T30

VDDIO_12

V25

VDDIO_13

V26

VDDIO_14

V28

VDDIO_15

V30

VDDIO_16

Y24

VDDIO_17

Y26

VDDIO_18

Y28

VDDIO_19

Y29

VDDIO_20

VDDIO_21

VDDIO_22

VDDIO_23

VDDIO_24

VDDIO_25

VDDIO_26

VDDIO_27

VDDIO_28

VDDIO_29

ZIF-SOCKET941-RH

ZIF-SOCKET941-RH

VCCP_NB CAP

VCCP_NB

C72

C72

VCCP_NB

C71

C71

C22u6.3X1206

C22u6.3X1206

2

C77

C77

X_C0.22u16X

X_C0.22u16X

C102

C102

C22u6.3X1206

C22u6.3X1206

VLDT_B_1

VLDT_B_2

VLDT_B_3

VLDT_B_4

POWER/GND4

POWER/GND4

C98

C98

C0.22u16X

C0.22u16X

C101

C101

C22u6.3X1206

C22u6.3X1206

VDDR_5

VDDR_6

VDDR_7

VDDR_8

VDDR_9

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

C22u6.3X1206

C22u6.3X1206

H1

H2

H5

H6

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

C99

C99

C0.01u50X

C0.01u50X

C78

C78

VLDT_RUN_B

CPU_VDDR

C4.7u10Y0805

C4.7u10Y0805

CPU_VDDR

C159

C159

C0.22u16X

C0.22u16X

CPU_VDDR

C75

C75

C0.22u16X

C0.22u16X

C105

C105

C110

C110

C108

C108

C0.01u50Y5

C0.01u50Y5

X_C0.01u50Y5

X_C0.01u50Y5

near VDDR 5pin

C164

C164

C160

C160

C0.22u16X

C0.22u16X

C4.7u10Y0805

C4.7u10Y0805

near VDDR 4pin

C65

C65

C64

C64

C0.22u16X

C0.22u16X

X_C4.7u10Y0805

X_C4.7u10Y0805

C4.7u10Y0805

C4.7u10Y0805

1

C113

C113

X_C0.01u50Y5

X_C0.01u50Y5

CPU_VDDR CAP

C161

C161

C176

X_C180p50N0402

X_C180p50N0402

C86

C86

C180p50N0402

C180p50N0402

C176

X_C1000p50X

X_C1000p50X

C90

C90

C1000p50X

C1000p50X

C163

C163

X_C4.7u10Y0805

X_C4.7u10Y0805

C180p50N0402

C180p50N0402

C66

C66

X_C180p50N0402

X_C180p50N0402

C181

C181

C180

C180

X_C1000p50X

X_C1000p50X

C45

C45

C81

C81

C1000p50X

C1000p50X

VCC_DDR

C155 X_C10u6.3X50805C155 X_C10u6.3X50805

VCC_DDR

C166 X_C22u6.3X1206C166 X_C22u6.3X1206

A A

5

4

VCC_DDR

C573

C573

X_C0.22u16X

X_C0.22u16X

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

BOTTOM

C589

C589

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

VCC_DDR

C116 C0.22u16XC116 C0.22u16X

VCC_DDR

C123 X_C4.7u10Y0805C123 X_C4.7u10Y0805

C50 X_C4.7u10Y0805C50 X_C4.7u10Y0805

C570

C570

C4.7u10Y0805

C4.7u10Y0805

3

C583

C583

C577

C577

X_C4.7u10Y0805

X_C4.7u10Y0805

VCC_DDR

C10u10X1206

C10u10X1206

C148 X_C180p50N0402C148 X_C180p50N0402

C154 C0.1u25Y0402-RHC154 C0.1u25Y0402-RH

C580

C580

C586

C586

C10u10X1206

C10u10X1206

C574

C574

X_C4.7u10Y0805

X_C4.7u10Y0805

C584C0.1u25Y0402-RH C584C0.1u25Y0402-RH

C0.22u16X

C0.22u16X

2

C587

C587

VCCP

C578

C578

C10u10X1206

C10u10X1206

VCCP

X_C10u10X1206

X_C10u10X1206

C581

C581

C0.22u16X

C0.22u16X

BOTTOM

C575

C575

BOTTOM

C0.22u16X

C0.22u16X

VCCP CAPVCC_DDR CAP

C571

C571

C10u10X1206

C10u10X1206

C591

C591

C568

C568

X_C10u10X1206

X_C10u10X1206

C592

C592

C0.01u50X

C0.01u50X

C588

C588

C10u10X1206

C10u10X1206

X_C180p50N0402

X_C180p50N0402

X_C22u6.3X1206

X_C22u6.3X1206

C104

C104

C585

C585

C10u10X1206

C10u10X1206

Title

Title

Title

Document Number

Document Number

Document Number

C579

C579

C582

C582

C10u6.3X51206

C10u6.3X51206

X_C10u6.3X51206

X_C10u6.3X51206

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

AM3 PWR & GND

AM3 PWR & GND

AM3 PWR & GND

MS-7599

MS-7599

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7599

1

C576

C576

C10u10X1206

C10u10X1206

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

C572

C572

C10u6.3X51206

C10u6.3X51206

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Tuesday, March 02, 2010

of

538

of

538

of

538

C569

C569

Rev

Rev

Rev

10

10

10

5

DIMM1

DIMM1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC_DDR

MEM_MA_DQS_H[7..0]

MEM_MA_DQS_L[7..0]

MEM_MA_DM[7..0]

MEM_MA_ADD[15..0]

MEM_MA_DATA[63..0]

54

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

107

110

113

116

119

121

VCC3

C187

C187

C0.1u16Y0402

C0.1u16Y0402

VTT_DDR

MEM_MA_EVENT_L

170

173

176

179

182

183

186

189

191

194

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

124

127

130

133

136

139

142

145

VSS

148

151

154

157

160

163

166

199

53

197

VDD

VSS

VSS

202

205

236

VDDSPD

VSS

208

79

68

120

240

48

187

198

167

VTT

VTT

VSS

VSS

VSS

VSS

211

214

217

220

223

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

226

229

232

RSVD

FREE1

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

VSS

VSS

235

239

A0

FREE249FREE3

FREE4

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

BA0

BA1

BA2

WE#

RAS#

CAS#

RESET#

CK0

CK0#

CK1(NU)

CK1#(NU)

VREFDQ

VREFCA

SCL

SDA

SA1

SA0

VSS

MEC1

MEC2

MEC3

DDRIII-240P_BLUE-RH

DDRIII-240P_BLUE-RH

MEC1

MEC2

MEC3

MEM_MA_DQS_H[7..0]4,7

MEM_MA_DQS_L[7..0]4,7

MEM_MA_DM[7..0]4,7

MEM_MA_ADD[15..0]4,7

MEM_MA_DATA[63..0]4,7

D D

MEM_MA_DATA0 MEM_MA_ADD0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

C C

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

B B

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

89

92

95

98

101

104

188

181

61

180

59

58

178

56

177

175

70

55

174

196

172

171

39

40

45

46

158

159

164

165

7

6

16

15

25

24

34

33

85

84

94

93

103

102

112

111

43

42

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

195

77

50

169

193

76

71

190

52

73

192

74

168

184

185

63

64

1

67

118

238

237

117

4

MEM_MA_EVENT_L 4,7

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA0_ODT0

MEM_MA0_ODT1

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA0_CS_L0

MEM_MA0_CS_L1

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA_RESET#

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

VDDR_VREF_DQ

VDDR_VREF_CA

SCL

SDA

3

MEM_MB_DQS_H[7..0]4,7

MEM_MB_DQS_L[7..0]4,7

MEM_MB_DM[7..0]4,7

MEM_MB_ADD[15..0]4,7

MEM_MB_DATA[63..0]4,7

VCC_DDR

54

DIMM2

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

C127

C127

C1000p16X0402

C1000p16X0402

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

VCC3

Y

D12

D12

X_1PS226_SOT23

SCL

SDA

VCC_DDR

R88

R88

15R1%

15R1%

R89

R89

15R1%

15R1%

MEM_MA0_ODT0 4

MEM_MA0_ODT1 4

MEM_MA_CKE0 4,7

MEM_MA_CKE1 4,7

MEM_MA0_CS_L0 4

MEM_MA0_CS_L1 4

MEM_MA_BANK0 4,7

MEM_MA_BANK1 4,7

MEM_MA_BANK2 4,7

MEM_MA_WE_L 4,7

MEM_MA_RAS_L 4,7

MEM_MA_CAS_L 4,7

MEM_MA_RESET# 4,7 MEM_MB_RESET# 4,7

MEM_MA0_CLK_H0 4

MEM_MA0_CLK_L0 4

MEM_MA0_CLK_H1 4

MEM_MA0_CLK_L1 4

SCL 7,13,16,20,21,22,25,29

SDA 7,13,16,20,21,22,25,29

R133

R133

15R1%

15R1%

R134

R134

15R1%

15R1%

VCC_DDR

VDDR_VREF_DQ

C53

C53

C0.1u16Y0402

C0.1u16Y0402

Z

VCC3

Z

C51

C51

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

VDDR_VREF_DQ

C54

C54

C0.1u25Y0402-RH

C0.1u25Y0402-RH

C132

C132

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

VDDR_VREF_CA

C129

C129

C0.1u25Y0402-RH

C0.1u25Y0402-RH

VDDR_VREF_CA

X_1PS226_SOT23

X

Y

D11

D11

X_1PS226_SOT23

X_1PS226_SOT23

X

VDDR_VREF_DQ

C55

C55

C1000p16X0402

C1000p16X0402

VDDR_VREF_CA

C872

C872

C4.7uF6.3V0603

C4.7uF6.3V0603

DIMM2

3

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

VSS

VSS

107

110

113

116

MEM_MB_DQS_H[7..0]

MEM_MB_DQS_L[7..0]

MEM_MB_DM[7..0]

MEM_MB_ADD[15..0]

MEM_MB_DATA[63..0]

VSS

VSS

VSS

VSS

VSS

VSS

VSS

119

121

124

127

130

133

136

139

2

170

173

176

179

182

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

142

145

148

151

154

1

VCC3

C188

C188

C0.1u16Y0402

C0.1u16Y0402

VTT_DDR

183

186

189

191

194

197

120

240

236

VTT

VDD

VDD

VDD

VSS

VSS

VSS

157

160

163

VTT

VDD

VDD

VDD

VDD

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

166

199

202

205

208

211

214

217

68

VSS

220

223

53

79

167

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

VSS

VSS

VSS

226

229

232

48

RSVD

FREE1

FREE249FREE3

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(NU)

VSS

VSS

VSS

235

239

187

RESET#

CK1(NU)

VREFDQ

VREFCA

MEC1

MEM_MB_EVENT_L

198

188

A0

181

FREE4

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

7

DQS0

6

DQS0#

16

DQS1

15

DQS1#

25

DQS2

24

DQS2#

34

DQS3

33

DQS3#

85

DQS4

84

DQS4#

94

DQS5

93

DQS5#

103

DQS6

102

DQS6#

112

DQS7

111

DQS7#

43

DQS8

42

DQS8#

125

126

134

135

143

144

152

153

203

204

212

213

221

222

230

231

161

162

195

ODT0

77

ODT1

50

CKE0

169

CKE1

193

CS0#

76

CS1#

71

BA0

190

BA1

52

BA2

73

WE#

192

RAS#

74

CAS#

168

184

CK0

185

CK0#

63

64

1

67

118

SCL

238

SDA

237

SA1

117

SA0

MEC1

MEC2

MEC3

DDRIII-240P_BLUE-RH

DDRIII-240P_BLUE-RH

MEC2

MEC3

MEM_MB_EVENT_L 4,7

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB0_ODT0

MEM_MB0_ODT1

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB0_CS_L0

MEM_MB0_CS_L1

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB_RESET#

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

VDDR_VREF_DQ

VDDR_VREF_CA

SCL

SDA

MEM_MB0_ODT0 4

MEM_MB0_ODT1 4

MEM_MB_CKE0 4,7

MEM_MB_CKE1 4,7

MEM_MB0_CS_L0 4

MEM_MB0_CS_L1 4

MEM_MB_BANK0 4,7

MEM_MB_BANK1 4,7

MEM_MB_BANK2 4,7

MEM_MB_WE_L 4,7

MEM_MB_RAS_L 4,7

MEM_MB_CAS_L 4,7

MEM_MB0_CLK_H0 4

MEM_MB0_CLK_L0 4

MEM_MB0_CLK_H1 4

MEM_MB0_CLK_L1 4

SCL 7,13,16,20,21,22,25,29

SDA 7,13,16,20,21,22,25,29

VCC3

ADDRESS A0

ADDRESS A2

SMBus Addressing

A A

Device

DIMMA0

DIMMB0

DIMMA1

DIMMB1

SMBus 0

8-bit Address (hex)

A0

A2

A4

A6

5

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

4

3

2

http://www.msi.com.tw

1

MS-7599

MS-7599

MS-7599

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Tuesday, March 02, 2010

Sheet

Sheet

Sheet

Rev

Rev

Rev

10

10

10

of

of

of

638

638

638

5

MEM_MA_DQS_H[7..0]4,6

MEM_MA_DQS_L[7..0]4,6

MEM_MA_DM[7..0]4,6

MEM_MA_ADD[15..0]4,6

MEM_MA_DATA[63..0]4,6

MEM_MA_DQS_H[7..0]

MEM_MA_DQS_L[7..0]

MEM_MA_DM[7..0]

MEM_MA_ADD[15..0]

MEM_MA_DATA[63..0]

VCC3

4

3

MEM_MB_DQS_L[7..0]4,6

MEM_MB_DQS_H[7..0]4,6

MEM_MB_DM[7..0]4,6

MEM_MB_ADD[15..0]4,6

MEM_MB_DATA[63..0]4,6

MEM_MB_DQS_L[7..0]

MEM_MB_DQS_H[7..0]

MEM_MB_DM[7..0]

MEM_MB_ADD[15..0]

MEM_MB_DATA[63..0]

2

VCC3

1

D D

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

C C

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

B B

A A

VCC_DDR

54

DIMM3

DIMM3

3

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

VSS

VSS

107

110

113

116

119

170

173

176

179

182

183

VDD

VDD

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

151