5

4

3

2

1

www.qdzbwx.com

Cover Sheet

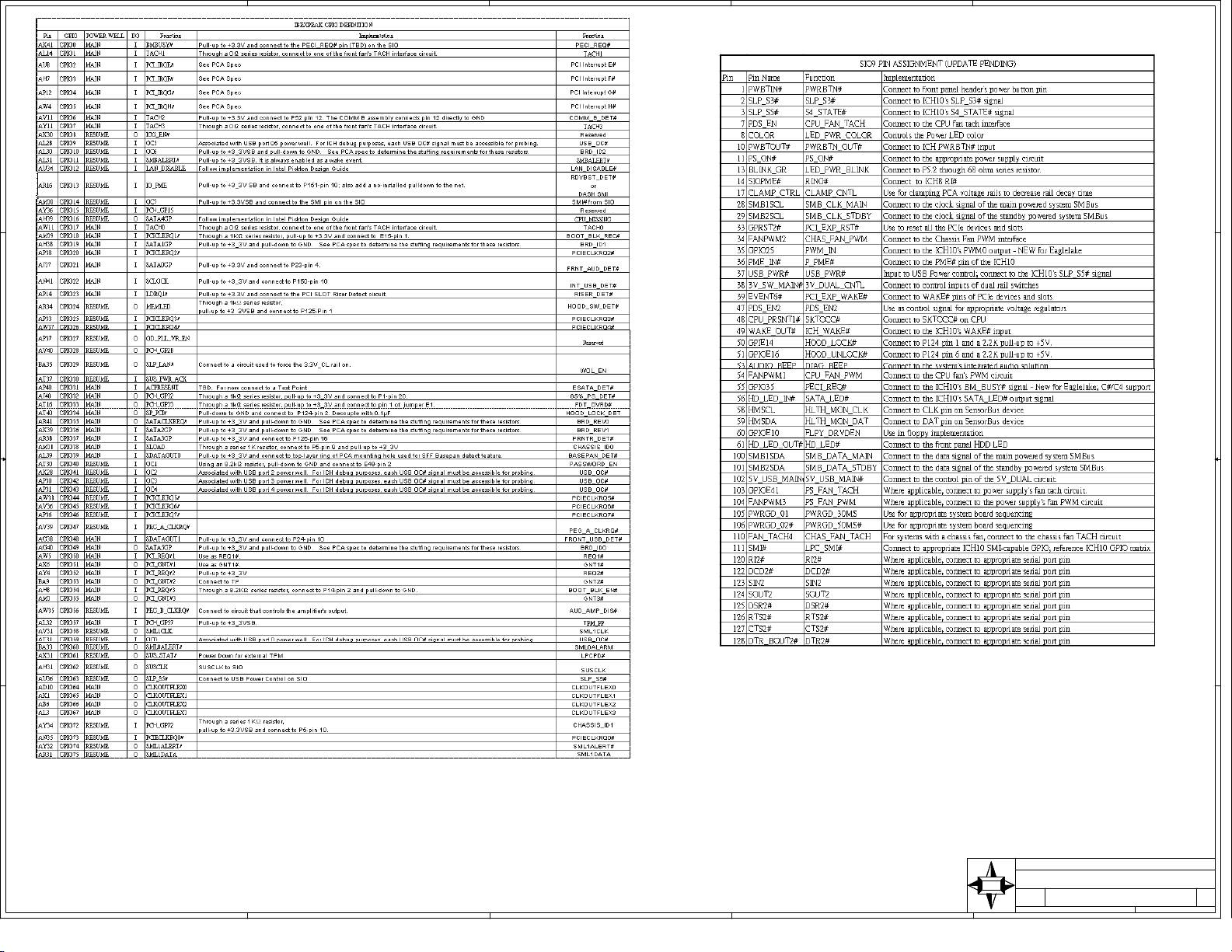

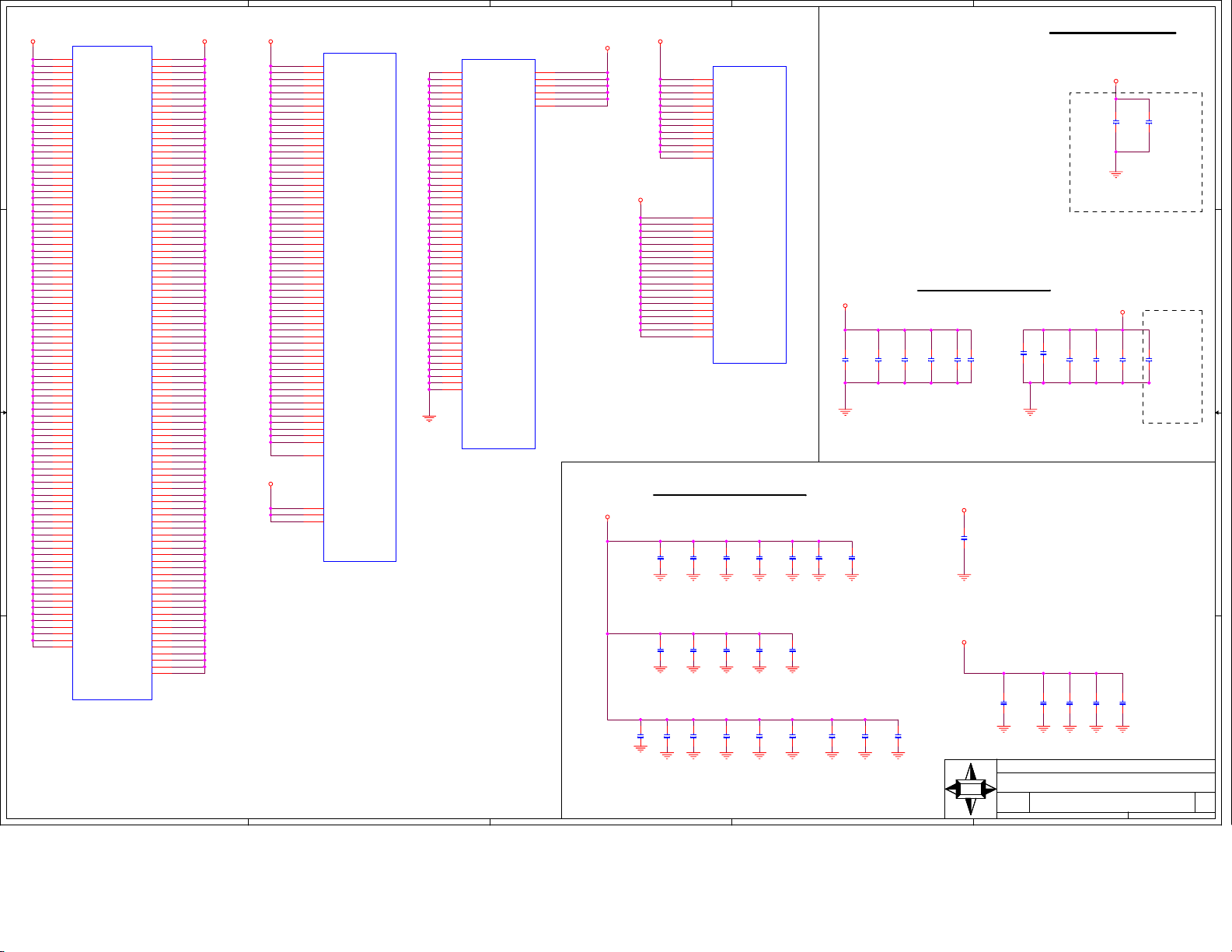

Block Diagram/Device Map/GPIO Table/Clock Distribution

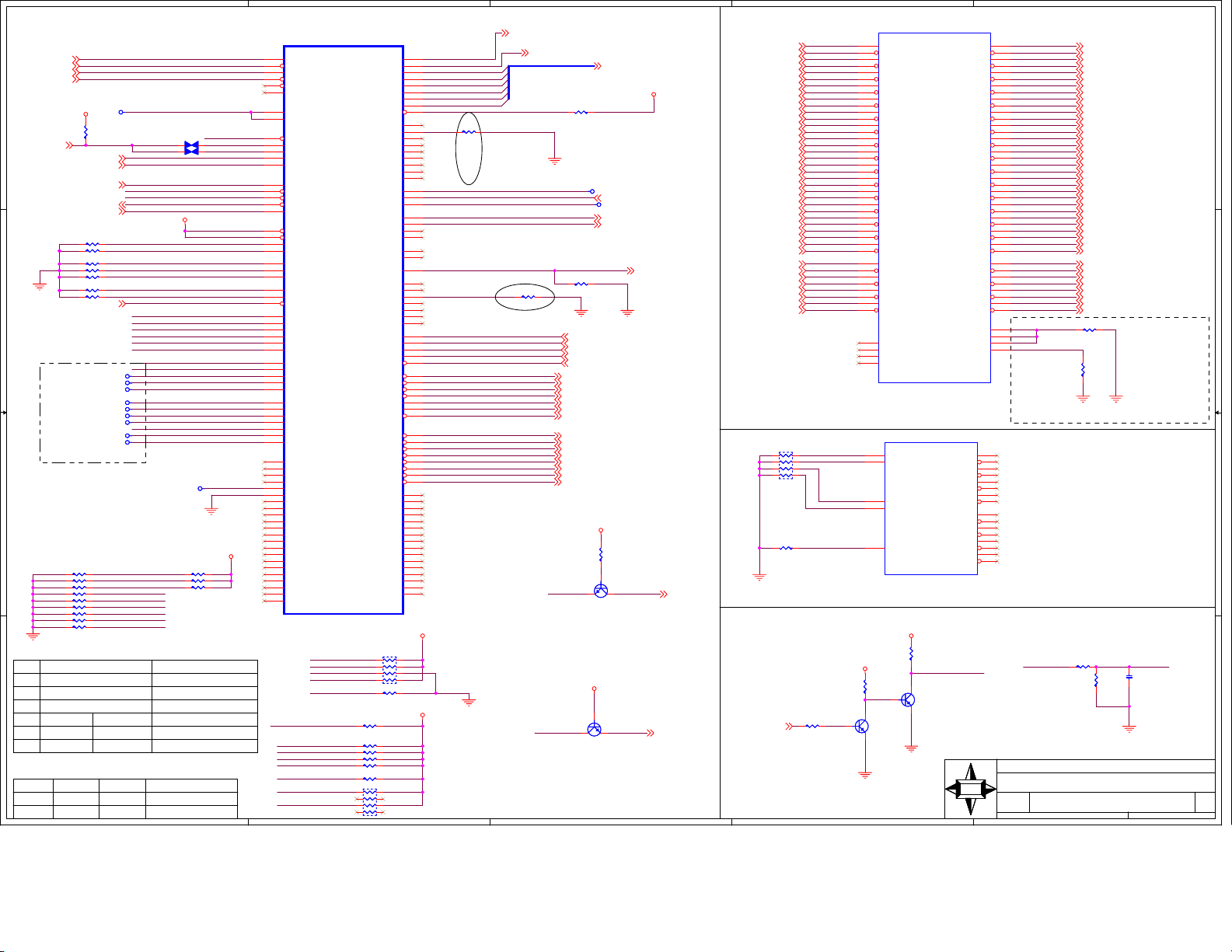

CPU-CLK/Control/MISC/PEG,CPU-Memory

D D

CPU-Power,CPU-GND

DDR III DIMM 1 / 2,DDR III DIMM 3 / 4

CLK GEN ICS9LPRS4115

PCH-PCI/E/DMI/USB/CLK

PCH-SATA/HOST/FAN/GPIO/VGA

PCH-SMB/LPC/AUDIO/RTC/RST

PCH-POWER,GND

SIO-Fintek F71889F/KB/FDD

C C

PCIE x16 Slots

PCIEx1 & X4 SLOT

PCI Slot 1 & 2

1394 Controller - VT6315N-CD

JMB-363 SATA X2/ IDE X1

LAN-RTL8111DL

Audio Codec ALC888S

SATA / FAN Control,USB Connector

B B

USB CONNECTOR

ACPI Controller UPI

CPU_VTT - 6103 1Phase

DDR Power - 6103 1Phase

PCH Power - 6103 1Phase

VRD11.1 - upi6213 4-Phase

upi6213 4-Phase(Dr.Mos)

PHASE Dropping & PSI

A A

ATX F_Panel/EMI/TPM

CPU/PCH XDP

Manual & Option parts

5

PageTitle

1

2~5

6

,9,78

10,11

12

13

14

15

16,17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

4

MS-7589

mATX(304.8mm X 215mm)

CPU:

INTEL -HAVENDALE/Lynnfied LGA 1156

System Chipset:

INTEL-IBEXPEAK PCH

OnBoard Chipset:

Clock Gen:IDT 4116

HD Audio Codec:ALC889

LAN:Realtek - 8111DL

SIO:FIN71889F

Flash ROM: 32 Mb SPI (CHIP)

Main Memory:

DDRIII (1066/1333MHz) * 4 (Dual Channel)

Expansion Slots:

PCI Express (X16) Slot * 1

PCI Express (X4) Slot * 1

PCI Express (X1) Slot * 3

PCI Slot *2

PWM:

Controller:ISL6213( 4-Phase 95W )

Controller:ISL

ACPI:

INTERSIL

Other:

JMB368 SATA*2 IDE*1

SATA(SATA2-300MB/s) *6

USB2.0 *14 (Rear*10 Front*4)

PRINT Header *1

COM Header *1

3

Ver:0A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Thursday, September 24, 2009

Thursday, September 24, 2009

2

Thursday, September 24, 2009

Cover Sheet

Cover Sheet

Cover Sheet

MS-7588

1

Sheet ofDate:

139

Sheet ofDate:

139

Sheet ofDate:

139

0A

0A

0A

5

d

d

d

4

3

2

1

NCT3016Y

Power use ATX_5VSB

D D

C C

ATX_5VSB

N3016Y Power LED Control

B B

www.qdzbwx.com

Modify- 2009.8.12

330R/6

330R/6

PLED1

PLED2

SMBCLK10,12,15,19,20,22,23,28,32,36

SMBDATA10,12,15,19,20,22,23,28,32,36

SLP_S3#15,18,28,32

SLP_S4#12,15,28,30

ATX_5VSB

R709

R709

R710

R710

330R/6

330R/6

R395 0/4R395 0/4

R399 0/4R399 0/4

R365 0/4R365 0/4

R390 0/4R390 0/4

C581

C581

0.1u/16V/4

0.1u/16V/4

NCT_SCL

NCT_SDA

PLED1

PLED2

NCT_XIN

NCT_XOUT

Update- 2009.8.24

U74

U74

1

VSB

5

GND

12

SCLK

11

SDA

3

SLP_S3#/GPIO3

4

SLP_S5#

9

PLED1/GPIO9/Ctl1/Wake1

10

PLED2/GPIO10/Ctl2/Wake2

6

XI / NC

7

XOUT/ NC

SUS_LED 35

NCT3016Y

NCT3016Y

Mode_sel/SLP_S5#_lch/GPIO18

EN#/AC_LOSS#/GPIO17

21

NC

PS_IN#

PS_OUT#

15

18

17

8

19

2

14

13

16

20

SYS5VSB_OFF

ATXPG/GPIO8

PWROK/GPIO19

PS_ON#/GPIO13

RSMRST#/GPIO16

3VCC/GPIO20

NCT3016Y-A-RH

NCT3016Y-A-RH

PANEL SWITCH

NCT_PSIN#

R725 33/4R725 33/4

SYS5VSB_OFF

NCT_WAKE#

NCT_PWROK

NCT_PSIN#

NCT_PSOUT#

NCT_PSON#

NCT_RSMRST#

3VCC_DET

10K/4/1

10K/4/1

Control DDR power,This pin

substitute SB SLP_S4#

SLP_S5_LCH# 28,30

3VSB_LAN_EN# 24,28

R407 0/4R407 0/4

Link to SIO PSIN

R421 0/4R421 0/4

R722 X_0/4R722 X_0/4

R723 0/4R723 0/4

SB_RSMRST# use this pin,

can't use SIO_RSMRST#

ATX_5VSB

R726

R726

PSIN#_R 24,35PWR_LED 35

C582

C582

0.1u/16V/Y/4

0.1u/16V/Y/4

NC_WAKE# 24

PCI_E Bus

SIO_PSIN# 18,35

PSON# 18,35

RSMRST# 15,18

Wake#

Link to ATX COON PSON#

,But doesn't use it

ASIC Timer Clock

EN#/VSB Discharge

EN# circuit

ATX_5VSB

R732 4.7K/4R732 4.7K/4

Pull-High

3VSB

R734 8.2K/4R734 8.2K/4

3VSB

R730 1K/4R730 1K/4

R717 X_4.7K/4R717 X_4.7K/4

ATX_5VSB

VCC3

R678 4.7K/4R678 4.7K/4

R711 1K/4R711 1K/4

ATX_5VSB

R715 X_4.7K/4R715 X_4.7K/4

R719 1K/4R719 1K/4

NCT_XIN

NCT_XOUT

4

R724

R724

3

10M/4

10M/4

R721 330K/4R721 330K/4

Enable ASIC Timer Circuit

Please do not change the ASIC timer

component.

3VSB_LAN_EN#

NCT_RSMRST#

NCT_PSOUT#

NCT_PWROK

3VCC_DET

NCT_PSON#

NCT_WAKE#

C175 C20p50NC175 C20p50N

Y7

Y7

32.768KHZ12.5P_D-LF

32.768KHZ12.5P_D-LF

1 2

C585 C39p50NC585 C39p50N

VSB Discharge circuit

5VSB

R716 X_0/8R716 X_0/8

R718

R718

X_4.7K/4

X_4.7K/4

NCT_PSOUT# must used 1K

resistance and connect to SYS_3VSB

or 3VDual power source for power

detect.

NCT_PWROK reserve R464,Support after

6 sec auto into Deep S5 , HW Straping

Pull High to VSB: 6 sec to Deep SLP

3VCC_DET must used 1K resistance and

connect to 3VCC power source for power

detect.

New future for WAKE 0 support

wake up event.It's HW strap pin

Pull High : Wake 0

Q71

Q71

X_P-NDS352AP_SOT23

X_P-NDS352AP_SOT23

DS

G

Disable ASIC Timer

Circuit

3VSB_LAN_EN#

Update- 2009.6.11

NCT_XIN

R714

R714

X_4.7K/4

X_4.7K/4

5VSB Power Switch

ATX_5VSB

R712 x_0R1206R712 x_0R1206

R713 x_0R1206R713 x_0R1206

A A

12

+

+

G

EC60

EC60

SMD10U/10V

SMD10U/10V

SYS5VSB_OFF

249K/4

249K/4

R728

R728

R727 10K/6R727 10K/6

5

DS

Q65

Q65

P06P03LCG_SOT89

P06P03LCG_SOT89

C584

C584

1u/10V/6

1u/10V/6

5VSB

Trace Width 80mils.

4

3

Strapping PIN

ATX_5VSB

R729 X_4.7K/4R729 X_4.7K/4

POWER ON STRAPPING PIN

SimpleMode_Sel Simple Mode

SLP_S5_LCH#

Name

2

SLP_S5_LCH# (SimpleMode_Sel):

8-PIN Function: Pull-high 10k

20-PIN Full Function: Floating (Internal Pull-Down)

01PIN

Full function18

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Title

Title

Title

MSI

MSI

MSI

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INT'L CO.,LTD

<Title>

<Title>

<Title>

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

<Doc> <RevCo

<Doc> <RevCo

<Doc> <RevCo

Custom

Custom

Custom

Thursday, September 24, 2009

Thursday, September 24, 2009

Thursday, September 24, 2009

NCT3016

NCT3016

NCT3016

MS-7581

MS-7581

MS-7581

1

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

11Thursday, September 24, 2009

11Thursday, September 24, 2009

11Thursday, September 24, 2009

of

of

of

40 47

40 47

40 47

10

10

10

5

www.schematic-x.blogspot.com

INTEL CONFIDENTIAL

4

3

2

1

D D

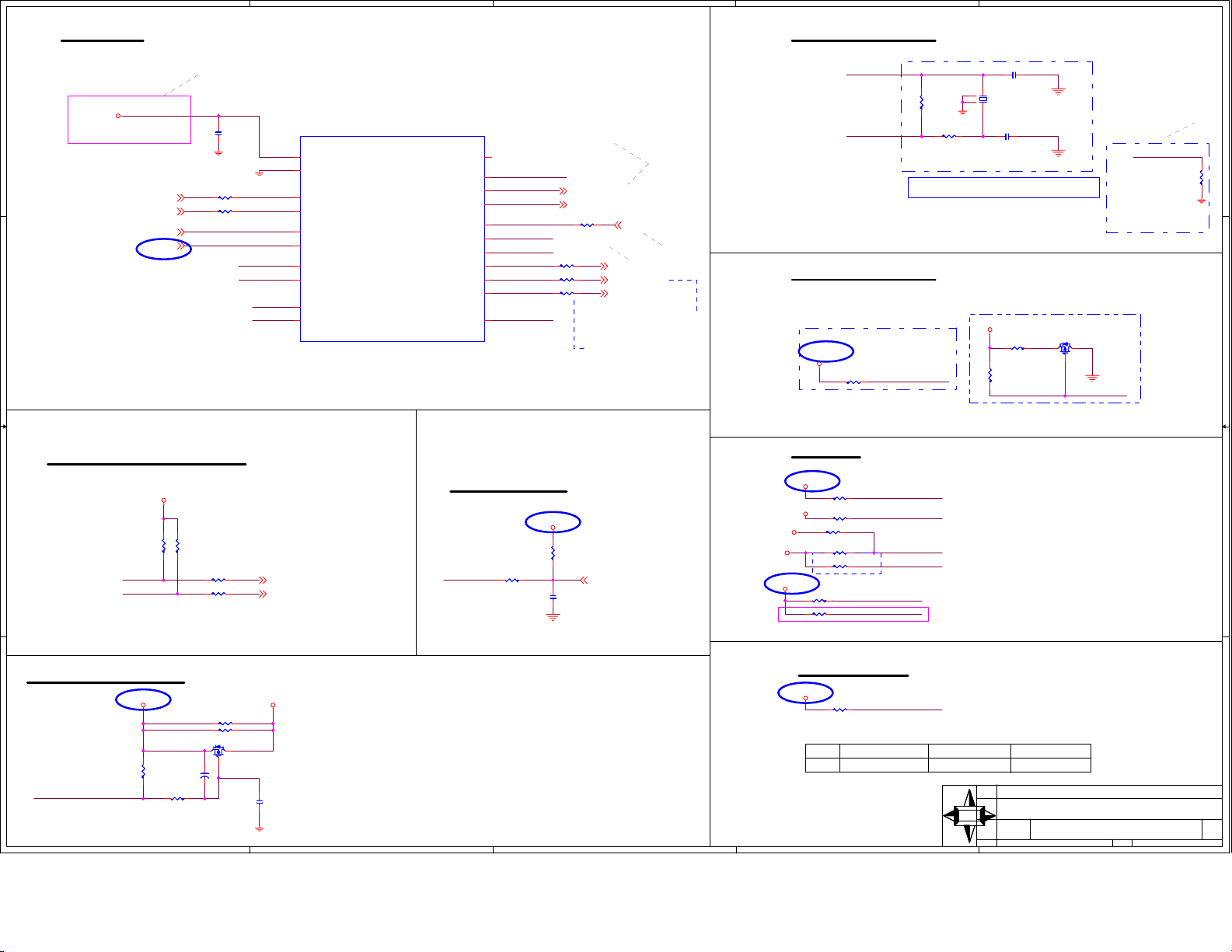

INTEL

PCIE

SLOT

16X

16X

LGA 1160

DDRIII 1066,1333

128bit

DDRIII 1066,1333

UNBUFFERED

DDRIII DIMM1

UNBUFFERED

DDRIII DIMM2

DDRIII FIRST LOGICAL DIMM DDRIII SECOND LOGICAL DIMM

UNBUFFERED

DDRIII DIMM3

UNBUFFERED

DDRIII DIMM4

FDI LINK DMI X4

IBEXPEAK

C C

USB-0

USB 2.0

PCIE X1

SLOT

HD AUDIO I/F

PCIE X1

SLOT

PCIE X1

SLOT

Audio Codec ALC889

PCIE X4

SLOT

GIGA LAN

USB-7

USB-8 USB-9

USB-2USB-6 USB-3USB-4USB-5

USB-1

USB-11 USB-12USB-10 USB-13

PCH

SPI ROM

SPI I/F

SATA II I/F

SATA#0 SATA#1 SATA#2 SATA#3

SATA#5

B B

PCI BUS

PCIE

ESATA*2 & IDE

SATA#4

PCI SLOT

#1

PCI SLOT

#2

PCI SLOT

#3

LPC I/F

A A

KBD

MOUSE

COM

5

4

SIO

FLOPPY PARALLAL PORT

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Thursday, September 24, 2009

Date:

Thursday, September 24, 2009

Date:

2

Thursday, September 24, 2009

MS-7588

Block Diagram

Block Diagram

Block Diagram

1

Sheet of

Sheet of

Sheet of

239

239

239

0A

0A

0A

5

4

3

2

1

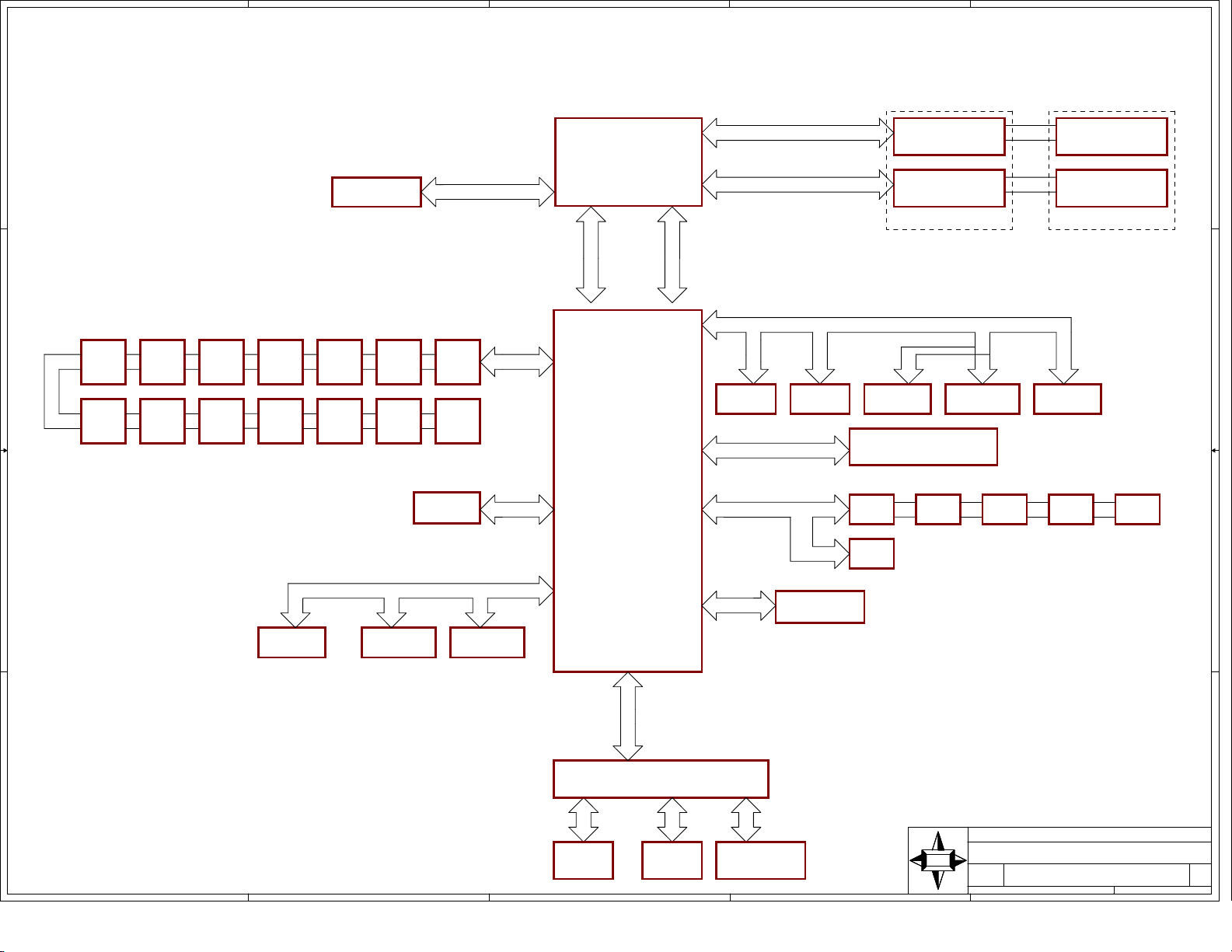

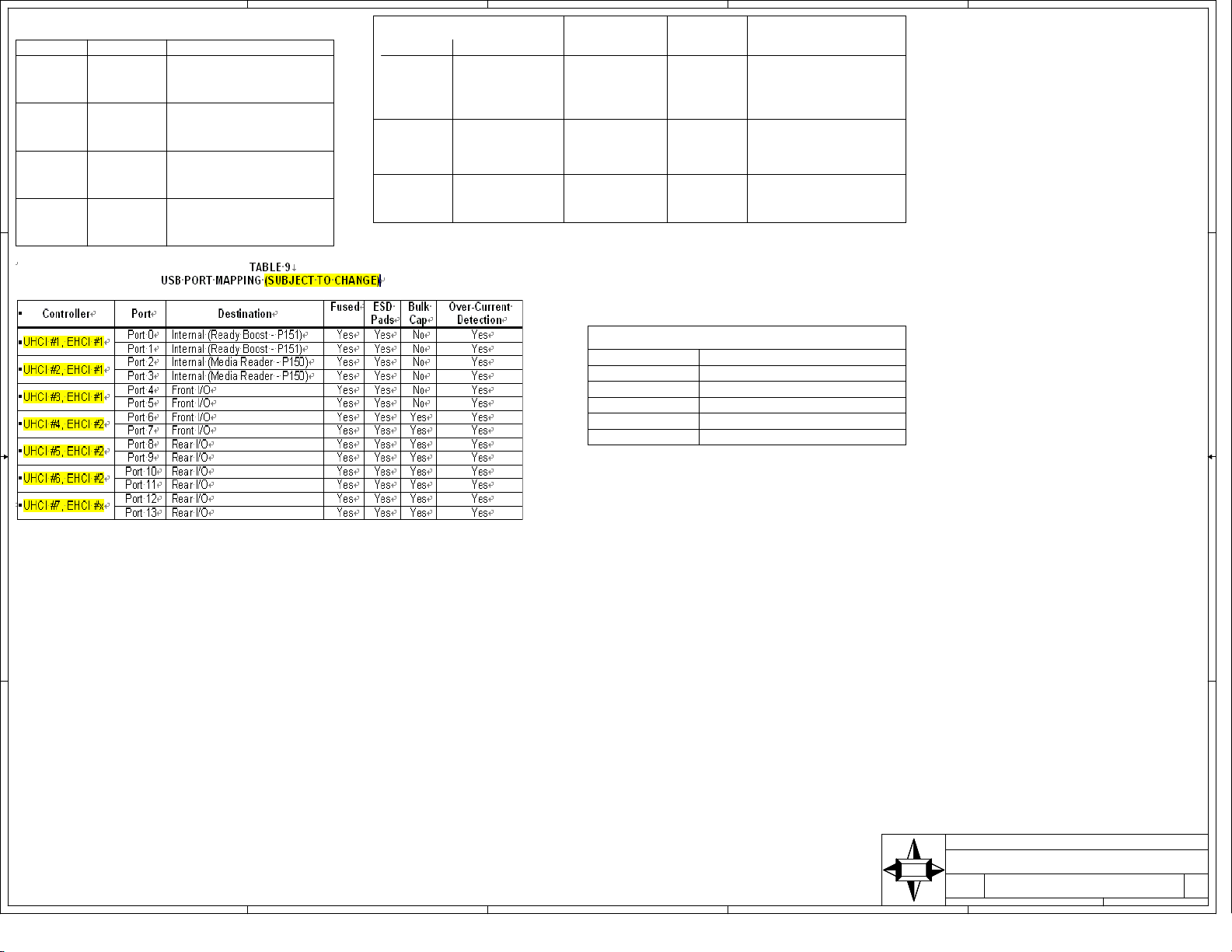

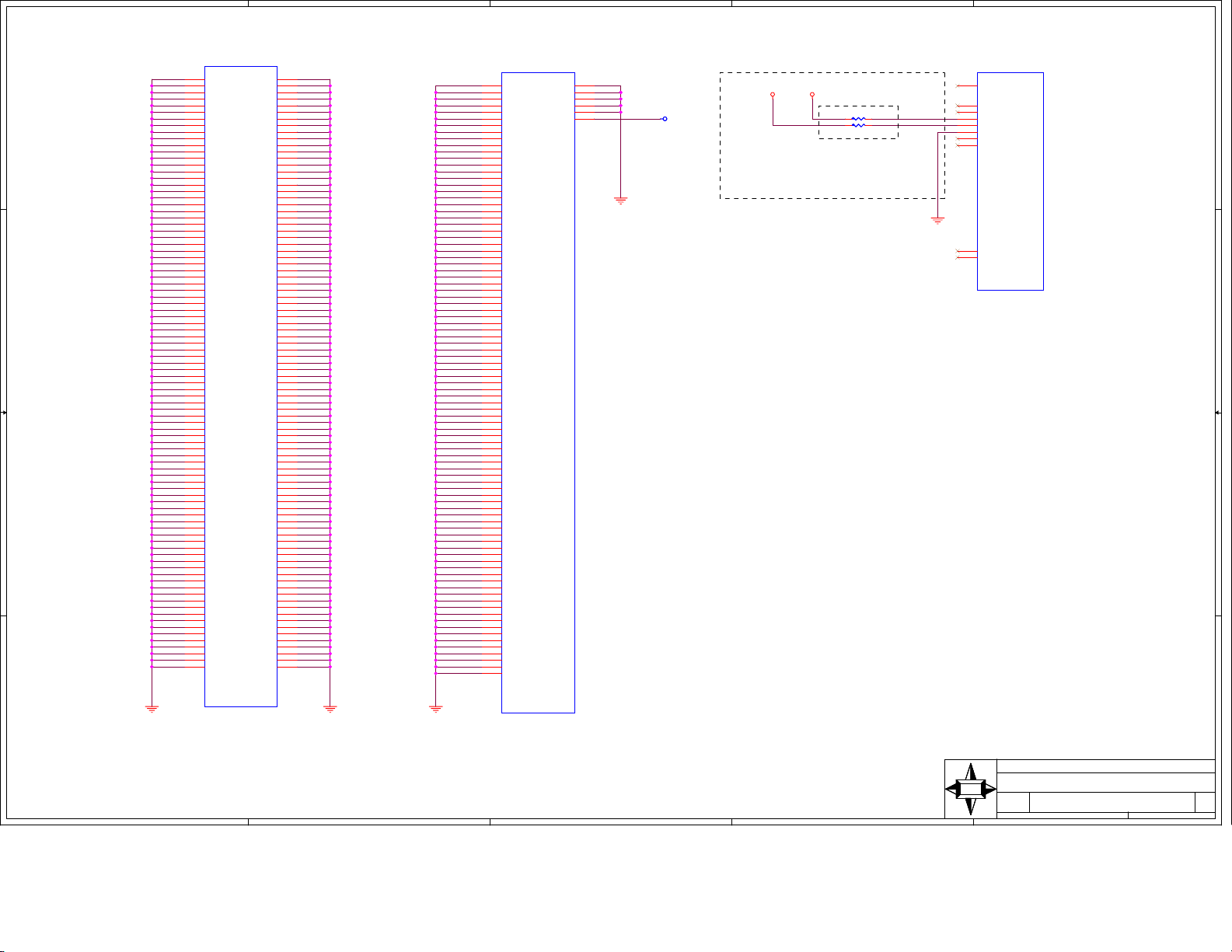

DDR DIMM Config.

DEVICE

DIMM 2

CH-A

D D

DIMM 4

10100000B

10100010B

CH-A

DIMM 1

CH-B

DIMM 3

CH-B

10100001B

10100011B

CLOCKADDRESS

MEM_MA0_CLK_H0/L0

MEM_MA0_CLK_H1/L1

MEM_MA0_CLK_H2/L2

MEM_MA1_CLK_H0/L0

MEM_MA1_CLK_H1/L1

MEM_MA1_CLK_H2/L2

MEM_MB0_CLK_H0/L0

MEM_MB0_CLK_H1/L1

MEM_MB0_CLK_H2/L2

MEM_MB1_CLK_H0/L0

MEM_MB1_CLK_H1/L1

MEM_MB1_CLK_H2/L2

PCI Config.

DEVICE MCP1 INT Pin

PCI_INT#E

PCI Slot 1

TPM

PCI_INT#F

PCI_INT#G

PCI_INT#H

REQ#/GNT#

PCI_REQ0#

PCI_GNT0#

IDSEL

AD16

CLOCK

CLK33M_PCISLOT_J20

LPCCLK0

LPCCLK1SIO

PCI RESET DEVICE

C C

Signals

PCIRST#

PE_RST#

PE_RST#

IBEXPEAK

Target

PCISLOT1

TPM_RST#

LPC/SIO

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

Device Map

Device Map

Device Map

MS-7588

0A

0A

0A

Sheet ofDate:

339

Sheet ofDate:

339

Sheet ofDate:

1

339

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Thursday, September 24, 2009

Thursday, September 24, 2009

5

4

3

2

Thursday, September 24, 2009

5

D D

C C

4

3

2

1

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

C

C

C

Thursday, September 24, 2009

Thursday, September 24, 2009

5

4

3

2

Thursday, September 24, 2009

GPIO Table

GPIO Table

GPIO Table

MS-7588

1

Sheet ofDate:

439

Sheet ofDate:

439

Sheet ofDate:

439

0A

0A

0A

5

D D

C C

4

3

2

1

B B

A A

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

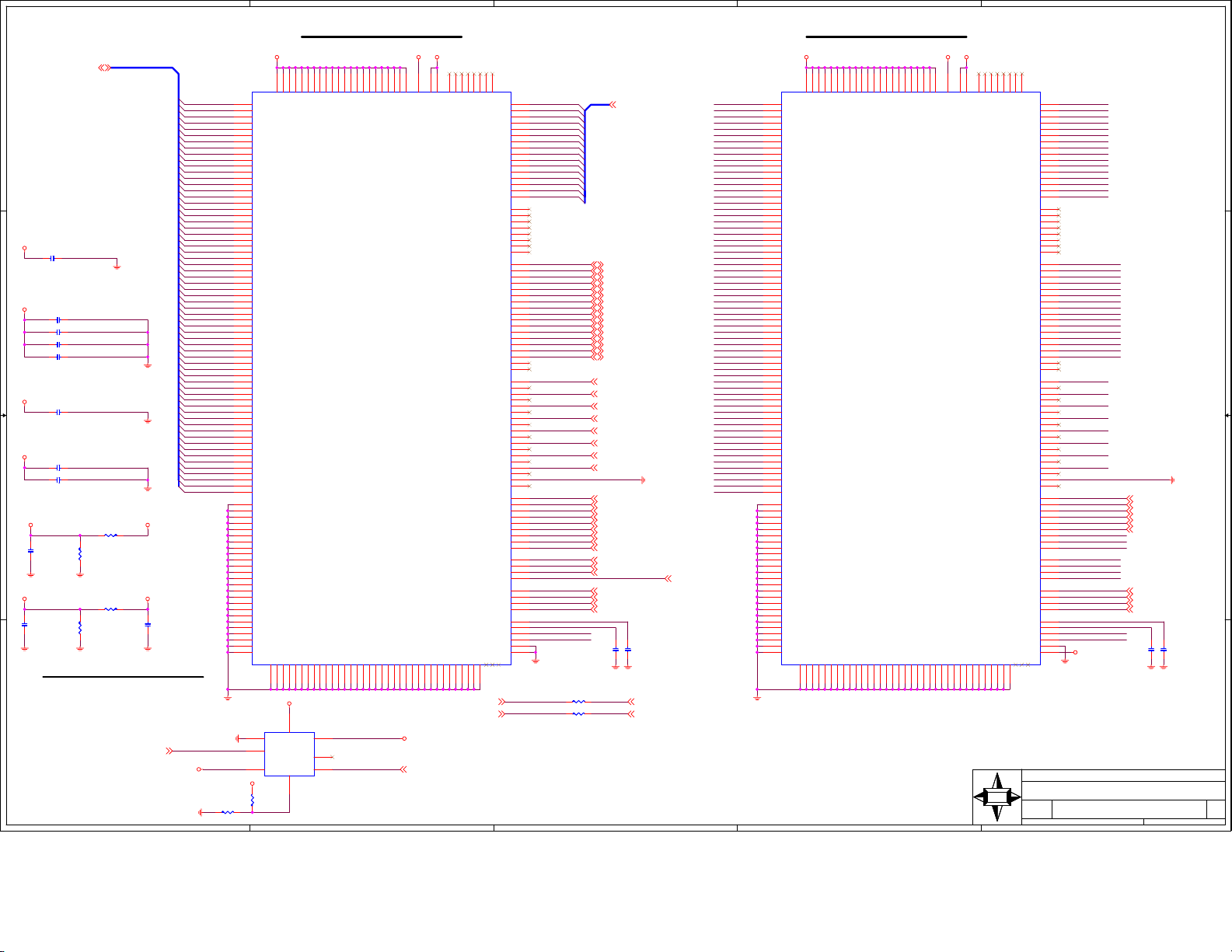

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

B

B

B

Date:

Thursday, September 24, 2009

Date:

Thursday, September 24, 2009

Date:

5

4

3

2

Thursday, September 24, 2009

MS-7588

Clock Distribution

Clock Distribution

Clock Distribution

Sheet of

Sheet of

Sheet of

1

0A

0A

0A

539

539

539

5

CPU1E

CLK133M_CPU_P13

CLK133M_CPU_N13

CK_DMI_P13

CK_DMI_N13

BACK SIDE

D D

CPU_PWRGD15

C C

代翴 璉

B B

CLK133M_CPU_P

CLK133M_CPU_N

CK_DMI_P

CK_DMI_N

CPU_VTT

R183

R183

X_49.9R1%0402

X_49.9R1%0402

VTT_PGD28,32

MEM_PWRGD15

H_PECI14,18

H_THERMTRIP#14

PM_SYNC14

R291 20R1%0402R291 20R1%0402

R289 20R1%0402R289 20R1%0402

R335 100R1%0402R335 100R1%0402

R323 24.9R1%0402R323 24.9R1%0402

R334 130R1%0402R334 130R1%0402

R324 49.9R1%0402R324 49.9R1%0402

R262 49.9R1%0402R262 49.9R1%0402

SKTOCC#18

R299 X_3.3KRR299 X_3.3KR

R303 X_3.3KRR303 X_3.3KR

R307 X_3.3KRR307 X_3.3KR

R301 X_3.3KRR301 X_3.3KR

R294 X_3.3KRR294 X_3.3KR

R306 X_3.3KRR306 X_3.3KR

R311 X_3.3KRR311 X_3.3KR

R296 3.01KRR296 3.01KR

R305 X_3.3KRR305 X_3.3KR

TP2TP2

TP27TP27

TP24TP24

TP28TP28

TP30TP30

TP26TP26

TP33TP33

TP32TP32

TP31TP31

TP25TP25

H_TDO_TDI_M

VTT_PGD

MEM_PWRGD

H_PECI

H_CATERR#

H_PROCHOT#

H_THERMTRIP#

PM_SYNC

H_COMP2

H_COMP3

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

H_COMP1

H_COMP0

SKTOCC#

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

H_MCP_CFG15

For DP port

X_COPPER

X_COPPER

X_COPPER

X_COPPER

CP2

CP2

CP3

CP3

CPU_VTT

H_MCP_CFG0

H_MCP_CFG1

H_MCP_CFG2

H_MCP_CFG3

H_MCP_CFG4

H_MCP_CFG5

H_MCP_CFG6

H_MCP_CFG7

H_MCP_CFG8

H_MCP_CFG9

H_MCP_CFG10

H_MCP_CFG11

H_MCP_CFG12

H_MCP_CFG13

H_MCP_CFG14

H_MCP_CFG15

H_MCP_CFG16

H_MCP_CFG17

TP29TP29

R293 X_3.3KRR293 X_3.3KR

R298 X_3.3KRR298 X_3.3KR

R302 X_3.3KRR302 X_3.3KR

CPURST#

PROC_PWROK

VCCP_PWRGD

TP_GFX_DPRSLPVR

CPU_VTT

CFG 0~5 HAVE INTERNAL PULL-UPS

CFG HL

0

SEE PEG CONFIG TABLE

1

SEE PEG CONFIG TABLE

2

SEE PEG CONFIG TABLE

3

NORM

A A

4

DISABLE

REVERSED

ENABLED

DESCRIPTION

PEG SEL0

PEG SEL1

PEG SEL2

PEG LANE REVERSAL

DP PRESENCE

5

PEG CONFIG TABLE

SEL2 SEL1 SEL0 PCIE CONFIG

1

1

1

1 1 X 16

0 2 X 8

5

1

CPU1E

AA7

BCLK[0]

AA6

BCLK[0]*

AA3

PEG_CLK

AA4

PEG_CLK*

Y8

BCLK[1]*

AA8

BCLK[1]

AF37

TDI_M

AF38

TD0_M

AF34

RSTIN*

AH36

PROC_PWROK

AH35

VCCPWRGOOD

AG37

VTTPWRGOOD

AH37

SM_DRAMPWROK

AG35

PECI

AG39

CATERR*

AH34

PROCHOT*

AF35

THERMTRIP*

AH39

PM_SYNC

AB5

PM_EXT_TS[0]*

AB4

PM_EXT_TS[1]*

B11

COMP2

C11

COMP3

AG1

SM_RCOMP[0]

AD1

SM_RCOMP[1]

AE1

SM_RCOMP[2]

AF2

COMP1

AF36

COMP0

AK38

SKTOCC*

E8

CFG0

G8

CFG1/RSVD

E10

CFG2/RSVD

F10

CFG3/PEG_LANE_REVERSAL

H10

CFG4/RSVD

H9

CFG5/VSS

E9

CFG6/FC_E9

F9

CFG7/FC_F9

G12

CFG8/FC_G12

H12

CFG9/FC_H12

K10

CFG10/FC_K10

K8

CFG11/FC_K8

J12

CFG12/FC_J12

L8

CFG13/FC_L8

K9

CFG14/FC_K9

K12

CFG15/FC_K12

H7

CFG16/FC_H7

L11

CFG17/FC_L11

A4

RSVD

B3

RSVD

C2

RSVD

D1

RSVD

J10

GFX_DPRSLPVR/RSVD

AV38

VSS

AK12

RSVD

AK13

RSVD

AK14

RSVD

AL12

RSVD

AM15

RSVD

AM16

RSVD

AM18

RSVD

AM19

RSVD

AM20

RSVD

AM21

RSVD

AU40

RSVD

AV1

RSVD

AV39

RSVD

AW2

RSVD

AW38

RSVD

AY37

RSVD

CPU_RESET_OUT#

PM_SYNC

CPURST#

H_PECI

H_PROCHOT#

H_THERMTRIP#

H_CATERR#

XDP_CPU_PRDY#

CPU_TDI

CPU_TDO

CPU_TRST#

CPU_TMS

CPU_TCK

4

VID[0]/MSID[0]

VID[1]/MSID[1]

VID[2]/MSID[2]

VID[3]/MSID[3]

VID[4]/MSID[4]

VID[5]/MSID[5]

GFX_VR_EN

GFX_IMON/RSVD

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

FC_AE38

VTT_SELECT

FC_AG40

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

VAXG_SENSE

VSSAXG_SENSE

BCLK_ITP*

BCLK_ITP

TAPPWRGOOD

RESET_OBS*

MISC

MISC

5 OF 12

5 OF 12

N12-160A010-F02

RN15 8P4R-51R0402RN15 8P4R-51R0402

R265 51R0402R265 51R0402

R245 51R0402R245 51R0402

R256 X_51R0402R256 X_51R0402

R255 X_51R0402R255 X_51R0402

R257 X_51R0402R257 X_51R0402

R207 51R0402R207 51R0402

R361 X_51R0402R361 X_51R0402

1

3

5

7

4

ISENSE

TRST*

PRDY*

PREQ*

BPM[0]*

BPM[1]*

BPM[2]*

BPM[3]*

BPM[4]*

BPM[5]*

BPM[6]*

BPM[7]*

1

3

5

7

2

4

6

8

VID[6]

VID[7]

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

DBR*

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

PSI*

TDO

TCK

TMS

U40

U39

U38

U37

U36

U35

U34

U33

AG38

F12

F6

G10

B12

E12

E11

C12

G11

J11

AE38

AF39

AG40

T35

T34

AE35

AE36

A13

B13

T40

AL18

AK18

T39

M12

L12

AL15

AL14

AM38

AM37

TDI

AN37

AN40

AM39

AJ38

AK37

AL40

AK40

AK39

AK34

AL39

AL33

AL32

AK33

AK32

AM31

AL30

AK30

AK31

AL17

AM17

AM25

AL29

AM30

AK29

AK28

AM29

AM28

AL27

AK27

AM26

AM27

AL26

AK26

AK25

CPU_VTT

2

4

6

8

CPU_VTT

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

H_VID7

R312 0R0402R312 0R0402

TP_MCP_VCCVTT_VID0

TP_MCP_VCCVTT_VID2

CPU_VCC_SENSE

CPU_VSS_SENSE

VCCP_IMAX

CPU_TDO

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TRST#

XDP_CPU_PRDY#

XDP_CPU_PREQ#

FP_RST#

XDP_CPU_BCLK_N

XDP_CPU_BCLK_P

XDP_CPU_PWRGD

CPU_RESET_OUT#

XDP_CPU_BPM_N0

XDP_CPU_BPM_N1

XDP_CPU_BPM_N2

XDP_CPU_BPM_N3

XDP_CPU_BPM_N4

XDP_CPU_BPM_N5

XDP_CPU_BPM_N6

XDP_CPU_BPM_N7

demo board empty

check list not empty

RN16

RN16

8P4R-51R0402

8P4R-51R0402

H_VID0 32

H_VID1 32

CPU_PSI

R232 0R0402R232 0R0402

H_PROCHOT#

3

H_VID[7..2] 32

R254 X_1KR1%0402R254 X_1KR1%0402

TP3TP3

VTT_SELECT 29

TP4TP4

CPU_VCC_SENSE 32

CPU_VSS_SENSE 32

R243 X_0R0402R243 X_0R0402

CPU_TDO 36

CPU_TDI 36

CPU_TCK 36

CPU_TMS 36

CPU_TRST# 36

XDP_CPU_PRDY# 36

XDP_CPU_PREQ# 36

FP_RST# 15,35,36

XDP_CPU_BCLK_N 36

XDP_CPU_BCLK_P 36

XDP_CPU_PWRGD 36

CPU_RESET_OUT# 36

XDP_CPU_BPM_N0 36

XDP_CPU_BPM_N1 36

XDP_CPU_BPM_N2 36

XDP_CPU_BPM_N3 36

XDP_CPU_BPM_N4 36

XDP_CPU_BPM_N5 36

XDP_CPU_BPM_N6 36

XDP_CPU_BPM_N7 36

demo board no connect

CPU_VTT

R178

R178

1KR1%0402

1KR1%0402

B

CPU_PSI

Q31

Q31

N-SST3904_SOT23

N-SST3904_SOT23

CPU_VTT

B

C E

N-SST3904_SOT23

N-SST3904_SOT23

CE

Q40

Q40

3

CPU_VTT

VCCP_IMAX 32

PSI# 34

SIO_TRIP# 18

EXP_A_RXP_019

EXP_A_RXN_019

EXP_A_RXP_119

EXP_A_RXN_119

EXP_A_RXP_219

EXP_A_RXN_219

EXP_A_RXP_319

EXP_A_RXN_319

EXP_A_RXP_419

EXP_A_RXN_419

EXP_A_RXP_519

EXP_A_RXN_519

EXP_A_RXP_619

EXP_A_RXN_619

EXP_A_RXP_719

EXP_A_RXN_719

EXP_A_RXP_819

EXP_A_RXN_819

EXP_A_RXP_919

EXP_A_RXN_919

EXP_A_RXP_1019

EXP_A_RXN_1019

EXP_A_RXP_1119

EXP_A_RXN_1119

EXP_A_RXP_1219

EXP_A_RXN_1219

EXP_A_RXP_1319

EXP_A_RXN_1319

EXP_A_RXP_1419

EXP_A_RXN_1419

EXP_A_RXP_1519

EXP_A_RXN_1519

DMI_RX013

DMI_RX0#13

DMI_RX113

DMI_RX1#13

DMI_RX213

DMI_RX2#13

DMI_RX313

DMI_RX3#13

1

3

5

7

RN25

RN25

8P4R-1KR0402

8P4R-1KR0402

R327 1KR1%0402R327 1KR1%0402

PLTRST#15,18,36

R180

R180

2

4

6

8

DMI_RX0

DMI_RX0#

DMI_RX1

DMI_RX1#

DMI_RX2

DMI_RX2#

DMI_RX3

DMI_RX3#

10KR1%0402

10KR1%0402

2

B

2

CPU1C

CPU1C

C9

PEG_RX[0]

D9

PEG_RX[0]*

B8

PEG_RX[1]

C8

PEG_RX[1]*

A7

PEG_RX[2]

A6

PEG_RX[2]*

B6

PEG_RX[3]

C6

PEG_RX[3]*

A5

PEG_RX[4]

B5

PEG_RX[4]*

B4

PEG_RX[5]

C4

PEG_RX[5]*

C3

PEG_RX[6]

D3

PEG_RX[6]*

D2

PEG_RX[7]

E2

PEG_RX[7]*

E1

PEG_RX[8]

F1

PEG_RX[8]*

G3

PEG_RX[9]

G2

PEG_RX[9]*

G1

PEG_RX[10]

H1

PEG_RX[10]*

J3

PEG_RX[11]

J2

PEG_RX[11]*

J1

PEG_RX[12]

K1

PEG_RX[12]*

L2

PEG_RX[13]

L3

PEG_RX[13]*

P3

PEG_RX[14]

P4

PEG_RX[14]*

T3

PEG_RE[15]

T4

PEG_RX[15]*

R1

DMI_RX[0]

T1

DMI_RX[0]*

U3

DMI_RX[1]

U2

DMI_RX[1]*

U1

DMI_RX[2]

V1

DMI_RX[2]*

W3

DMI_RX[3]

W2

DMI_RX[3]*

AM14

RSVD

AM13

RSVD

AK15

RSVD

AK16

RSVD

AC4

AD4

AC3

AD3

AC2

3VSB

R138

R138

10KR1%0402

10KR1%0402

CE

Q33

Q33

N-SST3904_SOT23

N-SST3904_SOT23

CPU1D

CPU1D

FDI_FSYNC[0]

FDI_LSYNC[0]

DISPLAY

DISPLAY

LINK

LINK

FDI_FSYNC[1]

FDI_LSYNC[1]

FDI_INT

4 OF 12

4 OF 12

CPU_VTT

B

PEG

PEG

DMI

DMI

3 OF 12

3 OF 12

VDDIO

VDDIO

R224

R224

150R0402

150R0402

CE

Q32

Q32

N-SST3904_SOT23

N-SST3904_SOT23

PEG_TX[0]

PEG_TX[0]*

PEG_TX[1]

PEG_TX[1]*

PEG_TX[2]

PEG_TX[2]*

PEG_TX[3]

PEG_TX[3]*

PEG_TX[4]

PEG_TX[4]*

PEG_TX[5]

PEG_TX[5]*

PEG_TX[6]

PEG_TX[6]*

PEG_TX[7]

PEG_TX[7]*

PEG_TX[8]

PEG_TX[8]*

PEG_TX[9]

PEG_TX[9]*

PEG_TX[10]

PEG_TX[10]*

PEG_TX[11]

PEG_TX[11]*

PEG_TX[12]

PEG_TX[12]*

PEG_TX[13]

PEG_TX[13]*

PEG_TX[14]

PEG_TX[14]*

PEG_TX[15]

PEG_TX[15]*

DMI_TX[0]

DMI_TX[0]*

DMI_TX[1]

DMI_TX[1]*

DMI_TX[2]

DMI_TX[2]*

DMI_TX[3]

DMI_TX[3]*

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

FDI_TX[0]

FDI_TX[0]*

FDI_TX[1]

FDI_TX[1]*

FDI_TX[2]

FDI_TX[2]*

FDI_TX[3]

FDI_TX[3]*

FDI_TX[4]

FDI_TX[4]*

FDI_TX[5]

FDI_TX[5]*

FDI_TX[6]

FDI_TX[6]*

FDI_TX[7]

FDI_TX[7]*

CPURST#

MSI

MSI

MSI

1

C7

D7

E7

E6

E5

F5

F3

F4

G6

G5

H4

H3

F7

G7

J6

J5

K3

K4

H8

J8

L6

L5

M4

M3

K7

L7

N6

N5

M8

N8

R5

R6

L1

M1

N3

N2

N1

P1

R2

R3

D11

C10

B10

A11

Break-out:10mil width, 6 mil space

Other Area:10mil width, 15 mil space

U6

U5

V4

V3

U8

U7

W8

W7

W5

W4

R8

R7

Y4

Y3

Y6

Y5

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Thursday, September 24, 2009

Thursday, September 24, 2009

Thursday, September 24, 2009

EXP_A_TXP_0 19

EXP_A_TXN_0 19

EXP_A_TXP_1 19

EXP_A_TXN_1 19

EXP_A_TXP_2 19

EXP_A_TXN_2 19

EXP_A_TXP_3 19

EXP_A_TXN_3 19

EXP_A_TXP_4 19

EXP_A_TXN_4 19

EXP_A_TXP_5 19

EXP_A_TXN_5 19

EXP_A_TXP_6 19

EXP_A_TXN_6 19

EXP_A_TXP_7 19

EXP_A_TXN_7 19

EXP_A_TXP_8 19

EXP_A_TXN_8 19

EXP_A_TXP_9 19

EXP_A_TXN_9 19

EXP_A_TXP_10 19

EXP_A_TXN_10 19

EXP_A_TXP_11 19

EXP_A_TXN_11 19

EXP_A_TXP_12 19

EXP_A_TXN_12 19

EXP_A_TXP_13 19

EXP_A_TXN_13 19

EXP_A_TXP_14 19

EXP_A_TXN_14 19

EXP_A_TXP_15 19

EXP_A_TXN_15 19

DMI_TX0

DMI_TX0 13

DMI_TX0#

DMI_TX0# 13

DMI_TX1

DMI_TX1 13

DMI_TX1#

DMI_TX1# 13

DMI_TX2

DMI_TX2 13

DMI_TX2#

DMI_TX2# 13

DMI_TX3

DMI_TX3 13

DMI_TX3#

DMI_TX3# 13

GRCOMP

GRBIAS

X_2KR0402

X_2KR0402

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

CPU-CNTL/CLK/MISC

R206

R206

R297

R297

49.9R1%0402

49.9R1%0402

R290

R290

750R1%0402

750R1%0402

MS-7588

MS-7588

MS-7588

1

R246

R246

X_1KR0402

X_1KR0402

CPURST#CPURST#PLTRST#

C71

C71

X_C100p50N0402

X_C100p50N0402

Sheet ofDate:

639

Sheet ofDate:

639

Sheet ofDate:

639

0A

0A

0A

5

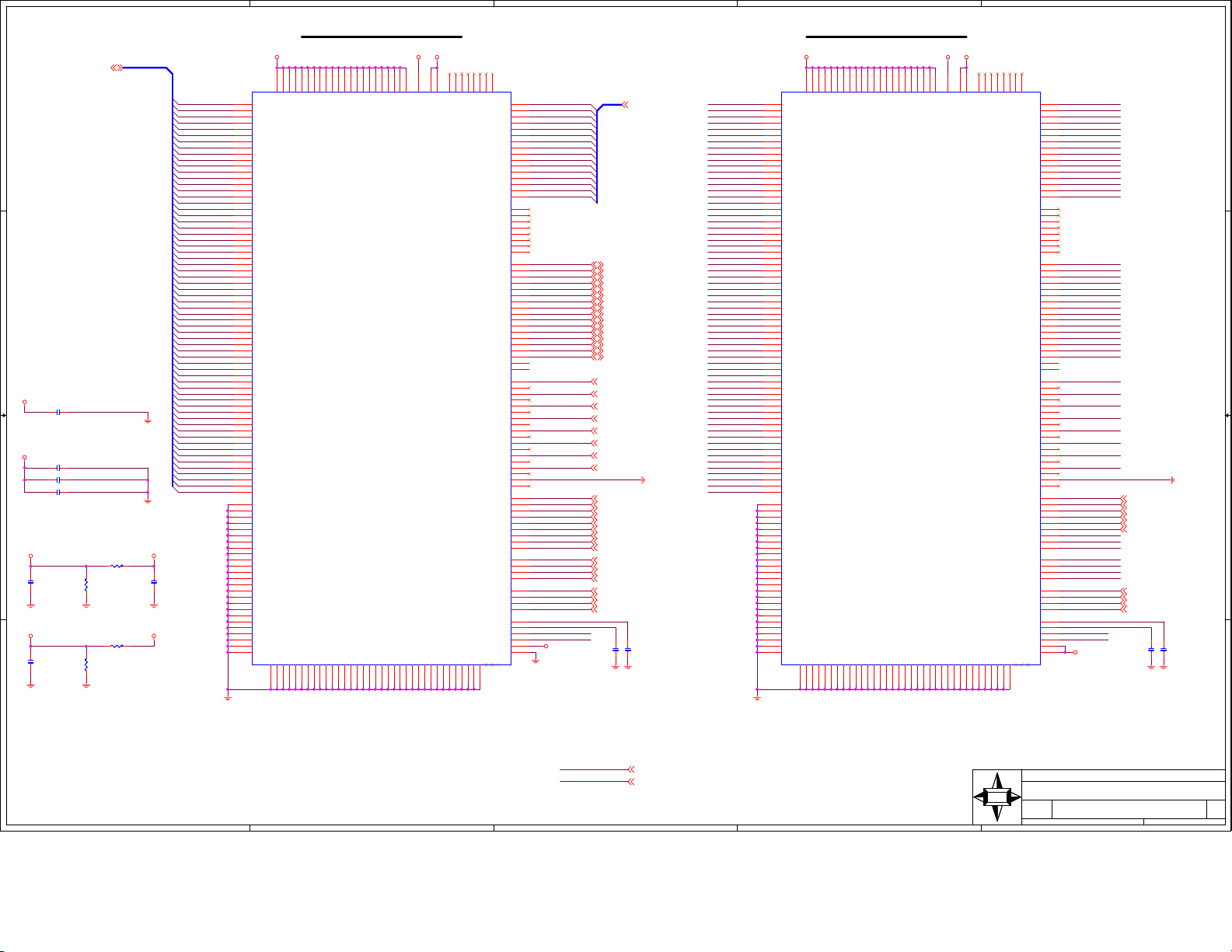

CPU1A

MEM_MA_ADD[15..0]10

D D

MEM_MA_WE_L10

MEM_MA_CAS_L10

MEM_MA_RAS_L10

MEM_MA_BANK010

MEM_MA_BANK110

MEM_MA_BANK210

MEM_MA_CS_L010

MEM_MA_CS_L110

MEM_MA_CS_L210

MEM_MA_CS_L310

MEM_MA_CKE010

MEM_MA_CKE110

MEM_MA_CKE210

MEM_MA_CKE310

MEM_MA_ODT010

C C

B B

A A

MEM_MA_ODT110

MEM_MA_ODT210

MEM_MA_ODT310

MEM_MA_CLK_H010

MEM_MA_CLK_L010

MEM_MA_CLK_H110

MEM_MA_CLK_L110

MEM_MA_CLK_H210

MEM_MA_CLK_L210

MEM_MA_CLK_H310

MEM_MA_CLK_L310

MEM_MA_ADD0

MEM_MA_ADD1

MEM_MA_ADD2

MEM_MA_ADD3

MEM_MA_ADD4

MEM_MA_ADD5

MEM_MA_ADD6

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD9

MEM_MA_ADD10

MEM_MA_ADD11

MEM_MA_ADD12

MEM_MA_ADD13

MEM_MA_ADD14

MEM_MA_ADD15 MEM_MB_ADD15

MEM_MA_WE_L

MEM_MA_CAS_L

MEM_MA_RAS_L

MEM_MA_BANK0

MEM_MA_BANK1

MEM_MA_BANK2

MEM_MA_CS_L0

MEM_MA_CS_L1

MEM_MA_CS_L2

MEM_MA_CS_L3

MEM_MA_CKE0

MEM_MA_CKE1

MEM_MA_CKE2

MEM_MA_CKE3

MEM_MA_ODT0

MEM_MA_ODT1

MEM_MA_ODT2

MEM_MA_ODT3

MEM_MA_CLK_H0

MEM_MA_CLK_L0

MEM_MA_CLK_H1

MEM_MA_CLK_L1

MEM_MA_CLK_H2

MEM_MA_CLK_L2

MEM_MA_CLK_H3

MEM_MA_CLK_L3

DDR3_DRAMRST#

5

AW18

AY15

AV15

AU15

AW14

AY13

AV14

AW13

AU14

AW12

AT19

AU13

AW11

AU24

AT11

AR10

AT22

AU22

AT20

AV20

AU19

AU12

AV21

AW24

AU21

AU23

AU10

AW10

AV10

AY10

AV23

AV24

AW23

AY24

AR22

AR21

AP18

AN18

AN21

AP21

AP19

AN19

AK22

AM22

AL23

AK23

AL10

AM10

AP10

AN10

AR11

AP11

AK11

AM11

AV8

AK9

AL9

CPU1A

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_WE*

SA_CAS*

SA_RAS*

SA_BA[0]

SA_BA[1]

SA_BA[2]

SA_CS[0]*

SA_CS[1]*

SA_CS[2]*

SA_CS[3]*

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_CK[0]

SA_CK[0]*

SA_CK[1]

SA_CK[1]*

SA_CK[2]

SA_CK[2]*

SA_CK[3]

SA_CK[3]*

SM_DRAMRST*

SA_CS[4]*

SA_CS[5]*

SA_CS[6]*

SA_CS[7]*

SA_DQS[8]

SA_DQS[8]*

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

DDR_A

DDR_A

1 OF 12

1 OF 12

SA_DQS[0]

SA_DQS[0]*

SA_DQS[1]

SA_DQS[1]*

SA_DQS[2]

SA_DQS[2]*

SA_DQS[3]

SA_DQS[3]*

SA_DQS[4]

SA_DQS[4]*

SA_DQS[5]

SA_DQS[5]*

SA_DQS[6]

SA_DQS[6]*

SA_DQS[7]

SA_DQS[7]*

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AK3

AJ3

AP2

AP3

AU4

AU3

AY6

AW6

AR28

AT29

AV32

AW32

AW36

AV35

AR39

AR38

AJ2

AN1

AU1

AV6

AN29

AW31

AU35

AT38

AH1

AJ4

AL2

AL1

AG2

AH2

AK1

AK2

AN3

AN2

AR3

AR2

AM3

AM2

AP1

AR4

AT4

AU2

AW3

AW4

AT3

AT1

AV2

AV4

AW5

AY5

AU8

AY8

AU5

AV5

AV7

AW7

AN27

AT28

AP28

AP30

AN26

AR27

AR29

AN30

AU30

AU31

AV33

AU34

AV30

AW30

AU33

AW33

AW35

AY35

AV37

AU37

AY34

AW34

AV36

AW37

AT39

AT40

AN38

AN39

AU38

AU39

AP39

AP40

4

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DDR3_DRAMRST#

4

MEM_MA_DQS_H0 10

MEM_MA_DQS_L0 10

MEM_MA_DQS_H1 10

MEM_MA_DQS_L1 10

MEM_MA_DQS_H2 10

MEM_MA_DQS_L2 10

MEM_MA_DQS_H3 10

MEM_MA_DQS_L3 10

MEM_MA_DQS_H4 10

MEM_MA_DQS_L4 10

MEM_MA_DQS_H5 10

MEM_MA_DQS_L5 10

MEM_MA_DQS_H6 10

MEM_MA_DQS_L6 10

MEM_MA_DQS_H7 10

MEM_MA_DQS_L7 10

MEM_MA_DM0 10

MEM_MA_DM1 10

MEM_MA_DM2 10

MEM_MA_DM3 10

MEM_MA_DM4 10

MEM_MA_DM5 10

MEM_MA_DM6 10

MEM_MA_DM7 10

MEM_MA_DATA[63..0] 10

R145 1KR1%0402R145 1KR1%0402

Q34

Q34

N-SST3904_SOT23

N-SST3904_SOT23

B

VCC_DDR

CE

R147

R147

470R0402

470R0402

R149 470R0402R149 470R0402

R165 470R0402R165 470R0402

R146 X_0R0402R146 X_0R0402

3

MEM_MB_ADD[15..0]11

MEM_MB_WE_L11

MEM_MB_CAS_L11

MEM_MB_RAS_L11

MEM_MB_BANK011

MEM_MB_BANK111

MEM_MB_BANK211

MEM_MB_CS_L011

MEM_MB_CS_L111

MEM_MB_CS_L211

MEM_MB_CS_L311

MEM_MB_CKE011

MEM_MB_CKE111

MEM_MB_CKE211

MEM_MB_CKE311

MEM_MB_ODT011

MEM_MB_ODT111

MEM_MB_ODT211

MEM_MB_ODT311

MEM_MB_CLK_H011

MEM_MB_CLK_L011

MEM_MB_CLK_H111

MEM_MB_CLK_L111

MEM_MB_CLK_H211

MEM_MB_CLK_L211

MEM_MB_CLK_H311

MEM_MB_CLK_L311

VCC_DDR

B

Q36

Q36

N-SST3904_SOT23

N-SST3904_SOT23

VCC_DDR

B

Q35

Q35

N-SST3904_SOT23

N-SST3904_SOT23

3

CE

CE

R150

R150

150R0402

150R0402

R148

R148

150R0402

150R0402

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB_BANK0

MEM_MB_BANK1

MEM_MB_BANK2

MEM_MB_CS_L0

MEM_MB_CS_L1

MEM_MB_CS_L2

MEM_MB_CS_L3

MEM_MB_CKE0

MEM_MB_CKE1

MEM_MB_CKE2

MEM_MB_CKE3

MEM_MB_ODT0

MEM_MB_ODT1

MEM_MB_ODT2

MEM_MB_ODT3

MEM_MB_CLK_H0

MEM_MB_CLK_L0

MEM_MB_CLK_H1

MEM_MB_CLK_L1

MEM_MB_CLK_H2

MEM_MB_CLK_L2

MEM_MB_CLK_H3

MEM_MB_CLK_L3

DDR3_DRAMRST#B 11

R166

R166

X_0R0402

X_0R0402

DDR3_DRAMRST#A 10

AU20

AU18

AV18

AU17

AY18

AV17

AW17

AU16

AT17

AY16

AY25

AW16

AW15

AW28

AY12

AV11

AU26

AW27

AW26

AU25

AW25

AV12

AY27

AW29

AV26

AV29

AW8

AU27

AU29

AV27

AU28

AR17

AR16

AT15

AR15

AN17

AN16

AR19

AR18

AM23

AM24

AL24

AK24

AR14

AR13

AR12

AT13

AN15

AP14

AM12

AN12

AN14

AP13

AY9

AU9

AV9

CPU1B

CPU1B

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_WE*

SB_CAS*

SB_RAS*

SB_BA[0]

SB_BA[1]

SB_BA[2]

SB_CS[0]*

SB_CS[1]*

SB_CS[2]*

SB_CS[3]*

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_CK[0]

SB_CK[0]*

SB_CK[1]

SB_CK[1]*

SB_CK[2]

SB_CK[2]*

SB_CK[3]

SB_CK[3]*

SB_CS[4]*

SB_CS[5]*

SB_CS[6]*

SB_CS[7]*

SB_DQS[8]

SB_DQS[8]*

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

DDR_B

DDR_B

2 OF 12

2 OF 12

2

MEM_MB_DQS_H0

AF4

SB_DQS[0]

SB_DQS[0]*

SB_DQS[1]

SB_DQS[1]*

SB_DQS[2]

SB_DQS[2]*

SB_DQS[3]

SB_DQS[3]*

SB_DQS[4]

SB_DQS[4]*

SB_DQS[5]

SB_DQS[5]*

SB_DQS[6]

SB_DQS[6]*

SB_DQS[7]

SB_DQS[7]*

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

2

AE5

AH6

AJ5

AN6

AM6

AR8

AP8

AT25

AR24

AP32

AR32

AR36

AR37

AL37

AM36

AE4

AH4

AM7

AT7

AN24

AN32

AM33

AK35

AD7

AD6

AH8

AJ8

AC7

AC6

AF5

AE6

AG5

AH7

AK6

AL4

AG6

AG4

AJ7

AK7

AL6

AN5

AP6

AR5

AL5

AM4

AN7

AP5

AT6

AR7

AR9

AM8

AN8

AR6

AL8

AT9

AN23

AP23

AR25

AR26

AT23

AP22

AP25

AT26

AT32

AP31

AR33

AM32

AT31

AR31

AR34

AT33

AR35

AT36

AN33

AP36

AP34

AT35

AN34

AP37

AL35

AM35

AJ36

AJ37

AN35

AM34

AJ35

AL36

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

CPU-Memory

CPU-Memory

CPU-Memory

Thursday, September 24, 2009

Thursday, September 24, 2009

Thursday, September 24, 2009

1

MEM_MB_DQS_H0 11

MEM_MB_DQS_L0 11

MEM_MB_DQS_H1 11

MEM_MB_DQS_L1 11

MEM_MB_DQS_H2 11

MEM_MB_DQS_L2 11

MEM_MB_DQS_H3 11

MEM_MB_DQS_L3 11

MEM_MB_DQS_H4 11

MEM_MB_DQS_L4 11

MEM_MB_DQS_H5 11

MEM_MB_DQS_L5 11

MEM_MB_DQS_H6 11

MEM_MB_DQS_L6 11

MEM_MB_DQS_H7 11

MEM_MB_DQS_L7 11

MEM_MB_DM0 11

MEM_MB_DM1 11

MEM_MB_DM2 11

MEM_MB_DM3 11

MEM_MB_DM4 11

MEM_MB_DM5 11

MEM_MB_DM6 11

MEM_MB_DM7 11

MEM_MB_DATA[63..0] 11

MS-7588

MS-7588

MS-7588

1

Sheet ofDate:

739

Sheet ofDate:

739

Sheet ofDate:

739

0A

0A

0A

5

CPU1F

CPU1F

CPU

CPU

A23

VCC

A24

POWER

POWER

VCC

A26

VCC

A27

VCC

A33

VCC

A35

VCC

A36

VCC

A38

VCC

D D

C C

B B

A A

B23

VCC

B25

VCC

B26

VCC

B28

VCC

B29

VCC

B31

VCC

B32

VCC

B34

VCC

B35

VCC

B37

VCC

B38

VCC

C23

VCC

C24

VCC

C25

VCC

C27

VCC

C28

VCC

C30

VCC

C31

VCC

C33

VCC

C34

VCC

C36

VCC

C37

VCC

C39

VCC

C40

VCC

D23

VCC

D24

VCC

D26

VCC

D27

VCC

D29

VCC

D30

VCC

D32

VCC

D33

VCC

D35

VCC

D36

VCC

D38

VCC

D39

VCC

E22

VCC

E23

VCC

E25

VCC

E26

VCC

E28

VCC

E29

VCC

E31

VCC

E32

VCC

E34

VCC

E35

VCC

E37

VCC

E38

VCC

E40

VCC

F21

VCC

F22

VCC

F24

VCC

F25

VCC

F27

VCC

F28

VCC

F30

VCC

F31

VCC

F33

VCC

F34

VCC

F36

VCC

F37

VCC

F39

VCC

F40

VCC

G20

VCC

G21

VCC

G23

VCC

G24

VCC

G26

VCC

G27

VCC

G29

VCC

G30

VCC

G32

VCC

G33

VCC

G35

VCC

G36

VCC

G38

VCC

G39

VCC

H19

VCC

H20

VCC

H22

VCC

H23

VCC

H25

VCC

6 OF 12

6 OF 12

H26

VCC

H28

VCC

H29

VCC

H31

VCC

H32

VCC

H34

VCC

H35

VCC

H37

VCC

H38

VCC

H40

VCC

J18

VCC

J19

VCC

J21

VCC

J22

VCC

J24

VCC

J25

VCC

J27

VCC

J28

VCC

J30

VCC

J31

VCC

J33

VCC

J34

VCC

J36

VCC

J37

VCC

J39

VCC

J40

VCC

K17

VCC

K18

VCC

K20

VCC

K21

VCC

K23

VCC

K24

VCC

K26

VCC

K27

VCC

K29

VCC

K30

VCC

K32

VCC

K33

VCC

K35

VCC

K36

VCC

K38

VCC

K39

VCC

L17

VCC

L19

VCC

L20

VCC

L22

VCC

L23

VCC

L25

VCC

L26

VCC

L28

VCC

L29

VCC

L31

VCC

L32

VCC

L34

VCC

L35

VCC

L37

VCC

L38

VCC

L40

VCC

M17

VCC

M19

VCC

M21

VCC

M22

VCC

M24

VCC

M25

VCC

M27

VCC

M28

VCC

M30

VCC

M33

VCC

M34

VCC

M36

VCC

M37

VCC

M39

VCC

M40

VCC

N33

VCC

N35

VCC

N36

VCC

N38

VCC

N39

VCC

P33

VCC

P34

VCC

P35

VCC

P36

VCC

P37

VCC

P38

VCC

P39

VCC

P40

VCC

R33

VCC

R34

VCC

R35

VCC

R36

VCC

R37

VCC

R38

VCC

R39

VCC

R40

VCC

5

VCC1_8

AA33

AA34

AA35

AA36

AA37

AA38

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AE33

AE34

AE39

AE40

AF33

AG33

AK20

AK21

AL20

AL21

AK19

AJ31

AJ32

AJ21

AJ25

AJ27

AJ29

AC8

AJ17

AJ19

AC5

AJ23

AG8

V33

V34

V35

V36

V37

V38

V39

V40

Y33

Y34

Y35

Y36

Y37

Y38

AE8

AF8

AF7

CPU1G

CPU1G

VTT_01

VTT_02

VTT_03

VTT_04

VTT_05

VTT_06

VTT_07

VTT_08

VTT_09

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

VTT_20

VTT_21

VTT_22

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

VTT_28

VTT_29

VTT_30

VTT_31

VTT_32

VTT_33

VTT_34

VTT_35

VTT_36

VTT_37

VTT_38

VTT_39

VTT_40

VTT_41

VTT_42

VTT_43

VTT_44

VTT_45

VTT_46

VTT_47

VTT_48

VTT_49

VTT_50

VTT_51

VTT_52

VTT_53

VTT_54

VTT_55

VTT_56

VTT_57

VTT_58

VTT_60

VCCPLL_01

VCCPLL_02

VCCPLL_03

CPU

CPU

POWER

POWER

7 OF 12

7 OF 12

4

CPU1H

CPU1H

A14

VAXG_01

A15

VAXG_02

A17

VAXG_03

A18

VAXG_04

B14

VAXG_05

B15

VAXG_06

B17

VAXG_07

B18

VAXG_08

C14

VAXG_09

C15

VAXG_10

C17

VAXG_11

C18

VAXG_12

C20

VAXG_13

C21

VAXG_14

D14

VAXG_15

D15

VAXG_16

D17

VAXG_17

D18

VAXG_18

D20

VAXG_19

D21

VAXG_20

E14

VAXG_21

E15

VAXG_22

E17

VAXG_23

E18

VAXG_24

E20

VAXG_25

F14

VAXG_26

F15

VAXG_27

F17

VAXG_28

F18

VAXG_29

F19

VAXG_30

G14

VAXG_31

G15

VAXG_32

G17

VAXG_33

G18

VAXG_34

H14

VAXG_35

H15

VAXG_36

H17

VAXG_37

J14

VAXG_38

J15

VAXG_39

J16

VAXG_40

K14

VAXG_41

K15

VAXG_42

K16

VAXG_43

L14

VAXG_44

L15

VAXG_45

L16

VAXG_46

M14

VAXG_47

M15

VAXG_48

M16

VAXG_49

CPU

CPU

POWER

POWER

VTT_61

VTT_62

VTT_63

VTT_64

VTT_65

VTT_66

T6

T7

T8

V7

V8

AB7

CPU_VTT

3

VCC_DDR

2

CPU_VTTVCCPVCCP CPU_VTT

CPU1I

CPU1I

L10

VTT_67

M10

VTT_68

M11

VTT_69

M9

VTT_70

N7

VTT_71

P6

VTT_72

P7

VTT_73

P8

VTT_74

T2

VTT_75

V2

VTT_76

V6

VTT_77

W1

VTT_78

W6

VTT_79

1

+1.5V_DDR3-Decoupling

VCC_DDR

C177

C177

C185

C22u6.3X50805-RH

C22u6.3X50805-RH

C185

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

CPU SOCKET CAVITY CAPS

AJ11

VDDQ_01

AJ13

VDDQ_02

AJ15

VDDQ_03

AT18

VDDQ_04

AT21

VDDQ_05

AT10

VDDQ_06

AU11

VDDQ_07

AV13

VDDQ_08

AV16

VDDQ_09

AV19

VDDQ_10

AV22

AV25

AV28

AW9

AY11

AY14

AY17

AY23

AY26

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

CPU

CPU

POWER

POWER

9 OF 12

9 OF 12

CPU_VTT

C156

C156

C22u6.3X50805-RH

C22u6.3X50805-RH

+CPU_VTT Decoupling

C155

C155

C4.7u10X51206-RH

C4.7u10X51206-RH

C142

C142

C172

C141

C141

C22u6.3X50805-RH

C22u6.3X50805-RH

C172

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C80

C80

X_C4.7u10X51206-RH

X_C4.7u10X51206-RH

C161

C161

C4.7u10X51206-RH

C4.7u10X51206-RH

C151

C151

CPU_VTT

C136

C136

C167

C167

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C137

C137

C559

C559

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

璉

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

CPU SOCKET CAVITY CAPS

8 OF 12

8 OF 12

+CPU_VCCP-Decoupling

VCCP

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C173

C173

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C153

C153

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C178

C178

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C139

C139

C22u6.3X50805-RH

C22u6.3X50805-RH

C179

C179

C158

C158

C22u6.3X50805-RH

C22u6.3X50805-RH

C162

C162

C558

C558

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C561

C561

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C22u6.3X50805-RH

C22u6.3X50805-RH

C170

C170

C22u6.3X50805-RH

C22u6.3X50805-RH

C152

C152

C22u6.3X50805-RH

C22u6.3X50805-RH

C171

C171

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C557

C557

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C169

C169

C22u6.3X50805-RH

C22u6.3X50805-RH

C140

C140

C22u6.3X50805-RH

C22u6.3X50805-RH

C160

C160

C168

C168

C180

C180

C22u6.3X50805-RH

C22u6.3X50805-RH

C562

C562

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C188

C188

X_C22u6.3X50805-RH

X_C22u6.3X50805-RH

C189

C189

PLACE ALL 08056 CAPS INSIDE CPU SOCKET CAVITY

4

3

2

VCC1_8

VCCP

MSI

MSI

MSI

C195

C195

C22u6.3X50805-RH

C22u6.3X50805-RH

C166

C201

C201

X_C1u10Y

X_C1u10Y

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

C166

C182

C182

X_C1u10Y

X_C1u10Y

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

CPU-Power

CPU-Power

CPU-Power

Thursday, September 24, 2009

Thursday, September 24, 2009

Thursday, September 24, 2009

X_C1u10Y

X_C1u10Y

C154

C154

X_C1u10Y

X_C1u10Y

MS-7588

MS-7588

MS-7588

1

C131

C131

X_C1u10Y

X_C1u10Y

Sheet ofDate:

Sheet ofDate:

Sheet ofDate:

0A

0A

0A

839

839

839

5

4

3

2

1

CPU1J

CPU1J

A16

VSS

A25

VSS

A28

VSS

A34

VSS

A37

VSS

D D

C C

B B

A A

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AE37

AF40

AG34

AG36

AH33

AH38

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AJ26

AJ28

AJ30

AJ33

AJ34

AJ40

AK10

AK17

AK36

AL11

AL13

AL16

AL19

AL22

AL25

AL28

AL31

AL34

AL38

AM40

AN13

AN20

AN22

AN25

AN28

AN31

AN36

AP12

AP15

AP16

AP17

AP20

AP24

AP26

AP27

AP29

AP35

AA5

VSS

AB3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB6

VSS

AB8

VSS

AC1

VSS

AD5

VSS

AD8

VSS

AE3

VSS

VSS

AE7

VSS

AF1

VSS

VSS

AF6

VSS

VSS

VSS

AH5

VSS

AG7

VSS

AH3

VSS

VSS

VSS

AJ1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ6

VSS

AJ9

VSS

VSS

VSS

VSS

AK5

VSS

AK8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

VSS

VSS

VSS

VSS

AL7

VSS

AM1

VSS

VSS

AK4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM5

VSS

VSS

AM9

VSS

AN4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN9

VSS

VSS

10 OF 12

10 OF 12

AP33

VSS

AP38

VSS

AP4

VSS

AP7

VSS

AP9

VSS

AR1

VSS

AR20

VSS

AR23

VSS

AR40

VSS

AT12

VSS

AT14

VSS

AT16

VSS

AT2

VSS

AT24

VSS

AT27

VSS

AT30

VSS

AR30

VSS

AT34

VSS

AT37

VSS

AT5

VSS

AU32

VSS

AT8

VSS

AV3

VSS

AV31

VSS

AV34

VSS

AU36

VSS

AU6

VSS

AY33

VSS

AY36

VSS

AY4

VSS

AY7

VSS

B16

VSS

B24

VSS

B27

VSS

B30

VSS

B33

VSS

B36

VSS

B7

VSS

B9

VSS

C13

VSS

C16

VSS

C19

VSS

C22

VSS

C26

VSS

C29

VSS

C32

VSS

C35

VSS

C38

VSS

C5

VSS

D10

VSS

D12

VSS

D13

VSS

D16

VSS

D19

VSS

D22

VSS

D25

VSS

D28

VSS

D31

VSS

D34

VSS

D37

VSS

D4

VSS

D40

VSS

D5

VSS

D6

VSS

D8

VSS

E13

VSS

E16

VSS

E19

VSS

E21

VSS

E24

VSS

E27

VSS

E3

VSS

E30

VSS

E33

VSS

E36

VSS

E39

VSS

E4

VSS

F11

VSS

F13

VSS

F16

VSS

F2

VSS

F20

VSS

F23

VSS

F26

VSS

F29

VSS

F32

VSS

F35

VSS

F38

VSS

F8

VSS

G13

VSS

CPU1K

CPU1K

G16

VSS

G19

VSS

G22

VSS

G25

VSS

G28

VSS

G31

VSS

G34

VSS

G37

VSS

G4

VSS

G40

VSS

G9

VSS

H11

VSS

H13

VSS

H16

VSS

H18

VSS

H2

VSS

H21

VSS

H24

VSS

H27

VSS

H30

VSS

H33

VSS

H36

VSS

H39

VSS

H5

VSS

H6

VSS

J13

VSS

J17

VSS

J20

VSS

J23

VSS

J26

VSS

J29

VSS

J32

VSS

J35

VSS

J38

VSS

J4

VSS

J7

VSS

J9

VSS

K11

VSS

K13

VSS

K19

VSS

K2

VSS

K22

VSS

K25

VSS

K28

VSS

K31

VSS

K34

VSS

K37

VSS

K40

VSS

K5

VSS

K6

VSS

L13

VSS

L18

VSS

L21

VSS

L24

VSS

L27

VSS

L30

VSS

L33

VSS

L36

VSS

L39

VSS

L4

VSS

L9

VSS

M13

VSS

M18

VSS

M2

VSS

M20

VSS

M23

VSS

M26

VSS

M29

VSS

M32

VSS

M35

VSS

M38

VSS

M5

VSS

M6

VSS

M7

VSS

N34

VSS

N37

VSS

N4

VSS

N40

VSS

P2

VSS

P5

VSS

R4

VSS

T33

VSS

T36

VSS

T37

VSS

T38

VSS

T5

VSS

U4

VSS

V5

VSS

W33

VSS

W34

VSS

11 OF 12

11 OF 12

VSS_NCTF

GND

GND

W35

VSS

W36

VSS

W37

VSS

W38

VSS

Y7

VSS

B39

TP_CGC DIMM_VREFA

FOR NEW 1156 CPU R310;R316

VREF_DQ_B VREF_DQ_A

TP23TP23

NOTE:R378,R461 STUFFED,IF DDR3 DIMM VREFDQ OPTION 2 UNSTUFFED.

FOLLOW DDR3 DIMM VREFDQ Platform Design

Guide Change Option 3

R357 X_0R0402R357 X_0R0402

R366 X_0R0402R366 X_0R0402

close to DIMM

ン

DIMM_VREFB

AH40

AJ39

AN11

A12

AD2

AE2

AF3

AG3

AU7

AY3

CPU1L

CPU1L

VDDIO

VDDIO

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

RSVD

RSVD

RSVD

RSVD

NC/SPARE

NC/SPARE

12 OF 12

12 OF 12

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7588

MS-7588

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Thursday, September 24, 2009

Thursday, September 24, 2009

5

4

3

2

Thursday, September 24, 2009

CPU-GND

CPU-GND

CPU-GND

MS-7588

1

Sheet ofDate:

939

Sheet ofDate:

939

Sheet ofDate:

939

0A

0A

0A

5

4

3

2

1

DDRIII DIMM_A1 DDRIII DIMM_A2

VCC_DDR VCC3

54

DIMM2

DIMM2

3

VDD51VDD

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

18

DQ10

19

DQ11

131

DQ12

132

DQ13

137

DQ14

138

DQ15

21

DQ16

22

DQ17

27

DQ18

28

DQ19

140

DQ20

141

DQ21

146

DQ22

147

DQ23

30

DQ24

31

DQ25

36

DQ26

37

DQ27

149

DQ28

150

DQ29

155

DQ30

156

DQ31

81

DQ32

82

DQ33

87

DQ34

88

DQ35

200

DQ36

201

DQ37

206

DQ38

207

DQ39

90

DQ40

91

DQ41

96

DQ42

97

DQ43

209

DQ44

210

DQ45

215

DQ46

216

DQ47

99

DQ48

100

DQ49

105

DQ50

106

DQ51

218

DQ52

219

DQ53

224

DQ54

225

DQ55

108

DQ56

109

DQ57

114

DQ58

115

DQ59

227

DQ60

228

DQ61

233

DQ62

234

DQ63

2

VSS

5

VSS

8

VSS

11

VSS

14

VSS

17

VSS

20

VSS

23

VSS

26

VSS

29

VSS

32

VSS

35

VSS

38

VSS

41

VSS

44

VSS

47

VSS

80

VSS

83

VSS

86

VSS

89

VSS

92

VSS

95

VSS

98

VSS

101

VSS

104

VSS

VSS

VSS

VSS

VSS

107

110

113

116

119

170

173

176

179

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

151

2

182

183

186

VDD

VDD

VDD

VSS

VSS

VSS

154

157

160

3

4

9

10

122

123

128

129

12

13

18

19

131

132

137

138

21

22

27

28

140

141

146

147

30

31

36

37

149

150

155

156

81

82

87

88

200

201

206

207

90

91

96

97

209

210

215

216

99

100

105

106

218

219

224

225

108

109

114

115

227

228

233

234

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

80

83

86

89

92

95

98

101

104

5VDIMM

R284

R284

13KR1%0402

13KR1%0402

DIMM1

DIMM1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3

4

8

VCC_DDR

VDD51VDD

VSS

VSS

107

110

U17

U17

GND

SDA

OUT1

18KR1%0402

18KR1%0402

54

113

5VDIMM

VDD57VDD60VDD62VDD65VDD66VDD69VDD72VDD75VDD78VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

116

119

121

124

127

130

1

7

OUT2

VCC

6

OUT3

5

SCL

BUS_SEL

2

170

173

176

179

VDD

VDD

DDR3

DDR3

VSS

VSS

VSS

VSS

VSS

VSS

133

136

139

142

145

148

151

VREF_CA_B

SMBCLK

UP6262AMA8_SOT23-8-RH

UP6262AMA8_SOT23-8-RH

MEM_MA_DATA[63..0]7

D D

VCC3

C55 C0.1u16Y0402C55 C0.1u16Y0402

Place close to DIMM1

VCC_DDR

C C

C197 C2.2u6.3YC197 C2.2u6.3Y

C181 C220p10XC181 C220p10X

C164 C2.2u6.3YC164 C2.2u6.3Y

C184 C2.2u6.3YC184 C2.2u6.3Y

Place close to DIMM1 with DIMM2

VCC_DDR

C144 C1u6.3Y0402-RHC144 C1u6.3Y0402-RH

Place close to DIMM2

VCC_DDR

C186 C1u6.3Y0402-RHC186 C1u6.3Y0402-RH

C157 C1u6.3Y0402-RHC157 C1u6.3Y0402-RH

MEM_MA_DATA[63..0]

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

UPI VOLTAGE CONSOLE

B B

VREF_CA_A

VREF_CA_A

C146

C146

C0.1u16Y0402

C0.1u16Y0402

UPI VOLTAGE CONSOLE

VREF_DQ_A

VREF_DQ_A

C266

C266

C0.1u16Y0402

C0.1u16Y0402

R280 1KR1%0402R280 1KR1%0402

R279

R279

1KR1%0402

1KR1%0402

R360 1KR1%0402R360 1KR1%0402

R356

R356

1KR1%0402

1KR1%0402

VCC_DDR

VCC_DDR

C271

C271

X_C2.2u6.3Y

X_C2.2u6.3Y

UPI VOLTAGE CONSOLE(2)

2.083325V

0x66:RH=18K,RL=13K

A A

VREF_CA_A

SMBDATA

VREF_CA_A

R283

R283

SMBDATA12,15,19,20,22,23,28,32,36,40

5

VCC3

182

VDD

VDD

VSS

VSS

154

4

236

183

186

189

191

194

197

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

157

160

163

166

199

202

205

208

VREF_CA_B

SMBCLK 12,15,19,20,22,23,28,32,36,40

VDDSPD

VSS

VTT_DDR

120

VSS

211

214

167

240

53

68

48

187

198

79

VTT

VTT

RSVD

FREE1

FREE249FREE3

NC/TEST4

NC/PAR_IN

NC/ERR_OUT

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK1#(NU)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

217

220

223

226

229

232

235

239

SMBCLK_DDR11

SMBDATA_DDR11

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

181

FREE4

A1

MEM_MA_ADD2

61

A2

MEM_MA_ADD3

180

A3

MEM_MA_ADD4

59

A4

MEM_MA_ADD5

58

A5

MEM_MA_ADD6

178

A6

MEM_MA_ADD7

56

A7

MEM_MA_ADD8

177

A8

MEM_MA_ADD9

175

A9

MEM_MA_ADD10

70

A10/AP

MEM_MA_ADD11

55

A11

MEM_MA_ADD12

174

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

172

A14

MEM_MA_ADD15 MEM_MA_ADD15

171

A15

39

CB0

40

CB1

45

CB2

46

CB3

158

CB4

159

CB5

164

CB6

165

CB7

MEM_MA_DQS_H0

7

DQS0

MEM_MA_DQS_L0

6

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

RESET#

CK1(NU)

VREFDQ

VREFCA

MEC1

MEC1

MEM_MA_DQS_H1

16

DQS1

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

25

DQS2

MEM_MA_DQS_L2

24

MEM_MA_DQS_H3

34

DQS3

MEM_MA_DQS_L3

33

MEM_MA_DQS_H4

85

DQS4

MEM_MA_DQS_L4

84

MEM_MA_DQS_H5

94

DQS5

MEM_MA_DQS_L5

93

MEM_MA_DQS_H6

103

DQS6

MEM_MA_DQS_L6

102

MEM_MA_DQS_H7

112

DQS7

MEM_MA_DQS_L7

111

43

DQS8

42

MEM_MA_DM0

125

126

MEM_MA_DM1

134

135

MEM_MA_DM2

143

144

MEM_MA_DM3

152

153

MEM_MA_DM4

203

204

MEM_MA_DM5

212

213

MEM_MA_DM6

221

222

MEM_MA_DM7

230

231

161

162

MEM_MA_ODT0

195

ODT0

MEM_MA_ODT1

77

ODT1

MEM_MA_CKE0

50

CKE0

MEM_MA_CKE1

169

CKE1

MEM_MA_CS_L0

193

CS0#

MEM_MA_CS_L1

76

CS1#

MEM_MA_BANK0

71

BA0

MEM_MA_BANK1

190

BA1

MEM_MA_BANK2

52

BA2

MEM_MA_WE_L

73

WE#

MEM_MA_RAS_L

192

RAS#

MEM_MA_CAS_L

74

CAS#

168

MEM_MA_CLK_H0

184

CK0

MEM_MA_CLK_L0

185

CK0#

MEM_MA_CLK_H1

63

MEM_MA_CLK_L1

64

VREF_DQ_A

1

VREF_CA_A

67

SMBCLK_DDR

118

SCL

SMBDATA_DDR

238

SDA

237

SA1

117

SA0

MEC2

MEC3

DDRIII-240P_BLACK-RH-8

DDRIII-240P_BLACK-RH-8

DIMM1(CHANNEL-A)

MEC2

MEC3

ADDRESS = 0:0 [SA1:SA0]

SMBCLK_DDR

SMBDATA_DDR

C135

C135

C0.1u16Y0402

C0.1u16Y0402

R117 33R0402R117 33R0402

R126 33R0402R126 33R0402

MEM_MA_ADD[15..0] 7

MEM_MA_DQS_H0 7

MEM_MA_DQS_L0 7

MEM_MA_DQS_H1 7

MEM_MA_DQS_L1 7

MEM_MA_DQS_H2 7

MEM_MA_DQS_L2 7

MEM_MA_DQS_H3 7

MEM_MA_DQS_L3 7

MEM_MA_DQS_H4 7

MEM_MA_DQS_L4 7

MEM_MA_DQS_H5 7

MEM_MA_DQS_L5 7

MEM_MA_DQS_H6 7

MEM_MA_DQS_L6 7

MEM_MA_DQS_H7 7

MEM_MA_DQS_L7 7

MEM_MA_DM0 7

MEM_MA_DM1 7

MEM_MA_DM2 7

MEM_MA_DM3 7

MEM_MA_DM4 7

MEM_MA_DM5 7

MEM_MA_DM6 7

MEM_MA_DM7 7

MEM_MA_ODT0 7

MEM_MA_ODT1 7

MEM_MA_CKE0 7

MEM_MA_CKE1 7