Page 1

5

CONTENT SHEET

4

3

2

1

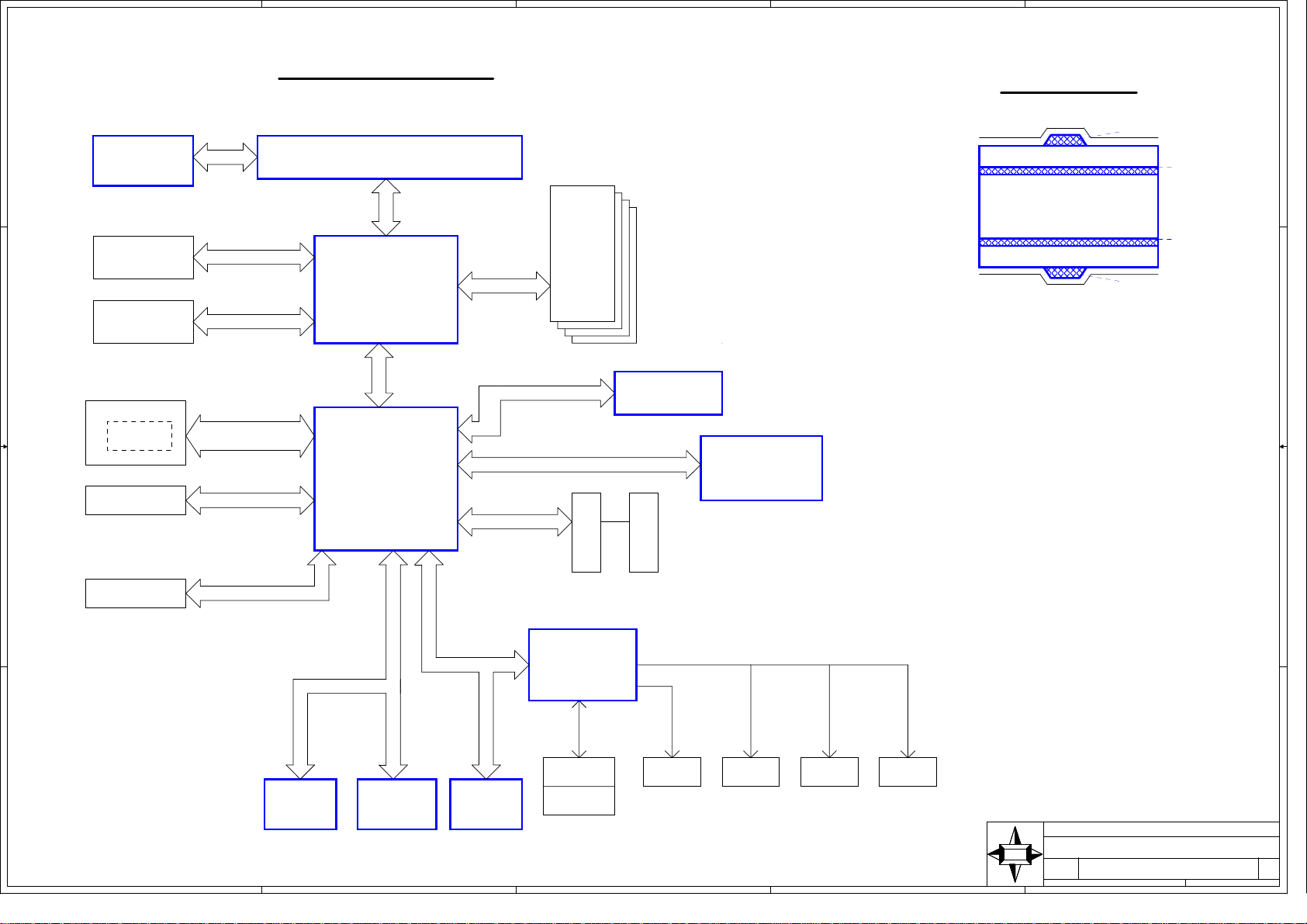

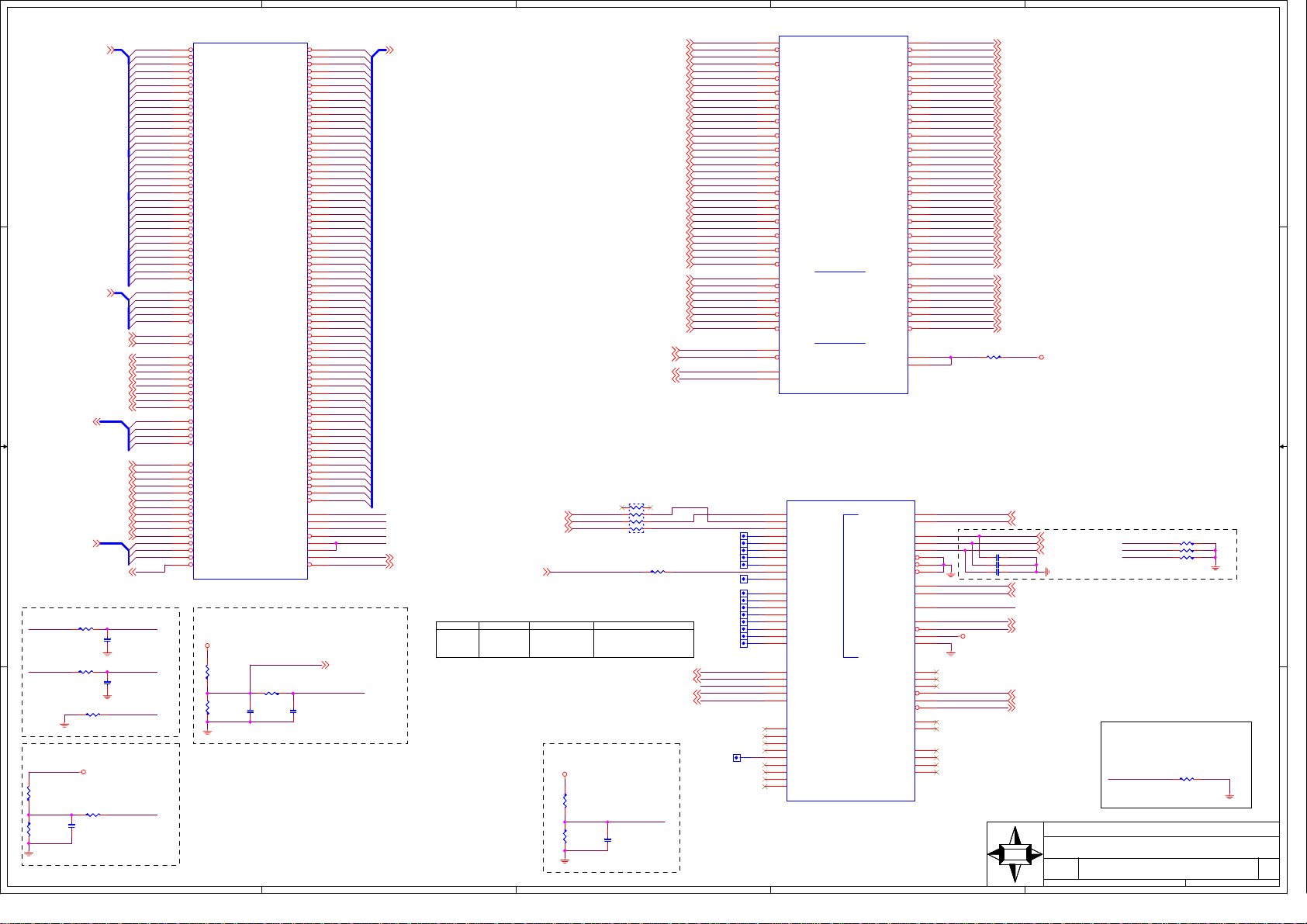

Cover Sheet, Block diagram

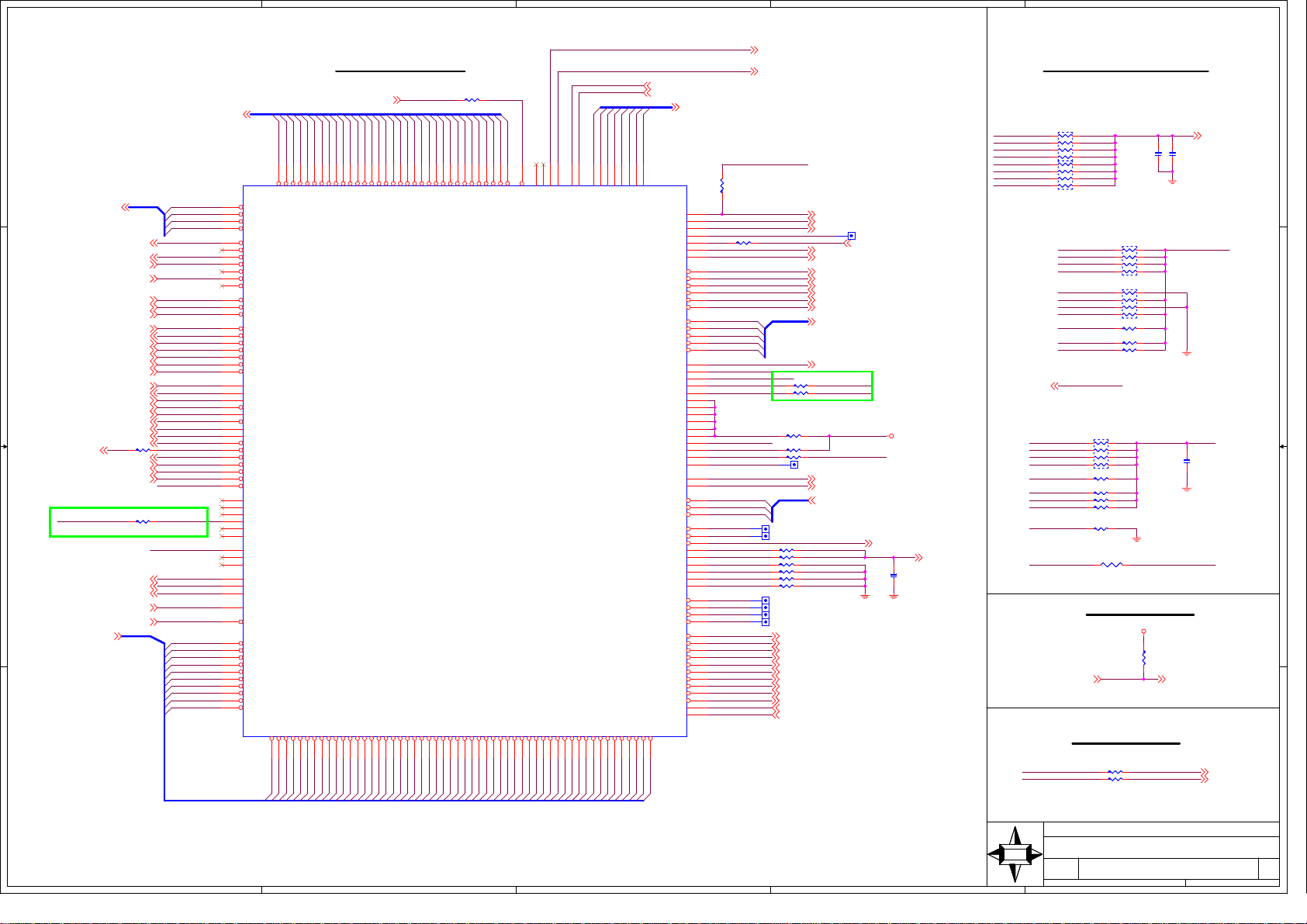

Intel LGA775 CPU - Signals/ Power/ GND

D D

Intel Bearlake - FSB, PCIE, DMI, VGA, MSIC

Intel Bearlake - Memory DDR2

Intel Bearlake - Power / GND

ICH9 - PCI, USB, DMI, TPM

ICH9 - Host, DMI, SATA, Audio, SPI, RTC, MSIC

ICH9 - Power, GND

DDR2 Chanel-A / Chanel-B

Clock Gen ICS9LPR906

C C

Super I/O Fintek F71882

Onboard VGA Port

SATA / FAN Control

LAN INTEL NINEVEH

Audio Codec ALC888S 20

PCIE Slot x16, x1

1-2

3-5

6

7

8-9

10

11

12

13-14

15

16

17

18

19

21

MS-7559

CPU:

System Chipset:

On Board Device:

Main Memory:

Intel Pentium 4, Pentium D, Conroe, Conroe-L, Celeron-D, Core2 Duo,

Wolfdale, Kentsfield and Yorkfield processors in LGA775 Package.

Intel Bearlake - Q35 North Bridge

Intel ICH9 (DO South Bridge)

CLOCK Gen ICS 9LPRS906

LPC Super I/O -- Fintek F71882F

LPC TPM -- SLB9635

LAN -- INTEL Nineveh

HD Audio Codec -- ALC888S

Dual-channel DDR-II * 4

uATX

Version: 0A

PCI Slot 1 & 2

USB Connectors

B B

System Power/ACPI Controller UPI

DDR2 / NB-Core Switching Power /AMT

VRD 11 - ISL6312 (3 Phases)

ATX Power-Con. / F_Panel

Manual & Option Parts

Power Delivery

Reset & PWROK map

A A

GPIO Setting & PCI Routing

Revision History

5

22

23

24

25

26

Expansion Slots:

PCI EXPRESS X16 SLOT *1

PCI EXPRESS X1 SLOT *1

PCI SLOT * 2

PWM:

Intersil ISL6312 (3 Phases)

27

28

29

Configration and BOM match up

Option

Bearlake-Q35/ICH9DO

STD

Function Orcad Configure

CFG-7559-vPRO

BOM

30

31

32

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7559

MS-7559

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, June 25, 2008

Date:

Wednesday, June 25, 2008

Date:

4

3

2

Wednesday, June 25, 2008

MS-7559

COVER SHEET

COVER SHEET

COVER SHEET

1

132

132

132

Sheet of

Sheet of

Sheet of

0A

0A

0A

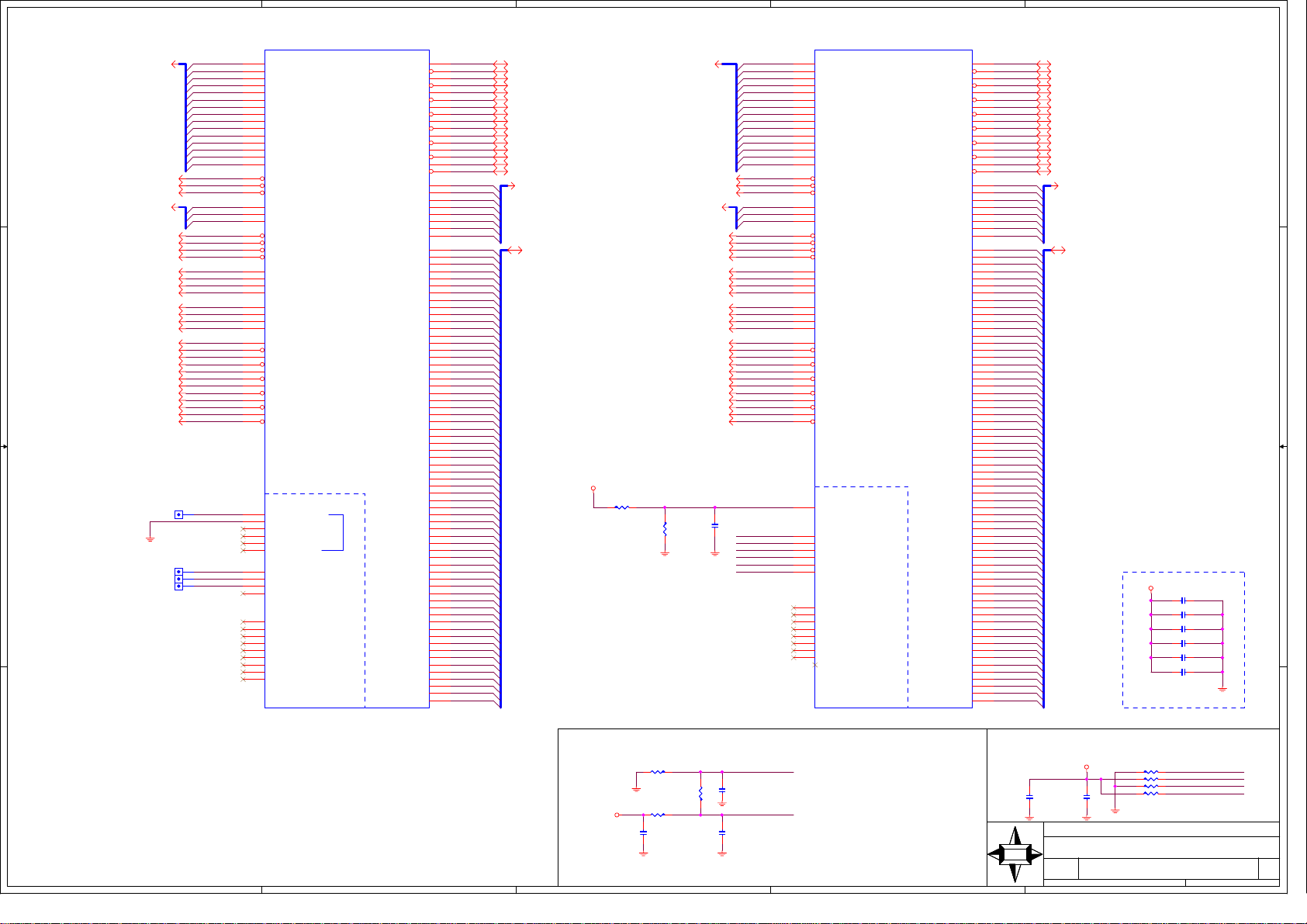

Page 2

5

4

3

2

1

Block Diagram

Board Stack-up

(1080 Prepreg Considerations)

D D

VRD 11

ISL6312

3-Phase PWM

Intel LGA775 Processor

FSB 800/1066/1333

FSB

DDR3 800/1066

Solder Mask

PREPREG 2.7mils

CORE 50mils

1.9mils Cu plus plating

1 oz. (1.2mils)

Cu Power

Plane

PCI_E X16

Connector

Analog

C C

Video Out

PCI_E x1

PCI EXPRESS X16

RGB

PCI_E x1

Bearlake

Q35

GMCH

DMI

DDRII

HD Audio Link

GLCI/LCI

ICH9DO

SATA-II 1~6

B B

USB Port 1~12

SATA2

PCI

USB2.0

LPC Bus

4 DDR II

DIMM

Modules

PCI Slot 1

HD Audio Codec

ALC888S

PCI Slot 2

LAN

INTEL Nineveh

Solder Mask

PREPREG 2.7mils

1.9mils Cu plus plating

Single End 50ohm Top/Bottom : 4mils

USB2.0 - 90ohm : 15/4.5/7.5/4.5/15

SATA - 95ohm : 15/4/8/4/15

LAN - 100ohm : 15/4/8/4/15

PCIE - 95ohm : 15/4/8/4/15

1 oz. (1.2mils)

Cu GND

Plane

LPC SIO

Fintek

SPI

F71882

A A

SPI

Flash ROM

5

SPI

Debug Port

4

TPM

SLB9635

Keyboard

Mouse

Floopy

3

Serial 1

Serial 2

LPT

2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7559

MS-7559

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, June 25, 2008

Date:

Wednesday, June 25, 2008

Date:

Wednesday, June 25, 2008

MS-7559

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

1

232

232

232

Sheet of

Sheet of

Sheet of

0A

0A

0A

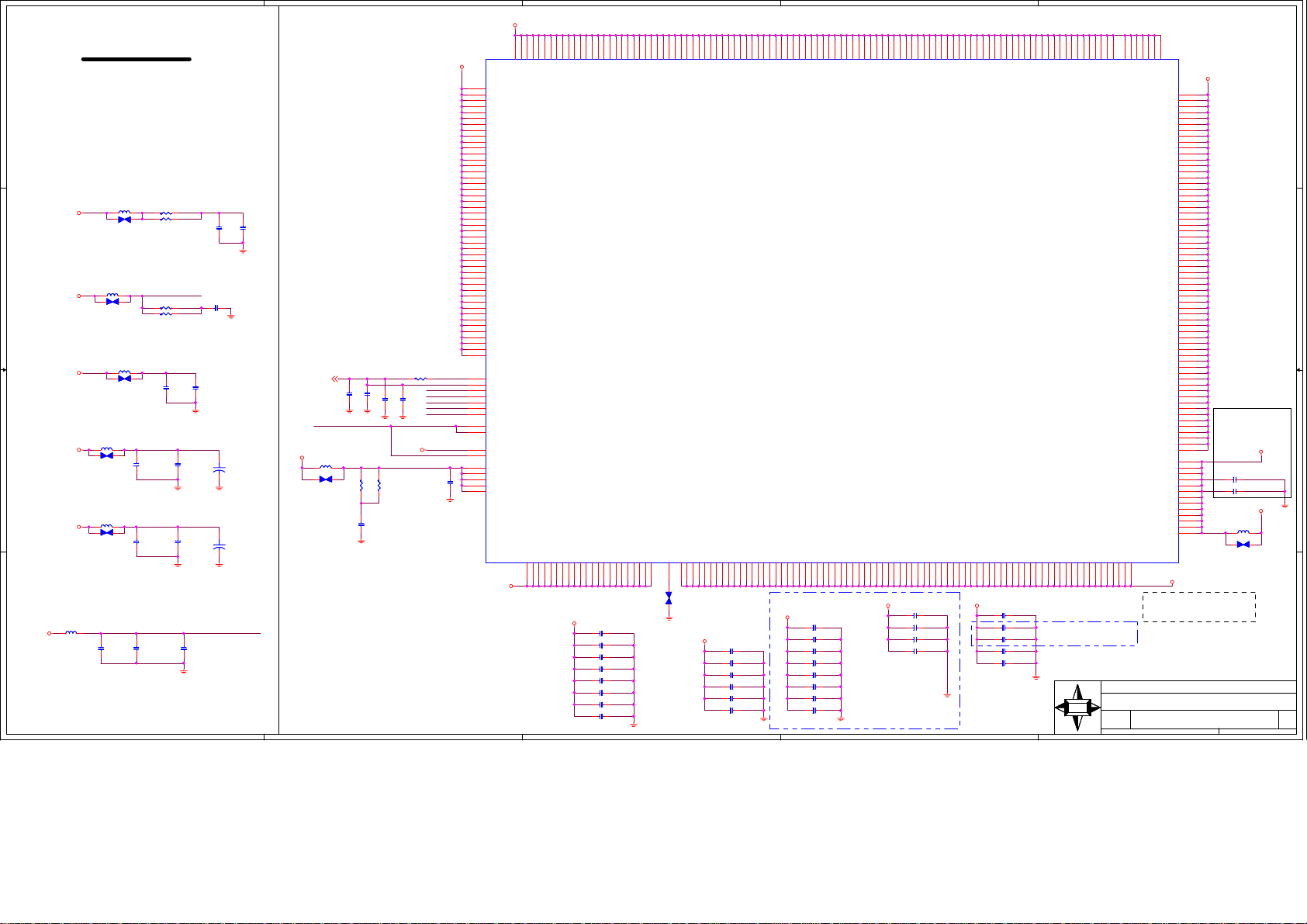

Page 3

5

4

3

2

1

VCC_SENSE

CPU SIGNAL BLOCK

Silk screen show "PROCESSOR"

H_A#18

H_A#17

H_A#16

AB6

D36#

D35#

D34#

E16

E15

G18

H_D#33

H_D#34

H_D#35

R628 X_0R/2R628 X_0R/2

H_A#10

H_A#15

H_A#11

H_A#12

H_A#13

H_A#14

U6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D33#

D32#

D31#

D30#

D29#

D28#

F15

F14

G16

G15

G14

G13

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_A#8

H_A#6

H_A#7

H_A#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D27#

D26#

D25#

D24#

F12

F11

E13

D13

H_D#23

H_D#24

H_D#25

H_D#26

H_A#5

H_A#4

D23#

D22#

E10

D10

H_D#21

H_D#22

H_A#3

L5

AC2

DBR#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

H_D#17

H_D#18

H_D#19

H_D#20

AN3

VCC_SENSE

H_D#16

AN4

VSS_SENSE

D11

H_D#15

VID2

VID3

VID4

VID5

VID7

VID6

AN6

AM7

AN5

AJ3

AK3

AM5

AL4

AK4

AL6

AM3

VID6

VID5

VID4

VID3

RSVD/VID7

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

H_D#6

H_D#7

H_D#8

VID2

FC5/CPU_GTLREF2

RSVD/CPU_GTLREF3

H_D#3

H_D#4

H_D#5

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

VCC_MB_REGULATION

D14#

D13#

D12#D8D11#

D10#

B12

B10

C12

C11

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

FP_RST#5,11,27

H_A#28

H_A#29

H_A#27

H_A#24

H_A#25

H_A#26

H_A#22

H_A#21

H_A#23

H_A#20

H_A#19

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

F21

F20

F18

E22

D22

G21

H_D#45

H_D#44

H_D#46

F17

E21

E19

E18

G17

H_D#43

H_D#42

H_D#41

H_D#40

H_D#39

H_D#38

H_D#37

H_D#36

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

PECI

VTIN1

GNDHM

H_TRMTRIP#

SLOTOCC#

H_PROCHOT#

H_IGNNE#

ICH_H_SMI#

H_A20M#

H_TESTHI13

BPM#1

BOOTSELECT

H_PWRGD

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

H_A#[3..35]6

H_A#31

H_A#30

H_A#32

H_A#35

H_A#33

H_A#34

AJ6

AJ5

AH5

AH4

AG5

AG4

A35#

A34#

A33#

A32#

A31#

D53#

D52#

D51#

D50#

D49#

D48#

B15

A14

C14

C15

D17

D20

G22

H_D#53

H_D#52

H_D#51

H_D#50

H_D#49

H_D#48

H_D#47

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

G5

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

XU1A

XU1A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

PECI

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D D

H_DBI#[0..3]6

H_IERR#4

H_FERR#11

H_STPCLK#11

H_INIT#11

H_DBSY#6

H_DRDY#6

H_TRDY#6

H_ADS#6

H_D#[0..63]6

H_DEFER#6

H_TDI5

H_TMS5

H_TRST#5

H_TCK5

H_TRMTRIP#11

R629 0R/2R629 0R/2

H_PROCHOT#4

H_IGNNE#11

ICH_H_SMI#11

R440 0R/2R440 0R/2

Kentsfield

CPU_BSEL06,15

CPU_BSEL16,15

CPU_BSEL26,15

H_PWRGD11

H_CPURST#4,5,6

H_LOCK#6

H_BNR#6

H_HIT#6

H_HITM#6

H_BPRI#6

H_TDO5

PECI11,16

VTIN116

GNDHM16

H_A20M#11

C C

H_SKTOCC#11

H_BPM#1

B B

A A

VSS_SENSE

CK_ITP_DN 5

CK_ITP_DP 5

VID[0..7] 26

VID1

VID0

AL5

AM2

VID1

VID0

VID_SELECT

GTLREF_SEL

H_D#1

H_D#2

AN7

H1

GTLREF0

H2

GTLREF1

H29

E24

GTLREF2

F2

G10

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

TESTHI12

P1

TESTHI11

H5

TESTHI10

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

FORCEPH

G6

RSVD#G6

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

T2

COMP5

J2

COMP4

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

ADSTB1#

R6

ADSTB0#

C17

DSTBP3#

G19

DSTBP2#

E12

DSTBP1#

B9

DSTBP0#

A16

DSTBN3#

G20

DSTBN2#

G12

DSTBN1#

C8

DSTBN0#

L1

LINT1/NMI

K1

LINT0/INTR

B4

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

H_D#0

VTT_OUT_RIGHT

R89

R89

680R/2

680R/2

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

R422 0R/2R422 0R/2

CPU_GTLREF2

CPU_GTLREF3

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

CK_H_CPU_DN

CK_H_CPU_DP

H_RS#2

H_RS#1

H_RS#0

TEST-U3

TEST-U2

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TEST-J17

TEST-H16

TEST-H15

TEST-J16

VCC_SENSE 26

VSS_SENSE 26

CPU_MCH_GTLREF

R419 0R/2R419 0R/2

R420 0R/2R420 0R/2

R190 51R/2R190 51R/2

R192 51R/2R192 51R/2

R214 130R1%/2R214 130R1%/2

X_TPX_TP

X_TPX_TP

X_TPX_TP

R143 X_49.9R1%/2R143 X_49.9R1%/2

R157 X_49.9R1%/2R157 X_49.9R1%/2

R231 49.9R1%/2R231 49.9R1%/2

R172 49.9R1%/2R172 49.9R1%/2

R146 49.9R1%/2R146 49.9R1%/2

R200 49.9R1%/2R200 49.9R1%/2

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 11

H_INTR 11

VRD_VIDSEL 26

CPU_GTLREF0 4

CPU_GTLREF1 4

CPU_MCH_GTLREF 6

CPU_GTLREF2 4

CPU_GTLREF3 4

H_BPM#5 5

H_BPM#4 5

H_BPM#3 5

H_BPM#2 5

H_BPM#1 5

H_BPM#0 5

H_REQ#[0..4] 6

H_TESTHI12 5

Kentsfield

H_BPM#2

H_BPM#3

V_FSB_VTTH_TESTHI2_7

VTT_OUT_RIGHT

CK_H_CPU_DN 15

CK_H_CPU_DP 15

H_RS#[0..2] 6

X_TPX_TP

V_FSB_VTT

H_BR#0 4,6

C86

C86

C0.1U16Y2

C0.1U16Y2

VTT_OUT_LEFT 4,5

PULL HIGHT PULL DOWN

RN5 8P4R-680R0402-RHRN5 8P4R-680R0402-RH

VID2

VID0

VID5

VID4

VID7

VID3

VID6

VID1

1

2

3

4

5

6

7

8

C0.1U16Y2

1

3

5

7

RN4 8P4R-680R0402-RHRN4 8P4R-680R0402-RH

H_BPM#1

H_BPM#0

H_BPM#5

H_BPM#3

H_TCK

H_TDO

H_TRST#

H_TDI

H_TMS

H_BPM#4

H_BPM#2

SLOTOCC#16

H_TESTHI12

H_TESTHI11

H_TESTHI9

H_TESTHI10

BPM#1

H_TESTHI8

H_TESTHI1

H_TESTHI13

BOOTSELECT

H_PWRGD VTT_OUT_LEFT

C0.1U16Y2

2

4

6

8

1

3

5

7

RN7 8P4R-51R/2RN7 8P4R-51R/2

1

3

5

7

RN8 8P4R-62R/2RN8 8P4R-62R/2

R170 62R/2R170 62R/2

R175 51R/2R175 51R/2

R222 51R/2R222 51R/2

SLOTOCC#

RN10 8P4R-51R/2RN10 8P4R-51R/2

1

2

3

4

5

6

7

8

R169 51R/2R169 51R/2

R165 51R/2R165 51R/2

R148 51R/2R148 51R/2

R156 51R/2R156 51R/2

R208 51R/2R208 51R/2

R417 X_100R/2R417 X_100R/2

Thermal TRIP

THRM#11,15,16

Reserved for ITP

CK_H_CPU_DN

R392 X_0R/2R392 X_0R/2

R395 X_0R/2R395 X_0R/2

VTT_OUT_RIGHT

C71

C71

VTT_OUT_RIGHT

2

4

6

8

2

4

6

8

VTT_OUT_LEFT

VCC3

R134

R134

10KR/2

10KR/2

ICH_THERM# 11,15,16

CK_ITP_DPCK_H_CPU_DP

CK_ITP_DN

VTT_OUT_RIGHT 4,5,11

C85

C85

C0.1U16Y2

C0.1U16Y2

C89

C89

C0.1U16Y2

C0.1U16Y2

CK_ITP_DP 5

CK_ITP_DN 5

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7559

MS-7559

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

Date:

5

4

3

2

Wednesday, July 09, 2008

MS-7559

LGA775 - Signal

LGA775 - Signal

LGA775 - Signal

1

332

332

332

Sheet of

Sheet of

Sheet of

0A

0A

0A

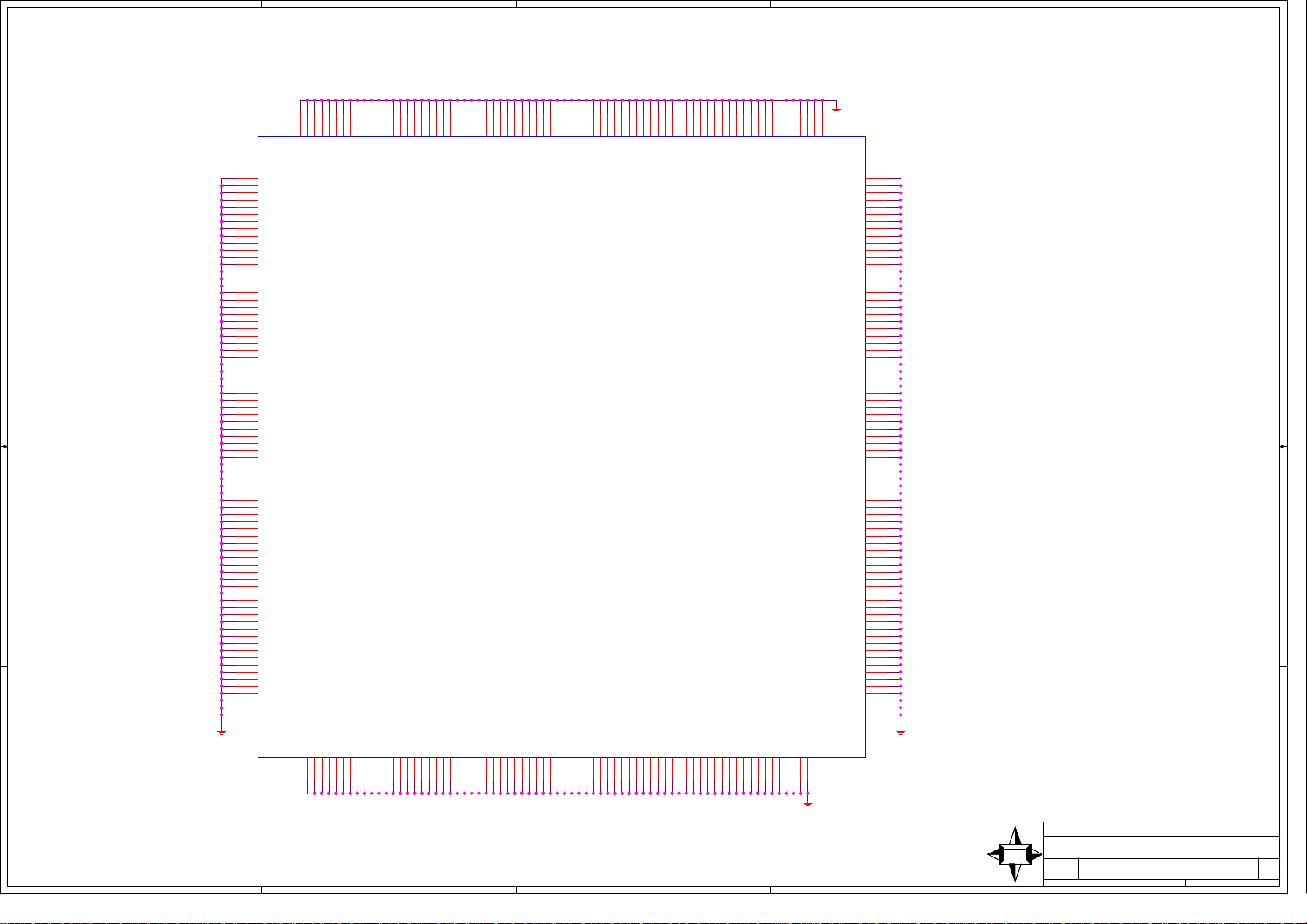

Page 4

5

VCCP

AG9

AF22

AF21

AG11

AF9

AF8

XU1B

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

XU1B

VCCP

VCC#AF19

VCC#AF18

VCC#AF15

VCC#AF14

VCC#AF12

VCC#AF11

VCC#AE9

VCC#AE23

VCC#AE22

VCC#AE21

VCC#AE19

VCC#AE18

VCC#AE15

VCC#AE14

VCC#AE12

VCC#AE11

VCC#AD8

VCC#AD30

VCC#AD29

VCC#AD28

VCC#AD27

VCC#AD26

VCC#AD25

VCC#AD24

VCC#AD23

VCC#AC8

VCC#AC30

VCC#AC29

VCC#AC28

VCC#AC27

VCC#AC26

VCC#AC25

VCC#AC24

VCC#AC23

VCC#AB8

VCC#AA8

VCC#AF9

VCC#AF8

VCC#AF22

VCC#AF21

VCC#AG11

VCC#Y27

VCC#Y28

VCC#Y29

VCC#Y30

VCC#Y8

Y8

Y27

Y28

Y29

Y30

D D

C C

VCCP

AG22

AG21

AG19

AG18

AG15

AG14

AG12

VCC#AG22

VCC#AG21

VCC#AG19

VCC#AG18

VCC#AG15

VCC#AG14

VCC#AG12

VCC#W29

VCC#W30

VCC#W8W8VCC#Y23

VCC#Y24

VCC#Y25

VCC#Y26

Y23

Y24

Y25

Y26

W29

W30

AG8

AH11

AG30

AG29

AG28

AG27

AG26

AG25

VCC#AG9

VCC#AG8

VCC#AH11

VCC#AG30

VCC#AG29

VCC#AG28

VCC#AG27

VCC#AG26

VCC#AG25

VCC#U30

VCC#U8U8VCC#V8V8VCC#W23

VCC#W24

VCC#W25

VCC#W26

VCC#W27

VCC#W28

U30

W23

W24

W25

W26

W27

W28

4

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AH12

VCC#AH18

VCC#AH15

VCC#AH14

VCC#AH12

VCC#U26

VCC#U27

VCC#U28

VCC#U29

U26

U27

U28

U29

AH28

AH29

AH30

VCC#AH8

VCC#AH9

VCC#AJ11

VCC#AH27

VCC#AH26

VCC#AH25

VCC#AH22

VCC#AH21

VCC#AH19

VCC#T29

VCC#T30

VCC#T8T8VCC#U23

VCC#U24

VCC#U25

T29

T30

U23

U24

U25

VCC#AJ12

VCC#AH28

VCC#AH29

VCC#AH30

VCC#T24

VCC#T25

VCC#T26

VCC#T27

VCC#T28

T23

T24

T25

T26

T27

T28

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AJ26

AJ8

AJ9

VCC#AJ8

VCC#AJ14

VCC#AJ15

VCC#AJ18

VCC#N30

VCC#N8N8VCC#P8P8VCC#R8R8VCC#T23

N30

VCC#AJ9

VCC#AJ19

VCC#AJ21

VCC#AJ22

VCC#AJ25

VCC#AJ26

VCC#AK11

VCC#AK12

VCC#M30

VCC#M8M8VCC#N23

VCC#N24

VCC#N25

VCC#N26

VCC#N27

VCC#N28

VCC#N29

N23

N24

N25

N26

N27

N28

N29

M30

AK25

VCC#AK14

VCC#AK15

VCC#AK18

VCC#AK19

VCC#AK21

VCC#AK22

VCC#AK25

VCC#M24

VCC#M25

VCC#M26

VCC#M27

VCC#M28

VCC#M29

M23

M24

M25

M26

M27

M28

M29

3

AM8

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

VCC#AK8

VCC#AK9

VCC#AL11

VCC#AL12

VCC#AL14

VCC#AL15

VCC#AK26

VCC#AL18

VCC#K25

VCC#K26

VCC#K27

VCC#K28

VCC#K29

VCC#K30

VCC#K8K8VCC#L8L8VCC#M23

K24

K25

K26

K27

K28

K29

K30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AL21

AL22

AL25

AL26

AL29

AL30

VCC#AL8

VCC#AL19

VCC#AL21

VCC#K24

K23

VCC#AL9

VCC#AL22

VCC#AL25

VCC#AL26

VCC#AL29

VCC#AL30

VCC#J26

VCC#J27

VCC#J28

VCC#J29

VCC#J30

VCC#J8J8VCC#J9J9VCC#K23

J26

J27

J28

J29

J30

AM21

VCC#AM11

VCC#AM12

VCC#AM14

VCC#AM15

VCC#AM18

VCC#AM19

VCC#AM21

VCC#J19

VCC#J20

VCC#J21

VCC#J22

VCC#J23

VCC#J24

VCC#J25

J19

J20

J21

J22

J23

J24

J25

AM9

AM22

AM25

AM26

AM29

AM30

AN11

AN12

AN14

AN15

AN18

VCC#AM8

VCC#AM9

VCC#AN11

VCC#AN12

VCC#AN14

VCC#AM22

VCC#AM25

VCC#AM26

VCC#AM29

VCC#J13

VCC#J14

VCC#J15

VCC#J18

J13

J14

J15

J18

VCC#AN15

VCC#AM30

VTT_OUT_RIGHT

VCC#AN29

VCC#AN30

VCC#AN8

VCC#AN9

VCC#J10

VCC#J11

VCC#J12

J10

J11

J12

AN8

AN9

AN26

AN29

AN30

AN19

AN21

AN22

VCCA

VSSA

VCC#AN18

VCC#AN19

VCC#AN21

VCC#AN22

VCCPLL

VCC-IOPLL

VTT#A25

VTT#A26

VTT#A27

VTT#A28

VTT#A29

VTT#A30

VTT#B25

VTT#B26

VTT#B27

VTT#B28

VTT#B29

VTT#B30

VTT#C25

VTT#C26

VTT#C27

VTT#C28

VTT#C29

VTT#C30

VTT#D25

VTT#D26

VTT#D27

VTT#D28

VTT#D29

VTT#D30

VTTPWRGD

VTT_OUT_LEFT

VTT_SEL

RSVD#F29

VCC#AN25

VCC#AN26

1122334

AN25

2

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL

F27

F29

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

4

Silk screen show "PROCESSOR"

C10U10Y5

C10U10Y5

H_VCCPLL 8

V_FSB_VTT

C164

C164

C156

C156

C10U10Y5

C10U10Y5

CAPS FOR FSB GENERIC

VTT_OUT_RIGHT 3,5,11

VTT_OUT_LEFT 3,5

VTT_SEL 24

V_FSB_VTT

C196

C196

C10u16X51206-RH

C10u16X51206-RH

1

*GTLREF VOLTAGE SHOULD BE

0.67 * VTT = 0.8V (At VTT=1.2V)

VTT_OUT_RIGHT

B B

VTT_OUT_RIGHT

R152 115R1%/2R152 115R1%/2

R142 115R1%/2R142 115R1%/2

R154 10R/2R154 10R/2 R167 10R/2R167 10R/2

R158

R158

C96

C96

200R1%/2

200R1%/2

C1U16Y3

C1U16Y3

R150 10R/2R150 10R/2

R145

R145

C92

C92

200R1%/2

200R1%/2

C1U16Y3

C1U16Y3

C101

C101

C220P50N2

C220P50N2

C93

C93

C220P50N2

C220P50N2

CPU_GTLREF0 3

CPU_GTLREF1 3

VTT_OUT_LEFT

V_FSB_VTT

R164 115R1%/2R164 115R1%/2

R123 115R1%/2R123 115R1%/2

R163

R163

200R1%/2

200R1%/2

R129

R129

200R1%/2

200R1%/2

C104

C104

C1U16Y3

C1U16Y3

R171 10R/2R171 10R/2

C81

C81

C1U16Y3

C1U16Y3

C110

C110

C220P50N2

C220P50N2

C116

C116

C220P50N2

C220P50N2

CPU_GTLREF2 3

CPU_GTLREF3 3

VTT_PWRGOOD

PLACE AT CPU END OF ROUTE

A A

VTT_OUT_RIGHT3,5,11

VTT_OUT_LEFT3,5

VTT_OUT_RIGHT

VTT_OUT_LEFT

5

R107 130R1%/2R107 130R1%/2

R139 62R/2R139 62R/2

R82 62R/2R82 62R/2

R168 62R/2R168 62R/2

H_PROCHOT#

H_IERR#

H_CPURST#

H_BR#0

H_PROCHOT# 3

H_IERR# 3

H_CPURST# 3,5,6

H_BR#0 3,6

4

VID_GD#24,26

3

VTT_OUT_RIGHT

R110

R110

X_1KR/2

X_1KR/2

VRM_PGD11,26

*PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

*TRACE WIDTH TO CAPS MUST BE NO SMALLER THAN 12MILS

V_FSB_VTT V_1P5_ICH

B

L7 X_L10U_100mA_0805L7 X_L10U_100mA_0805

X_COPPER

X_COPPER

R122

R122

X_680R/2

X_680R/2

CE

Q19

Q19

X_2N3904

X_2N3904

R631 0R/2R631 0R/2

21

CP2

CP2

1.2V VTT_PWRGOOD

VTT_PWG

2

C168

C168

C1U16Y3

C1U16Y3

C163

C163

C10U10Y5

C10U10Y5

H_VCCA

H_VSSA

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

MSI

MSI

MSI

CP8

CP8

H_VCCPLL

X_COPPER

X_COPPER

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7559

MS-7559

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Tuesday, July 08, 2008

Date:

Tuesday, July 08, 2008

Date:

Tuesday, July 08, 2008

MS-7559

LGA775 - Power

LGA775 - Power

LGA775 - Power

1

C184

C184

C10000P25X2

C10000P25X2

432

432

432

Sheet of

Sheet of

Sheet of

C189

C189

C10U10Y5

C10U10Y5

0A

0A

0A

Page 5

XU1C

XU1C

5

V30

V29

V28

V27

W4

Y2

V26

V6

V3

T3

V25

V24

V23

U7

R5

R30

R29

R28

R27

R26

R25

4

L30

L29

L28

L27

L26

L25

L24

P30

P29

P28

P27

P26

R2

R24

R23

P25

P4

M1

P24

P23

N3

L6

L3

L23

H9

K2

K5

J7

3

F7

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

2

1

D D

C C

B B

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AE5

AE7

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF3

AF30

AF6

AF7

A12

A15

A18

A2

A21

A6

A9

AA3

AA6

AA7

AB1

AB7

VSS#A12

VSS#A15

VSS#A18

VSS#A2

VSS#A21

VSS#A6

VSS#A9

VSS#AA23

VSS#AA24

VSS#AA25

VSS#AA26

VSS#AA27

VSS#AA28

VSS#AA29

VSS#AA3

VSS#AA30

VSS#AA6

VSS#AA7

VSS#AB1

VSS#AB23

VSS#AB24

VSS#AB25

VSS#AB26

VSS#AB27

VSS#AB28

VSS#AB29

VSS#AB30

VSS#AB7

VSS#AC3

VSS#AC6

VSS#AC7

VSS#AD4

VSS#AD7

VSS#AE10

VSS#AE13

VSS#AE16

VSS#AE17

VSS#AE2

VSS#AE20

VSS#AE24

VSS#AE25

VSS#AE26

VSS#AE27

VSS#AE28

VSS#AE29

VSS#AE30

VSS#AE5

VSS#AE7

VSS#AF10

VSS#AF13

VSS#AF16

VSS#AF17

VSS#AF20

VSS#AF23

VSS#AF24

VSS#AF25

VSS#AF26

VSS#AF27

VSS#AF28

VSS#AF29

VSS#AF3

VSS#AF30

VSS#AF6

VSS#AF7

VSS#Y7Y7VSS#Y5Y5VSS#Y2

VSS#AG10

AG10

VSS#V7V7VSS#V6

VSS#V3

VSS#W7W7VSS#W4

VSS#V30

VSS#V29

VSS#V28

VSS#AG13

VSS#AG16

VSS#AG17

VSS#AG20

VSS#AG23

VSS#AG24

VSS#AG7

VSS#AH1

VSS#AH10

AH1

AG7

AG13

AG16

AH10

AG17

AG20

AG23

AG24

VSS#T7T7VSS#T6T6VSS#T3

VSS#U7

VSS#V27

VSS#V26

VSS#V25

VSS#AH13

VSS#AH16

VSS#AH17

AH13

AH16

AH17

VSS#R7R7VSS#R5

VSS#V24

VSS#V23

VSS#AH20

VSS#AH23

AH20

AH23

VSS#R30

VSS#R29

VSS#R28

VSS#AH24

VSS#AH3

VSS#AH6

VSS#AH7

VSS#AJ10

VSS#AJ13

VSS#AJ16

VSS#AJ17

VSS#AJ20

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

AH24

AJ20

VSS#P7P7VSS#P4

VSS#R2

VSS#P30

VSS#P29

VSS#P28

VSS#P27

VSS#P26

VSS#P25

VSS#R27

VSS#R26

VSS#R25

VSS#R24

VSS#R23

VSS#AJ23

VSS#AJ24

VSS#AJ27

VSS#AJ28

VSS#AJ29

VSS#AJ30

VSS#AJ4

VSS#AJ7

AJ4

AJ23

AJ7

AJ24

AJ27

AJ28

AJ29

AJ30

VSS#P24

VSS#AK10

VSS#AK13

VSS#AK16

VSS#AK17

VSS#AK2

VSS#AK20

VSS#AK23

AK2

AK10

AK13

AK16

AK17

AK20

AK23

VSS#L7L7VSS#L6

VSS#N7N7VSS#N6N6VSS#N3

VSS#P23

VSS#AK24

VSS#AK27

VSS#AK28

AK24

AK27

AK28

VSS#L3

VSS#M7M7VSS#M1

VSS#L30

VSS#L29

VSS#L28

VSS#L27

VSS#L26

VSS#L25

VSS#AK29

VSS#AK30

VSS#AK5

VSS#AK7

VSS#AL10

VSS#AL13

VSS#AL16

VSS#AL17

VSS#AL20

VSS#AL23

VSS#AL24

VSS#AL27

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AK29

AK30

AL27

VSS#J4J4VSS#J7

VSS#K2

VSS#K7K7VSS#K5

VSS#L24

VSS#L23

VSS#AL28

VSS#AL7

VSS#AM1

VSS#AM10

VSS#AM13

AL7

AM1

AL28

AM10

AM13

VSS#H3H3VSS#H6H6VSS#H7H7VSS#H8H8VSS#H9

VSS#H25

VSS#H26

VSS#H27

VSS#H28

VSS#AM16

VSS#AM17

VSS#AM20

VSS#AM23

VSS#AM24

VSS#AM27

VSS#AM28

VSS#AM4

VSS#AN1

VSS#AN10

VSS#AN13

AN1

AM4

AN10

AM16

AM17

AM20

AM23

AN13

AM24

AM27

AM28

VSS#H18

VSS#H19

VSS#H20

VSS#H21

VSS#H22

VSS#H23

VSS#H24

VSS#AN16

VSS#AN17

VSS#AN2

VSS#AN20

VSS#AN23

VSS#AN24

VSS#AN27

AN2

AN16

AN17

AN20

AN23

AN24

AN27

VSS#F7

VSS#H10

VSS#H11

VSS#H12

VSS#H13

VSS#H14

VSS#H17

VSS#AN28

AN28

VSS#B1B1VSS#B11

B11

COMP6

COMP7

RSVD/COMP8

RSVD#AE4

RSVD#D1

RSVD#D14

RSVD#E5

RSVD#E6

RSVD#E7

RSVD#E23

RSVD#F23

RSVD

RSVD#J3

RSVD#N4

RSVD#P5

RSVD#AC4

IMPSEL#

MSID1

MSID0

FC28

FC27

FC26

FC23

VSS#F4

VSS#F22

VSS#F19

VSS#F16

VSS#F13

VSS#F10

VSS#E8

VSS#E28

VSS#E27

VSS#E26

VSS#E25

VSS#E20

VSS#E2

VSS#E17

VSS#E14

VSS#E11

VSS#D9

VSS#D6

VSS#D5

VSS#D3

VSS#D24

VSS#D21

VSS#D18

VSS#D15

VSS#D12

VSS#C7

VSS#C4

VSS#C24

VSS#C22

VSS#C19

VSS#C16

VSS#C13

VSS#C10

VSS#B8

VSS#B5

VSS#B14

VSS#B17

VSS#B20

VSS#B24

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

ZIF-SOCKET775-RH-1,ZIF-SOCKET775_TH-2

B14

B17

B20

B24

Silk screen show "PROCESSOR"

Y3

AE3

B13

AE4

D1

D14

E5

E6

E7

E23

F23

AL3

J3

N4

P5

AC4

F6

V1

W1

U1

G1

E29

A24

F4

F22

F19

F16

F13

F10

E8

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

H_COMP6

H_COMP7

H_COMP8

X_TP X_TP

X_TP X_TP

X_TP X_TP

X_TP X_TP

R160 51R/2R160 51R/2

R144 X_51R/2R144 X_51R/2

R141 X_51R/2R141 X_51R/2

X_TP X_TP

X_TP X_TP

R140 X_49.9R1%/2R140 X_49.9R1%/2

R128 X_49.9R1%/2R128 X_49.9R1%/2

R202 24.9R1%/2R202 24.9R1%/2

R423 0R/2R423 0R/2

R147 51R/2R147 51R/2

H_TESTHI12

H_BPM#0

VTT_OUT_RIGHT 3,4,11

H_TESTHI12 3

H_BPM#0 3

VTT_OUT_LEFT 3,4

Kentsfield

JDP_DEBUG

H_BPM#0 H_TDO

H_BPM#03

H_BPM#1 H_TDI

H_BPM#2

H_BPM#23

H_BPM#3

H_BPM#33

H_BPM#4

H_BPM#43

H_BPM#5

H_BPM#53

A A

5

CK_ITP_DP3

CK_ITP_DN3

CK_ITP_DP

CK_ITP_DN

SMBCLK11,13,15,21,24,26

SMBDATA11,13,15,21,24,26

VTT_OUT_RIGHT3,4,11

JDP_DEBUG

9

BPM0*

7

BPM1*

6

BPM2*

4

BPM3*

3

BPM4*

1

BPM5*

16

100M_CLK_DP

18

100M_CLK_DN

13

XDP_H_CLK_DP

15

XDP_H_CLK_DN

22

SCL

24

SDA

14

VTT

28

NC

4

TRST

PWRGOOD

RESET*

DBR*

TESTIN*

GND1

GND2

GND3

GND4

GND5

GND6

GND7

GND8

X_JCPDBG1

X_JCPDBG1

TDO

TMS

TCK

TDI

23

29

H_TMS

31

H_TCK

30

H_TRST#

25

R537 X_1.5KR1%R537 X_1.5KR1%

10

R538 X_1KRR538 X_1KR

19

21

R542 X_62/6R542 X_62/6

12

2

5

8

11

17

20

26

27

H_TDO 3

H_TDI 3H_BPM#13

H_TMS 3

H_TCK 3

H_TRST# 3

FP_RST#

VTT_OUT_RIGHT 3,4,11

H_CPURST# 3,4,6

FP_RST# 3,11,27

VTT_OUT_RIGHT 3,4,11

3

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MS-7559

MS-7559

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

Date:

2

Wednesday, July 09, 2008

MS-7559

LGA775 - GND

LGA775 - GND

LGA775 - GND

1

532

532

532

Sheet of

Sheet of

Sheet of

0A

0A

0A

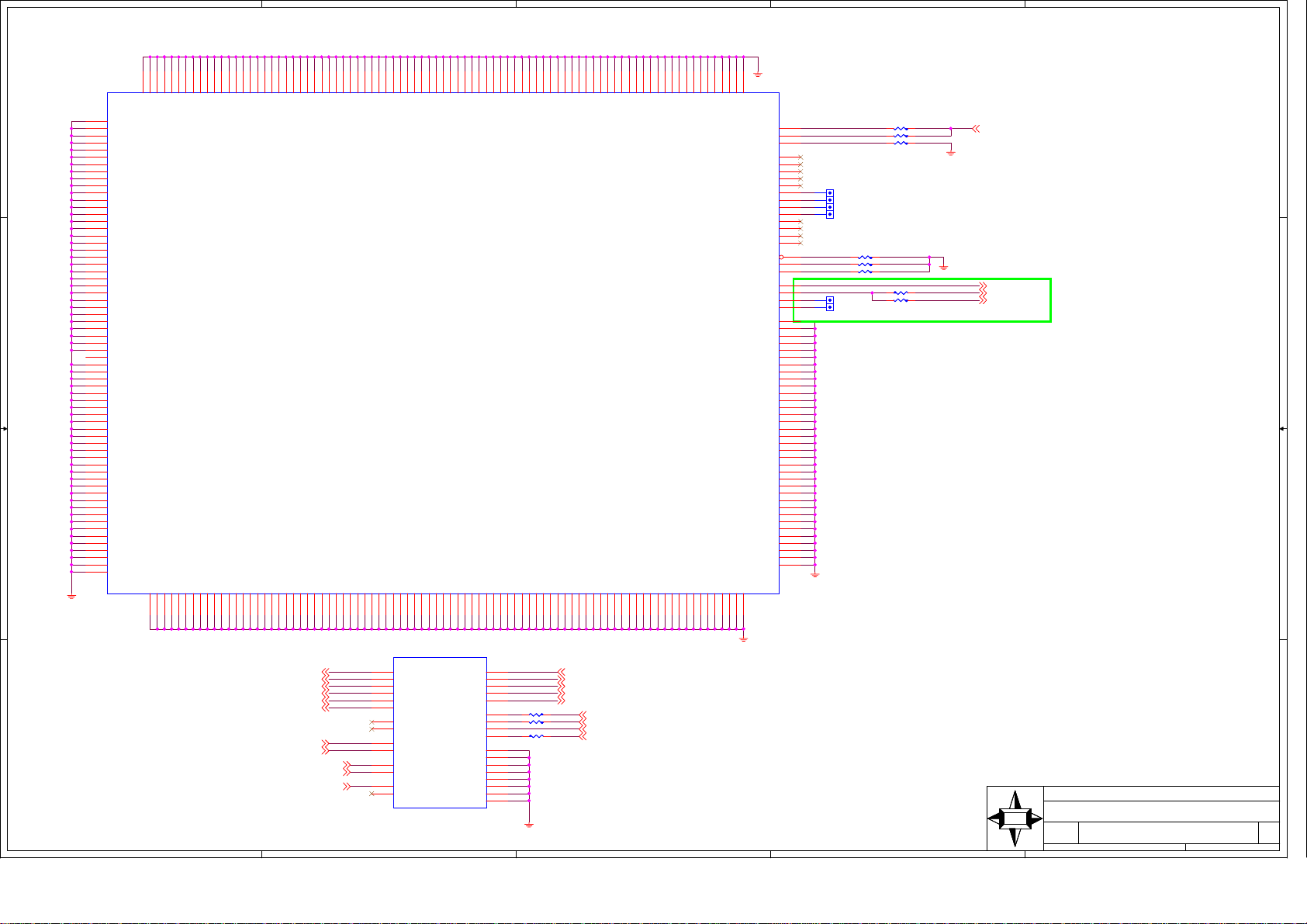

Page 6

5

U1MCH

U1MCH

U3B

U3B

J42

FSB_AB_3

L39

FSB_AB_4

J40

FSB_AB_5

L37

FSB_AB_6

L36

FSB_AB_7

K42

FSB_AB_8

N32

FSB_AB_9

N34

FSB_AB_10

M38

FSB_AB_11

N37

FSB_AB_12

M36

FSB_AB_13

R34

FSB_AB_14

N35

FSB_AB_15

N38

FSB_AB_16

U37

FSB_AB_17

N39

FSB_AB_18

R37

FSB_AB_19

P42

FSB_AB_20

R39

FSB_AB_21

V36

FSB_AB_22

R38

FSB_AB_23

U36

FSB_AB_24

U33

FSB_AB_25

R35

FSB_AB_26

V33

FSB_AB_27

V35

FSB_AB_28

Y34

FSB_AB_29

V42

FSB_AB_30

V38

FSB_AB_31

Y36

FSB_AB_32

Y38

FSB_AB_33

Y39

FSB_AB_34

AA37

FSB_AB_35

F40

FSB_REQB_0

L35

FSB_REQB_1

L38

FSB_REQB_2

G43

FSB_REQB_3

J37

FSB_REQB_4

M34

FSB_ADSTBB_0

U34

FSB_ADSTBB_1

M42

FSB_DSTBPB_0

M43

FSB_DSTBNB_0

G35

FSB_DSTBPB_1

H33

FSB_DSTBNB_1

G27

FSB_DSTBPB_2

H27

FSB_DSTBNB_2

B38

FSB_DSTBPB_3

C38

FSB_DSTBNB_3

M40

FSB_DINVB_0

J33

FSB_DINVB_1

G29

FSB_DINVB_2

E33

FSB_DINVB_3

W40

FSB_ADSB

Y40

FSB_TRDYB

W41

FSB_DRDYB

T43

FSB_DEFERB

Y43

FSB_HITMB

U42

FSB_HITB

V41

FSB_LOCKB

AA42

FSB_BREQ0B

W42

FSB_BNRB

G39

FSB_BPRIB

U40

FSB_DBSYB

U41

FSB_RSB_0

AA41

FSB_RSB_1

U39

FSB_RSB_2

C31

FSB_CPURSTB

1 OF 7

1 OF 7

Q35

Q35

*GTLREF VOLTAGE SHOULD BE

0.67*VTT=0.8V (At VTT=1.2V)

V_FSB_VTT

R225

R225

100R1%/2

100R1%/2

R229

R229

200R1%/2

200R1%/2

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB

FSB

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

FSB_SCOMP

FSB_SCOMPB

FSB_DVREF

FSB_ACCVREF

HPL_CLKINP

HPL_CLKINN

CPU_MCH_GTLREF

R234 51R/2R234 51R/2

C255

C255

C1U16Y3

C1U16Y3

R40

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

D35

E41

B41

D42

C40

C35

B40

D38

D37

B33

D33

C34

B35

A32

D32

B25

D23

C25

D25

D24

B24

R32

U32

MCH_GTLREF

C252

C252

C220P50N2

C220P50N2

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

CK_H_MCH_DP

CK_H_MCH_DN

CPU_MCH_GTLREF 3

H_ADS#3

H_HITM#3

H_HIT#3

H_BR#03,4

H_BNR#3

H_BPRI#3

C245

C245

X_C2.7P25N2

X_C2.7P25N2

HXSCOMPB

C241

C241

X_C2.7P25N2

X_C2.7P25N2

HXRCOMP

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_RS#0

H_RS#1

H_RS#2

H_A#[3..35]3 H_D#[0..63] 3

D D

H_REQ#[0..4]3

C C

B B

V_FSB_VTT HXSCOMP

V_FSB_VTT

H_ADSTB#03

H_ADSTB#13

H_DSTBP#03

H_DSTBN#03

H_DSTBP#13

H_DSTBN#13

H_DSTBP#23

H_DSTBN#23

H_DSTBP#33

H_DSTBN#33

H_DBI#[0..3]3

H_TRDY#3

H_DRDY#3

H_DEFER#3

H_LOCK#3

H_DBSY#3

H_RS#[0..2]3

H_CPURST#3,4,5

R226

R226

49.9R1%/2

49.9R1%/2

R220

R220

49.9R1%/2

49.9R1%/2

R237

R237

16.5R1%/2

16.5R1%/2

HXSWING SHOULD BE 1/4*VTT

V_FSB_VTT

A A

R219

R219

100R1%/2

100R1%/2

R217

R217

301R1%0402

301R1%0402

V_FSB_VTT

R228

R228

49.9R1%/2

49.9R1%/2

C247

C247

C0.1U16Y2

C0.1U16Y2

Ver 3.2 R217 ===>301R C247==>0.1U

HXSWING

5

HXSWING

HXRCOMP

HXSCOMP

HXSCOMPB

MCH_GTLREF

4

CK_H_MCH_DP 15

CK_H_MCH_DN 15

4

CPU_BSEL13,15

CPU_BSEL03,15

CPU_BSEL23,15

EXP16_PRSNT#21

Really need or just reserve the invert?

PIN H L

DDR2MTYPE

EXP_SLR

Normal

EXP_EN

Concurrent

Enable

MCH_TCEN

EXP16_PRSNT#

DDR3

Reverse

Non-concurrent

Disable

CL_VREF_MCH = 0.349V

Close to GMCH

V_1P25_CL_MCH

R286

R286

1KR1%/2

1KR1%/2

R290

R290

392R1%/2

392R1%/2

3

EXP_A_RXP_021

EXP_A_RXN_021

EXP_A_RXP_121

EXP_A_RXN_121

EXP_A_RXP_221

EXP_A_RXN_221

EXP_A_RXP_321

EXP_A_RXN_321

EXP_A_RXP_421

EXP_A_RXN_421

EXP_A_RXP_521

EXP_A_RXN_521

EXP_A_RXP_621

EXP_A_RXN_621

EXP_A_RXP_721

EXP_A_RXN_721

EXP_A_RXP_821

EXP_A_RXN_821

EXP_A_RXP_921

EXP_A_RXN_921

EXP_A_RXP_1021

EXP_A_RXN_1021

EXP_A_RXP_1121

EXP_A_RXN_1121

EXP_A_RXP_1221

EXP_A_RXN_1221

EXP_A_RXP_1321

EXP_A_RXN_1321

EXP_A_RXP_1421

EXP_A_RXN_1421

EXP_A_RXP_1521

EXP_A_RXN_1521

DMI_ITP_MRP_010

DMI_ITN_MRN_010

DMI_ITP_MRP_110

DMI_ITN_MRN_110

DMI_ITP_MRP_210

DMI_ITN_MRN_210

DMI_ITP_MRP_310

DMI_ITN_MRN_310

CK_PE_100M_MCH_DP15

CK_PE_100M_MCH_DN15

SDVO_CTRL_DATA21

SDVO_CTRL_CLK21

RN31

RN31

8P4R-10KR/2

8P4R-10KR/2

1

2

3

4

5

6

MCH_BS2

7

8

R270 0R/2R270 0R/2

Description

MEMORY TYPE

PCI_E Lane Reversal

PCI_E/SDVO co-existence

TLS confidentiality

CLINK_DATA11

CLINK_CLK11

CLINK_RST11

CLINK_PWOK11

CL_VREF_MCH

C306

C306

C0.1U16Y2

C0.1U16Y2

3

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH_DP

CK_PE_100M_MCH_DN

SDVO_CTRL_DATA

SDVO_CTRL_CLK

MCH_BS0

MCH_BS1

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

EXP_EN

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

X_TPX_TP

CLINK_DATA

CLINK_CLK

CL_VREF_MCH

CLINK_RST

CLINK_PWOK

X_TPX_TP

U3A

U3A

F13

PEG_RXP_0

E13

PEG_RXN_0

K15

PEG_RXP_1

J15

PEG_RXN_1

F12

PEG_RXP_2

E12

PEG_RXN_2

J12

PEG_RXP_3

H12

PEG_RXN_3

J11

PEG_RXP_4

H11

PEG_RXN_4

F7

PEG_RXP_5

E7

PEG_RXN_5

E5

PEG_RXP_6

F6

PEG_RXN_6

C2

PEG_RXP_7

D2

PEG_RXN_7

G6

PEG_RXP_8

G5

PEG_RXN_8

L9

PEG_RXP_9

L8

PEG_RXN_9

M8

PEG_RXP_10

M9

PEG_RXN_10

M4

PEG_RXP_11

L4

PEG_RXN_11

M5

PEG_RXP_12

M6

PEG_RXN_12

R9

PEG_RXP_13

R10

PEG_RXN_13

T4

PEG_RXP_14

R4

PEG_RXN_14

R6

PEG_RXP_15

R7

PEG_RXN_15

W2

DMI_RXP_0

V1

DMI_RXN_0

Y8

DMI_RXP_1

Y9

DMI_RXN_1

AA7

DMI_RXP_2

AA6

DMI_RXN_2

AB3

DMI_RXP_3

AA4

DMI_RXN_3

B12

EXP_CLKINP

B13

EXP_CLKINN

G17

SDVO_CTRLDATA

E17

SDVO_CTRLCLK

Q35

Q35

G20

J20

J18

K20

F20

G18

E18

K17

J17

G15

L17

E20

N18

N15

N17

L15

L18

M18

AD12

AD13

AM5

AA12

AM15

AA10

AA9

AA11

Y12

V31

U30

U31

R29

R30

U3E

U3E

BSEL0

BSEL1

BSEL2

ALLZTEST

XORTEST

MTYPE

EXP_SLR

RESERVED_12

EXP_EN

RFU_G15

RESERVED_14

TCEN

RESERVED_16

RESERVED_17

RESERVED_18

RESERVED_19

RESERVED_20

RESERVED_21

CL_DATA

CL_CLK

CL_VREF

CL_RSTB

CL_PWROK

RESERVED_22

RESERVED_23

RESERVED_24

RESERVED_25

RESERVED_V31

RESERVED_26

RESERVED_27

RESERVED_28

RESERVED_29

Q35

Q35

U1MCH

U1MCH

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

PEG_TXN_2

PEG_TXP_3

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PCIE

PCIE

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI

DMI

EXP_COMPO

EXP_COMPI

CRT_GREENB

CRT_DDC_DATA

CRT_DDC_CLK

DPL_REFCLKINP

DPL_REFCLKINN

RESERVED_34

RESERVED_35

RESERVED_36

RESERVED_37

MISC VGA

MISC VGA

RESERVED_33

RESERVED_32

RESERVED_31

RESERVED_30

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

2 OF 7

2 OF 7

CRT_HSYNC

CRT_VSYNC

CRT_RED

CRT_GREEN

CRT_BLUE

CRT_REDB

CRT_BLUEB

CRT_IREF

RSTINB

PWROK

ICH_SYNCB

5 OF 7

5 OF 7

2

VCC

VSS

2

NC

D11

D12

B11

A10

C10

D9

B9

B7

D7

D6

B5

B6

B3

B4

F2

E2

F4

G4

J4

K3

L2

K1

N2

M2

P3

N4

R2

P1

U2

T2

V3

U4

V7

V6

W4

Y4

AC8

AC9

Y2

AA2

AC11

AC12

C15

E15

B18

C19

B20

C18

D19

D20

L13

M13

A20

C14

D13

L12

M11

H18

F17

A14

AM18

AM17

J13

A42

R20

R13

R12

U11

U12

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

R272 24.9R1%/2R272 24.9R1%/2

HSYNC

VSYNC

C516 C3.3p50N/4C516 C3.3p50N/4

C530 C3.3p50N/4C530 C3.3p50N/4

C537 C3.3p50N/4C537 C3.3p50N/4

MCH_DDC_DATA

MCH_DDC_CLK

DACREFSET

CK_DOT96_MCH_DP

CK_DOT96_MCH_DN

V_1P25_CORE

reserve a 0.1u cap

CHIP_PWGD

1

EXP_A_TXP_0 21

EXP_A_TXN_0 21

EXP_A_TXP_1 21

EXP_A_TXN_1 21

EXP_A_TXP_2 21

EXP_A_TXN_2 21

EXP_A_TXP_3 21

EXP_A_TXN_3 21

EXP_A_TXP_4 21

EXP_A_TXN_4 21

EXP_A_TXP_5 21

EXP_A_TXN_5 21

EXP_A_TXP_6 21

EXP_A_TXN_6 21

EXP_A_TXP_7 21

EXP_A_TXN_7 21

EXP_A_TXP_8 21

EXP_A_TXN_8 21

EXP_A_TXP_9 21

EXP_A_TXN_9 21

EXP_A_TXP_10 21

EXP_A_TXN_10 21

EXP_A_TXP_11 21

EXP_A_TXN_11 21

EXP_A_TXP_12 21

EXP_A_TXN_12 21

EXP_A_TXP_13 21

EXP_A_TXN_13 21

EXP_A_TXP_14 21

EXP_A_TXN_14 21

EXP_A_TXP_15 21

EXP_A_TXN_15 21

DMI_MTP_IRP_0 10

DMI_MTN_IRN_0 10

DMI_MTP_IRP_1 10

DMI_MTN_IRN_1 10

DMI_MTP_IRP_2 10

DMI_MTN_IRN_2 10

DMI_MTP_IRP_3 10

DMI_MTN_IRN_3 10

V_1P25_CORE

HSYNC 17

VSYNC 17

VGA_RED 17

VGA_GREEN 17

VGA_BLUE 17

Close to GMCH within 250 mils.

Stuff 0-ohm for non-Graphic sku.

MCH_DDC_DATA 17

MCH_DDC_CLK 17

CK_DOT96_MCH_DP 15

CK_DOT96_MCH_DN 15

PLTRST# 10,11,16

CHIP_PWGD 11,24

ICH_SYNC# 11

MSI

MSI

MSI

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

VGA_RED

R255 150R/4R255 150R/4

VGA_GREEN

R254 150R/4R254 150R/4

VGA_BLUE

R252 150R/4R252 150R/4

Close to GMCH.

Change to 0-ohm for

non-Graphic sku

DACREFSET

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Bearlake - FSB, PCIE, DMI, VGA, MSIC

Bearlake - FSB, PCIE, DMI, VGA, MSIC

Bearlake - FSB, PCIE, DMI, VGA, MSIC

MS-7559

MS-7559

MS-7559

1

R241 1.3KR1%/2R241 1.3KR1%/2

632

632

632

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 7

5

U1MCH

NC

NC

Q35

Q35

U1MCH

3 OF 7

3 OF 7

U3C

U3C

MAA_A0

MAA_A[0..14]13,14

D D

WE_A#13,14

CAS_A#13,14

RAS_A#13,14

SBS_A[0..2]13,14

SCS_A#013,14

SCS_A#113,14

SCS_A#213,14

SCS_A#313,14

SCKE_A013,14

SCKE_A113,14

SCKE_A213,14

SCKE_A313,14

ODT_A013,14

ODT_A113,14

ODT_A213,14

C C

B B

ODT_A313,14

P_DDR0_A13

N_DDR0_A13

P_DDR1_A13

N_DDR1_A13

P_DDR2_A13

N_DDR2_A13

P_DDR3_A13

N_DDR3_A13

P_DDR4_A13

N_DDR4_A13

P_DDR5_A13

N_DDR5_A13

X_TP X_TP

X_TP X_TP

X_TP X_TP

X_TP X_TP

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

WE_A#

CAS_A#

RAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A#0

SCS_A#1

SCS_A#2

SCS_A#3

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

ODT_A0

ODT_A1

ODT_A2

ODT_A3

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

P_DDR3_A

N_DDR3_A

P_DDR4_A

N_DDR4_A

P_DDR5_A

N_DDR5_A

BB30

DDR_A_MA_0

AY25

DDR_A_MA_1

BA23

DDR_A_MA_2

BB23

DDR_A_MA_3

AY23

DDR_A_MA_4

BB22

DDR_A_MA_5

BA22

DDR_A_MA_6

BB21

DDR_A_MA_7

AW21

DDR_A_MA_8

BA21

DDR_A_MA_9

BB31

DDR_A_MA_10

AY21

DDR_A_MA_11

BC20

DDR_A_MA_12

AY38

DDR_A_MA_13

BA19

DDR_A_MA_14

BA33

DDR_A_WEB

AW35

DDR_A_CASB

AY33

DDR_A_RASB

BA31

DDR_A_BS_0

AY31

DDR_A_BS_1

AY20

DDR_A_BS_2

BA34

DDR_A_CSB_0

AY35

DDR_A_CSB_1

BB33

DDR_A_CSB_2

BB38

DDR_A_CSB_3

AY19

DDR_A_CKE_0

AW18

DDR_A_CKE_1

BB19

DDR_A_CKE_2

BA18

DDR_A_CKE_3

BB35

DDR_A_ODT_0

BA38

DDR_A_ODT_1

BA35

DDR_A_ODT_2

BA39

DDR_A_ODT_3

AR31

DDR_A_CK_0

AU31

DDR_A_CKB_0

AP27

DDR_A_CK_1

AN27

DDR_A_CKB_1

AV33

DDR_A_CK_2

AW33

DDR_A_CKB_2

AP29

DDR_A_CK_3

AP31

DDR_A_CKB_3

AM26

DDR_A_CK_4

AM27

DDR_A_CKB_4

AT33

DDR_A_CK_5

AU33

DDR_A_CKB_5

BC16

DDR3_DRAMRSTB

AN15

DDR3_DRAM_PWROK

AY37

DDR3_A_CSB1

BB29

DDR3_A_MA0

BB34

DDR3_A_WEB

AW32

DDR3_B_ODT3

BC43

TEST3

BC1

TEST1

A43

TEST0

AN21

RESERVED_1

N20

NC_1

B2

NC_2

B42

NC_3

B43

NC_4

BB1

NC_5

BB2

NC_6

BB43

NC_7

BC2

NC_8

BC42

NC_9

DDR_A

DDR_A

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DQS_1

DDR_A_DQSB_1

DDR_A_DQS_2

DDR_A_DQSB_2

DDR_A_DQS_3

DDR_A_DQSB_3

DDR_A_DQS_4

DDR_A_DQSB_4

DDR_A_DQS_5

DDR_A_DQSB_5

DDR_A_DQS_6

DDR_A_DQSB_6

DDR_A_DQS_7

DDR_A_DQSB_7

DDR_A_DQ_10

DDR_A_DQ_11

DDR_A_DQ_12

DDR_A_DQ_13

DDR_A_DQ_14

DDR_A_DQ_15

DDR_A_DQ_16

DDR_A_DQ_17

DDR_A_DQ_18

DDR_A_DQ_19

DDR_A_DQ_20

DDR_A_DQ_21

DDR_A_DQ_22

DDR_A_DQ_23

DDR_A_DQ_24

DDR_A_DQ_25

DDR_A_DQ_26

DDR_A_DQ_27

DDR_A_DQ_28

DDR_A_DQ_29

DDR_A_DQ_30

DDR_A_DQ_31

DDR_A_DQ_32

DDR_A_DQ_33

DDR_A_DQ_34

DDR_A_DQ_35

DDR_A_DQ_36

DDR_A_DQ_37

DDR_A_DQ_38

DDR_A_DQ_39

DDR_A_DQ_40

DDR_A_DQ_41

DDR_A_DQ_42

DDR_A_DQ_43

DDR3

DDR3

DDR_A_DQ_44

DDR_A_DQ_45

DDR_A_DQ_46

DDR_A_DQ_47

DDR_A_DQ_48

DDR_A_DQ_49

DDR_A_DQ_50

DDR_A_DQ_51

DDR_A_DQ_52

DDR_A_DQ_53

DDR_A_DQ_54

DDR_A_DQ_55

DDR_A_DQ_56

DDR_A_DQ_57

DDR_A_DQ_58

DDR_A_DQ_59

DDR_A_DQ_60

DDR_A_DQ_61

DDR_A_DQ_62

DDR_A_DQ_63

4

DDR_A_DM_0

DDR_A_DM_1

DDR_A_DM_2

DDR_A_DM_3

DDR_A_DM_4

DDR_A_DM_5

DDR_A_DM_6

DDR_A_DM_7

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5

DDR_A_DQ_6

DDR_A_DQ_7

DDR_A_DQ_8

DDR_A_DQ_9

AP2

AP3

AW2

AW1

AY7

BA6

AT20

AU18

AR41

AR40

AL41

AL40

AG42

AG41

AC42

AC41

AN2

AW3

BB6

AN18

AU43

AM43

AG40

AC40

AM1

AN3

AR2

AR3

AL3

AM2

AR5

AR4

AV4

AV3

BA4

BB3

AU2

AU1

AY2

AY3

BB5

AY6

BA9

BB9

BA5

BB4

BC7

AY9

AT18

AR18

AU21

AT21

AP17

AN17

AP20

AV20

AV42

AU40

AP42

AN39

AV40

AV41

AR42

AP41

AN41

AM39

AK42

AK41

AN40

AN42

AL42

AL39

AJ40

AH43

AF39

AE40

AJ42

AJ41

AF41

AF42

AD40

AD43

AB41

AA40

AE42

AE41

AC39

AB42

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

DQM_A0

DQM_A1

DQM_A2

DQM_A3

DQM_A4

DQM_A5

DQM_A6

DQM_A7

DATA_A0

DATA_A1

DATA_A2

DATA_A3

DATA_A4

DATA_A5

DATA_A6

DATA_A7

DATA_A8

DATA_A9

DATA_A10

DATA_A11

DATA_A12

DATA_A13

DATA_A14

DATA_A15

DATA_A16

DATA_A17

DATA_A18

DATA_A19

DATA_A20

DATA_A21

DATA_A22

DATA_A23

DATA_A24

DATA_A25

DATA_A26

DATA_A27

DATA_A28

DATA_A29

DATA_A30

DATA_A31

DATA_A32

DATA_A33

DATA_A34

DATA_A35

DATA_A36

DATA_A37

DATA_A38

DATA_A39

DATA_A40

DATA_A41

DATA_A42

DATA_A43

DATA_A44

DATA_A45

DATA_A46

DATA_A47

DATA_A48

DATA_A49

DATA_A50

DATA_A51

DATA_A52

DATA_A53

DATA_A54

DATA_A55

DATA_A56

DATA_A57

DATA_A58

DATA_A59

DATA_A60

DATA_A61

DATA_A62

DATA_A63

DQS_A0 13

DQS_A#0 13

DQS_A1 13

DQS_A#1 13

DQS_A2 13

DQS_A#2 13

DQS_A3 13

DQS_A#3 13

DQS_A4 13

DQS_A#4 13

DQS_A5 13

DQS_A#5 13

DQS_A6 13

DQS_A#6 13

DQS_A7 13

DQS_A#7 13

DQM_A[0..7] 13

DATA_A[0..63] 13

VCC_DDR

R289 1KR1%/2R289 1KR1%/2

3

MAA_B[0..14]14

SBS_B[0..2]14

SCS_B#014

SCS_B#114

SCS_B#214

SCS_B#314

SCKE_B014

SCKE_B114

SCKE_B214

SCKE_B314

P_DDR0_B14

N_DDR0_B14

P_DDR1_B14

N_DDR1_B14

P_DDR2_B14

N_DDR2_B14

P_DDR3_B14

N_DDR3_B14

P_DDR4_B14

N_DDR4_B14

P_DDR5_B14

N_DDR5_B14

PLACE 0.1UF CAP

CLOSE TO MCH

R287

R287

1KR1%/2

1KR1%/2

ODT_B014

ODT_B114

ODT_B214

ODT_B314

WE_B#14

CAS_B#14

RAS_B#14

C302

C302

C0.1U16Y2

C0.1U16Y2

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

MAA_B14

WE_B#

CAS_B#

RAS_B#

SBS_B0

SBS_B1

SBS_B2

SCS_B#0

SCS_B#1

SCS_B#2

SCS_B#3

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

ODT_B0

ODT_B1

ODT_B2

ODT_B3

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

P_DDR3_B

N_DDR3_B

P_DDR4_B

N_DDR4_B

P_DDR5_B

N_DDR5_B

MCH_VREF_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

DDR_RCOMPVOL

DDR_RCOMPVOH

AW15

BB15

BA15

AY15

BA14

BB14

AW12

BA13

BB13

AY13

BA17

AY12

BA11

AY27

BB11

BB25

AW26

AY24

BB17

AY17

AY11

BA25

BA29

BA26

BA30

AW11

BC12

BA10

BB10

BB27

AW29

BA27

AY29

AW31

AV31

AU27

AT27

AV32

AT32

AR29

AU29

AV29

AW27

AN33

AP32

AM6

BB40

BA40

AM8

AM10

AW42

AN32

AM31

AG32

AF32

AP21

AA39

AM21

AL4

AL2

BA2

U3D

U3D

DDR_B_MA_0

DDR_B_MA_1

DDR_B_MA_2

DDR_B_MA_3

DDR_B_MA_4

DDR_B_MA_5

DDR_B_MA_6

DDR_B_MA_7

DDR_B_MA_8

DDR_B_MA_9

DDR_B_MA_10

DDR_B_MA_11

DDR_B_MA_12

DDR_B_MA_13

DDR_B_MA_14

DDR_B_WEB

DDR_B_CASB

DDR_B_RASB

DDR_B_BS_0

DDR_B_BS_1

DDR_B_BS_2

DDR_B_CSB_0

DDR_B_CSB_1

DDR_B_CSB_2

DDR_B_CSB_3

DDR_B_CKE_0

DDR_B_CKE_1

DDR_B_CKE_2

DDR_B_CKE_3

DDR_B_ODT_0

DDR_B_ODT_1

DDR_B_ODT_2

DDR_B_ODT_3

DDR_B_CK_0

DDR_B_CKB_0

DDR_B_CK_1

DDR_B_CKB_1

DDR_B_CK_2

DDR_B_CKB_2

DDR_B_CK_3

DDR_B_CKB_3

DDR_B_CK_4

DDR_B_CKB_4

DDR_B_CK_5

DDR_B_CKB_5

DDR_B

DDR_B

DDR_VREF

DDR_RCOMPXPD

DDR_RCOMPXPU

DDR_RCOMPYPD

DDR_RCOMPYPU

DDR_RCOMPVOL

DDR_RCOMPVOH

RESERVED_2

RESERVED_3

RESERVED_4

RESERVED_5

RESERVED_6

RESERVED_7

RESERVED_8

RESERVED_9

RESERVED_10

4 OF 7

4 OF 7

Q35

Q35

U1MCH

U1MCH

2

DDR_B_DQS_0

DDR_B_DQSB_0

DDR_B_DQS_1

DDR_B_DQSB_1

DDR_B_DQS_2

DDR_B_DQSB_2

DDR_B_DQS_3

DDR_B_DQSB_3

DDR_B_DQS_4

DDR_B_DQSB_4

DDR_B_DQS_5

DDR_B_DQSB_5

DDR_B_DQS_6

DDR_B_DQSB_6

DDR_B_DQS_7

DDR_B_DQSB_7

DDR_B_DM_0

DDR_B_DM_1

DDR_B_DM_2

DDR_B_DM_3

DDR_B_DM_4

DDR_B_DM_5

DDR_B_DM_6

DDR_B_DM_7

DDR_B_DQ_0

DDR_B_DQ_1

DDR_B_DQ_2

DDR_B_DQ_3

DDR_B_DQ_4

DDR_B_DQ_5

DDR_B_DQ_6

DDR_B_DQ_7

DDR_B_DQ_8

DDR_B_DQ_9

DDR_B_DQ_10

DDR_B_DQ_11

DDR_B_DQ_12

DDR_B_DQ_13

DDR_B_DQ_14

DDR_B_DQ_15

DDR_B_DQ_16

DDR_B_DQ_17

DDR_B_DQ_18

DDR_B_DQ_19

DDR_B_DQ_20

DDR_B_DQ_21

DDR_B_DQ_22

DDR_B_DQ_23

DDR_B_DQ_24

DDR_B_DQ_25

DDR_B_DQ_26

DDR_B_DQ_27

DDR_B_DQ_28

DDR_B_DQ_29

DDR_B_DQ_30

DDR_B_DQ_31

DDR_B_DQ_32

DDR_B_DQ_33

DDR_B_DQ_34

DDR_B_DQ_35

DDR_B_DQ_36

DDR_B_DQ_37

DDR_B_DQ_38

DDR_B_DQ_39

DDR_B_DQ_40

DDR_B_DQ_41

DDR_B_DQ_42

DDR_B_DQ_43

DDR_B_DQ_44

DDR_B_DQ_45

DDR_B_DQ_46

DDR_B_DQ_47

DDR_B_DQ_48

DDR_B_DQ_49

DDR_B_DQ_50

DDR_B_DQ_51

DDR_B_DQ_52

DDR_B_DQ_53

DDR_B_DQ_54

DDR_B_DQ_55

DDR_B_DQ_56

DDR_B_DQ_57

DDR_B_DQ_58

DDR_B_DQ_59

DDR_B_DQ_60

DDR_B_DQ_61

DDR_B_DQ_62

DDR_B_DQ_63

AV6

AU5

AR12

AP12

AP15

AR15

AT24

AU26

AW39

AU39

AL35

AL34

AG35

AG36

AC36

AC37

AR7

AW9

AW13

AP23

AU37

AM37

AG39

AD38

AN7

AN8

AW5

AW7

AN5

AN6

AN9

AU7

AT11

AU11

AP13

AR13

AR11

AU9

AV12

AU12

AU15

AV13

AU17

AT17

AU13

AM13

AV15

AW17

AV24

AT23

AT26

AP26

AU23

AW23

AR24

AN26

AW37

AV38

AN36

AN37

AU35

AR35

AN35

AR37

AM35

AM38

AJ34

AL38

AR39

AM34

AL37

AL32

AG38

AJ38

AF35

AF33

AJ37

AJ35

AG33

AF34

AD36

AC33

AA34

AA36

AD34

AF38

AC34

AA33

DQS_B0

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

DQM_B0DQM_B0

DQM_B1DQM_B1

DQM_B2DQM_B2

DQM_B3DQM_B3

DQM_B4DQM_B4

DQM_B5DQM_B5

DQM_B6DQM_B6

DQM_B7DQM_B7

DATA_B0DATA_B0

DATA_B1DATA_B1

DATA_B2DATA_B2

DATA_B3DATA_B3

DATA_B4DATA_B4

DATA_B5DATA_B5

DATA_B6DATA_B6

DATA_B7DATA_B7

DATA_B8DATA_B8

DATA_B9DATA_B9

DATA_B10DATA_B10

DATA_B11DATA_B11

DATA_B12DATA_B12

DATA_B13DATA_B13

DATA_B14DATA_B14

DATA_B15DATA_B15

DATA_B16DATA_B16

DATA_B17DATA_B17

DATA_B18DATA_B18

DATA_B19DATA_B19

DATA_B20DATA_B20

DATA_B21DATA_B21

DATA_B22DATA_B22

DATA_B23DATA_B23

DATA_B24DATA_B24

DATA_B25DATA_B25

DATA_B26DATA_B26

DATA_B27DATA_B27

DATA_B28DATA_B28

DATA_B29DATA_B29

DATA_B30DATA_B30

DATA_B31DATA_B31

DATA_B32DATA_B32

DATA_B33DATA_B33

DATA_B34DATA_B34

DATA_B35DATA_B35

DATA_B36DATA_B36

DATA_B37DATA_B37

DATA_B38DATA_B38

DATA_B39DATA_B39

DATA_B40DATA_B40

DATA_B41DATA_B41

DATA_B42DATA_B42

DATA_B43DATA_B43

DATA_B44DATA_B44

DATA_B45DATA_B45

DATA_B46DATA_B46

DATA_B47DATA_B47

DATA_B48DATA_B48

DATA_B49DATA_B49

DATA_B50DATA_B50

DATA_B51DATA_B51

DATA_B52DATA_B52

DATA_B53DATA_B53

DATA_B54DATA_B54

DATA_B55DATA_B55

DATA_B56DATA_B56

DATA_B57DATA_B57

DATA_B58DATA_B58

DATA_B59DATA_B59

DATA_B60DATA_B60

DATA_B61DATA_B61

DATA_B62DATA_B62

DATA_B63DATA_B63

DQS_B0 14

DQS_B#0 14

DQS_B1 14

DQS_B#1 14

DQS_B2 14

DQS_B#2 14

DQS_B3 14

DQS_B#3 14

DQS_B4 14

DQS_B#4 14

DQS_B5 14

DQS_B#5 14

DQS_B6 14

DQS_B#6 14

DQS_B7 14

DQS_B#7 14

DQM_B[0..7] 14

DATA_B[0..63] 14

1

Place close to GMCH

VCC_DDR

C238 C2.2U6.3Y3C238 C2.2U6.3Y3

C281 X_C2.2U6.3Y3C281 X_C2.2U6.3Y3

C274 C2.2U6.3Y3C274 C2.2U6.3Y3

C251 C2.2U6.3Y3C251 C2.2U6.3Y3

C226 C2.2U6.3Y3C226 C2.2U6.3Y3

C261 C2.2U6.3Y3C261 C2.2U6.3Y3

SCROMP1,3 CLOSED TO VCC_DDR

A A

VCC_DDR

5

4

R276 1KR1%/2R276 1KR1%/2

R279

R279

3.01KR1%/2

3.01KR1%/2

R278 1KR1%/2R278 1KR1%/2

C293

C293

C0.1U16Y2

C0.1U16Y2

3

DDR_RCOMPVOL

DDR_RCOMPVOL = 0.2 * VCC_DDR

C297

C297

C10000P25X2

C10000P25X2

DDR_RCOMPVOH

DDR_RCOMPVOH = 0.8 * VCC_DDR

C298

C298

C10000P25X2

C10000P25X2

C209

C209

C0.1U16Y2

C0.1U16Y2

MSI

MSI

MSI

2

VCC_DDR

C208

C208

C0.1U16Y2

C0.1U16Y2

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

MICRO-STAR INT'L CO.,LTD

Size Document Description Rev

Size Document Description Rev

Size Document Description Rev

Custom

Custom

Custom

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

Date:

Wednesday, July 09, 2008

R281 19.1R1%/2R281 19.1R1%/2

R280 19.1R1%/2R280 19.1R1%/2

R210 19.1R1%/2R210 19.1R1%/2

R211 19.1R1%/2R211 19.1R1%/2

MS-7559

MS-7559

MS-7559

Bearlake - Memory

Bearlake - Memory

Bearlake - Memory

1

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

732

732

732

Sheet of

Sheet of

Sheet of

0A

0A

0A

Page 8

5

4

V_1P25_CORE

3

2

1

NB POWER

V_FSB_VTT

D D

L14

L14

X_L10U_100mA_0805

X_L10U_100mA_0805

X_L10U_100mA_0805

X_L10U_100mA_0805

X_L10U_100mA_0805

X_L10U_100mA_0805

X_L10U_100mA_0805

L13

L13

L0.1U_50mA

L0.1U_50mA

2 1

C278

C10u10X50805-RH

C10u10X50805-RH

X_L10U_100mA_0805

2 1

X_COPPER

X_COPPER

X_L10U_100mA_0805

X_L10U_100mA_0805

L11

L11

2 1

CP6

CP6

X_COPPER

X_COPPER

L12

L12

2 1

CP7

CP7

X_COPPER

X_COPPER

V_1P25_CORE

C C

V_1P25_CL_MCH

V_1P25_CL_MCH

V_1P25_CORE

B B

V_1P25_CORE

VCC3

A A

2 1

CP9

CP9

X_COPPER

X_COPPER

L9

L9

CP4

CP4

L10

L10

2 1

CP5

CP5

X_COPPER

X_COPPER

C10u10X50805-RH

C10u10X50805-RH

C10u10X50805-RH

C10u10X50805-RH

C275

C275

C0.1U16Y2

C0.1U16Y2

R235 1R1%/2R235 1R1%/2

R236 1R1%/2R236 1R1%/2

R238 1R1%/2R238 1R1%/2

R239 1R1%/2R239 1R1%/2

C248

C248

C2.2u6.3X5

C2.2u6.3X5

VCCA_DPLLA

VCCA_DPLLA

C256

C256

VCCA_DPLLB

C263

C263

C10000P25X2

C10000P25X2

5

VCCA_MPLL

VCCA_HPLL

C276

C276

VCCA_GPLL

C283

C283

C10u10X50805-RH

C10u10X50805-RH

C242 C10u10X50805-RHC242 C10u10X50805-RH

C249

C249

C0.1U16Y2

C0.1U16Y2

C257

C257

C0.1U16Y2

C0.1U16Y2

C262

C262

C0.1U16Y2

C0.1U16Y2

V_3P3_DAC_FILTERED

C280

C280

C0.1U16Y2

C0.1U16Y2

EC72

EC72

+

+

CD220u16EL11-RH

CD220u16EL11-RH

EC73

EC73

+

+

CD220u16EL11-RH

CD220u16EL11-RH

H_VCCPLL4

C10u10X50805-RH

C10u10X50805-RH

VCC_DDR

X_L10U_100mA_0805

X_L10U_100mA_0805

X_COPPER

X_COPPER

H_VCCPLL

C296

C296

C1U16Y3

C1U16Y3

V_3P3_DAC_FILTERED

L8

L8

2 1

R223

R223

CP3

CP3

1R1%/2

1R1%/2

C10u10X50805-RH

C10u10X50805-RH

C202

C202

C237

C237

C313

C313

C0.1U16Y2

C0.1U16Y2

VCC_CKDDR

R230

R230

1R1%/2

1R1%/2

4

R271 1R1%/2R271 1R1%/2

C300

C300

C0.1U16Y2

C0.1U16Y2

VCC3

C207

C207

C1U16Y3

C1U16Y3

VCCA_GPLL

VCCA_MPLL

VCCA_HPLL

VCCA_DPLLA

VCCA_DPLLB

BB42

BB41

BA43

BA42

AY42

A28

A30

B27

B28

B29

B30

C27

C29

C30

D27

D28

D29

E23

E26

E27

E29

F23

F24

F26

G23

G24

G26

H23

H24

J23

J24

K23

K24

L23

L24

M23

M24

M29

N23

N24

N26

N29

P23

P24

P26

P27

P29

R23

R24

R26

R27

B21

C21

B15

A24

C23

A22

C22

B16

C17

B17

A16

U3F

U3F

VTT_FSB_1

VTT_FSB_2

VTT_FSB_3

VTT_FSB_4

VTT_FSB_5

VTT_FSB_6

VTT_FSB_7

VTT_FSB_8

VTT_FSB_9

VTT_FSB_10

VTT_FSB_11

VTT_FSB_12

VTT_FSB_13

VTT_FSB_14

VTT_FSB_15

VTT_FSB_16

VTT_FSB_17

VTT_FSB_18

VTT_FSB_19

VTT_FSB_20

VTT_FSB_21

VTT_FSB_22

VTT_FSB_23

VTT_FSB_24

VTT_FSB_25

VTT_FSB_26

VTT_FSB_27

VTT_FSB_28

VTT_FSB_29

VTT_FSB_30

VTT_FSB_31

VTT_FSB_32

VTT_FSB_33

VTT_FSB_34

VTT_FSB_35

VTT_FSB_36

VTT_FSB_37

VTT_FSB_38

VTT_FSB_39

VTT_FSB_40

VTT_FSB_41

VTT_FSB_42

VTT_FSB_43

VTT_FSB_44

VTT_FSB_45

VTT_FSB_46

VCCDQ_CRT

VCCD_CRT

VCCA_EXPPLL

VCCA_MPLL

VCCA_HPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_DAC_1

VCCA_DAC_2

VCC3_3

VCCA_EXP

VCC_CKDDR_5

VCC_CKDDR_4

VCC_CKDDR_3

VCC_CKDDR_2

VCC_CKDDR_1

VCC_DDR

AA13

AA14

VCC_1

AA15

AA17

VCC_2

VCC_3

VCC_DDR_1

AV18

AV26

AA19

AA21

AA23

VCC_4

VCC_5

VCC_6

VCC_DDR_2

VCC_DDR_3

VCC_DDR_4

AY32

AW20

AW24

AA25

AA26

AA27

VCC_7

VCC_8

VCC_9

VCC_DDR_5

VCC_DDR_6

VCC_DDR_7

BB12

BB16

BB18

V_FSB_VTT

AA3

AB17

AB18

VCC_10

VCC_11

VCC_12

VCC_13

VCC_DDR_8

VCC_DDR_9

VCC_DDR_10

VCC_DDR_11

BB20

BB24

BB26

C221 X_C1U6.3Y2C221 X_C1U6.3Y2

C182 C1U6.3Y2C182 C1U6.3Y2

C179 C1U6.3Y2C179 C1U6.3Y2

C169 C1U6.3Y2C169 C1U6.3Y2

C223 X_C1U6.3Y2C223 X_C1U6.3Y2

C172 C1U6.3Y2C172 C1U6.3Y2

C224 X_C1U6.3Y2C224 X_C1U6.3Y2

C186 C1U6.3Y2C186 C1U6.3Y2

AB20

AB22

AB24

VCC_14

VCC_15

VCC_16

VCC_DDR_12

VCC_DDR_13

VCC_DDR_14

BB28

BB32

BB37

AB26

AB27

AC13

VCC_17

VCC_18

VCC_19

VCC_DDR_15

VCC_DDR_16

VCC_DDR_17

BB39

BC14

BC18

AC14

AC15

AC17

VCC_20

VCC_21

VCC_22

VCC_DDR_18

VCC_DDR_19

VCC_DDR_20

BC22

BC26

BC30

X_COPPER

X_COPPER

AC19

AC21

AC23