MSI MS-7550 Schematics

1

MS-7550 Ver:1.0

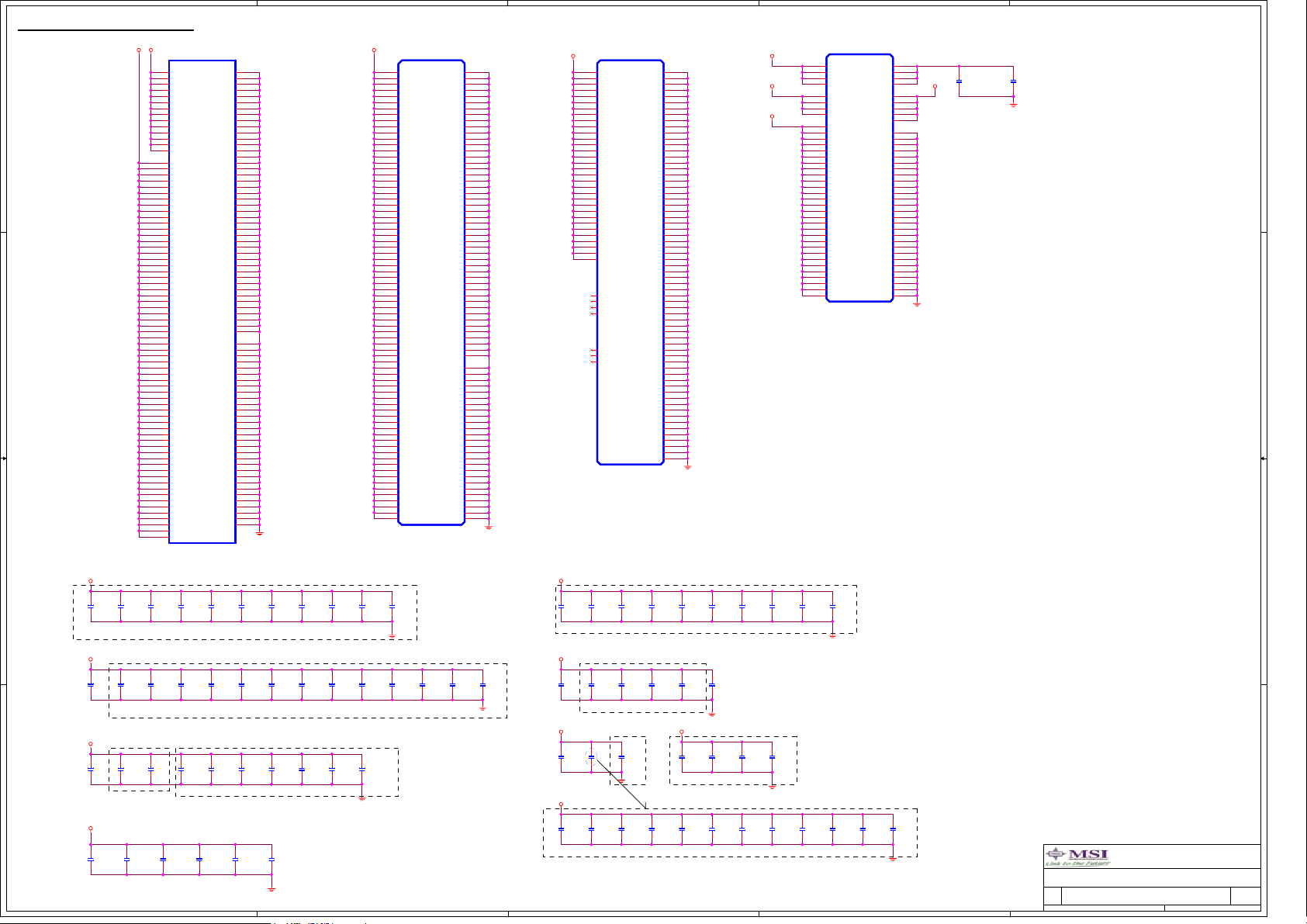

Cover Sheet

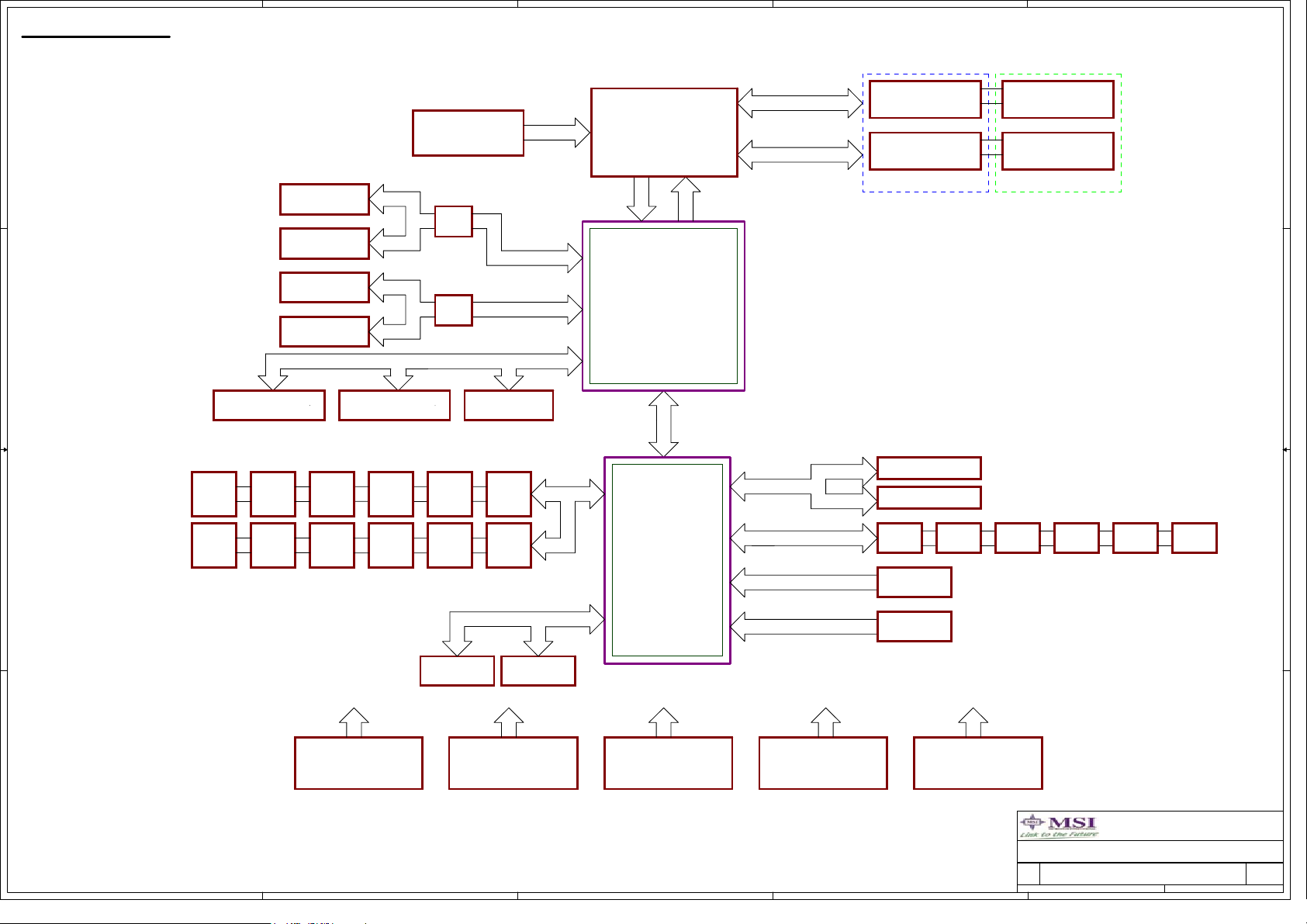

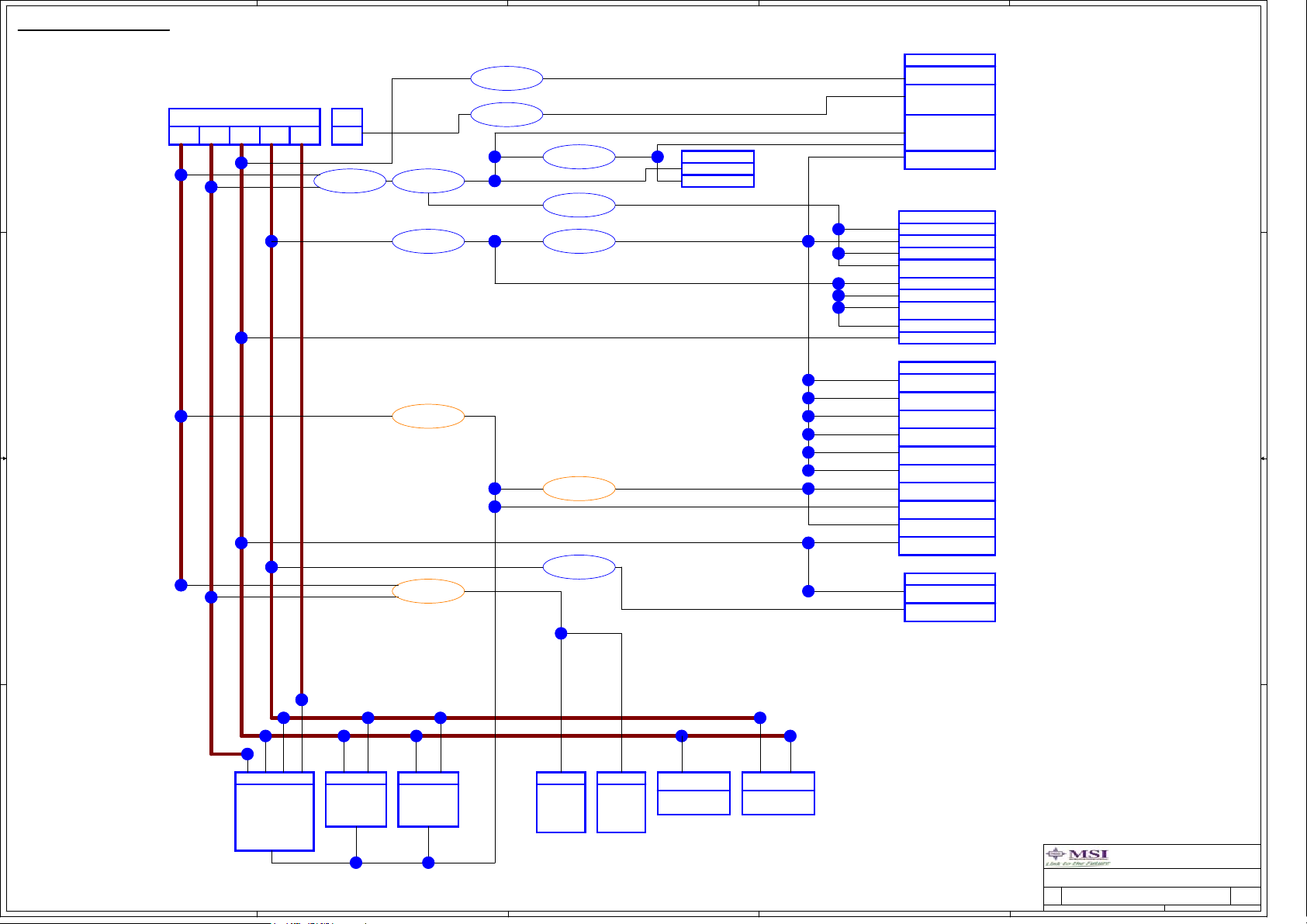

BLOCK DIAGRAM

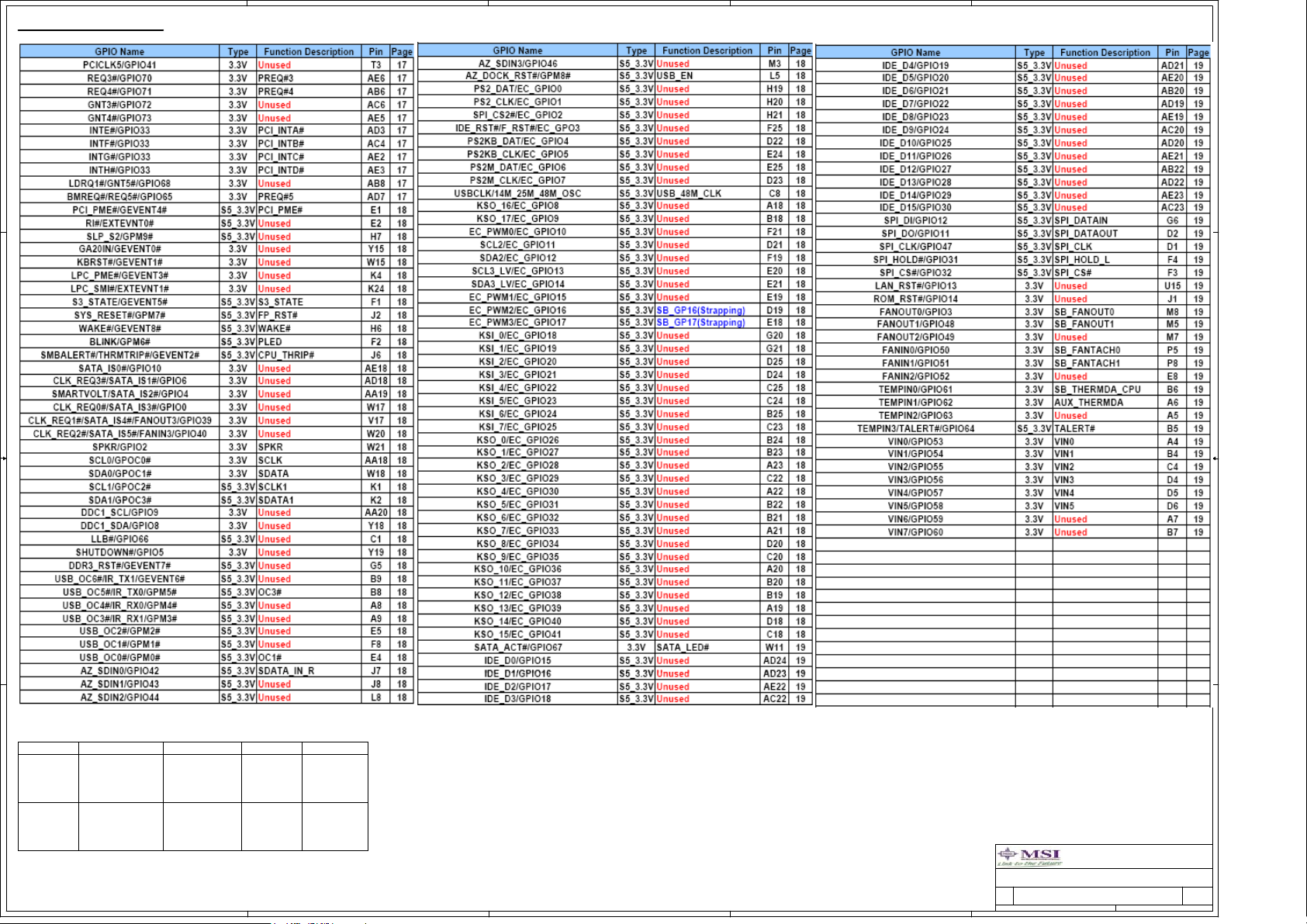

GPIO Configuration

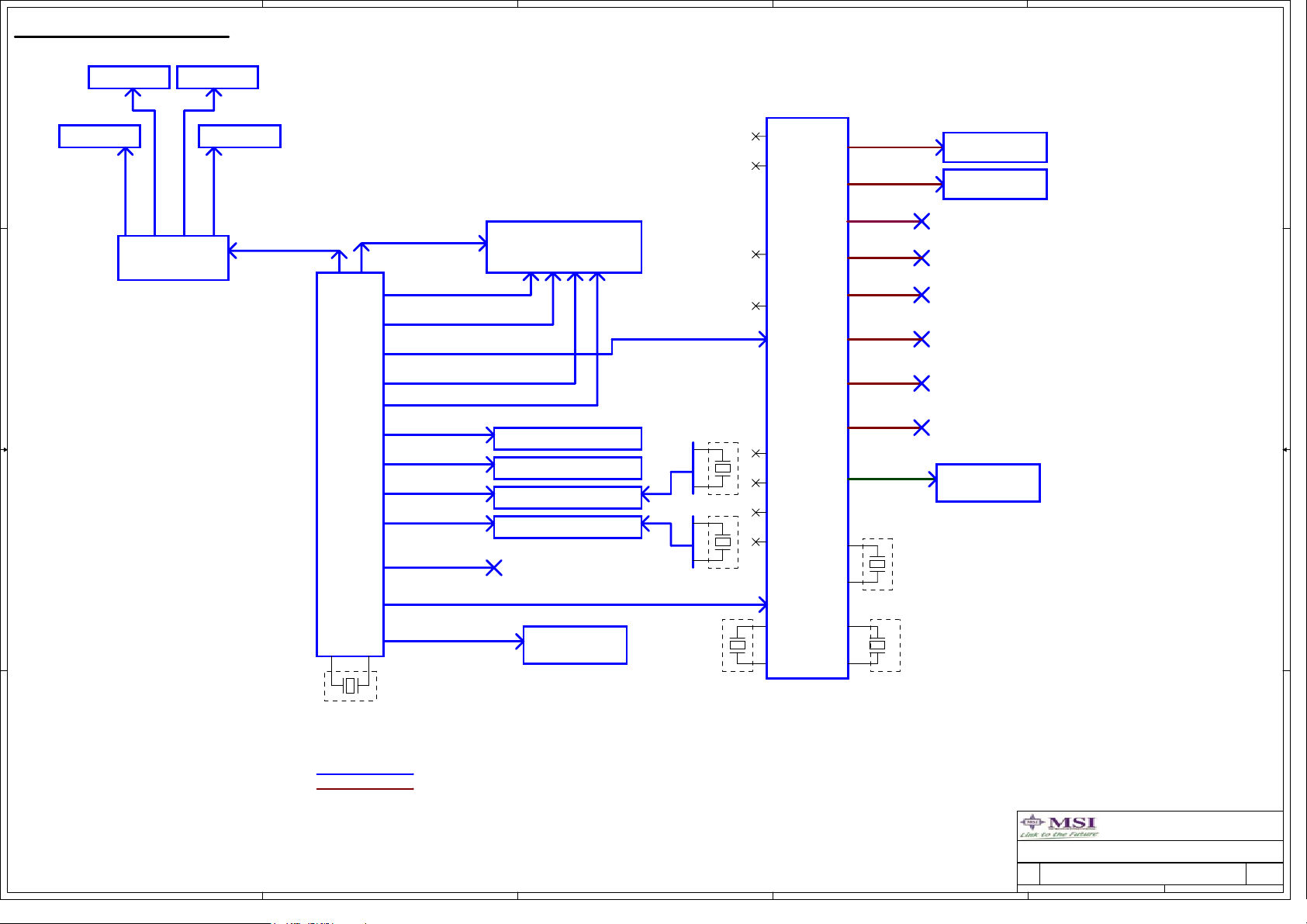

Clock Distribution

Power Deliver Chart

VRM ST L6740L 3+1 Phase

AMD Socket AM2 & AM2+

DDR II DIMM 1and DIMM2 1 & 2 & 3 & 4

DDR Terminatior

AMD - RS780 / RX780

AMD - SB700

DVI-I Connector

Clock Gen - Silego SLG8LP625

SATA / FAN / CPU Thermo

A A

LAN - Realtek RTL8111C

Super I/O - F71882FG

System Power-1& ACPI

System Power-2

IEEE1394 - JMicron JMB381

Azalia CODEC - Realtek ALC888

USB Connectors

PCI Express x16 & x1 Slot

PCI Express x8 Slot / SW

1

2

3

4

5

6

7 ~ 9

10 ~ 11

12

13 ~ 16

17 ~ 21

22

23

24

25

26

27

28

29

30

31

32

33

CPU:

AMD AM2+

AMD AMD Athlon 64 X2

AMD Athlon 64 FX

AMD Athlon 64

AMD Sempron CPUs

System Chipset:

AMD - RS780D (North Bridge)

AMD - SB750 (South Bridge)

On Board Chipset:

Super I/O - F71882FG

BIOS - SPI

Azalia CODEC - Realtek ALC888

LAN - Realtek RTL8111C

IEEE1394 - JMicron JMB381

Main Memory:

DDR II * 4 (Max 4GB)

Expansion Slots:

PCI Express X16 Slot * 1

PCI Express X8 Slot * 1

PCI Express X1 Slot * 2

PCI 2.3 Slot * 2

Intersil PWM:

Controller - Intersil ISL6323 4+1 Phase

PCI Slot 1 & 2

ATX & Front Panel

Auto BOM Manual

Side Port Memory

Power Wattage / Auto PSI

History

34

35

36

37

38

39

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

COVER SHEET

COVER SHEET

COVER SHEET

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

of

of

of

139Wednesday, May 28, 2008

139Wednesday, May 28, 2008

139Wednesday, May 28, 2008

5

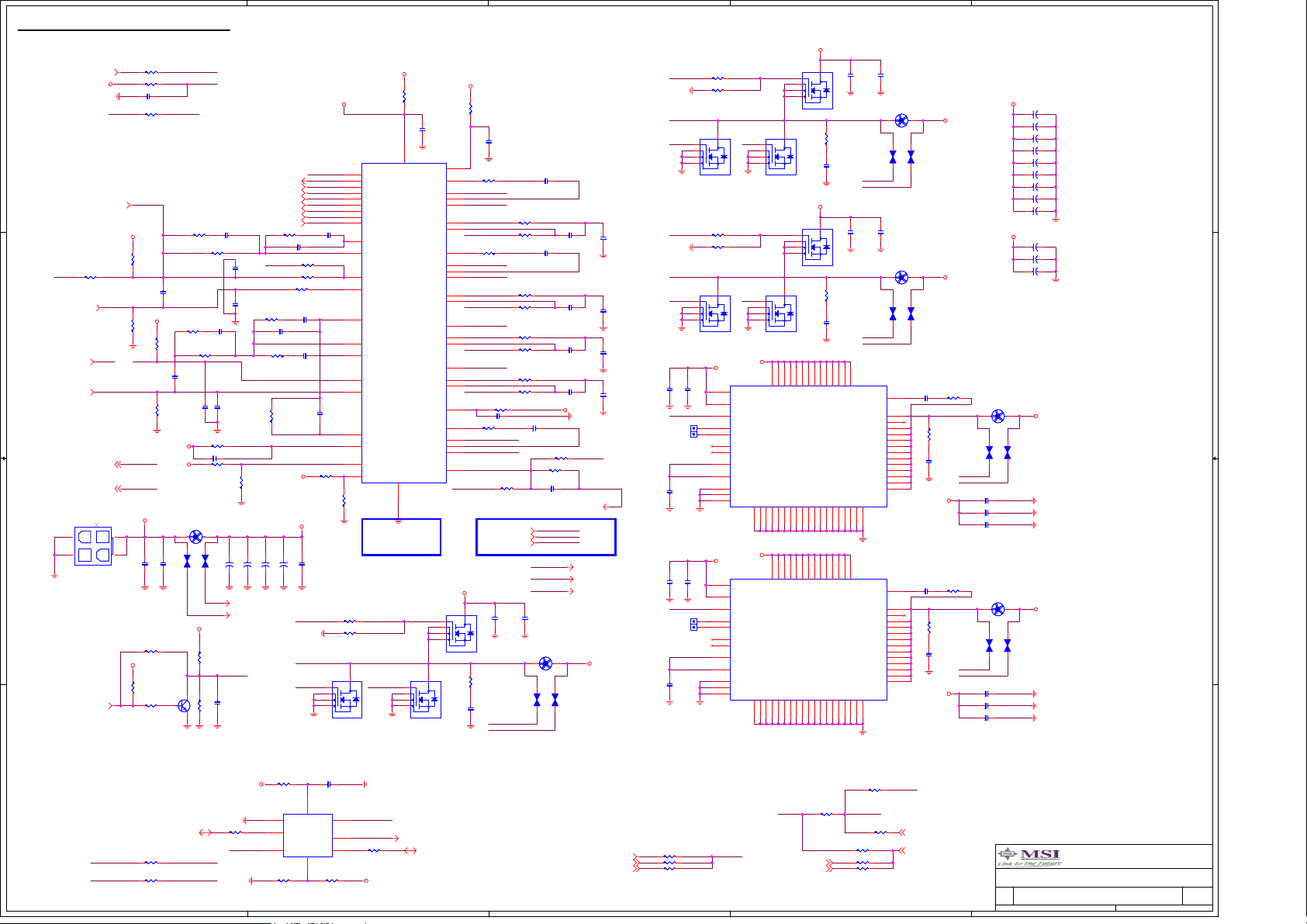

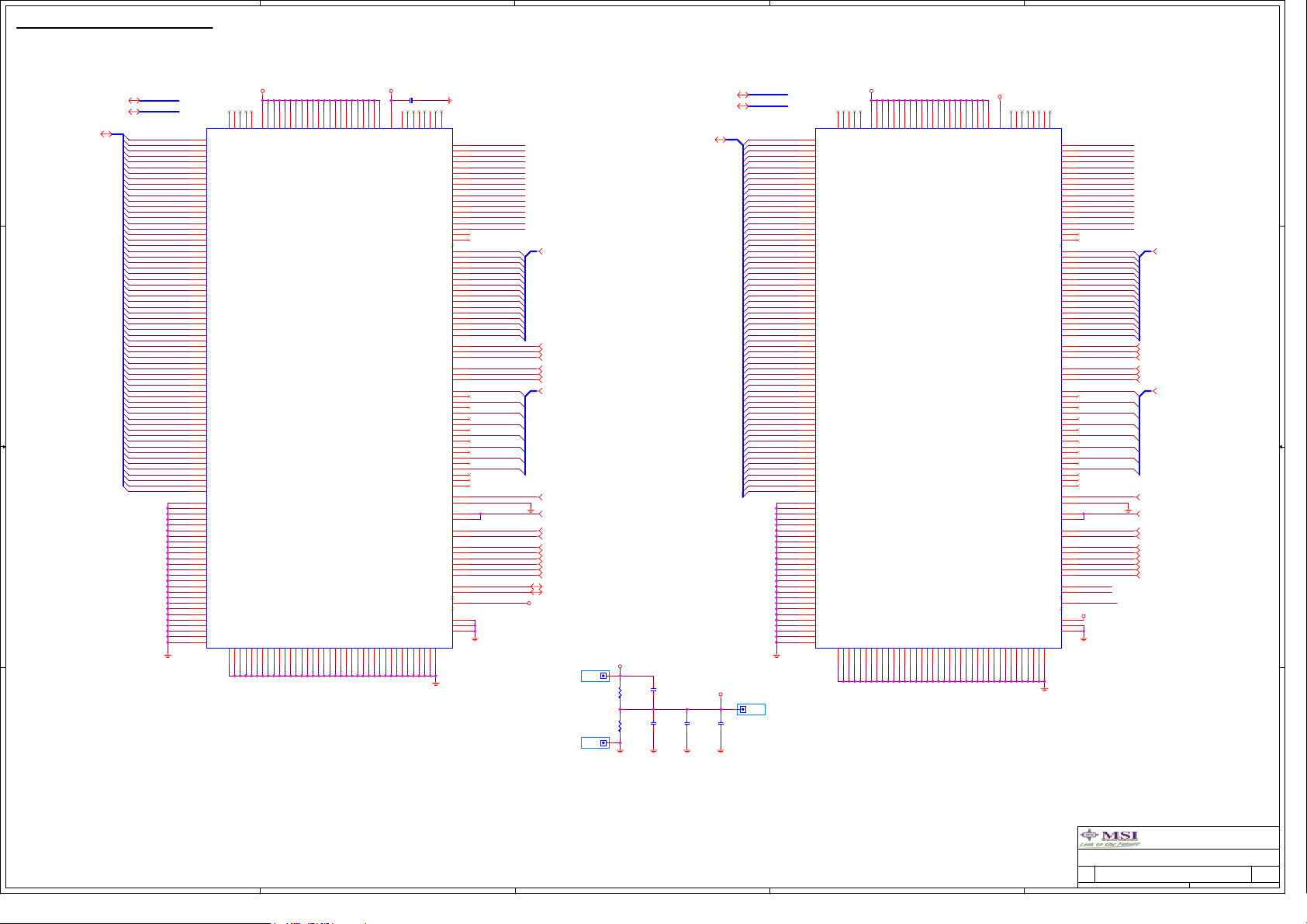

BLOCK Diagram

4

3

2

1

Project MS-7304 Block Diagram

DDRII 400,533,667,800

D D

Intersil

ISL6263 4+1

Phase

22

AMD

AM2/AM2g2

AM2 SOCKET

7,8,9

DVI CON

22

HyperTransport LINK

OUT

16x16 2.6GHZ(HT3)

IN

128bit

DDRII 400,533,667,800

128bit

UNBUFFERED

DDRII DIMM1

UNBUFFERED

DDRII DIMM2

DDRII FIRST LOGICAL DIMM

10

10

UNBUFFERED

DDRII DIMM3

UNBUFFERED

DDRII DIMM4

DDRII SECOND LOGICAL DIMM

11

11

SW

HDMI CON

PCIE GFX x8

C C

PCIE GFX x16

22

31

31

4X1 PCIE INTERFACE

SW

TMDS

PCIE x16

ATI NB - RS780D

HyperTransport LINK0 CPU I/F

1 16X PCIE VIDEO I/F

1 1X PCIE I/F

1 DVI-I

13,14,15,16

Gbit ETHERNET JMicron JM381

25

PCIE x1 SLOT*2

3125

A-LINK

4X PCIE

USB-4USB-5

30

30 30 30 30 30

USB-1USB-2USB-3

USB-0

REARREARREARREARREARREAR

USB 2.0

ATI SB - SB700

USB2.0 (10)

AZALIA

AZALIA CODEC

SATA2 (4 PORTS)

HD AUDIO HDR

USB-11

HDR

B B

USB-10

HDR

30

HDR HDR HDR HDR

30

USB-7USB-8USB-9

USB-6

AC97 2.3

30303030

HD AUDIO 1.0

ACPI 1.1

SPI I/F

SERIAL ATA 2.0

SPI Bus

SATA#0

24

SPI ROM 8M

PCI/PCI BRIDGE

PCI BUS

LPC BUS

SIO F71882

29

29

SATA#124SATA#224SATA#3

19

19

SATA#424SATA#5

24

ESATA

24

17,18,19,20,21

PCI SLOT 1

PCI SLOT 0

30 30

ATX CON &

DUAL POWER

A A

5

27

4

ACPI CONTROLLER

UPI

CPU CORE POWER

NB CORE POWER

27

3

6

CPU VLDT Power

RX780/RS780 CORE

POWER

PCIE & SB POWER

27

DDR2 DRAM POWER

2

27

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK Diagram

BLOCK Diagram

BLOCK Diagram

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

239Wednesday, May 28, 2008

239Wednesday, May 28, 2008

239Wednesday, May 28, 2008

of

of

1

of

5

4

3

2

1

GPIO Configuration

D D

C C

B B

PCI Config.

DEVICE MCP1 INT Pin REQ#/GNT#

PCI Slot 1

A A

PCI Slot 2

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PCI_INTA#

5

PREQ#0

PGNT#0

PREQ#1

PGNT#1

IDSEL

AD20

AD21

CLOCK

PCICLK0

PCICLK1

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

GPIO Configuration

GPIO Configuration

GPIO Configuration

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

1

339Wednesday, May 28, 2008

339Wednesday, May 28, 2008

339Wednesday, May 28, 2008

of

of

of

5

4

3

2

1

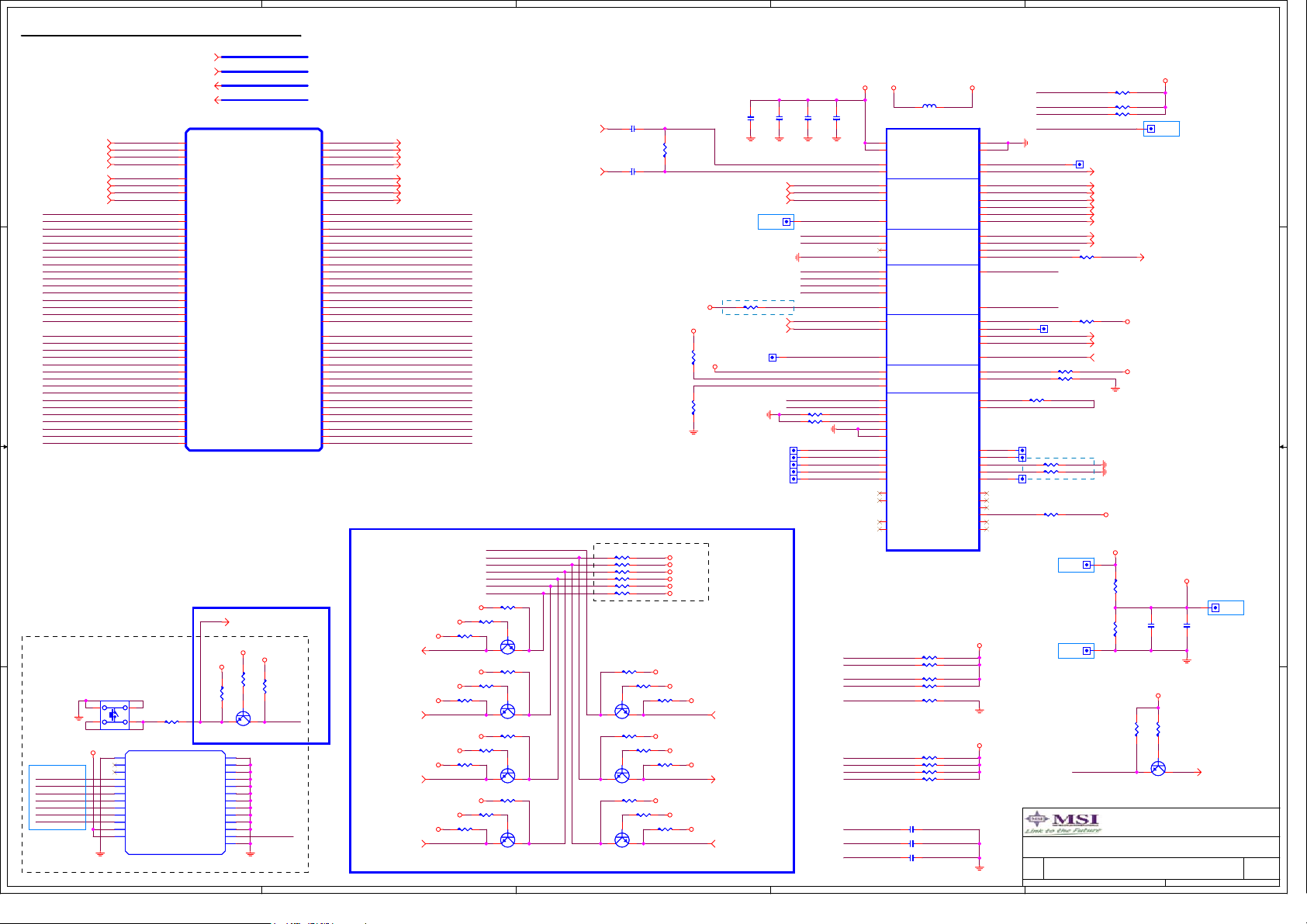

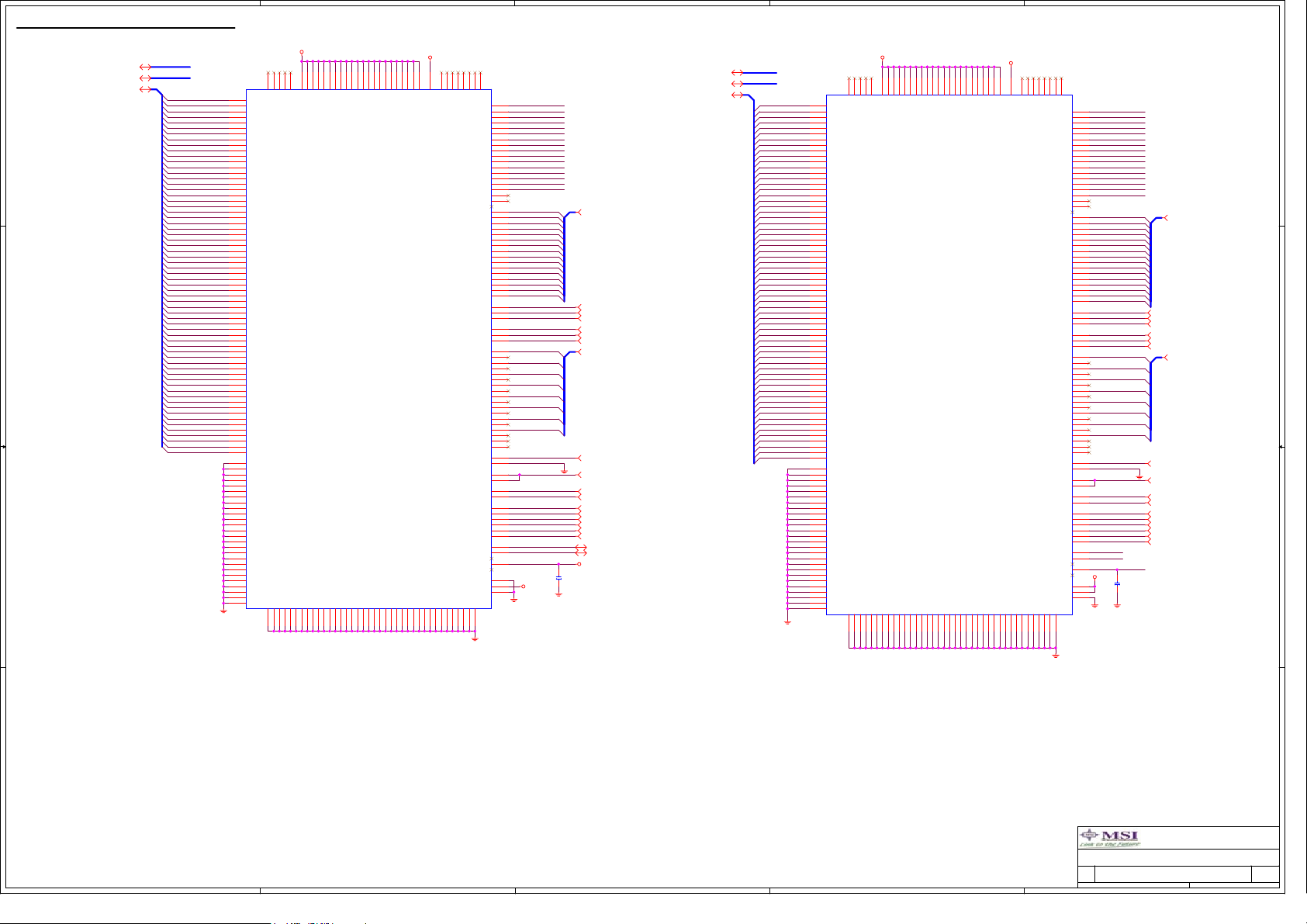

Clock Distribution Chart

DIMM3 DIMM4

D D

DIMM1 DIMM2

CPU_HT_CLK

NB_HT_CLK

AMD SB

SB700

3 PAIR MEM CLK

3 PAIR MEM CLK

3 PAIR MEM CLK

3 PAIR MEM CLK

AM2/AM2g2 CPU

AM2 SOCKET

C C

B B

1 PAIR CPU CLK

200MHZ

HT REFCLK

100MHz DIFF(RX780/RS780)

EXTERNAL

CLK GEN.

NB-OSCIN

14.318MHZ

NB ALINK PCIE CLK

100MHZ

SB ALINK PCIE CLK

100MHZ

NB GFX PCIE CLK

100MHZ

NB GPP PCIE CLK

100MHZ

(RX780)

PCIE GFX CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

PCIE GPP CLK

100MHZ

USB CLK

48MHZ

HWM CLK

48MHZ

AMD NB

RX780D

PCIE GFX SLOT 1 - 16 LANES

PCIE GPP SLOT 1 - 1 LANE

PCIE GBE LAN RTL8111C

PCI-e IEEE-1394 JMB381

HWM

F75388

25MHZ

OSC

INPUT

25MHz LAN

24.576MHz

IEEE-1394

25MHz SATA

NB_DISP_CLK

GPP_CLK3

PCIE_RCLK/

NB_LNK_CLK

SLT_GFX_CLK

GPP_CLK0

GPP_CLK1

GPP_CLK2

USB_CLK

25M_48M_66M_OSC

PCI CLK0

33MHZ

PCI CLK1

33MHZ

PCI CLK2

33MHZ

PCI CLK3

33MHZ

PCI CLK4

33MHZ

PCI CLK5

33MHZ

LPC_CLK0

33MHZ

LPC CLK1

33MHZ

SB_BITCLK

48MHZ

25MHz

32.768KHz

PCI SLOT 0 33MHz

PCI SLOT 1 33MHz

HD AUDIO

ALC 888

14.31818MHz

A A

5

External clock mode

Internal clock mode

4

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Clock Distribution Chart

Clock Distribution Chart

Clock Distribution Chart

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

439Wednesday, May 28, 2008

439Wednesday, May 28, 2008

439Wednesday, May 28, 2008

of

of

1

of

5

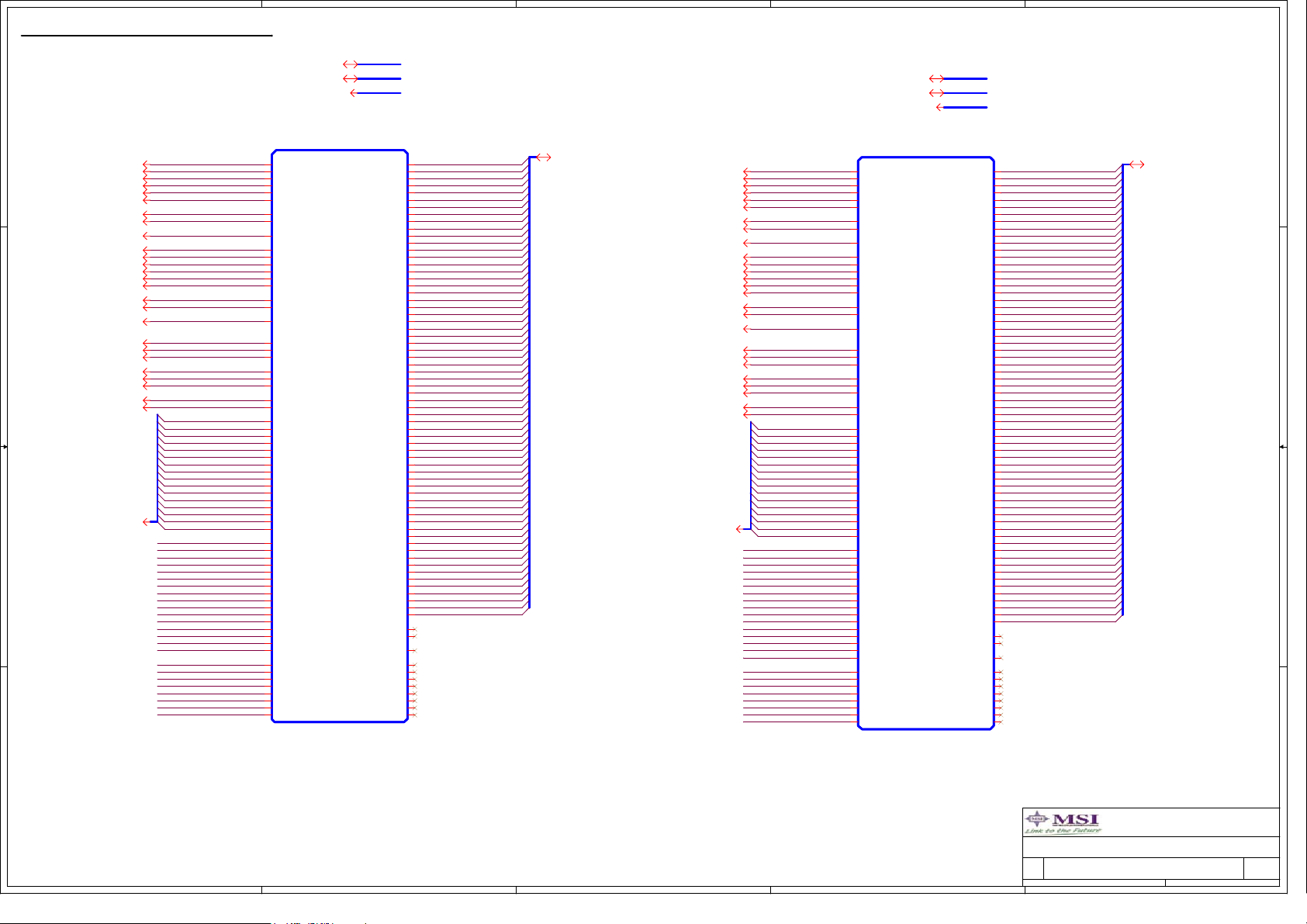

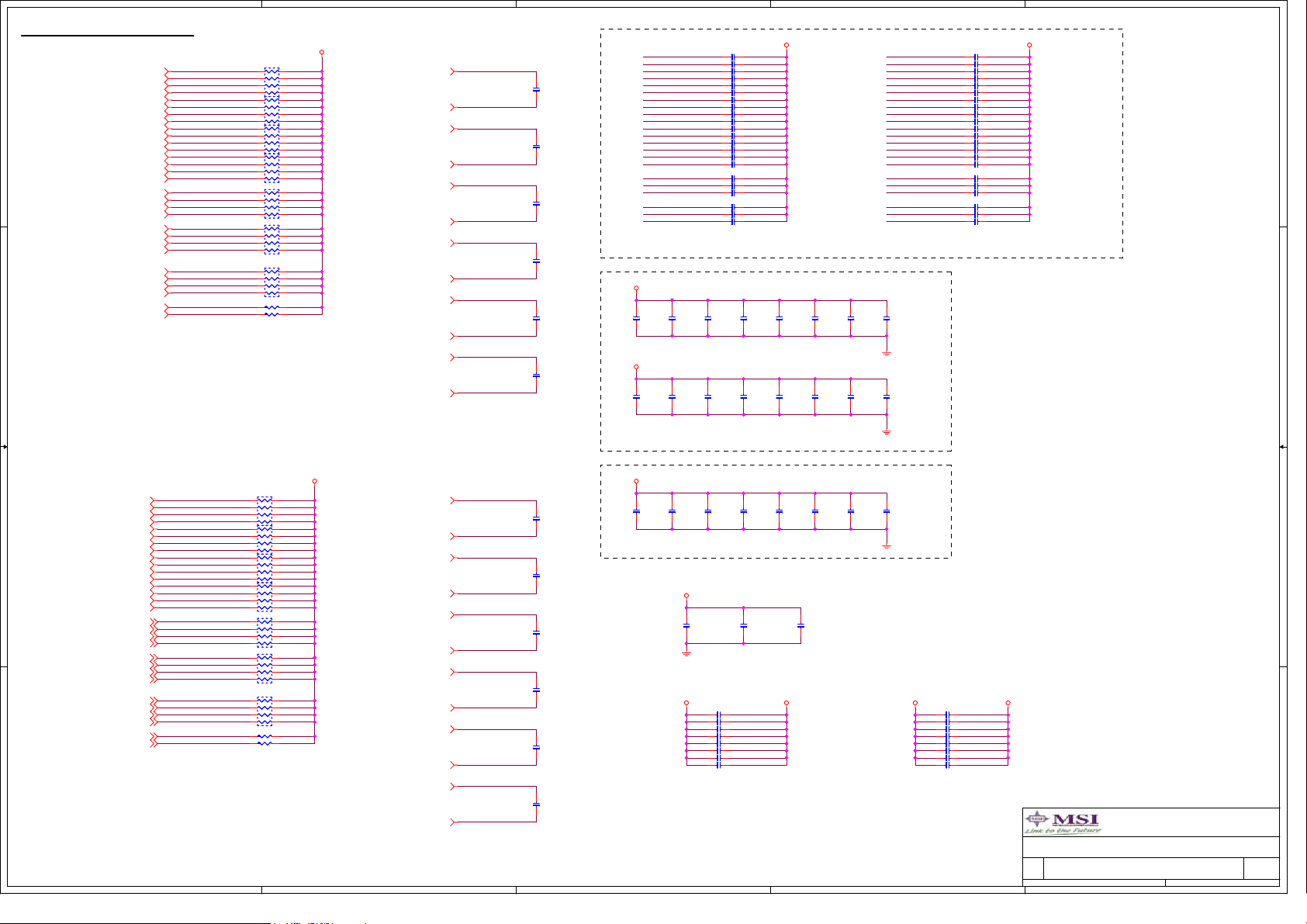

Power Deliver Chart

4

3

2

1

2.5V Shunt

Regulator

VRM SW

REGUALTOR

D D

ATX P/S WITH 1A STBY CURRENT

5V

5VSB

+/-5%

+/-5%

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PW

12V

+/-5%

5VDIMM Linear

REGULATOR

1.8V VDD SW

REGULATOR

1.8V VCC SW

REGULATOR

VDDA25 (S0, S1)

VCCP (S0, S1) / VCC_NB (S0, S1)

0.9V VTT_DDR

REGULATOR

1.1V VCC Linear

REGULATOR

1.2V VCC Linear

REGULATOR

VCC_DDR (S0, S1, S3)

VTT_DDR (S0, S1, S3)

DDRII DIMMX4

VDD MEM

12A

VTT_DDR

2A

NB_VCC1P1 (S0, S1)

VCC_1V2 (S0, S1)

+1.8V_S0 (S0, S1)

VCC3 (S0, S1)

C C

AMD AM2r2 CPU

VDDA 2.5V 0.2A

VDDCORE

0.8-1.55V

DDR2 MEM I/F

VDD MEM 1.8V

VTT MEM 0.9V

VLDT 1.2V

NB RS780/RX780

VDDHT/RX 1.1V

VDDHTTX 1.2V

VDDPCIE 1.1V

NB CORE VDDC

1.1V

VDDA18PCIE 1.8V

PLLs 1.8V

VDD18/VDD18_MEM

1.8V

VDD_MEM 1.8V/1.5V

AVDD 3.3V

110A

10A

2A

0.5A

1.2A

0.5A

2A

7A

0.9A

0.1A

0.01A

0.5A

0.135A

SB700

X4 PCI-E

VCC3_SB Linear

REGULATOR

VCC3_SB (S0, S1, S3, S5)

1.2V_SB Linear

REGULATOR

+1.2VSB (S0, S1)

VCC3_SB (S0, S1, S3, S5)

VCC3 (S0, S1)

+5VA Linear

B B

5VDUAL Linear

REGULATOR

REGULATOR

+5VA (S0, S1)

ATA I/O

ATA PLL

PCI-E PVDD

SB CORE

CLOCK

1.2V S5 PW

3.3V S5 PW

USB CORE I/O

3.3V I/O

AUDIO CODEC

3.3V CORE

5V ANALOG

0.8A

0.5A

0.01A

80mA

0.6A

0.22A

0.01A

0.2A

0.45A

0.1A

0.1A

5.0A

7.6A

0.5A

0.1A

X1 PCIE per

3.3V

12V

3.3Vaux

PCI Slot (per slot)

A A

5

5V

3.3V

12V

3.3VDual

-12V

0.375A

X16 PCIE per USB X4 FR

3.3V

12V

3.3VDual

3.0A

5.5A

0.1A

3.0A

0.5A

0.1A

4

VDD

5VDual

USB X6 RL

VDD

5VDual

3.0A2.0A

3

ENTHENET

3.3V (S3)

3.3V (S0, S1)

0.1A

0.5A

IEEE-1394 x1

3.3V (S0, S1)

12V (S0, S1) 1.1A

0.1A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Power Deliver Chart

Power Deliver Chart

Power Deliver Chart

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

1

539Wednesday, May 28, 2008

539Wednesday, May 28, 2008

539Wednesday, May 28, 2008

of

of

of

5

4

3

2

1

VRM ISL6323CRZ 4+1 Phase

VIN

5

Q78

Q78

4

3

2

1

C4.7u16Y1206

N-NTMFS4841NHT1G_SO8-RH

N-NTMFS4841NHT1G_SO8-RH

5

N-NTMFS4841NHT1G_SO8-RH

N-NTMFS4841NHT1G_SO8-RH

5

VIN8VIN9VIN10VIN11VIN12VIN13VIN14VIN15VIN16VIN17VIN18VIN19VIN

Dr.Mos

Dr.Mos

VIN8VIN9VIN10VIN11VIN12VIN13VIN14VIN15VIN16VIN17VIN18VIN19VIN

Dr.Mos

Dr.Mos

C4.7u16Y1206

R199

R199

2.2R1%0805

2.2R1%0805

C748

C748

C1000P50X0402

C1000P50X0402

VIN

5

Q83

Q83

4

3

2

1

C4.7u16Y1206

C4.7u16Y1206

R624

R624

2.2R1%0805

2.2R1%0805

C778

C778

C1000P50X0402

C1000P50X0402

C801

C801

C10u16Y1206

C10u16Y1206

PHASE11

ISEN1

C803

C803

PHASE22

ISEN2

59

20

BOOT

VIN_IN

VSWH_IN

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

PGND_IN

R2J20602NP_QFN56-RH

R2J20602NP_QFN56-RH

39

58

20

59

BOOT

VIN_IN

VSWH_IN

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

VSWH

PGND_IN

R2J20602NP_QFN56-RH

R2J20602NP_QFN56-RH

39

58

C750

C750

CH-0.25u40A0.65m-RH

CH-0.25u40A0.65m-RH

CHOKE3

CHOKE3

1 2

12

12

CP41CP41

CP40CP40

C779

C779

C10u16Y1206

C10u16Y1206

CH-0.25u40A0.65m-RH

CH-0.25u40A0.65m-RH

CHOKE4

CHOKE4

1 2

12

12

CP44CP44

CP43CP43

C0.1u16X

C0.1u16X

C39

C39

5

57

21

40

41

42

43

44

45

46

47

48

49

50

C0.1u16X

C0.1u16X

C40

C40

5

57

21

40

41

42

43

44

45

46

47

48

49

50

VCCP

VCCP

VCCP

VCCP

R622 0RR622 0R

R660

R660

3.3R0805

3.3R0805

C808

C808

C2200p50X-RH

C2200p50X-RH

VIN

R629 0RR629 0R

R661

R661

3.3R0805

3.3R0805

C811

C811

C2200p50X-RH

C2200p50X-RH

VIN

VCCP

CPU_VDDNB

CH-0.25u40A0.65m-RH

CH-0.25u40A0.65m-RH

CHOKE16

CHOKE16

1 2

12

CP49CP49

PHASE33

ISEN3

C754 C10u16Y1206C754 C10u16Y1206

C747 C10u16Y1206C747 C10u16Y1206

C753 X_C1U16X5C753 X_C1U16X5

CH-0.25u40A0.65m-RH

CH-0.25u40A0.65m-RH

CHOKE17

CHOKE17

1 2

12

CP51CP51

PHASE44

ISEN4

C772 C10u16Y1206C772 C10u16Y1206

C749 C10u16Y1206C749 C10u16Y1206

C761 X_C1U16X5C761 X_C1U16X5

+

+

EC69

EC69

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC70

EC70

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC71

EC71

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC72

EC72

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC73

EC73

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC74

EC74

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC75

EC75

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC76

EC76

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC77

EC77

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC78

EC78

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC79

EC79

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

+

+

EC80

EC80

1 2

CD820u2.5Fp-1

CD820u2.5Fp-1

VCCP

VCCP

12

CP48CP48

VCCP

VCCP

12

CP50CP50

2.2R0805

2.2R0805

7X7 QFN

U2

U2

24

EN

37

VDDPWRGD

34

PWROK

9

VID5

8

VID4

7

VID3/SVC

6

VID2/SVD

5

VID1/SEL

4

VID0/VFIXEN

48

COMP_NB

1

FB_NB

2

VSEN_NB

3

RGND_NB

18

COMP

17

FB

15

RCOMP

13

VSEN

12

RGND

19

APA

16

RESET

14

OFS

11

FS

BOTTOM PAD

CONNECT TO GND

Through 8 VIAs

5

LGATE_NB

VCC5

R80

R80

C34

C34

C4.7U10Y0805

C4.7U10Y0805

10

29

PVCC1_2

VCC

31

BOOT1

32

UGATE1

33

PHASE1

30

LGATE1

20

ISEN1+

21

ISEN1-

27

BOOT2

26

UGATE2

25

PHASE2

28

LGATE2

22

ISEN2+

23

ISEN2-

35

PWM3

44

ISEN3+

43

ISEN3-

36

PWM4

46

ISEN4+

45

ISEN4-

42

PVCC_NB

40

BOOT_NB

39

UGATE_NB

38

PHASE_NB

41

LGATE_NB

47

ISEN_NB

GND

49

ISL6323CRZ_QFN48-RH

ISL6323CRZ_QFN48-RH

Q86

Q86

4

3

2

1

N-NTMFS4841NHT1G_SO8-RH

N-NTMFS4841NHT1G_SO8-RH

5

Q84

Q84

4

3

2

1

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

+12VIN

R84

R84

2.2R0805

2.2R0805

C35

C35

C1U16X5

C1U16X5

R72 0R0402R72 0R0402

R88

R88

4.32KR1%0402

4.32KR1%0402

R166 0R0402R166 0R0402

R144

R144

4.32KR1%0402

4.32KR1%0402

R104 0R0402R104 0R0402

R103

R103

4.32KR1%0402

4.32KR1%0402

R120 0R0402R120 0R0402

R150

R150

4.32KR1%0402

4.32KR1%0402

R163

R163

5.6KR1%0402

5.6KR1%0402

ISEN3-38

ISEN4-38

VCCPB38

C804

C804

PHASE_NB_A

ISEN_NB_A

C796 C0.1U25XC796 C0.1U25X

C154

C154

C0.1u16X0402-2

C0.1u16X0402-2

C262 C0.1U25XC262 C0.1U25X

C131

C131

C0.1u16X0402-2

C0.1u16X0402-2

C124

C124

C0.1u16X0402-2

C0.1u16X0402-2

C739

C739

C0.1u16X0402-2

C0.1u16X0402-2

C108 C0.1U25XC108 C0.1U25X

R194 X_0R0402R194 X_0R0402

R140 X_6.2KR1%0402R140 X_6.2KR1%0402

V2

C132

C132

C0.1u16X0402-2

C0.1u16X0402-2

ISEN3ISEN4VCCPB

V1

V2

V3

C805

C805

C10u16Y1206

C10u16Y1206

CH-0.5u40A0.93m-RH

CH-0.5u40A0.93m-RH

CHOKE6

CHOKE6

1 2

12

12

CP57CP57

CP56CP56

ISEN1ISEN1+

ISEN2ISEN2+

ISEN3

ISEN4ISEN4+

+12VIN

NB_FB

ISEN_NB_A38

V1 38

V2 38

V3 38

CPU_VDDNB

CPU_VDDNB

R139 2.2R1%0805R139 2.2R1%0805

U_G1

PHASE1

L_G1

ISEN1PHASE11

R105 2.2R1%0805R105 2.2R1%0805

U_G2

PHASE2

L_G2

ISEN2PHASE22

PWM3

ISEN3+

ISEN3PHASE33

PWM4

ISEN4PHASE44

R110 2.2R1%0805R110 2.2R1%0805

C66 C1U25X0805C66 C1U25X0805

R100

R100

2.2R1%0805

2.2R1%0805

UGATE_NB

PHASE_NB

LGATE_NB

PHASE_NB_A ISEN_NB_A

VIN

5

C4.7u16Y1206

C4.7u16Y1206

R627

R627

2.2R1%0805

2.2R1%0805

C781

C781

C1000P50X0402

C1000P50X0402

C37

C37

C100

C100

C59

C59

C259

C259

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402

U_G1

R201 1R0805R201 1R0805

R200 10KR0402R200 10KR0402

PHASE1

L_G1

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

U_G2

PHASE2

L_G2

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

C806

C806

C809

C809

C1U25X0805

C1U25X0805

PWM3

TP58TP58

TP57TP57

C807

C807

C1U25X0805

C1U25X0805

PWM4

TP60TP60

TP59TP59

C810

C810

C1u25Y0805

C1u25Y0805

C1u25Y0805

C1u25Y0805

Q79

Q79

4

3

2

1

R625 1R0805R625 1R0805

R623 10KR0402R623 10KR0402

Q82

Q82

4

3

2

1

C774

C1U25X0805

C774

C1U25X0805

C775

C1U25X0805

C775

C1U25X0805

5

5

VIN

U22

U22

4

3

56

7

52

2

53

55

54

6

51

1

VIN

U26

U26

4

3

56

7

52

2

53

55

54

6

51

1

Q80

Q80

L_G1

4

3

2

1

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

Q81

Q81

L_G2

4

3

2

1

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

VIN

VCIN

VLDRV

PWM

GH

GL

NC

NC

DISBL#

Reg5V

CGND

CGND

CGND

PGND22PGND23PGND24PGND25PGND26PGND27PGND28PGND29PGND30PGND31PGND32PGND33PGND34PGND35PGND36PGND37PGND38PGND

VIN

VCIN

VLDRV

PWM

GH

GL

NC

NC

DISBL#

Reg5V

CGND

CGND

CGND

PGND22PGND23PGND24PGND25PGND26PGND27PGND28PGND29PGND30PGND31PGND32PGND33PGND34PGND35PGND36PGND37PGND38PGND

VCC3

ISEN_NB_B

100R0402

100R0402

100R0402

100R0402

VCCPA

12V138

12V238

5

GNDGND

GNDGND

12V

12V

12V

12V

R86 300R0402R86 300R0402

R6 4.7KR0402R6 4.7KR0402

C1 C0.1u16X0402-2C1 C0.1u16X0402-2

R207 X_0R0402R207 X_0R0402

CPU_VDDNB

R154

R154

X_C0.1U16Y0402

X_C0.1U16Y0402

R146

R146

R12

R12

100R0402

100R0402

VCCPB

R155

R155

100R0402

100R0402

12V1

12V2

+12VIN

3

4

R52 X_0R0402R52 X_0R0402

VCC5_SB

R17

R17

4.7KR0402

4.7KR0402

R16

R16

4.7KR0402

4.7KR0402

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

CPU_CORE_TYPE7,38

D D

6262_VSEN_NB38

PWM_VNB

R193 0R0402R193 0R0402

V_GND7

C C

B B

COREFB+7

COREFB-7

JPWR2

JPWR2

1

2

PWRCONN4P_CREAM-RH-1

PWRCONN4P_CREAM-RH-1

VCORE_EN#27

CPU_VID1

VRM_GD

NB_FB

R131

R131

X_470R1%0402

X_470R1%0402

R143

R143

360R1%0402

360R1%0402

6262_VSEN_NB

C173

C173

VCCP

X_470R1%0402

X_470R1%0402

R138

R138

X_C1000P50X0402

X_C1000P50X0402

560R1%0402-RH

560R1%0402-RH

R159

R159

C73

C73

X_C0.1U16Y0402

X_C0.1U16Y0402

C38

C38

X_C0.1U16Y0402

X_C0.1U16Y0402

R118 56KR1%0402R118 56KR1%0402

5V

C843 C100P50N0402C843 C100P50N0402

R167 59KR1%0402R167 59KR1%0402

5V

CHOKE7 CH-1.2u25A3.5m-RHCHOKE7 CH-1.2u25A3.5m-RH

1 2

C251

X_C0.01u25X0402

C251

X_C0.01u25X0402

C802

C4.7u16Y1206

C802

C4.7u16Y1206

12

CP53CP53

+12VIN

R8

R7

C

C

B

B

Q1

Q1

E

E

X_C680P50X0402

X_C680P50X0402

C49

C49

V3 NB_FB

C44

C44

X_C0.1U16Y0402

X_C0.1U16Y0402

C215

C215

X_C0.1U16Y0402

X_C0.1U16Y0402

1.2KR1%0402

1.2KR1%0402

R70

R70

C87

C87

V1

R165

R165

1.3KR1%0402

1.3KR1%0402

C218

C218

X_C0.1U16Y0402

X_C0.1U16Y0402

R85

R85

X_10KR0402

X_10KR0402

EC20

CD1000U16EL20-2+EC20

CD1000U16EL20-2

EC26

CD1000U16EL20-2+EC26

CD1000U16EL20-2

12

+

+

12

12

CP52CP52

12V2

12V2 38

12V1

12V1 38

10KR1%0402R810KR1%0402

H:2V

L:0.8V

PWM_EN

3.6KR1%0402R73.6KR1%0402

C201

C0.1U25X

C201

C0.1U25X

VRM_GD27

VRM_PWROK15

CPU_VID57

CPU_VID47

CPU_VID37

CPU_VID27

CPU_VID17

CPU_VID07

R160

R160

1.2KR1%0402

1.2KR1%0402

C799 C10P50N0402C799 C10P50N0402

ISEN_NB_A

R151 0R0402R151 0R0402

R148 X_0R0402R148 X_0R0402

R157 0R0402R157 0R0402

C0.01U16X0402

C0.01U16X0402

1 2

C244 C33P50N0402C244 C33P50N0402

C797 C0.01U16X0402C797 C0.01U16X0402

COREFB-

R19

R19

4.99KR1%0402

4.99KR1%0402

5V

VIN

EC6

X_CD1000U16EL20-2+EC6

X_CD1000U16EL20-2

EC10

CD1000U16EL20-2+EC10

CD1000U16EL20-2

+

+

12

12

UGATE_NB

PHASE_NB

LGATE_NB

N-NTMFS4837NHT1G_SO8-RH

N-NTMFS4837NHT1G_SO8-RH

PWM_EN

CPU_VID1

C0.01U16X0402

C0.01U16X0402

1 2

C800

C800

ISEN_NB_B

6262_RGND_NB

C798

C798

12

C0.1U16Y0402

C0.1U16Y0402

C85

C85

VRM_SET

OFS

R145

R145

X_100KR0402

X_100KR0402

R183

R183

120KR1%0402

120KR1%0402

C246

C0.1U16Y0402

C246

C0.1U16Y0402

4

3

2

1

5V

R628 1R0805R628 1R0805

R626 10KR0402R626 10KR0402

Q85

Q85

R878 2.2RR878 2.2R

VCC5

A A

R526 0R0402R526 0R0402

6262_VSEN_NB

6262_RGND_NB

SDATA10,11,18,22,23,25,27,38

R646 X_0R0402R646 X_0R0402

R647 X_0R0402R647 X_0R0402

5

6262_VNB

6262_VNB

6262_VNB

UP6262M8_SOT23-8-RH

UP6262M8_SOT23-8-RH

X_1KR0402

X_1KR0402

R548

R548

C825 C0.1U25XC825 C0.1U25X

5V

0x60:RH=10K,RL=NC

1

U106

U106

3

GND

VCC

4

SDA

8

OUT1

BUS_SEL

2

7

OUT2

6

OUT3

5

SCL

R662 10KR0402R662 10KR0402

6262_VCORE

V_1P5_FB

R547 0R0402R547 0R0402

VCC5

4

V_1P5_FB 27

SCLK 10,11,18,22,23,25,27,38

R337 0R0402R337 0R0402

V_NB7

R642 X_0R0402R642 X_0R0402

OCV126

R643 X_0R0402R643 X_0R0402

OCV226

3

PWM_VNB

R641

R641

X_0R0402

X_0R0402

OCV326

OCV426

R648

R648

X_0R0402

X_0R0402

VCCPBVCCPA

R639

R639

0R0402

0R0402

R640

R640

0R0402

0R0402

R580 0R0402R580 0R0402

R638 0R0402R638 0R0402

2

6262_VCORE

VSO 26

VSI 26

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

C

C

C

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

VRM ISL6323CRZ 4+1 Phase

VRM ISL6323CRZ 4+1 Phase

VRM ISL6323CRZ 4+1 Phase

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

1

639Wednesday, May 28, 2008

639Wednesday, May 28, 2008

639Wednesday, May 28, 2008

of

of

of

5

4

3

2

1

CPU AM2 HT I/F,CTRL&DEBUG

CPU1A

CPU1A

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

VCC3_SB

R609 10KR0402R609 10KR0402

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

IMC_CRST_L 18

+1.8V_S0

+1.8V_S0

R602 10KR0402R602 10KR0402

R610

R610

10KR0402

10KR0402

B

B

LDT_RST#

C

C

E

E

Q4

Q4

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

2

4

6

8

10

12

14

16

18

20

22

IMC_CRST_L

24

26

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CLKOUT_H1 13

HT_CLKOUT_L1 13

HT_CLKOUT_H0 13

HT_CLKOUT_L0 13

HT_CTLOUT_H1 13

HT_CTLOUT_L1 13

HT_CTLOUT_H0 13

HT_CTLOUT_L0 13

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

IMC_TDI18

IMC_TRST_L18

IMC_TDO18

4

VCC3

VCC3

VCC3

VCC3

+1.8V_S0

IMC_TDI

+1.8V_S0

IMC_TRST_L

+1.8V_S0

IMC_TDO

+1.8V_S0

IMC_TMS

CPU_DBREQ_L

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST_L

CPU_TDO

R448 10KR0402R448 10KR0402

+1.8V_S0

R430 10KR0402R430 10KR0402

R508 10KR0402R508 10KR0402

R511 10KR0402R511 10KR0402

+1.8V_S0

R512 10KR0402R512 10KR0402

R509 10KR0402R509 10KR0402

R514 10KR0402R514 10KR0402

+1.8V_S0

R515 10KR0402R515 10KR0402

R513 10KR0402R513 10KR0402

R517 10KR0402R517 10KR0402

+1.8V_S0

R518 10KR0402R518 10KR0402

R516 10KR0402R516 10KR0402

VDDA25

C75

C75

C90

C81

C81

C71

C4.7U10Y0805

C4.7U10Y0805

LDT_RST#15,17

For AMD

TP31TP31

COREFB+6

COREFB-6

TP6TP6

C71

C1u16Y

C1u16Y

CPU_DBREQ_L

CPU_VTT_SENSE

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

CPU_TEST25_H

CPU_TEST25_L

R124 300R0402R124 300R0402

R119 300R0402R119 300R0402

TP21TP21

TP22TP22

TP25TP25

TP20TP20

TP27TP27

C79

C79

C3900P50X

CPU_CLK23

CPU_CLK#23

C3900P50X

C88

C88

C3900P50X

C3900P50X

C0.1U16Y0402

R130

R130

169R1%0402

169R1%0402

2007-12-21 AMD Update

Phenom-TestNoise-Dec19-2007-MSI.pdf

VCC_DDR

C0.1U16Y0402

LDT_PWRGD17

LDT_STOP#15,17

R220 300R0402R220 300R0402

VCC_DDR

R177

R177

R173

R173

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

+1.8V_S0

+1.8V_S0

R59410KR0402 R59410KR0402

+1.8V_S0

+1.8V_S0

R59710KR0402 R59710KR0402

+1.8V_S0

+1.8V_S0

R60010KR0402 R60010KR0402

CPU_M_VREF

VCC3

IMC_DBREQ_L 18

VCC3

IMC_DBRDY 18

VCC3

IMC_TCK 18IMC_TMS18

39.2R1%0402

39.2R1%0402

39.2R1%0402

39.2R1%0402

Reserve for debug

R603 X_1KR0402R603 X_1KR0402

R604 X_1KR0402R604 X_1KR0402

R605 X_1KR0402R605 X_1KR0402

R606 X_1KR0402R606 X_1KR0402

R607 X_1KR0402R607 X_1KR0402

R608 X_1KR0402R608 X_1KR0402

B

B

C

C

E

E

Q70N-MMBT3904_NL_SOT23

Q70N-MMBT3904_NL_SOT23

RN ???

R59510KR0402 R59510KR0402

R59310KR0402 R59310KR0402

B

B

C

C

E

E

Q71N-MMBT3904_NL_SOT23

Q71N-MMBT3904_NL_SOT23

B

B

C

C

E

E

Q74 N-MMBT3904_NL_SOT23

Q74 N-MMBT3904_NL_SOT23

R59810KR0402 R59810KR0402

R59610KR0402 R59610KR0402

B

B

C

C

E

E

Q72N-MMBT3904_NL_SOT23

Q72N-MMBT3904_NL_SOT23

B

B

C

C

E

E

Q75 N-MMBT3904_NL_SOT23

Q75 N-MMBT3904_NL_SOT23

R60110KR0402 R60110KR0402

R59910KR0402 R59910KR0402

B

B

C

C

E

E

Q73N-MMBT3904_NL_SOT23

Q73N-MMBT3904_NL_SOT23

B

B

C

C

E

E

Q76 N-MMBT3904_NL_SOT23

Q76 N-MMBT3904_NL_SOT23

3

C90

C3300P50X0402

C3300P50X0402

CPUCLKIN

CPUCLKIN#

LDT_PWRGD

LDT_STOP#

LDT_RST#

CPU_PRESENT_L

CPU_SIC

CPU_SID

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

COREFB+

COREFB-

CPU_SID

CPU_SIC

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL4

AK4

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AH7

AJ6

LDT_STOP#

LDT_RST#

LDT_PWRGD

PROCHOT_L

HTREF1

HTREF2

LDT_RST#

CPU1D

CPU1D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

ALERT_L

SA0

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

R184 X_1KR0402R184 X_1KR0402

R182 1KR0402R182 1KR0402

R188 1KR0402R188 1KR0402

R125 510R0402R125 510R0402

R127 510R0402R127 510R0402

R108 300R0402R108 300R0402

R107 300R0402R107 300R0402

R117 300R0402R117 300R0402

R112 300R0402R112 300R0402

C207 C1000P50X0402C207 C1000P50X0402

C208 C1000P50X0402C208 C1000P50X0402

C64 X_C1000P50X0402C64 X_C1000P50X0402

2

VDDA25VDDA_25

L1

L1

47n300mA_0805-RH-2

47n300mA_0805-RH-2

MISC

MISC

KEY/VSS1

KEY/VSS2

PLATFORM_TYPE

CORE_TYPE

VID(5)

VID(4)

SVC/VID(3)

SVD/VID(2)

PVIEN/VID(1)

VID(0)

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

TDO

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

VCC_DDR

VCC_DDR

CPU_CORE_TYPE

CPU_VID3

CPU_VID2

R115 300R0402R115 300R0402

R114 1KR0402R114 1KR0402

R113 1KR0402R113 1KR0402

CPU_CORE_TYPE

H22

AE9

CPU_PF_TYPE

F2

CPU_CORE_TYPE

G5

CPU_VID5

D2

CPU_VID4

D1

CPU_VID3

C1

CPU_VID2

E3

CPU_VID1

E2

CPU_VID0

E1

AG9

AG8

CPU_THRIP_L#

AK7

PROCHOT_L

AL7

CPU_TDO

AK10

CPU_DBRDY

B6

AK11

AL11

G4

G3

F1

HTREF1

V8

HTREF2

V7

R132 80.6R1%0402R132 80.6R1%0402

C11

D11

Keep trace < 1" from CPU.

TP30TP30

AK8

TP26TP26

AH8

R213 300R0402R213 300R0402

AJ9

R176 300R0402R176 300R0402

AL8

AJ8

TP28TP28

J10

H9

AK9

R180 300R0402R180 300R0402

AK5

G7

D4

TP7TP7

CPU_CORE_TYPE 6,38

CPU_VID5 6

CPU_VID4 6

CPU_VID3 6

CPU_VID2 6

CPU_VID1 6

CPU_VID0 6

THERMDC_CPU 26

THERMDA_CPU 26

R111 0R0402R111 0R0402

R178 100R0402R178 100R0402

TP9TP9

PSI#

R187 44.2R1%R187 44.2R1%

R189 44.2R1%R189 44.2R1%

2007-12-21 AMD Update

Phenom-TestNoise-Dec19-2007-MSI.pdf

For AMD

TP4TP4

For AMD

TP5TP5

V_NB 6

V_GND 6

PSI# 38

VCC_DDR

300R0402

300R0402

CPU_THRIP_L#

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

CPU AM2 HT I/F,CTRL&DEBUG

CPU AM2 HT I/F,CTRL&DEBUG

CPU AM2 HT I/F,CTRL&DEBUG

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

VCC_DDR

For AMD

CPU_PROCHOT# 17

VCC_DDR

VCC_1V2

VCC_DDR

R123

R123

15R1%

15R1%

R122

R122

15R1%

15R1%

VCC_DDR

R185

R185

E

E

Q32

Q32

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

1

TP24TP24

CPU_M_VREF

C83

C83

C0.1U16Y0402

C0.1U16Y0402

R186

R186

4.7KR0402

4.7KR0402

B

B

C

C

For AMD

TP23TP23

C91

C91

C1000P50X0402

C1000P50X0402

CPU_THRIP# 18

of

of

of

739Wednesday, May 28, 2008

739Wednesday, May 28, 2008

739Wednesday, May 28, 2008

HT_CADIN_H[15..0]13

HT_CADIN_L[15..0]13

HT_CADOUT_H[15..0]13

HT_CADOUT_L[15..0]13

D D

HT_CLKIN_H113

HT_CLKIN_L113

HT_CLKIN_H013

HT_CLKIN_L013

HT_CTLIN_H113

HT_CTLIN_L113

HT_CTLIN_H013

HT_CTLIN_L013

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

C C

B B

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

AMD REQUEST

SW1 X_SW-TACTB1-4PS

SW1 X_SW-TACTB1-4PS

1 2

12

12

3 4

34

34

VCC_DDR

For AMD

CPU_DBREQ_L

A A

CPU_DBRDY

CPU_TCK

CPU_TMS

CPU_TDI

CPU_TRST_L

CPU_TDO

11

13

15

17

19

21

23

X_100R0402

X_100R0402

R3

R3

J1

J1

1

3

5

7

9

KEY

KEY

X_H2X13[25]_black

X_H2X13[25]_black

5

5

4

3

2

1

CPU AM2 DDR MEMORY I/F

MEM_MA_DQS_L[7..0]10,11

MEM_MA_DQS_H[7..0]10,11

MEM_MA_DM[7..0]10,11

D D

CPU1B

CPU1B

MEMORY INTERFACE A

MEM_MA0_CLK_H210,12

MEM_MA0_CLK_L210,12

MEM_MA0_CLK_H110,12

MEM_MA0_CLK_L110,12

MEM_MA0_CLK_H010,12

MEM_MA0_CLK_L010,12

MEM_MA0_CS_L110,12

MEM_MA0_CS_L010,12

MEM_MA0_ODT010,12

MEM_MA1_CLK_H211,12

MEM_MA1_CLK_L211,12

MEM_MA1_CLK_H111,12

MEM_MA1_CLK_L111,12

MEM_MA1_CLK_H011,12

MEM_MA1_CLK_L011,12

MEM_MA1_CS_L111,12

MEM_MA1_CS_L011,12

MEM_MA1_ODT011,12

C C

B B

MEM_MA_CAS_L10,11,12

MEM_MA_WE_L10,11,12

MEM_MA_RAS_L10,11,12

MEM_MA_BANK210,11,12

MEM_MA_BANK110,11,12

MEM_MA_BANK010,11,12

MEM_MA_CKE111,12

MEM_MA_CKE010,12

MEM_MA_ADD[15..0]10,11,12

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

MEM_MA1_CLK_H2

MEM_MA1_CLK_L2

MEM_MA1_CLK_H1

MEM_MA1_CLK_L1

MEM_MA1_CLK_H0

MEM_MA1_CLK_L0

MEM_MA1_CS_L1

MEM_MA1_CS_L0

MEM_MA1_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

G19

AC25

AA24

AC28

AE20

AE19

G20

G21

W27

AD27

AA25

AC27

AB25

AB27

AA26

AA27

M25

M27

AC26

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

G15

AF15

AF19

AJ25

AH29

H19

U27

U26

V27

N25

Y27

L27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

D29

C29

C25

D25

E19

F19

F15

B29

E24

E18

H15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DATA[63..0] 10,11

MEM_MB0_CLK_H210,12

MEM_MB0_CLK_L210,12

MEM_MB0_CLK_H110,12

MEM_MB0_CLK_L110,12

MEM_MB0_CLK_H010,12

MEM_MB0_CLK_L010,12

MEM_MB0_CS_L110,12

MEM_MB0_CS_L010,12

MEM_MB0_ODT010,12

MEM_MB1_CLK_H211,12

MEM_MB1_CLK_L211,12

MEM_MB1_CLK_H111,12

MEM_MB1_CLK_L111,12

MEM_MB1_CLK_H011,12

MEM_MB1_CLK_L011,12

MEM_MB1_CS_L111,12

MEM_MB1_CS_L011,12

MEM_MB1_ODT011,12

MEM_MB_CAS_L10,11,12

MEM_MB_WE_L10,11,12

MEM_MB_RAS_L10,11,12

MEM_MB_BANK210,11,12

MEM_MB_BANK110,11,12

MEM_MB_BANK010,11,12

MEM_MB_CKE111,12

MEM_MB_CKE010,12

MEM_MB_ADD[15..0]10,11,12

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB1_CLK_H2

MEM_MB1_CLK_L2

MEM_MB1_CLK_H1

MEM_MB1_CLK_L1

MEM_MB1_CLK_H0

MEM_MB1_CLK_L0

MEM_MB1_CS_L1

MEM_MB1_CS_L0

MEM_MB1_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

A18

A19

U31

U30

C19

D19

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MEM_MB_DQS_L[7..0]10,11

MEM_MB_DQS_H[7..0]10,11

MEM_MB_DM[7..0]10,11

CPU1C

CPU1C

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEMORY INTERFACE B

MEMORY INTERFACE B

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DATA[63..0] 10,11

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

CPU AM2 DDR MEMORY I/F

CPU AM2 DDR MEMORY I/F

CPU AM2 DDR MEMORY I/F

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

1

of

of

of

839Wednesday, May 28, 2008

839Wednesday, May 28, 2008

839Wednesday, May 28, 2008

5

4

3

2

1

CPU AM2 PWR & GND

CPU_VDDNB

CPU1F

CPU1F

VDD1

VDD1

A4

VDDNB1

A6

VDDNB2

B5

VDDNB3

B7

VDDNB4

C6

VDDNB5

C8

VDDNB6

D7

VDDNB7

D9

VDDNB8

AA10

AA12

AA14

AA16

AA18

AB11

AC10

AE10

E8

VDDNB9

E10

VDDNB10

F9

VDDNB11

F11

VDDNB12

G10

VDDNB13

G12

VDDNB14

AA8

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

AB7

VDD9

AB9

VDD10

VDD11

AC4

VDD12

AC5

VDD13

AC8

VDD14

VDD15

AD2

VDD16

AD3

VDD17

AD7

VDD18

AD9

VDD19

VDD20

AF7

VDD21

AF9

VDD22

AG4

VDD23

AG5

VDD24

AG7

VDD25

AH2

VDD26

AH3

VDD27

B3

VDD28

C2

VDD31

C4

VDD32

D3

VDD35

D5

VDD36

E4

VDD39

E6

VDD40

F5

VDD43

F7

VDD44

G6

VDD47

G8

VDD48

H7

VDD51

H11

VDD52

H23

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

K11

VDD64

K13

VDD65

K15

VDD66

K17

VDD67

K19

VDD68

K21

VDD69

K23

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

Y17

VDD150

Y19

VDD151

D D

C C

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCCPVCCP

CPU1G

CPU1G

VDD2

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCCP

Change to

Passive

Pin

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

CPU1H

CPU1H

VDD3

VDD3

N17

VSS1

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

M21

VDD21

M23

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

W22

VDD31

Y23

VDD32

5

GND

6

GND

7

GND

8

GND

1

GND

2

GND

3

GND

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

VCC_1V2

VTT_DDR

VCC_DDR

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

CPU1I

CPU1I

VDDIO

VDDIO

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

VLDT_RUN_B

VTT_DDR

C105

C105

C4.7U10Y0805

C4.7U10Y0805

C103

C103

X_C0.01U25Y

X_C0.01U25Y

B B

A A

VCCP

C636

C636

C22u6.3X1206_

C22u6.3X1206_

C22u6.3X1206

C22u6.3X1206

VCCP

C101

C101

C0.01u16X-1

C0.01u16X-1

CPU_VDDNB

C70

C70

C22u6.3X1206_

C22u6.3X1206_

X_C22u6.3X1206

X_C22u6.3X1206

VCC_1V2

C214

C214

X_C4.7U10Y0805

X_C4.7U10Y0805

Bottom side

C639

C639

C650

C650

C654

C662

C662

C22u6.3X1206_

C22u6.3X1206_

C648

C648

X_C22u6.3X1206

X_C22u6.3X1206

C656

C656

C22u6.3X1206_

C22u6.3X1206_

C640

C640

X_C22u6.3X1206

X_C22u6.3X1206

C22u6.3X1206_

C22u6.3X1206_

C654

C22u6.3X1206_

C22u6.3X1206_

X_C22u6.3X1206

X_C22u6.3X1206

Bottom side

C659

C659

C633

C633

X_C0.22U16X

X_C0.22U16X

C4.7U10Y0805

C4.7U10Y0805

C10u6.3X50805

C10u6.3X50805

C0.22U16X

C0.22U16X

Bottom side TOP side, place close to CPU socket

C634

C634

C630

C630

C10u6.3X50805

C10u6.3X50805

C0.01u16X-1

C0.01u16X-1

C228

C228

C209

C209

X_C0.22u10Y0402

X_C0.22u10Y0402

5

C637

C637

X_C10u6.3X50805

X_C10u6.3X50805

C94

C94

X_C10u6.3X50805

X_C10u6.3X50805

C225

C225

C0.22u10Y0402

C0.22u10Y0402

C631

C631

X_C10u6.3X50805

X_C10u6.3X50805

C78

C78

X_C0.22U16X

X_C0.22U16X

X_C180P50N0402

X_C180P50N0402

C653

C653

X_C10u6.3X50805

X_C10u6.3X50805

C95

C95

X_C0.22U16X

X_C0.22U16X

C235

C235

X_C180P50N0402

X_C180P50N0402

C642

C642

X_C10u6.3X50805

X_C10u6.3X50805

C76

C76

C4.7U10Y0805

C4.7U10Y0805

C220

C220

C658

C658

C10u6.3X50805

C10u6.3X50805

C77

C77

C0.01U16X0402

C0.01U16X0402

C643

C643

C22u6.3X1206_

C22u6.3X1206_

C664

C664

C10u6.3X50805

C10u6.3X50805

12

C97

C97

X_C0.01U16X0402

X_C0.01U16X0402

C651

C651

X_C22u6.3X1206

X_C22u6.3X1206

C661

C661

12

C96

C96

C644

C644

C645

C645

C0.01u16X-1

C0.01u16X-1

4

C649

C649

C4.7U10Y0805

C4.7U10Y0805

C657

C657

C4.7U10Y0805

C4.7U10Y0805

C646

C646

X_C4.7U10Y0805

X_C4.7U10Y0805

VCC_DDR

C647

C647

C632

C632

X_C22u6.3X1206

C22u6.3X1206_

C22u6.3X1206_

VCC_DDR

C47p50N0402

C47p50N0402

VTT_DDR

X_C22u6.3X1206

X_C22u6.3X1206

VTT_DDR

C0.22u10Y0402

C0.22u10Y0402

X_C22u6.3X1206

C22u6.3X1206_

C22u6.3X1206_

Place along the VCC_DDR/VSS plane splite

C213

C213

C184

C184

C4.7U10Y0805

C4.7U10Y0805

X_C4.7U10Y0805

X_C4.7U10Y0805

Bottom side

C204

C204

C45

C45

C0.01u16X-1

C0.01u16X-1

C0.22U16X

C0.22U16X

C86

C86

C63

C63

C0.22u10Y0402

C0.22u10Y0402

X_C0.22u10Y0402

X_C0.22u10Y0402

C652

C652

X_C22u6.3X1206

X_C22u6.3X1206

C112

C112

C4.7U10Y0805

C4.7U10Y0805

C665

C665

C60

C60

C0.22u10Y0402

C0.22u10Y0402

3

Bottom side

C635

C635

C660

C660

X_C0.22U16X

X_C0.22U16X

C0.01u16X-1

C0.01u16X-1

C113

C113

C197

C197

X_C4.7U10Y0805

X_C4.7U10Y0805

C47p50N0402

C47p50N0402

VTT_DDR

Place behind the DIMM Slot

C265

C265

X_C4.7U10Y0805

X_C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

Place between the DIMM Slot

12

C212

C212

C68

C68

X_C4.7U10Y0805

X_C4.7U10Y0805

C0.01U16X0402

C0.01U16X0402

C655

C655

C0.01u16X-1

C0.01u16X-1

C114

C114

C261

C261

X_C4.7U10Y0805

X_C4.7U10Y0805

C238

C238

C4.7U10Y0805

C4.7U10Y0805

C638

C638

X_C180p50N

X_C180p50N

C52

C52

C4.7U10Y0805

C4.7U10Y0805

C55

C55

X_C4.7U10Y0805

X_C4.7U10Y0805

C641

C641

X_C10u6.3X50805

X_C10u6.3X50805

C256

C256

C50

C50

C4.7U10Y0805

C4.7U10Y0805

C663

C663

X_C0.22U16X

X_C0.22U16X

C241

C241

C10u6.3X50805

C10u6.3X50805

C666

C666

C305

C305

C230

C230

C0.1U16Y0402

C0.1U16Y0402

X_C0.1U16Y0402

X_C0.1U16Y0402

C222

C222

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

CPU AM2 PWR & GND

CPU AM2 PWR & GND

CPU AM2 PWR & GND

MS-7550 1.0

MS-7550 1.0

MS-7550 1.0

1

939Wednesday, May 28, 2008

939Wednesday, May 28, 2008

939Wednesday, May 28, 2008

of

of

of

5

FIRST LOGICAL DDR DIMM

4

3

2

1

MEM_MA_DQS_H[7..0]8,11

D D

C C

B B

MEM_MA_DQS_L[7..0]8,11

MEM_MA_DATA[63..0]8,11

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DIMM1

DIMM1

3

DQ0

4

DQ1

9

DQ2

10

DQ3

122

DQ4

123

DQ5

128

DQ6

129

DQ7

12

DQ8

13

DQ9

21

DQ10

22

DQ11

131

DQ12

132

DQ13

140

DQ14

141

DQ15

24

DQ16

25

DQ17

30

DQ18

31

DQ19

143

DQ20

144

DQ21

149

DQ22

150

DQ23

33

DQ24

34

DQ25

39

DQ26

40

DQ27

152

DQ28

153

DQ29

158

DQ30

159

DQ31

80

DQ32

81

DQ33

86

DQ34

87

DQ35

199

DQ36

200

DQ37

205

DQ38

206

DQ39

89

DQ40

90

DQ41

95

DQ42

96