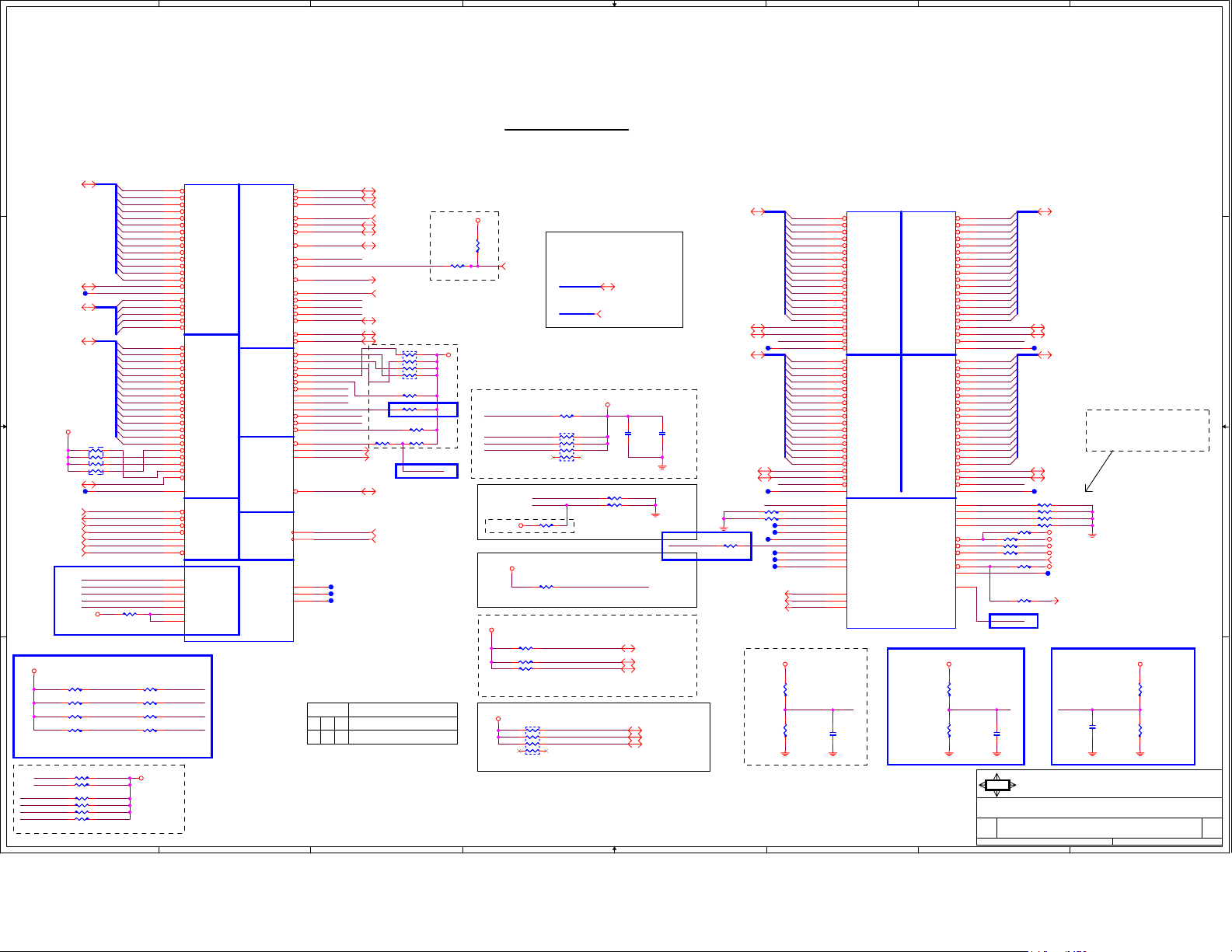

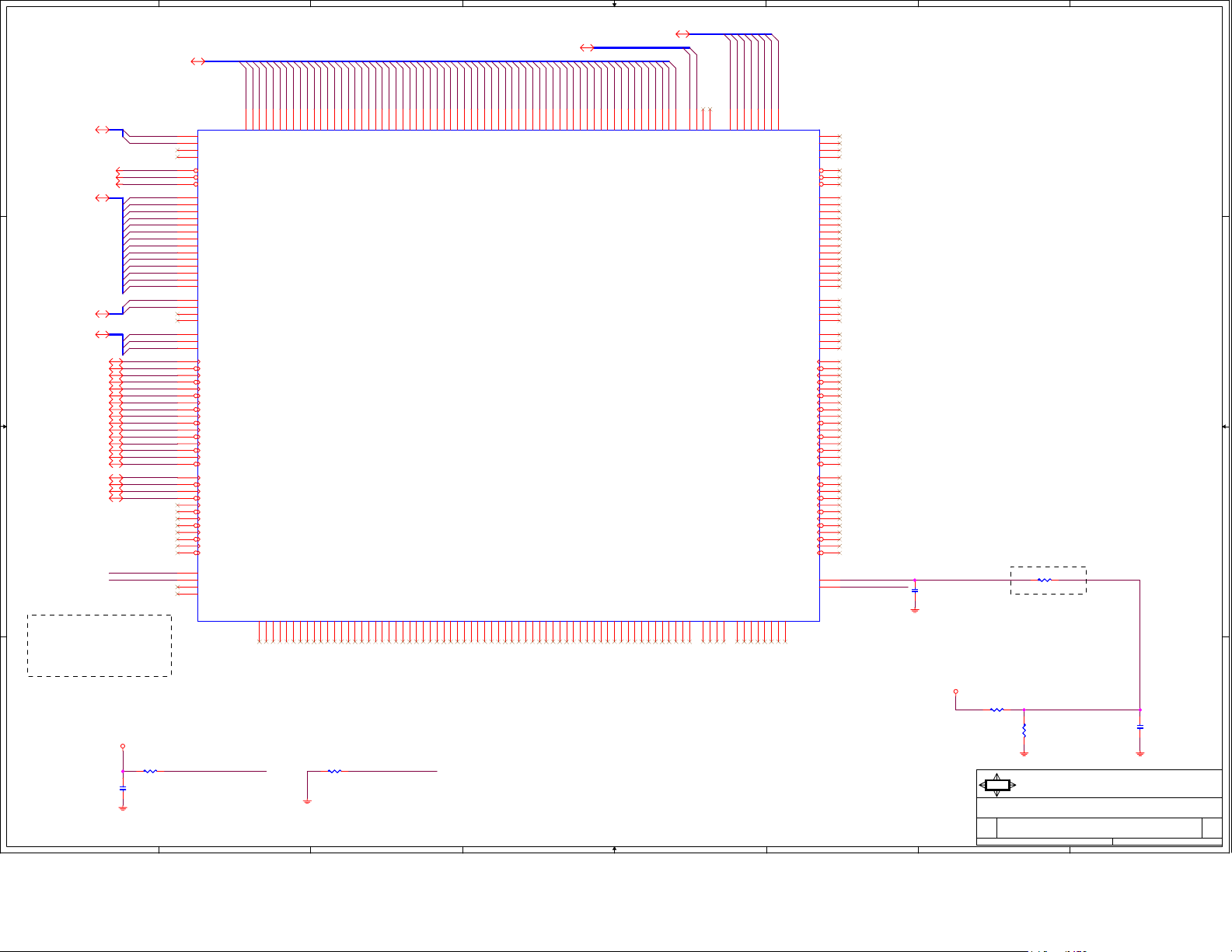

MSI MS-7445 Schematics Version 0A

1

COVER SHEET

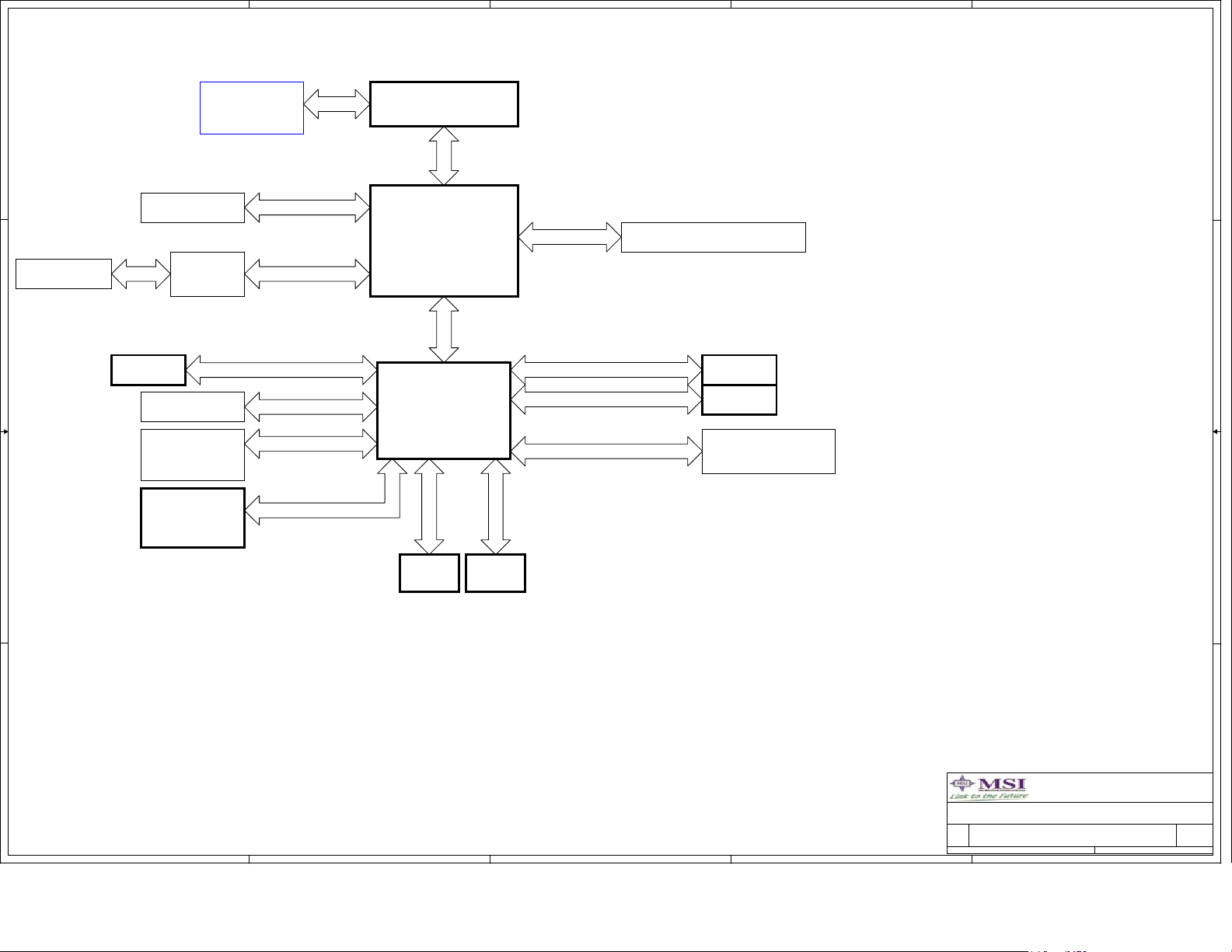

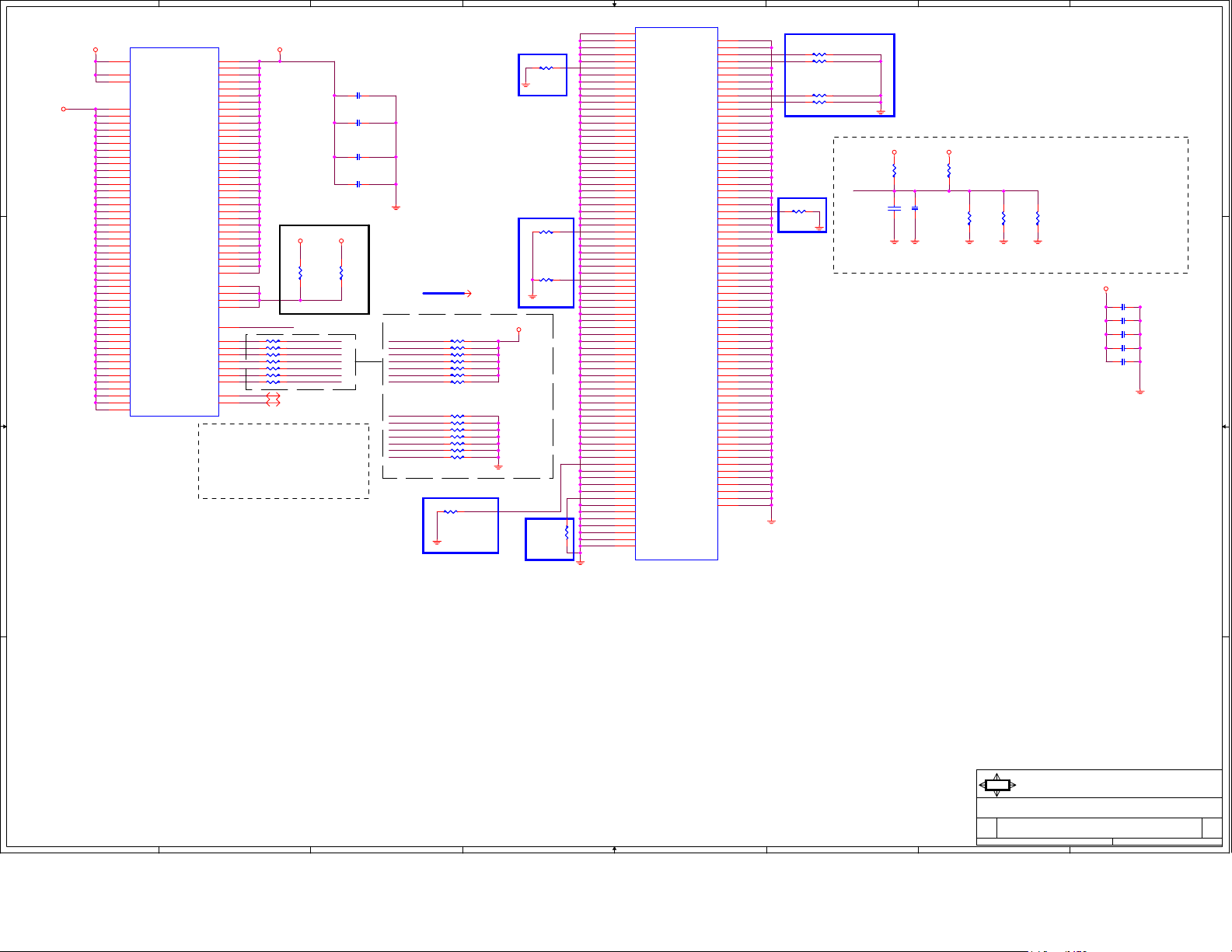

BLOCK DIAGRAM

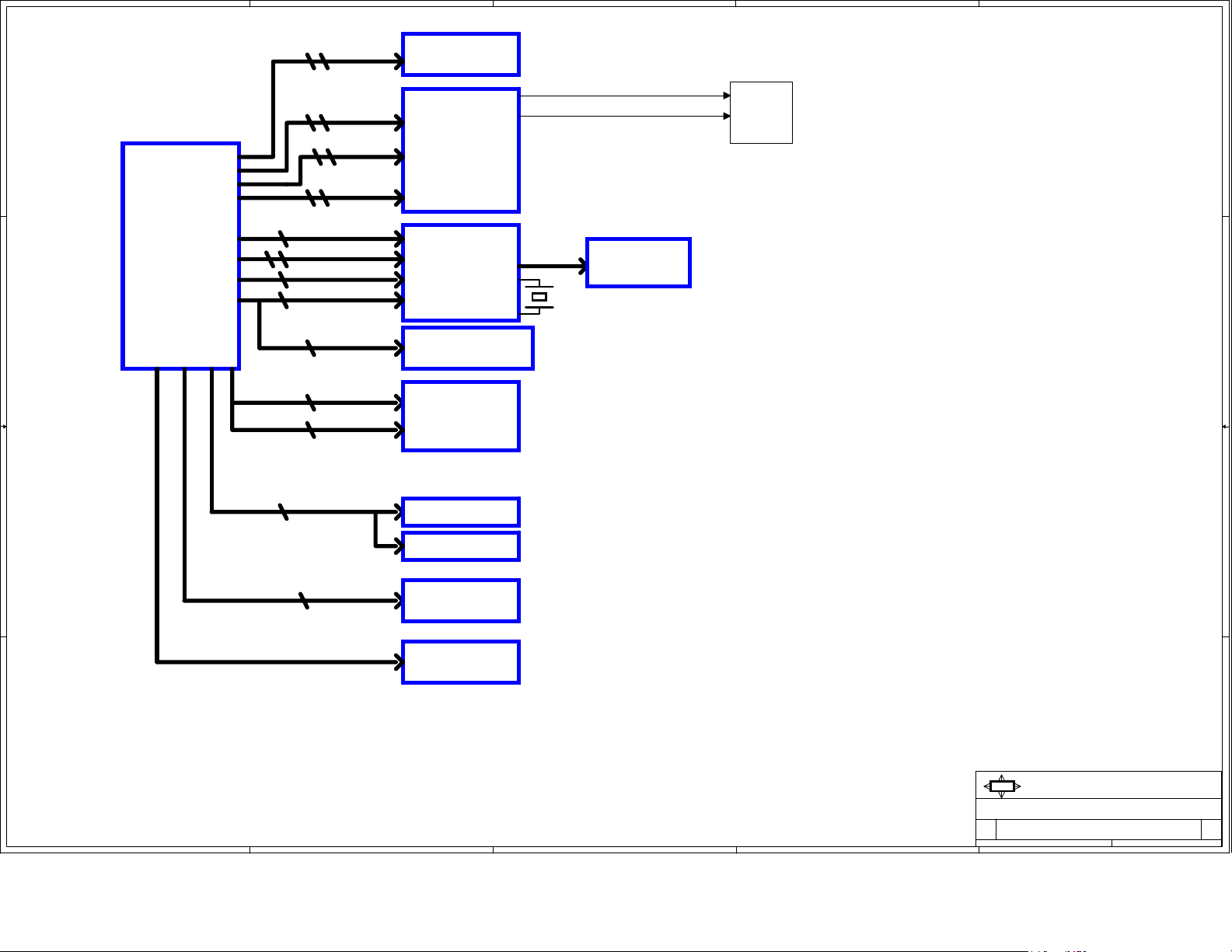

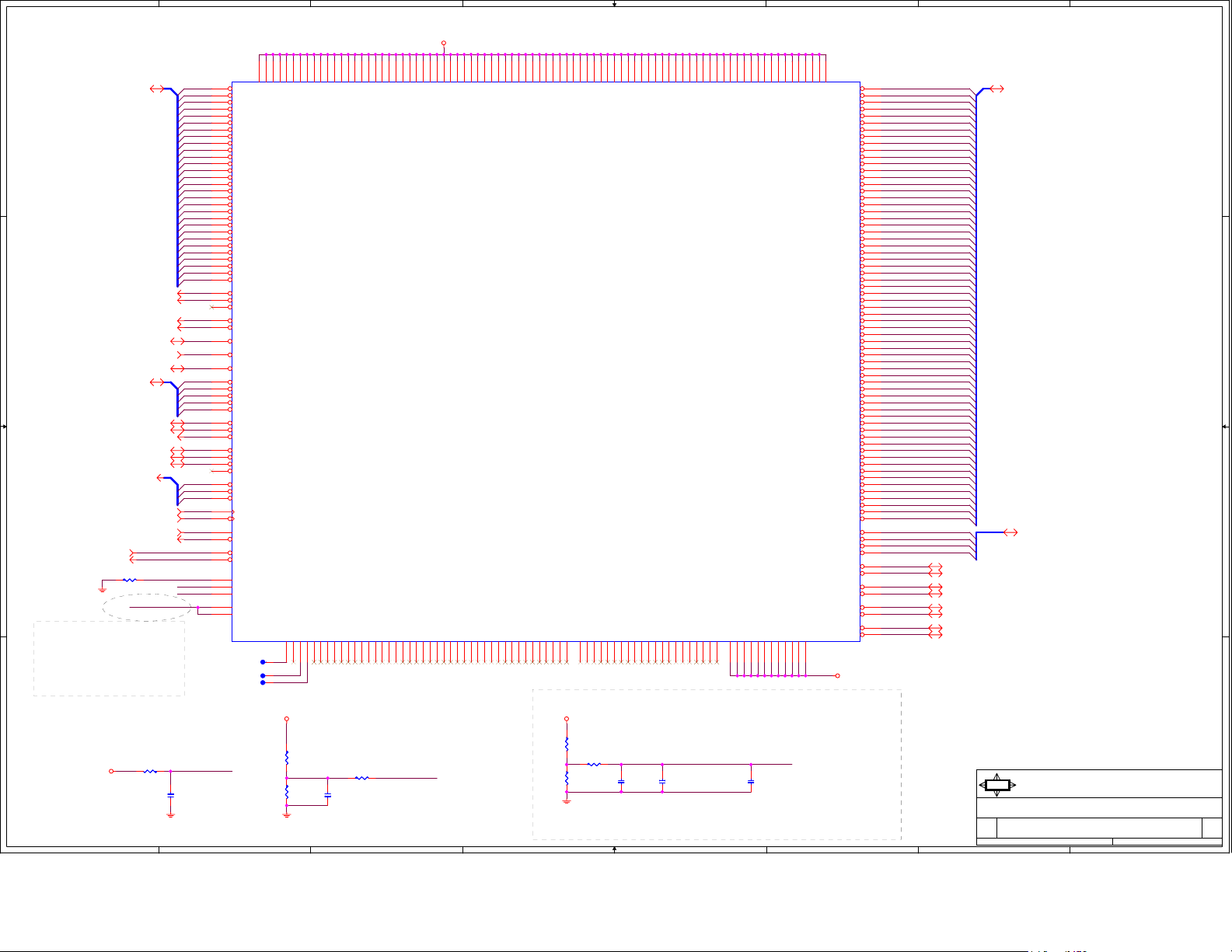

CLOCK MAP

1

2

3

MS-7445

CPU:

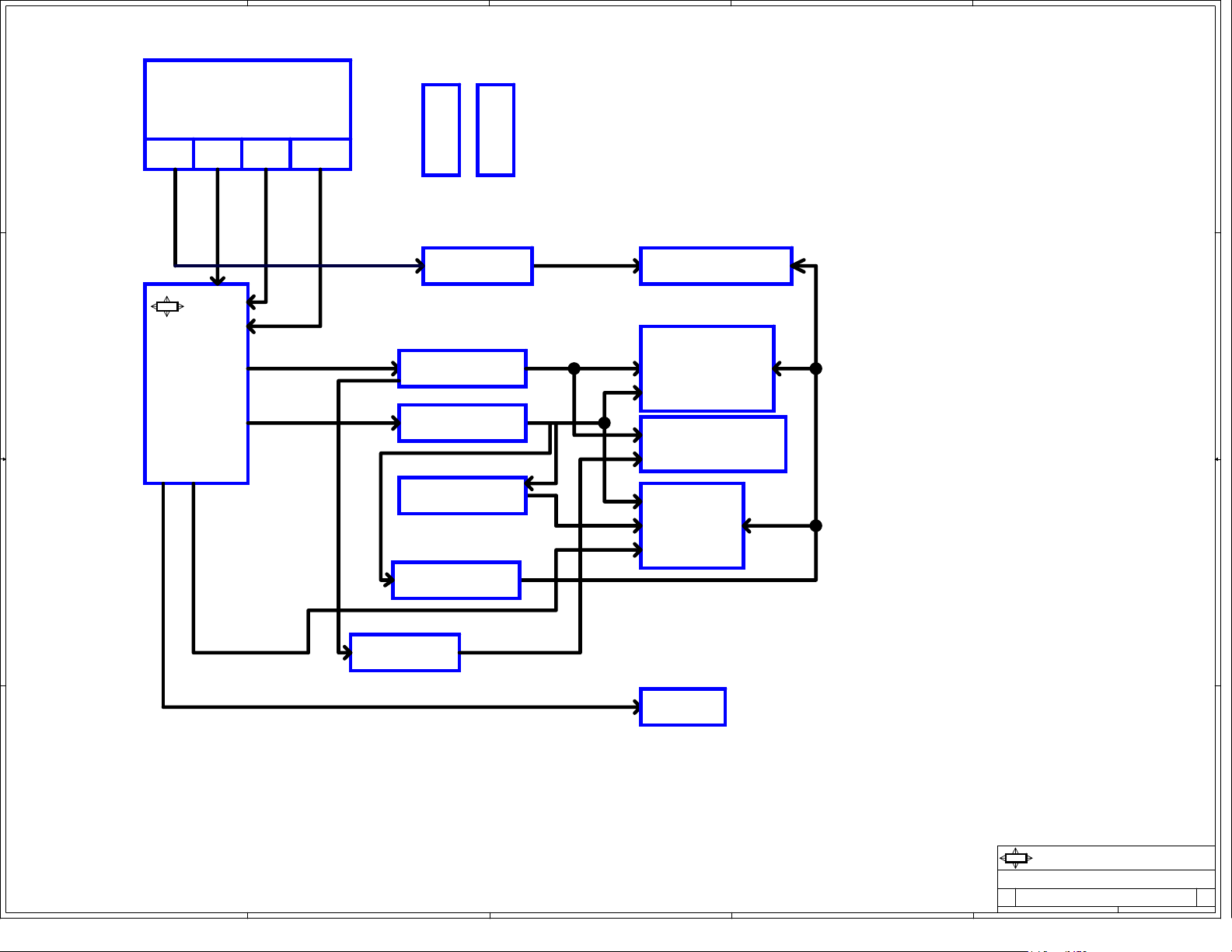

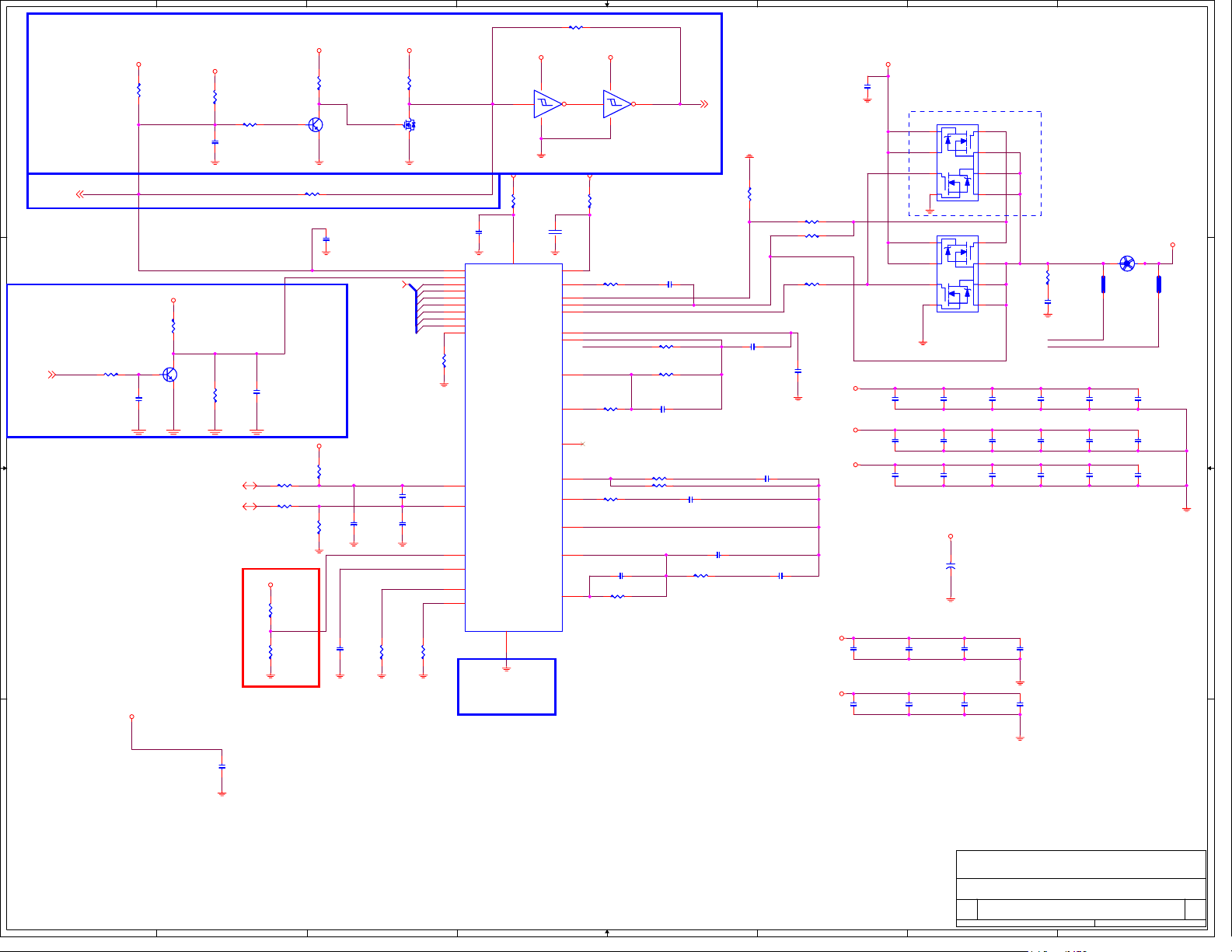

POWER MAP

GPIO MAP

Intel Diamondville-CPU

VRM Single Phase

Intel Lakeport -GMCH

DDR II SO-DIMM

Mini PCIE Slot

CLK - Realtek RTM876-665

VGA CONNECTOR

CH7307 & DVI CONNECTOR

A A

LAN 8111C

ICH7

4

5

6-7

8

9-12

13-14

15

16

17

18

19

20-22

Intel Atom

System Chipset:

Intel 945GC (North Bridge)

Intel ICH7(South Bridge)

On Board Chipset:

SIO -- Fintek 71882

BIOS -- SPI

HD AUDIO CODEC(ALC888)

LAN -- Realtek RTL8111C

Clock Generator -- Real RTM876-665

DVI -- CH7307

TPM LPC Debug port

USB CONNECTORS

Front Panel&Card

+19V DC-IN

ACPI Controller

HD AUDIO CODEC(ALC 888)

SATA & SIO F71882 & FAN CONTROL

Auto BOM manual

PWOK MAP

History

23

24

25

26

27

28

29

30

31

32

Main Memory:

DDR II SO-DIMM x 1 (Max 2GB)

Expansion Slots:

Internal Mini PCIE x2

Intersil PWM:

Controller:

1

6314

MSI

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet of

Date: Sheet of

Date: Sheet

MICRO-STAR INt'L CO., LTD.

COVER SHEET

COVER SHEET

COVER SHEET

MS-7445

MS-7445

MS-7445

of

132Friday, December 26, 2008

132Friday, December 26, 2008

132Friday, December 26, 2008

0A

0A

0A

1

2

3

4

5

VRM

A A

1-Phase PWM

Intel Diamondville

>1.6GHz, DC

Block Diagram

FSB

533

SATA

USB

RGB

DVI

Lakeport

945GC

ICH7

DMI

PCI Express x1

DDR II

533 SO-DIMM x1

Mini PCIE1

Mini PCIE1

Realtek RTL8111C

GbE LAN

Analog

Video Out

Digital

Video Out

B B

CH7307

Mini PCIE1

SATA 0~1

USB Port 0~7

include

4in1 Cardreader

Azalia Codec

C C

ALC888

FINTEK

SIO

SPI

BIOS

(For HWM)

D D

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet

Date: Sheet

1

2

3

4

Date: Sheet

MICRO-START INT'L CO.,LTD.

MS-7445 0A

MS-7445 0A

MS-7445 0A

5

of

of

of

232Friday, December 26, 2008

232Friday, December 26, 2008

232Friday, December 26, 2008

5

4

3

2

1

HCLK

CLOCK MAP

D D

MCHCLK

PE_100M

Diamondville

Lakeport

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

266MHz

266MHz

266MHz

266MHz

DDRII

SO-DIMM

MCH

DOTCLK

Realtek

RTM876-665

Clock

Generator

C C

ICHCLK

SATACLK

ICH14.318MHz

USB48MHz

ICH7

24MHz

ALC888 Azalia

32.768MHz

48MHz

4in1 CardReader

48MHz

PCI_CLK

FINTEK SIO

33MHz

PE_100M

B B

100MHz

Mini PCIE

Mini PCIE

PE_100M

100MHz

LAN Realtek

8111C

LPC Debug port

33MHz

A A

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

CLOCK MAP

CLOCK MAP

CLOCK MAP

MS-7445

MS-7445

MS-7445

1

0A

0A

332Friday, December 26, 2008

332Friday, December 26, 2008

332Friday, December 26, 2008

0A

of

of

of

5

4

3

2

1

POWER MAP

DC19V IN

D D

+12V +5V +3.3V +5VSB

MSI

C C

ACPI

VCC5_SB

VCC5

V_FSB_VTT

B B

4.9A

PCIE1

PCIE1

VRM

VCC_DDR

6.75+1.2 = 7.95A7.95*1.8/5/0.8 = 3.58A

UPI

V_1P5_CORE

UPI

V_1P05_CORE

LINEAR

LINEAR

22.84A

0.86A

4.9A

17.08A

0.86A

Diamondville

Lakeport

4.4A

MCH

13.8A + 1.5A

= 15.3A

2.35A

SO-DIMM

1.2A

DDR2 X 1

1.78A

0.86A

0.375A

ICH7

14mA

8A

0.9A

0.375A

VCC3_SB VTT_DDR

W83310DS

5VDUAL

A A

5

4

1.2A

3A

3

USB

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

2

Date: Sheet

POWER MAP

POWER MAP

POWER MAP

MS-7445

MS-7445

MS-7445

1

0A

0A

432Friday, December 26, 2008

432Friday, December 26, 2008

432Friday, December 26, 2008

0A

of

of

of

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

8

7

6

5

4

3

2

1

ICH7

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name or status

GPIO[0] SIO_SMI# AB18 I/O Vcc3p3 N Y 5 Input pull high VCC3

GPIO[1] PCIREQ[5]# C8 I/O V5REF N Y 5 Input PREQ#5

GPIO[2] PIRQE# G8 I/OD V5REF N Y 5 Input PIRQ#E

GPIO[3] PIRQF# F7 I/OD V5REF N Y 5 Input PIRQ#F

GPIO[4] PIRQG# F8 I/OD V5REF N Y 5 Input PIRQ#G

D D

GPIO[5] PIRQH# G7 I/OD V5REF N Y 5 Input PIRQ#H

GPIO[6] AC21 I/O Vcc3p3 N Y 3.3 Input

GPIO[7] OVT# AC18 I/O Vcc3p3 N Y 3.3 Input pull high VCC3

GPIO[8] SIO_PME# E21 I/O VccSus3p3 N Y 3.3 Input SIO_PME# pull high VCC3_SB

GPIO[9] WLAN_PWRON E20 I/O VccSus3p3 N Y 3.3 Output pull high VCC3_SB

GPIO[10] WLAN2_PWRON A20 I/O VccSus3p3 N Y 3.3 Output pull high VCC3_SB

GPIO[11] SMBALERT# B23 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[12] unmuxed F19 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[13] unmuxed E19 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[14] ADT7467_ALERT R4 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[15] unmuxed E22 I/O VccSus3p3 N Y 3.3 Input pull high VCC3_SB

GPIO[16] unmuxed AC22 I/O Vcc3p3 N N 3.3 0 NC

GPIO[17] PCIGNT[5]# D8 I/O Vcc3p3 N N 3.3 N/A NC

GPIO[18] unmuxed AC20 I/O Vcc3p3 N N 3.3 1 NC

GPIO[21] SATA1GP AF19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[20] unmuxed AF21 I/O Vcc3p3 N N 3.3 1 NC

GPIO[21] SATA0GP AF19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

C C

GPIO[22] PCIREQ[4]# A13 I/O Vcc3p3 N N 3.3 Input PREQ#4

GPIO[23] LDRQ1# AA5 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[24] unmuxed R3 I/O VccSus3p3 N N 3.3 No Change NC

GPIO[25] unmuxed D20 I/O VccSus3p3 Y N 3.3 1 pull high VCC3 SB

GPIO[26] unmuxed A21 I/O VccSus3p3 N N 3.3 0 NC

GPIO[27] unmuxed B21 I/O VccSus3p3 N N 3.3 0 NC

GPIO[28] unmuxed E23 I/O VccSus3p3 N N 3.3 0 NC

GPIO[29] OC#2 C3 I/O VccSus3p3 N N 3.3 Input OC#5

GPIO[30] OC#2 A2 I/O VccSus3p3 N N 3.3 Input OC#6

GPIO[31] OC#2 B3 I/O VccSus3p3 N N 3.3 Input OC#7

GPIO[32] CLEAR_CMOS# AG18 I/O Vcc3p3 N N 3.3 1 CLEAR_CMOS#, ONLY pull high VCC3

GPIO[33] unmuxed AC19 I/O Vcc3p3 N N 3.3 1 NC

GPIO[34] unmuxed U2 I/O Vcc3p3 N N 3.3 0 NC

GPIO[35] unmuxed AD21 I/O Vcc3p3 N N 3.3 1 NC

GPIO[36] SATA2GP AH19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[37] SATA3GP AE19 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[38] unmuxed AD20 I/O Vcc3p3 N N 3.3 Input pull high VCC3

B B

GPIO[39] unmuxed AE20 I/O Vcc3p3 N N 3.3 Input pull high VCC3

GPIO[48] GNT4# A14 I/O Vcc3p3 N N 3.3 N/A GNT4#

GPIO[49] CPUPWRGD AG24 I/O V_CPU_IO N N CPU N/A H_PWRGD

GPI[15..0] can configured to cause a SMI# or SCI.

SIGNAL DEVICE

MiniPCIeRST#

TPMRST#

LANRST#

PCIRST_ICH7#

PCIRST_DVI#

H_CPURST#

FWHRST#

MCHRST#

MINI PCIE SLOT

TPM & SIO

LAN 8111C

BUFFER IC

CH7307C

CPU

LPT Debug port

MCH

SMBCLK, SMBDATA DDR2, PCIEX1, CLKGEN, ICH7

DDRII DIMM Config.

CLOCKDEVICE ADDRESS

DIMM 1

A0H

JUMPER SETTING

JBAT1

(1-2)NORMAL

MCLK_A0/MCLK_A#0

MCLK_A1/MCLK_A#1

MCLK_A2/MCLK_A#2

(2-3)CLEAR

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

A A

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

2

GPIO MAP

GPIO MAP

GPIO MAP

MS-7445

MS-7445

MS-7445

0A

0A

532Monday, December 29, 2008

532Monday, December 29, 2008

532Monday, December 29, 2008

1

0A

of

of

of

8

7

6

5

4

3

2

1

D D

U10A

R351

R351

0R0402

0R0402

R352

R352

0R0402

0R0402

R356

R356

0R0402

0R0402

R357

R357

0R0402

0R0402

V_FSB_VTT

U10A

P21

A[3]#

H20

N20

R20

J19

N19

G20

M19

H21

L20

M20

K19

J20

L21

K20

D17

N21

J21

G19

P20

R19

C19

F19

E21

A16

D19

C14

C18

C20

E20

D20

B18

C15

B16

B17

C16

A17

B14

B15

A14

B19

M18

U18

T16

J4

R16

T15

R15

U17

D6

G6

H6

K4

K5

M15

L16

ADDR GROUP

0

ADDR GROUP

0

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

AP0

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

ADDR GROUP 1

ADDR GROUP 1

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

AP1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

GTLREF_EA

NC1

BPM[0]#_2

NC2

BPM[1]#_2

NC3

BPM[2]#_2

NC4

NC5

BPM[3]#_2

TDI_M

NC6

TDO_M

NC7

H_BPM#0

H_BPM#1

H_BPM#2

H_BPM#3

0B changed 3

unstuff Resistors refer

to CRB V0.8

Diamondville

Diamondville

7

CONTROL

CONTROL

XDP/ITP SIGNALSTHERM

XDP/ITP SIGNALSTHERM

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

H CLK

H CLK

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HIT#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

BR1#

BCLK[0]

BCLK[1]

RSVD3

RSVD2

RSVD1

TCK

TDO

TMS

V19

Y19

U21

T21

T19

Y18

T20

H_IERR#

F16

V16

W20

D15

H_RS#0

W18

H_RS#1

Y17

H_RS#2

U20

W19

AA17

V20

H_BPM#0

K17

H_BPM#1

J18

H_BPM#2

H15

H_BPM#3

J15

H_BPM#4

K18

PREQ#

J16

H_TCK

M17

H_TDI

N16

TDI

M16

H_TMS

L17

H_TRST#

K16

V15

H_PROCHOT#

G17

E4

E5

H17

V11

V12

C21

C1

A3

T17T17

T19T19

T21T21

H_ADS# 9

H_BNR# 9

H_BPRI# 9

H_DEFER# 9

H_DRDY# 9

H_DBSY# 9

H_LOCK# 9

H_CPURST# 9

H_TRDY# 9

H_HIT# 9

H_HITM# 9

R723

R723

22R1%0402

22R1%0402

CPU_TMPA 29

VTIN_GND 29

CK_H_CPU 16

CK_H_CPU# 16

BSEL

02

1 FSB FREQUENCY

1

0 0 133 MHZ (533)

For Diamondville processor

, the BSEL is fixed to operate

at 133-MHz BCLK frequency.

H_BR#0 9

R715 X_150R1%0402-1R715 X_150R1%0402-1

TRMTRIP# 20

TABLE

6

H_A#[3..31]9

H_ADSTB#09

T1T1

H_REQ#[0..4]9

C C

H_A#[3..31]9

V_FSB_VTT

7 8

5 6

H_ADSTB#19

H_A20M#20

H_FERR#20

H_IGNNE#20

H_STPCLK#20

ICH_H_SMI#20

H_A20M#

H_IGNNE#

3 4

1 2

T4T4

H_INTR20

H_NMI20

GTLREF_2

H_BPM#0_2

H_BPM#1_2

H_BPM#2_2

H_BPM#3_2

V_FSB_VTT

R714

R714

X_51R1%0402

X_51R1%0402

R724

R724

X_51R1%0402

X_51R1%0402

R725

R725

X_51R1%0402

X_51R1%0402

R726

R726

X_51R1%0402

X_51R1%0402

R243 X_1KST_0402R243 X_1KST_0402

R227 X_1KST_0402R227 X_1KST_0402

R229 X_56R/4R229 X_56R/4

R716 X_51R1%0402R716 X_51R1%0402

R717 X_51R1%0402R717 X_51R1%0402

R718 X_1KST_0402R718 X_1KST_0402

8

8P4R-1KR0402

8P4R-1KR0402

B B

V_FSB_VTT

A A

H_STPCLK#

H_INTR

H_NMI

ICH_H_SMI#

R14 unstuffed refer to CRB V0.8

RN2

RN2

51R1%0402

51R1%0402

H_BPM#0_2

H_BPM#1_2

H_BPM#2_2

H_BPM#3_2

R728

R728

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

1

3

5

7

R713

R713

R727

R727

RN35

RN35

R235

R235

62R

62R

H_PROCHOT_N

0B changed 2

2

4

6

8

51R1%0402

51R1%0402

X_51R1%0402

X_51R1%0402

0B changed 1

unstuff R712 refer

to CRB V0.8

V_FSB_VTT

R712

R712

X_330R0402-1

X_330R0402-1

R27

R27

1KST_0402

1KST_0402

V_FSB_VTT

8P4R-51R0402

8P4R-51R0402

CPU SIGNAL BLOCK

H_INIT# 20

0B Change 13

H_IERR#

H_TDI

H_TMS

PREQ#

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

R15 51R1%0402R15 51R1%0402

R16 1KST_0402R16 1KST_0402

R17 51R1%0402R17 51R1%0402

V_FSB_VTT

R1 1KST_0402R1 1KST_0402

1

3

5

7

H_TCK

H_TRST#

R240

R240

X_51R1%0402

X_51R1%0402

R13 56R/4R13 56R/4

PLACE AT ICH END OF ROUTE

0B changed 5

PLACE AT CPU END OF ROUTE

RN3

RN3

1

2

3

4

5

6

7

8

8P4R-470R

8P4R-470R

5

RN1

RN1

2

4

6

8

0B changed 4

H_FERR#

H_CPURST#

H_PWRGD

H_BR#0

H_FSBSEL2

H_FSBSEL1

H_FSBSEL0

H_DBI#[0..3] 9

H_RS#[0..2] 9

V_FSB_VTT

C1

0.1u10X4C10.1u10X4

8P4R-51R0402

8P4R-51R0402

R2 51R1%0402R2 51R1%0402

R3 51R1%0402R3 51R1%0402

H_CPURST# 9

H_PWRGD 20

H_BR#0 9

C2

0.1u10X4C20.1u10X4

H_PROCHOT_N

H_FSBSEL2 11,16

H_FSBSEL1 11,16

H_FSBSEL0 11,16

U10B

H_D#[0..63]9

H_DSTBN#09

H_DSTBP#09

T2T2

H_D#[0..63]9

H_DSTBN#19

H_DSTBP#19

T5T5

R5 X_1KR0402R5 X_1KR0402

R7 X_1KR0402R7 X_1KR0402

R415

R415

0R0402

0R0402

H_FSBSEL011,16

H_FSBSEL111,16

H_FSBSEL211,16

1KST_0402

1KST_0402

2KR1%0402

2KR1%0402

4

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DBI#0

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DBI#1

GTLREF

BINIT#

T7T7

EDM

T8T8

EXTBGREF

T9T9

FORCEPR#

HFPLL

T11T11

MCERR#

T12T12

RSP#

T13T13

V_FSB_VTT V_FSB_VTTV_FSB_VTT

R18

R18

EXTBGREF GTLREF_2

R21

R21

Y11

W10

Y12

AA14

AA11

W12

AA16

Y10

Y13

W15

AA13

Y16

W13

AA9

Y14

Y15

W16

AA5

AA6

AA8

T17

N15

P17

0.5" max

length

U10B

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

Y9

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

W9

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

V9

DP#0

D[16]#

Y8

D[17]#

W3

D[18]#

U1

D[19]#

W7

D[20]#

W6

D[21]#

Y7

D[22]#

D[23]#

Y3

D[24]#

W2

D[25]#

V3

D[26]#

U2

D[27]#

T3

D[28]#

D[29]#

V2

D[30]#

W4

D[31]#

Y4

DSTBN[1]#

Y5

DSTBP[1]#

Y6

DINV[1]#

R4

DP#1

A7

GTLREF

U5

ACLKPH

V5

DCLKPH

BINIT#

R6

EDM

M6

EXTBGR

FORCEPR#

N6

HFPLL

MCERR#

T6

RSP#

J6

BSEL[0]

H5

BSEL[1]

G5

BSEL[2]

Diamondville

Diamondville

C4

C4

C1u10X50402-RH

C1u10X50402-RH

3

DATA GRP0

DATA GRP0

DATA GRP1

DATA GRP1

MISC

MISC

1.21KR1%0402-1

1.21KR1%0402-1

1.74KR1%0402

1.74KR1%0402

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

DATA GRP2DATA GRP3

DATA GRP2DATA GRP3

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DP#2

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

DP#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

CORE_D

CMREF

R19

R19

R22

R22

H_D#32

R3

H_D#33

R2

H_D#34

P1

H_D#35

N1

H_D#36

M2

H_D#37

P2

H_D#38

J3

H_D#39

N3

H_D#40

G3

H_D#41

H2

H_D#42

N2

H_D#43

L2

H_D#44

M3

H_D#45

J2

H_D#46

H1

H_D#47

J1

K2

K3

H_DBI#2

L1

M4

H_D#48

C2

H_D#49

G2

H_D#50

F1

H_D#51

D3

H_D#52

B4

H_D#53

E1

H_D#54

A5

H_D#55

C3

H_D#56

A6

H_D#57

F2

H_D#58

C6

H_D#59

B6

H_D#60

B3

H_D#61

C4

H_D#62

C7

H_D#63

D2

E2

F3

H_DBI#3

C5

D4

H_COMP0

T1

H_COMP1

T2

H_COMP2

F20

H_COMP3

F21

R25 X_1KR0402R25 X_1KR0402

R10 1KR0402R10 1KR0402

R18

R11 1KR0402R11 1KR0402

R17

R12 1KR0402R12 1KR0402

U4

V17

R14 X_1KR0402R14 X_1KR0402

N18

A13

B7

GTLREF

0.5" max

length

GTLREF

C5

C5

X_0.1u10X4

X_0.1u10X4

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

2

H_D#[0..63] 9

H_DSTBN#2 9

H_DSTBP#2 9

T3T3

H_D#[0..63] 9

0B changed 6

Change R4,R8 to 24.9R

R6,R9 to 49.9R.

H_DSTBN#3 9

H_DSTBP#3 9

T6T6

R4 24.9R1%0402R4 24.9R1%0402

R6 49.9R1%0402R6 49.9R1%0402

R8 24.9R1%0402R8 24.9R1%0402

R9 49.9R1%0402R9 49.9R1%0402

VCC3_SB

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

H_PWRGD 20

V_FSB_VTT

T14T14

0R0402

0R0402

R254

R254

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

ATOM - Signals

ATOM - Signals

ATOM - Signals

0.5" max length

25 MIL AWAY FROM HIGH

SPEED SIGNAL

HCOMP0,2==>18MIL

HCOMP1,3==>5MIL

H_SB_CPUSLP_N 20

0.5" max

length

C3

0.1u10X4C30.1u10X4

MS-7445

MS-7445

MS-7445

R20

R20

1.62KR1%0402

1.62KR1%0402

R23

R23

2.74KR1%0402

2.74KR1%0402

of

of

of

632Monday, December 29, 2008

632Monday, December 29, 2008

632Monday, December 29, 2008

1

0A

0A

0A

8

U10C

V_FSB_VTT

VCCP

D D

C C

B B

U10C

V10

VCCF

A9

VCCQ1

B9

VCCQ2

A10

VCCP1

A11

VCCP2

A12

VCCP3

B10

VCCP4

B11

VCCP5

B12

VCCP6

C10

VCCP7

C11

VCCP8

C12

VCCP9

D10

VCCP10

D11

VCCP11

D12

VCCP12

E10

VCCP13

E11

VCCP14

E12

VCCP15

F10

VCCP16

F11

VCCP17

F12

VCCP18

G10

VCCP19

G11

VCCP20

G12

VCCP21

H10

VCCP22

H11

VCCP23

H12

VCCP24

J10

VCCP25

J11

VCCP26

J12

VCCP27

K10

VCCP28

K11

VCCP29

K12

VCCP30

L10

VCCP31

L11

VCCP32

L12

VCCP33

M10

VCCP34

M11

VCCP35

M12

VCCP36

N10

VCCP37

N11

VCCP38

N12

VCCP39

P10

VCCP40

P11

VCCP41

P12

VCCP42

R10

VCCP43

R11

VCCP44

R12

VCCP45

Diamondville

Diamondville

POWER

POWER

VCCPC64

VCCPC63

VCCPC62

VCCPC61

VCCSENSE

VSSSENSE

7

V_FSB_VTT

C9

VTT1

D9

VTT2

E9

VTT3

F8

VTT4

F9

VTT5

G8

VTT6

G14

VTT7

H8

VTT8

H14

VTT9

J8

VTT10

J14

VTT11

K8

VTT12

K14

VTT13

L8

VTT14

L14

VTT15

M8

VTT16

M14

VTT17

N8

VTT18

N14

VTT19

P8

VTT20

P14

VTT21

R8

VTT22

R14

VTT23

T8

VTT24

T14

VTT25

U8

VTT26

U9

VTT27

U10

VTT28

U11

VTT29

U12

VTT30

U13

VTT31

U14

VTT32

F14

F13

E14

E13

D7

VCCA

F15

VID[0]

D16

VID[1]

E18

VID[2]

G15

VID[3]

G16

VID[4]

E17

VID[5]

G18

VID[6]

C13

D13

LAYOUT NOTE:

Route VCCSENSE and VSSSENSE

traces at 27.4Ohms with 50

mil spacing.

Place PU and PD within 1

inch of CPU.

0B changed 7

unstuff R304,stuff R303

V_FSB_VTT

R3030RR303

0R

H_VCCA

R172 0R0402R172 0R0402

R190 0R0402R190 0R0402

R191 0R0402R191 0R0402

R192 0R0402R192 0R0402

R214 0R0402R214 0R0402

R220 0R0402R220 0R0402

R268 0R0402R268 0R0402

VID0

VID1

VID2

VID3

VID4

VID5

VID6

VCC_VRM_SENSE 8

VSS_VRM_SENSE 8

6

C483 X_C0.1u10YC483 X_C0.1u10Y

C484 X_C0.1u10YC484 X_C0.1u10Y

C485 X_C0.1u10YC485 X_C0.1u10Y

C486 X_C0.1u10YC486 X_C0.1u10Y

VCCP

R304

R304

X_0R

X_0R

Change VID circuit for jump VID.

VID3

VID1

VID2

VID4

VID0

VID5

VID6

VID0

VID1

VID2

VID3

VID4

VID5

VID6

R409 24.9R1%0402R409 24.9R1%0402

VID[6..0] 8

R473 2.2KR0402R473 2.2KR0402

R472 2.2KR0402R472 2.2KR0402

R471 2.2KR0402R471 2.2KR0402

R470 2.2KR0402R470 2.2KR0402

R469 2.2KR0402R469 2.2KR0402

R468 2.2KR0402R468 2.2KR0402

R467 2.2KR0402R467 2.2KR0402

R269 X_0R0402R269 X_0R0402

R274 X_0R0402R274 X_0R0402

R275 X_0R0402R275 X_0R0402

R276 X_0R0402R276 X_0R0402

R281 X_0R0402R281 X_0R0402

R282 X_0R0402R282 X_0R0402

R286 X_0R0402R286 X_0R0402

V_FSB_VTT

5

R426

R426

X_0R0402

X_0R0402

X_0R0402

X_0R0402

R412

R412

X_0R0402

X_0R0402

R413

R413

R414

R414

X_0R0402

X_0R0402

THRMDC_2

THRMDA_2

H_COMP0_2

4

U10D

U10D

A2

VSS

A4

VSS

A8

VSS

A15

A18

A19

A20

B13

B20

B21

C17

D14

D18

D21

E15

E16

E19

F17

F18

G13

G21

H13

H16

H18

H19

J13

J17

K13

K15

K21

L13

L15

L18

L19

M13

B1

B2

B5

B8

C8

D1

D5

D8

E3

E6

E7

E8

F4

F5

F6

F7

G1

G4

G7

G9

H3

H4

H7

H9

J5

J7

J9

K1

K6

K7

K9

L3

L4

L5

L6

L7

L9

M1

M5

M7

M9

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

THRMDC_2

VSS

VSS

VSS

VSS

VSS

VSS

THRMDA_2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

COMP[0]_2

VSS

VSS

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Diamondville

Diamondville

COMP[1]_2

COMP[2]_2

COMP[3]_2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N9

N7

N5

N4

M21

N13

N17

P3

P4

P5

P6

P7

P9

P13

P15

P16

P18

P19

R1

R5

R7

R9

R13

R21

T4

T5

T7

T9

T10

T11

T12

T13

T18

U3

U6

U7

U15

U16

U19

V1

V4

V6

V7

V8

V13

V14

V18

V21

W1

W5

W8

W11

W14

W17

W21

Y1

Y2

Y20

Y21

AA2

AA3

AA4

AA7

AA10

AA12

AA15

AA18

AA19

AA20

H_COMP1_2

H_COMP2_2

H_COMP3_2

R425

R425

X_0R0402

X_0R0402

2.5A: before VCC stable

1.5A: after VCC stable

3

R400 49.9R1%0402R400 49.9R1%0402

R386 24.9R1%0402R386 24.9R1%0402

R407 49.9R1%0402R407 49.9R1%0402

R424 X_0R0402R424 X_0R0402

2

0B changed 8-->change pull up circuit follow CRB V0.7.

X_0R

X_0R

H_VCCA

C6

C6

C10U10Y1206

C10U10Y1206

V_1P5_CORE

R24

R24

VCC_DDR

C7

C7

C0.01u10X-1

C0.01u10X-1

R719

R719

2R1%

2R1%

R720

R720

53.6R1%

53.6R1%

R721

R721

53.6R1%

53.6R1%

NEAR THE PROCESS SOCKET

R722

R722

53.6R1%

53.6R1%

1

V_FSB_VTT

C8 C10U10Y0805C8 C10U10Y0805

C9 C10U10Y0805C9 C10U10Y0805

C10 C10U10Y0805C10 C10U10Y0805

C11 C0.1u10YC11 C0.1u10Y

C12 C0.1u10YC12 C0.1u10Y

CAPS FOR FSB GENERIC

A A

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

ATOM - Power

ATOM - Power

ATOM - Power

MS-7445

MS-7445

MS-7445

2

0A

0A

0A

of

of

of

732Monday, December 29, 2008

732Monday, December 29, 2008

732Monday, December 29, 2008

1

8

Reference from MS-7440

VCC3

R28

R28

X_4.7KR

X_4.7KR

D D

VRM_GD16

VRM_GD

+12V

Reference from MS-96C4

10KR0402

10KR0402

C C

VID_GD#

VID_GD#27

B B

R465 10KR0402R465 10KR0402

C405

C405

X_C1000p50X0402

X_C1000p50X0402

+12V

Q71

Q71

N-MMBT3904

N-MMBT3904

VCC_VRM_SENSE7

VSS_VRM_SENSE7

R445

R445

VCCP

R137

R137

1KR0402

1KR0402

C208

C208

X_C0.01u25X0402

X_C0.01u25X0402

R444

R444

2.2KR0402

2.2KR0402

7

R136 10KR0402R136 10KR0402

VCC5_SB

B

B

R31

R31

VID_PG

C33

C33

C0.1u25Y0402-RH

C0.1u25Y0402-RH

VCCP

R48 0R0402R48 0R0402

R51 0R0402R51 0R0402

VCC5

R55

R55

X_100K

X_100K

R56

R56

3KR1%0402

3KR1%0402

Power team tuned

R139

R139

10KR0402

10KR0402

Q12

Q12

C

C

E

E

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

X_0R

X_0R

C18

C18

C10u6.3X5-RH

C10u6.3X5-RH

VID[6..0]7

R46

R46

100_0402

100_0402

C31

C31

R52

R52

X_C0.01u25X0402

X_C0.01u25X0402

100_0402

100_0402

C39

C39

C0.01u16X0402

C0.01u16X0402

100K 1%_0402

100K 1%_0402

6

G

P0_SS

R57

R57

VCC3

R138

R138

1KR0402

1KR0402

DS

Q13

Q13

N-2N7002_SOT23-1

N-2N7002_SOT23-1

VID6

VID5

VID4

VID3

VID2

VID1

VID0

R101

R101

0R0402

0R0402

C26

C26

X_C0.01u16X0402

X_C0.01u16X0402

C32

C32

X_C0.1u25Y0402-RH

X_C0.1u25Y0402-RH

R58

R58

243KR1%0402-RH-1

243KR1%0402-RH-1

C16

C1u10X

C1u10X

U3

U3

1

PGOOD

17

EN

32

VID7

25

VID6

26

VID5

27

VID4

28

VID3

29

VID2

30

VID1

31

VID0

12

VSEN

11

RGND

5

OFS

4

REF

3

FS

2

SS

6X6 QFN

BOTTOM PAD

CONNECT TO GND

Through 8 VIAs

VCC5

GND

33

R32

R32

2.2R

2.2R

18

VCC

1 2

ISL6314CRZ

ISL6314CRZ

5

R340RR34

U11A

U11A

147

X_LVC14APWR_TSSOP14

X_LVC14APWR_TSSOP14

C17

C17

C1U25X0805

C1U25X0805

19

PVCC

22

BOOT

23

UGATE

24

PHASE

21

LGATE

16

ISEN+

15

ISEN-

14

ISENNO

13

OCSET

20

NC

10

VDIFF

8

DVC

9

FB

7

COMP

6

APA

0R

VCC3_SBVCC3_SB

U11B

U11B

147

X_LVC14APWR_TSSOP14

X_LVC14APWR_TSSOP14

3 4

+12V

R33

R33

2.2R

2.2R

R39 2.2_1%R39 2.2_1%

PHASE_CPU0

R45

R45

1.2KR1%0402

1.2KR1%0402

R47 X_220_1%_0402R47 X_220_1%_0402

R49 169R1%0402R49 169R1%0402

R50

R50

22KR1%0402-RH-1

22KR1%0402-RH-1

C37 C0.1u25Y0402-RHC37 C0.1u25Y0402-RH

R54 3K_1%R54 3K_1%

4

C19 C0.1u25Y0402-RHC19 C0.1u25Y0402-RH

R40 12KR1%0402-RH-1R40 12KR1%0402-RH-1

R42

R42

24KR1%0402

24KR1%0402

C24 C0.022u16X0402C24 C0.022u16X0402

C27 1000p_0402C27 1000p_0402

C36 C470p16X-1C36 C470p16X-1

R53 768R1%0402R53 768R1%0402

ALLPWRGD 16,21,27

10KR

10KR

R113

R113

C22 X_C0.1u25Y0402-RHC22 X_C0.1u25Y0402-RH

C25 X_2200pC25 X_2200p

C38 C0.01u16X0402C38 C0.01u16X0402

C10u25X51206-RH

C10u25X51206-RH

R35 0R0805R35 0R0805

R36 10KR0402R36 10KR0402C16

R37 0R0805R37 0R0805

ISEN_CPU0

C23

C23

C0.1u25Y0402-RH

C0.1u25Y0402-RH

VCCP

VCCP

3

VCCP

VCCP

VCCP

C15

C15

+12V

Stuff for ATOM Dual Core

Unstuff for ATOM Single Core

Q5

Q5

2

3

4

NN-SP8K10S_SOP8-RH

NN-SP8K10S_SOP8-RH

Q1

Q1

2

3

4

NN-SP8K10S_SOP8-RH

NN-SP8K10S_SOP8-RH

C139

C585

C585

C10u6.3X5-RH

C10u6.3X5-RH

C596

C596

C10u6.3X5-RH

C10u6.3X5-RH

C139

C1u10X50402-RH

C1u10X50402-RH

C149

C149

C1u10X50402-RH

C1u10X50402-RH

C211

C211

C1u10X50402-RH

C1u10X50402-RH

C142

C142

C1u10X50402-RH

C1u10X50402-RH

C150

C150

C1u10X50402-RH

C1u10X50402-RH

C160

C160

C1u10X50402-RH

C1u10X50402-RH

VCCP

+

+

12

C586

C586

C10u6.3X5-RH

C10u6.3X5-RH

C591

C591

X_C10u6.3X5-RH

X_C10u6.3X5-RH

2

81

7

6

5

81

7

6

5

EC46

EC46

C820u2.5SO-RH

C820u2.5SO-RH

C587

C587

X_C10u6.3X5-RH

X_C10u6.3X5-RH

C592

C592

C10u6.3X5-RH

C10u6.3X5-RH

C143

C143

C1u10X50402-RH

C1u10X50402-RH

C152

C152

C1u10X50402-RH

C1u10X50402-RH

C457

C457

C1u10X50402-RH

C1u10X50402-RH

C590

C590

C10u6.3X5-RH

C10u6.3X5-RH

C595

C595

C10u6.3X5-RH

C10u6.3X5-RH

R38

R38

2.2R0805

2.2R0805

C20

C20

1000p_0402

1000p_0402

PHASE_CPU0

ISEN_CPU0

C144

C144

C1u10X50402-RH

C1u10X50402-RH

C154

C154

C1u10X50402-RH

C1u10X50402-RH

C456

C456

C1u10X50402-RH

C1u10X50402-RH

1

CHOKE1

CHOKE1

1 2

CH-1.2u15A1.7m-RH

CH-1.2u15A1.7m-RH

SP1

SP1

X_PAD_0402

X_PAD_0402

C145

C145

C1u10X50402-RH

C1u10X50402-RH

C156

C156

C1u10X50402-RH

C1u10X50402-RH

C459

C459

C1u10X50402-RH

C1u10X50402-RH

4A/8A

VCCP

SP2

SP2

X_PAD_0402

X_PAD_0402

C147

C147

C1u10X50402-RH

C1u10X50402-RH

C158

C158

C1u10X50402-RH

C1u10X50402-RH

C458

C458

C1u10X50402-RH

C1u10X50402-RH

C40

C40

C10u25X51206-RH

C10u25X51206-RH

A A

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

<OrgAddr1>

<OrgAddr1>

<OrgAddr1>

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

VRM- Single Phase

VRM- Single Phase

VRM- Single Phase

MS-7445

MS-7445

MS-7445

2

0A

0A

0A

of

of

of

832Monday, December 29, 2008

832Monday, December 29, 2008

832Monday, December 29, 2008

1

8

H_A#[3..31]6

D D

H_ADSTB#06

H_ADSTB#16

H_REQ#[0..4]6

H_RS#[0..2]6

H_BR#06

H_BPRI#6

H_BNR#6

H_LOCK#6

H_ADS#6

H_HIT#6

H_HITM#6

H_DEFER#6

H_TRDY#6

H_DBSY#6

H_DRDY#6

CK_H_MCH16

CK_H_MCH#16

PWR_GD21,27,29

H_CPURST#6

ICH_SYNC#

HXRCOMP

MCH_GTLREF_CPU

HXSCOMP

HXSWING

C C

B B

PCIRST_ICH7#20,29

ICH_SYNC#21

R59 16.9R1%R59 16.9R1%

Rule:

HXRCOMP_N_10/7/7

HXSCOMP_N_5/8/8

HSWING_N_15/10/10

A A

R63

V_FSB_VTT

R63

_60.4R1%-1

_60.4R1%-1

8

C46

C46

X_C2.2P50N

X_C2.2P50N

7

N17

P17

P18

P20

P21

AA22

AB21

AB22

AB23

AC22

AD14

U15A

U15A

H_A#3 H_D#0

J39

HA3#

H_A#4

K38

VCC

VCC

VCC

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

AA37

AA41

AJ12

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

U34

U32

U35

M36

D42

U39

U40

W42

D41

G37

U41

W41

W40

U42

M31

M29

C30

M18

C27

D27

D28

J42

K35

J37

V33

V42

Y36

Y38

V32

Y34

V35

F38

E41

K36

E42

P40

V41

Y40

T40

Y43

T43

AJ9

A28

B27

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

VCC

AA35

T30T30

T32T32

T33T33

V_FSB_VTT

AF6

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

L15

U27

R27

M15

AA42

AA34

AA38

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/3*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R61

HXSCOMP

R61

301R1%

301R1%

R66

R66

84.5R1%

84.5R1%

C47

C47

C0.1u10Y

C0.1u10Y

AF7

AF8

AF9

AF10

AF11

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

A43

M11

AG25

AG26

AG27

R64 62RR64 62R

6

V_1P5_CORE

AF12

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AH1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AJ24

AJ27

AL39

AK40

AY14

BC16

AD30

AC34

AW17

AW18

HXSWING

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

Y30

Y33

V31

U30

AF31

AA30

AC30

AD31

5

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

NC

NC

NC

NC

NC

AK21

AJ23

AJ26

AL29

AL20

AJ21

AL26

AJ29

AK27

AG29

V_FSB_VTT

V30

BC2NCBC1

BC43NCBC42

R60

R60

124R1%

124R1%

R62 10RR62 10R

R65

R65

210R1%

210R1%

BB2NCBB1NCBA2

AW2

BB43

AW26

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

C43

C43

C0.1u10Y

C0.1u10Y

U20

VCC

NC

AV27NCAV26

U21

VCC

NC

U22

U23

VCC

VCC

NC

E35

C42

C44

C44

X_C220P50N

X_C220P50N

VCC

NC

U24

VCC

NCC2NC

4

U25

U26

VCC

VCC

B43NCB42NCB41

V15

V17

VCC

V18

VCC

VCC

NCB3NCB2NC

V19

A42

V20

V21

V22

VCC

VCC

VCC

VCC

VCC

VCC

Y17

Y18

MCH_GTLREF_CPU

3

V23

V25

V27

W17

W18

W19

W20

W22

W24

W26

W27

Y15

M17

P41

HD0#

H_D#1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y19

Y21

Y23

Y25

Y27

AA15

AA17

AA18

AA19

AA20

C45

C45

C0.1u10Y

C0.1u10Y

VCC

VCC

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

KDINV_0#

HDINV_1#

HDINV_2#

HDINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

(INTEL-QG82945G-A2)

(INTEL-QG82945G-A2)

V_1P5_CORE

M39

H_D#2

P42

H_D#3

M42

H_D#4

N41

H_D#5

M40

H_D#6

L40

H_D#7

M41

H_D#8

K42

H_D#9

G39

H_D#10

J41

H_D#11

G42

H_D#12

G40

H_D#13

G41

H_D#14

F40

H_D#15

F43

H_D#16

F37

H_D#17

E37

H_D#18

J35

H_D#19

D39

H_D#20

C41

H_D#21

B39

H_D#22

B40

H_D#23

H34

H_D#24

C37

H_D#25

J32

H_D#26

B35

H_D#27

J34

H_D#28

B34

H_D#29

F32

H_D#30

L32

H_D#31

J31

H_D#32

H31

H_D#33

M33

H_D#34

K31

H_D#35

M27

H_D#36

K29

H_D#37

F31

H_D#38

H29

H_D#39

F29

H_D#40

L27

H_D#41

M24

H_D#42

J26

H_D#43

K26

H_D#44

G26

H_D#45

H24

H_D#46

K24

H_D#47

F24

H_D#48

E31

H_D#49

A33

H_D#50

E40

H_D#51

D37

H_D#52

C39

H_D#53

D38

H_D#54

D33

H_D#55

C35

H_D#56

D34

H_D#57

C34

H_D#58

B31

H_D#59

C31

H_D#60

C32

H_D#61

D32

H_D#62

B30

H_D#63

D30

K40

A38

E29

B32

K41

L43

F35

G34

J27

M26

E34

B37

CAPS SHOULD BE PLACED NEAR MCH PIN

7

6

5

4

3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

2

H_D#[0..63] 6

H_DBI#[0..3] 6

H_DSTBP#0 6

H_DSTBN#0 6

H_DSTBP#1 6

H_DSTBN#1 6

H_DSTBP#2 6

H_DSTBN#2 6

H_DSTBP#3 6

H_DSTBN#3 6

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - CPU

Intel Lakeport - CPU

Intel Lakeport - CPU

MS-7445

MS-7445

MS-7445

2

1

0A

0A

0A

of

of

of

932Friday, December 26, 2008

932Friday, December 26, 2008

932Friday, December 26, 2008

1

8

7

6

5

4

3

2

1

DATA_A51

AE40

AJ34

SADQ51

SBDQ49

DATA_A52

AM41

SADQ52

SBDQ50

AF32

DATA_A53

AM42

AF34

DQM_A[0..7]13

DQM_A6

DQM_A1

DQM_A4

DQM_A2

DQM_A7

DQM_A3

SBCKE2

BA13

BB13

DQM_A5

DQM_A0

AC40

AG40

AP39

AT34

AP18

BB10

AY2

AR3

SADM6

SADM5

SADM4

SADM3

SADM2

SADM1

SADM0

SBDM2

SBDM3

SBDM4

SBDM5

SBDM6

SBDM7

SBCKE3

AJ39

AP13

AP23

AR29

AR38

AD39

SADM7

SBDQS0#

SBDQS1#

SBDQS2#

SBDQS3#

SBDQS4#

SBDQS5#

SBDQS6#

SBDQS7#

SMVREF1

SMVREF0

SBDM1

AW7

AL11

SBCS0#

SBCS1#

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS1

SBDQS2

SBDQS3

SBDQS4

SBDQS5

SBDQS6

SBDQS7

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SBDM0

BA40

AW41

BA41

AW40

BA23

AY24

BB23

BB22

BB21

BA21

AY21

BC20

AY19

AY20

BA18

BA19

BB18

BA22

BB17

BA17

AW42

AY42

AV40

AV43

AU40

AW23

AY23

AY17

AM8

AM6

AV7

AR9

AV13

AT13

AU23

AR23

AT29

AV29

AP36

AM35

AG34

AG32

AD36

AD38

AM29

AM27

AV9

AW9

AL38

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

AM2

AM4

MCH_VREF_A

PLACE 0.1UF CAP CLOSE TO MCH

C49

C49

C0.1u10Y

C0.1u10Y

0B Change 20

R411 0R0402R411 0R0402

DATA_A56

DATA_A61

DATA_A62

DATA_A57

DATA_A60

DATA_A58

DATA_A54

DATA_A55

AF41

AF42

SADQ53

SADQ54

SADQ55

SBDQ51

SBDQ52

SBDQ53

AJ32

AL31

AD40

SADQ56

SBDQ54

AG35

DATA_A63

DATA_A59

AD43

AA39

SADQ57

SADQ58

SBDQ55

SBDQ56

AD32

AC32

AA40

AD34

SCKE_A1

SCKE_A0

AE42

AE41

AB41

AB42

BB25

AY25

BC24

BA25

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

SACKE0

SACKE1

SACKE2

SACKE3

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

SBCKE0

SBCKE1

Y32

AF35

AF37

AA32

BA14

AY16

AC33

AC35

DATA_A[0..63]13

DATA_A16

DATA_A21

SADQ17

SBDQ15

DATA_A18

BA12

SADQ18

SBDQ16

AM15

DATA_A19

BB12

AM13

DATA_A24

DATA_A25

DATA_A26

DATA_A22

DATA_A23

DATA_A20

BA9

SADQ19

SBDQ17

AV15

SADQ20

SBDQ18

BB9

SADQ21

SBDQ19

AM17

DATA_A27

BC11

AY12

AM20

AM18

AV20

AM21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

AT15

AP15

AN12

AR13

AM24

AM23

SADQ27

SBDQ25

DATA_A28

AP17

AV24

DATA_A34

DATA_A32

DATA_A31

DATA_A35

AR17

SADQ29

SBDQ27

AM26

DATA_A30

AP20

AP21

DATA_A36

DATA_A33

AT20

AP32

AV34

AV38

AU39

AV32

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

AT24

AP24

AR21

AU27

AN29

AR31

DATA_A29

SADQ28

SBDQ26

DATA_A6

DATA_A0

DATA_A1

DATA_A3

D D

SCS_A#[0..1]13,14

RAS_A#13,14

CAS_A#13,14

MAA_A[0..13]13,14

C C

B B

ODT_A[0..1]13,14

SBS_A[0..2]13,14

DQS_A013

DQS_A#013

DQS_A113

DQS_A#113

DQS_A213

DQS_A#213

DQS_A313

DQS_A#313

DQS_A413

DQS_A#413

DQS_A513

DQS_A#513

DQS_A613

DQS_A#613

DQS_A713

DQS_A#713

P_DDR0_A13

N_DDR0_A13

P_DDR1_A13

N_DDR1_A13

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

WE_A#13,14

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

SMPCOMP_N

SMPCOMP_P MCH_VREF_B

Rule:

U15B

U15B

BB37

SACS0#

BA39

SACS1#

BA35

SACS2#

AY38

SACS3#

BA34

SARAS#

BA37

SACAS#

BB35

SAWE#

BA32

SAMA0

AW32

SAMA1

BB30

SAMA2

BA30

SAMA3

AY30

SAMA4

BA27

SAMA5

BC28

SAMA6

AY27

SAMA7

AY28

SAMA8

BB27

SAMA9

AY33

SAMA10

AW27

SAMA11

BB26

SAMA12

BC38

SAMA13

AW37

SAODT0

AY39

SAODT1

AY37

SAODT2

BB40

SAODT3

BC33

SABA0

AY34

SABA1

BA26

SABA2

AU4

SADQS0

AR2

SADQS0#

BA3

SADQS1

BB4

SADQS1#

AY11

SADQS2

BA10

SADQS2#

AU18

SADQS3

AR18

SADQS3#

AU35

SADQS4

AV35

SADQS4#

AP42

SADQS5

AP40

SADQS5#

AG42

SADQS6

AG41

SADQS6#

AC42

SADQS7

AC41

SADQS7#

BB32

SACLK0

AY32

SACLK0#

AY5

SACLK1

BB5

SACLK1#

AK42

SACLK2

AK41

SACLK2#

BA31

SACLK3

BB31

SACLK3#

AY6

SACLK4

BA5

SACLK4#

AH40

SACLK5

AH43

SACLK5#

AL5

MCH_SRCOMP0

AJ6

MCH_SRCOMP1

AJ8

SMOCDCOMP0

AM3

SMOCDCOMP1

(INTEL-QG82945G-A2)

(INTEL-QG82945G-A2)

DATA_A2

AP3

AP2

AU3

AV4

SADQ0

SADQ1

SADQ2

SBDQ0

AL6

AL8

SMPCOMP_N_12mils

DATA_A10

DATA_A8

DATA_A7

DATA_A9

DATA_A4

DATA_A5

AN1

AP4

AU5

AU2

AW3

AY3

BA7

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

AL9

AP8

AP9

AP6

AU7

AJ11

AM10

DATA_A17

DATA_A14

DATA_A15

DATA_A12

DATA_A11

DATA_A13

BB7

AV1

AW4

BC6

AY7

AW12

AY10

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

AV6

AR5

AR7

AV12

AR12

AR10

AM11

SCKE_A[0..1]13,14

DATA_A37

DATA_A38

AT32

SADQ36

SADQ37

SBDQ34

SBDQ35

AM31

AR34

SADQ38

SBDQ36

AP27

DATA_A39

AU37

AR27

DATA_A45

AN43

AP35

SADQ42

SBDQ40

DATA_A43

AM40

SADQ43

SBDQ41

AP37

DATA_A44

DATA_A49

DATA_A48

DATA_A47

DATA_A46

DATA_A50

AU41

AU42

AP41

AN40

AL41

AL42

AF39

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

AL35

AL34

AN32

AR35

AU38

AM38

AM34

DATA_A41

DATA_A42

DATA_A40

AR41

AR42

SADQ39

SADQ40

SADQ41

SBDQ37

SBDQ38

SBDQ39

AP31

AU31

SMPCOMP_P_12mils

VCC_DDR

R67 1KR1%R67 1KR1%

A A

VCC_DDR

R69 80.6R1%R69 80.6R1%

C50

C50

C0.1u10Y

C0.1u10Y

8

7

R70 80.6R1%R70 80.6R1%

SMPCOMP_PSMPCOMP_N

MSI

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Date: Sheet

Date: Sheet

6

5

4

3

Date: Sheet

2

MCH_VREF_A

C48

R68

R68

1KR1%

1KR1%

PLACE 0.1UF CAP CLOSE TO MCH

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

MICRO-STAR INt'L CO., LTD.

Intel Lakeport - Memory

Intel Lakeport - Memory

Intel Lakeport - Memory

MS-7445

MS-7445

MS-7445

C48

C0.1u10Y

C0.1u10Y

10 32Monday, December 29, 2008

10 32Monday, December 29, 2008

10 32Monday, December 29, 2008

1

0A

0A

0A

of

of

of

Loading...

Loading...