MSI MS-7409 Schematic 0904

5

4

3

2

1

MSI

MS-7409 Ver:0A

D D

C C

B B

CPU:

AMD M2 Athlon 64

System Chipset:

ATI RS690

ATI SB600

On Board Chipset:

WINBOND Super I/O -- W83627DHG

LAN*1 -- Realtek 8111B/8111C

HD Codec --ALC888

BIOS -- SPI ROM 8M

Main Memory:

DDR * 1 (Max 2GB)

Expansion Slots:

MINI PCI-E*1

PCI 2.2 Slot X 1

PWM:

Controller--Intersil ISL6312CR 3 Phase

Clock Generator:

Controller--ICS951464AGLFT

Title Page

Cover Sheet 1

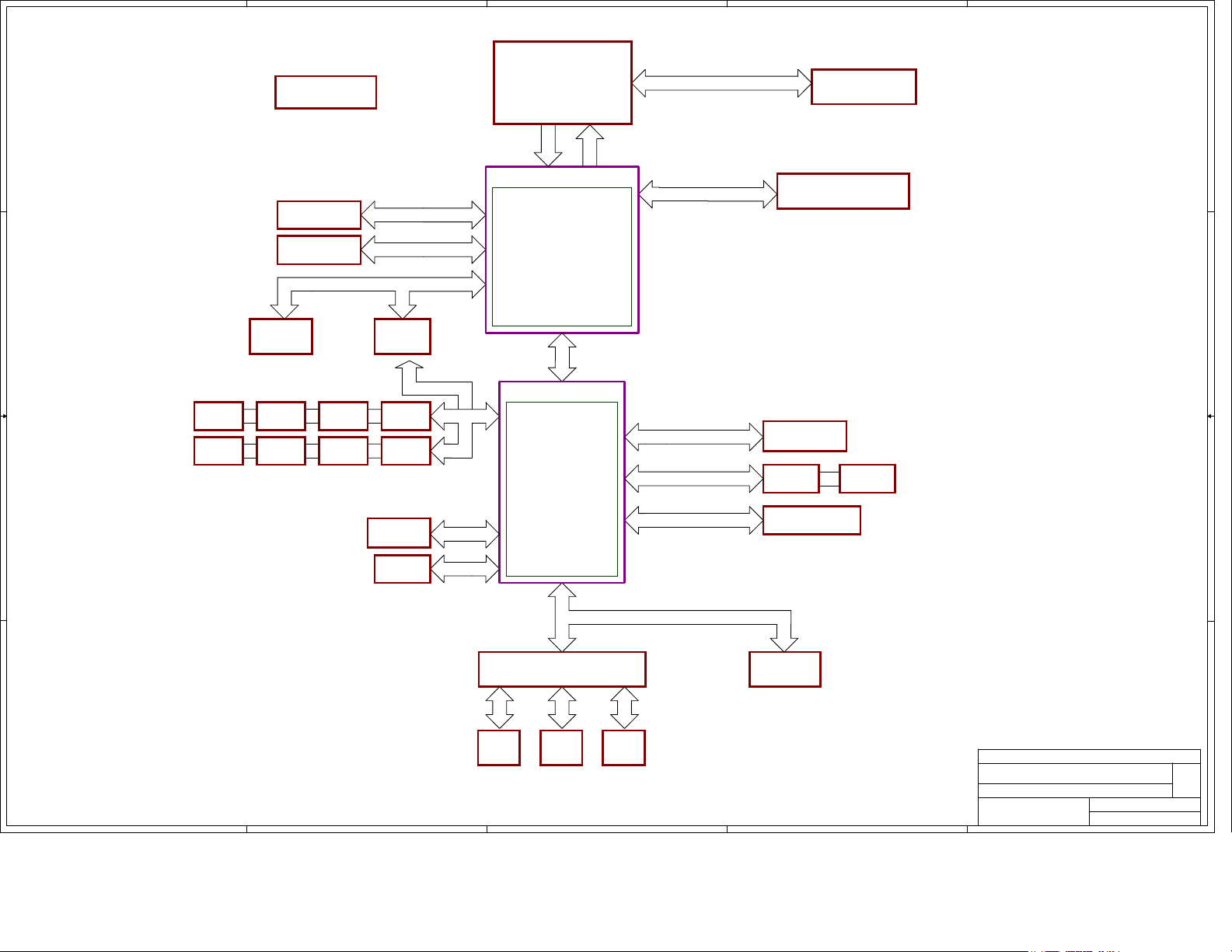

Block Diagram

SB600 GPIO Config

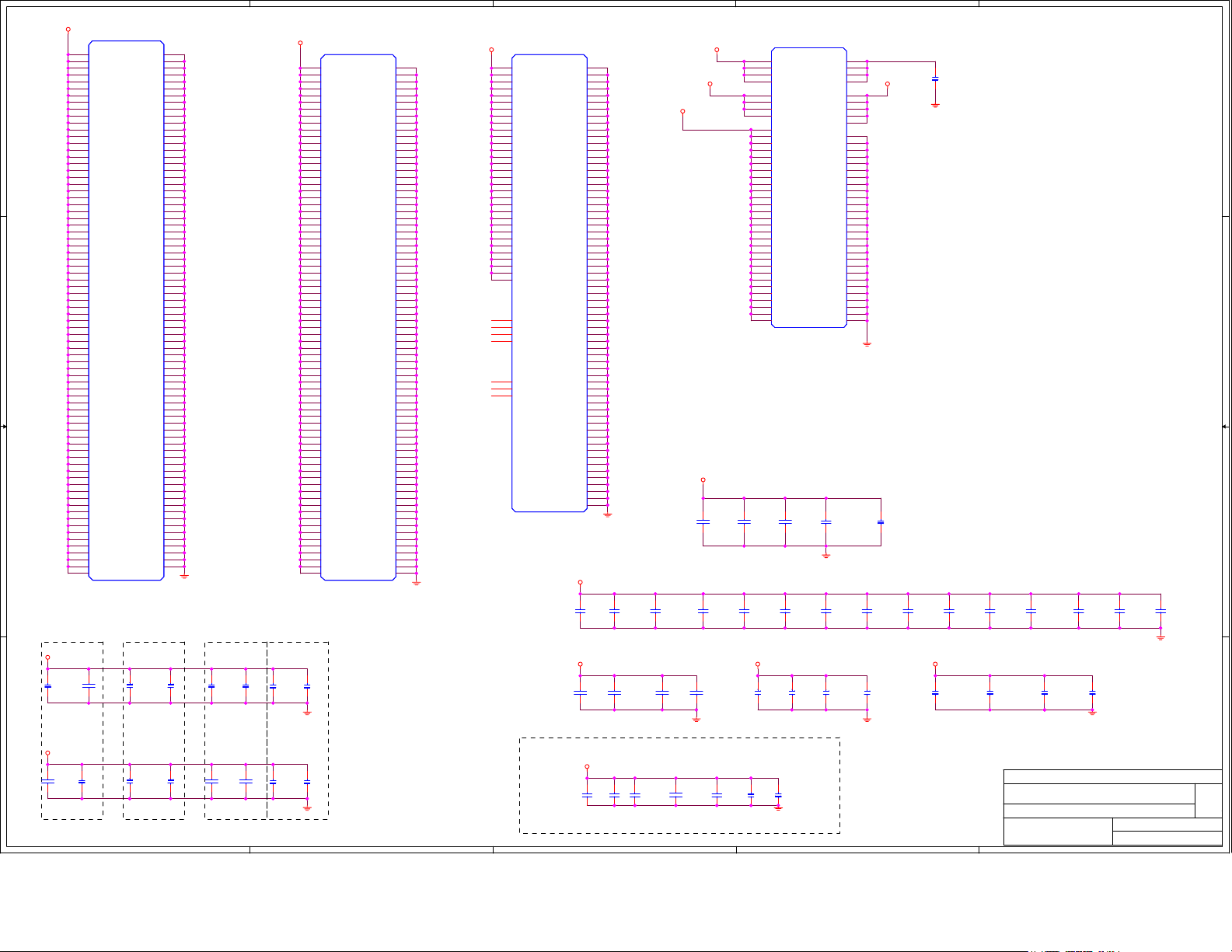

AMD M2 940

SYSTEM Memory

DDR Terminations

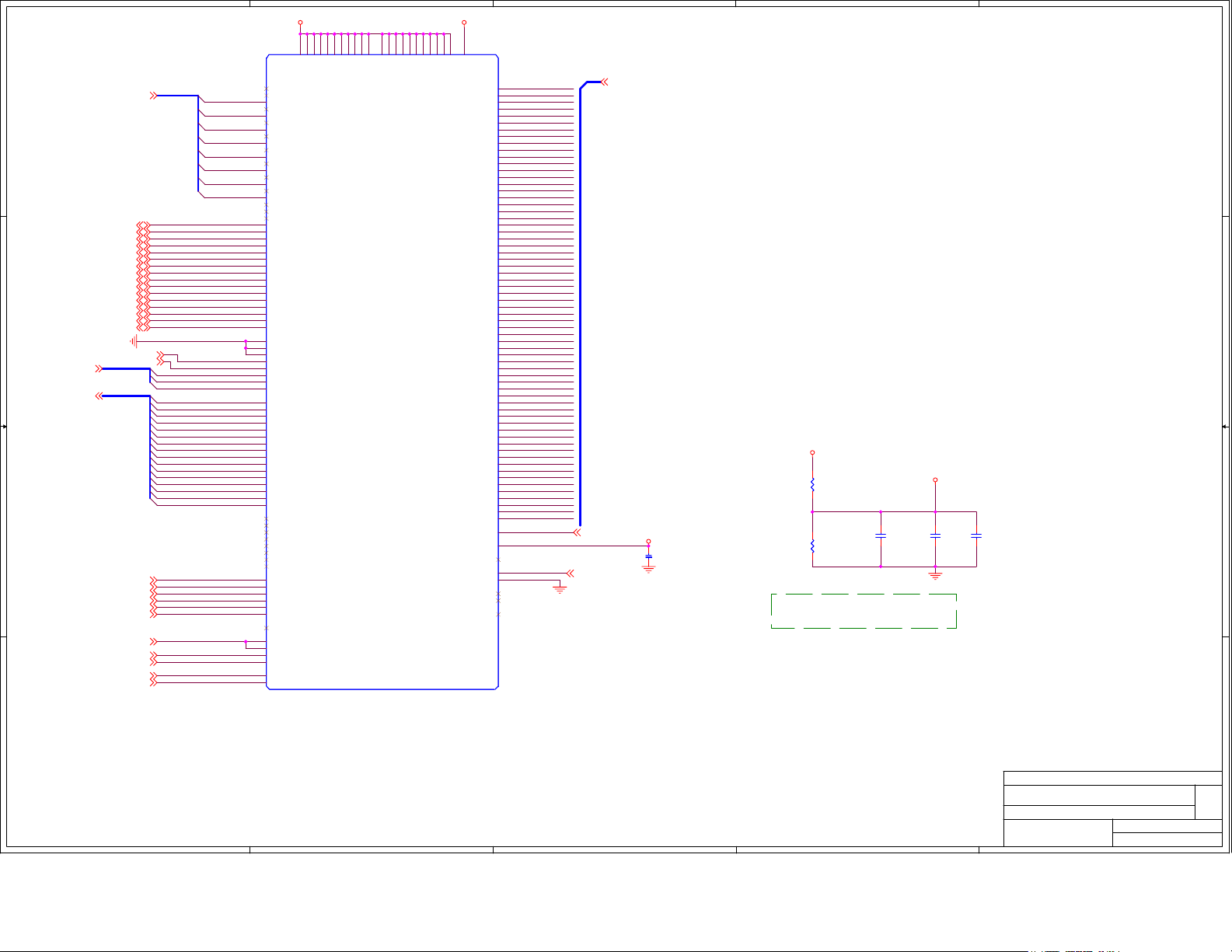

ATI RS690

CLOCK Generator ICS 951464

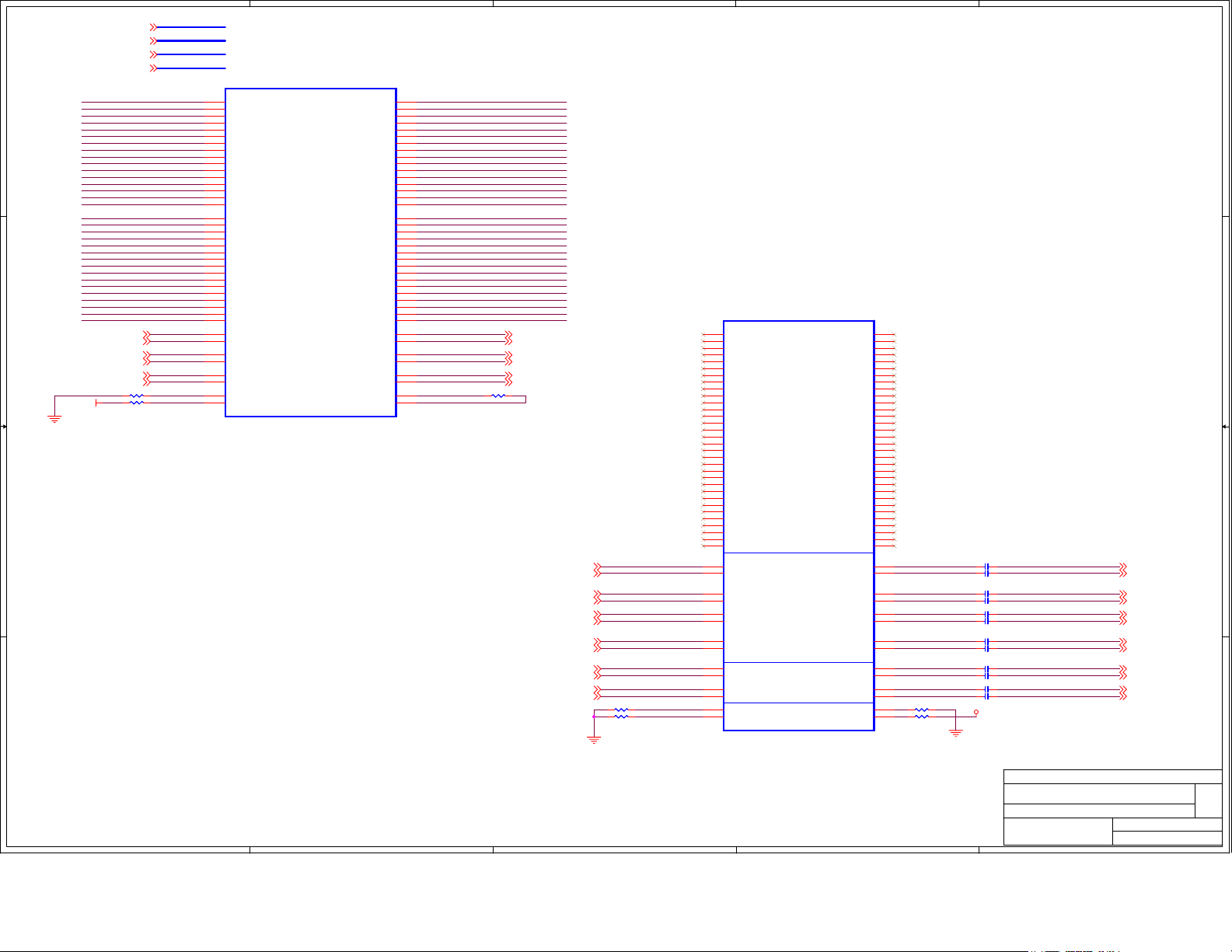

ATI SB600

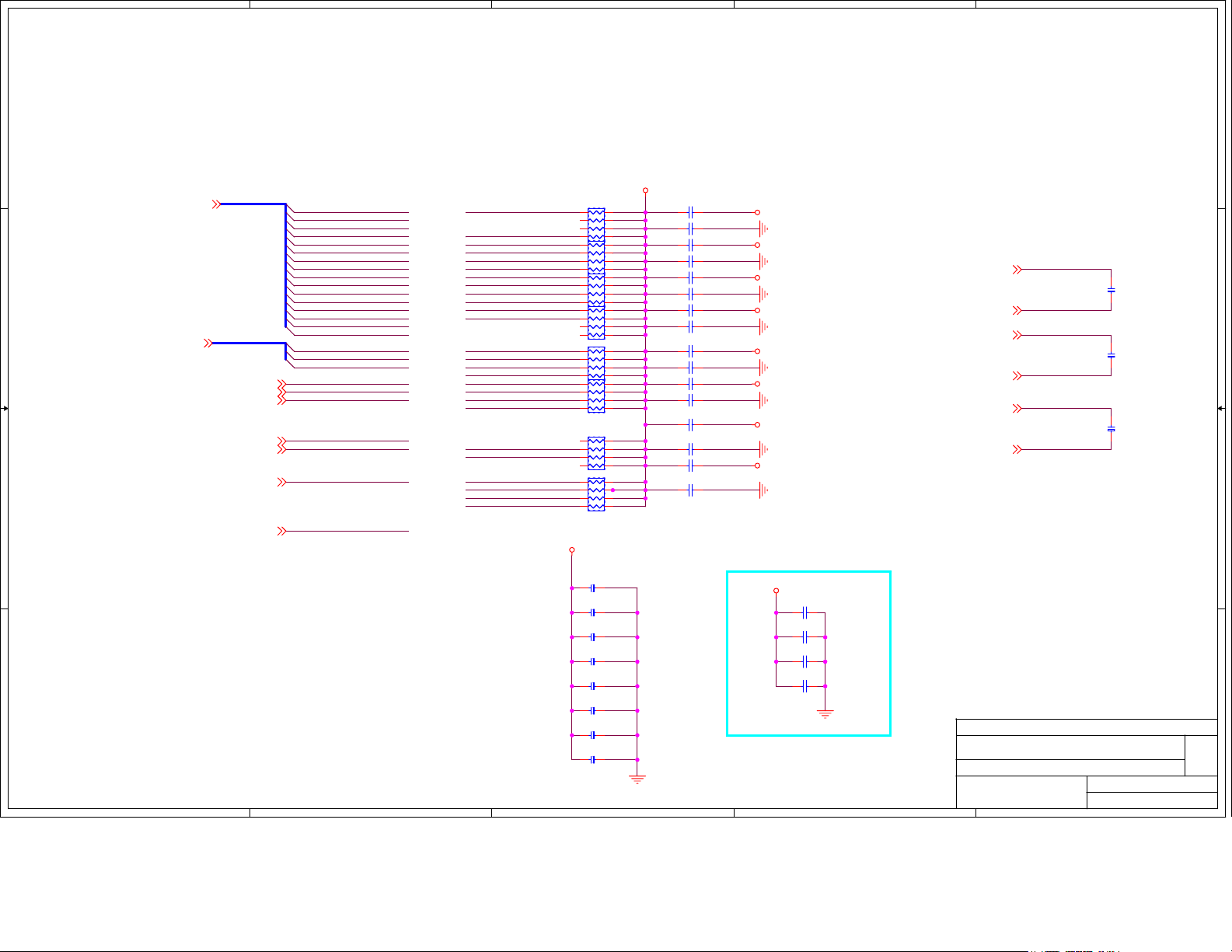

PCI-Express X 1,PCI SLOT1

LAN*1 Realtek 8111B/8111C

LPC SUPER I/O& COM PORT

FAN/KB&MS

HD Audio - ALC888

USB connectors

HDMI & VGA Connector

ATX Connector / Front Panel /EMI

MS-6 ACPI Controller & MS-6+

MS- 11 DDR2 1.8V POWER

PWM - ISL6312CR

RESERVE

MANUAL PARTS

GPIO&JUMPER/Option Part

POWER OK MAP

POWER MAP

RESET MAP

History

2

3

4,5,6

7

8

9-11

12

13-16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

Cover Sheet

Cover Sheet

Cover Sheet

1

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Sheet

Sheet

Sheet

Rev

Rev

Rev

0A

0A

0A

of

134

of

134

of

134

5

4

3

2

1

128bits

EXTERNAL CLOCK GENERATOR

ICS951464

D D

AMD

M2

M2 SOCKET

OUT

16x16

IN

DDRII

400,533,667,800

HyperTransport

UNBUFFERED

DDRII DIMM1

HDMI

VGA CON

HDMI

CRT

ATI NB - RS690

HyperTransport LINK0 CPU I/F

INTEGRATED GRAPHICS

DDR2 MEMORY (X16)

LVTM(RS690)

DDR2 400/533/667/800

DDR2 MEMORY DEVICE

4MX16X4 84-PIN FBGA

1 16X PCIE VIDEO I/F

X1 PCIE INTERFACE

C C

Gb LAN

Realtek

8111C

MINI PCIE

1 X4 PCIE I/F WITH SB

4 1X PCIE I/F(RS690)

VER:A12

PCIE

X4

USB#3

USB#1USB#2

USB#6USB#7 USB#5

USB#0

USB#4

USB#8

USB 2.0

ATI SB - SB600

USB2.0 (10)

SATA II (2 PORTS)

AZALIA HD AUDIO

ATA 66/100/133

SPI I/F

LPC I/F

HD AUDIO I/F

SATA II I/F

AZALIA CODEC

ALC888

SATA#0

SATA#1

ACPI 1.1

B B

SPI ROM

PCI SLOT

SPI I/F

PCI BUS

INT RTC

HW MONITOR

PCI/PCI BDGE

ATA 66/100/133 I/F

IDE CONNECTOR

VER:A21

LPC BUS

Winbond LPC SIO W83627DHG

A A

5

4

PWM

SMART

FAN*2

KBD

MOUSE

COM

PORT

* 2

3

TPM MODULE

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

Block Diagram

Block Diagram

Block Diagram

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

2

2

2

Rev

Rev

Rev

0A

0A

0A

34

34

34

of

of

of

5

4

3

2

1

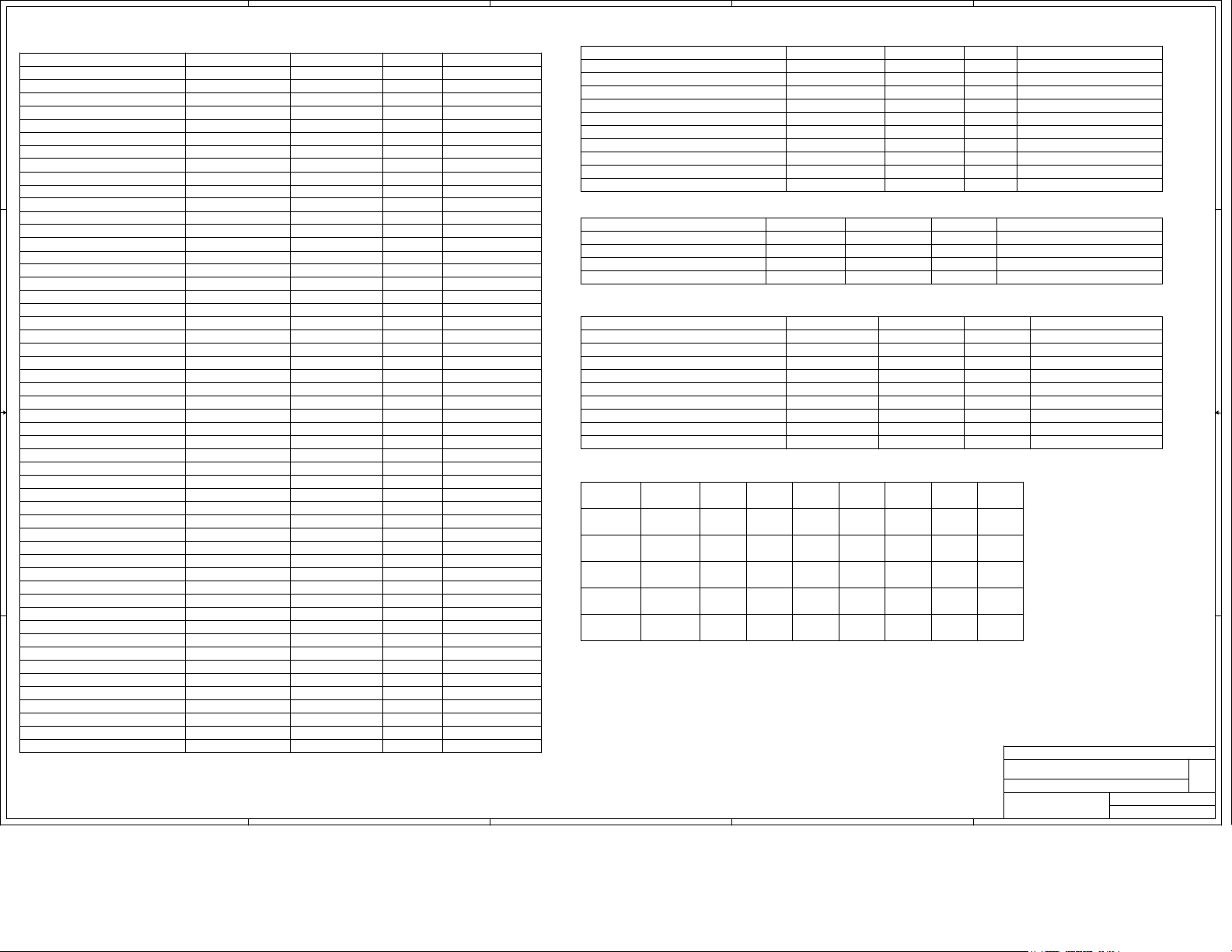

SB600 GPIO Config.

GPIO Pin

SSMUXSEL

ROM_CS#/

SPKR/

D D

FANOUT0/

SMARTVOLT/SATA_IS2#/

SHUTDOWN#/

GHI#

WD_PWRGD/

DDC1_SDA/

DDC1_SCL/

SATA_IS0#/

SPI_DO

SPI_DI

LAN_RST#

ROM_RST#

IDE_D[0..15]

SPI_HOLD#

SPI_CS#

INTE#

C C

INTF#

INTG#

INTH#

DPSLP_OD#

AC_BITCLK

AC_SDOUT

AC_SYNC

SPDIF_OUT

ACZ_SDIN0

ACZ_SDIN1

ACZ_SDIN2

AC_RST#

AC_SDIN3

SPI_CLK

FANOUT1/

B B

FANOUT2/

FANIN0/

FANIN1/

FANIN2/

VIN[0..7]/

TEMPIN0/

TEMPIN1/

TEMPIN2/

TEMPIN3/TALERT#/

BMREQ#/REQ5#/

LLB#/

SATA_ACT#

LDRQ1#/GNT5#/

RTC_IRQ#/

REQ3#

A A

REQ4#

GNT3#

GNT4#

/SATA_IS3#/GPIO0

GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

/SATA_IS1#/GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

/GPIO11

/GPIO12

/GPIO13

/GPIO14

/GPIO[15..30]

/GPIO31

/GPIO32

/GPIO33

/GPIO34

/GPIO35

/GPIO36

/GPIO37

/GPIO38

/GPIO39

/GPIO40

/PCICLK7/GPIO41

/GPIO42

/GPIO43

/GPIO44

/GPIO45

/GPIO46

/GPIO47

GPIO48

GPIO49

GPIO50

GPIO51

GPIO52

GPIO[53..60]

GPIO61

GPIO62

GPIO63

GPIO64

GPIO65

GPIO66

/GPIO67

GPIO68

GPIO69

/GPIO70

/GPIO71

/GPIO72

/GPIO73

5

Type

I/OD(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/OD(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

OD(3.3V)

I/O(3.3V)

I/O(S5_3.3V)/VBAT

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

I/O(3.3V)

Default Power

Output(Low)

by Strapping

Input(TS)

Input(PU)

Input(TS)

Input(TS)

Output(TS)

by Strapping

Input(TS)

Input(TS)

Input(TS)

Output(PD)

Output(PD)

Standby

Standby

Output(Low)

Output(Low)

Output(High)

Input(PU)

Input(PU)

Standby

Standby

Input(PU)

Input(PU)

Input(PU)

Input(PU)

Input(TS)

Input(PD)

Output(Low)

Output(Low)

Output(Low)

Input(PD)

Input(PD)

Input(PD)

Output(Low)

Input(PD)

Input(PD)

Standby

Standby

Standby

Standby

Standby

Standby

Input(PU)

Input(PU)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(TS)

Input(PU)

Standby

Output(TS)

Input(PU)

Input(PU)

Standby

Input(PU)

Input(PU)

Output(TS)

Output(TS)

4

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Main

Function

NC

NC

NC

NC

NC

NC

GHI#

NC

NC

PD_DET

NC

SPI_DATAOUT

SPI_DATAIN

LAN_RST#

NC

IDE_D[0..15]

SPI_HOLD#

SPI_CS#

INTE#

INTF#

INTG#

INTH#

TP16

NC

AC_SDATA_OUT

NC

NC

AZ_SDIN0

NC

NC

NC

GPIO46

SPI_CLK

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

(Program to Output)

NC

TALERT#

BMREQ#

NC

SATA_ACT#

NC

AUTO_ON#

NC

NC

NC

NC

(Not Default)

(Not Default)

(Not Default)

(Not Default)

(Not Default)

SB600 GPM Config.

GPM Pin Type Function

USB_OC0#/

USB_OC1#/

USB_OC2#/

USB_OC3#/

USB_OC4#/

USB_OC5#/DDR3_RST#/

BLINK/

SYS_RESET#/

USB_OC8#/AZ_DOCK_RST#/

USB_OC9#/SLP_S2#/

GPM#0

GPM#1

GPM#2

GPM#3

GPM#4

GPM#5

GPM#6

GPM#7

GPM#9

GPM#8

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O/OD(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

SB600 GPOC Config.

GPOC Pin Type Function

GPOC0#

SCL0/

SDA0/

SCL1/

SDA1/

GPOC1#

GPOC2#

GPOC3#

I/O(3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

Default

Input(TS)

Input(TS)

Input(TS)

Input(TS)

SB600 EXTEVENT & GEVENT Config.

GPM Pin Type Function

EXTEVENT0#

RI#/

LPC_SMI#/

SMBALERT#/ /GEVENT2#

LPC_PME#/

PCI_PME#/

S3_STATE/

USB_OC6#/

USB_OC7#/

WAKE#/

EXTEVENT1#

THRMTRIP#

GEVENT3#

GEVENT4#

GEVENT5#

GEVENT6#

GEVENT7#

GEVENT8#

I/O(S5_3.3V)

I/O(3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

I/O(S5_3.3V)

PCI Config.

IEEE 1394

GIGA LAN

PCI1

PCI2

Super I/O

3

CLOCK

REQ# GNT# INTA# INTB# INTC# INTD#

IDSEL

2

Default Power

Input(PU)

Input(PU)

Input(PU)

Input(PU)

Output(Low)

Input(PU)

Input(PU)

Input(PU)

Input(PU)

Input(PD)

Power

Main

Main

Standby

Standby

Default

Input(PU)

Input(PU)

Input(PU)

Input(PU)

Input(PU)

by Strapping

Input(PU)

Input(PU)

Input(PU)

Standby

Standby

Standby

Standby

Standby

Standby

Standby

Standby

Standby

Standby

Power

Standby

Main

Standby

Standby

Standby

Standby

Standby

Standby

Standby

USB OverCurrent for PORT0,1,2,3

USB OverCurrent for PORT4,5,6,7

NC

NC

WLAN_PWRON

(Not Default)

GPM6#

SYS_RESET#

(Not Default)

NC

NC

SMBUS1

SMBUS1

SMBUS2

SMBUS2

(Not Default)

(Not Default)

(Not Default)

(Not Default)

NC

NC

THRMTRIP#

LPC_PME#

PCI_PME#

(Reserved)

(Not Default)

(Not Default)

NC

NC

NC

PCIE_WAKE#

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

POWER DELIVERY CHART

POWER DELIVERY CHART

POWER DELIVERY CHART

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

(Not Default)

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Sheet

Sheet

Sheet

1

(Not Default)

(Not Default)

Rev

Rev

Rev

0A

0A

0A

of

of

of

334

334

334

5

4

3

2

1

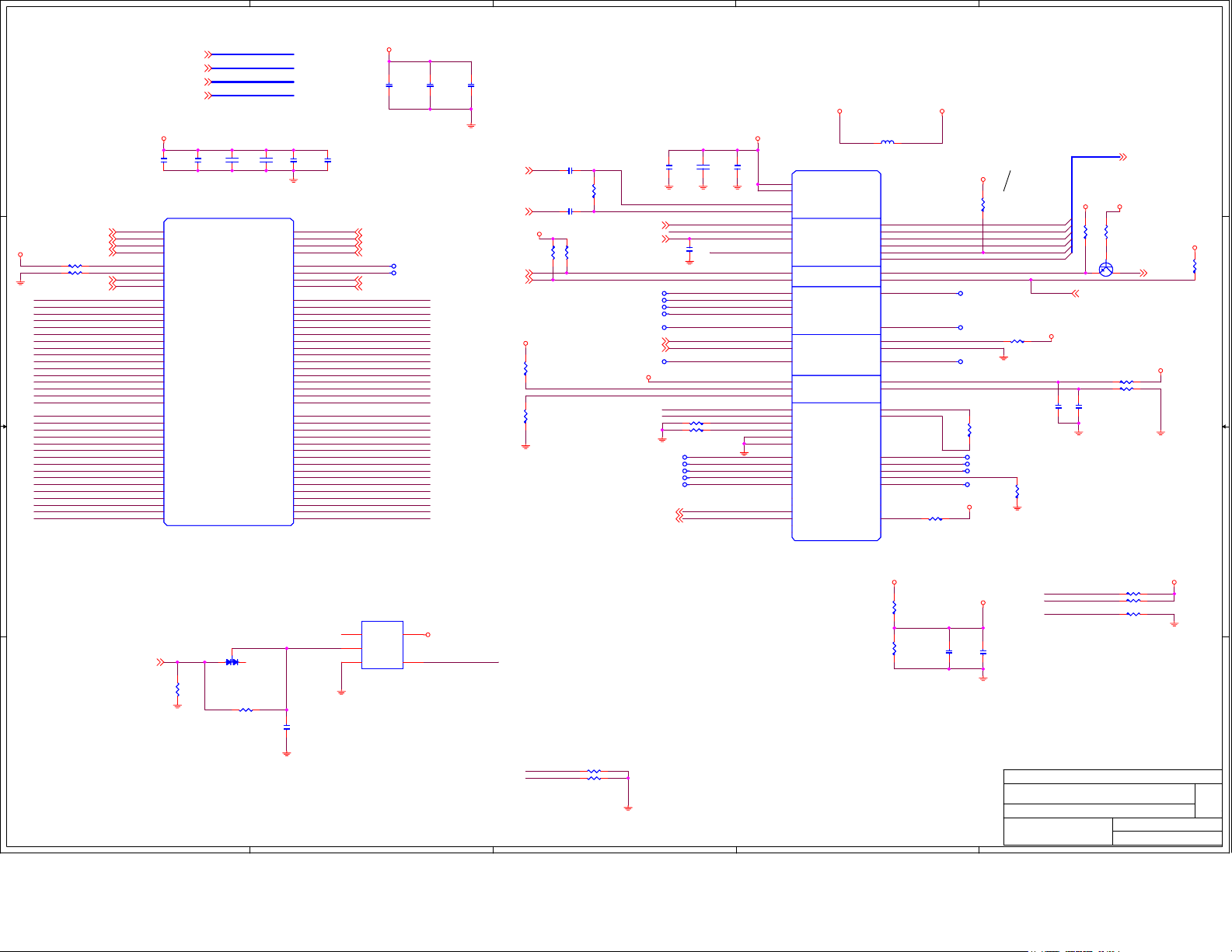

VCCA_1V2

C275

C275

X_C180P50N0402

X_C180P50N0402

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3HT_CADIN_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

OE

OE

1

A

A

2

GND

GND

3

SN74LVC1G17

SN74LVC1G17

4

C263

C263

X_C180P50N0402

X_C180P50N0402

TP29TP29

TP28TP28

U30

U30

VCC

VCC

5

Y

Y

4

C264

C264

C180P50N0402

C180P50N0402

+1.8V_S0

CPU_LDTSTOP#

VDDA25VDDA_25

C4.7U10Y0805

R123

R123

169R1%0402

169R1%0402

LDT_PWRGD13

THERMDC_CPU19

THERMDA_CPU19

3

C4.7U10Y0805

LDT_RST#13

COREFB+27

COREFB-27

C171

VCC_DDR

R174

R174

300/4

300/4

R180

R180

39.2R1%0402

39.2R1%0402

R170

R170

39.2R1%0402

39.2R1%0402

LDT_RST#

LDT_PWRGD

C171

C3900P25X

C3900P25X

C170

C170

C3900P25X

C3900P25X

M_ZN

M_ZP

R173

R173

300/4

300/4

R160 680R160 680

R161 680R161 680

CPU_CLK12

CPU_CLK#12

CPU_SIC13

CPU_SID13

VCC_DDR

C155

C155

CPUCLKIN

CPUCLKIN#

C244

C244

X_102P/50V/X7R/4

X_102P/50V/X7R/4

TP20TP20

TP24TP24

TP30TP30

TP19TP19

TP12TP12

TP10TP10

CPU_M_VREF

TP6TP6

TP7TP7

TP11TP11

TP9TP9

TP26TP26

C163

C163

0.22u_10V_0402

0.22u_10V_0402

R121 300/4R121 300/4

R116 300/4R116 300/4

C180

C180

3300P/50V/4

3300P/50V/4

LDT_PWRGD

CPU_LDTSTOP#

LDT_RST#

CPU_PRESENT_L

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

COREFB+

COREFBCPU_VTT_SENSE

CPU_TEST25_H

CPU_TEST25_L

VDDA25

C10

D10

AK6

AL10

AJ10

AH10

AH11

AJ11

AH9

AG9

AG8

AH7

A8

B8

C9

D8

C7

AL3

AL6

AL9

A5

G2

G1

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

E5

AJ5

AJ6

CPU1D

CPU1D

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

ZIF-SOCKET940

ZIF-SOCKET940

MISC

MISC

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

PSI_L

TEST8

2

80S/0805

80S/0805

2 1

TDO

16.9 1%

16.9 1%

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

VCC_DDR

R112

R112

L18

L18

Required for compatibility

with future processors

VID5

VID4

VID3

VID2

VID1

VID0

CPU_THRIP_L#

PROCHOT_L

CPU_TDO

CPU_DBRDY

CPU_VDDIOFB_H

CPU_PSI_L

HTREF1

HTREF0

TEST29H

TEST29L

R172 300/4R172 300/4

R111

R111

16.9 1%

16.9 1%

C151

C151

0.1u/10V/4

0.1u/10V/4

VCC_DDR

TP23TP23

TP4TP4

TP8TP8

VCC_DDR

CPU_M_VREF

R117

R117

300/4

300/4

From SIO for System-Initiated throttling

R417

R417

VCC_DDR

300/4

300/4

C243

C243

102P/50V/X7R/4

102P/50V/X7R/4

R122

R122

80.6R1%0402

80.6R1%0402

TEST29_L and TEST29_H should be routed as

a differential pair with 80 Ohm impedance

TP21TP21

TP27TP27

TP22TP22

TP25TP25

R177

R177

300/4

300/4

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

C150

C150

102P/50V/X7R/4

102P/50V/X7R/4

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

M2 HT I/F CTRL & DEBUG

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

VCC_DDRVCC_DDR

R179

R179

R175

R175

300/4

300/4

4.7K/4

4.7K/4

Q18 N-MMBT3904_NL_SOT23Q18 N-MMBT3904_NL_SOT23

PROCHOT_L 19

R159 44.2KR1%0402R159 44.2KR1%0402

R157 44.2KR1%0402R157 44.2KR1%0402

C241

C241

102P/50V/X7R/4

102P/50V/X7R/4

R171 1K/4 1%R171 1K/4 1%

R120 510RR120 510R

R115 510RR115 510R

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

VID[0..5] 27

VCC_DDR

CPU_THRIP# 14,25

VCCA_1V2

VCC_DDR

Rev

Rev

Rev

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

434

434

434

of

of

of

R176

R176

300/4

300/4

0A

0A

0A

C265

C265

C4.7U10Y0805

C4.7U10Y0805

0.22u_10V_0402

0.22u_10V_0402

CPU1A

CPU1A

HYPERTRANSPORT

HYPERTRANSPORT

680

680

R352

R352

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

C276

C276

C262

C262

0.22u_10V_0402

0.22u_10V_0402

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

231

D12

D12

BAT54S9

BAT54S9

R350 8.87K/4R350 8.87K/4

C540

C540

47p

47p

C273

C273

C180P50N0402

C180P50N0402

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

C274

C274

X_C180P50N0402

X_C180P50N0402

HT_CADIN_H[15..0]9

HT_CADIN_L[15..0]9

HT_CADOUT_H[15..0]9

HT_CADOUT_L[15..0]9

D D

VCCA_1V2

C277

C277

C4.7U10Y0805

C4.7U10Y0805

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

VCCA_1V2

HT_CLKIN_L09

R151 51R1%0402R151 51R1%0402

R153 51R1%0402R153 51R1%0402

HT_CTLIN_H09

HT_CTLIN_L09

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

C C

B B

A A

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

N6

L0_CLKIN_H(1)

P6

L0_CLKIN_L(1)

N3

L0_CLKIN_H(0)

N2

L0_CLKIN_L(0)

V4

L0_CTLIN_H(1)

V5

L0_CTLIN_L(1)

U1

L0_CTLIN_H(0)

V1

L0_CTLIN_L(0)

U6

L0_CADIN_H(15)

V6

L0_CADIN_L(15)

T4

L0_CADIN_H(14)

T5

L0_CADIN_L(14)

R6

L0_CADIN_H(13)

T6

L0_CADIN_L(13)

P4

L0_CADIN_H(12)

P5

L0_CADIN_L(12)

M4

L0_CADIN_H(11)

M5

L0_CADIN_L(11)

L6

L0_CADIN_H(10)

M6

L0_CADIN_L(10)

K4

L0_CADIN_H(9)

K5

L0_CADIN_L(9)

J6

L0_CADIN_H(8)

K6

L0_CADIN_L(8)

U3

L0_CADIN_H(7)

U2

L0_CADIN_L(7)

R1

L0_CADIN_H(6)

T1

L0_CADIN_L(6)

R3

L0_CADIN_H(5)

R2

L0_CADIN_L(5)

N1

L0_CADIN_H(4)

P1

L0_CADIN_L(4)

L1

L0_CADIN_H(3)

M1

L0_CADIN_L(3)

L3

L0_CADIN_H(2)

L2

L0_CADIN_L(2)

J1

L0_CADIN_H(1)

K1

L0_CADIN_L(1)

J3

L0_CADIN_H(0)

J2

L0_CADIN_L(0)

ZIF-SOCKET940

ZIF-SOCKET940

LDT_STOP#

LDT_STOP#10,13

5

5

D D

CPU1B

CPU1B

MEMORY INTERFACE A

MEM_MA0_CLK_H27,8

MEM_MA0_CLK_L27,8

MEM_MA0_CLK_H17,8

MEM_MA0_CLK_L17,8

MEM_MA0_CLK_H07,8

MEM_MA0_CLK_L07,8

MEM_MA0_CS_L17,8

MEM_MA0_CS_L07,8

MEM_MA0_ODT07,8

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

AG21

AG20

AC25

AA24

AC28

AE20

AE19

W27

AD27

AA25

G19

H19

U27

U26

G20

G21

V27

AC27

C C

B B

MEM_MA_CAS_L7,8

MEM_MA_WE_L7,8

MEM_MA_RAS_L7,8

MEM_MA_BANK27,8

MEM_MA_BANK17,8

MEM_MA_BANK07,8

MEM_MA_CKE07,8

MEM_MA_ADD[15..0]7,8

MEM_MA_DQS_H77

MEM_MA_DQS_L77

MEM_MA_DQS_H67

MEM_MA_DQS_L67

MEM_MA_DQS_H57

MEM_MA_DQS_L57

MEM_MA_DQS_H47

MEM_MA_DQS_L47

MEM_MA_DQS_H37

MEM_MA_DQS_L37

MEM_MA_DQS_H27

MEM_MA_DQS_L27

MEM_MA_DQS_H17

MEM_MA_DQS_L17

MEM_MA_DQS_H07

MEM_MA_DQS_L07

MEM_MA_DM[7..0]7

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AB25

AB27

AA26

AA27

M25

M27

AC26

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

N25

Y27

L27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

ZIF-SOCKET940

ZIF-SOCKET940

4

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA[63..0] 7

3

AJ19

AK19

A18

A19

U31

U30

AE30

AC31

AD29

AL19

AL18

C19

D19

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

N31

AA31

AA28

M31

M29

N28

N29

AE31

N30

P29

AA29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AH17

AJ23

AK29

C30

A23

B17

B13

2

MEMORY INTERFACE B

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

ZIF-SOCKET940

ZIF-SOCKET940

CPU1C

CPU1C

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

1

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

M2 DDR MEMORY I/F

M2 DDR MEMORY I/F

M2 DDR MEMORY I/F

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7409

MS-7409

MS-7409

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

534

534

534

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

VCCP

CPU1F

CPU1F

VDD1

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

AA10

VDD4

AA12

VDD5

AA14

VDD6

AA16

VDD7

AA18

VDD8

AB7

VDD9

D D

C C

B B

AB11

AC10

AE10

AB9

AC4

AC5

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

B3

B5

B7

C2

C4

C6

C8

D3

D5

D7

D9

E4

E6

E8

E10

F5

F7

F9

F11

G6

G8

G10

G12

H7

H11

H23

J8

J12

J14

J16

J18

J20

J22

J24

K7

K9

K11

K13

K15

K17

K19

K21

K23

L4

L5

L8

L10

L12

Y17

Y19

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD150

VDD151

ZIF-SOCKET940

ZIF-SOCKET940

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCCP

L14

L16

L18

M2

M3

M7

M9

M11

M13

M15

M17

M19

N8

N10

N12

N14

N16

N18

P7

P9

P11

P13

P15

P17

P19

R4

R5

R8

R10

R12

R14

R16

R18

R20

T2

T3

T7

T9

T11

T13

T15

T17

T19

T21

U8

U10

U12

U14

U16

U18

U20

V9

V11

V13

V15

V17

V19

V21

W4

W5

W8

W10

W12

W14

W16

W18

W20

Y2

Y3

Y7

Y9

Y11

Y13

Y15

Y21

ZIF-SOCKET940

ZIF-SOCKET940

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD37

VDD38

VDD39

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD2

VDD2

CPU1G

CPU1G

4

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCCP

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

W22

L20

L22

N20

N22

P21

P23

R22

T23

U22

V23

Y23

5

6

7

8

1

2

3

VDD3

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

NC1

NC2

NC3

NC4

GND

GND

GND

ZIF-SOCKET940

ZIF-SOCKET940

CPU1H

CPU1H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VCCP

22u_6V_0805

22u_6V_0805

C489

C489

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

3

22u_6V_0805

22u_6V_0805

C510

C510

VCC_DDR

0.22u_10V_0402

0.22u_10V_0402

22u_6V_0805

22u_6V_0805

C467

C467

VTT_DDR

VCCP

C541

C541

22u_6V_0805

22u_6V_0805

VCCA_1V2

0.22u_10V_0402

0.22u_10V_0402

C498

C498

C466

C466

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

22u_6V_0805

22u_6V_0805

C490

C490

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

ZIF-SOCKET940

ZIF-SOCKET940

C539

C539

0.22u_10V_0402

0.22u_10V_0402

22u_6V_0805

22u_6V_0805

C518

C518

CPU1I

CPU1I

VDDIO

VDDIO

22u_6V_0805

22u_6V_0805

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

H6

H5

H2

H1

AK12

VTT5

AJ12

VTT6

AH12

VTT7

AG12

VTT8

AL12

VTT9

K24

VSS1

K26

VSS2

K28

VSS3

K30

VSS4

L7

VSS5

L9

VSS6

L11

VSS7

L13

VSS8

L15

VSS9

L17

VSS10

L19

VSS11

L21

VSS12

L23

VSS13

M8

VSS14

M10

VSS15

M12

VSS16

M14

VSS17

M16

VSS18

M18

VSS19

M20

VSS20

M22

VSS21

N4

VSS22

N5

VSS23

N7

VSS24

N9

VSS25

N11

VSS26

N13

VSS27

N15

VSS28

C531

C531

0.01u_16V_0402

0.01u_16V_0402

22u_6V_0805

22u_6V_0805

C528

C528

2

VLDT_RUN_B

VTT_DDR

C456

C456

180P

180P

C499

C499

C4.7U10Y0805

C4.7U10Y0805

22u_6V_0805

22u_6V_0805

C526

C526

C169

C169

22u_6V_0805

22u_6V_0805

C459

C459

22u_6V_0805

22u_6V_0805

C512

C512

22u_6V_0805

22u_6V_0805

C461

C461

22u_6V_0805

22u_6V_0805

C469

C469

1

22u_6V_0805

22u_6V_0805

C460

C460

22u_6V_0805

22u_6V_0805

C530

C530

180p 0402 X41000p 0402 X40.22u 0402 X4 4.7u 0805 X4

VTT_DDR

0.22u_10V_0402

180p

C161

C168

C168

C280

C280

0.22u

0.22u

0.22u_10V_0402

0.22u_10V_0402

A A

VTT_DDR

C165

C165

0.22u_10V_0402

0.22u_10V_0402

C283

C283

180P

180P

C281

C281

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C282

C282

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

5

C161

C162

C162

102P

102P

C167

C167

102P

102P

C166

C166

C279

C279

102P

102P

C284

C284

102P

102P

180p

180p

180p

180p

C178

C178

C272

C272

C179

C179

180p

180p

C271

C271

180p

180p

CPU Bottom

4

C218

C218

0.22u_10V_0402

0.22u_10V_0402

VCC_DDR

22u_6V_0805

22u_6V_0805

C501

C501

180p

C251

C251

22u_6V_0805

22u_6V_0805

C519

C519

22u_6V_0805

22u_6V_0805

3

C219

C219

180p

180p

0.22u_10V_0402

0.22u_10V_0402

C492

C492

0.22u_10V_0402

C250

C250

C483

C483

VCC_DDRVCC_DDR

C4.7U10Y0805

C4.7U10Y0805

0.01u_16V_0402

0.01u_16V_0402

C529

C529

C538

C538

180P

180P

C249

C249

C248

C248

C4.7U10Y0805

C4.7U10Y0805

C465

C465

180p

180p

C217

C217

C4.7U10Y0805

C4.7U10Y0805

C216

C216

2

C4.7U10Y0805

C4.7U10Y0805

VCC_DDR

C246

C246

0.22u

0.22u

C247

C247

180p

180p

C220

C220

0.22u

0.22u

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

AM2 PWR & GND

AM2 PWR & GND

AM2 PWR & GND

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

C221

C221

180p

180p

MS-7409

MS-7409

MS-7409

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Rev

Rev

Rev

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

634

634

634

of

of

of

0A

0A

0A

5

172

178

184

187

VDD1

VDD2

164

DQS17_H

MEM_MA_DM[7..0]5

D D

MEM_MA_DQS_H75

MEM_MA_DQS_L75

MEM_MA_DQS_H65

MEM_MA_DQS_L65

MEM_MA_DQS_H55

MEM_MA_DQS_L55

MEM_MA_DQS_H45

MEM_MA_DQS_L45

MEM_MA_DQS_H35

MEM_MA_DQS_L35

MEM_MA_DQS_H25

MEM_MA_DQS_L25

MEM_MA_DQS_H15

MEM_MA_DQS_L15

C C

MEM_MA_BANK[2..0]5,8

MEM_MA_ADD[15..0]5,8

B B

MEM_MA_DQS_H05

MEM_MA_DQS_L05

SCL12,14,25

SDA12,14,25

MEM_MA0_CLK_H05,8

MEM_MA0_CLK_L05,8

MEM_MA0_CLK_H15,8

MEM_MA0_CLK_L15,8

MEM_MA0_CLK_H25,8

MEM_MA0_CLK_L25,8

MEM_MA_CKE05,8

MEM_MA_RAS_L5,8

MEM_MA_CAS_L5,8

MEM_MA0_CS_L05,8

MEM_MA0_CS_L15,8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA_CKE0

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

SCL

SDA

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD3

4

69

170

175

181

189

197

64

VDD4

VDD5

VDD6

VDD753VDD859VDD9

191

VDD1067VDD11

VDDQ1

VDDQ2

VDDQ3

VDDQ4

194

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

72

VCC3VCC_DDR

78

VDDQ1075VDDQ11

ERR_OUT_L

238

VDDSPD

DIMM1DIMM1

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

WE_L

VREF

TEST

ODT0

ODT1

PAR_IN

NC1

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

MEM_MA_DATA8

12

MEM_MA_DATA7

129

MEM_MA_DATA6

128

MEM_MA_DATA5

123

MEM_MA_DATA4

122

MEM_MA_DATA3

10

MEM_MA_DATA2

9

MEM_MA_DATA1

4

MEM_MA_DATA0

3

MEM_MA_WE_L

73

VDDR_VREF

1

102

MEM_MA0_ODT0

195

77

55

68

19

3

MEM_MA_DATA[63..0] 5

MEM_MA_WE_L 5,8

X_0.1u/25V/4

X_0.1u/25V/4

MEM_MA0_ODT0 5,8

C642

C642

VDDR_VREF

2

MEM_VREF_SUS

VCC_DDR

R118

R118

1K_0402 1%

1K_0402 1%

C175

R119

R119

1K_0402 1%

1K_0402 1%

C175

0.1u_10V_0402

0.1u_10V_0402

LAYOUT: PLACE CLOSE TO DIMMs

VDDR_VREF

C176

C176

1n_50v_0402

1n_50v_0402

C174

C174

1n_50v_0402

1n_50v_0402

1

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7409

MS-7409

MS-7409

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

734

734

734

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

D D

MEM_MA_ADD[15..0]5,7

C C

MEM_MA_BANK[2..0]5,7

B B

MEM_MA_ADD[15..0]

MEM_MA_BANK[2..0]

MEM_MA_CAS_L5,7

MEM_MA_WE_L5,7

MEM_MA_RAS_L5,7

MEM_MA0_CS_L05,7

MEM_MA0_CS_L15,7

MEM_MA0_ODT05,7

MEM_MA_CKE05,7

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

MEM_MA0_ODT0

MEM_MA_CKE0

4

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

MEM_MA_CKE0

MEM_MA_BANK2

MEM_MA_ADD6

MEM_MA_ADD4

MEM_MA_ADD1

MEM_MA_ADD3

MEM_MA_WE_L

MEM_MA0_CS_L0

MEM_MA_CAS_L

MEM_MA0_ODT0

MEM_MA0_CS_L1

MEM_MA_ADD13

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD12

MEM_MA_ADD9

MEM_MA_ADD11

MEM_MA_ADD7

MEM_MA_ADD8

MEM_MA_ADD5

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

8P4R-47_RN0402

MEM_MA_ADD2

MEM_MA_ADD0

MEM_MA_ADD10

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_RAS_L

VCC_DDR

3

VTT_DDR

C533 0.1u_10V_0402C533 0.1u_10V_0402

RN21

RN21

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN26

RN26

RN31

RN31

RN34

RN34

RN22

RN22

RN25

RN25

RN29

RN29

RN33

RN33

C554 0.1u_10V_0402C554 0.1u_10V_0402

C487 0.1u_10V_0402C487 0.1u_10V_0402

C477 0.1u_10V_0402C477 0.1u_10V_0402

C520 0.1u_10V_0402C520 0.1u_10V_0402

C463 0.1u_10V_0402C463 0.1u_10V_0402

C542 0.1u_10V_0402C542 0.1u_10V_0402

C478 0.1u_10V_0402C478 0.1u_10V_0402

C500 0.1u_10V_0402C500 0.1u_10V_0402

C471 0.1u_10V_0402C471 0.1u_10V_0402

C511 0.1u_10V_0402C511 0.1u_10V_0402

C550 0.1u_10V_0402C550 0.1u_10V_0402

C513 0.1u_10V_0402C513 0.1u_10V_0402

C548 0.1u_10V_0402C548 0.1u_10V_0402

C494 0.1u_10V_0402C494 0.1u_10V_0402

C553 0.1u_10V_0402C553 0.1u_10V_0402

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

2

MEM_MA0_CLK_H25,7

MEM_MA0_CLK_L25,7

MEM_MA0_CLK_H15,7

MEM_MA0_CLK_L15,7

MEM_MA0_CLK_H05,7

MEM_MA0_CLK_L05,7

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

1

C269

C269

C1.5P/4

C1.5P/4

C183

C183

C1.5P/4

C1.5P/4

C184

C184

C1.5P/4

C1.5P/4

EMI

C270 C1U16YC270 C1U16Y

C287 C1U16YC287 C1U16Y

C380 C1U16YC380 C1U16Y

C398 C1U16YC398 C1U16Y

C399 C1U16YC399 C1U16Y

A A

5

4

C402 C1U16YC402 C1U16Y

C403 C1U16YC403 C1U16Y

C410 C1U16YC410 C1U16Y

3

VCC_DDR

C504 0.1u_10V_0402C504 0.1u_10V_0402

C505 0.1u_10V_0402C505 0.1u_10V_0402

C524 0.1u_10V_0402C524 0.1u_10V_0402

C525 0.1u_10V_0402C525 0.1u_10V_0402

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Document Number

Document Number

Document Number

2

DDR2 Terminatior

DDR2 Terminatior

DDR2 Terminatior

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Sheet

Sheet

Sheet

834

834

834

1

Title

Micro Star Restricted Secret

Title

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

HT_CADIN_H[15..0]4

HT_CADIN_L[15..0]4

HT_CADOUT_H[15..0]4

HT_CADOUT_L[15..0]4

HT_CADOUT_H15

HT_CADOUT_L15

D D

C C

VDDHT_PKG

B B

A A

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

HT_CLKOUT_H14

HT_CLKOUT_L14

HT_CLKOUT_H04

HT_CLKOUT_L04

HT_CTLOUT_H04

HT_CTLOUT_L04

R92 49.9/4R92 49.9/4

R98 49.9/4R98 49.9/4

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

R19

R18

R21

R22

U22

U21

U18

U19

W19

W20

AC21

AB22

AB20

AA20

AA19

Y19

T24

R25

U25

U24

V23

U23

V24

V25

AA25

AA24

AB23

AA23

AB24

AB25

AC24

AC25

W21

W22

Y24

W25

P24

P25

HT_RXCALN

A24

HT_RXCALP

C24

U11A

U11A

HT_RXCAD15P

HT_RXCAD15N

HT_RXCAD14P

HT_RXCAD14N

HT_RXCAD13P

HT_RXCAD13N

HT_RXCAD12P

HT_RXCAD12N

HT_RXCAD11P

HT_RXCAD11N

HT_RXCAD10P

HT_RXCAD10N

HT_RXCAD9P

HT_RXCAD9N

HT_RXCAD8P

HT_RXCAD8N

HT_RXCAD7P

HT_RXCAD7N

HT_RXCAD6P

HT_RXCAD6N

HT_RXCAD5P

HT_RXCAD5N

HT_RXCAD4P

HT_RXCAD4N

HT_RXCAD3P

HT_RXCAD3N

HT_RXCAD2P

HT_RXCAD2N

HT_RXCAD1P

HT_RXCAD1N

HT_RXCAD0P

HT_RXCAD0N

HT_RXCLK1P

HT_RXCLK1N

HT_RXCLK0P

HT_RXCLK0N

HT_RXCTLP

HT_RXCTLN

HT_RXCALP

HT_RXCALN

RS690

RS690

PART 1 OF 5

PART 1 OF 5

HYPER TRANSPORT I/F

HYPER TRANSPORT I/F

4

HT_TXCAD15P

HT_TXCAD15N

HT_TXCAD14P

HT_TXCAD14N

HT_TXCAD13P

HT_TXCAD13N

HT_TXCAD12P

HT_TXCAD12N

HT_TXCAD11P

HT_TXCAD11N

HT_TXCAD10P

HT_TXCAD10N

HT_TXCAD9P

HT_TXCAD9N

HT_TXCAD8P

HT_TXCAD8N

HT_TXCAD7P

HT_TXCAD7N

HT_TXCAD6P

HT_TXCAD6N

HT_TXCAD5P

HT_TXCAD5N

HT_TXCAD4P

HT_TXCAD4N

HT_TXCAD3P

HT_TXCAD3N

HT_TXCAD2P

HT_TXCAD2N

HT_TXCAD1P

HT_TXCAD1N

HT_TXCAD0P

HT_TXCAD0N

HT_TXCLK1P

HT_TXCLK1N

HT_TXCLK0P

HT_TXCLK0N

HT_TXCTLP

HT_TXCTLN

HT_TXCALP

HT_TXCALN

3

HT_TXCALP

HT_TXCALN

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

R100 100/4/1R100 100/4/1

mini pcie

lan

HT_CLKIN_H1 4

HT_CLKIN_L1 4

HT_CLKIN_H0 4

HT_CLKIN_L0 4

HT_CTLIN_H0 4

HT_CTLIN_L0 4

A_RX2P13

A_RX2N13

A_RX3P13

A_RX3N13

GPP_RX2P17

GPP_RX2N17

GPP_RX0P18

GPP_RX0N18

A_RX0P13

A_RX0N13

A_RX1P13

A_RX1N13

A_RX2P

A_RX2N

A_RX3P

A_RX3N

GPP_RX2P

GPP_RX2N

GPP_RX0N

R209 X_1.47KR1%0402R209 X_1.47KR1%0402

R194 X_8.25K/6/1R194 X_8.25K/6/1

*

AA11

AB11

AA12

AB12

AA14

AB14

AB7

AB6

W11

W12

AA7

AB9

AA9

W14

W15

G5

G4

M8

M7

M4

M5

R4

R5

R7

R8

U4

U5

W4

W5

W9

U11B

U11B

GFX_RX0P

GFX_RX0N

J8

GFX_RX1P

J7

GFX_RX1N

J4

GFX_RX2P

J5

GFX_RX2N

L8

GFX_RX3P

L7

GFX_RX3N

L4

GFX_RX4P

L5

GFX_RX4N

GFX_RX5P

GFX_RX5N

GFX_RX6P

GFX_RX6N

P8

GFX_RX7P

P7

GFX_RX7N

P4

GFX_RX8P

P5

GFX_RX8N

GFX_RX9P

GFX_RX9N

GFX_RX10P

GFX_RX10N

GFX_RX11P

GFX_RX11N

GFX_RX12P

GFX_RX12N

Y4

GFX_RX13P

Y5

GFX_RX13N

V9

GFX_RX14P

GFX_RX14N

GFX_RX15P

GFX_RX15N

GPP_RX0P

GPP_RX0N

GPP_RX1P

GPP_RX1N

Y7

GPP_RX2P

GPP_RX2N

GPP_RX3P

GPP_RX3N

SB_RX0P

SB_RX0N

SB_RX1P

SB_RX1N

PCEH_ISET

PCEH_TXISET

RS690

RS690

PART 2 OF 5

PART 2 OF 5

PCIE GFX I/F

PCIE GFX I/F

PCIE I/F GPP

PCIE I/F GPP

PCIE I/F SB

PCIE I/F SB

P21

P22

P18

P19

M22

M21

M18

M19

L18

L19

G22

G21

J20

J21

F21

F22

N24

N25

L25

M24

K25

K24

J23

K23

G25

H24

F25

F24

E23

F23

E24

E25

L21

L22

J24

J25

N23

P23

C25

D24

GFX_TX0P

GFX_TX0N

GFX_TX1P

GFX_TX1N

GFX_TX2P

GFX_TX2N

GFX_TX3P

GFX_TX3N

GFX_TX4P

GFX_TX4N

GFX_TX5P

GFX_TX5N

GFX_TX6P

GFX_TX6N

GFX_TX7P

GFX_TX7N

GFX_TX8P

GFX_TX8N

GFX_TX9P

GFX_TX9N

GFX_TX10P

GFX_TX10N

GFX_TX11P

GFX_TX11N

GFX_TX12P

GFX_TX12N

GFX_TX13P

GFX_TX13N

GFX_TX14P

GFX_TX14N

GFX_TX15P

GFX_TX15N

GPP_TX0P

GPP_TX0N

GPP_TX1P

GPP_TX1N

GPP_TX2P

GPP_TX2N

GPP_TX3P

GPP_TX3N

SB_TX0P

SB_TX0N

SB_TX1P

SB_TX1N

PCEH_PCAL

PCEH_NCAL

2

J1

H2

K2

K1

K3

L3

L1

L2

N2

N1

P2

P1

P3

R3

R1

R2

T2

U1

V2

V1

V3

W3

W1

W2

Y2

AA1

AA2

AB2

AB1

AC1

AE3

AE4

AD8

AE8

AD7

AE7

AD4

AE5

AD5

AD6

AE9

AD10

AC8

AD9

AD11

AE11

A_TX2P_C

A_TX2N_C

A_TX3P_C

A_TX3N_C

GPP_TX2P_C

GPP_TX2N_C

GPP_TX0P_CGPP_RX0P

GPP_TX0N_C

A_TX0P_C

A_TX0N_C

A_TX1P_C

A_TX1N_C

R124 562R1%0402R124 562R1%0402

R125 2KR1%0402R125 2KR1%0402

*

*

C182 0.1u/16V/4C182 0.1u/16V/4

C186 0.1u/16V/4C186 0.1u/16V/4

C177 0.1u/16V/4C177 0.1u/16V/4

C181 0.1u/16V/4C181 0.1u/16V/4

C152 0.1u/16V/4C152 0.1u/16V/4

C156 0.1u/16V/4C156 0.1u/16V/4

C157 0.1u/16V/4C157 0.1u/16V/4

C159 0.1u/16V/4C159 0.1u/16V/4

C189 0.1u/16V/4C189 0.1u/16V/4

C191 0.1u/16V/4C191 0.1u/16V/4

C187 0.1u/16V/4C187 0.1u/16V/4

C188 0.1u/16V/4C188 0.1u/16V/4

VDDA12_PKG2

1

A_TX2P 13

A_TX2N 13

A_TX3P 13

A_TX3N 13

GPP_TX2P 17

GPP_TX2N 17

GPP_TX0P 18

GPP_TX0N 18

A_TX0P 13

A_TX0N 13

A_TX1P 13

A_TX1N 13

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

RS690-HT LINK/PCIE/HDMI

RS690-HT LINK/PCIE/HDMI

RS690-HT LINK/PCIE/HDMI

MS-7409

MS-7409

MS-7409

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Tuesday, September 04, 2007

Sheet

Sheet

Sheet

934

934

1

934

Rev

Rev

Rev

0A

0A

0A

of

of

of

Loading...

Loading...