MSI MS-7407 7407 0A 0531

5

4

3

2

1

Page Title

MS-7407 Ver : 0A

01

02

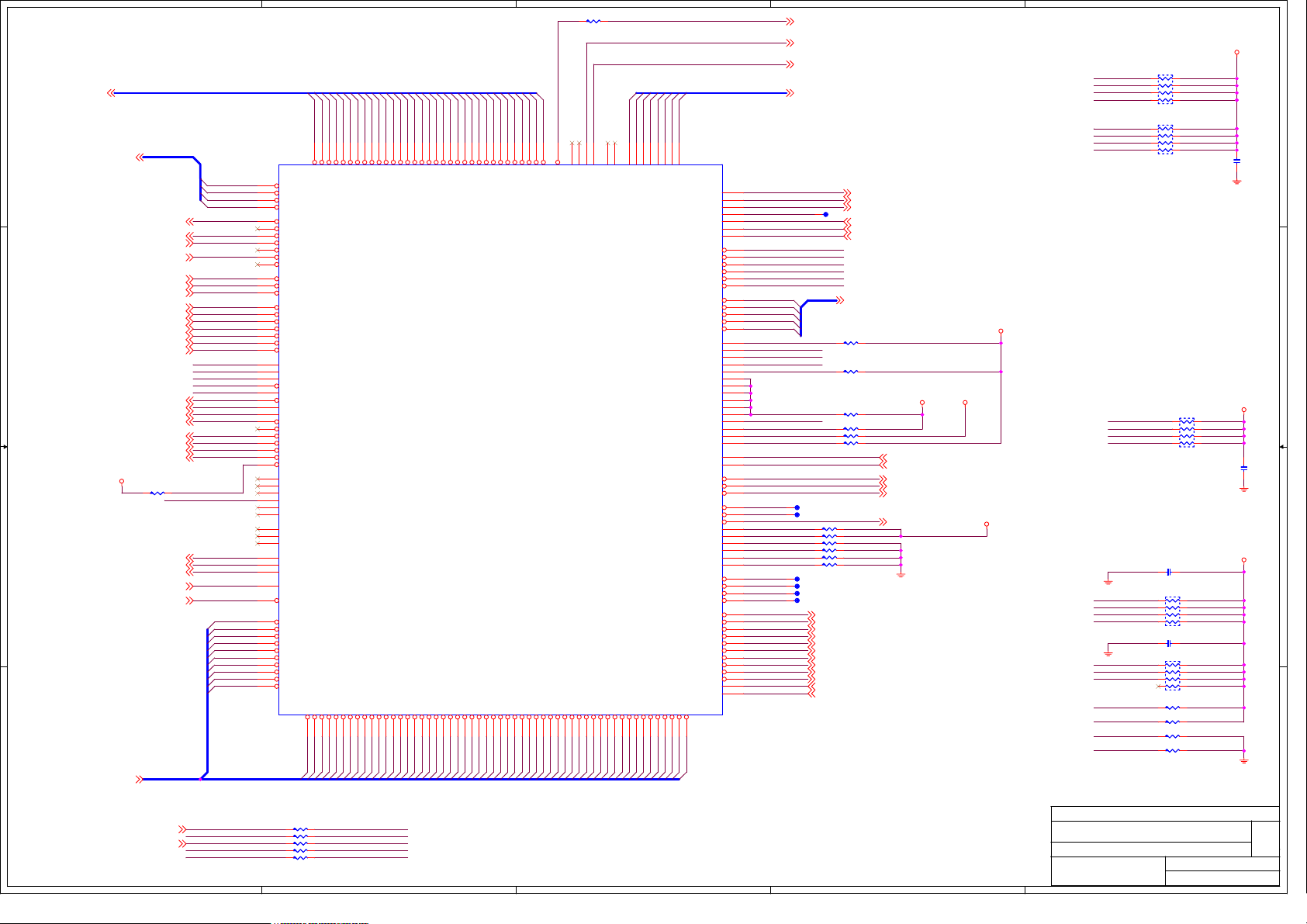

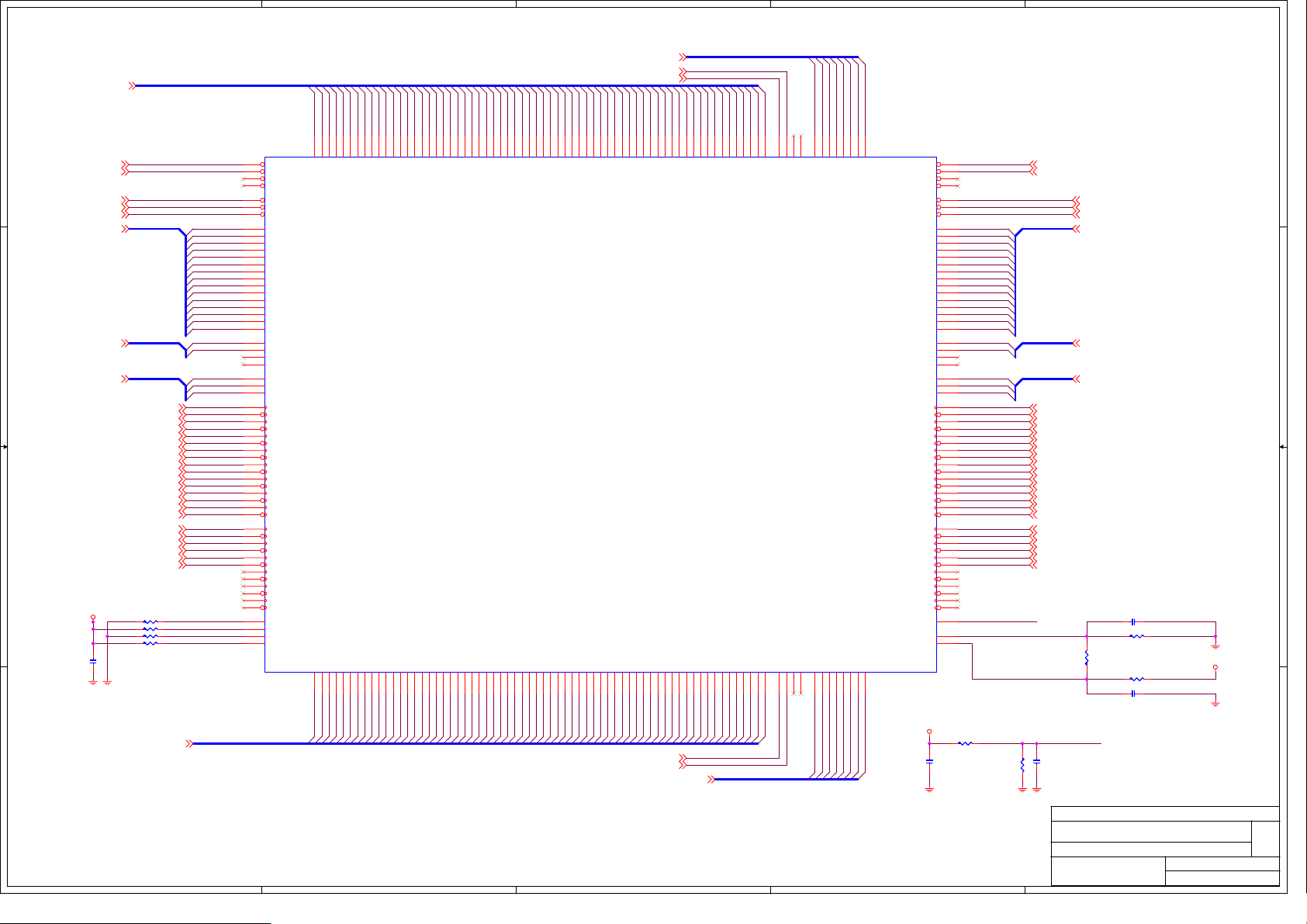

Intel (R) LGA775 Processor (130W)

Intel (R) ( GMCH G31) + ICH7 Chipset

D D

03

04

05

CPU:

Intel Core 2 Duo/Extreme/Quad & Pentium D Processor

06

07

08

09

010

011

System Chipset:

Intel G31 (North Bridge) Rev :

Intel ICH7 (South Bridge) Rev :

C C

On Board Chipset:

CLOCK : ICS9LP505

PLC LAN ET82566DC

LPC Super I/O : W83627DHG Ver :

Audio Codec : ALC888 7.1 Channel Ver : A1

BIOS : SPI- 16M

012

013

014

015

016

017

018

019

020

021

022

023

024

025

026

B B

Main Memory:

DDR II * 2 (Max 4GB)

027

028

029

030

Expansion Slots:

PCI X SLOT *1 (FOR PCIE & PCI Riser)

031

032

033

034

035

COVER

BLOCK DIAGRAM

GPIO & Jumper Setting

Clock Generator - ICS9LP505

Intel LGA775 - Signal

Intel LGA775 - Power

Intel LGA775 - Gnd

Broadwater G31 - CPU

Broadwater G31 - Memory

Broadwater G31 - PCI Express

Broadwater G31 - Power / GND

VGA Connector

DDR II DIMM 1 / Termination

DDR II DIMM 2 / Termination

ICH7 - PCI / DMI / CPU / LAN

ICH7 - LPC / ATA / USB

ICH7 - Power

PCI Slot

PLC LAN1 - 82566DC

1394 VT6308

Azalia CODEC ALC888

LPC I/O W83627DHG

IDE / FDD / SATA Connector

USB Connector

KB/MS & FAN

VRD11 - IISL6312 3Phase

MS7 ACPI Controller

DDRII Power

ATX & Front Panel & LED

Manual Parts

Revision History

Power Delivery

CLOCK MAP

PWOK MAP

Reset MAP

036

037

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

COVER

COVER

COVER

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

Rev

Rev

Rev

0A

0A

0A

of

135

of

135

of

135

5

4

3

2

1

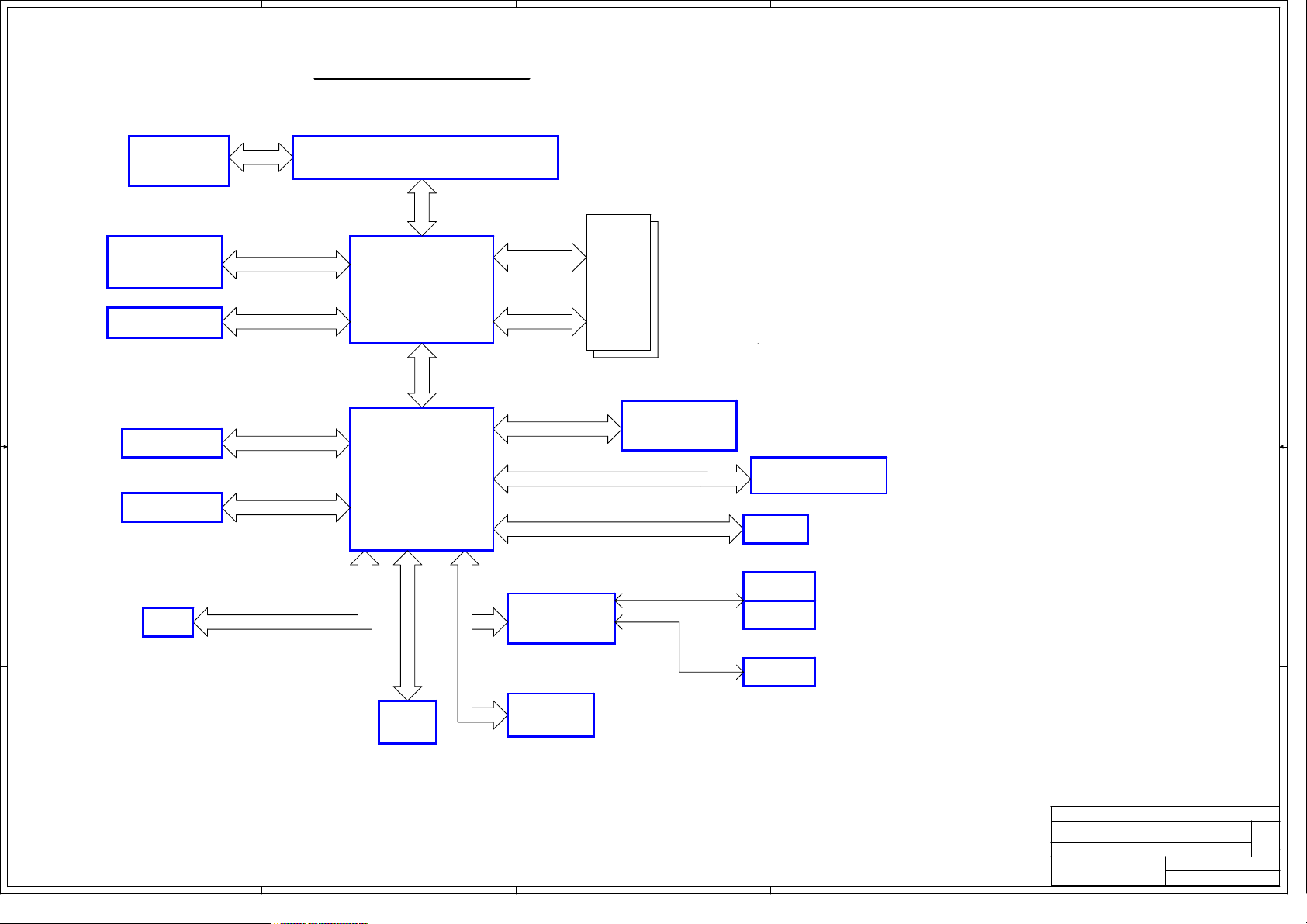

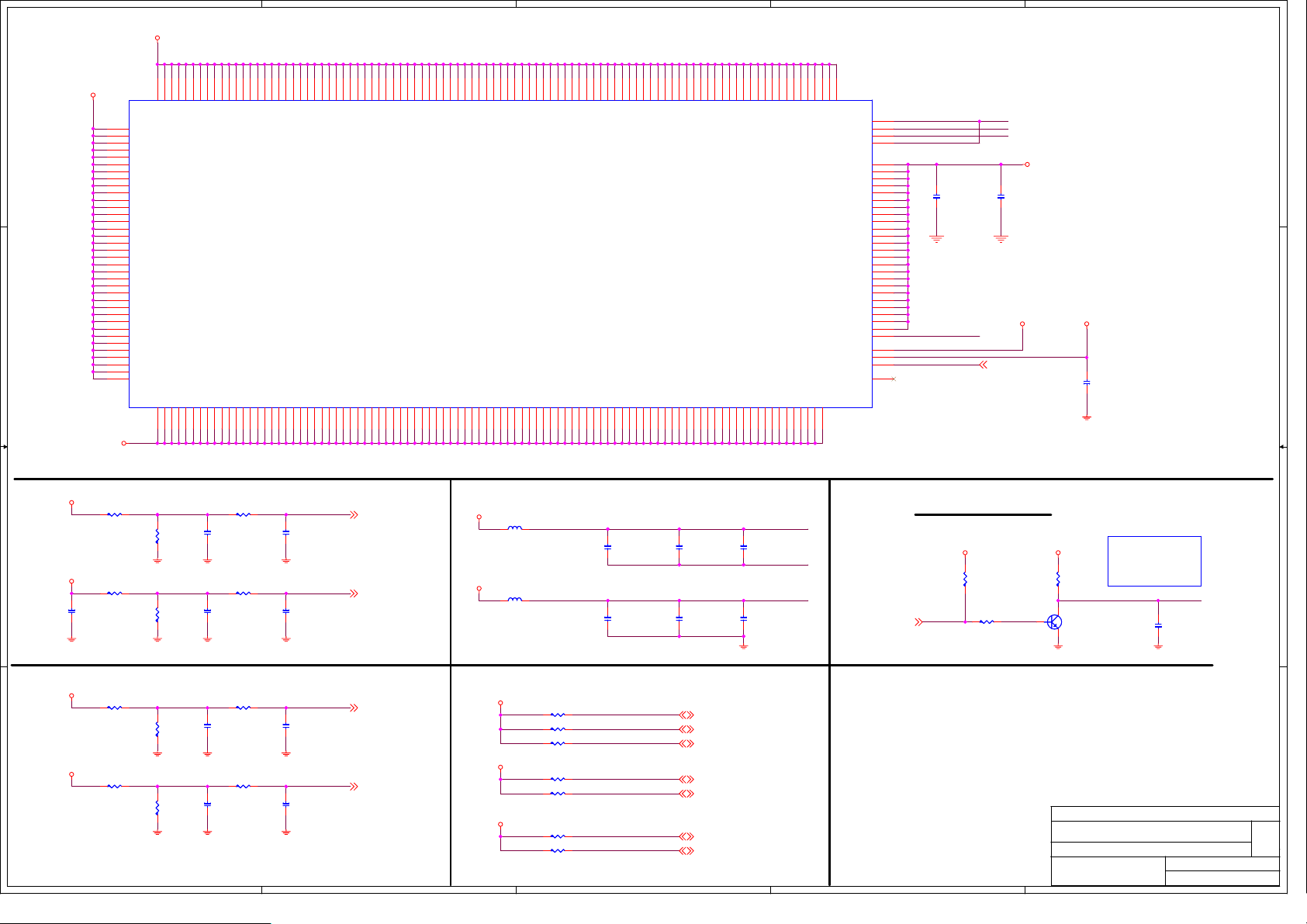

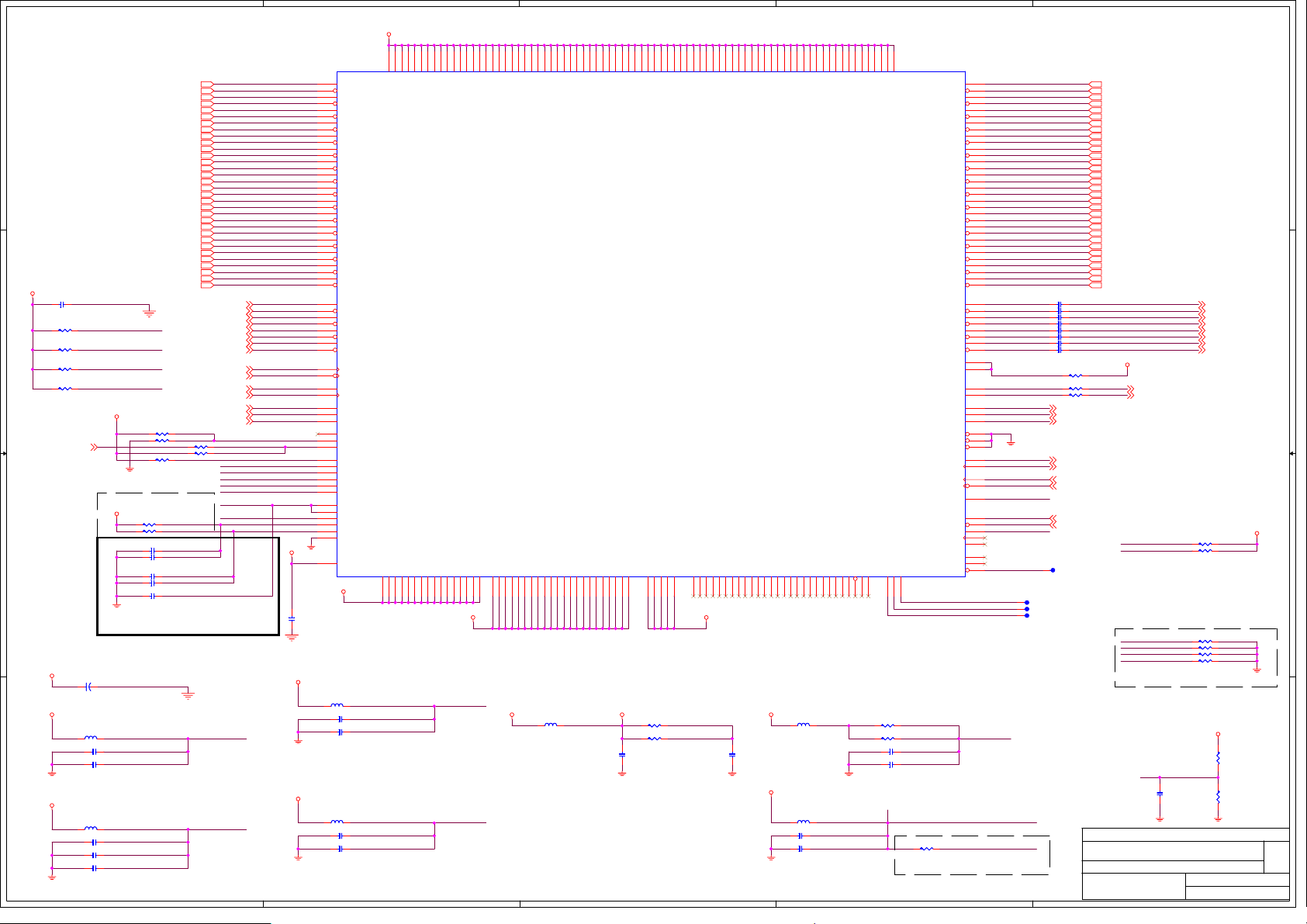

Block Diagram

D D

VRD 11

3-Phase PWM

Intel LGA775 Processor(130W)

FSB 800/1066

FSB

DDR2 667/800

Channel1

VGA

Intel GMA 3000

RGB

Bearlake

G31

PCIE X 16

C C

SATA-II X 2

PCIE X 16

DMI

SATA2

ICH7

USB Port 0~6

B B

USB 2.0

DDRII

Channel2

DDRII

HD Audio Link

PLC LAN

2 DDR II

SODIMM

Modules

HD Audio Codec

PCI

ALC888

Gb

LAN

PCI Slot

82566DC

Keyboard

IDE

SPI

PATA

LPC Bus

SIO

W83627DHG

Mouse

Serial Port

SPI

TPM

ROM

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

235

235

235

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

4

3

2

1

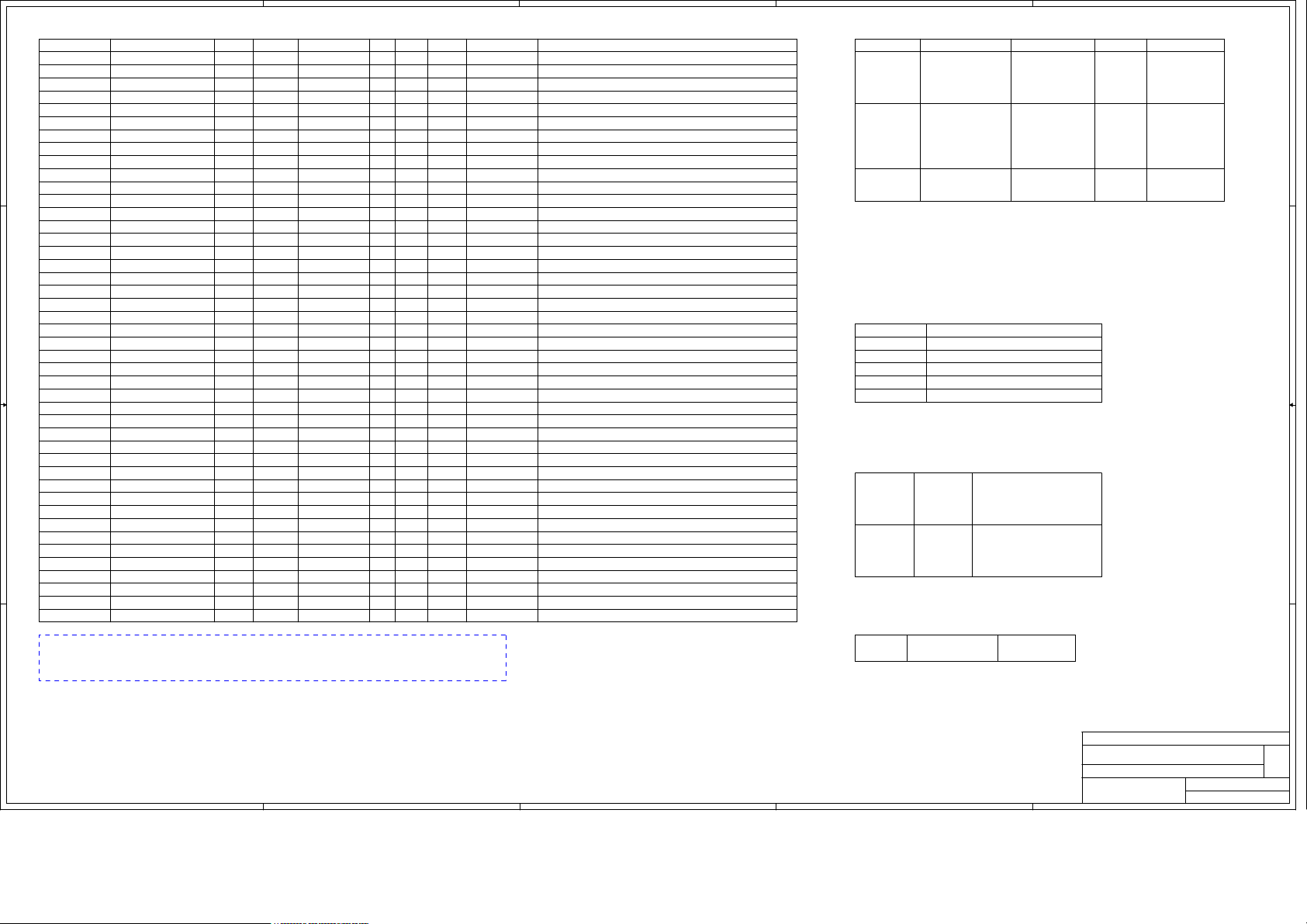

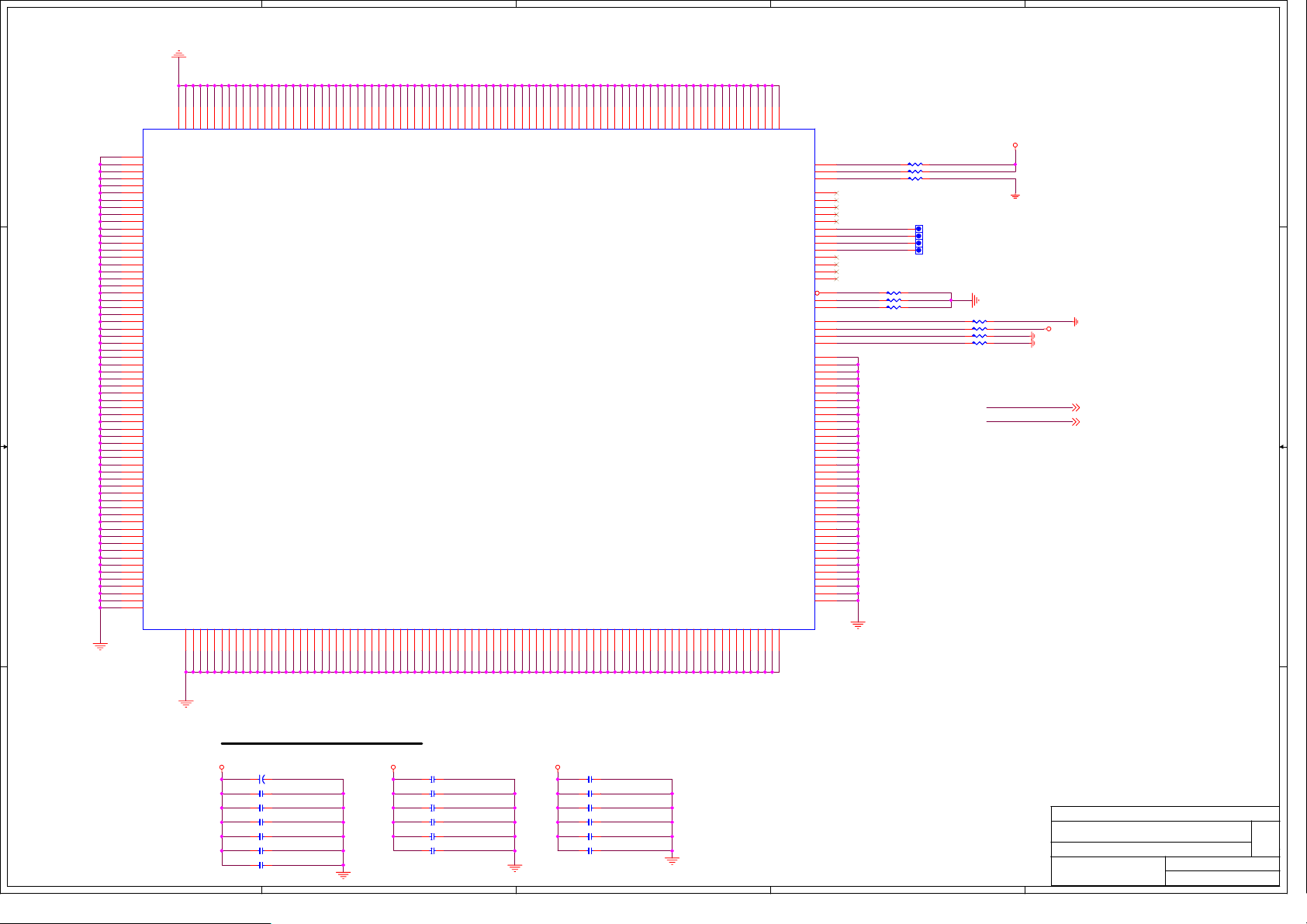

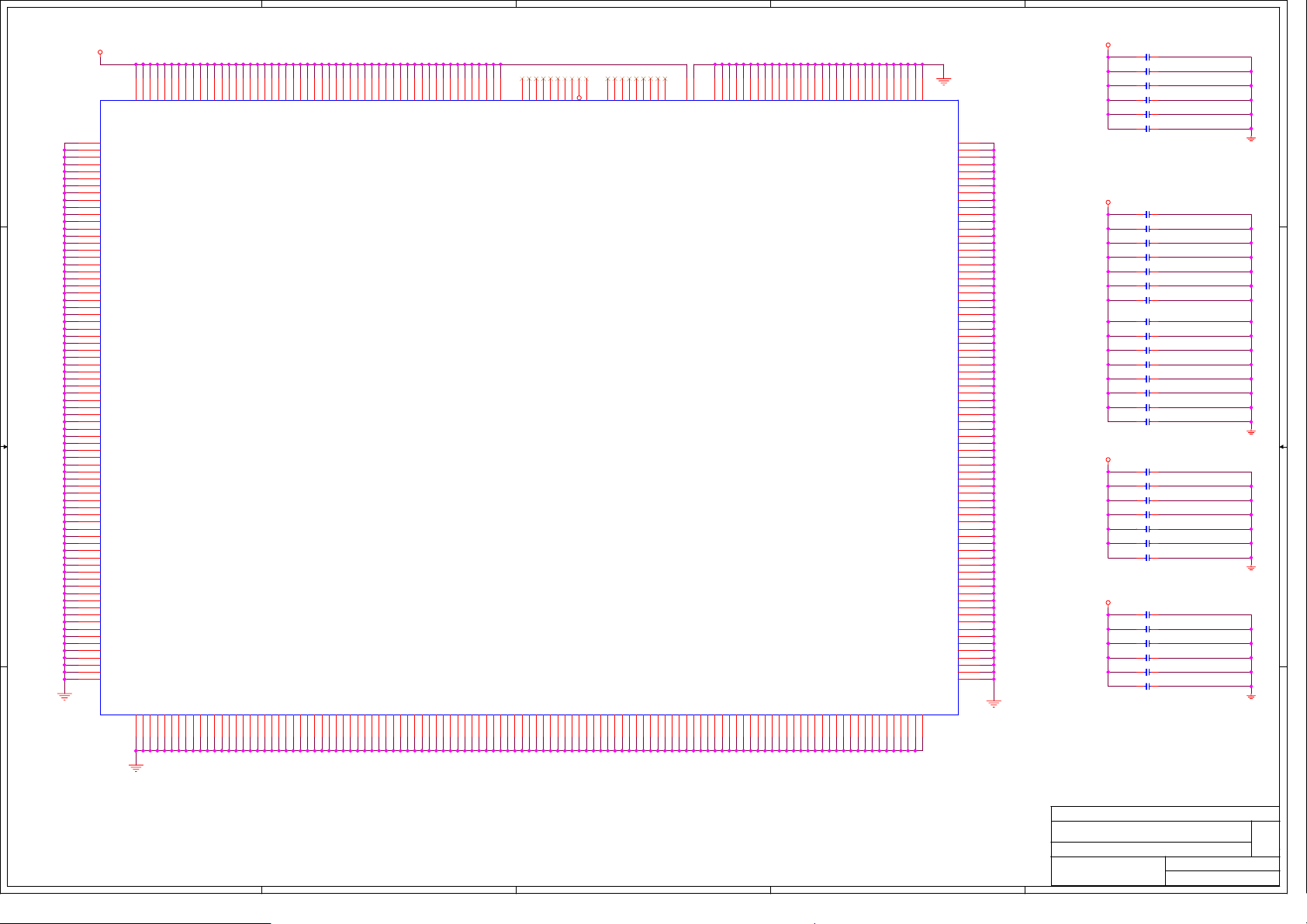

ICH7

GPIO Alt Func Pin I/O/NC Power PU SMI Tol Default Signal Name

GPIO[0] BM_BUSY# AB18 I/O Vcc3p3 N Y 3.3 Input strapped high

GPIO[1] PCIREQ[5]# C8 I/O V5REF N Y 5 Input PREQ#5

GPIO[2] PIRQE# G8 I/OD V5REF N Y 5 Input PIRQ#E

GPIO[3] PIRQF# F7 I/OD V5REF N Y 5 Input PIRQ#F

D D

GPIO[4] PIRQG# F8 I/OD V5REF N Y 5 Input PIRQ#G

GPIO[5] PIRQH# G7 I/OD V5REF N Y 5 Input PIRQ#H

GPIO[6] unmuxed AC21 I/O Vcc3p3 N Y 3.3 Input ATADET0

GPIO[7] unmuxed AC18 I/O Vcc3p3 N Y 3.3 Input strapped high

GPIO[8] unmuxed E21 I/O VccSus3p3 N Y 3.3 Input SIO_PME#

GPIO[9] unmuxed E20 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[10] unmuxed A20 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[11] SMBALERT# B23 I/O VccSus3p3 N Y 3.3 Input strapped high

PCI Config.

DEVICE

PCI Slot 1

PCI Slot 2

1394 PIRQ#B

MCP1 INT Pin

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#C

PIRQ#D

PIRQ#A PGNT#2

PIRQ#B

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#2

PREQ#1

PGNT#1

CLOCKIDSEL

AD20

PCI_CLK1

AD21 PCI_CLK2

AD19 1394_PCLK

GPIO[12] unmuxed F19 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[13] unmuxed E19 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[14] unmuxed R4 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[15] unmuxed E22 I/O VccSus3p3 N Y 3.3 Input strapped high

GPIO[16] unmuxed AC22 I/O Vcc3p3 N N 3.3 0 NC

GPIO[17] PCIGNT[5]# D8 I/O Vcc3p3 N N 3.3 N/A PGNT#5

GPIO[18] unmuxed AC20 I/O Vcc3p3 N N 3.3 1 SIO_HOLD#

GPIO[19] SATA1GP AH18 I/O Vcc3p3 N N 3.3 Input strapped high

C C

GPIO[20] unmuxed AF21 I/O Vcc3p3 N N 3.3 1 NC

GPIO[21] SATA0GP AF19 I/O Vcc3p3 N N 3.3 Input strapped high

GPIO[22] PCIREQ[4]# A13 I/O Vcc3p3 N N 3.3 Input PREQ#4

GPIO[23] LDRQ1# AA5 I/O Vcc3p3 N N 3.3 Input NC

GPIO[24] unmuxed R3 I/O VccSus3p3 N N 3.3 No Change LANPHY_DIS#

GPIO[25] unmuxed D20 I/O VccSus3p3 Y N 3.3 1 DMI_MODE

GPIO[26] unmuxed A21 I/O VccSus3p3 N N 3.3 0 NC

PCI RESET DEVICE

Signals

PCIRST#1

PCIRST#2

PCIRST#3

PLTRST#

HD_RST#

Target

SIO,TPM

1394,PCIE X16 SLOT

PCI SLOT 1,2

MS7

Primary IDE

GPIO[27] unmuxed B21 I/O VccSus3p3 N N 3.3 0 LAN2_EN

GPIO[28] unmuxed E23 I/O VccSus3p3 N N 3.3 0 NC

GPIO[29] OC5# C3 I/O VccSus3p3 N N 3.3 Input USB_OCP#4

GPIO[30] OC6# A2 I/O VccSus3p3 N N 3.3 Input USB_OCP#4

GPIO[31] OC7# B3 I/O VccSus3p3 N N 3.3 Input USB_OCP#4

GPIO[32] unmuxed AG18 I/O Vcc3p3 N N 3.3 1 SPI_WP#

GPIO[33] unmuxed AC19 I/O Vcc3p3 N N 3.3 1 NC

GPIO[34] unmuxed U2 I/O Vcc3p3 N N 3.3 0 NC

B B

GPIO[35] unmuxed AD21 I/O Vcc3p3 N N 3.3 1 NC

DDRII DIMM Config.

CLOCK

SCLK_A0/SCLK_A#0

SCLK_A2/SCLK_A#2

DIMM 1

ADDRESSDEVICE

A0H SCLK_A1/SCLK_A#1

GPIO[36] SATA2GP AH19 I/O Vcc3p3 N N 3.3 Input strapped high

GPIO[37] SATA3GP AE19 I/O Vcc3p3 N N 3.3 Input strapped high

GPIO[38] unmuxed AD20 I/O Vcc3p3 N N 3.3 Input strapped high

GPIO[39] unmuxed AE20 I/O Vcc3p3 N N 3.3 Input strapped high

DIMM 2

A2H

SCLK_B0/SCLK_B#0

SCLK_B1/SCLK_B#1

SCLK_B2/SCLK_B#2

GPIO[48] GNT4# A14 I/O Vcc3p3 N N 3.3 N/A PGNT#4

GPIO[49] CPUPWRGD AG24 I/O V_CPU_IO N N CPU N/A H_PWRGD

JUMPER SETTING

Following are the GPIOs that need to be terminated properly if not used:

GPIO[39:36,23:21,19,7:0]: default as inputs and should be pulled up to Vcc3_3 if unused.

GPIO[31:29,15:8]: default as inputs and should be pulled up to VccSus3_3 if unused.

A A

5

4

3

JBAT1

(1-2)NORMAL

2

(2-3)CLEAR

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

GPIO & Jumper Setting

GPIO & Jumper Setting

GPIO & Jumper Setting

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

335

335

335

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

4

3

2

1

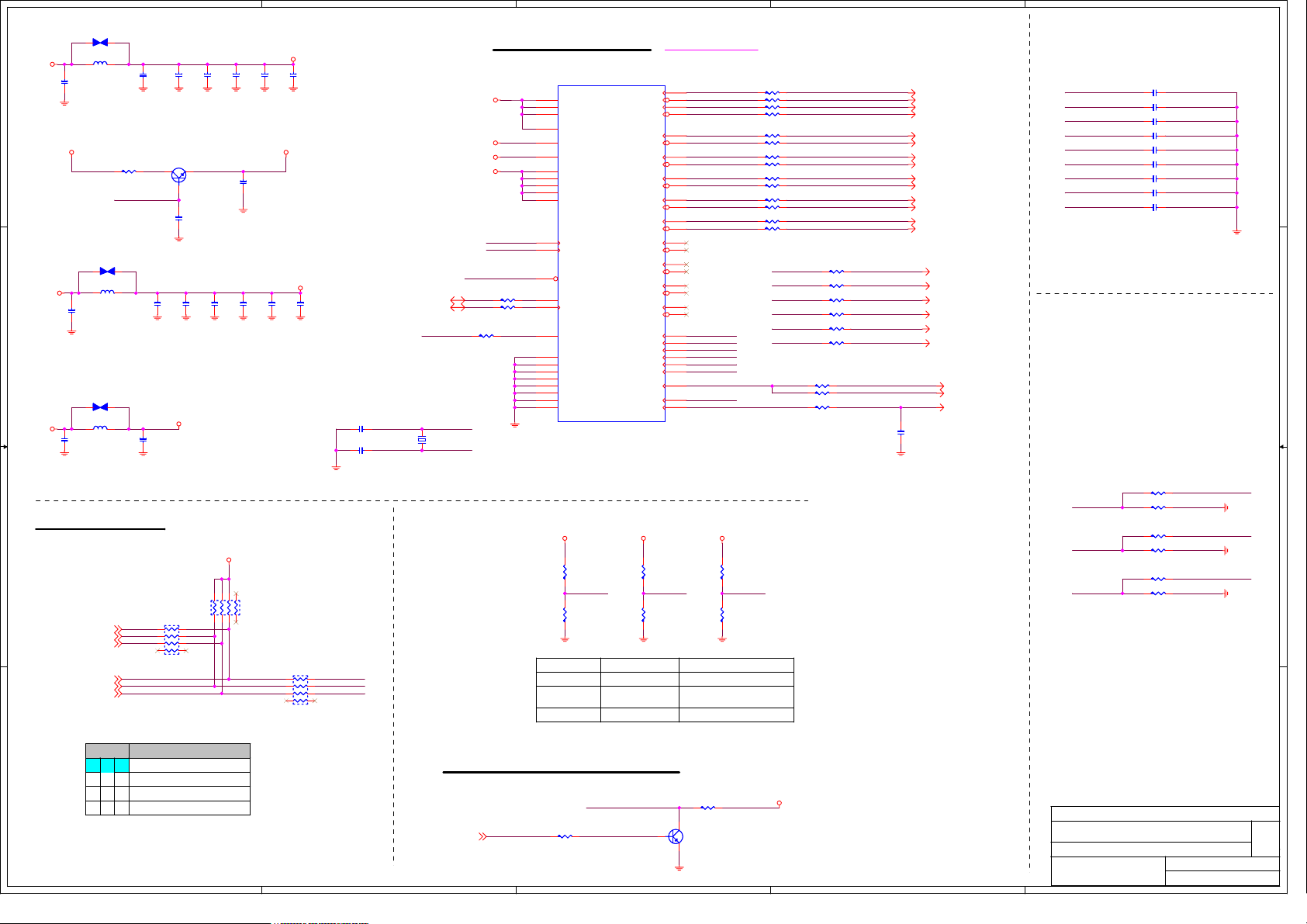

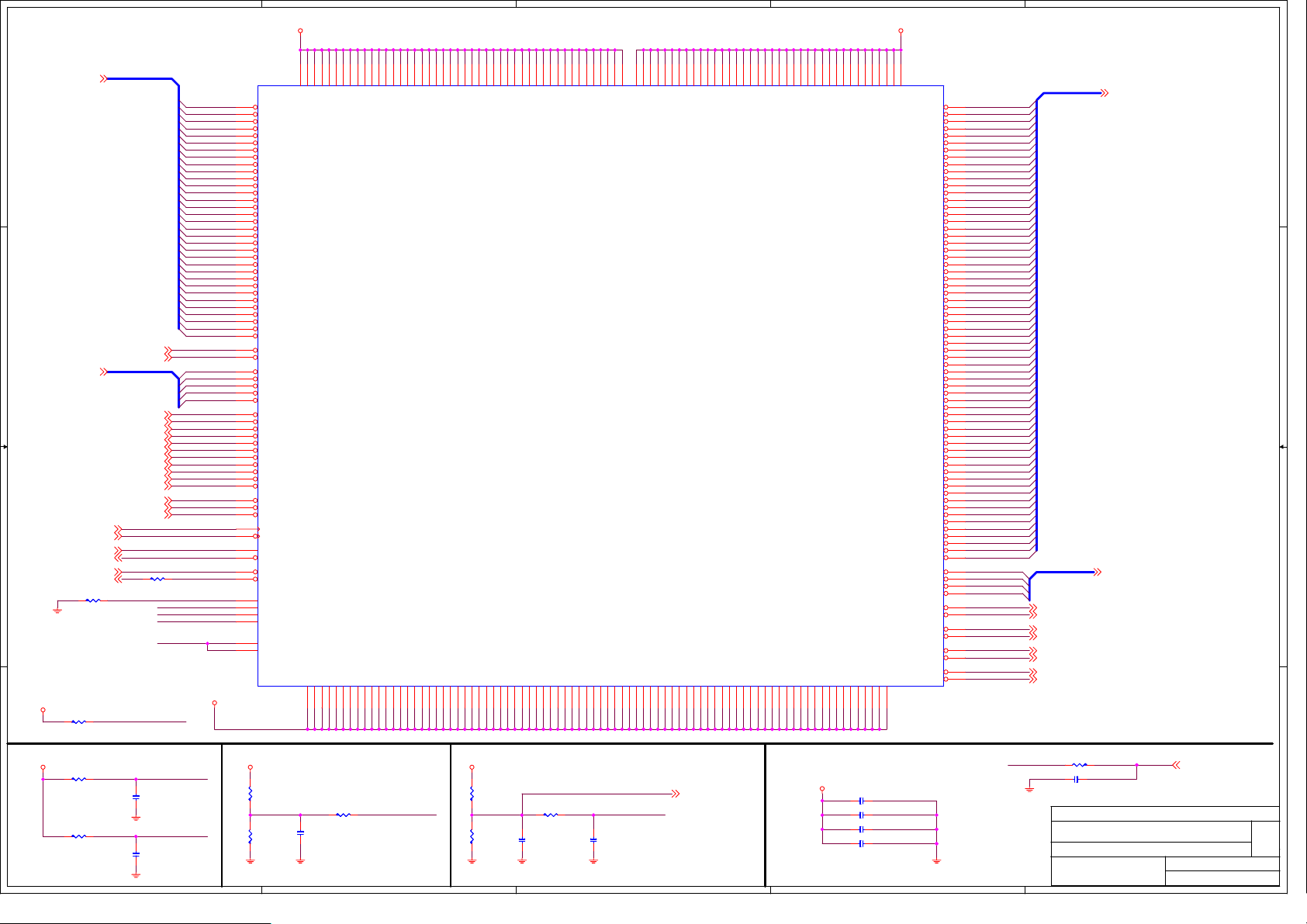

CP1 X_COPPERCP1 X_COPPER

L1

L1

VCC3

C38

C38

C0.1u25Y

C0.1u25Y

D D

VDD_CK VDD_CK_IO

VDD_CK_IO

C105

C105

C0.1u25Y

C0.1u25Y

C C

VCC3

21

80L3_70_0805

80L3_70_0805

R94

R94

15R0805

15R0805

CK_VOUT

CP3 X_COPPERCP3 X_COPPER

L4

L4

21

80L3_70_0805

80L3_70_0805

CP2 X_COPPERCP2 X_COPPER

L2

L2

21

80L3_70_0805

80L3_70_0805

C80

C80

C4.7u10Y0805

C4.7u10Y0805

C87

C87

C46

C46

C0.1u10X0402

C0.1u10X0402

C4.7u10Y0805

C4.7u10Y0805

Q9

Q9

N-PMBS3904_SOT23-RH

N-PMBS3904_SOT23-RH

C E

B

C104

C104

C100p50N0402

C100p50N0402

C92

C92

C10u10Y0805

C10u10Y0805

VDD_CK48

C82

C82

C0.1u10X0402

C0.1u10X0402

C69

C69

C0.1u10X0402

C0.1u10X0402

C90

C90

C96

C96

C10u10Y0805

C10u10Y0805

C10u10Y0805

C10u10Y0805

C94

C94

C0.1u10X0402

C0.1u10X0402

C103

C103

C10u10Y0805

C10u10Y0805

C89

C89

C0.1u10X0402

C0.1u10X0402

C95

C95

C0.1u10X0402

C0.1u10X0402

VDD_CK

VDD_CKIO

C93

C93

C0.1u10X0402

C0.1u10X0402

C91

C91

C0.1u10X0402

C0.1u10X0402

C98

C98

C0.1u10X0402

C0.1u10X0402

C63 C22P50NC63 C22P50N

14.318MHZ16P_D

14.318MHZ16P_D

C71 C22P50NC71 C22P50N

SMBDATA_MAIN(13,16,18,27)

SMBCLK_MAIN(13,16,18,27)

CK_VOUT

PLL_XI

12

Y2

Y2

PLL_XO

Clock Generator - ICS9LP505

U3

U3

VDD_CK

VDD_CK48

VDD_CK

VDD_CKIO

PLL_XI

PLL_XO

CK_VID_GD#

R25 0RR25 0R

R77 33R0402R77 33R0402

47

VDDCPU

31

VDDSRC

16

VDD

2

VDDPCI

9

VDD48

53

VDDREF

41

VDDI/OCPU

12

VDDI/O96MHZ

37

VDDSRCI/O

26

VDDSRCI/O

20

VDDPLL3I/O

52

X1

51

X2

48

CK_PWRGD/PD#

55

SDATA

56

SCLK

40

IO_VOUT

44

GNDCPU

15

GND

34

GNDSRC

23

GNDSRC

19

GND

11

GND48

8

GNDPCI

50

GNDREF

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

DOT96T/SRCT0

DOT96C/SRCC0

SRCT1/SE1

SRCC1/SE2

SRCT2/SATAT

SRCT2/SATAT

SRCT3/CR#_C

SRCC3/CR#_D

PCI_STOP#/SRCT5

CPU_STOP#/SRCC5

SRCT7/CR#_F

SRCC7/CR#_E

CPUT2_ITP/SRCT8

CPUC2_ITP/SRCC8

PCI0/CR#A

PCI1/CR#B

PCI2/TME

PCI4/SRC5_EN

PCI_F5/ITP_EN

FSLA/USB_48MHz

FSLB/TEST_MODE

REF0/FSLC/TESTSEL

ICS/ICS9LP505-2HGLFT

ICS/ICS9LP505-2HGLFT

Trace length less than 0.5inchs

46

45

43

42

CK_DOT96

13

CK_DOT96#

14

CK_PE_SRC1

17

CK_PE_SRC1#

18

CK_PE_SRC2

21

CK_PE_SRC2#

22

CK_PE_SRC3

24

CK_PE_SRC3#

25

CK_PE_SRC4 CK_PE_100M_16PORT

27

SRCT4

SRCC4

SRCT6

SRCC6

PCI3

28

30

29

33

32

36

35

39

38

1

3

4

5

6

7

10

49

54

CK_PE_SRC4#

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

PCICLK1

ICHPCLK

SIOPCLK

1394PCLK

SRC5_EN

ITP_EN

FSA

FSB

FSC

R59 33R0402R59 33R0402

R66 33R0402R66 33R0402

R70 33R0402R70 33R0402

R74 33R0402R74 33R0402

R67 33R0402R67 33R0402

R73 33R0402R73 33R0402

R72 33R0402R72 33R0402

R75 33R0402R75 33R0402

R76 33R0402R76 33R0402

R78 33R0402R78 33R0402

R80 33R0402R80 33R0402

R81 33R0402R81 33R0402

R82 33R0402R82 33R0402

R83 33R0402R83 33R0402

PCICLK1

SIOPCLK

ICHPCLK

1394PCLK 1394_PCLK

SRC5_EN PCI_CLK2

ITP_EN TPM_PCLK

OK

CK_H_CPU

CK_H_CPU#

CK_H_MCH

CK_H_MCH#

CK_96M_DREF

CK_96M_DREF#

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_ICHSATA

CK_ICHSATA#

CK_PE_100M_ICH

CK_PE_100M_ICH#

CK_PE_100M_16PORT#

R27 33R0402R27 33R0402

R42 33R0402R42 33R0402

R37 33R0402R37 33R0402R30 0RR30 0R

R45 33R0402R45 33R0402

R51 33R0402R51 33R0402

R53 33R0402R53 33R0402

R65 22R0402R65 22R0402

R62 22R0402R62 22R0402

R38 33R0402R38 33R0402

PCI_CLK1

SIO_PCLK

ICH_PCLK

SIO_48MCLK

CK_14M_ICH

CK_H_CPU (5)

CK_H_CPU# (5)

CK_H_MCH (8)

CK_H_MCH# (8)

CK_96M_DREF (10)

CK_96M_DREF# (10)

CK_PE_100M_MCH (10)

CK_PE_100M_MCH# (10)

CK_ICHSATA (16)

CK_ICHSATA# (16)

CK_PE_100M_ICH (15)

CK_PE_100M_ICH# (15)

CK_PE_100M_16PORT (18)

CK_PE_100M_16PORT# (18)

PCI_CLK1 (18)

SIO_PCLK (22)

ICH_PCLK (15)

1394_PCLK (20)

PCI_CLK2 (18)

TPM_PCLK (28)

SIO_48MCLK (22)

USB_48MCLK (16)

CK_14M_ICH (16)

C39

C39

X_C10p50N0402

X_C10p50N0402

CK_14M_ICH

PCI_CLK1

ICH_PCLK

USB_48MCLK

SIO_48MCLK

SIO_PCLK

1394_PCLK

PCI_CLK2

TPM_PCLK

C51 X_C10p50N0402C51 X_C10p50N0402

C44 X_C10p50N0402C44 X_C10p50N0402

C59 X_C10p50N0402C59 X_C10p50N0402

C86 X_C10p50N0402C86 X_C10p50N0402

C83 X_C10p50N0402C83 X_C10p50N0402

C70 X_C10p50N0402C70 X_C10p50N0402

C66 X_C10p50N0402C66 X_C10p50N0402

C73 X_C10p50N0402C73 X_C10p50N0402

C74 X_C10p50N0402C74 X_C10p50N0402

CK_14M_ICH

BSEL[0..2] Level Shift

B B

RN3

RN3

FSB FREQUENCY

0

0

266 MHz (1066)

0

200 MHZ (800)

133 MHZ (533)

1

5

1

3

5

7

8P4R-10KR0402

8P4R-10KR0402

TABLE

H_BSL0(10)

H_BSL1(10)

OK

H_BSL2(10)

CPU_BSEL0(5)

CPU_BSEL1(5)

OK

CPU_BSEL2(5)

BSEL

2

A A

1

0

0

0

10

0

0

V_FSB_VTT

246

8

RN5

RN5

8P4R-470R0402

8P4R-470R0402

135

2

4

6

8

7

RN2

RN2

1

3

5

7

8P4R-1KR0402

8P4R-1KR0402

FSA

2

4

6

8

FSB

FSC

OK

Clock Generator VTT Power Down Block

VRM_GD(26,27)

4

VDD_CK VDD_CK VDD_CK

R54

R40

R40

X_10KR0402

X_10KR0402

SIOPCLK SRC5_EN ITP_EN

R36

R36

10KR0402

10KR0402

SIGNAL

SIOPCLK

SRC5_EN

ITP_EN For SRCCLK8CPU_ITPCLK

CK_VID_GD#

R71 220RR71 220R

R54

10KR0402

10KR0402

R43

R43

X_10KR0402

X_10KR0402

Pull-High

Trusted Mode

Enable

SRC5/SRC5#

VIDGDVRM_GD

B

3

Pull-Low

Overclocking

Enable

CPU_STOP#/PCI_STOP#

R56 10KR0402R56 10KR0402

CE

Q6

Q6

N-PMBS3904_SOT23-RH

N-PMBS3904_SOT23-RH

R57

R57

X_10KR0402

X_10KR0402

R58

R58

10KR0402

10KR0402

VDD_CK

USB_48MCLK

SIO_48MCLK

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

R19 47KR0402R19 47KR0402

R26 33KR0402R26 33KR0402

R69 47KR0402R69 47KR0402

R68 33KR0402R68 33KR0402

R64 X_47KR0402R64 X_47KR0402

R63 X_33KR0402R63 X_33KR0402

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Clock Generator - ICS954119

Clock Generator - ICS954119

Clock Generator - ICS954119

MS-7407

MS-7407

MS-7407

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

VCC3V

VCC3V

VCC3V

Rev

Rev

Rev

0A

0A

0A

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

of

of

of

435

435

435

5

H_A#[3..35](8)

MCERR# Chipset does not support this signal

BINIT# Chipset does not support this signal

D D

C C

B B

A A

H_A#[3..35]

H_DBI#[0..3](8)

VTT_OUT_LEFT

H_D#[0..63](8)

H_DBI#[0..3]

H_IERR#(6)

H_FERR#(6,15)

H_STPCLK#(15)

H_INIT#(15)

H_DBSY#(8)

H_DRDY#(8)

H_TRDY#(8)

H_ADS#(8)

H_LOCK#(8)

H_BNR#(8)

H_HIT#(8)

H_HITM#(8)

H_BPRI#(8)

H_DEFER#(8)

PECI(22)

THERMDA(22)

THERMDC(22)

TRMTRIP#(6,15)

H_PROCHOT#(6,16)

H_IGNNE#(15)

H_SMI#(15)

H_A20M#(15)

R344 51R1%0402R344 51R1%0402

CPU_REV_C9

CPU_BSEL0(4)

CPU_BSEL1(4)

CPU_BSEL2(4)

H_PWRGD(6,15)

H_CPURST#(6,8)

H_D#[0..63]

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_IERR#

H_FERR#

H_STPCLK#

H_INIT#

H_DBSY#

H_DRDY#

H_TRDY#

H_ADS#

H_LOCK#

H_BNR#

H_HIT#

H_HITM#

H_BPRI#

H_DEFER#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

PECI

THERMDA

THERMDC

TRMTRIP#

H_PROCHOT#

H_IGNNE#

H_SMI#

H_A20M#

H_TESTHI13

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

H_PWRGD

H_CPURST#

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

G5

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

U14A

U14A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

PECI

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD#AH2

RESERVED0

RESERVED1

RESERVED2

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

H_D#53

H_A#35

H_A#34

AJ6

AJ5

A35#

D52#

C14

C15

H_D#52

H_D#51

H_A#33

AH5

A34#

A33#

D51#

D50#

A14

H_D#50

H_A#31

H_A#32

AH4

A32#

D49#

D17

H_D#49

H_D#48

AG5

A31#

D48#

D20

H_A#29

H_A#30

AG4

AG6

A30#

D47#

D22

G22

H_D#47

H_D#46

H_A#28

AF4

A29#

A28#

D46#

D45#

E22

H_D#45

H_A#27

H_A#26

AF5

AB4

A27#

D44#

F21

G21

H_D#43

H_D#44

4

H_A#25

AC5

A26#

A25#

D43#

D42#

E21

H_D#42

H_A#23

H_A#24

AB5

AA5

A24#

D41#

F20

E19

H_D#41

H_D#40

H_A#22

AD6

A23#

A22#

D40#

D39#

E18

H_D#39

H_A#20

H_A#21

AA4

A21#

A20#Y4A19#Y6A18#W6A17#

D38#

D37#

F18

F17

H_D#38

H_D#37

H_A#18

H_A#19

D36#

G17

G18

H_D#35

H_D#36

H_A#17

AB6

D35#

D34#

E16

H_D#34

H_A#11

H_A#16

H_A#15

H_A#12

H_A#13

H_A#14

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D33#

D32#

D31#

D30#

D29#

D28#

F15

F14

E15

G16

G15

G14

H_D#31

H_D#33

H_D#29

H_D#30

H_D#32

H_D#28

H_A#6

H_A#8

H_A#10

H_A#7

H_A#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D27#

D26#

D25#

D24#

F12

E13

D13

G13

H_D#26

H_D#25

H_D#27

H_D#23

H_D#24

D23#

F11

H_A#4

H_A#5

D22#

E10

D10

H_D#22

H_D#21

R327 X_0R0402R327 X_0R0402

H_A#3

AC2

L5

AN3

DBR#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

H_D#17

H_D#19

H_D#20

H_D#18

H_D#16

AN5

AJ3

AK3

AN4

AN6

ITP_CLK1

ITP_CLK0

VSS_SENSE

VCC_SENSE

VSS_MB_REGULATION

VCC_MB_REGULATION

D14#

D13#

D12#D8D11#

D10#

B12

B10

D11

C12

C11

H_D#14

H_D#11

H_D#12

H_D#15

H_D#10

H_D#13

3

VID7

VID6

VID4

VID5

AM7

AM5

AL4

AK4

VID6

VID5

RSVD/VID7

RSVD/CPU_GTLREF3

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

H_D#9

H_D#8

H_D#6

H_D#5

H_D#7

VCC_VRM_SENSE

VSS_VRM_SENSE

VID[0..7]

VID3

VID1

VID0

VID2

AL6

AM3

AL5

AM2

VID4

VID3

VID2

VID1

VID0

VID_SELECT

GTLREF_SEL

FC5/CPU_GTLREF2

H_D#1

H_D#3

H_D#2

H_D#4

AN7

H1

GTLREF0

H2

GTLREF1

H29

E24

GTLREF2

F2

G10

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

TESTHI12

P1

TESTHI11

H5

TESTHI10

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

FORCEPH

G6

RSVD#G6

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

T2

COMP5

J2

COMP4

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

ADSTB1#

R6

ADSTB0#

C17

DSTBP3#

G19

DSTBP2#

E12

DSTBP1#

B9

DSTBP0#

A16

DSTBN3#

G20

DSTBN2#

G12

DSTBN1#

C8

DSTBN0#

L1

LINT1/NMI

K1

LINT0/INTR

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

B4

H_D#0

FP_RST# (16,29)

VCC_VRM_SENSE (26)

VSS_VRM_SENSE (26)

VID[0..7] (26)

Pull Hi 1K VTT_OUT_RIGHT on PWM

VRD_VIDSEL

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

CPU_MCH_GTLREF

CPU_GTLREF2

CPU_GTLREF3

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

CK_H_CPU#

CK_H_CPU

H_RS#2

H_RS#1

H_RS#0

H_AP#1

H_AP#0

H_BR#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

H_DP#3

H_DP#2

H_DP#1

H_DP#0

H_ADSTB#1

H_ADSTB#0

H_DSTBP#3

H_DSTBP#2

H_DSTBP#1

H_DSTBP#0

H_DSTBN#3

H_DSTBN#2

H_DSTBN#1

H_DSTBN#0

H_NMI

H_INTR

T13T13

T14T14

T7T7

T10T10

T11T11

T8T8

VRD_VIDSEL (26)

CPU_GTLREF0 (6)

CPU_GTLREF1 (6)

T4T4

CPU_MCH_GTLREF (8)

CPU_GTLREF2 (6)

CPU_GTLREF3 (6)

H_REQ#[0..4] (8)

R391 51R1%0402R391 51R1%0402

R340 51R1%0402R340 51R1%0402

R134 51R1%0402R134 51R1%0402

R137 51R1%0402R137 51R1%0402

R367 X_130R1%0402R367 X_130R1%0402

R325 X_51R1%0402R325 X_51R1%0402

R346 49.9R1%0402R346 49.9R1%0402

R324 49.9R1%0402R324 49.9R1%0402

R390 49.9R1%0402R390 49.9R1%0402

R341 49.9R1%0402R341 49.9R1%0402

R358 49.9R1%0402R358 49.9R1%0402

R197 49.9R1%0402R197 49.9R1%0402

COMP 10W/7S

H_ADSTB#1 (8)

H_ADSTB#0 (8)

H_DSTBP#3 (8)

H_DSTBP#2 (8)

H_DSTBP#1 (8)

H_DSTBP#0 (8)

H_DSTBN#3 (8)

H_DSTBN#2 (8)

H_DSTBN#1 (8)

H_DSTBN#0 (8)

H_NMI (15)

H_INTR (15)

2

V_FSB_VTT VTT_OUT_RIGHT

CK_H_CPU# (4)

CK_H_CPU (4)

H_RS#2 (8)

H_RS#1 (8)

H_RS#0 (8)

H_BR#0 (6,8)

VTT_OUT_LEFT

VTT_OUT_LEFT

VID2

VID0

VID5

VID4

VID7

VID3

VID6

VID1

H_TESTHI1

H_TESTHI11

H_TESTHI9

H_TESTHI10

H_BPM#0

H_BPM#1

H_BPM#5

H_BPM#3

H_TDI

H_BPM#2

H_TMS

H_BPM#4

H_TDO

H_TRST#

H_TCK

1

VTT_OUT_RIGHT

RN23

RN23

1

2

3

4

5

6

7

8

8P4R-680R

8P4R-680R

RN24

RN24

1

2

3

4

5

6

7

8

8P4R-680R

8P4R-680R

C0.1u16Y0402

C0.1u16Y0402

RN25

RN25

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

C0.1u16Y0402

C0.1u16Y0402

C397 C0.1u16Y0402C397 C0.1u16Y0402

RN22

RN22

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

C390 C0.1u16Y0402C390 C0.1u16Y0402

RN21

RN21

1

2

3

4

5

6

7

8

8P4R-51R0402

8P4R-51R0402

R352 51R1%0402R352 51R1%0402

R351 51R1%0402R351 51R1%0402

R332 62R0402R332 62R0402

R331 62R0402R331 62R0402

C391

C391

VTT_OUT_LEFT

C396

C396

VTT_OUT_RIGHT

Micro Star Restricted Secret

Micro Star Restricted Secret

H_TESTHI_M_U1(7)

CPU_TP_G1(7)

5

H_TESTHI_M_U1 H_TESTHI12

H_TESTHI8

H_TESTHI9

U1

R375 0R0402R375 0R0402

C9

R363 0R0402R363 0R0402

G1

R364 X_0R0402R364 X_0R0402

G3

R362 0R0402R362 0R0402

G4

R329 0R0402R329 0R0402

H_BPM#1CPU_REV_C9

H_BPM#0CPU_TP_G1

H_BPM#3

H_BPM#2

W2

AJ1

AJ2

AG2

AD2

4

3

2

Title

Title

Title

Intel LGA775 - Signal

Intel LGA775 - Signal

Intel LGA775 - Signal

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

535

535

535

Micro Star Restricted Secret

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

VCCP

4

3

2

1

VCCP

D D

C C

VTT_OUT_RIGHT

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

B B

VTT_OUT_RIGHT

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

R369

R369

115R1%0402-RH

115R1%0402-RH

R370

R370

115R1%0402-RH

115R1%0402-RH

C405

C405

C10U6.3X51206

C10U6.3X51206

U14B

U14B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF8

AF22

AF21

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y29

Y30

GTL_REF0

R355

R355

200R1%0402

200R1%0402

GTL_REF1

R356

R356

200R1%0402

200R1%0402

AF9

VCC

VCC

Y28

AG11

VCC

VCC

Y27

AG12

VCC

VCC

Y26

AG19

AG18

AG15

AG14

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

Y23

Y24

Y25

R342 10R0402-1R342 10R0402-1

C389

C389

C1U6.3X50402-1

C1U6.3X50402-1

R343 10R0402-1R343 10R0402-1

C384

C384

C1U6.3X50402-1

C1U6.3X50402-1

AG21

VCC

VCC

W30

AG22

VCC

VCC

W29

AG25

VCC

VCC

W28

AG26

VCC

VCC

W27

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

AG9

AG8

AG30

VCC

VCC

VCC

VCCU8VCCV8VCC

W23

CPU_GTLREF0

C377

C377

C220P25N0402

C220P25N0402

CPU_GTLREF1

C379

C379

C220P25N0402

C220P25N0402

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

U24

AH27

AH26

AH25

AH22

AH28

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

T28

T29

T30

U23

CPU_GTLREF0 (5)

CPU_GTLREF1 (5)

VCC

VCC

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

N23

N24

N25

N26

N27

N28

N29

N30

V_FSB_VTT

L12 10U100m_0805-RHL12 10U100m_0805-RH

V_1P5_ICH

L10 10U100m_0805-RHL10 10U100m_0805-RH

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

M23

M24

M25

M26

M27

M28

M29

M30

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

21

C170

C170

C10u10Y0805

C10u10Y0805

21

C156

C156

C10u10Y0805

C10u10Y0805

C169

C169

C10u10Y0805

C10u10Y0805

C155

C155

C1U16X5

C1U16X5

AM22

VCC

VCC

J18

AM25

AM26

VCC

VCC

J14

J15

C168

C168

C1U16X5

C1U16X5

H_VCCPLL

AM29

AM30

AM8

AM9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

J11

J12

J13

H_VCCA

H_VSSA

C157

C157

C0.01u16X0402

C0.01u16X0402

AN11

VCC

VCC

AN9

AN12

VCC

VCC

AN8

AN14

AN15

AN18

AN19

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

AN25

AN26

AN29

AN30

AN21

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTTPWRGD

VTT_SEL

RSVD#F29

A23

B23

D23

C23

A25

VTT

A26

VTT

A27

VTT

A28

VTT

A29

VTT

A30

VTT

B25

VTT

B26

VTT

B27

VTT

B28

VTT

B29

VTT

B30

VTT

C25

VTT

C26

VTT

C27

VTT

C28

VTT

C29

VTT

C30

VTT

D25

VTT

D26

VTT

D27

VTT

D28

VTT

D29

VTT

D30

VTT

AM6

AA1

J1

F27

F29

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

H_VCCA

H_VSSA

H_VCCPLL

C160

C160

C10u10Y0805

C10u10Y0805

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

FSB_VTT_SEL

VTT_PWRGOOD

VID_GD#(26,27)

VID_GD#

V_FSB_VTT

C173

C173

C10u10Y0805

C10u10Y0805

VTT_OUT_RIGHT VTT_OUT_LEFT

FSB_VTT_SEL (27)

VTT_OUT_RIGHTVCC5_SB

R401

R401

1KR0402-1

1KR0402-1

R392

R392

VTT_PWG#

2.7KR0402

2.7KR0402

B

C378

C378

C0.1u16Y0402

C0.1u16Y0402

1.25V VTT_PWRGOOD

R379

R379

680R0402

680R0402

CE

Q37

Q37

N-MMBT3904_NL_SOT23

N-MMBT3904_NL_SOT23

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_PWG

C404

C404

X_C1U6.3X50402-1

X_C1U6.3X50402-1

VTT_OUT_RIGHT

R368

R368

115R1%0402-RH

115R1%0402-RH

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

A A

VTT_OUT_RIGHT

R373

R373

115R1%0402-RH

115R1%0402-RH

GTL_REF2

R339

R339

200R1%0402

200R1%0402

GTL_REF3

R372

R372

200R1%0402

200R1%0402

5

R354 10R0402-1R354 10R0402-1

C388

C388

C1U6.3X50402-1

C1U6.3X50402-1

R360 10R0402-1R360 10R0402-1

C395

C395

C1U6.3X50402-1

C1U6.3X50402-1

CPU_GTLREF2

C376

C220P25N0402

C220P25N0402

CPU_GTLREF3

C392

C392

C220P25N0402

C220P25N0402

CPU_GTLREF2 (5)

CPU_GTLREF3 (5)

4

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

CPU signal termination

PLACE AT CPU END OF ROUTE

R365 130R1%0402R365 130R1%0402

R348 62R0402R348 62R0402C376

R139 62R0402R139 62R0402

R350 X_100R1%0402R350 X_100R1%0402

R326 62R0402R326 62R0402

PLACE AT ICH END OF ROUTE

R361 62R0402R361 62R0402

R374 62R0402R374 62R0402

H_PROCHOT#

4W/6S

H_IERR#

4W/6S

H_CPURST#

4W/12S

H_PWRGD

公板有上

H_BR#0

4W/12S

TRMTRIP#

4W/6S

H_FERR#

4W/6S

3

H_PROCHOT# (5,16)

H_IERR# (5)

H_CPURST# (5,8)

H_PWRGD (5,15)

H_BR#0 (5,8)

TRMTRIP# (5,15)

H_FERR# (5,15)

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Intel LGA775 - Power

Intel LGA775 - Power

Intel LGA775 - Power

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

635

635

635

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

U14C

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AE29

AE30

AF10

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

AF27

AF28

AF29

AF30

AC3

AC6

AC7

AD4

AD7

AE2

AE5

AE7

AF3

AF6

AF7

U14C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

A12

A15

A18

A2

A21

A6

A9

AA3

AA6

AA7

AB1

AB7

VSS

AG10

VSS

AG13

VSS

AG16

VSS

AG17

VSS

AG20

VSS

AG23

V30

VSS

AG24

VSSV3VSS

VSS

AG7

V29

AH1

VSS

V28

VSS

VSS

AH10

V27

AH13

VSS

VSS

V26

VSS

VSS

AH16

V25

VSS

VSS

AH17

V24

VSS

VSS

AH20

V23

VSS

VSS

AH23

U7

VSS

VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AH24

AJ10

VSS

AJ13

VSS

R30

VSS

AJ16

D D

C C

B B

R29

AJ17

VSS

VSS

R28

AJ20

VSS

VSS

R27

AJ23

VSS

VSS

R26

AJ24

VSS

VSS

R25

AJ27

VSS

VSS

R24

VSS

VSS

AJ28

4

R23

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

AJ29

AJ30

3

F7

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

VSS

VSS

AM17

VSS

AM20

VSS

AM23

VSS

AM24

VSS

AM27

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AM28

H28

AM4

VSS

VSS

AN1

VSS

VSS

VSS

VSS

AN10

VSS

VSS

AN13

VSS

VSS

AN16

VSS

VSS

AN17

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

AN27

VSS

VSS

AN28

VSS

VSS

VSSB1VSS

B11

VSS

VSS

VSS

VSS

Y3

COMP6

AE3

COMP7

RSVD/COMP8

VSS

VSS

B14

B17

B20

B13

AE4

RSVD#AE4

D1

RSVD#D1

D14

RSVD#D14

E5

RSVD#E5

E6

RSVD#E6

RSVD#E7

RSVD#E23

RSVD#F23

RSVD

RSVD#J3

RSVD#N4

RSVD#P5

RSVD#AC4

IMPSEL#

MSID1

MSID0

FC28

FC27

FC26

FC23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

ZIF-SOCK775-15U-IN,ZIF-SOCK775-15U-IN_TH

B24

E7

E23

F23

AL3

J3

N4

P5

AC4

F6

V1

W1

U1

G1

E29

A24

F4

F22

F19

F16

F13

F10

E8

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

CPU_TP_E7

CPU_TP_E23

CPU_TP_F23

CPU_GND_AL3

IMPSEL

MSID1

MSID0

H_TESTHI_M_U1

CPU_TP_G1

CPU_GND_E29

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK2

AK10

AK13

AK16

AK17

AK20

AK23

AK24

AK27

VSS

AK28

VSS

AK29

VSS

AK30

L30

L29

L28

L27

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

L26

AL24

VSS

VSS

L25

AL27

VSS

VSS

L24

AL28

VSS

VSS

K2

L23

K5

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

AM13

AM16

H_COMP6

H_COMP7

H_COMP8

R322 51R1%0402R322 51R1%0402

R347 51R1%0402R347 51R1%0402

R376 51R1%0402R376 51R1%0402

2

R349 49.9R1%0402R349 49.9R1%0402

R330 49.9R1%0402R330 49.9R1%0402

R200 24.9R1%0402R200 24.9R1%0402

1

TP7TP7

1

TP2TP2

1

TP3TP3

1

TP8TP8

VTT_OUT_RIGHT

10W/7S

10W/7S

R359 X_0R0402R359 X_0R0402

R323 51R1%0402R323 51R1%0402

R136 X_1KR0402R136 X_1KR0402

R142 X_1KR0402R142 X_1KR0402

CPU_TP_G1

H_TESTHI_M_U1

1

VTT_OUT_LEFT

CPU_TP_G1 (5)

H_TESTHI_M_U1 (5)

CPU DECOUPLING CAPACITORS

+

+

EC24 C100U2SP-LF

EC24 C100U2SP-LF

A A

5

1 2

C183 C22u6.3X50805-RHC183 C22u6.3X50805-RH

C227 C22u6.3X50805-RHC227 C22u6.3X50805-RH

C229 C22u6.3X50805-RHC229 C22u6.3X50805-RH

C230 C22u6.3X50805-RHC230 C22u6.3X50805-RH

C231 C22u6.3X50805-RHC231 C22u6.3X50805-RH

C232 C22u6.3X50805-RHC232 C22u6.3X50805-RH

C233 C22u6.3X50805-RHC233 C22u6.3X50805-RHC146 C22u6.3X50805-RHC146 C22u6.3X50805-RH

C234 C22u6.3X50805-RHC234 C22u6.3X50805-RH

C242 C22u6.3X50805-RHC242 C22u6.3X50805-RH

C245 C22u6.3X50805-RHC245 C22u6.3X50805-RH

C246 C22u6.3X50805-RHC246 C22u6.3X50805-RH

4

VCCPVCCP VCCP

C247 C22u6.3X50805-RHC247 C22u6.3X50805-RH

C248 C22u6.3X50805-RHC248 C22u6.3X50805-RH

C249 C22u6.3X50805-RHC249 C22u6.3X50805-RH

C250 C22u6.3X50805-RHC250 C22u6.3X50805-RH

C263 C22u6.3X50805-RHC263 C22u6.3X50805-RH

C145 C22u6.3X50805-RHC145 C22u6.3X50805-RH

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Intel LGA775 - GND

Intel LGA775 - GND

Intel LGA775 - GND

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

3

2

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

735

735

735

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

V_FSB_VTT V_1P25_MCH

4

3

2

1

H_A#[3..35](5)

D D

C C

H_REQ#[0..4](5)

B B

H_CPURST#(5,6)

ICH_SYNC#(16)

R148 16.5R1%0402-RHR148 16.5R1%0402-RH

VCC3

R253 X_1KR0402R253 X_1KR0402

H_A#[3..35]

H_A#3

J42

H_A#4

L39

H_A#5

J40

H_A#6

L37

H_A#7

L36

H_A#8

K42

H_A#9

N32

H_A#10

N34

H_A#11

M38

H_A#12

N37

H_A#13

M36

H_A#14

R34

H_A#15

N35

H_A#16

N38

H_A#17

U37

H_A#18

N39

H_A#19

R37

H_A#20

P42

H_A#21

R39

H_A#22

V36

H_A#23

R38

H_A#24

U36

H_A#25

U33

H_A#26

R35

H_A#27

V33

H_A#28

V35

H_A#29

Y34

H_A#30

V42

H_A#31

V38

H_A#32

Y36

H_A#33

Y38

H_A#34

Y39

H_A#35

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

ICHSYNC#

W10/S7

W4/S14

W4/S14

W10/S5

V_1P25_MCH

AA37

M34

G43

W40

W41

AA42

W42

G39

AA41

AM17

AM18

U34

F40

L35

L38

J37

Y40

T43

Y43

U42

V41

U40

U41

U39

R32

U32

C31

J13

D23

C25

D25

B25

D24

B24

H_ADSTB#0(5)

H_ADSTB#1(5)

H_REQ#[0..4]

H_ADS#(5)

H_TRDY#(5)

H_DRDY#(5)

H_DEFER#(5)

H_HITM#(5)

H_HIT#(5)

H_LOCK#(5)

H_BR#0(5,6)

H_BNR#(5)

H_BPRI#(5)

H_DBSY#(5)

H_RS#0(5)

H_RS#1(5)

CK_H_MCH(4)

CK_H_MCH#(4)

PWRGD(16,27)

PLTRST#(10,15,27)

H_RS#2(5)

R249 0R0402R249 0R0402

ICHSYNC#

H_ADSTB#0

H_ADSTB#1

H_ADS#

H_TRDY#

H_DRDY#

H_DEFER#

H_HITM#

H_HIT#

H_LOCK#

H_BR#0

H_BNR#

H_BPRI#

H_DBSY#

H_RS#0

H_RS#1

H_RS#2

HXRCOMP

HXSCOMP

HXSCOMP#

HXSWING

MCH_GTLREF

U20A

U20A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HADSTB0#

HADSTB1#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADS#

HTRDY#

HDRDY#

HDEFER#

HHITM#

HHIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSCOMP#

HSWING

HDVREF

HACCVREF

P29

P27

P26

P24

P23

N29

N26

N24

N23

M29

M24

M23

L24

L23

K24

K23

J24

J23

H24

H23

G26

G24

G23

F26

F24

F23

E29

E27

E26

E23

D29

D28

D27

C30

C29

C27

B30

B29

B28

B27

A30

A28

R27

R26

R24

R23

AG19

AG18

AG17

AG15

AG14

AF26

AF25

AF24

AF22

AF20

AF18

AF17

AF15

AF14

AE27

AE26

AE25

AE23

AE21

AE19

AE17

AD27

AD26

AD18

AD17

AD15

AD14

AC27

AC26

AC17

AC15

AC14

AB27

AB26

AB18

AB17

AA27

AA26

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AJ12

VCC

AJ11

VCC

AJ10

VCC

VCC

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDSTBP0#

HDSTBN0#

HDSTBP1#

HDSTBN1#

HDSTBP2#

HDSTBN2#

HDSTBP3#

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCY6VCC

VCC

VCC

VCCV9VCC

VCC

VCCU9VCCU6VCCU3VCC

VCC

VCCN9VCCN8VCCN6VCCN3VCCL6VCCJ6VCCJ3VCCJ2VCCG2VCC

AJ9

AJ8

AJ7

AJ6

AJ5

AJ4

AJ3

AJ2

AH4

AH2

AH1

AG13

AG12

AG11

AG10

AG9

AG8

AG7

AG6

AG5

AG4

AG3

AG2

AF13

AF12

AF11

AD24

AD22

AD20

AC25

AC23

AC21

AC19

AC13

AC6

AB24

AB22

AB20

AA25

AA23

AA21

AA19

AA13

Y24

Y22

Y20

Y13

V13

V12

V10

U13

U10

N12

AA3

N11

F11

VCCF9VCCD4VCC

C13

VCCC9VCC

P20

HDSTBN3#

VCC

VCC

VCC

VCC

INTEL-NR88BOBVBVA[G31]-A1-RH

Y11

AG25

INTEL-NR88BOBVBVA[G31]-A1-RH

AG21

AG20

R40

P41

R41

N40

R42

M39

N41

N42

L41

J39

L42

J41

K41

G40

F41

F42

C42

D41

F38

G37

E42

E39

E37

C39

B39

G33

A37

F33

E35

K32

H32

B34

J31

F32

M31

E31

K31

G31

K29

F31

J29

F29

L27

K27

H26

L26

J26

M26

C33

C35

E41

B41

D42

C40

D35

B40

C38

D37

B33

D33

C34

B35

A32

D32

M40

J33

G29

E33

L40

M43

G35

H33

G27

H27

B38

D38

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0

H_DSTBN#0

H_DSTBP#1

H_DSTBN#1

H_DSTBP#2

H_DSTBN#2

H_DSTBP#3

H_DSTBN#3

H_D#[0..63]

H_DBI#[0..3]

H_DSTBP#0 (5)

H_DSTBN#0 (5)

H_DSTBP#1 (5)

H_DSTBN#1 (5)

H_DSTBP#2 (5)

H_DSTBN#2 (5)

H_DSTBP#3 (5)

H_DSTBN#3 (5)

H_D#[0..63] (5)

H_DBI#[0..3] (5)

V_FSB_VTT V_FSB_VTT V_FSB_VTT

A A

R169 49.9R1%0402R169 49.9R1%0402

W4/S14

R170 49.9R1%0402R170 49.9R1%0402

W4/S14

HXSCOMP

C223

X_C2.7P25N0402

X_C2.7P25N0402

HXSCOMP#

C224

C224

X_C2.7P25N0402

X_C2.7P25N0402

5

HXSWING SHOULD BE 1/4*VTT

R156

R156

301R1%0402

301R1%0402

R157

R157

100R1%0402

100R1%0402

R187 51R1%0402R187 51R1%0402 R168 51R1%0402R168 51R1%0402

C208

C208

C0.01u16X0402

C0.01u16X0402

HXSWINGHX_SWING MCH_GTLREF

W10/S5

4

*GTLREF VOLTAGE SHOULD BE

0.63*VTT=0.756V

R149

R149

100R1%0402

100R1%0402

R155

R155

200R1%0402

200R1%0402

C194

C194

C1U6.3X50402-1

C1U6.3X50402-1

CPU_MCH_GTLREF

C222

C222

C220P25N0402

C220P25N0402

3

CPU_MCH_GTLREF (5)

V_FSB_VTT

C203 X_C0.1u16Y0402C203 X_C0.1u16Y0402C223

C209 C0.1u16Y0402C209 C0.1u16Y0402

C186 C10u10Y0805C186 C10u10Y0805

C198 C1u16YC198 C1u16Y

2

R268 0R0402R268 0R0402

C323 C0.01u16X0402C323 C0.01u16X0402

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MCH_CLPWROKPWRGD

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Broadwater G31 - CPU

Broadwater G31 - CPU

Broadwater G31 - CPU

MS-7407

MS-7407

MS-7407

1

MCH_CLPWROK (10)

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Rev

Rev

Rev

0A

0A

0A

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

of

of

of

835

835

835

5

4

3

2

1

DATA_B48

DATA_B47

AL32

AG38

SDQ_B47

SDQ_B48

SDQ_A47

SDQ_A48

AJ40

AL39

DATA_A47

DATA_A48

DQM_A[0..7](13)

DATA_B49

DATA_B50

AJ38

AF35

SDQ_B49

SDQ_B50

SDQ_A49

SDQ_A50

AF39

AH43

DATA_A49

DATA_A50

DATA_B52

DATA_B51

AF33

AJ37

SDQ_B51

SDQ_B52

SDQ_A51

SDQ_A52

AJ42

AE40

DATA_A52

DATA_A51

DQM_B[0..7]

DATA_B55

DATA_B53

DATA_B54

AJ35

AG33

AF34

SDQ_B53

SDQ_B54

SDQ_B55

SDQ_A53

SDQ_A54

SDQ_A55

AJ41

AF41

AF42

DATA_A55

DATA_A54

DATA_A53

DATA_B56

DATA_B57

AD36

AC33

SDQ_B56

SDQ_B57

SDQ_A56

SDQ_A57

AD40

AD43

DATA_A56

DATA_A57

DQM_A[0..7]

SCKE_B1

SCKE_B0

DATA_B58

DATA_B59

AA34

AA36

SDQ_B58

SDQ_B59

SDQ_A58

SDQ_A59

AB41

AA40

DATA_A58

DATA_A59

DATA_B61

DATA_B60

AD34

AF38

SDQ_B60

SDQ_B61

SDQ_A60

SDQ_A61

AE42

AE41

DATA_A61

DATA_A60

DATA_B63

DATA_B62

AC34

AA33

SDQ_B62

SDQ_B63

SDQ_A62

SDQ_A63

AB42

AC39

DATA_A63

DATA_A62

AY12

AW12

SCKE_B0

SCKE_A0

AY20

BC20

SCKE_A1

SCKE_A0

BB11

BA11

SCKE_B1

Reserved20

Reserved16

SCKE_A1

Reserved13

Reserved17

AY21

BA19

DQM_B0

DQM_B1

AR7

AW9

SDM_B0

SDM_A0

BA2

AR2

DQM_A1

DQM_A0

DQM_B3

DQM_B2

AW13

AP23

SDM_B1

SDM_B2

SDM_A1

SDM_A2

AY9

AN18

DQM_A2

DQM_A3

DQM_B4

DQM_B5

AU37

AM37

SDM_B3

SDM_B4

SDM_A3

SDM_A4

AU43

AM43

DQM_A4

DQM_A5

DQM_B6

DQM_B7

AG39

AD38

SDM_B5

SDM_B6

SDM_A5

SDM_A6

AC40

AG40

DQM_A6

DQM_A7

SDM_B7

SMRCOMPVOL

SMRCOMPVOH

SDM_A7

SCS_B0#

SCS_B1#

Reserved14

Reserved15

SRAS_B#

SCAS_B#

SWE_B#

SMA_B0

SMA_B1

SMA_B2

SMA_B3

SMA_B4

SMA_B5

SMA_B6

SMA_B7

SMA_B8

SMA_B9

SMA_B10

SMA_B11

SMA_B12

SMA_B13

SMA_B14

SODT_B0

SODT_B1

Reserved21

Reserved22

SBS_B0

SBS_B1

SBS_B2

SDQS_B0

SDQS_B0#

SDQS_B1

SDQS_B1#

SDQS_B2

SDQS_B2#

SDQS_B3

SDQS_B3#

SDQS_B4

SDQS_B4#

SDQS_B5

SDQS_B5#

SDQS_B6

SDQS_B6#

SDQS_B7

SDQS_B7#

SCLK_B0

SCLK_B0#

SCLK_B1

SCLK_B1#

SCLK_B2

SCLK_B2#

Reserved7

Reserved8

Reserved9

Reserved10

Reserved11

Reserved12

SVREF

VCC_DDR

SCS_B#0

BB27

SCS_B#1

BB30

AY27

AY31

RAS_B#

AW26

CAS_B#

AW29

WE_B#

BA27

MAA_B0

BB17

MAA_B1

AY17

MAA_B2

BA17

MAA_B3

BC16

MAA_B4

AW15

MAA_B5

BA15

MAA_B6

BB15

MAA_B7

BA14

MAA_B8

AY15

MAA_B9

BB14

MAA_B10

AW18

MAA_B11

BB13

MAA_B12

BA13

MAA_B13

AY29

MAA_B14

AY13

ODT_B0

BA29

ODT_B1

BA30

BB29

BB31

SBS_B0

AY19

SBS_B1

BA18

SBS_B2

BC12

DQS_B0

AV6

DQS_B#0

AU5

DQS_B1

AR12

DQS_B#1

AP12

DQS_B2

AP15

DQS_B#2

AR15

DQS_B3

AT24

DQS_B#3

AU26

DQS_B4

AW39

DQS_B#4

AU39

DQS_B5

AL35

DQS_B#5

AL34

DQS_B6

AG35

DQS_B#6

AG36

DQS_B7

AC36

DQS_B#7

AC37

P_DDR0_B

AV31

N_DDR0_B

AW31

P_DDR1_B

AU27

N_DDR1_B

AT27

AV32

N_DDR2_B

AT32

AU29

AR29

AV29

AW27

AN33

AP32

MCH_VREF

AM6

DDR_RCOMPVOL

AM8

AM10

DDR_RCOMPVOH

R286 1KR1%0402R286 1KR1%0402

R287

C338

C338

C1u16Y

C1u16Y

R287

1KR1%0402

1KR1%0402

SCS_B#0 (14)

SCS_B#1 (14)

MAA_B[0..14]

ODT_B[0..1]

SBS_B[0..2]

DQS_B0 (14)

DQS_B#0 (14)

DQS_B1 (14)

DQS_B#1 (14)

DQS_B2 (14)

DQS_B#2 (14)

DQS_B3 (14)

DQS_B#3 (14)

DQS_B4 (14)

DQS_B#4 (14)

DQS_B5 (14)

DQS_B#5 (14)

DQS_B6 (14)

DQS_B#6 (14)

DQS_B7 (14)

DQS_B#7 (14)

P_DDR0_B (14)

N_DDR0_B (14)

P_DDR1_B (14)

N_DDR1_B (14)

P_DDR2_B (14)

N_DDR2_B (14)

MCH_VREF

10W/10S

C336

C336

C0.1u16Y0402

C0.1u16Y0402

RAS_B# (14)

CAS_B# (14)

WE_B# (14)

MAA_B[0..14] (14)

ODT_B[0..1] (14)

SBS_B[0..2] (14)

DDR_RCOMPVOL = 0.2 * VCC_DDR

C317 C0.01u16X0402C317 C0.01u16X0402

R271 1KR1%0402R271 1KR1%0402

R275

R275

3.01KR1%0402

3.01KR1%0402

R270 1KR1%0402R270 1KR1%0402

C324 C0.01u16X0402C324 C0.01u16X0402

DDR_RCOMPVOH = 0.8 * VCC_DDR

VCC_DDR

DQM_B[0..7](14)

SCKE_B1(14)

DATA_B42

DATA_B41

AM35

AM38

SDQ_B40

SDQ_B41

SDQ_A40

SDQ_A41

AN41

AM39

DATA_A41

DATA_A42

DATA_B44

DATA_B43

AJ34

AL38

SDQ_B42

SDQ_B43

SDQ_A42

SDQ_A43

AK42

AK41

DATA_A44

DATA_A43

DATA_B45

DATA_B46

AR39

AM34

AL37

SDQ_B44

SDQ_B45

SDQ_A44

SDQ_A45

AL42

AN40

AN42

DATA_A45

DATA_A46

SCKE_B0(14)

SDQ_B46

SDQ_A46

SCKE_A0(13)

SCKE_A1(13)

DATA_B[0..63](14)

D D

SCS_A#0(13)

SCS_A#1(13)

RAS_A#(13)

CAS_A#(13)

WE_A#(13)

MAA_A[0..14](13)

C C

B B

A A

C316

C316

C0.1u16Y0402

C0.1u16Y0402

ODT_A[0..1](13)

SBS_A[0..2](13)

VCC_DDR

DATA_B[0..63]

SCS_A#0

SCS_A#1

MAA_A[0..14]

ODT_A[0..1]

SBS_A[0..2]

DQS_A0(13)

DQS_A#0(13)

DQS_A1(13)

DQS_A#1(13)

DQS_A2(13)

DQS_A#2(13)

DQS_A3(13)

DQS_A#3(13)

DQS_A4(13)

DQS_A#4(13)

DQS_A5(13)

DQS_A#5(13)

DQS_A6(13)

DQS_A#6(13)

DQS_A7(13)

DQS_A#7(13)

P_DDR0_A(13)

N_DDR0_A(13)

P_DDR1_A(13)

N_DDR1_A(13)

P_DDR2_A(13)

N_DDR2_A(13)

R284 20R1%0402R284 20R1%0402

R274 20R1%0402R274 20R1%0402

R321 20R1%0402R321 20R1%0402

R333 20R1%0402R333 20R1%0402

DATA_A[0..63](13)

DATA_B0

DATA_B4

DATA_B3

DATA_B2

DATA_B1

DATA_B6

DATA_B5

DATA_B9

DATA_B7

DATA_B8

DATA_B13

DATA_B11

DATA_B14

DATA_B12

DATA_B10

AP13

AN6

AN9

SDQ_B5

SDQ_A5

AP2

AU1

DATA_A6

DATA_A5

AU7

AT11

SDQ_B6

SDQ_B7

SDQ_A6

SDQ_A7

AV4

AY2

DATA_A8

DATA_A7

AU11

SDQ_B8

SDQ_B9

SDQ_A8

SDQ_A9

AY3

BB5

DATA_A9

DATA_A10

AR13

SDQ_B10

SDQ_A10

AY6

DATA_A11

AN7

AN8

AW5

AW7

SDQ_B0

SDQ_A0

AR5

DATA_A1

DATA_A0

SDQ_B1

SDQ_A1

AV3

AR4

DATA_A2

AN5

SDQ_B2

SDQ_B3

SDQ_A2

SDQ_A3

AV2

AP3

DATA_A3

DATA_A4

SDQ_B4

SDQ_A4

U20B

U20B

AW35

SCS_A0#

BA35

SCS_A1#

BA34

Reserved18

BB38

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

MAA_A14

ODT_A0

ODT_A1

SBS_A0

SBS_A1

SBS_A2

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A P_DDR2_B

N_DDR2_A

SRCOMP0

SRCOMP1

SRCOMP2

SRCOMP3

5W/10S

DATA_A[0..63]

Reserved24

BB33

SRAS_A#

AY35

SCAS_A#

BB34

SWE_A#

BA31

SMA_A0

BB25

SMA_A1

BA26

SMA_A2

BA25

SMA_A3

AY25

SMA_A4

BA23

SMA_A5

AY24

SMA_A6

AY23

SMA_A7

BB23

SMA_A8

BA22

SMA_A9

AY33

SMA_A10

BB22

SMA_A11

AW21

SMA_A12

AY38

SMA_A13

BA21

SMA_A14

AY37

SODT_A0

BA38

SODT_A1

BB35

Reserved23

BA39

Reserved19

BA33

SBS_A0

AW32

SBS_A1

BB21

SBS_A2

AU4

SDQS_A0

AR3

SDQS_A0#

BB3

SDQS_A1

BA4

SDQS_A1#

BB9

SDQS_A2

BA9

SDQS_A2#

AT20

SDQS_A3

AU18

SDQS_A3#

AR41

SDQS_A4

AR40

SDQS_A4#

AL41

SDQS_A5

AL40

SDQS_A5#

AG42

SDQS_A6

AG41

SDQS_A6#

AC42

SDQS_A7

AC41

SDQS_A7#

AU31

SCLK_A0

AR31

SCLK_A0#

AP27

SCLK_A1

AN27

SCLK_A1#

AV33

SCLK_A2

AW33

SCLK_A2#

AP29

Reserved3

AP31

Reserved4

AM26

Reserved1

AM27

Reserved2

AT33

Reserved5

AU33

Reserved6

AN2

SRCOMP0

AN3

SRCOMP1

BB40

SRCOMP2

BA40

SRCOMP3

INTEL-NR88BOBVBVA[G31]-A1-RH

INTEL-NR88BOBVBVA[G31]-A1-RH

AR11

AU9

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_A11

SDQ_A12

SDQ_A13

AW2

AW3

DATA_A12

DATA_A13

DATA_B15

AV12

AU12

SDQ_B14

SDQ_B15

SDQ_A14

SDQ_A15

BA5

BB4

DATA_A15

DATA_A14

DATA_B16

DATA_B17

AU15

AV13

SDQ_B16

SDQ_B17

SDQ_A16

SDQ_A17

AY7

BC7

DATA_A17

DATA_A16

DATA_B18

DATA_B19

AU17

AT17

SDQ_B18

SDQ_B19

SDQ_A18

SDQ_A19

AY11

AW11

DATA_A18

DATA_A19

DATA_B21

DATA_B20

AU13

AM13

SDQ_B20

SDQ_B21

SDQ_A20

SDQ_A21

BB6

BA6

DATA_A20

DATA_A21

DATA_B22

DATA_B23

AV15

AW17

SDQ_B22

SDQ_B23

SDQ_A22

SDQ_A23

BA10

BB10

DATA_A22

DATA_A23

DATA_B25

DATA_B24

AV24

AT23

SDQ_B24

SDQ_B25

SDQ_A24

SDQ_A25

AT18

AR18

DATA_A25

DATA_A24

DATA_B27

DATA_B26

AT26

AP26

SDQ_B26

SDQ_B27

SDQ_A26

SDQ_A27

AT21

AU21

DATA_A27

DATA_A26

DATA_B28

DATA_B29

AU23

AW23

SDQ_B28

SDQ_B29

SDQ_A28

SDQ_A29

AP17

AN17

DATA_A29

DATA_A28

DATA_B31

DATA_B30

AR24

AN26

SDQ_B30

SDQ_B31

SDQ_A30

SDQ_A31

AP20

AV20

DATA_A31

DATA_A30

DATA_B33

DATA_B32

AW37

AV38

SDQ_B32

SDQ_B33

SDQ_A32

SDQ_A33

AV42

AU40

DATA_A33

DATA_A32

DATA_B34

DATA_B35

AN36

AN37

SDQ_B34

SDQ_B35

SDQ_A34

SDQ_A35

AP42

AN39

DATA_A34

DATA_A35

DATA_B36

DATA_B37

AU35

AR35

SDQ_B36

SDQ_B37

SDQ_A36

SDQ_A37

AV40

AV41

DATA_A37

DATA_A36

DATA_B38

DATA_B39

AN35

AR37

SDQ_B38

SDQ_B39

SDQ_A38

SDQ_A39

AP41

AR42

DATA_A38

DATA_A39

DATA_B40

DATA_A40

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Broadwater G31 - Memory

Broadwater G31 - Memory

Broadwater G31 - Memory

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7407

MS-7407

MS-7407

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Thursday, May 31, 2007

Thursday, May 31, 2007

Thursday, May 31, 2007

Sheet

Sheet

Sheet

935

935

935

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

U20C

U20C

PE0RX0+(18)

PE0RX0-(18)

PE0RX1+(18)

PE0RX1-(18)

PE0RX2+(18)

D D

V_1P25_MCH

C162 C0.1u16Y0402C162 C0.1u16Y0402

R218 5.1KR0402R218 5.1KR0402

C C

R221 5.1KR0402R221 5.1KR0402

R230 5.1KR0402R230 5.1KR0402

R238 5.1KR0402R238 5.1KR0402

EXP_PRSNT(18)

B B

V_1P25_MCH

EC20 CD470U10EL11-RH

EC20 CD470U10EL11-RH

V_1P25_MCH

L15 10U100m_0805L15 10U100m_0805

A A

V_1P25_MCH

L17 10U100m_0805L17 10U100m_0805

DMI_ITP_MRP_0

DMI_ITP_MRP_1

DMI_ITP_MRP_2

DMI_ITP_MRP_3

V_1P25_MCH

for Graphic 946GZ

V_1P5_ICH