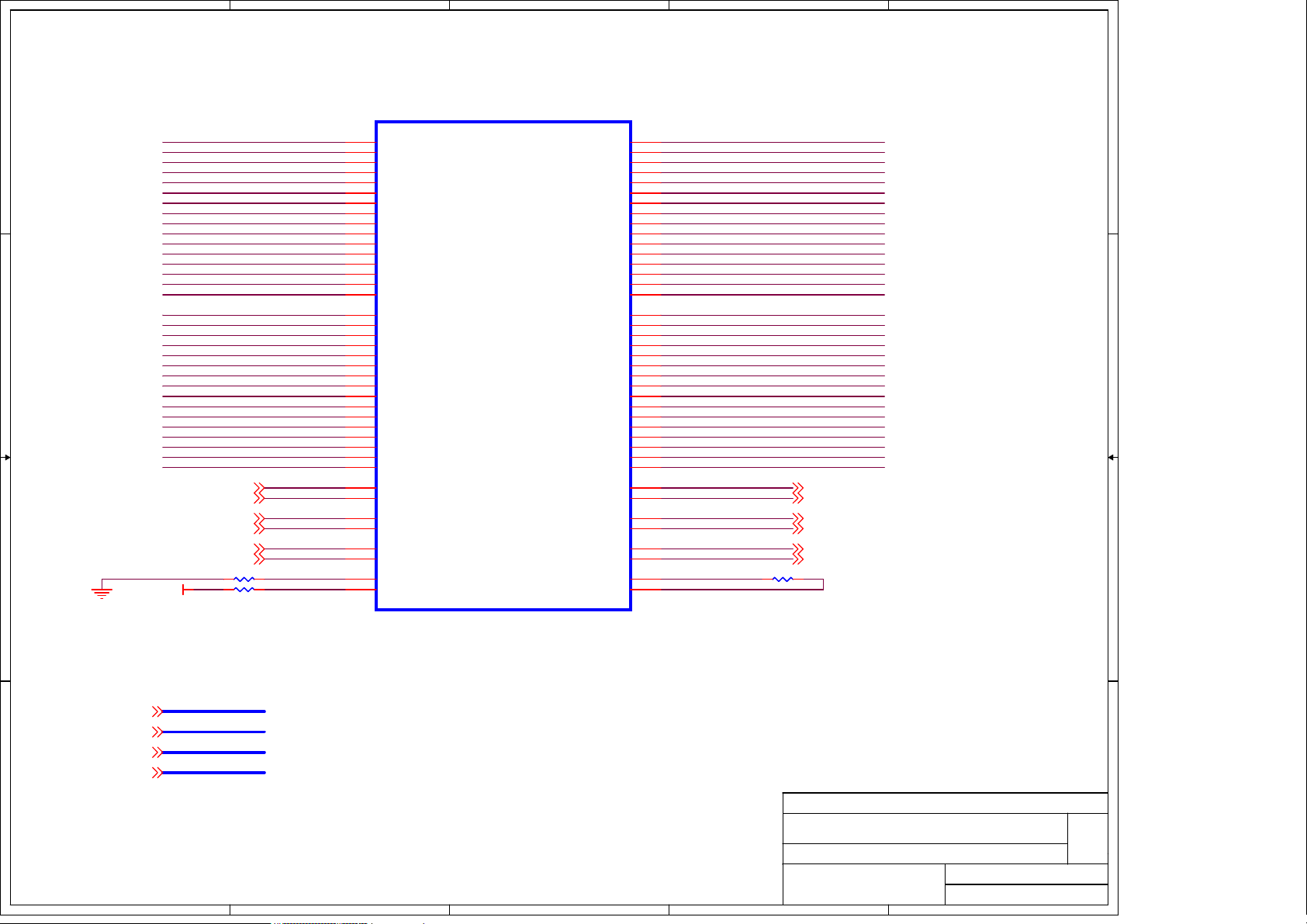

MSI MS-7405 Schematics

5

4

3

2

1

MSI

MS-7405 Ver:0A

D D

C C

B B

CPU:

AMD M2 Athlon 64/Athlon 64 FX

System Chipset:

ATI RS485/RS690

ATI SB460/SB600

On Board Chipset:

Winbond Super I/O -- W83627DHG Ver.C

LAN -- RTL8110SC

HD Codec --ALC888

BIOS -- SPI ROM

Main Memory:

DDR * 4 (Max 4GB)

Expansion Slots:

PCI-E X 1 *3

PCI-E X 16 *1

PWM:

Controller--Intersil ISL6566CR 3 Phase

Clock Generator:

Controller--RTM 870T-691

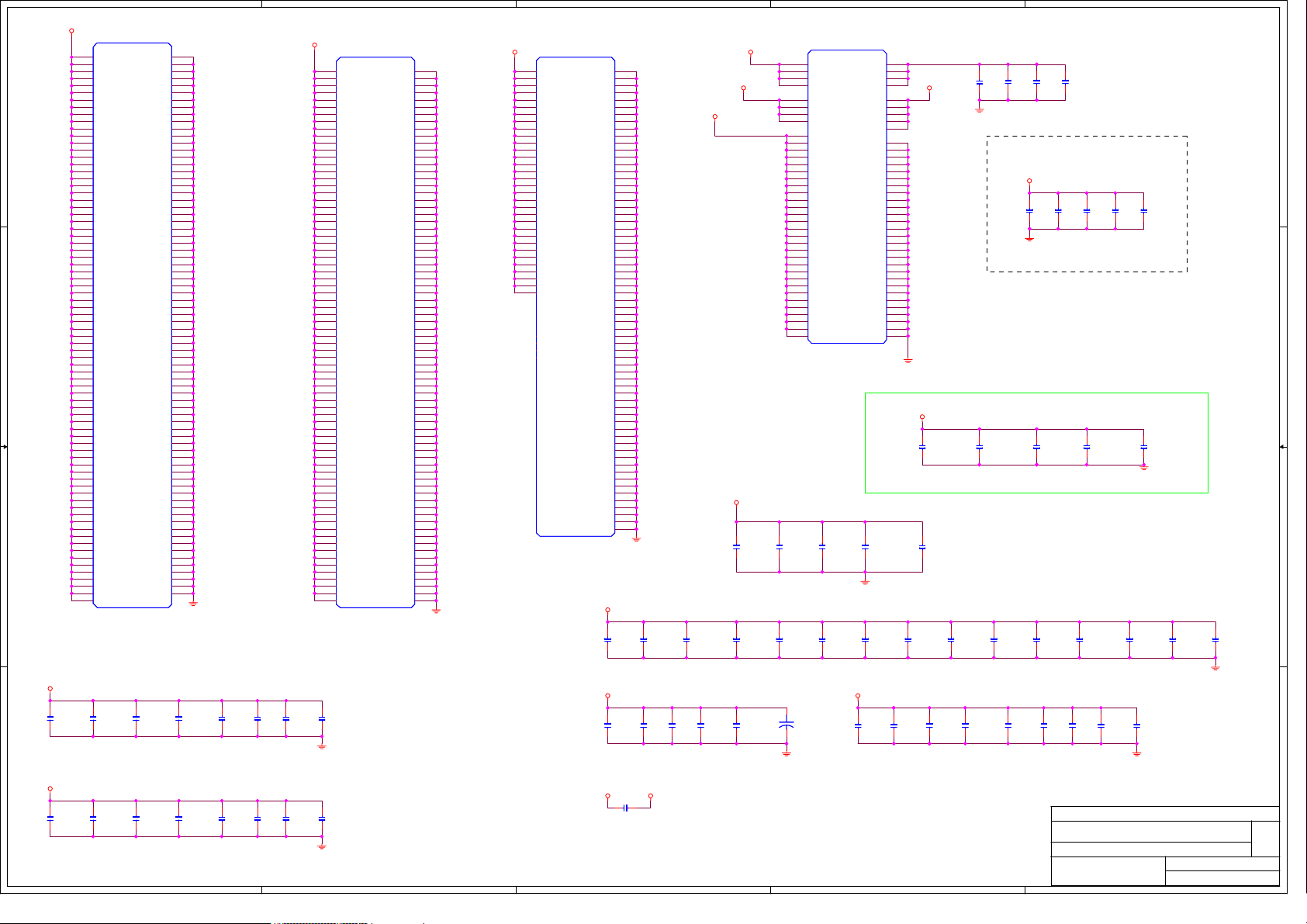

Title Page

Cover Sheet 1

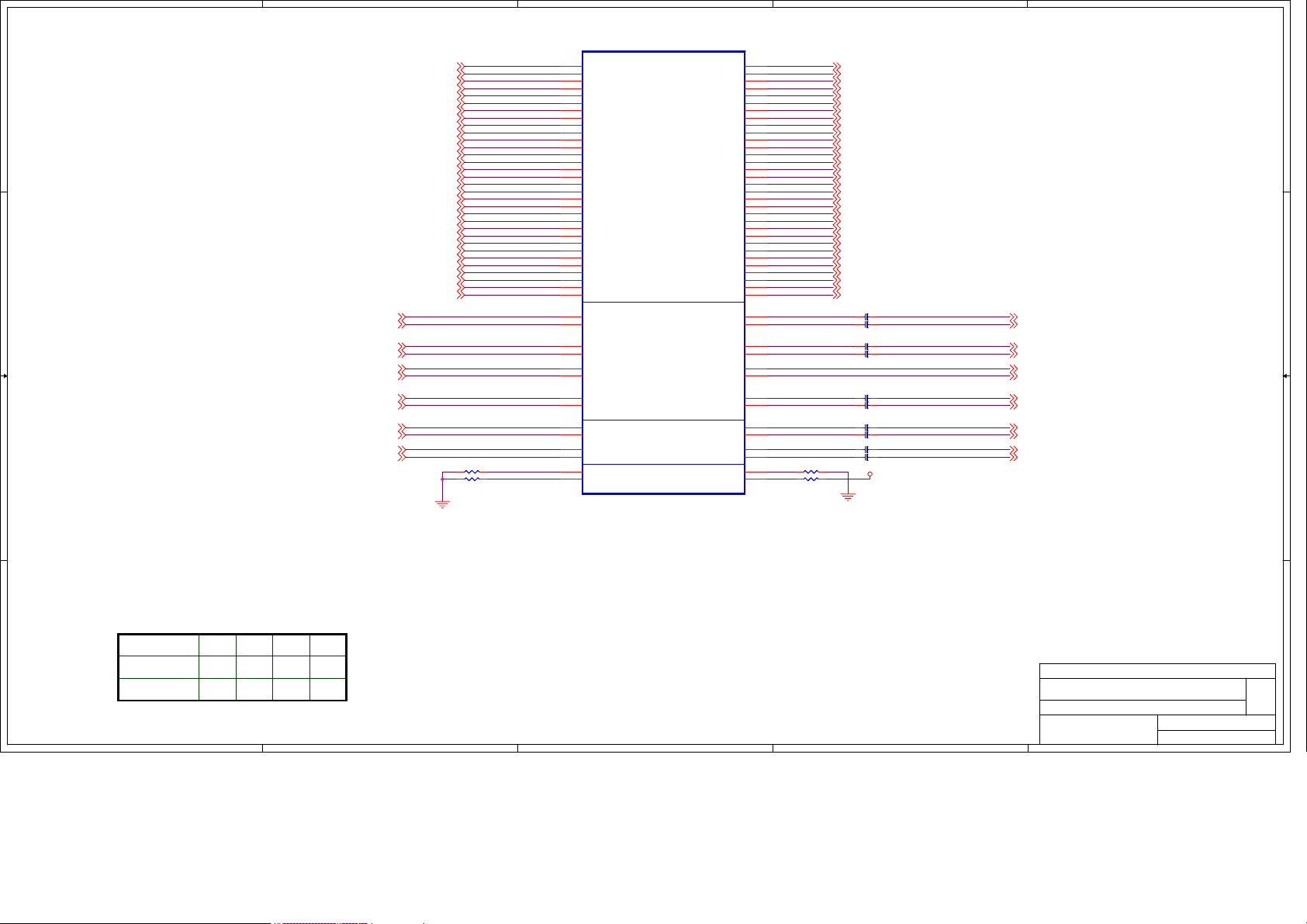

Block Diagram

AMD M2 940

System Memory

DDR2 Terminations

ATI RS690

CLOCK GENERATOR RTM 870T-691

ATI SB600

DAE-3 Circuit

PCI-Express X 16 ,X1

I/O W83627DHG Ver.C / FDD/TPM

LAN RTL8101E/RTL8111B

HD Audio - ALC888

1394 Controller-VT6308

USB connectors

PWM - ISL6566CR

MS-6 ACPI Controller & MS-6+

IDE / SATA / FAN / LPT

ATX Connector / Front Panel / KB / CON

VGA Connector

GPIO/PCI Config.

MANUAL PARTS

Revision history

Option Part

POWER MAP

POWER OK MAP

RESET MAP

2

3,4,5

6,7

8

9-12

13

14-18

19

20

21

22

23

24

25

26

27-28

29

30

31

32

33

34

35

36

37

38

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

Cover Sheet

Cover Sheet

Cover Sheet

1

MS-7405

MS-7405

MS-7405

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

Rev

Rev

Rev

0A

0A

0A

of

of

of

139

139

139

5

4

3

2

1

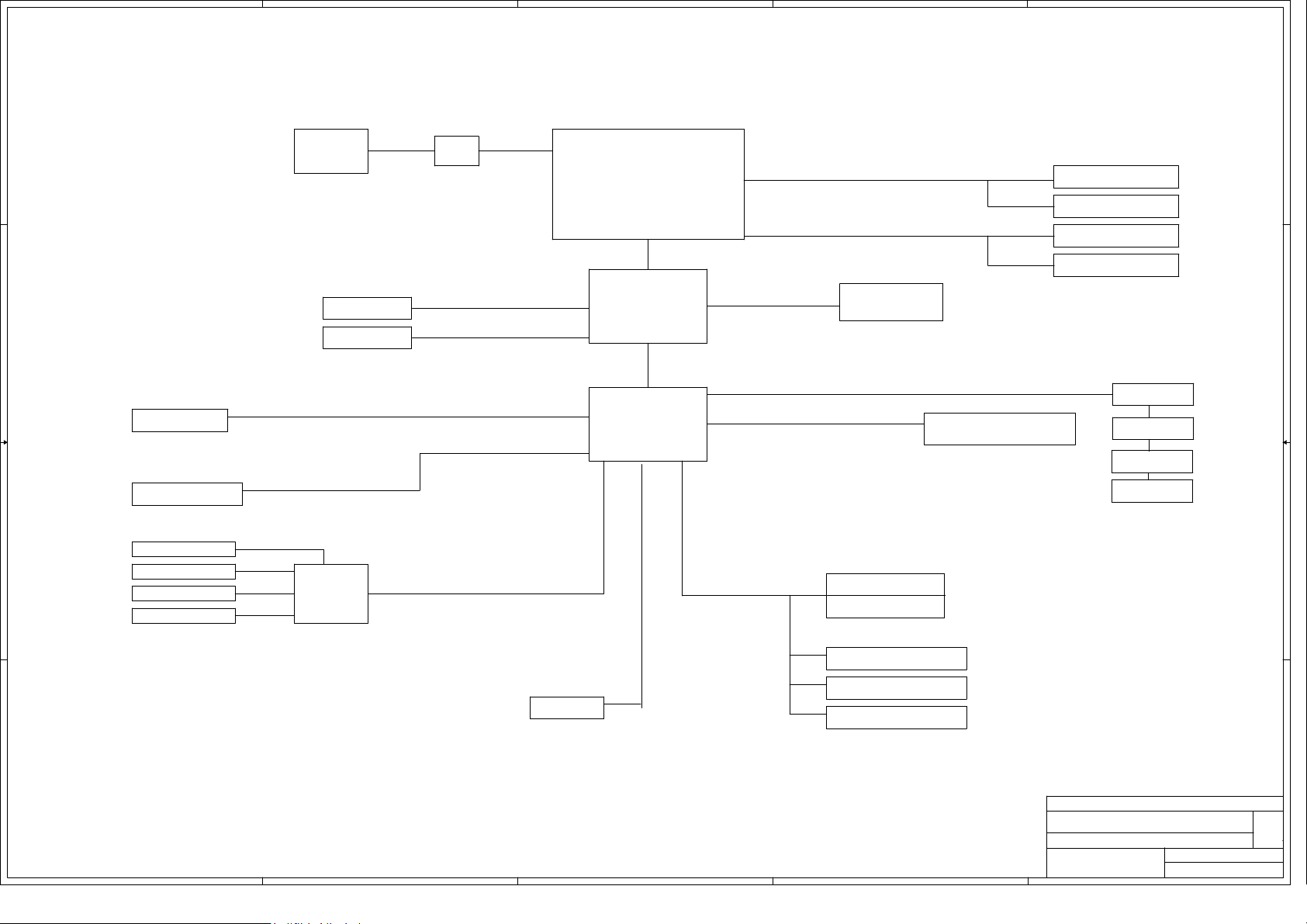

BLOCK DIAGRAM

D D

POWER

SUPPLY

CONNECTOR

VREG

SOCKET 940

K9

DDR2 SDRAM CONN 0

128-BIT 400/533MHZ

HT 16X16 1GHZ

PEX X16

C C

ATA 133

PRIMARY IDE

PEX X1

PCI EXPRESS

PCI EXPRESS

ATI

RS690

465 BGA

ATI

SB600

HT 8X8 1GHZ

AZAILIA/AC97

VGA CONN

PCI 33MHZ

Realtek ALC 888(HD, 7.1Channel)

DDR2 SDRAM CONN 2

DDR2 SDRAM CONN 1

DDR2 SDRAM CONN3

LAN-RTL8100C

IEEE1394-VT6308

564 BGA

PCI SLOT 1

X4 - SATA CONN

B B

FLOPPY CONN

PS2/KBRD CONN

PARALLEL CONN

COM1-2 CONN

INTEGRATED SATA 1/2

SIO

LPC SUPER I/O

W83627DHG

LPC BUS 33MHZ

X8 USB2.0 (SB460)

X10 USB2.0 (SB600)

BACK PANEL CONN

USB2 PORTS 0-1

DOUBLE STACK

USB2 PORTS 2-3

X2/GBIT LAN

FRONT PANEL HDR

USB2 PORTS 4-5

PCI SLOT 2

USB2 PORTS 6-7

SPI

A A

5

4

3

USB2 PORTS 8-9

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

2

Block Diagram

MS-7405

MS-7405

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7405

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

1

239

239

239

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

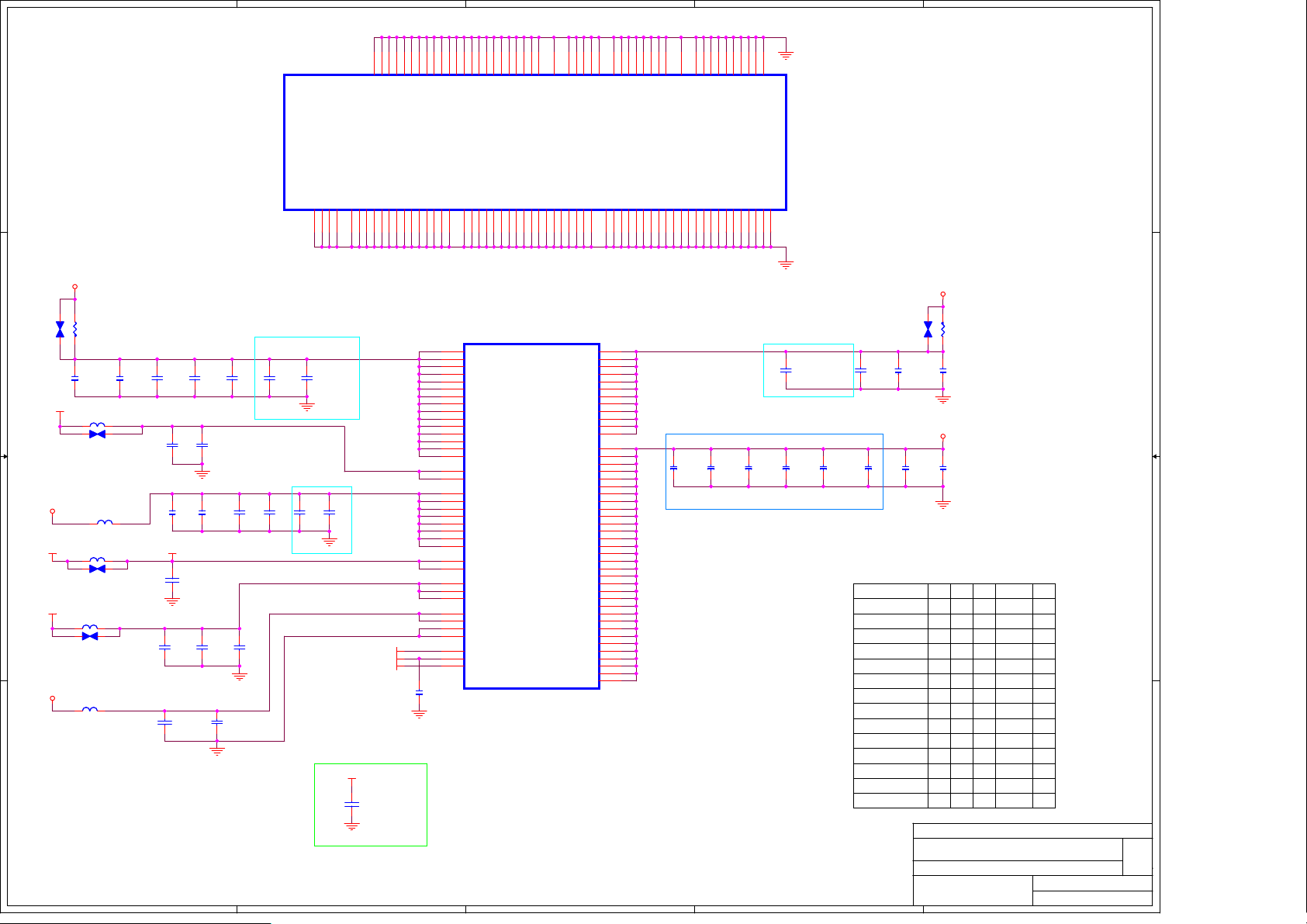

C166

C166

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

475P/1206

475P/1206

CPU1A

CPU1A

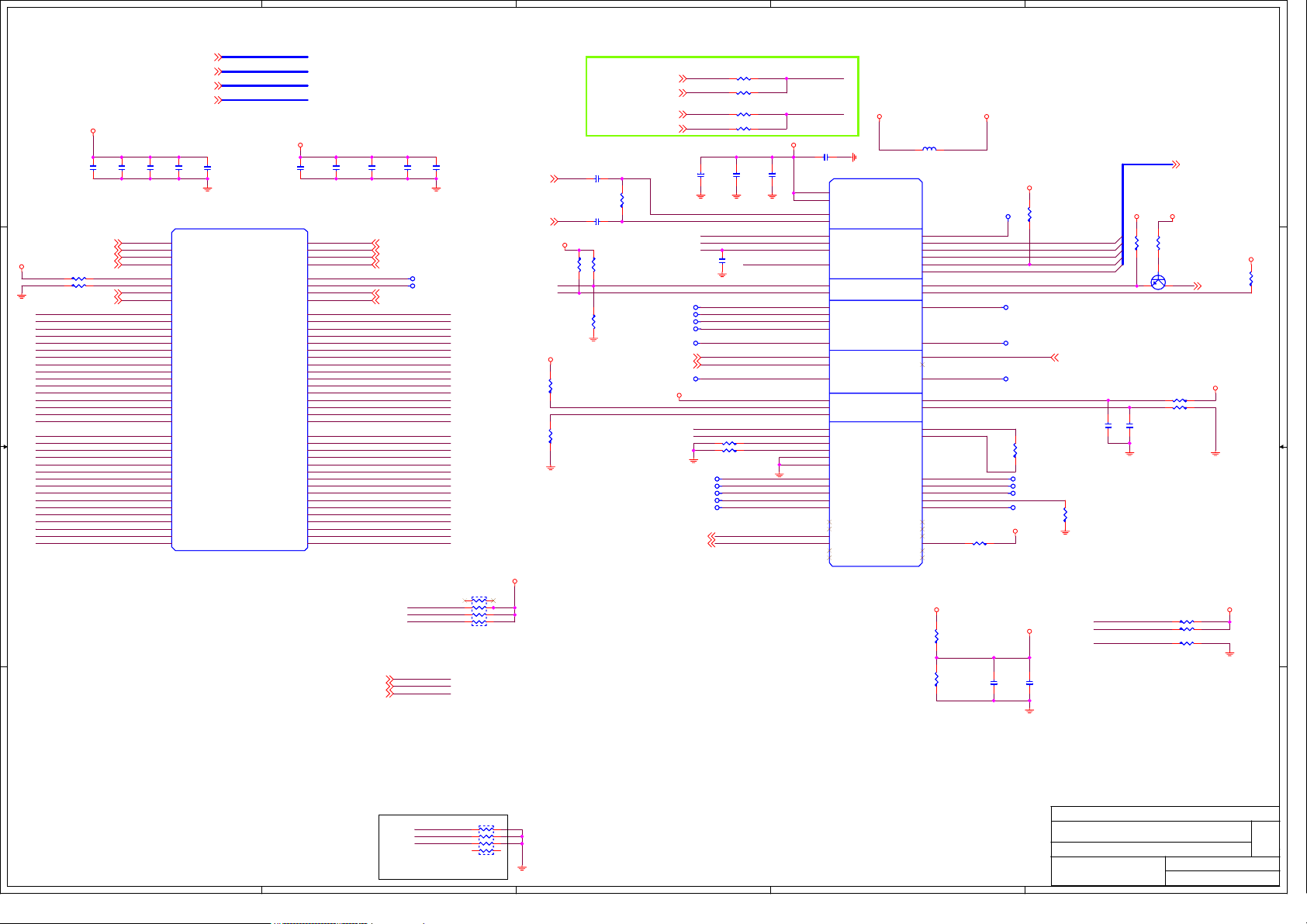

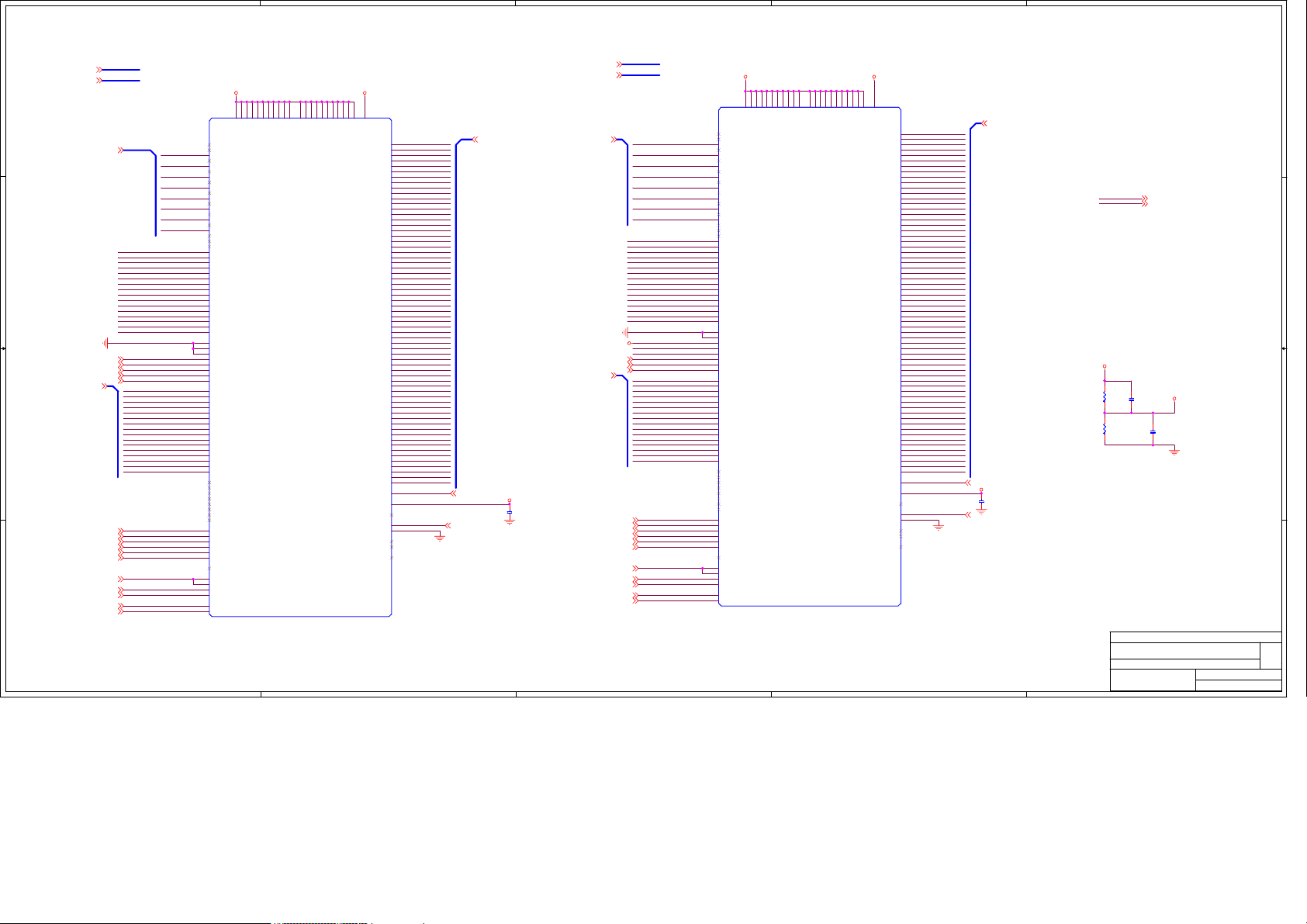

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

VCCA_1V2 VDDA25

C167

C167

C191

C191

X_475P/1206

X_475P/1206

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

475P/1206

475P/1206

HT_CADIN_H[15..0]9

HT_CADIN_L[15..0]9

HT_CADOUT_H[15..0]9

HT_CADOUT_L[15..0]9

D D

VCCA_1V2

C C

B B

VCCA_1V2

C186

C186

224P/16v/6

224P/16v/6

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

HT_CLKIN_L09

R116 49.9/4R116 49.9/4

R117 49.9/4R117 49.9/4

HT_CTLIN_H09

HT_CTLIN_L09

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

C175

C175

224P/16v/6

224P/16v/6

X_224P/16v/6

X_224P/16v/6

C179

C179

C199

C199

X_224P/16v/6

X_224P/16v/6

N6

L0_CLKIN_H(1)

P6

L0_CLKIN_L(1)

N3

L0_CLKIN_H(0)

N2

L0_CLKIN_L(0)

V4

L0_CTLIN_H(1)

V5

L0_CTLIN_L(1)

U1

L0_CTLIN_H(0)

V1

L0_CTLIN_L(0)

U6

L0_CADIN_H(15)

V6

L0_CADIN_L(15)

T4

L0_CADIN_H(14)

T5

L0_CADIN_L(14)

R6

L0_CADIN_H(13)

T6

L0_CADIN_L(13)

P4

L0_CADIN_H(12)

P5

L0_CADIN_L(12)

M4

L0_CADIN_H(11)

M5

L0_CADIN_L(11)

L6

L0_CADIN_H(10)

M6

L0_CADIN_L(10)

K4

L0_CADIN_H(9)

K5

L0_CADIN_L(9)

J6

L0_CADIN_H(8)

K6

L0_CADIN_L(8)

U3

L0_CADIN_H(7)

U2

L0_CADIN_L(7)

R1

L0_CADIN_H(6)

T1

L0_CADIN_L(6)

R3

L0_CADIN_H(5)

R2

L0_CADIN_L(5)

N1

L0_CADIN_H(4)

P1

L0_CADIN_L(4)

L1

L0_CADIN_H(3)

M1

L0_CADIN_L(3)

L3

L0_CADIN_H(2)

L2

L0_CADIN_L(2)

J1

L0_CADIN_H(1)

K1

L0_CADIN_L(1)

J3

L0_CADIN_H(0)

J2

L0_CADIN_L(0)

For S3 issue(LDT RST can not still low)

LDT_PWRGD14

224P/16v/6

224P/16v/6

C180

C180

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3HT_CADIN_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

LDT_STOP#11,14

LDT_RST#14

4

C201

C201

X_224P/16v/6

X_224P/16v/6

LDT_STOP#

LDT_PWRGD

LDT_RST#

C196

C196

TP15TP15

TP14TP14

LDT_RST#

LDT_PWRGD

LDT_STOP#

X_224P/16v/6

X_224P/16v/6

1

3

5

7

+1.8V_S0

RN56

RN56

2

4

6

8

X_8P4R-330R

X_8P4R-330R

3

for DHG Remove R512, R514, add R513, R515

for SB600 or EHG Remove R515, R513, add R514, R512

THERM_SIC

THERM_SID

near cpu

C673

C58

C58

C673

C22U6.3X1206/B

C22U6.3X1206/B

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

SIC

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

C50

C50

224P/16v/6

224P/16v/6

C45

C45

X_C1000P50X

X_C1000P50X

TP24TP24

TP27TP27

TP16TP16

TP22TP22

TP6TP6

TP1TP1

R43 300/4R43 300/4

R42 300/4R42 300/4

TP10TP10

TP11TP11

TP13TP13

TP8TP8

TP18TP18

R512 X_0/4R512 X_0/4

R513 X_0/4R513 X_0/4

R514 X_0/4R514 X_0/4

R515 X_0/4R515 X_0/4

C64

C64

3300P/50V/4

3300P/50V/4

LDT_PWRGD

LDT_STOP#

LDT_RST#

CPU_PRESENT_L

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

COREFB+

COREFBCPU_VTT_SENSE

CPU_TEST25_H

CPU_TEST25_L

CPU_SIC14

SIO_THERM_SIC21

CPU_SID14

SIO_THERM_SID21

C56

VCC_DDR

R109

R109

300/4

300/4

R112

R112

39.2R1%

39.2R1%

R113

R113

39.2R1%

39.2R1%

C56

C3900P25X

C3900P25X

C3900P25X

C3900P25X

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

C55

C55

R104

R104

300/4

300/4

THERM_SIC

THERM_SID

R280

R280

X_300/4

X_300/4

169R1%

169R1%

475P/1206

475P/1206

R73

R73

CPUCLKIN

CPUCLKIN#

COREFB+26

COREFB-26

CPU_M_VREF

THERMDC_CPU21

THERMDA_CPU21

CPU_CLK13

CPU_CLK#13

VCC_DDR

CPU1D

CPU1D

MISC

MISC

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

TDO

PSI_L

TEST8

80S/0805L480S/0805

2 1

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

VCC_DDR

R57

R57

15/6/1

15/6/1

VDDA25VDDA_25

L4

VID4

VID3

VID2

VID1

VID0

CPU_THRIP_L#

CPU_TDO

CPU_DBRDY

CPU_VDDIOFB_H

CPU_PSI_L

R108 300/4R108 300/4

R54

R54

15/6/1

15/6/1

0.1u/25V/4

0.1u/25V/4

1

VID[0..4] 26

VCC_DDR

TP9TP9

R18

R18

300/4

300/4

TP26TP26

TP7TP7

CPU_VDDIOFB_H 28

TP12TP12

C160

C160

102P/50V/X7R/4

102P/50V/X7R/4

R52

R52

80.6R1%

80.6R1%

TP21TP21

TP17TP17

TP20TP20

TP19TP19

VCC_DDR

CPU_M_VREF

C59

C65

C65

C59

C1000P16X

C1000P16X

R106

R106

300/4

300/4

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

VCC_DDRVCC_DDR

R511

R511

R510

R510

300/4

300/4

4.7K/4

4.7K/4

Q45 N-MMBT3904_NL_SOT23Q45 N-MMBT3904_NL_SOT23

R111 44.2RSTR111 44.2RST

R114 44.2RSTR114 44.2RST

C161

C161

102P/50V/X7R/4

102P/50V/X7R/4

R118 1K/4R118 1K/4

R67 510RR67 510R

R72 510RR72 510R

VCC_DDR

CPU_THRIP# 27

VCCA_1V2

VCC_DDR

R105

R105

300/4

300/4

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

RN58

LDT_STOP#

LDT_PWRGD

LDT_RST#

For SB600

5

4

RN58

1

3

5

7

8P4R-680R

8P4R-680R

2

4

6

8

3

2

Micro Star Restricted Secret

Title

Title

Title

ATHLON64 HT I/F CTRL & DEBUG

ATHLON64 HT I/F CTRL & DEBUG

ATHLON64 HT I/F CTRL & DEBUG

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7405

MS-7405

MS-7405

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

339

339

339

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

4

3

2

1

MEM_MA_DQS_L[7..0]6,7

MEM_MA_DQS_H[7..0]6,7

MEM_MA_DM[7..0]6,7

D D

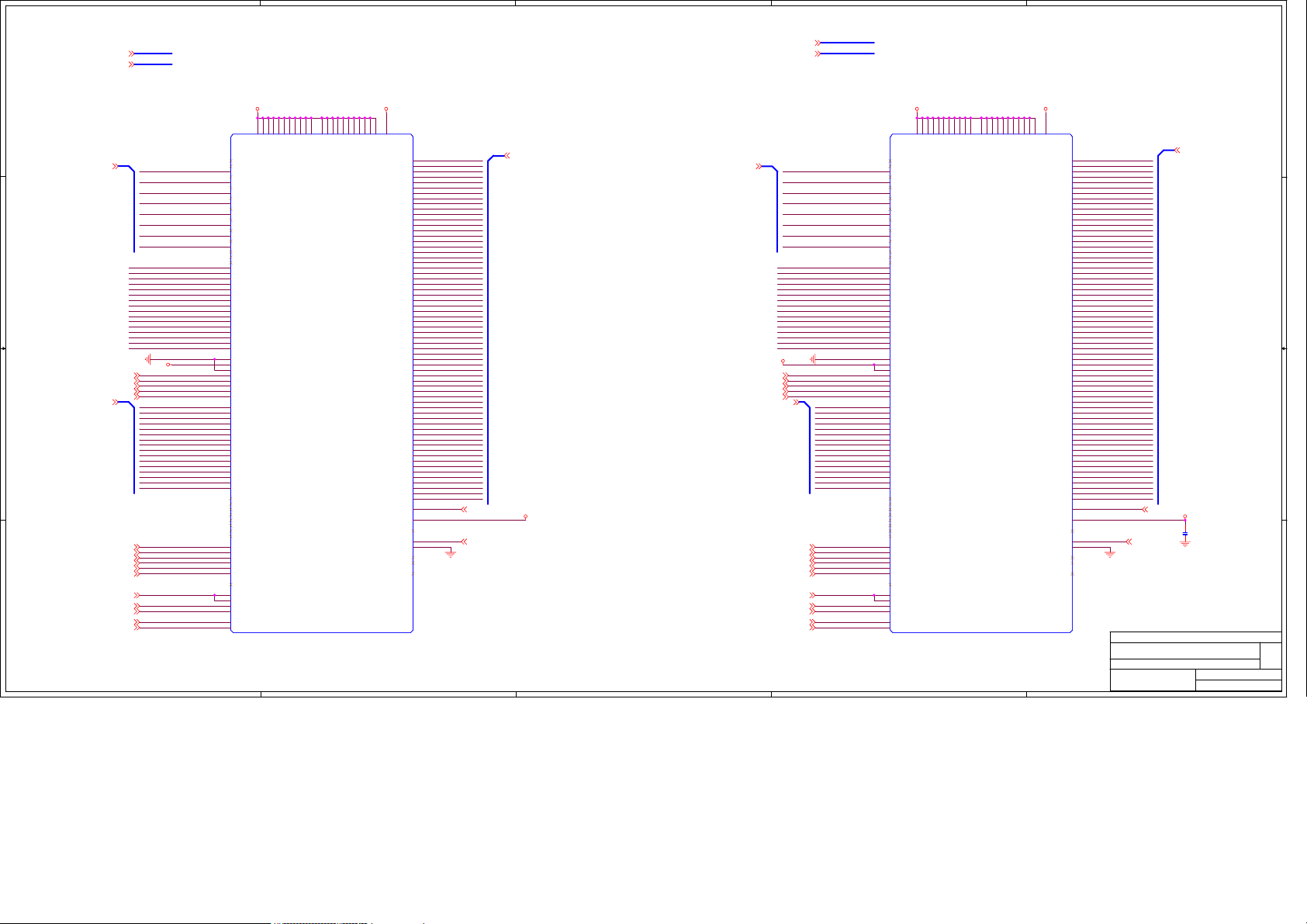

CPU1B

CPU1B

MEMORY INTERFACE A

MEM_MA0_CLK_H26,8

MEM_MA0_CLK_L26,8

MEM_MA0_CLK_H16,8

MEM_MA0_CLK_L16,8

MEM_MA0_CLK_H06,8

MEM_MA0_CLK_L06,8

MEM_MA0_CS_L16,8

MEM_MA0_CS_L06,8

MEM_MA0_ODT06,8

MEM_MA1_CLK_H27,8

MEM_MA1_CLK_L27,8

MEM_MA1_CLK_H17,8

MEM_MA1_CLK_L17,8

MEM_MA1_CLK_H07,8

MEM_MA1_CLK_L07,8

MEM_MA1_CS_L17,8

MEM_MA1_CS_L07,8

MEM_MA1_ODT07,8

C C

MEM_MA_ADD[15..0]6,7,8

B B

MEM_MA_CAS_L6,7,8

MEM_MA_WE_L6,7,8

MEM_MA_RAS_L6,7,8

MEM_MA_BANK26,7,8

MEM_MA_BANK16,7,8

MEM_MA_BANK06,7,8

MEM_MA_CKE17,8

MEM_MA_CKE06,8

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

MEM_MA1_CLK_H2

MEM_MA1_CLK_L2

MEM_MA1_CLK_H1

MEM_MA1_CLK_L1

MEM_MA1_CLK_H0

MEM_MA1_CLK_L0

MEM_MA1_CS_L1

MEM_MA1_CS_L0

MEM_MA1_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

F19

F15

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

MEMORY INTERFACE A

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA_DATA63

AE14

MEM_MA_DATA62

AG14

MEM_MA_DATA61

AG16

MEM_MA_DATA60

AD17

MEM_MA_DATA59

AD13

MEM_MA_DATA58

AE13

MEM_MA_DATA57

AG15

MEM_MA_DATA56

AE16

MEM_MA_DATA55

AG17

MEM_MA_DATA54

AE18

MEM_MA_DATA53

AD21

MEM_MA_DATA52

AG22

MEM_MA_DATA51

AE17

MEM_MA_DATA50

AF17

MEM_MA_DATA49

AF21

MEM_MA_DATA48

AE21

MEM_MA_DATA47

AF23

MEM_MA_DATA46

AE23

MEM_MA_DATA45

AJ26

MEM_MA_DATA44

AG26

MEM_MA_DATA43

AE22

MEM_MA_DATA42

AG23

MEM_MA_DATA41

AH25

MEM_MA_DATA40

AF25

MEM_MA_DATA39

AJ28

MEM_MA_DATA38

AJ29

MEM_MA_DATA37

AF29

MEM_MA_DATA36

AE26

MEM_MA_DATA35

AJ27

MEM_MA_DATA34

AH27

MEM_MA_DATA33

AG29

MEM_MA_DATA32

AF27

MEM_MA_DATA31

E29

MEM_MA_DATA30

E28

MEM_MA_DATA29

D27

MEM_MA_DATA28

C27

MEM_MA_DATA27

G26

MEM_MA_DATA26

F27

MEM_MA_DATA25

C28

MEM_MA_DATA24

E27

MEM_MA_DATA23

F25

MEM_MA_DATA22

E25

MEM_MA_DATA21

E23

MEM_MA_DATA20

D23

MEM_MA_DATA19

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

MEM_MA_DATA9

G18

MEM_MA_DATA8

E17

MEM_MA_DATA7

G16

MEM_MA_DATA6

E15

MEM_MA_DATA5

G13

MEM_MA_DATA4

H13

MEM_MA_DATA3

H17

MEM_MA_DATA2

E16

MEM_MA_DATA1

E14

MEM_MA_DATA0

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA[63..0] 6,7

MEM_MB_ADD[15..0]6,7,8

MEM_MB_DQS_L[7..0]6,7

MEM_MB_DQS_H[7..0]6,7

MEM_MB_DM[7..0]6,7

CPU1C

CPU1C

MEMORY INTERFACE B

MEM_MB0_CLK_H26,8

MEM_MB0_CLK_L26,8

MEM_MB0_CLK_H16,8

MEM_MB0_CLK_L16,8

MEM_MB0_CLK_H06,8

MEM_MB0_CLK_L06,8

MEM_MB0_CS_L16,8

MEM_MB0_CS_L06,8

MEM_MB0_ODT06,8

MEM_MB1_CLK_H27,8

MEM_MB1_CLK_L27,8

MEM_MB1_CLK_H17,8

MEM_MB1_CLK_L17,8

MEM_MB1_CLK_H07,8

MEM_MB1_CLK_L07,8

MEM_MB1_CS_L17,8

MEM_MB1_CS_L07,8

MEM_MB1_ODT07,8

MEM_MB_CAS_L6,7,8

MEM_MB_WE_L6,7,8

MEM_MB_RAS_L6,7,8

MEM_MB_BANK26,7,8

MEM_MB_BANK16,7,8

MEM_MB_BANK06,7,8

MEM_MB_CKE17,8

MEM_MB_CKE06,8

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB1_CLK_H2

MEM_MB1_CLK_L2

MEM_MB1_CLK_H1

MEM_MB1_CLK_L1

MEM_MB1_CLK_H0

MEM_MB1_CLK_L0

MEM_MB1_CS_L1

MEM_MB1_CS_L0

MEM_MB1_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AJ19

AK19

AE30

AC31

AD29

AL19

AL18

W29

W28

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

M31

M29

AE31

AA29

AA30

AK13

AJ13

AK17

AJ17

AK23

AL23

AL28

AL29

AJ14

AH17

AJ23

AK29

A18

A19

U31

U30

C19

D19

N31

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

D31

C31

C24

C23

D17

C17

C14

C13

C30

A23

B17

B13

MEMORY INTERFACE B

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DATA[63..0] 6,7

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

ATHLON64 DDR MEMORY I/F

ATHLON64 DDR MEMORY I/F

ATHLON64 DDR MEMORY I/F

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7405

MS-7405

MS-7405

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

439

439

439

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

VCCP

CPU1F

CPU1F

VDD1

VDD1

A4

VDD1

A6

VDD2

AA8

VDD3

AA10

VDD4

AA12

VDD5

AA14

VDD6

AA16

VDD7

AA18

VDD8

AB7

VDD9

D D

C C

B B

AB11

AC10

AE10

AB9

AC4

AC5

AC8

AD2

AD3

AD7

AD9

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

F11

G10

G12

H11

H23

K11

K13

K15

K17

K19

K21

K23

Y17

Y19

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

J12

VDD55

J14

VDD56

J16

VDD57

J18

VDD58

J20

VDD59

J22

VDD60

J24

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

L10

VDD74

L12

VDD75

VDD150

VDD151

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

VCCP

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

N8

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

P7

VDD19

P9

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

V9

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

VDD72

VDD73

VDD74

VDD75

CPU1G

CPU1G

VDD2

VDD2

4

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

AK20

AK22

AK24

AK26

AK28

AK30

AL5

B4

B9

B11

B14

B16

B18

B20

B22

B24

B26

B28

B30

C3

D14

D16

D18

D20

D22

D24

D26

D28

D30

E11

F4

F14

F16

F18

F20

F22

F24

F26

F28

F30

G9

G11

H8

H10

H12

H14

H16

H18

H22

H24

H26

H28

H30

J4

J5

J7

J9

J11

J13

J15

J17

J19

J21

J23

K2

K3

K8

K10

K12

K14

K16

K18

K20

K22

Y18

VCCP

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

W22

3

VCC_DDR

VCCA_1V2

VTT_DDR

VCCP

C645

C645

X_224P/16v/6

X_224P/16v/6

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

C648

C648

X_224P/16v/6

X_224P/16v/6

CPU1H

CPU1H

VDD3

VDD3

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

L20

VDD19

L22

VDD20

VDD21

VDD22

N20

VDD23

N22

VDD24

P21

VDD25

P23

VDD26

R22

VDD27

T23

VDD28

U22

VDD29

V23

VDD30

VDD31

Y23

VDD32

5

GND

6

GND

7

GND

8

GND

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VCCP

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT1

VTT2

VTT3

VTT4

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO6

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

C647

C647

CPU1I

CPU1I

VDDIO

VDDIO

224P/16v/6

224P/16v/6

VLDT_B1

VLDT_B2

VLDT_B3

VLDT_B4

VTT5

VTT6

VTT7

VTT8

VTT9

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

For EMI

C649

C649

0.01u/50V/6/X7R

0.01u/50V/6/X7R

H6

H5

H2

H1

AK12

AJ12

AH12

AG12

AL12

K24

K26

K28

K30

L7

L9

L11

L13

L15

L17

L19

L21

L23

M8

M10

M12

M14

M16

M18

M20

M22

N4

N5

N7

N9

N11

N13

N15

2

VCC_DDR

VLDT_RUN_B

VTT_DDR

C678

C678

X_0.1u/25V/4

X_0.1u/25V/4

C670

C670

X_180P

X_180P

4.7u/10V/8

4.7u/10V/8

C73

C73

C84

C84

X_C10000P50Y5

X_C10000P50Y5

C215

C215

180P

180P

C681

C681

X_0.1u/25V/4

X_0.1u/25V/4

C77

C77

C75

C75

X_C10000P50Y5

X_C10000P50Y5

X_C10000P50Y5

X_C10000P50Y5

For AMD requirement

VCCA_1V2

C208

C208

C205

C205

180P

180P

180P

180P

Close to CPU

C682

C682

X_0.1u/25V/4

X_0.1u/25V/4

C210

C210

180P

180P

C683

C683

X_0.1u/25V/4

X_0.1u/25V/4

C212

C212

180P

180P

1

C684

C684

X_0.1u/25V/4

X_0.1u/25V/4

C633

C633

C640

C640

X_C22U6.3X1206/B

X_C22U6.3X1206/B

X_C22U6.3X1206/B

X_C22U6.3X1206/B

VTT_DDR

C157

C157

C274

C274

224P/16v/6

224P/16v/6

224P/16v/6

224P/16v/6

A A

VTT_DDR

C238

C238

C34

C34

224P/16v/6

224P/16v/6

224P/16v/6

224P/16v/6

C207

C207

C4.7U10Y0805

C4.7U10Y0805

C213

C213

C4.7U10Y0805

C4.7U10Y0805

5

C202

C202

X_C4.7U10Y0805

X_C4.7U10Y0805

C291

C291

X_C4.7U10Y0805

X_C4.7U10Y0805

C194

C194

X_180P

X_180P

C187

C187

X_180P

X_180P

C184

C184

X_180P

X_180P

C226

C226

180P

180P

C62

C62

C1000P50X

C1000P50X

C237

C237

C1000P50X

C1000P50X

C229

C229

C1000P50X

C1000P50X

C51

C51

C1000P50X

C1000P50X

C634

C634

X_224P/16v/6

X_224P/16v/6

VCC_DDR VCC3

C671 103P/16V/4C671 103P/16V/4

4

C638

C638

224P/16v/6

224P/16v/6

3

C204

C204

224P/16v/6

224P/16v/6

C635

C635

C10U6.3X51206/B

C10U6.3X51206/B

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C263

C263

C189

C189

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C4.7U10Y0805

C642

C642

C627

C627

C10U6.3X51206/B

C10U6.3X51206/B

C10U6.3X51206/B

C10U6.3X51206/B

+

+

EC22

EC22

1000u/6.3V/8*11.5

1000u/6.3V/8*11.5

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C636

C636

VCC_DDRVCC_DDR

C646

C646

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C133

C133

C641

C641

X_C22U6.3X1206

X_C22U6.3X1206

C632

C632

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C22

C22

C4.7U10Y0805

C4.7U10Y0805

2

C628

C628

C10U6.3X51206/B

C10U6.3X51206/B

C195

C195

C4.7U10Y0805

C4.7U10Y0805

C639

C639

X_C22U6.3X1206/B

X_C22U6.3X1206/B

C631

C631

224P/16v/6

224P/16v/6

C70

C70

X_C22U6.3X1206

X_C22U6.3X1206

C220

C220

C197

C197

224P/16v/6

224P/16v/6

0.01u/50V/6/X7R

0.01u/50V/6/X7R

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

C643

C644

C644

C643

C10U6.3X51206/B

C10U6.3X51206/B

C669

C669

180P

180P

MS-7405

MS-7405

MS-7405

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

C630

C630

C10U6.3X51206/B

C10U6.3X51206/B

C22U6.3X1206/B

C22U6.3X1206/B

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

ATHLON64 PWR & GND

ATHLON64 PWR & GND

ATHLON64 PWR & GND

C95

C95

C629

C629

X_C22U6.3X1206

X_C22U6.3X1206

C10U6.3X51206/B

C10U6.3X51206/B

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

of

of

of

539

539

539

Rev

Rev

Rev

0A

0A

0A

5

4

3

2

1

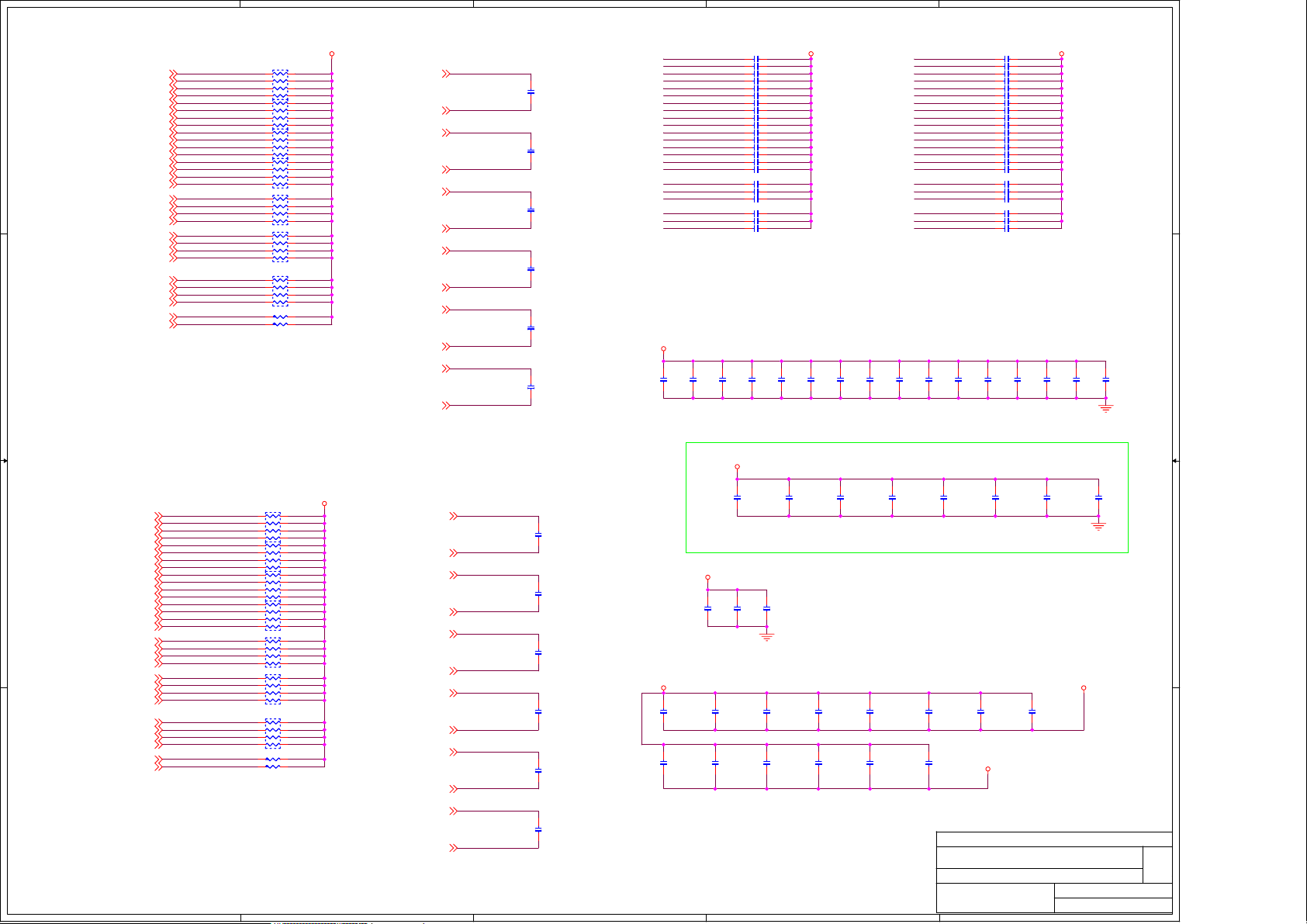

MEM_MA_DQS_H[7..0]4,7

MEM_MA_DQS_L[7..0]4,7

D D

MEM_MA_DM[7..0]4,7

C C

SCL7,13,15

SDA7,13,15

MEM_MA_BANK24,7,8

MEM_MA_BANK14,7,8

MEM_MA_BANK04,7,8

MEM_MA_ADD[15..0]4,7,8

B B

MEM_MA0_CLK_H04,8

MEM_MA0_CLK_L04,8

MEM_MA0_CLK_H14,8

MEM_MA0_CLK_L14,8

MEM_MA0_CLK_H24,8

MEM_MA0_CLK_L24,8

MEM_MA_CKE04,8

MEM_MA_RAS_L4,7,8

MEM_MA_CAS_L4,7,8

A A

MEM_MA0_CS_L04,8

MEM_MA0_CS_L14,8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA_CKE0

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

5

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

SCL

SDA

VCC_DDR

69

170

VDD5

197

VDD6

64

VDD753VDD859VDD9

175

VDD1067VDD11

VDDQ1

VDDQ2

172

178

184

187

189

VDD1

VDD2

VDD3

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

VDD4

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

181

VDDQ3

191

194

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

VCC3

78

238

72

DIMM1DIMM1

VDDQ1075VDDQ11

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

ODT0

ODT1

ERR_OUT_L

PAR_IN

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0

3

DQ0

MEM_MA_WE_L

73

VDDR_VREF

1

102

TEST

MEM_MA0_ODT0

195

77

55

68

19

NC1

4

MEM_MA_DATA[63..0] 4,7

MEM_MA_WE_L 4,7,8

X_0.1u/25V/4

X_0.1u/25V/4

MEM_MA0_ODT0 4,8

VDDR_VREF

C618

C618

MEM_MB_DQS_H[7..0]4,7

MEM_MB_DQS_L[7..0]4,7

MEM_MB_DM[7..0]4,7

MEM_MB_BANK24,7,8

MEM_MB_BANK14,7,8

MEM_MB_BANK04,7,8

MEM_MB_ADD[15..0]4,7,8

MEM_MB0_CLK_H04,8

MEM_MB0_CLK_L04,8

MEM_MB0_CLK_H14,8

MEM_MB0_CLK_L14,8

MEM_MB0_CLK_H24,8

MEM_MB0_CLK_L24,8

MEM_MB_CKE04,8

MEM_MB_RAS_L4,7,8

MEM_MB_CAS_L4,7,8

MEM_MB0_CS_L04,8

MEM_MB0_CS_L14,8

VCC3

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

SCL

SDA

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB_CKE0

MEM_MB_RAS_L

MEM_MB_CAS_L

MEM_MB0_CS_L0

MEM_MB0_CS_L1

3

VCC_DDR

69

170

VDD5

197

VDD6

64

VDD753VDD859VDD9

175

VDD1067VDD11

VDDQ1

VDDQ2

172

178

184

187

189

VDD1

VDD2

VDD3

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

VDD4

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

181

VDDQ3

191

VDDQ4

194

VDDQ5

72

VDDQ651VDDQ756VDDQ862VDDQ9

VCC3

78

VDDQ1075VDDQ11

238

VDDSPD

WE_L

VREF

ODT0

ODT1

ERR_OUT_L

PAR_IN

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

TEST

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

DIMM2DIMM2

236

235

230

229

117

116

111

110

227

226

218

217

108

107

99

98

215

214

209

208

96

95

90

89

206

205

200

199

87

86

81

80

159

158

153

152

40

39

34

33

150

149

144

143

31

30

25

24

141

140

132

131

22

21

13

12

129

128

123

122

10

9

4

3

73

1

102

195

77

55

68

19

2

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_WE_L

VDDR_VREF

MEM_MB0_ODT0

MEM_MB_DATA[63..0] 4,7

MEM_MB_WE_L 4,7,8

VDDR_VREF

C619

C619

C1000P10X0402

C1000P10X0402

MEM_MB0_ODT0 4,8

SCL

SDA

VCC_DDR

C19

C19

R24

R24

49.9

49.9

0.1u/25V/4

0.1u/25V/4

R22

R22

49.9

49.9

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

SCL 7,13,15

SDA 7,13,15

VDDR_VREF

VDDR_VREF

C621

C621

0.1u/25V/4

0.1u/25V/4

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

MS-7405

MS-7405

MS-7405

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

639

639

639

Rev

Rev

Rev

0A

0A

0A

of

of

of

5

4

3

2

1

MEM_MA_DQS_H[7..0]4,6

MEM_MA_DQS_L[7..0]4,6

D D

MEM_MA_DM[7..0]4,6

C C

SCL6,13,15

SDA6,13,15

MEM_MA_BANK24,6,8

MEM_MA_BANK14,6,8

MEM_MA_BANK04,6,8

MEM_MA_ADD[15..0]4,6,8

B B

MEM_MA1_CLK_H04,8

MEM_MA1_CLK_L04,8

MEM_MA1_CLK_H14,8

MEM_MA1_CLK_L14,8

MEM_MA1_CLK_H24,8

MEM_MA1_CLK_L24,8

MEM_MA_CKE14,8

A A

MEM_MA_RAS_L4,6,8

MEM_MA_CAS_L4,6,8

MEM_MA1_CS_L04,8

MEM_MA1_CS_L14,8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

VCC3

SCL

SDA

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA1_CLK_H0

MEM_MA1_CLK_L0

MEM_MA1_CLK_H1

MEM_MA1_CLK_L1

MEM_MA1_CLK_H2

MEM_MA1_CLK_L2

MEM_MA_CKE1 MEM_MB_CKE1

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA1_CS_L0

MEM_MA1_CS_L1

5

VCC_DDR VCC3

69

VDD4

170

189

197

64

VDD5

VDD6

VDD753VDD859VDD9

VDD1067VDD11

172

178

184

187

VDD1

VDD2

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

VDD3

164

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

175

VDDQ1

181

VDDQ2

191

VDDQ3

194

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

78

238

72

DIMM3DIMM3

VDDQ1075VDDQ11

VDDSPD

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

ERR_OUT_L

PAR_IN

4

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

NC1

MEM_MA_DATA63

236

MEM_MA_DATA62

235

MEM_MA_DATA61

230

MEM_MA_DATA60

229

MEM_MA_DATA59

117

MEM_MA_DATA58

116

MEM_MA_DATA57

111

MEM_MA_DATA56

110

MEM_MA_DATA55

227

MEM_MA_DATA54

226

MEM_MA_DATA53

218

MEM_MA_DATA52

217

MEM_MA_DATA51

108

MEM_MA_DATA50

107

MEM_MA_DATA49

99

MEM_MA_DATA48

98

MEM_MA_DATA47

215

MEM_MA_DATA46

214

MEM_MA_DATA45

209

MEM_MA_DATA44

208

MEM_MA_DATA43

96

MEM_MA_DATA42

95

MEM_MA_DATA41

90

MEM_MA_DATA40

89

MEM_MA_DATA39

206

MEM_MA_DATA38

205

MEM_MA_DATA37

200

MEM_MA_DATA36

199

MEM_MA_DATA35

87

MEM_MA_DATA34

86

MEM_MA_DATA33

81

MEM_MA_DATA32

80

MEM_MA_DATA31

159

MEM_MA_DATA30

158

MEM_MA_DATA29

153

MEM_MA_DATA28

152

MEM_MA_DATA27

40

MEM_MA_DATA26

39

MEM_MA_DATA25

34

MEM_MA_DATA24

33

MEM_MA_DATA23

150

MEM_MA_DATA22

149

MEM_MA_DATA21

144

MEM_MA_DATA20

143

MEM_MA_DATA19

31

MEM_MA_DATA18

30

MEM_MA_DATA17

25

MEM_MA_DATA16

24

MEM_MA_DATA15

141

MEM_MA_DATA14

140

MEM_MA_DATA13

132

MEM_MA_DATA12

131

MEM_MA_DATA11

22

MEM_MA_DATA10

21

MEM_MA_DATA9

13

MEM_MA_DATA8

12

MEM_MA_DATA7

129

MEM_MA_DATA6

128

MEM_MA_DATA5

123

MEM_MA_DATA4

122

MEM_MA_DATA3

10

MEM_MA_DATA2

9

MEM_MA_DATA1

4

MEM_MA_DATA0

3

MEM_MA_WE_L

73

1

102

MEM_MA1_ODT0

195

77

55

68

19

MEM_MA_WE_L 4,6,8

MEM_MA1_ODT0 4,8

MEM_MA_DATA[63..0] 4,6

VDDR_VREF VDDR_VREF

3

MEM_MB_DM[7..0]4,6

MEM_MB_DQS_L[7..0]4,6

MEM_MB_DQS_H[7..0]4,6

VCC_DDR VCC3

181

VDDQ2

VDDQ3

191

194

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

78

238

72

DIMM4DIMM4

VDDQ1075VDDQ11

VDDSPD

ERR_OUT_L

PAR_IN

DQ63

DQ62

DQ61

DQ60

DQ59

DQ58

DQ57

DQ56

DQ55

DQ54

DQ53

DQ52

DQ51

DQ50

DQ49

DQ48

DQ47

DQ46

DQ45

DQ44

DQ43

DQ42

DQ41

DQ40

DQ39

DQ38

DQ37

DQ36

DQ35

DQ34

DQ33

DQ32

DQ31

DQ30

DQ29

DQ28

DQ27

DQ26

DQ25

DQ24

DQ23

DQ22

DQ21

DQ20

DQ19

DQ18

DQ17

DQ16

DQ15

DQ14

DQ13

DQ12

DQ11

DQ10

WE_L

VREF

TEST

ODT0

ODT1

MEM_MB_DATA63

236

MEM_MB_DATA62

235

MEM_MB_DATA61

230

MEM_MB_DATA60

229

MEM_MB_DATA59

117

MEM_MB_DATA58

116

MEM_MB_DATA57

111

MEM_MB_DATA56

110

MEM_MB_DATA55

227

MEM_MB_DATA54

226

MEM_MB_DATA53

218

MEM_MB_DATA52

217

MEM_MB_DATA51

108

MEM_MB_DATA50

107

MEM_MB_DATA49

99

MEM_MB_DATA48

98

MEM_MB_DATA47

215

MEM_MB_DATA46

214

MEM_MB_DATA45

209

MEM_MB_DATA44

208

MEM_MB_DATA43

96

MEM_MB_DATA42

95

MEM_MB_DATA41

90

MEM_MB_DATA40

89

MEM_MB_DATA39

206

MEM_MB_DATA38

205

MEM_MB_DATA37

200

MEM_MB_DATA36

199

MEM_MB_DATA35

87

MEM_MB_DATA34

86

MEM_MB_DATA33

81

MEM_MB_DATA32

80

MEM_MB_DATA31

159

MEM_MB_DATA30

158

MEM_MB_DATA29

153

MEM_MB_DATA28

152

MEM_MB_DATA27

40

MEM_MB_DATA26

39

MEM_MB_DATA25

34

MEM_MB_DATA24

33

MEM_MB_DATA23

150

MEM_MB_DATA22

149

MEM_MB_DATA21

144

MEM_MB_DATA20

143

MEM_MB_DATA19

31

MEM_MB_DATA18

30

MEM_MB_DATA17

25

MEM_MB_DATA16

24

MEM_MB_DATA15

141

MEM_MB_DATA14

140

MEM_MB_DATA13

132

MEM_MB_DATA12

131

MEM_MB_DATA11

22

MEM_MB_DATA10

21

MEM_MB_DATA9

13

DQ9

MEM_MB_DATA8

12

DQ8

MEM_MB_DATA7

129

DQ7

MEM_MB_DATA6

128

DQ6

MEM_MB_DATA5

123

DQ5

MEM_MB_DATA4

122

DQ4

MEM_MB_DATA3

10

DQ3

MEM_MB_DATA2

9

DQ2

MEM_MB_DATA1

4

DQ1

MEM_MB_DATA0

3

DQ0

MEM_MB_WE_L

73

1

102

MEM_MB1_ODT0

195

77

55

68

19

NC1

MEM_MB1_ODT0 4,8

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MEM_MB_DATA[63..0] 4,6

MEM_MB_WE_L 4,6,8

C622

C622

0.1u/25V/4

0.1u/25V/4

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

SECOND LOGICAL DDR DIMM

SECOND LOGICAL DDR DIMM

SECOND LOGICAL DDR DIMM

MS-7405

MS-7405

MS-7405

Last Revision Date:

Last Revision Date:

Last Revision Date:

Monday, May 14, 2007

Monday, May 14, 2007

Monday, May 14, 2007

Sheet

Sheet

Sheet

739

739

1

739

Rev

Rev

Rev

0A

0A

0A

of

of

of

69

170

VDD5

197

VDD6

64

VDD753VDD859VDD9

175

VDD1067VDD11

VDDQ1

172

178

184

187

189

VDD1

VDD2

VDD3

DQS17_H

DQS17_L

DQS16_H

DQS16_L

DQS15_H

DQS15_L

DQS14_H

DQS14_L

DQS13_H

DQS13_L

DQS12_H

DQS12_L

DQS11_H

DQS11_L

DQS10_H

DQS10_L

DQS9_H

DQS9_L

DQS8_H

DQS8_L

DQS7_H

DQS7_L

DQS6_H

DQS6_L

DQS5_H

DQS5_L

DQS4_H

DQS4_L

DQS3_H

DQS3_L

DQS2_H

DQS2_L

DQS1_H

DQS1_L

DQS0_H

DQS0_L

SA2

SA1

SA0

SCL

SDA

BA2

BA1

BA0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

CB7

CB6

CB5

CB4

CB3

CB2

CB1

CB0

CK0_H

CK0_L

CK1_H

CK1_L

CK2_H

CK2_L

RESET_L

CKE0

CKE1

RAS_L

CAS_L

S0_L

S1_L

2

VDD4

164

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB1_CLK_H0

MEM_MB1_CLK_L0

MEM_MB1_CLK_H1

MEM_MB1_CLK_L1

MEM_MB1_CLK_H2

MEM_MB1_CLK_L2

165

232

233

223

224

211

212

202

203

155

156

146

147

134

135

125

126

46

45

114

113

105

104

93

92

84

83

37

36

28

27

16

15

7

6

101

240

239

120

119

54

190

71

173

174

196

176

57

70

177

179

58

180

60

61

182

63

183

188

168

167

162

161

49

48

43

42

185

186

137

138

220

221

18

52

171

192

74

193

76

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4