MSI MS-7390V0A 7390V0A

5

4

3

2

1

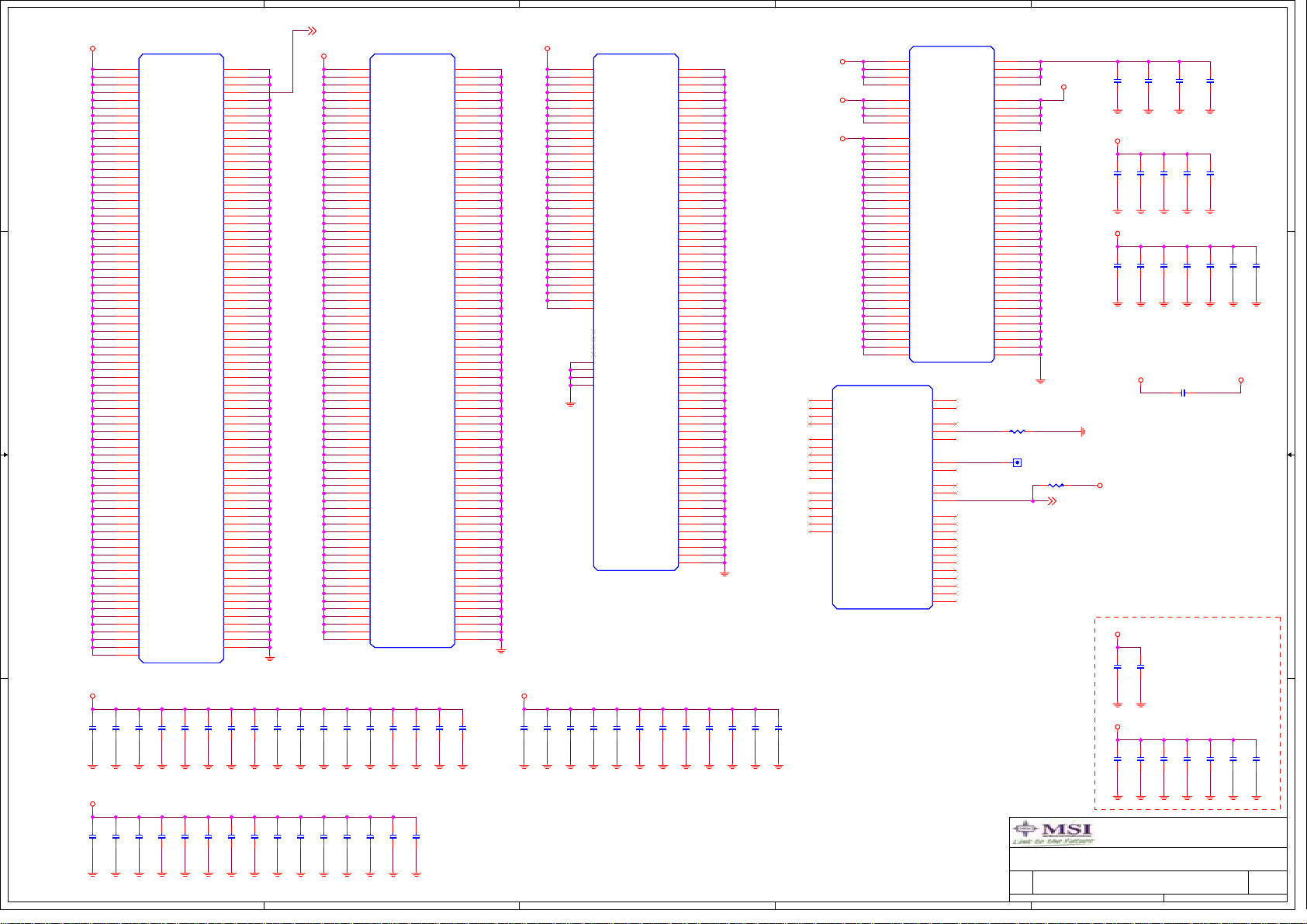

CONTENT SHEET

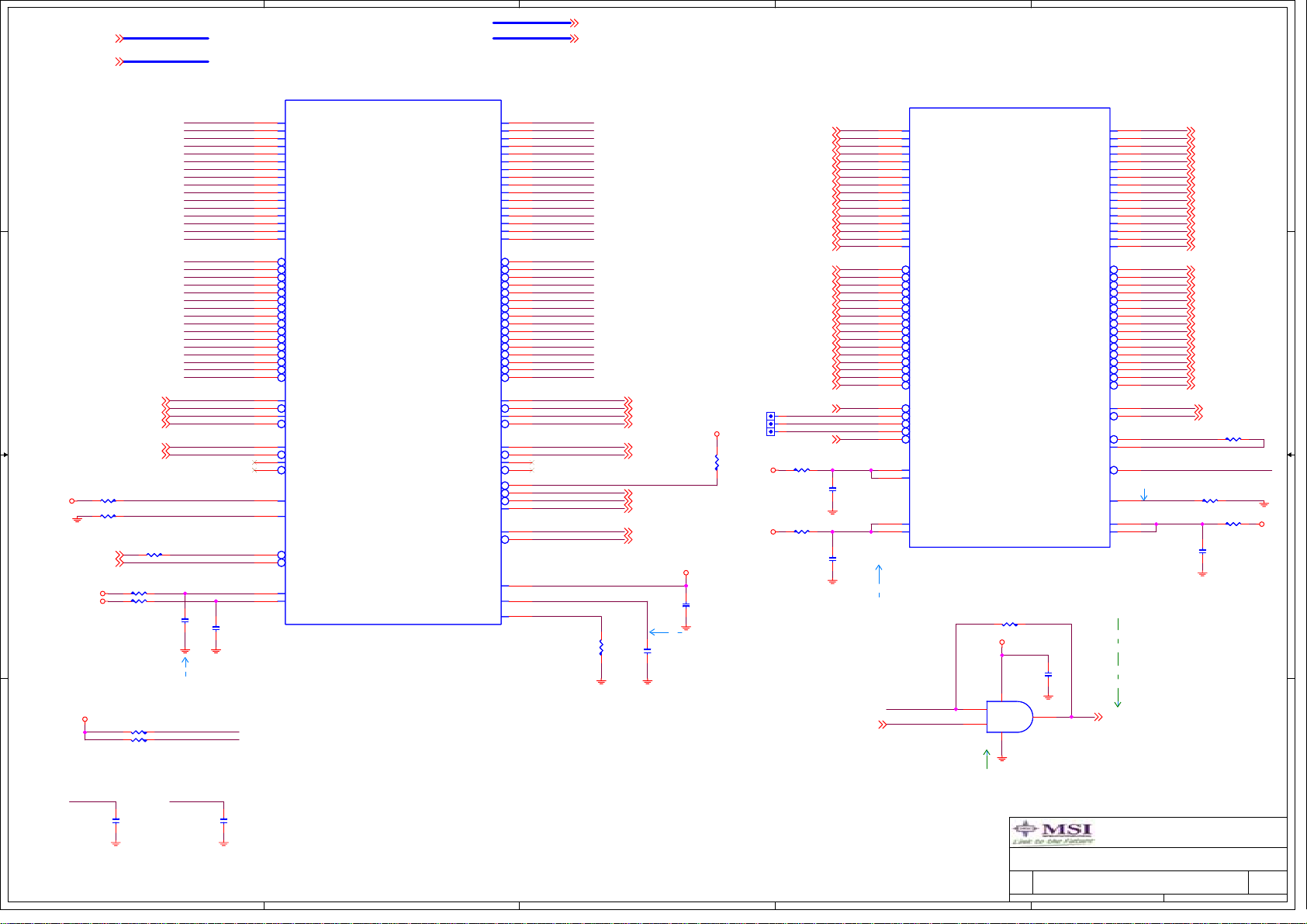

Cover Sheet, Block diagram

D D

K9 M2 CPU-Signals/Memorys/Power/GND

FIRST LOGICAL DDR DIMM

SECOND LOGIC DDR DIMM

DDR Terminatior & EMI

MCP65P HT&PEX X16

MCP65P PEX X1 & GPHY

MCP65P PCI & LPC & SATA & IDE

MCP65P HDA & USB &GPIO &MSIC

C C

MCP65P POWER & GND

Pri PCI-E Slot 8X & 1X

Sec PCI-E Slot 8X & 1X

PCI Slot 1 & 2

FINTEK 71882

Audio Codec ALC888 18

1-2

3-5

6

7

8

9

10

11

12

13

14

15

16

17

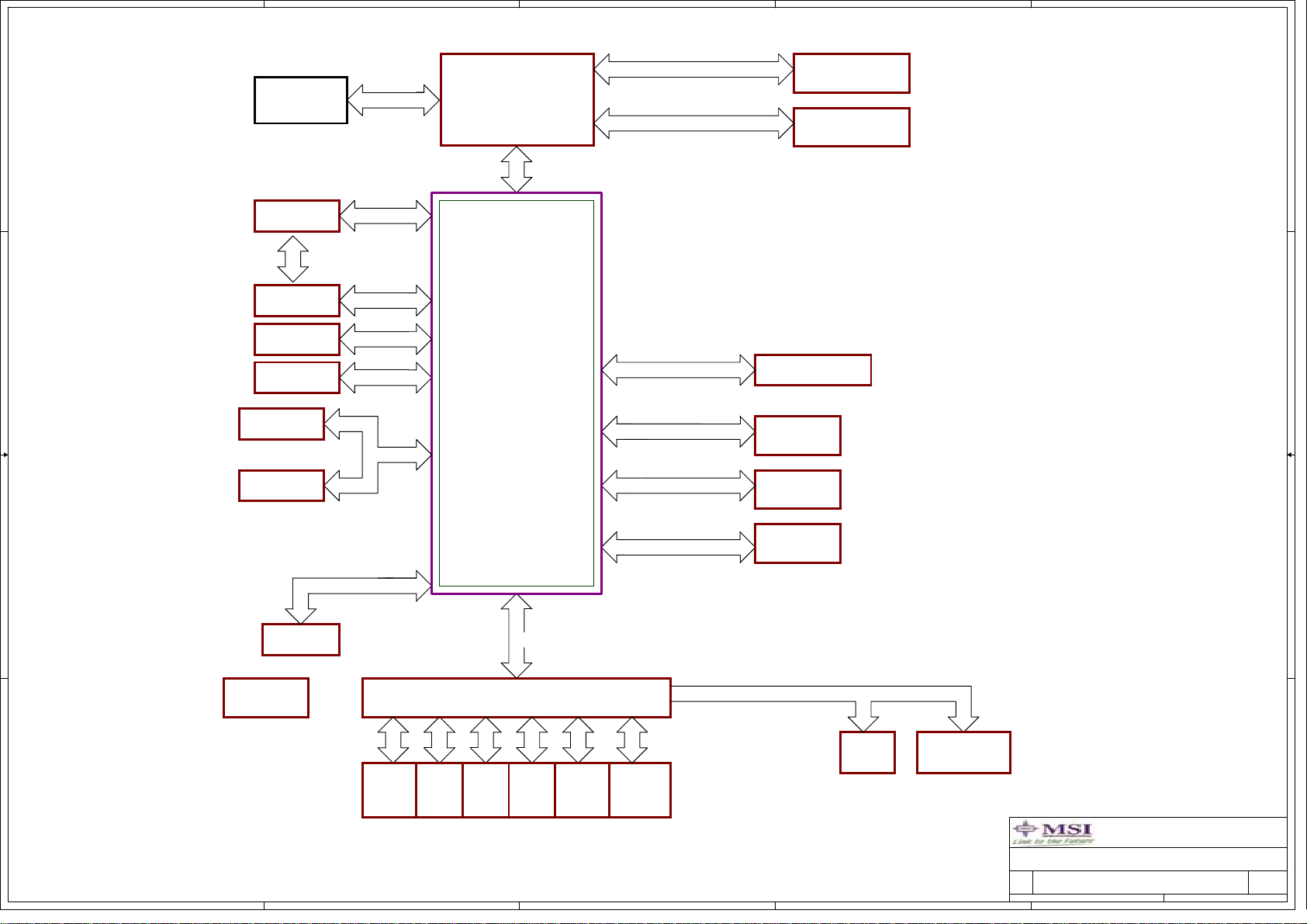

CPU:

AMD AM2& AM2+ Socket940

AM2 89W (3000+~6000+)

AM2+ up to 95W

System Chipset:

nVIDIA MCP65P(NF570LT-SLI)

On Board Device:

LPC Super I/O -- Fintek F71882F

LAN -- Realtek 8211BL (PHY)

HD Audio Codec -- ALC888

Main Memory:

Dual-channel DDR-II *4

ATX

Version: 0A

Realtek 8211BL

B B

USB

19

20

Expansion Slots:

PCI EXPRESS X16 SLOT *2(Real X8)-SLI

ACPI UPI

DDR Power & Chip Power

ATX&Front&FAN&IDE&SPI&PARALL

VRM

Menual Parts

Power Map

A A

Power Sequence

Reset Signals

Clock Distribution

GPIO Configuration

5

4

21

22

23

24

25

26

27

28

29

30

PCI EXPRESS X1 SLOT * 2

PCI SLOT * 2

PWM:

3

Intersil ISL6566 (3Phases)

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Cover Page

Cover Page

Cover Page

MS-7390 0A

MS-7390 0A

MS-7390 0A

130Friday, November 30, 2007

130Friday, November 30, 2007

130Friday, November 30, 2007

of

of

1

of

5

4

3

2

1

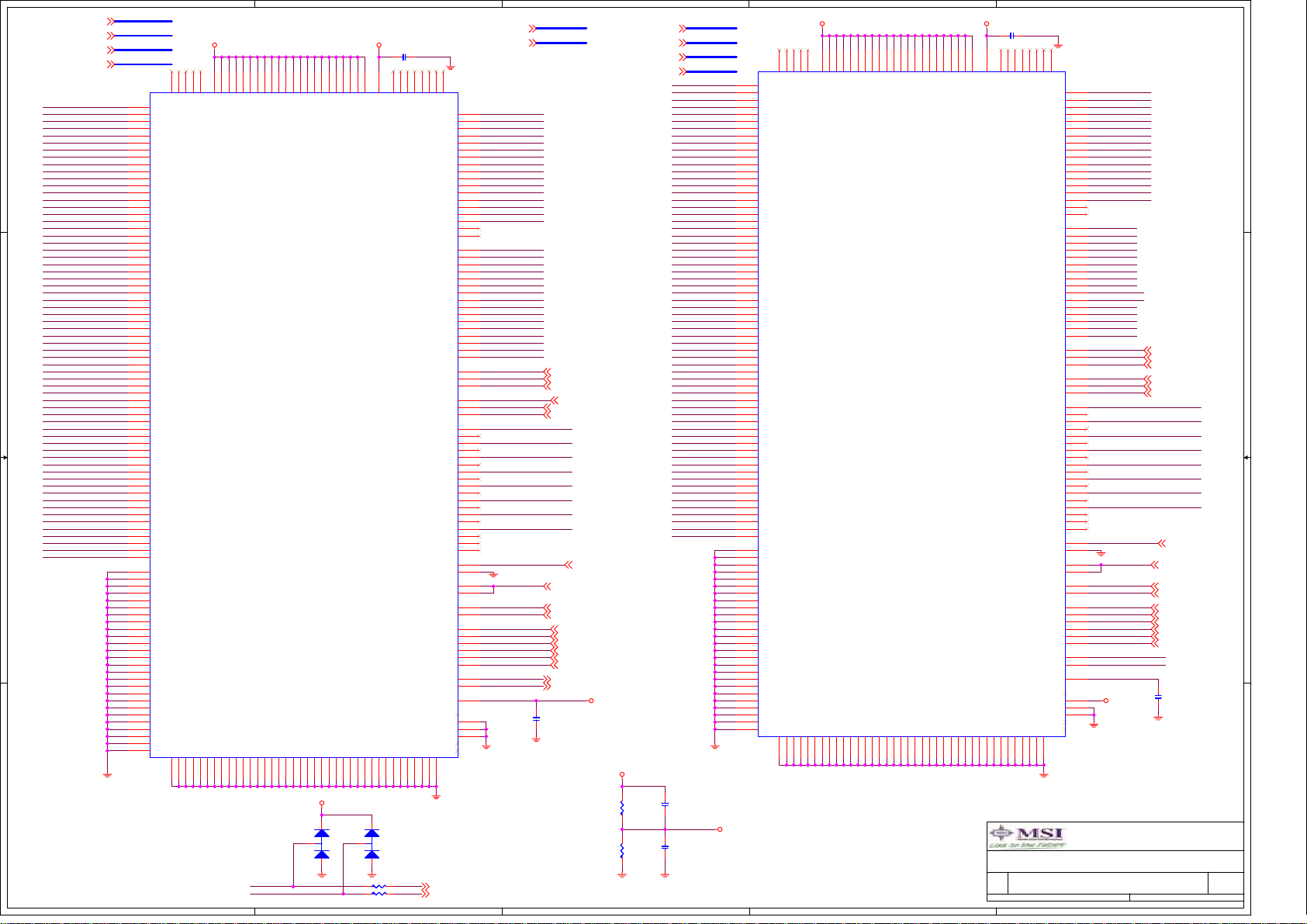

AMD

VRM ISL6566

3-Phase PWM

D D

HyperTransport LINK0

PCIE X16

SLI

PCIE X16

C C

PCIE X1

PCIE X1

PCIE X8

PCIE X8

PCIE X1

PCIE X1

Rear port x 4

USB2.0

Front port x 6

AM2/AM2+ 940

1G

nVIDIA

MCP65P

LINK0

16x16

DDR400/533/667/800

DDRII

DDR400/533/667/800

GMII

AC LINK

SATA-II Link

UNBUFFERED DDR

DIMM1

240-PIN DDRII

UNBUFFERED DDR

DIMM2

240-PIN DDRII

Realtek

RT8211BL

Azalia CODEC

ALC888(8CH)

SATA-II Port

#1~2~3~4

ATA 66/100/133

B B

IDE*1

PCI BUS

PCI SLOT x2

ACPI UPI

A A

5

FLOPPY

*1 *1 *1 *1

4

W83627DHG

KB &

LPT

MOUSE

SERIAL

PORTS

FAN

CONTROL

Vcore

CONTROL

3

SPI

Header

SPI

SPI FLASH ROMSPI Pin

4M

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

Block Diagram

Block Diagram

Block Diagram

MS-7390 0A

MS-7390 0A

MS-7390 0A

230Friday, November 30, 2007

230Friday, November 30, 2007

230Friday, November 30, 2007

of

of

1

of

5

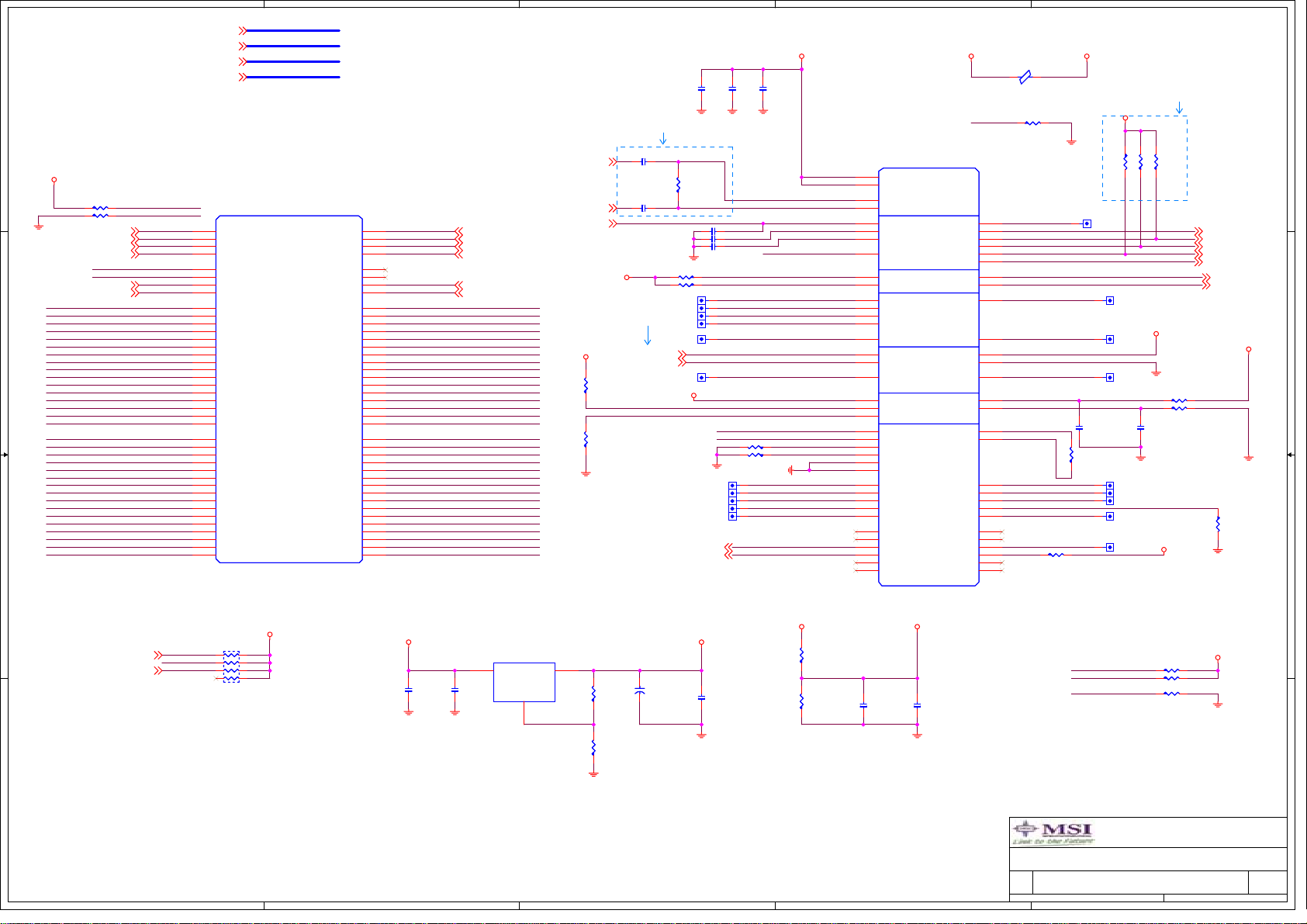

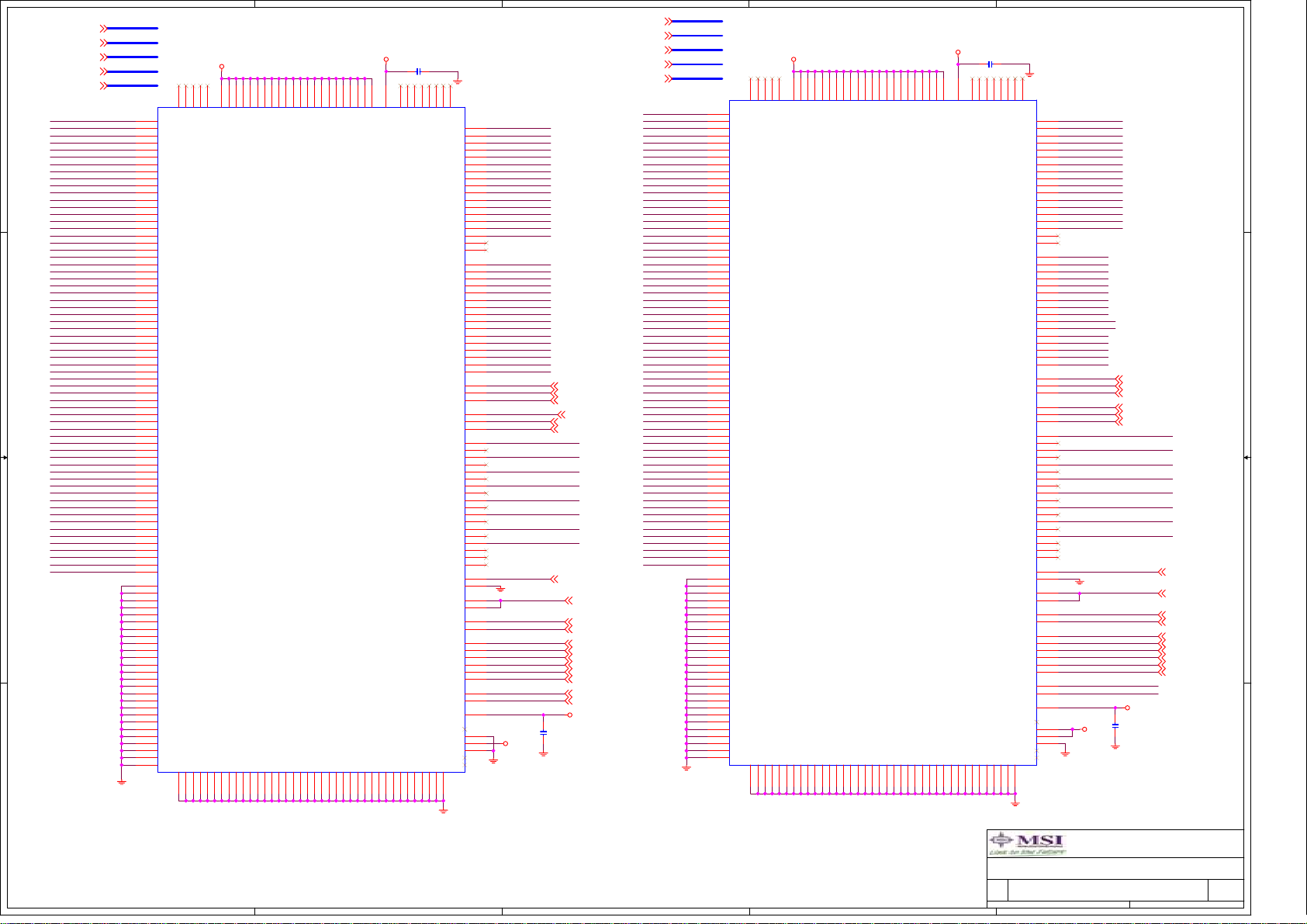

HT_CADIN_H[15..0]9

HT_CADIN_L[15..0]9

HT_CADOUT_H[15..0]9

HT_CADOUT_L[15..0]9

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

4

3

VDDA25

C59

C0.22u16X/6

C59

C0.22u16X/6

C55

C4.7u10Y/8

C55

C4.7u10Y/8

C64

C3300p50X/4

C64

C3300p50X/4

2

VDDA_25 VDDA25

L1

L1

80L3A-100_0805

80L3A-100_0805

1

Place Near The VRM Part

CPUVID1

D D

1.2V_HT

R92 51R1%/2R92 51R1%/2

R95 51R1%/2R95 51R1%/2

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

HT_CLKIN_L09

HT_CTLIN_H09

HT_CTLIN_L09

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

C C

B B

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

LDT_STOP#9

LDT_RST#9

HT_CTLIN_H1

HT_CTLIN_L1

HT_CTLIN_H1

HT_CTLIN_L1

LDT_STOP#

LDT_PWRGD

LDT_RST#

CPU1A

CPU1A

N6

L0_CLKIN_H(1)

P6

L0_CLKIN_L(1)

N3

L0_CLKIN_H(0)

N2

L0_CLKIN_L(0)

V4

L0_CTLIN_H(1)

V5

L0_CTLIN_L(1)

U1

L0_CTLIN_H(0)

V1

L0_CTLIN_L(0)

U6

L0_CADIN_H(15)

V6

L0_CADIN_L(15)

T4

L0_CADIN_H(14)

T5

L0_CADIN_L(14)

R6

L0_CADIN_H(13)

T6

L0_CADIN_L(13)

P4

L0_CADIN_H(12)

P5

L0_CADIN_L(12)

M4

L0_CADIN_H(11)

M5

L0_CADIN_L(11)

L6

L0_CADIN_H(10)

M6

L0_CADIN_L(10)

K4

L0_CADIN_H(9)

K5

L0_CADIN_L(9)

J6

L0_CADIN_H(8)

K6

L0_CADIN_L(8)

U3

L0_CADIN_H(7)

U2

L0_CADIN_L(7)

R1

L0_CADIN_H(6)

T1

L0_CADIN_L(6)

R3

L0_CADIN_H(5)

R2

L0_CADIN_L(5)

N1

L0_CADIN_H(4)

P1

L0_CADIN_L(4)

L1

L0_CADIN_H(3)

M1

L0_CADIN_L(3)

L3

L0_CADIN_H(2)

L2

L0_CADIN_L(2)

J1

L0_CADIN_H(1)

K1

L0_CADIN_L(1)

J3

L0_CADIN_H(0)

J2

L0_CADIN_L(0)

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

RN4

RN4

8P4R-300R/6

8P4R-300R/6

1

3

5

7

2

4

6

8

VCC_DDR

L0_CLKOUT_H(1)

L0_CLKOUT_L(1)

L0_CLKOUT_H(0)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

C51

C51

C10u10Y/8

C10u10Y/8

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

U6

U6

VIN3VOUT

C49

C49

C1u16Y/6

C1u16Y/6

Place the component near the cpu no far 500mil

VCC_DDR

R112

R112

39.2R1%/2

39.2R1%/2

R106

R106

39.2R1%/2

39.2R1%/2

R79

R79

100R1%/2

100R1%/2

C70 C3900p16X/4C70 C3900p16X/4

C73 C3900p16X/4C73 C3900p16X/4

R110 1K/2R110 1K/2

R111 X_1K/2R111 X_1K/2

COREFB+24

COREFB-24

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

THERMDC_CPU17

THERMDA_CPU17

+

+

12

EC2

EC2

CD100u16EL5-RH

CD100u16EL5-RH

R83

R83

169R1%/2

169R1%/2

C61 X_220p25N/4C61 X_220p25N/4

C58 X_220p25N/4C58 X_220p25N/4

C66 X_220p25N/4C66 X_220p25N/4

TP2TP2

TP19TP19

TP18TP18

TP1TP1

TP15TP15

CPU_M_VREF

VDDA_25VCC5

ADJ

LT1087S_SOT89

LT1087S_SOT89

1

LDT_PWRGD9,24

2

CPU_CLK9

CPU_CLK#9

ROUTE AS DIFF PAIR

10/5/5/5/10

VCC_DDR

COREFB+

COREFB-

TP11TP11

TP13TP13

TP16TP16

TP10TP10

TP17TP17

C54

C54

C10u10Y/8

C10u10Y/8

THERM_SIC

THERM_SID

CPU_TDI

CPU_TRST_L

CPU_TCK

CPU_TMS

CPU_DBREQ_L

CPU_VTT_SENSE

CPU_TEST25_H

CPU_TEST25_L

R76 300R/2R76 300R/2

R77 300R/2R77 300R/2

CPUCLKIN

CPUCLKIN#

LDT_PWRGD

LDT_STOP#

LDT_RST#

CPU_PRESENT_L

VCC_DDR

R74

R74

15R1%/3

15R1%/3

R75

R75

15R1%/3

15R1%/3

CPU1D

CPU1D

C10

VDDA1

D10

VDDA2

A8

CLKIN_H

B8

CLKIN_L

C9

PWROK

D8

LDTSTOP_L

C7

RESET_L

AL3

CPU_PRESENT_L

AL6

SIC

AK6

SID

AL10

TDI

AJ10

TRST_L

AH10

TCK

AL9

TMS

A5

DBREQ_L

G2

VDD_FB_H

G1

VDD_FB_L

E12

VTT_SENSE

F12

M_VREF

AH11

M_ZN

AJ11

M_ZP

A10

TEST25_H

B10

TEST25_L

F10

TEST19

E9

TEST18

AJ7

TEST13

F6

TEST9

D6

TEST17

E7

TEST16

F8

TEST15

C5

TEST14

AH9

TEST12

E5

TEST7

AJ5

TEST6

AG9

TEST5

AG8

TEST4

AH7

TEST3

AJ6

TEST2

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

C56

C56

C0.1U16X/4

C0.1U16X/4

THERMTRIP_L

PROCHOT_L

VDDIO_FB_H

VDDIO_FB_L

CPU_M_VREF

C63

C63

X_C1000p16X/4

X_C1000p16X/4

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

TDO

DBRDY

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

R86 X_300R/2R86 X_300R/2

D2

D1

C1

E3

E2

E1

AK7

AL7

AK10

B6

AK11

AL11

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

CPUVID1

CPU_THRIP#

CPU_PROCHOT#

CPU_TDO

CPU_DBRDY

CPU_VDDIOFB_H

CPU_VDDIOFB_L

CPU_PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

R108 300R/2R108 300R/2

VCC_DDR

TP9TP9

TP3TP3

TP7TP7TP8TP8

TP14TP14

C151

C151

X_C1000p10X/4

X_C1000p10X/4

R80

R80

80.6R1%/3

80.6R1%/3

TP23TP23

TP20TP20

TP22TP22

TP21TP21

TP24TP24

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

R16 300R/2R16 300R/2

R25 1KR0402R25 1KR0402

R31 1KR0402R31 1KR0402

VCC_DDR

R109 44.2R1%/2R109 44.2R1%/2

R104 44.2R1%/2R104 44.2R1%/2

C150

C150

X_C1000p10X/4

X_C1000p10X/4

VCC_DDR

R107 1K/2R107 1K/2

R82 510R/2R82 510R/2

R81 510R/2R81 510R/2

CPUVID4 24

CPUVID3 24

CPUVID2 24

CPUVID1 24

CPUVID0 24

CPU_THRIP# 9

CPU_PROCHOT# 9

1.2V_HT

R105

R105

300R/2

300R/2

VCC_DDR

R78

R78

100R1%/2

100R1%/2

A A

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

K9 M2 HT I/F,CTRL

K9 M2 HT I/F,CTRL

K9 M2 HT I/F,CTRL

MS-7390 0A

MS-7390 0A

MS-7390 0A

330Friday, November 30, 2007

330Friday, November 30, 2007

330Friday, November 30, 2007

of

of

1

of

5

4

3

2

1

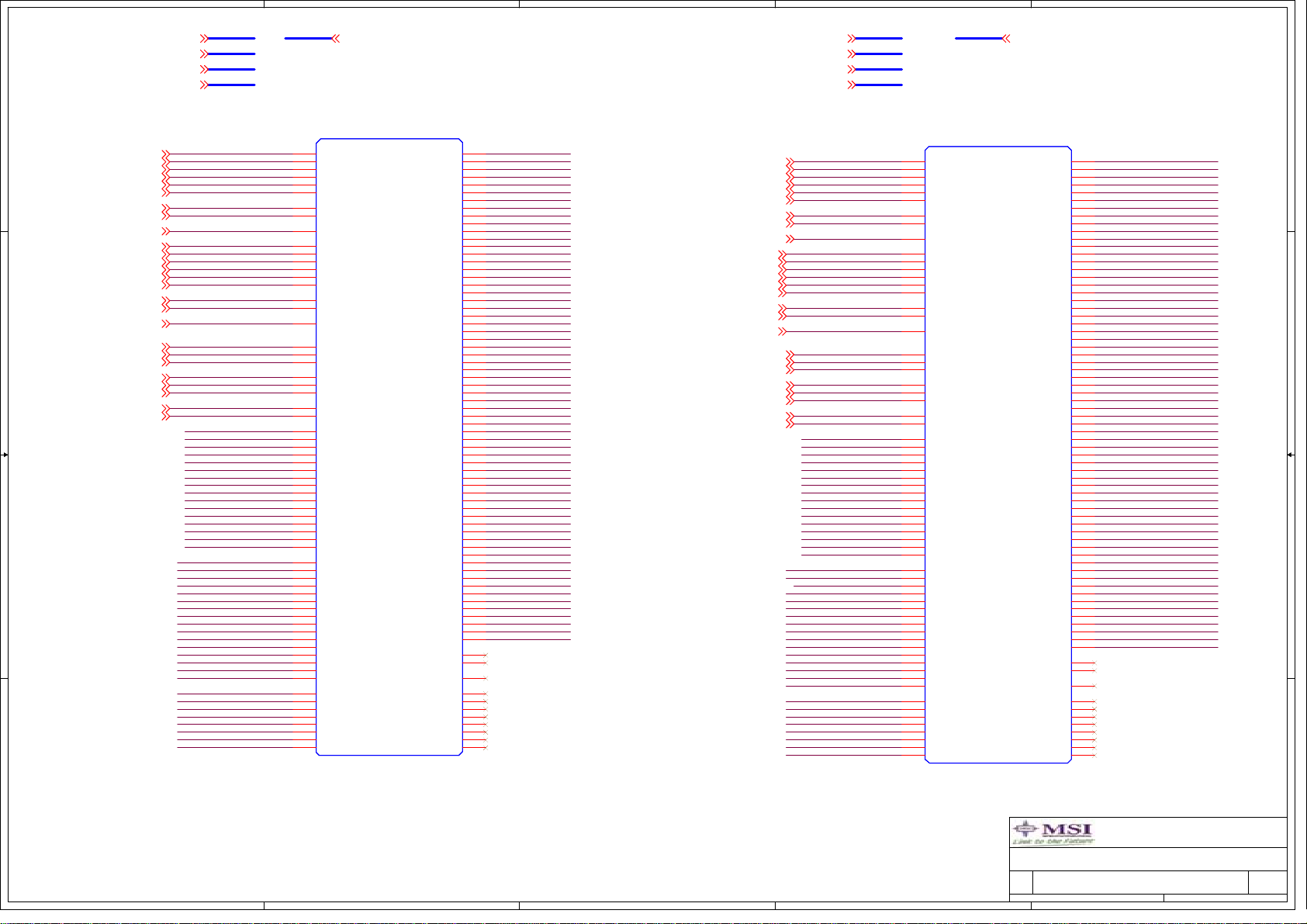

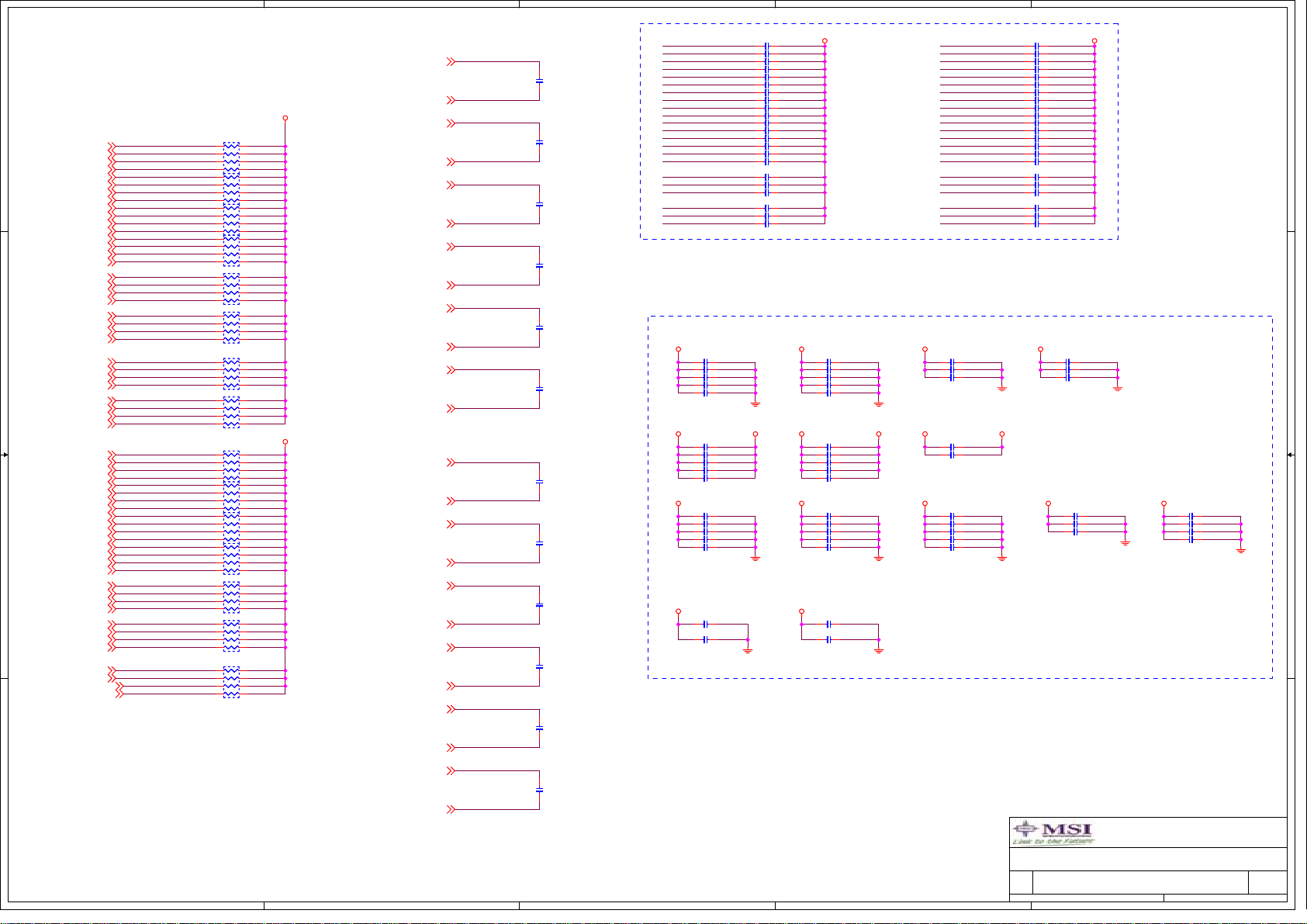

MEM_MA_DQS_L[7..0]6,7

MEM_MA_DQS_H[7..0]6,7

MEM_MA_DM[7..0]6,7

MEM_MA_ADD[15..0]6,7,8 MEM_MB_ADD[15..0]6,7,8

D D

MEM_MA0_CLK_H26,8

MEM_MA0_CLK_L26,8

MEM_MA0_CLK_H16,8

MEM_MA0_CLK_L16,8

MEM_MA0_CLK_H06,8

MEM_MA0_CLK_L06,8

MEM_MA0_CS_L16,8

MEM_MA0_CS_L06,8

MEM_MA0_ODT06,8

MEM_MA1_CLK_H27,8

MEM_MA1_CLK_L27,8

MEM_MA1_CLK_H17,8

MEM_MA1_CLK_L17,8

MEM_MA1_CLK_H07,8

MEM_MA1_CLK_L07,8

MEM_MA1_CS_L17,8

MEM_MA1_CS_L07,8

MEM_MA1_ODT07,8

C C

B B

A A

MEM_MA_CAS_L6,7,8

MEM_MA_WE_L6,7,8

MEM_MA_RAS_L6,7,8

MEM_MA_BANK26,7,8

MEM_MA_BANK16,7,8

MEM_MA_BANK06,7,8

MEM_MA_CKE17,8

MEM_MA_CKE06,8

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

MEM_MA1_CLK_H2

MEM_MA1_CLK_L2

MEM_MA1_CLK_H1

MEM_MA1_CLK_L1

MEM_MA1_CLK_H0

MEM_MA1_CLK_L0

MEM_MA1_CS_L1

MEM_MA1_CS_L0

MEM_MA1_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE1

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

AG21

AG20

G19

H19

U27

U26

AC25

AA24

AC28

AE20

AE19

G20

G21

V27

W27

AD27

AA25

AC27

AB25

AB27

AA26

N25

Y27

AA27

M25

M27

N24

AC26

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

D29

C29

C25

D25

E19

G15

AF15

AF19

AJ25

AH29

B29

E24

E18

H15

L27

T25

T27

F19

F15

MEM_MA_DATA[63..0] 6,7

CPU1B

CPU1B

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DQS_H(8)

MA_DQS_L(8)

MA_DM(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA18

MEM_MA_DATA17

MEM_MA_DATA16

MEM_MA_DATA15

MEM_MA_DATA14

MEM_MA_DATA13

MEM_MA_DATA12

MEM_MA_DATA11

MEM_MA_DATA10

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MB0_CLK_H26,8

MEM_MB0_CLK_L26,8

MEM_MB0_CLK_H16,8

MEM_MB0_CLK_L16,8

MEM_MB0_CLK_H06,8

MEM_MB0_CLK_L06,8

MEM_MB0_CS_L16,8

MEM_MB0_CS_L06,8

MEM_MB0_ODT06,8

MEM_MB1_CLK_H27,8

MEM_MB1_CLK_L27,8

MEM_MB1_CLK_H17,8

MEM_MB1_CLK_L17,8

MEM_MB1_CLK_H07,8

MEM_MB1_CLK_L07,8

MEM_MB1_CS_L17,8

MEM_MB1_CS_L07,8

MEM_MB1_ODT07,8

MEM_MB_CAS_L6,7,8

MEM_MB_WE_L6,7,8

MEM_MB_RAS_L6,7,8

MEM_MB_BANK26,7,8

MEM_MB_BANK16,7,8

MEM_MB_BANK06,7,8

MEM_MB_CKE17,8

MEM_MB_CKE06,8

MEM_MB_DQS_L[7..0]6,7

MEM_MB_DQS_H[7..0]6,7

MEM_MB_DM[7..0]6,7

MEM_MB1_CLK_H2

MEM_MB1_CLK_L2

MEM_MB1_CLK_H1

MEM_MB1_CLK_L1

MEM_MB1_CLK_H0

MEM_MB1_CLK_L0

MEM_MB1_CS_L1

MEM_MB1_CS_L0

MEM_MB1_ODT0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE1

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

CPU1C

CPU1C

AJ19

MB0_CLK_H(2)

AK19

MB0_CLK_L(2)

A18

MB0_CLK_H(1)

A19

MB0_CLK_L(1)

U31

MB0_CLK_H(0)

U30

MB0_CLK_L(0)

AE30

MB0_CS_L(1)

AC31

MB0_CS_L(0)

AD29

MB0_ODT(0)

AL19

MB1_CLK_H(2)

AL18

MB1_CLK_L(2)

C19

MB1_CLK_H(1)

D19

MB1_CLK_L(1)

W29

MB1_CLK_H(0)

W28

MB1_CLK_L(0)

AE29

MB1_CS_L(1)

AB31

MB1_CS_L(0)

AD31

MB1_ODT(0)

AC29

MB_CAS_L

AC30

MB_WE_L

AB29

MB_RAS_L

N31

MB_BANK(2)

AA31

MB_BANK(1)

AA28

MB_BANK(0)

M31

MB_CKE(1)

M29

MB_CKE(0)

N28

MB_ADD(15)

N29

MB_ADD(14)

AE31

MB_ADD(13)

N30

MB_ADD(12)

P29

MB_ADD(11)

AA29

MB_ADD(10)

P31

MB_ADD(9)

R29

MB_ADD(8)

R28

MB_ADD(7)

R31

MB_ADD(6)

R30

MB_ADD(5)

T31

MB_ADD(4)

T29

MB_ADD(3)

U29

MB_ADD(2)

U28

MB_ADD(1)

AA30

MB_ADD(0)

AK13

MB_DQS_H(7)

AJ13

MB_DQS_L(7)

AK17

MB_DQS_H(6)

AJ17

MB_DQS_L(6)

AK23

MB_DQS_H(5)

AL23

MB_DQS_L(5)

AL28

MB_DQS_H(4)

AL29

MB_DQS_L(4)

D31

MB_DQS_H(3)

C31

MB_DQS_L(3)

C24

MB_DQS_H(2)

C23

MB_DQS_L(2)

D17

MB_DQS_H(1)

C17

MB_DQS_L(1)

C14

MB_DQS_H(0)

C13

MB_DQS_L(0)

AJ14

MB_DM(7)

AH17

MB_DM(6)

AJ23

MB_DM(5)

AK29

MB_DM(4)

C30

MB_DM(3)

A23

MB_DM(2)

B17

MB_DM(1)

B13

MB_DM(0)

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

MEM_MB_DATA[63..0] 6,7

MB_DM(8)

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

K9 M2 DDR MEMORY

K9 M2 DDR MEMORY

K9 M2 DDR MEMORY

MS-7390 0A

MS-7390 0A

MS-7390 0A

430Friday, November 30, 2007

430Friday, November 30, 2007

430Friday, November 30, 2007

of

of

1

of

5

4

3

2

1

VCCP

D D

C C

B B

VTT_DDR

C53

C10u6.3X/8

C53

C10u6.3X/8

A4

VDD

A6

VDD

AA8

VDD

AA10

VDD

AA12

VDD

AA14

VDD

AA16

VDD

AA18

VDD

AB7

VDD

AB9

VDD

AB11

VDD

AC4

VDD

AC5

VDD

AC8

VDD

AC10

VDD

AD2

VDD

AD3

VDD

AD7

VDD

AD9

VDD

AE10

VDD

AF7

VDD

AF9

VDD

AG4

VDD

AG5

VDD

AG7

VDD

AH2

VDD

AH3

VDD

B3

VDD

B5

VDD

B7

VDD

C2

VDD

C4

VDD

C6

VDD

C8

VDD

D3

VDD

D5

VDD

D7

VDD

D9

VDD

E4

VDD

E6

VDD

E8

VDD

E10

VDD

F5

VDD

F7

VDD

F9

VDD

F11

VDD

G6

VDD

G8

VDD

G10

VDD

G12

VDD

H7

VDD

H11

VDD

H23

VDD

J8

VDD

J12

VDD

J14

VDD

J16

VDD

J18

VDD

J20

VDD

J22

VDD

J24

VDD

K7

VDD

K9

VDD

K11

VDD

K13

VDD

K15

VDD

K17

VDD

K19

VDD

K21

VDD

K23

VDD

L4

VDD

L5

VDD

L8

VDD

L10

VDD

L12

VDD

Y17

VDD

Y19

VDD

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

C0.01u10X/4

C0.01u10X/4

C198

C0.22u10X/6

C198

C0.22u10X/6

CPU1F

CPU1F

C72

C72

C4.7u6.3X/6

C4.7u6.3X/6

C161

C10u6.3X/8

C161

C10u6.3X/8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C190

C190

X_C4.7u6.3X/6

X_C4.7u6.3X/6

C196

C196

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

C67

C4.7u6.3X/6

C67

C4.7u6.3X/6

C16

X_C4.7u6.3X/6

C16

X_C4.7u6.3X/6

VCCP

C179

C4.7u6.3X/6

C179

C4.7u6.3X/6

X_C4.7u6.3X/6

X_C4.7u6.3X/6

SLOTOCC# 24

L14

L16

L18

M11

M13

M15

M17

M19

N10

N12

N14

N16

N18

P11

P13

P15

P17

P19

R10

R12

R14

R16

R18

R20

T11

T13

T15

T17

T19

T21

U10

U12

U14

U16

U18

U20

V11

V13

V15

V17

V19

V21

W10

W12

W14

W16

W18

W20

Y11

Y13

Y15

Y21

X_C4.7u6.3X/6

X_C4.7u6.3X/6

C40

C4.7u6.3X/6

C40

C4.7u6.3X/6

C62

C62

CPU1G

CPU1G

VDD

VDD

VDD

M2

VDD

M3

VDD

M7

VDD

M9

VDD

VDD

VDD

VDD

VDD

VDD

N8

VDD

VDD

VDD

VDD

VDD

VDD

P7

VDD

P9

VDD

VDD

VDD

VDD

VDD

VDD

R4

VDD

R5

VDD

R8

VDD

VDD

VDD

VDD

VDD

VDD

VDD

T2

VDD

T3

VDD

T7

VDD

T9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

U8

VDD

VDD

VDD

VDD

VDD

VDD

VDD

V9

VDD

VDD

VDD

VDD

VDD

VDD

VDD

W4

VDD

W5

VDD

W8

VDD

VDD

VDD

VDD

VDD

VDD

VDD

Y2

VDD

Y3

VDD

Y7

VDD

Y9

VDD

VDD

VDD

VDD

VDD

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

C186

C186

C199

C0.22u10X/6

C199

C0.22u10X/6

C26

C0.22u10X/6

C26

C0.22u10X/6

C173

X_C0.22u10X/6

C173

X_C0.22u10X/6

AK20

VSS

AK22

VSS

AK24

VSS

AK26

VSS

AK28

VSS

AK30

VSS

AL5

VSS

B4

VSS

B9

VSS

B11

VSS

B14

VSS

B16

VSS

B18

VSS

B20

VSS

B22

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

C3

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D22

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

E11

VSS

F4

VSS

F14

VSS

F16

VSS

F18

VSS

F20

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

G9

VSS

G11

VSS

H8

VSS

H10

VSS

H12

VSS

H14

VSS

H16

VSS

H18

VSS

H22

VSS

H24

VSS

H26

VSS

H28

VSS

H30

VSS

J4

VSS

J5

VSS

J7

VSS

J9

VSS

J11

VSS

J13

VSS

J15

VSS

J17

VSS

J19

VSS

J21

VSS

J23

VSS

K2

VSS

K3

VSS

K8

VSS

K10

VSS

K12

VSS

K14

VSS

K16

VSS

K18

VSS

K20

VSS

K22

VSS

Y18

VSS

C0.01u10X/4

C0.01u10X/4

C57

X_C0.22u10X/6

C57

X_C0.22u10X/6

C172

C172

VCCP

VCCP

X_C4.7u6.3X/8

X_C4.7u6.3X/8

C485

C4.7u6.3X/8

C485

C4.7u6.3X/8

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

M21

M23

N20

N22

R22

U22

W22

X_C10u6.3X/8

X_C10u6.3X/8

C461

C461

CPU1H

CPU1H

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

L20

VDD

L22

VDD

VDD

VDD

VDD

VDD

P21

VDD

P23

VDD

VDD

T23

VDD

VDD

V23

VDD

VDD

Y23

VDD

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

C479

C10u6.3X/8

C479

C10u6.3X/8

C486

C486

C0.01u10X/4

C0.01u10X/4

C469

C0.01u10X/4

C469

C0.01u10X/4

C76

C76

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

C489

C4.7u6.3X/8

C489

C4.7u6.3X/8

X_C4.7u6.3X/8

X_C4.7u6.3X/8

C490

C490

X_C0.22u10X/6

X_C0.22u10X/6

C75

C0.22u10X/6

C75

C0.22u10X/6

C74

C74

C77

C4.7u10Y/8

C77

C4.7u10Y/8

C0.01u10X/4

C0.01u10X/4

C475

C475

1.2V_HT

VTT_DDR

VCC_DDR

L25

L26

L31

L30

W26

W25

AE27

U24

V24

AE28

Y31

Y30

AG31

V31

W31

AF31

CPU1E

CPU1E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

CPU1I

CPU1I

AJ4

AJ3

AJ2

AJ1

D12

C12

B12

A12

AB24

AB26

AB28

AB30

AC24

AD26

AD28

AD30

AF30

M24

M26

M28

M30

P24

P26

P28

P30

T24

T26

T28

T30

V25

V26

V28

V30

Y24

Y26

Y28

Y29

ZIF-SOCK940-RH-1

ZIF-SOCK940-RH-1

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

VLDT_A1

VLDT_A2

VLDT_A3

VLDT_A4

VTT

VTT

VTT

VTT

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

E20

B19

AL4

AK4

AK3

F2

F3

G4

G3

G5

AD25

AE24

AE25

AJ18

AJ20

C18

C20

G24

G25

H25

V29

W30

H6

VLDT_B1

H5

VLDT_B2

H2

VLDT_B3

H1

VLDT_B4

AK12

VTT

AJ12

VTT

AH12

VTT

AG12

VTT

AL12

VTT

K24

VSS

K26

VSS

K28

VSS

K30

VSS

L7

VSS

L9

VSS

L11

VSS

L13

VSS

L15

VSS

L17

VSS

L19

VSS

L21

VSS

L23

VSS

M8

VSS

M10

VSS

M12

VSS

M14

VSS

M16

VSS

M18

VSS

M20

VSS

M22

VSS

N4

VSS

N5

VSS

N7

VSS

N9

VSS

N11

VSS

N13

VSS

N15

VSS

R103 X_0R/2R103 X_0R/2

CPU_CORETYPE#

VTT_DDR

TP12TP12

R85 300R/2R85 300R/2

VLDT_RUN_B

1.2V_HT

1.2V_HT

VCC_DDR

CPU_CORETYPE# 24

VCCP

VCCP

C84

C0.01u10X/4

C84

C0.01u10X/4

C82

X_C0.01u10X/4

C82

X_C0.01u10X/4

C83

C0.01u10X/4

C83

C0.01u10X/4

C92

C4.7u6.3X/6

C92

C4.7u6.3X/6

C188

C0.22u16X/6

C188

C149

X_C0.22u16X/6

C149

X_C0.22u16X/6

C169

X_C4.7u10Y/8/B

C169

X_C4.7u10Y/8/B

VCCP VCC_DDR

C451

C10u6.3X/8/B

C451

C10u6.3X/8/B

C462

C0.22u10X/6

C462

C0.22u10X/6

C0.22u16X/6

C158

X_C0.22u16X/6

C158

X_C0.22u16X/6

C164

X_C0.22u16X/6

C164

X_C0.22u16X/6

X_C0.22u16X/6

X_C0.22u16X/6

C184

C4.7u10Y/8

C184

C4.7u10Y/8

C449 X_C2.2u6.3X/6C449 X_C2.2u6.3X/6

5020 Parts

C471

X_C10u6.3X/8/B

C471

X_C10u6.3X/8/B

C4.7u10Y/8

C4.7u10Y/8

C460

X_C0.22u10X/6

C460

X_C0.22u10X/6

C192

C192

X_C0.22u16X/6

X_C0.22u16X/6

X_C4.7u10Y/8

X_C4.7u10Y/8

C480

C480

C195

C195

C454

C454

C180

C4.7u10Y/8

C180

C4.7u10Y/8

C155

C0.22u16X/6

C155

C0.22u16X/6

C468

C4.7u10Y/8

C468

C4.7u10Y/8

C175

X_C180p50N/4

C175

X_C180p50N/4

C194

X_C180p50N/4

C194

X_C180p50N/4

C455

C0.01u10X/4

C455

C0.01u10X/4

C484

C0.01u10X/4

C484

C0.01u10X/4

A A

VCC_DDR

X_C10u6.3X/8

X_C10u6.3X/8

C483

C10u6.3X/8

C483

C10u6.3X/8

C493

C493

C448

C10u6.3X/8

C448

C10u6.3X/8

5

C459

X_C10u6.3X/8

C459

X_C10u6.3X/8

C456

X_C0.22u10X/6

C456

X_C0.22u10X/6

C488

X_C0.22u10X/6

C488

X_C0.22u10X/6

C474

C180p50N/6

C474

C180p50N/6

C450

C0.01u10X/4

C450

C0.01u10X/4

C0.01u10X/4

C0.01u10X/4

C465

C465

C10u6.3X/8

C10u6.3X/8

C487

C0.01u10X/4

C487

C0.01u10X/4

C235

C235

X_C4.7u6.3X/6

X_C4.7u6.3X/6

C491

C4.7u6.3X/6

C491

C4.7u6.3X/6

C478

C478

C470

C4.7u6.3X/6

C470

C4.7u6.3X/6

4

C212

X_C4.7u6.3X/6

C212

X_C4.7u6.3X/6

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

K9 M2 PWR & GND

K9 M2 PWR & GND

K9 M2 PWR & GND

MS-7390 0A

MS-7390 0A

MS-7390 0A

530Friday, November 30, 2007

530Friday, November 30, 2007

530Friday, November 30, 2007

of

of

1

of

5

MEM_MA_DQS_H[7..0]4,7

MEM_MA_DQS_L[7..0]4,7

MEM_MA_DATA[63..0]4,7

MEM_MA_DM[7..0]4,7

DIMM1

DIMM1

MEM_MA_DATA0

MEM_MA_DATA1

D D

C C

B B

A A

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

5

VCC_DDR VCC3

170

191

194

181

175

75

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

130

133

136

139

142

145

148

SCL

SDA

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

102

68

19

55

NC2

NC1

RC118RC0

VDD51VDD56VDD62VDD72VDD78VDD

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

118

121

124

127

VDDQ

VDDQ53VDDQ59VDDQ64VDDQ

VSS

VSS

VSS

151

154

Z

197

VSS

VSS

157

160

3VDUAL

163

Y

X

172

VDDQ69VDDQ

VSS

166

187

184

189

67

178

VDDQ

VDDQ

VDDQ

VDDQ

VSS

VSS

VSS

VSS

VSS

169

198

201

204

207

D9

1PS226_SOT23

D9

1PS226_SOT23

Z

R140 X_R/2R140 X_R/2

R148 X_R/2R148 X_R/2

4

C216 X_C0.1u16Y/4C216 X_C0.1u16Y/4

238

CB042CB143CB248CB349CB4

VDDQ

VDDSPD

VSS

VSS

VSS

VSS

VSS

210

213

216

219

D10

1PS226_SOT23

D10

1PS226_SOT23

Y

X

4

VSS

222

225

161

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2#(DU)

VSS

VSS

VSS

228

231

MEM_MB_ADD[15..0]4,7,8

MEM_MA_ADD[15..0]4,7,8

162

167

168

CB5

CB6

CB7

MEM_MA_DQS_H0

7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A10_AP

A16/BA2

WE#

CAS#

RAS#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK2(DU)

SDA

VREF

VSS

VSS

234

237

MEM_SMB_CLK0 12

MEM_SMB_DATA0 12

MEM_MA_DQS_L0

6

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

28

MEM_MA_DQS_L2

27

MEM_MA_DQS_H3

37

MEM_MA_DQS_L3

36

MEM_MA_DQS_H4

84

MEM_MA_DQS_L4

83

MEM_MA_DQS_H5

93

MEM_MA_DQS_L5

92

MEM_MA_DQS_H6

105

MEM_MA_DQS_L6

104

MEM_MA_DQS_H7

114

MEM_MA_DQS_L7

113

46

45

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

183

A1

MEM_MA_ADD2

63

A2

MEM_MA_ADD3

182

A3

MEM_MA_ADD4

61

A4

MEM_MA_ADD5

60

A5

MEM_MA_ADD6

180

A6

MEM_MA_ADD7

58

A7

MEM_MA_ADD8

179

A8

MEM_MA_ADD9

177

A9

MEM_MA_ADD10

70

MEM_MA_ADD11

57

A11

MEM_MA_ADD12

176

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

174

A14

MEM_MA_ADD15

173

A15

BA1

BA0

SCL

SA0

SA1

SA2

MEM_MA_BANK2

54

MEM_MA_BANK1

190

MEM_MA_BANK0

71

MEM_MA_WE_L

73

MEM_MA_CAS_L

74

MEM_MA_RAS_L

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

MEM_MA0_ODT0

195

77

MEM_MA_CKE0

52

171

MEM_MA0_CS_L0

193

MEM_MA0_CS_L1

76

MEM_MA0_CLK_H0

185

MEM_MA0_CLK_L0

186

MEM_MA0_CLK_H1

137

MEM_MA0_CLK_L1

138

MEM_MA0_CLK_H2

220

MEM_MA0_CLK_L2

221

SCL

120

SDA

119

VDDR_VREF

1

X1

X1

239

240

101

X2

X2

X3

X3

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

SPD. Address = A0h

MEM_MA_BANK2 4,7,8

MEM_MA_BANK1 4,7,8

MEM_MA_BANK0 4,7,8

MEM_MA_WE_L 4,7,8

MEM_MA_CAS_L 4,7,8

MEM_MA_RAS_L 4,7,8

MEM_MA0_ODT0 4,8

MEM_MA_CKE0 4,8

MEM_MA0_CS_L0 4,8

MEM_MA0_CS_L1 4,8

MEM_MA0_CLK_H0 4,8

MEM_MA0_CLK_L0 4,8

MEM_MA0_CLK_H1 4,8

MEM_MA0_CLK_L1 4,8

MEM_MA0_CLK_H2 4,8

MEM_MA0_CLK_L2 4,8

SCL 7

SDA 7

VDDR_VREF

C33

C33

C0.1u16Y/4

C0.1u16Y/4

MEM_MB_DQS_H[7..0]4,7

MEM_MB_DQS_L[7..0]4,7

MEM_MB_DATA[63..0]4,7

VCC_DDR

3

MEM_MB_DM[7..0]4,7

R40

R40

49.9R1%/2

49.9R1%/2

R45

R45

49.9R1%/2

49.9R1%/2

3

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

C52

C52

X_C0.1u16Y/4

X_C0.1u16Y/4

VDDR_VREF

C31

C31

X_C0.1u16Y/4

X_C0.1u16Y/4

DIMM2

DIMM2

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

VDDR_VREF

VCC_DDR VCC3

102

68

19

55

3

DQ0

4

DQ1

9

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

2

VSS

5

VSS

8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC2

NC1

RC118RC0

VDD51VDD56VDD62VDD72VDD78VDD

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

118

2

C217 X_C0.1u16Y/4C217 X_C0.1u16Y/4

170

197

172

187

184

189

67

178

191

194

181

175

75

VDD

VDD

VDD

VDD

VDDQ

VDDQ53VDDQ59VDDQ64VDDQ

VDDQ

VDDQ69VDDQ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

121

124

127

130

133

136

139

142

145

148

151

154

157

160

163

166

2

238

161

162

167

168

CB042CB143CB248CB349CB4

CB5

CB6

CB7

VDDQ

VDDQ

VDDQ

VDDQ

VDDSPD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

169

198

201

204

207

210

213

216

219

222

225

228

Title

Title

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

7

DQS0

6

DQS0#

16

DQS1

15

DQS1#

28

DQS2

27

DQS2#

37

DQS3

36

DQS3#

84

DQS4

83

DQS4#

93

DQS5

92

DQS5#

105

DQS6

104

DQS6#

114

DQS7

113

DQS7#

46

DQS8

45

DQS8#

188

A0

183

A1

63

A2

182

A3

61

A4

60

A5

180

A6

58

A7

179

A8

177

A9

70

A10_AP

57

A11

176

A12

196

A13

174

A14

173

A15

54

A16/BA2

190

BA1

71

BA0

73

WE#

74

CAS#

192

RAS#

125

DM0/DQS9

126

NC/DQS9#

134

DM1/DQS10

135

NC/DQS10#

146

DM2/DQS11

147

NC/DQS11#

155

DM3/DQS12

156

NC/DQS12#

202

DM4/DQS13

203

NC/DQS13#

211

DM5/DQS14

212

NC/DQS14#

223

DM6/DQS15

224

NC/DQS15#

232

DM7/DQS16

233

NC/DQS16#

164

DM8/DQS17

165

NC/DQS17#

195

ODT0

77

ODT1

52

CKE0

171

CKE1

193

CS0#

76

CS1#

185

CK0(DU)

186

CK0#(DU)

137

CK1(CK0)

138

CK1#(CK0#)

220

CK2(DU)

221

CK2#(DU)

120

SCL

119

SDA

1

VREF

X1

X1

239

SA0

240

SA1

101

SA2

X2

X2

X3

X3

VSS

VSS

VSS

VSS

DDRII-240_ORANGE-RH

DDRII-240_ORANGE-RH

231

234

237

SPD. Address = A2h

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

MICRO-START INT'L CO.,LTD.

1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_ADD0

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MB_ADD3

MEM_MB_ADD4

MEM_MB_ADD5

MEM_MB_ADD6

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MB_ADD9

MEM_MB_ADD10

MEM_MB_ADD11

MEM_MB_ADD12

MEM_MB_ADD13

MEM_MB_ADD14

MEM_MB_ADD15

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_WE_L

MEM_MB_CAS_L

MEM_MB_RAS_L

MEM_MB0_ODT0

MEM_MB_CKE0

MEM_MB_CKE0

MEM_MB0_CS_L0

MEM_MB0_CS_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

MS-7390 0A

MS-7390 0A

MS-7390 0A

MEM_MB_DM0

MEM_MB_DM1

MEM_MB_DM2

MEM_MB_DM3

MEM_MB_DM4

MEM_MB_DM5

MEM_MB_DM6

MEM_MB_DM7

SCL

SDA

VDDR_VREF

VCC3

1

MEM_MB_BANK2 4,7,8

MEM_MB_BANK1 4,7,8

MEM_MB_BANK0 4,7,8

MEM_MB_WE_L 4,7,8

MEM_MB_CAS_L 4,7,8

MEM_MB_RAS_L 4,7,8

MEM_MB0_ODT0 4,8

MEM_MB_CKE0 4,8

MEM_MB0_CS_L0 4,8

MEM_MB0_CS_L1 4,8

MEM_MB0_CLK_H0 4,8

MEM_MB0_CLK_L0 4,8

MEM_MB0_CLK_H1 4,8

MEM_MB0_CLK_L1 4,8

MEM_MB0_CLK_H2 4,8

MEM_MB0_CLK_L2 4,8

C32

C32

C1000p50X/4

C1000p50X/4

of

of

of

630Friday, November 30, 2007

630Friday, November 30, 2007

630Friday, November 30, 2007

5

MEM_MA_DM[7..0]4,6

MEM_MA_ADD[15..0]4,6,8

MEM_MA_DQS_H[7..0]4,6

MEM_MA_DQS_L[7..0]4,6

MEM_MA_DATA[63..0]4,6

D D

C C

B B

A A

MEM_MA_DATA0

MEM_MA_DATA1

MEM_MA_DATA2

MEM_MA_DATA3

MEM_MA_DATA4

MEM_MA_DATA5

MEM_MA_DATA6

MEM_MA_DATA7

MEM_MA_DATA8

MEM_MA_DATA9

MEM_MA_DATA10

MEM_MA_DATA11

MEM_MA_DATA12

MEM_MA_DATA13

MEM_MA_DATA14

MEM_MA_DATA15

MEM_MA_DATA16

MEM_MA_DATA17

MEM_MA_DATA18

MEM_MA_DATA19

MEM_MA_DATA20

MEM_MA_DATA21

MEM_MA_DATA22

MEM_MA_DATA23

MEM_MA_DATA24

MEM_MA_DATA25

MEM_MA_DATA26

MEM_MA_DATA27

MEM_MA_DATA28

MEM_MA_DATA29

MEM_MA_DATA30

MEM_MA_DATA31

MEM_MA_DATA32

MEM_MA_DATA33

MEM_MA_DATA34

MEM_MA_DATA35

MEM_MA_DATA36

MEM_MA_DATA37

MEM_MA_DATA38

MEM_MA_DATA39

MEM_MA_DATA40

MEM_MA_DATA41

MEM_MA_DATA42

MEM_MA_DATA43

MEM_MA_DATA44

MEM_MA_DATA45

MEM_MA_DATA46

MEM_MA_DATA47

MEM_MA_DATA48

MEM_MA_DATA49

MEM_MA_DATA50

MEM_MA_DATA51

MEM_MA_DATA52

MEM_MA_DATA53

MEM_MA_DATA54

MEM_MA_DATA55

MEM_MA_DATA56

MEM_MA_DATA57

MEM_MA_DATA58

MEM_MA_DATA59

MEM_MA_DATA60

MEM_MA_DATA61

MEM_MA_DATA62

MEM_MA_DATA63

DIMM3

DIMM3

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC_DDR

170

102

68

19

55

NC2

NC1

RC118RC0

NC/TEST

VSS

VSS

VSS

VSS

VSS

VSS

100

103

106

109

112

115

75

VDD51VDD56VDD62VDD72VDD78VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

118

121

124

127

130

133

191

194

VDD

VSS

VSS

136

139

181

VDD

VSS

142

175

VDD

VDDQ

VSS

VSS

145

148

197

VDDQ53VDDQ59VDDQ64VDDQ

VSS

VSS

VSS

VSS

151

154

157

160

163

172

187

184

189

178

VDDQ

VDDQ

VDDQ

VDDQ69VDDQ

VSS

VSS

VSS

VSS

VSS

166

169

198

201

204

67

VDDQ

VSS

207

4

VCC3

VDDQ

VSS

210

VSS

C228 X_C0.1u16Y/4C228 X_C0.1u16Y/4

238

CB042CB143CB248CB349CB4

VDDSPD

VSS

VSS

VSS

VSS

VSS

213

216

219

222

225

3

MEM_MB_DQS_H[7..0]4,6

MEM_MB_DQS_L[7..0]4,6

MEM_MB_DM[7..0]4,6

MEM_MB_ADD[15..0]4,6,8

MEM_MB_DATA[63..0]4,6

161

162

167

168

CB5

CB6

CB7

MEM_MA_DQS_H0

7

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

DQS8#

A10_AP

A16/BA2

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

VSS

VSS

VSS

228

231

234

237

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

WE#

CAS#

RAS#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

SDA

VREF

VSS

MEM_MA_DQS_L0

6

MEM_MA_DQS_H1

16

MEM_MA_DQS_L1

15

MEM_MA_DQS_H2

28

MEM_MA_DQS_L2

27

MEM_MA_DQS_H3

37

MEM_MA_DQS_L3

36

MEM_MA_DQS_H4

84

MEM_MA_DQS_L4

83

MEM_MA_DQS_H5

93

MEM_MA_DQS_L5

92

MEM_MA_DQS_H6

105

MEM_MA_DQS_L6

104

MEM_MA_DQS_H7

114

MEM_MA_DQS_L7

113

46

45

MEM_MA_ADD0

188

A0

MEM_MA_ADD1

183

A1

MEM_MA_ADD2

63

A2

MEM_MA_ADD3

182

A3

MEM_MA_ADD4

61

A4

MEM_MA_ADD5

60

A5

MEM_MA_ADD6

180

A6

MEM_MA_ADD7

58

A7

MEM_MA_ADD8

179

A8

MEM_MA_ADD9

177

A9

MEM_MA_ADD10

70

MEM_MA_ADD11

57

A11

MEM_MA_ADD12

176

A12

MEM_MA_ADD13

196

A13

MEM_MA_ADD14

174

A14

MEM_MA_ADD15

173

A15

BA1

BA0

SCL

SA0

SA1

SA2

DDRII-240_GREEN-RH

DDRII-240_GREEN-RH

MEM_MA_BANK2

54

MEM_MA_BANK1

190

MEM_MA_BANK0

71

MEM_MA_WE_L

73

MEM_MA_CAS_L

74

MEM_MA_RAS_L

192

125

126

134

135

146

147

155

156

202

203

211

212

223

224

232

233

164

165

MEM_MA1_ODT0

195

77

52

171

MEM_MA1_CS_L0

193

MEM_MA1_CS_L1

76

MEM_MA1_CLK_H0

185

MEM_MA1_CLK_L0

186

MEM_MA1_CLK_H1

137

MEM_MA1_CLK_L1

138

MEM_MA1_CLK_H2

220

MEM_MA1_CLK_L2

221

SCL

120

SDA

119

1

X1

X1

239

240

VCC3

101

X2

X2

X3

X3

MEM_MA_DM0

MEM_MA_DM1

MEM_MA_DM2

MEM_MA_DM3

MEM_MA_DM4

MEM_MA_DM5

MEM_MA_DM6

MEM_MA_DM7

MEM_MA_CKE1

C46

C46

C0.1u16Y/4

C0.1u16Y/4

MEM_MA_BANK2 4,6,8

MEM_MA_BANK1 4,6,8

MEM_MA_BANK0 4,6,8

MEM_MA_WE_L 4,6,8

MEM_MA_CAS_L 4,6,8

MEM_MA_RAS_L 4,6,8

MEM_MA1_ODT0 4,8

MEM_MA_CKE1 4,8

MEM_MA1_CS_L0 4,8

MEM_MA1_CS_L1 4,8

MEM_MA1_CLK_H0 4,8

MEM_MA1_CLK_L0 4,8

MEM_MA1_CLK_H1 4,8

MEM_MA1_CLK_L1 4,8

MEM_MA1_CLK_H2 4,8

MEM_MA1_CLK_L2 4,8

SCL 6

SDA 6

VDDR_VREF

SPD. Address = A4h SPD. Address = A6h

MEM_MB_DATA0

MEM_MB_DATA1

MEM_MB_DATA2

MEM_MB_DATA3

MEM_MB_DATA4

MEM_MB_DATA5

MEM_MB_DATA6

MEM_MB_DATA7

MEM_MB_DATA8

MEM_MB_DATA9

MEM_MB_DATA10

MEM_MB_DATA11

MEM_MB_DATA12

MEM_MB_DATA13

MEM_MB_DATA14

MEM_MB_DATA15

MEM_MB_DATA16

MEM_MB_DATA17

MEM_MB_DATA18

MEM_MB_DATA19

MEM_MB_DATA20

MEM_MB_DATA21

MEM_MB_DATA22

MEM_MB_DATA23

MEM_MB_DATA24

MEM_MB_DATA25

MEM_MB_DATA26

MEM_MB_DATA27

MEM_MB_DATA28

MEM_MB_DATA29

MEM_MB_DATA30

MEM_MB_DATA31

MEM_MB_DATA32

MEM_MB_DATA33

MEM_MB_DATA34

MEM_MB_DATA35

MEM_MB_DATA36

MEM_MB_DATA37

MEM_MB_DATA38

MEM_MB_DATA39

MEM_MB_DATA40

MEM_MB_DATA41

MEM_MB_DATA42

MEM_MB_DATA43

MEM_MB_DATA44

MEM_MB_DATA45

MEM_MB_DATA46

MEM_MB_DATA47

MEM_MB_DATA48

MEM_MB_DATA49

MEM_MB_DATA50

MEM_MB_DATA51

MEM_MB_DATA52

MEM_MB_DATA53

MEM_MB_DATA54

MEM_MB_DATA55

MEM_MB_DATA56

MEM_MB_DATA57

MEM_MB_DATA58

MEM_MB_DATA59

MEM_MB_DATA60

MEM_MB_DATA61

MEM_MB_DATA62

MEM_MB_DATA63

DIMM4

DIMM4

3

4

9

10

122

123

128

129

12

13

21

22

131

132

140

141

24

25

30

31

143

144

149

150

33

34

39

40

152

153

158

159

80

81

86

87

199

200

205

206

89

90

95

96

208

209

214

215

98

99

107

108

217

218

226

227

110

111

116

117

229

230

235

236

2

5

8

11

14

17

20

23

26

29

32

35

38

41

44

47

50

65

66

79

82

85

88

91

94

97

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCC_DDR

102

19

55

NC1

RC118RC0

NC/TEST

VSS

VSS

VSS

VSS

100

103

106

109

68

NC2

VDD51VDD56VDD62VDD72VDD78VDD

VSS

VSS

VSS

VSS

112

115

118

121

75

VDD

VSS

VSS

VSS

124

127

130

2

VCC3

C226 X_C0.1u16Y/4C226 X_C0.1u16Y/4

161

162

167

VSS

VSS

222

225

228

168

CB5

CB6

CB7

DQS0

DQS0#

DQS1

DQS1#

DQS2

DQS2#

DQS3

DQS3#

DQS4

DQS4#

DQS5

DQS5#

DQS6

DQS6#

DQS7

DQS7#

DQS8

DQS8#

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13

A14

A15

A16/BA2

BA1

BA0

WE#

CAS#

RAS#

DM0/DQS9

NC/DQS9#

DM1/DQS10

NC/DQS10#

DM2/DQS11

NC/DQS11#

DM3/DQS12

NC/DQS12#

DM4/DQS13

NC/DQS13#

DM5/DQS14

NC/DQS14#

DM6/DQS15

NC/DQS15#

DM7/DQS16

NC/DQS16#

DM8/DQS17

NC/DQS17#

ODT0

ODT1

CKE0

CKE1

CS0#

CS1#

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

SCL

SDA

VREF

X1

SA0

SA1

SA2

X2

X3

VSS

VSS

VSS

VSS

DDRII-240_ORANGE-RH

DDRII-240_ORANGE-RH

231

234

237

7

6

16

15

28

27

37

36

84

83

93

92

105

104

114

113

46

45

188

183

63

182

61

60

180

58

179

177

70

57

176