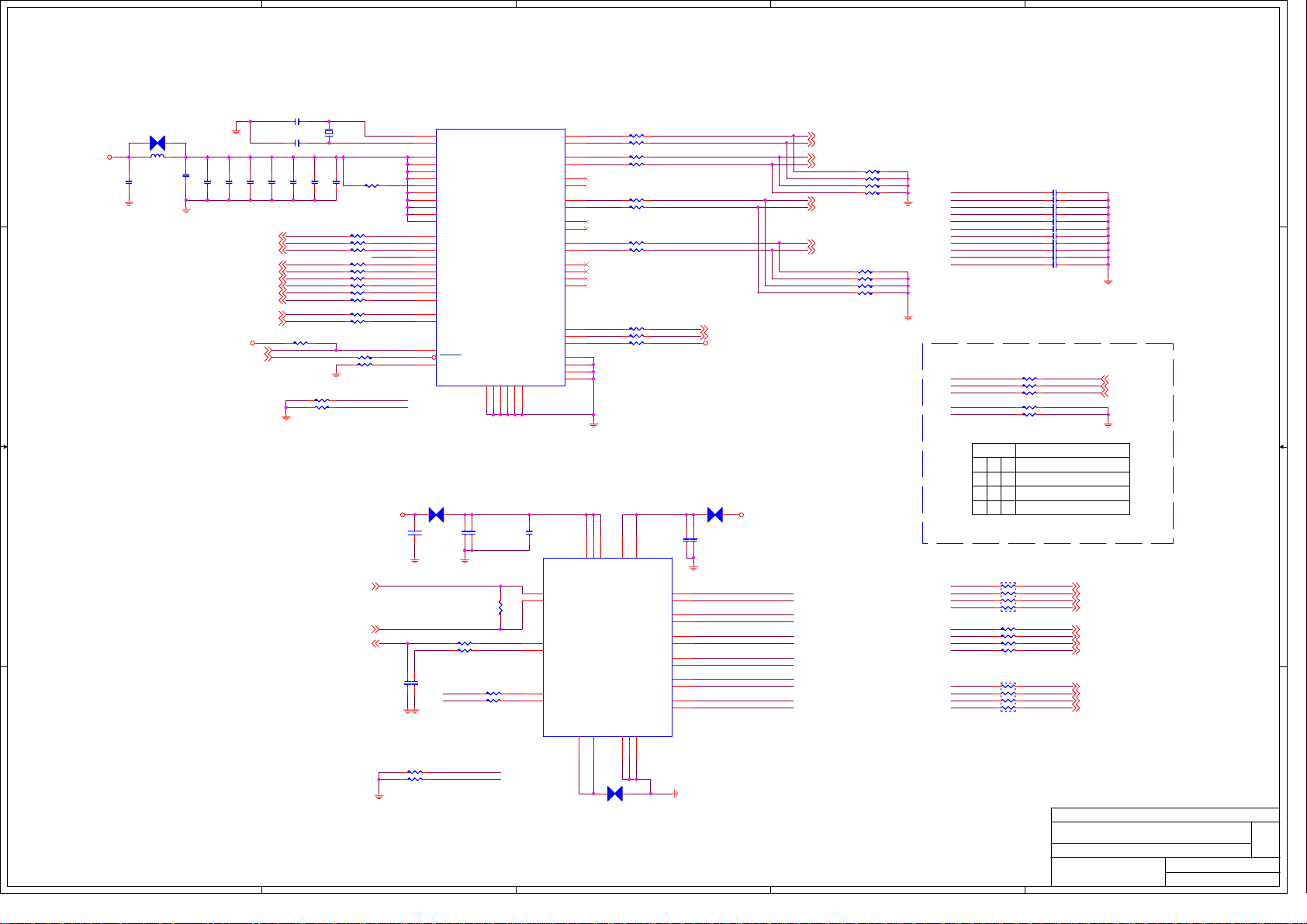

Page 1

5

4

3

2

1

CPU:

Intel LGA775

D D

C C

B B

A A

Page Title

01

02

03

04

05

06

07

08

09

010

011

012

013

014

015

016

017

018

019

020

021

022

023

024

025

026

027

028

029

030

031

032

033

COVER

BLOCK DIAGRAM

PWR map/CLOCK map

GPIO/MEMORY/PCI/HW STRPPING

CLOCK GEN. & Buffer

Intel LGA775 - Signal

Intel LGA775 - Power

Intel LGA775 - Gnd

PT900-1(HOST)

PT900-2(MEM)

PT900-3(GFX)

PT900-4(DISPLAY)

VT8237A-1(USB & PCI)

VT8237A-2(IDE & SATA)

VT8237A-3(VLINK & LAN)

MEM-DDRII SLOT1 & 2

PCI-Express Slot x16 & PCI x1

HD Audio -ALC888

Giga LAN RTL8110SC

IDE & SATA

DVI VT1632

USB-REAR & FRONT

LPC IO-W83627EHG & FWH ROM

KB/MS & FAN & VGA

VRM- Intersil 6312

MS7 ACPI controller

BULK/Decop/Front Pan/ATX CON

Auto BOM manual

HISTORY

5

4

3

System Chipset:

P4M900 (North Bridge)

VT8237A (South Bridge)

On Board Chipset:

BIOS -- LPC ROM

Audio - ALC888

LPC Super I/O -- W83627EHG

Giga LAN -- RealTek RTL8110SC

CLOCK --ICS953002+ICS9P936AFLF

DVI VIA VT1632

Main Memory:

single-channel --DDRII*2

Expansion Slots:

PCI- 64 Slot (Only for Riser Card use)

(PCI Express X16 * 1 PCI 2.3Slot * 1)

PWM(VRM11/FMB 05B):

Intersil 6312

I/O

IDE *1

SATA Standard ver : 2 ; Lite ver : 1

USB 2.0 (Rear X 4,Front X2 ,1 for Card Reader Module )

DVI-I

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

COVER

COVER

COVER

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

129

129

129

Rev

Rev

Rev

0A

0A

0A

of

of

of

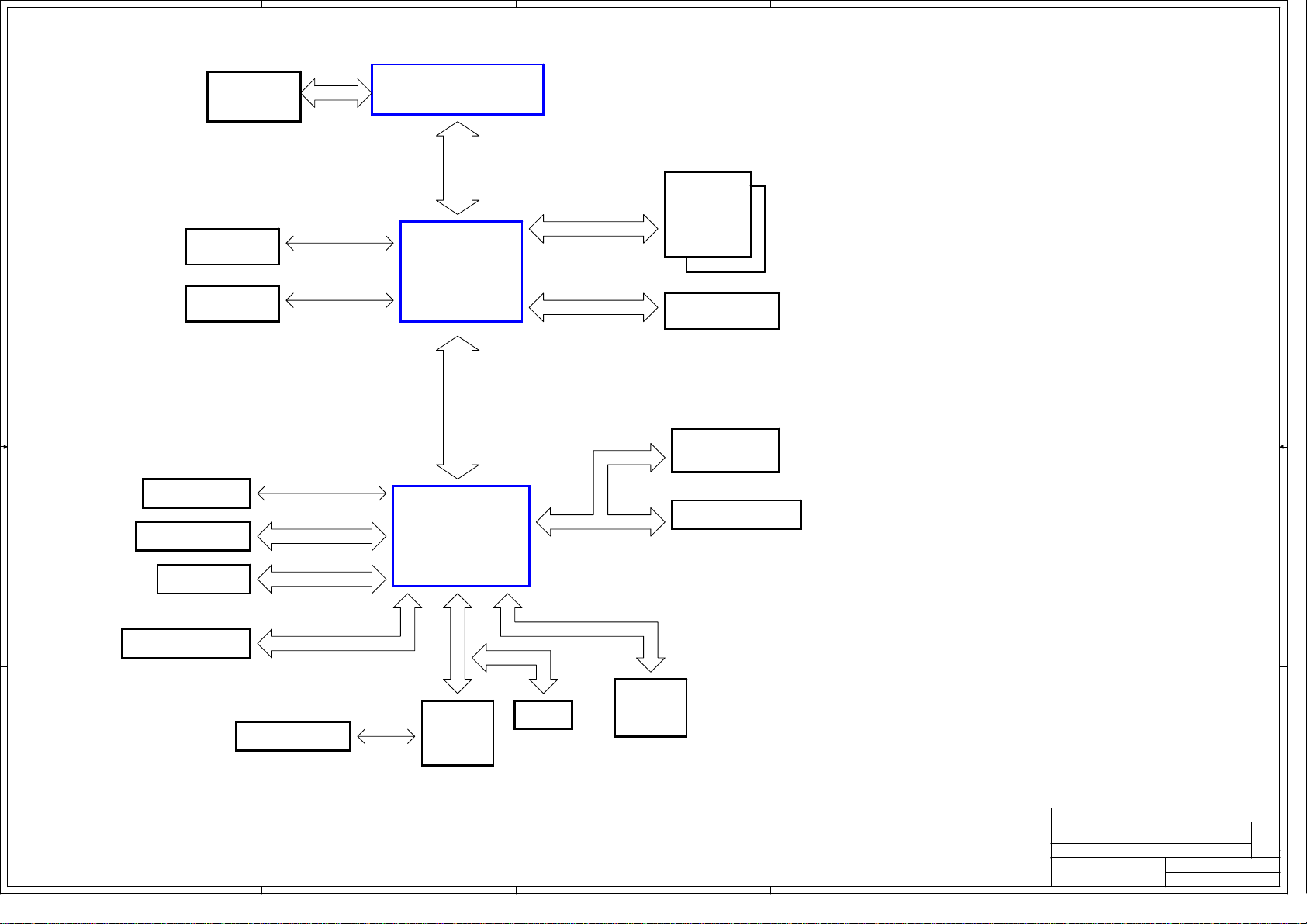

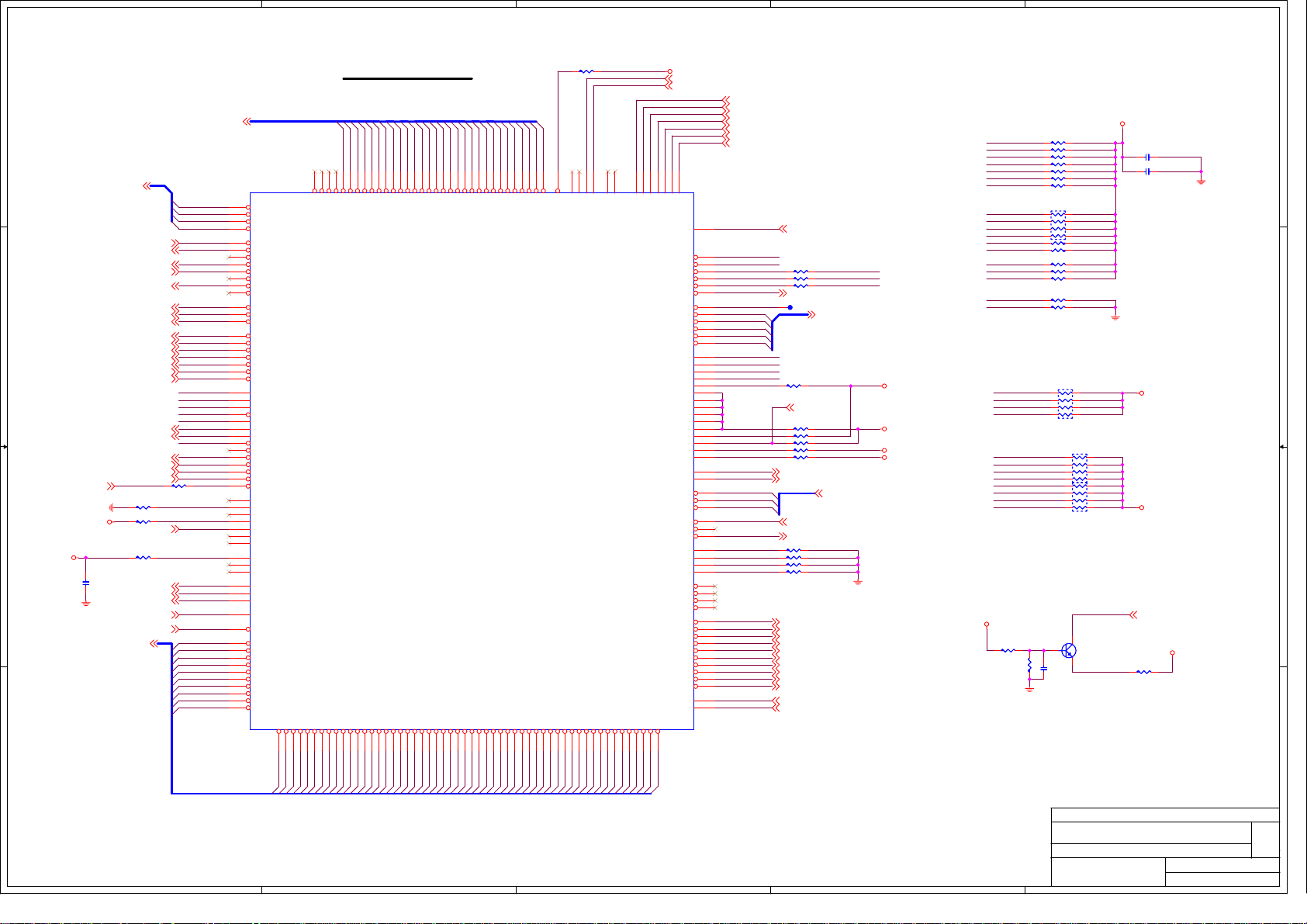

Page 2

5

4

3

2

1

VRM 11

Intersil 6312

D D

3-Phase PWM

Intel LGA-775

Processor

1066/800/533 MHz

FSB

DDR2

DDR2 400/533/667 MHz

CRT

DVI

P4M900

NB

single channel

VT 1632

C C

1GB/sec

Ultra V-Link

DIMM X 2

Modules

PCI Express

X 16

Giga LAN

RTL8110S

PS2 KB/MS

IDE Primary

B B

Ultra DMA-133/100/66

VT8237A

SB

PCI BUS

PCI SLOT 1

SATASATA

USB2.0 4+2 PORT

USB 2.0

LPC

HD

Serial Port

A A

5

4

I/O

Super

FWH

Audio

3

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

229

229

229

Rev

Rev

Rev

0A

0A

0A

of

of

of

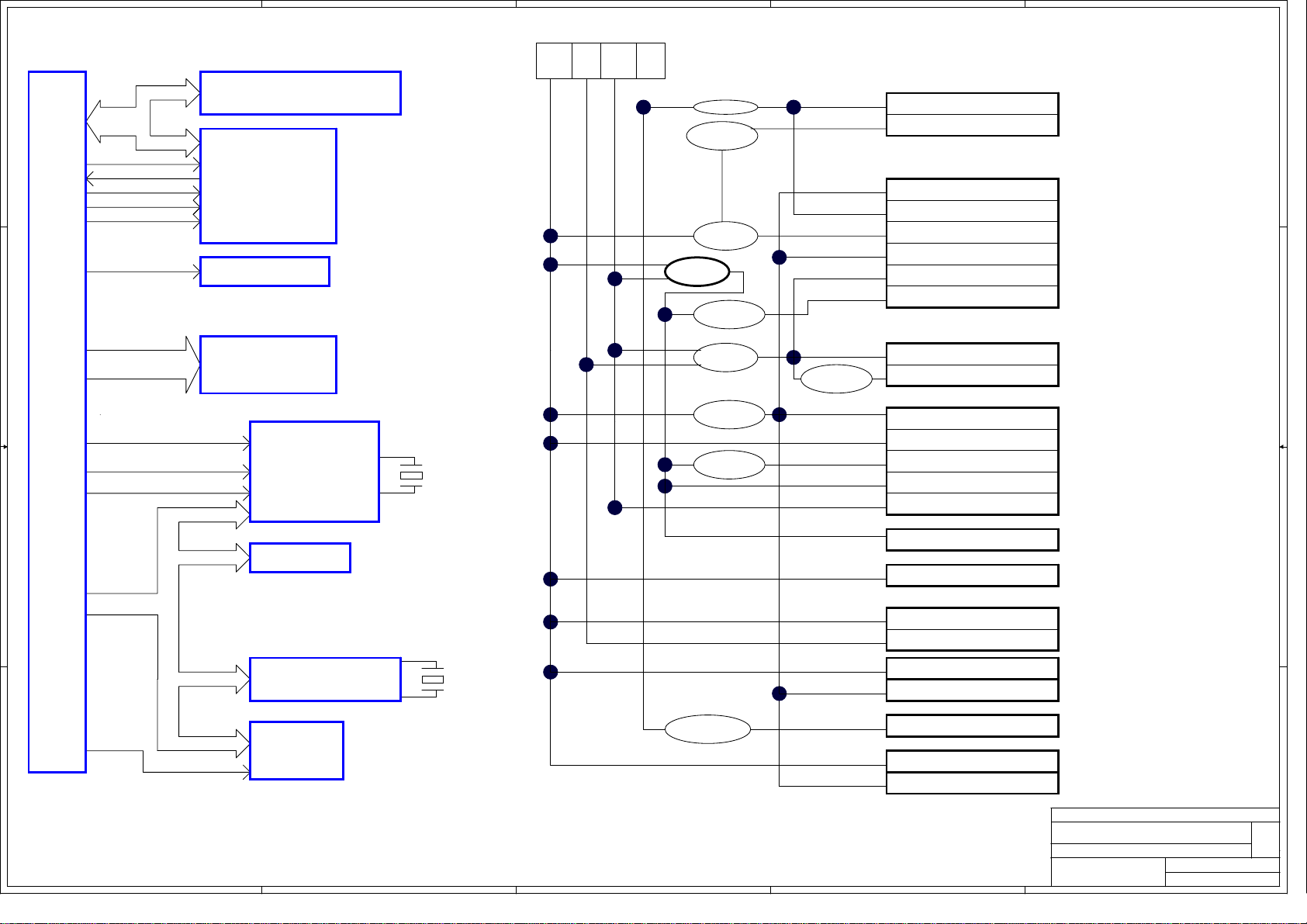

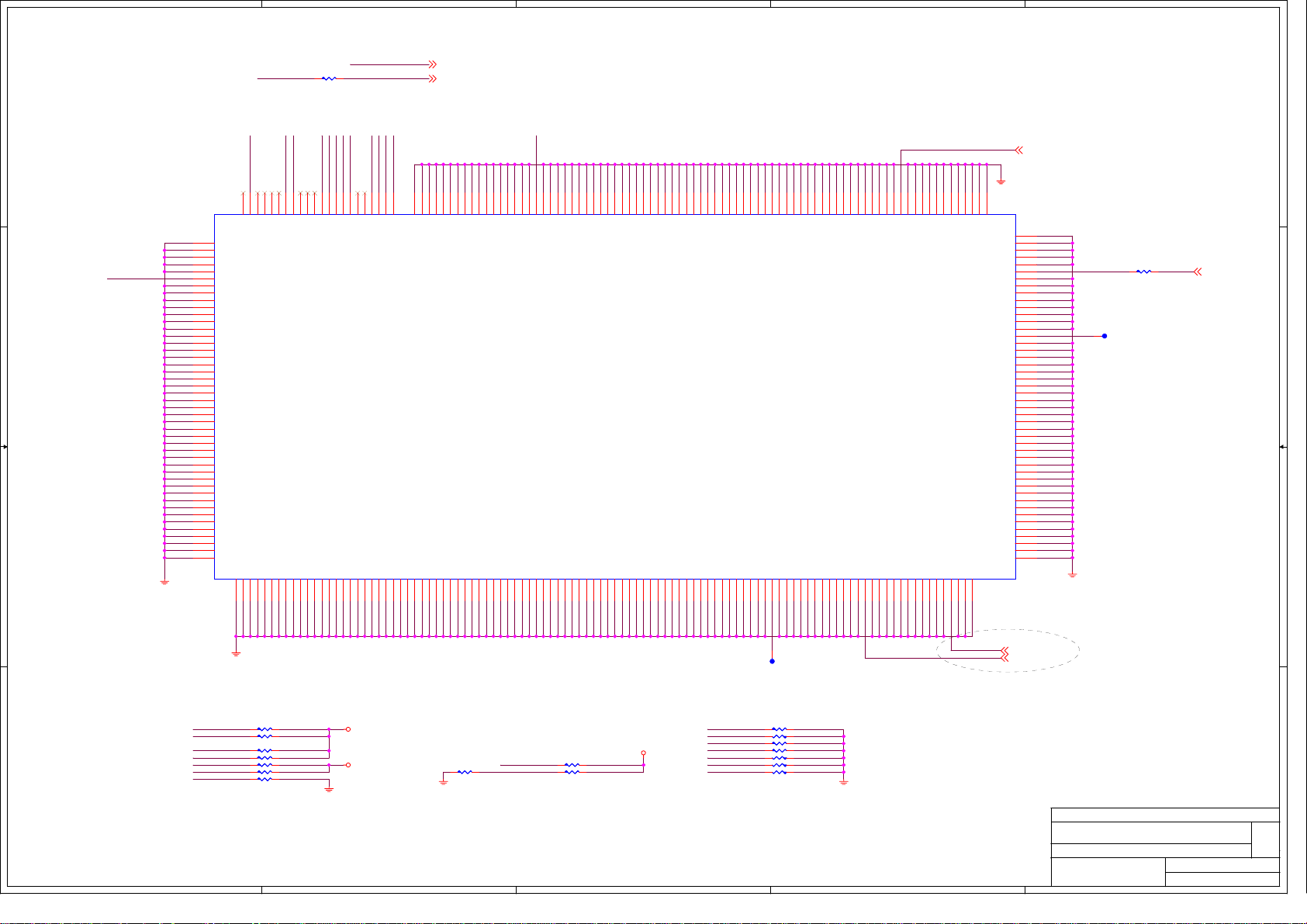

Page 3

5

4

3

2

1

P4M900 PLATFORM CLOCK GENERATOR MAP

P4M890 PLATFORM POWER DELIVERY MAP

3.3V 5V 5VSB 12V

Intel LGA775 Processor

D D

CPU HOST

CLK

66MHZ

DCLKO

DCLKI

PCI-E CLK

GUICLK-14.318MHZ

PCI-E CLK

North Bridge

P4M900

PCI-E x16 Slot 1

VRM PROCESSOR VCCP

1.2V VREG

5.3A

1.5V VREG

7A

3VSB VREG

PROCESSOR 1.2V

NORTH BRIDGE VCC_PCIX

NORTH BRIDGE VCCP

NORTH BRIDGE NBVCC15

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEM

1.8V VCC_DDR

NORTH BRIDGE RESUME 1.5V_SB

1.5VSB

VREG

C C

CLOCK GENERATOR

MEM CLK

14.318MHZ

66MHZ

48MHZ

PCI CLK

DDRII Dimm Slot1,2

Sorth Bridge

VT8237A

25MHZ

DDRII 1.8 VREG

15A

2.5V VREG

3A

2.5VSB

VREG

VTT 0.9V VREG

2A

DDR DIMM1 / DIMM2 1.8V

DDR VTT 0.9V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

B B

PCI CLK

PCI Slot 1

BIOS 3V

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

LAN-PHY VCC3_SB

Giga LAN

RTL8110S

Winbond

25MHZ

HD CODEC VDD5

VREG

48MHZ

PCI CLK

PCI CLK

83627EHG

A A

5

4

3

CLK 3.3V

DDR BUFFER +2.5V

HD CODEC VDD5

SATA RAID 3.3V

SATA RAID +2.5V

2

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

PWR map/CLOCK map

PWR map/CLOCK map

PWR map/CLOCK map

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

329

329

329

Rev

Rev

Rev

0A

0A

0A

of

of

of

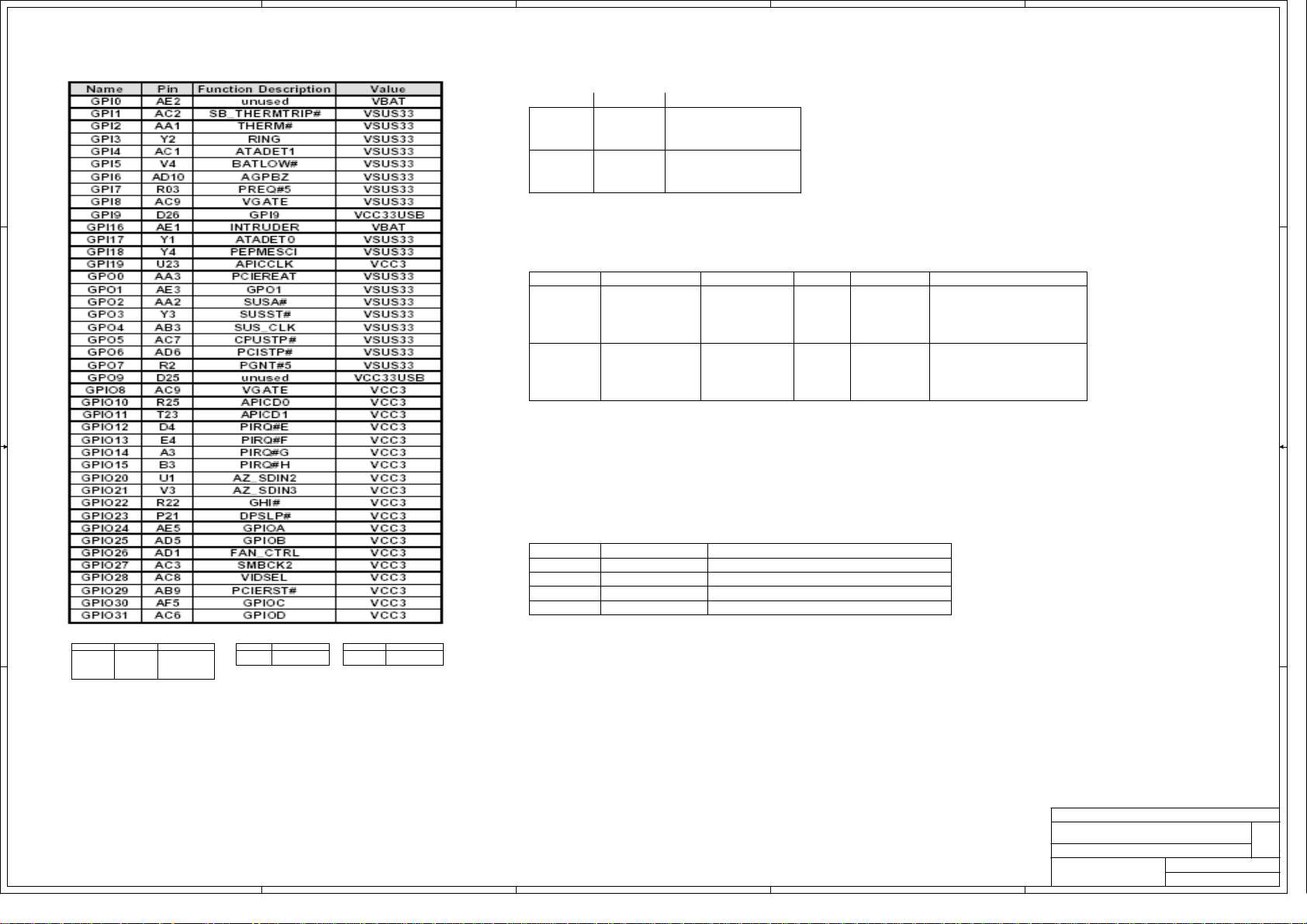

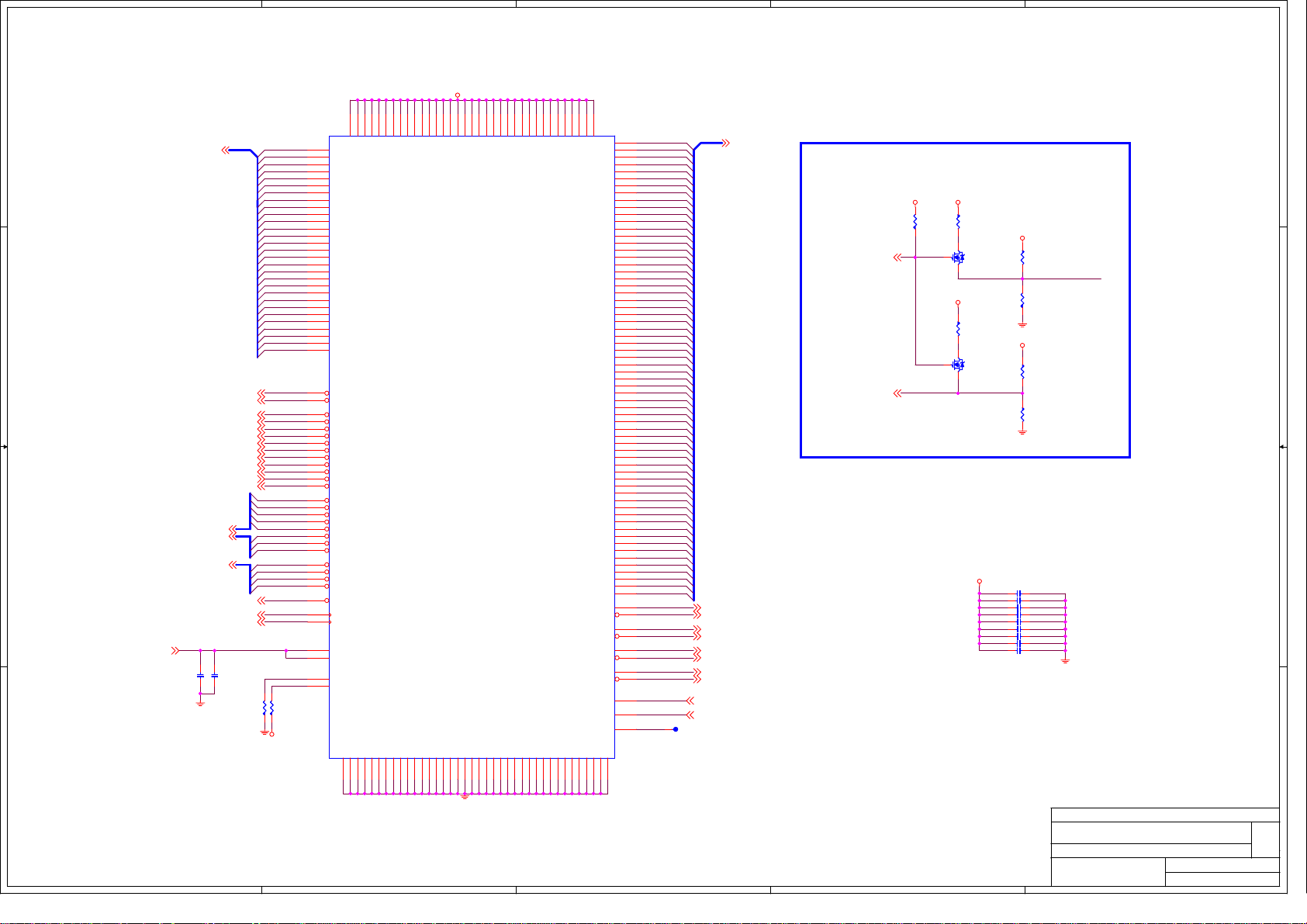

Page 4

5

4

3

2

1

SB-VT8237A

DDR DIMM Config.

DEVICE

D D

DIMM 1 MDCLKA0/A#0

DIMM 2

1010000B

1010001B

CLOCKADDRESS

MDCLKA1/A#1

MDCLKA2/A#2

MDCLKB0/B#0

MDCLKB1/B#1

MDCLKB2/B#2

PCI Config.

DEVICE

IDSEL

CLOCKREQ#/GNT#

CLK GEN PIN OUTMCP1 INT Pin

PIRQ#A

PCI Slot 1

C C

Giga Lan

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#E

PREQ#0

PGNT#0

PREQ#2

PGNT#2

AD20

AD21

PCICLK1

LAN_PCLK

12 (PCI_CLK1)

13 (PCI_CLK2)

PCI RESET DEVICE

B B

Signals

PCIRST#

Source

SB

MS7

GPIOA

0

0

1

1

GPIOC

0

1 133MHz

0

1

HOST CLOCK

100MHz

200MHz

AUTO MODE

GPIOB IOQ Depth

1

1 Level 1

GPIOD

08 Level0

GTL pullup

Enable

Disable

PCIRST#2

HDRST#

MS7

MS7

Target

MS7

NB & TV-OUT & SPIO & BIOSPCIRST#1

PCI slot 1 & PCIE X 16

Primary

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

General Purpose Spec

General Purpose Spec

General Purpose Spec

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

429

429

429

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 5

5

4

3

2

1

D D

VCC3

C0.1U16Y0402

C0.1U16Y0402

C C

C2

C2

CP1

CP1

X_COPPER

X_COPPER

FB1

FB1

X_80L3_100_0805

X_80L3_100_0805

C10

C10

C4.7U6.3X5

C4.7U6.3X5

C5

C3

C4

C0.1U16Y0402C5C0.1U16Y0402

C0.1U16Y0402C3C0.1U16Y0402

C0.1U16Y0402C4C0.1U16Y0402

GUICK12

SB14MHZ14

PCICLK117

LAN_PCLK19

SPCLK15

FWH_PCLK23

SIO_PCLK23

USBCLK13

SIO48M23

SMBCK14,16,17,19,24,26

SMBDT14,16,17,19,24,26

VCC3

VRM_PWGD25

FP_RST#26,27

C56P50NC1 C56P50NC1

C56P50NC9 C56P50NC9

C11

C11

C6

C7

C0.1U16Y0402

C0.1U16Y0402

C0.1U16Y0402C6C0.1U16Y0402

C0.1U16Y0402C7C0.1U16Y0402

GUICK

SB14MHZ

PCICLK1

LAN_PCLK

SPCLK

FWH_PCLK

SIO_PCLK

USBCLK MODE

R32 1KR/0402R32 1KR/0402

R39 1KR/0402R39 1KR/0402

R40 4.7KR0402R40 4.7KR0402

Y114.318MHZ32P_D Y114.318MHZ32P_D

VCC3V

VCC3V

C8

R3 10KR/4R3 10KR/4

C0.1U16Y0402C8C0.1U16Y0402

R12 33R/4R12 33R/4

R13 33R/4R13 33R/4

R17 33R/4R17 33R/4

R18 33R/4R18 33R/4

R19 33R/4R19 33R/4

R21 33R/4R21 33R/4

R23 33R/4R23 33R/4

R25 33R/4R25 33R/4

R27 33R/4R27 33R/4

R28 33R/4R28 33R/4

R29 33R/4R29 33R/4

R34 0R0402R34 0R0402

R35 475R1%04R35 475R1%04

FS0

FS1

FS2

FS3

SEL24/48SIO48M

MODE

SEL24/48

U1

U1

6

X1

7

X2

1

VDDA

3

VDDREF

10

VDDPCI

16

VDDPCI

20

*Turbo

22

VDD48

26

VDD3V66

39

VDDPCIE

45

VDDPCIE

49

VDDCPU

4

**FSL0/REF0

5

FSL1/REF1

11

**FSL2/PCI0

12

**FS3/~PCI1

13

PCI2

14

PCI3

17

PCI4

18

PCI5

23

**Mode/48MHz

24

*Sel24_48#/24_48MHz

31

SCLK

48

SDATA

9

VTTPWGD/PD#

21

RESET

55

IREF

ICS953002D

ICS953002D

VER:D

CPUT0

CPUC0

CPUT1

CPUC1

CPUT2_ITP/PCIEXT0

CPUC2_ITP/PCIEXC0

PCIEXT1

PCIEXC1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

PCIEXT4

PCIEXC4

PCIEXT5/CPU_STOP#*

PCIEXC5/PCI_PCIEX_STOP#*

3V66_0

**FS4/3V66_1

**ITP_EN/3V66_2

GND

GNDREF

GNDPCI

GNDPCI

GND48

GNDPCIE

GND3V66

GNDCPU

GND56GNDPCIE

25

40

30

52

32

R4 33R/4R4 33R/4

54

R1 33R/4R1 33R/4

53

R5 33R/4R5 33R/4

51

R2 33R/4R2 33R/4

50

47

46

R10 33R/4R10 33R/4

44

R11 33R/4R11 33R/4

43

42

41

R14 33R/4R14 33R/4

38

R16 33R/4R16 33R/4

37

36

35

34

33

R30 33R/4R30 33R/4

29

FS4

R31 33R/4R31 33R/4

28

ITP

R33 1KR/0402R33 1KR/0402

27

2

8

19

15

CPUCLK

CPUCLK#

NBHCLK

NBHCLK#

PECLK1

PECLK1#

PECLK_NB

PECLK_NB#

VCLK

GCLK_NB

VCLK 15

GCLK_NB 11

VCC3

CPUCLK 6

CPUCLK# 6

NBHCLK 9

NBHCLK# 9

R6 51R1%/4R6 51R1%/4

R7 51R1%/4R7 51R1%/4

R8 51R1%/4R8 51R1%/4

R9 51R1%/4R9 51R1%/4

PECLK1 17

PECLK1# 17

PECLK_NB 11

PECLK_NB# 11

R20 51R1%/4R20 51R1%/4

R22 51R1%/4R22 51R1%/4

R24 51R1%/4R24 51R1%/4

R26 51R1%/4R26 51R1%/4

VCLK

GCLK_NB

FWH_PCLK

USBCLK

SIO48M

LAN_PCLK

PCICLK1

SIO_PCLK

SPCLK

GUICK

SB14MHZ

CLOCK STRAPPING

FS0

FS1

FS2

FS3

FS4

R36 10KRR36 10KR

R37 10KRR37 10KR

R38 10KRR38 10KR

R41 10KRR41 10KR

R42 10KRR42 10KR

C12 C22P50N0402C12 C22P50N0402

C13 X_10P50N04C13 X_10P50N04

C14 10P50N04C14 10P50N04

C15 X_10P50N04C15 X_10P50N04

C16 X_10P50N04C16 X_10P50N04

C18 10P50N04C18 10P50N04

C19 10P50N04C19 10P50N04

C20 10P50N04C20 10P50N04

C21 10P50N04C21 10P50N04

C22 X_10P50N04C22 X_10P50N04

C23 X_10P50N04C23 X_10P50N04

BSEL0

BSEL1

BSEL2

BSEL0 6,7

BSEL1 6,7

BSEL2 6,7

1=24MHz mode,0=48MHz mode

BSEL

1

CP2

CP2

X_COPPER

X_COPPER

C25

C25

C26

100R1%0402

100R1%0402

R46 22R/4R46 22R/4

R48 22R/4R48 22R/4

SMBDT

R50 33R/4R50 33R/4

SMBCK

R51 33R/4R51 33R/4

MCLKOT

MCLKOC

C26

C0.1U16Y0402

C0.1U16Y0402

R43

R43

C24

C24

C0.1U16Y0402

C4.7U10Y0805

C4.7U10Y0805

B B

MCLKOT10

MCLKOC10

MCLKIT10

X_C5P50N0402

X_C5P50N0402

A A

5

C0.1U16Y0402

MCLKOT

MCLKOC

MCLKIT

C31

C31

C5P50N0402

C5P50N0402

C30

C30

R52 X_4.7KR/4R52 X_4.7KR/4

R53 X_4.7KR/4R53 X_4.7KR/4

4

VDD1.8

C27

C27

C0.1U16Y0402

C0.1U16Y0402

U2

U2

3

BUF_INT

4

BUF_INC

11

FB_OUTT

12

FB_OUTC

16

SDATA

15

SCLK

ICS9P936_SSOP28

ICS9P936_SSOP28

10

21

27

VDD2.5/1.8

VDD2.5/1.8

VDD2.5/1.8

AGND

AGND

2

25

AGNDC

CP4 X_COPPERCP4 X_COPPER

26

AVDD2.5

GND

GND

9

22

C0.1U16Y0402

C0.1U16Y0402

1

AVDD2.5

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

GND

28

3

C28

C28

5

6

7

8

13

14

18

17

20

19

24

23

CP3

CP3

X_COPPER

X_COPPER

C29

C29

C0.1U16Y0402

C0.1U16Y0402

+2.5VVCC_DDR

DCLKA0

DCLKA#0

DCLKA2

DCLKA#2

DCLKA1

DCLKA#1

DCLKB1

DCLKB#1

DCLKB0

DCLKB#0

DCLKB2

DCLKB#2

2

0

0 0 133 MHZ (533)

RN1

DCLKA2

DCLKA#2

DCLKA1

DCLKA#1

DCLKA0

DCLKA#0

DCLKB#1

DCLKB1

DCLKB#0

DCLKB0

DCLKB#2

DCLKB2

RN1

1

3

5

7

8P4R-10R0402

8P4R-10R0402

R44 10R/4R44 10R/4

R45 10R/4R45 10R/4

R47 10R/4R47 10R/4

R49 10R/4R49 10R/4

RN2

RN2

1

3

5

7

8P4R-10R0402

8P4R-10R0402

TABLE

02

FSB FREQUENCY

267 MHZ (1067)000

01 200 MHZ (800)

1

2

4

6

8

2

4

6

8

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MDCLKA2 16

MDCLKA#2 16

MDCLKA1 16

MDCLKA#1 16

MDCLKA0 16

MDCLKA#0 16

MDCLKB#1 16

MDCLKB1 16

MDCLKB#0 16

MDCLKB0 16

MDCLKB#2 16

MDCLKB2 16

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

CLOCK GEN. & Buffer

CLOCK GEN. & Buffer

CLOCK GEN. & Buffer

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

529

529

529

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 6

5

4

3

2

1

HA#6

HD#19

HA#5

HA#4

HD#17

HD#18

HA#3

L5

HD#15

HD#16

D11

R54 62R/4R54 62R/4

AC2

AN3

AN4

DBR#

RSVD

D14#

D13#

D12#D8D11#

B12

C12

C11

HD#11

HD#12

HD#13

HD#14

AN6

AN5

RSVD

VSS_SENSE

VCC_SENSE

D10#

D9#

B10

A11

A10

HD#8

HD#9

HD#10

AJ3

AK3

ITP_CLK1

ITP_CLK0

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

HD#5

HD#6

HD#7

CPU SIGNAL BLOCK

D D

HDBI#[0..3]9

CPU_GTLREF27

HIERR#7

FERR#7,15

STPCLK#15

HINIT#15

HDBSY#9

HDRDY#9

HTRDY#9

C C

SLP#9,15

VTT_OUT_LEFT

VTT_OUT_RIGHT

B B

C34

C34

X_C0.1U16Y0402

X_C0.1U16Y0402

A A

HADS#9

HLOCK#9

HBNR#9

HITM#9

HBPRI#9

HDEFER#9

TMP_CPUTIN23,24

TMP_GND23,24

PROCHOT#7

IGNNE#15

SMI#15

A20M#15

SLP#

R75 1KR/0402R75 1KR/0402

R76 62R/4R76 62R/4

CPU_GTLREF37

R78 1KR/0402R78 1KR/0402

BSEL05,7

BSEL15,7

BSEL25,7

CPU_GD7,26

CPURST#7,9

HD#[0..63]9

HIT#9

R74 0R0402R74 0R0402

HA#[3..31]9

HDBI#0

HDBI#1

HDBI#2

HDBI#3

STPCLK#

HINIT#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

H_TESTHI13

TEST_N5

TEST_C9

CPU_BOOT

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

CPU1A

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

HD#53

D53#

C14

HD#52

D52#

C15

HD#51

D51#

A14

HD#50

D50#

D17

HD#49

AJ6

D49#

D20

HD#48

AJ5

A35#

D48#

G22

HD#47

AH5

A34#

D47#

D22

HD#46

AH4

A33#

D46#

E22

HD#45

HA#31

AG5

A32#

D45#

G21

HD#44

HA#30

AG4

A31#

D44#

F21

HD#43

HA#29

AG6

A30#

D43#

E21

HD#42

HA#28

AF4

A29#

D42#

F20

HD#41

HA#27

AF5

A28#

D41#

E19

HD#40

HA#26

AB4

A27#

D40#

E18

HD#39

HA#25

AC5

A26#

D39#

F18

HD#38

HA#24

AB5

A25#

D38#

F17

HD#37

HA#23

AA5

A24#

D37#

G17

HD#36

HA#22

AD6

A23#

D36#

G18

HD#35

HA#21

AA4

A22#

D35#

E16

HD#34

HA#20

A21#

D34#

E15

HD#33

HA#18

HA#19

HA#17

AB6

A20#Y4A19#Y6A18#W6A17#

D33#

D32#

D31#

D30#

F15

G16

G15

HD#30

HD#31

HD#32

HA#12

HA#11

HA#16

HA#13

HA#14

HA#15

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

E13

D13

G14

G13

HD#25

HD#26

HD#24

HD#27

HD#28

HD#29

HA#10

HA#8

HA#7

HA#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

F11

E10

D10

HD#20

HD#21

HD#22

HD#23

HD#4

VID6

AM5

HD#3

VID5

AL4

VID6#

HD#2

VID4

VID3

AK4

AL6

VID5#

VID4#

TESTHI12

TESTHI11

TESTHI10

LINT1/NMI

LINT0/INTR

B4

HD#0

HD#1

VID3#

GTLREF0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

VTT_OUT_LEFT

VCC_VRM_SENSE 25

VSS_VRM_SENSE 25

VID2

VID0

VID1

AM3

AL5

AM2

VID2#

VID1#

VID0#

H1

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

G5

PCREQ#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

P1

H5

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

RSVD

G6

RSVD

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

ZIF-SOCK775-15u

ZIF-SOCK775-15u

VID6 25

VID5 25

VID4 25

VID3 25

VID2 25

VID1 25

VID0 25

CPU_GTLREF0

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

FORCEPH

RSVD_G6

HRS#2

HRS#1

HRS#0

HBR#0

H_COMP3

H_COMP2

H_COMP1

H_COMP0

NMI_SB

INTR

CPU_GTLREF0 7

R62 X_0R0402R62 X_0R0402

R63 X_0R0402R63 X_0R0402

R65 X_0R0402R65 X_0R0402

H_BPM#0 8

T1T1

HREQ#[0..4] 9

R68 62R/4R68 62R/4

H_TESTHI0 9

R69 62R/4R69 62R/4

R70 62R/4R70 62R/4

R71 62R/4R71 62R/4

R72 130R1%0402R72 130R1%0402

R73 X_62R/4R73 X_62R/4

CPUCLK# 5

CPUCLK 5

HRS#[0..2] 9

-HAP0 9

HBR#0 7,9

R77 60.4R1%0402R77 60.4R1%0402

R79 60.4R1%0402R79 60.4R1%0402

R80 60.4R1%0402R80 60.4R1%0402

R81 60.4R1%0402R81 60.4R1%0402

HADSTB#1 9

HADSTB#0 9

HDSTBP#3 9

HDSTBP#2 9

HDSTBP#1 9

HDSTBP#0 9

HDSTBN#3 9

HDSTBN#2 9

HDSTBN#1 9

HDSTBN#0 9

NMI_SB 15

INTR 15

H_TESTHI8

H_TESTHI9

TEST_C9

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_RIGHT

VID1

VID2

VID3

VID4

VID0

VID5

VID6

H_BPM#1

H_BPM#0

H_BPM#5

H_BPM#3

H_BPM#4

H_BPM#2

H_TDO

H_TDI

H_TMS

H_TCK

H_TRST#

R55 680R04R55 680R04

R56 680R04R56 680R04

R57 680R04R57 680R04

R58 680R04R58 680R04

R59 680R04R59 680R04

R60 680R04R60 680R04

R61 680R04R61 680R04

RN3 8P4R-51R/4RN3 8P4R-51R/4

1

2

3

4

5

6

7

8

R143 51R1%0402R143 51R1%0402

R145 51R1%0402R145 51R1%0402

R257 62R/4R257 62R/4

R262 62R/4R262 62R/4

R64 62R/4R64 62R/4

R66 62R/4R66 62R/4

R67 62R/4R67 62R/4

C32 C0.1U16Y0402C32 C0.1U16Y0402

C33 C0.1U16Y0402C33 C0.1U16Y0402

PLACE BPM TERMINATION NEAR CPU

RN5

H_TESTHI11

H_TESTHI12

H_TESTHI9

H_TESTHI10

SMI#

HINIT#

IGNNE#

STPCLK#

H_TESTHI13

NMI_SB

A20M#

INTR

RN5

1

2

3

4

5

6

7

8

8P4R-62R/4

8P4R-62R/4

RN6 8P4R-62R/4RN6 8P4R-62R/4

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN7 8P4R-62R/4RN7 8P4R-62R/4

VTT_OUT_LEFT

VTT_OUT_LEFT

THE VT8327A IS OD PIN NEED TO PULL HIGH

V_FSB_VTT

R82 2.7KR0402R82 2.7KR0402

R83

R83

X_10KR04

X_10KR04

SB_THERMTRIP#

Q1

Q1

N-PMBS3904_SOT23

N-PMBS3904_SOT23

C35

C35

THERMTRIP#

X_C0.1U16Y0402

X_C0.1U16Y0402

SB_THERMTRIP# 14

V_FSB_VTT

R84 62R/4R84 62R/4

AP 339G

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Intel LGA775 - Signal

Intel LGA775 - Signal

Intel LGA775 - Signal

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

629

629

629

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 7

5

VCCP

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

CPU1B

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AD8

AC8

AB8

AA8

VCCP

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

W29

W28

W27

VCCP

D D

C C

AG27

VCC

VCC

W26

AG28

VCC

VCC

W25

AG29

VCC

VCC

W24

AG30

VCC

W23

AG8

VCC

AG9

VCC

VCCU8VCCV8VCC

4

AH11

VCC

VCC

U30

AH12

VCC

VCC

U29

AH14

VCC

VCC

U28

AH15

VCC

VCC

U27

AH18

VCC

VCC

U26

AH19

VCC

VCC

U25

AH21

VCC

VCC

U24

AH22

VCC

U23

AH25

VCC

VCCT8VCC

AH26

VCC

VCC

T30

AH27

VCC

VCC

T29

AH28

VCC

VCC

T28

AH29

VCC

VCC

T27

AH30

VCC

VCC

T26

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

AJ11

T23

VCC

AJ12

VCC

AJ14

VCC

AJ15

VCC

VCCN8VCCP8VCCR8VCC

AJ18

VCC

VCC

N30

AJ19

N29

VCC

VCC

AJ21

VCC

VCC

N28

AJ22

N27

VCC

VCC

AJ25

N26

VCC

VCC

AJ26

N25

VCC

VCC

3

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

N23

N24

M27

M28

M29

M30

K30

M23

M24

M25

M26

AM8

AM9

AN11

AN12

VCC

VCC

VCC

VCC

VCC

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

J10

J11

AN8

AN9

AN14

VCC

VCC

AN30

AN15

VCC

VCC

AN29

2

AN18

AN26

VCC

VCC

AN19

VCC

VCC

AN25

AN21

AN22

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

HS11HS22HS33HS4

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

4

H_VCCA

A23

H_VSSA

B23

H_VCCPLL

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

AA1

J1

VTT_SEL

R85 X_1KR/0402R85 X_1KR/0402

F27

F29

ZIF-SOCK775-15u

ZIF-SOCK775-15u

V_FSB_VTT

TEJ/PSC

0

1

RSVD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC3

1

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_OUT_RIGHT

B B

VTT_OUT_RIGHT

VTT_OUT_LEFT

R91 124R1%04R91 124R1%04

R97 124R1%04R97 124R1%04

R100 X_124R1%04R100 X_124R1%04

R95

R95

210R1%04

210R1%04

R99

R99

210R1%04

210R1%04

R102

R102

X_210R1%04

X_210R1%04

R92 10R/4R92 10R/4

C36

C36

C1U16Y

C1U16Y

R98 10R/4R98 10R/4

C40

C40

C1U16Y

C1U16Y

R101 X_10R/4R101 X_10R/4

C47

C47

X_C1U16Y

X_C1U16Y

CPU_GTLREF0

C37

C37

C220P50N04

C220P50N04

CPU_GTLREF1

C41

C41

C220P50N04

C220P50N04

CPU_GTLREF2

C49

C49

X_C220P50N04

X_C220P50N04

CPU_GTLREF1 8

CPU_GTLREF2 6

V_FSB_VTT

V_FSB_VTT

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

CHECK CPU

R86 120R/4R86 120R/4

R87 100R/4R87 100R/4

R88 62R/4R88 62R/4

R89 62R/4R89 62R/4

R90 62R/4R90 62R/4

R93 62R/4R93 62R/4

RN8

RN8

1

3

5

7

8P4R-470R/4

8P4R-470R/4

L1 X_10U100m_0805L1 X_10U100m_0805

CP5

CP5

X_COPPER

X_COPPER

PROCHOT#

CPU_GD

HBR#0

CPURST#

FERR#

HIERR#

2

BSEL2

4

BSEL1

6

BSEL0

8

C43

C43

10U10Y/8

10U10Y/8

PROCHOT# 6

CPU_GD 6,26

HBR#0 6,9

CPURST# 6,9

FERR# 6,15

HIERR# 6CPU_GTLREF0 6

BSEL2 5,6

BSEL1 5,6

BSEL0 5,6

H_VCCA

C44

C44

X_C1U16Y

X_C1U16Y

H_VSSA

CHECK CURRENT

R632

R632

1.6V

100R1%0603

100R1%0603

130mA

1.5V

V_FSB_VTT

VIA AP407

R633

R633

1.5KR1%0603

1.5KR1%0603

R94 0R0402R94 0R0402

R96 X_0R0402R96 X_0R0402

V_FSB_VTT

C42 C0.1U16Y0402C42 C0.1U16Y0402

C45 C1U16YC45 C1U16Y

C46 10U10Y/8C46 10U10Y/8

C48 X_10U10Y/8C48 X_10U10Y/8

C38

C38

10U10Y/8

10U10Y/8

H_VCCPLL

C39

C39

C0.1U16Y0402

C0.1U16Y0402

CAPS FOR FSB GENERIC

A A

V_FSB_VTT

R103 X_124R1%04R103 X_124R1%04

5

R106

R106

X_210R1%04

X_210R1%04

R104 X_10R/4R104 X_10R/4

C50

C50

X_C1U16Y

X_C1U16Y

CPU_GTLREF3

C51

C51

X_C220P50N04

X_C220P50N04

CPU_GTLREF3 6

4

VCC5_SB

R107

R107

1KR/0402

1KR/0402

VID_GD#26

R108 1KR/0402R108 1KR/0402

VTT_OUT_RIGHT

3

R105

R105

1.25V VTT_PWRGOOD

680R/4

680R/4

VTT_PWG

Q2

Q2

N-PMBS3904_SOT23

N-PMBS3904_SOT23

VTT_PWG 25

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Intel LGA775 - Power

Intel LGA775 - Power

Intel LGA775 - Power

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

2

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

729

729

729

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 8

5

4

3

2

1

CPU_GTLREF1

COMP8

B13

AF27

VSS

CPU_GTLREF1

H2

AF28

COMP4

J2

GTLVREF1

VSS

AF29

TEST_J3

RSVDJ3RSVDN4RSVD

COMP4

VSS

VSS

AF3

AF30

GTLVREF_NB

COMP5

T2

P5

COMP5

VSS

VSS

VSS

AF6

AF7

MSID0

MSID1

W1

MSID1V1MSID0

VSS

AG10

AG13

VSS

CS_GTLREF

R109 0R0402R109 0R0402

D D

TEST_E5

IMPSEL

CS_GTLREF

COMP7

AE3

AC4

AE4

D14

E23

F23

RSVD

VSS

AE30

COMP7

VSS

AE5

AE7

RSVD

VSS

AF10

RSVDD1RSVD

VSS

VSS

AF13

AF16

E24

RSVD

RSVDE5RSVDE6RSVDE7RSVD

CS_GTLREF

VSS

VSS

VSS

AF17

AF20

AF23

VSS

AF24

VSS

AF25

VSS

AF26

RSVDF6RSVD

VSS

CPU1C

CPU1C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

A24

AA3

AA6

AA7

AB1

AB7

AC3

AC6

AC7

AD4

AD7

AE2

VSS

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

TEST_A24

C C

B B

COMP6

Y3

COMP6

VSS

AG16

VSS

AG17

VSS

AG20

AG23

CPU_GTLREF1 7

GTLVREF_NB 9

V30

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AH10

AH13

AH16

AH17

AG24

VSSV3VSS

VSS

AH20

V29

VSS

AH23

V28

VSS

VSS

AH24

V27

AH3

VSS

VSS

V26

VSS

VSS

AH6

TEST_U1

V25

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

AJ17

VSS

VSS

AJ20

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

GTL_DET 9

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

AM7

VID7#

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

H28

H29

VSS

VSS

VSS

GTLREF_SEL

VSS

VSS

VSS

VSS

AN2

AN17

AN20

AN23

VSS

VSS

AN24

VSS

VSS

AN27

AN28

VSS

VSS

VSS

VSS

VID_SELECT

VSSB1VSS

B11

AN7

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

ZIF-SOCK775-15u

B14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

TEST_G1

R110 X_0R0402R110 X_0R0402

T2T2

H_BPM#0 6

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

VSS

AL17

VSS

AL20

VSS

AL23

VSS

AL24

VSS

AL27

VSS

L30

AL28

VSS

VSSL3VSS

VSS

AL3

L29

L28

L27

VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

VSS

AM4

VID_SELECT

VID7

T3T3

TEST_U1 TEST_A24

R111 62R/4R111 62R/4

TEST_G1

R113 62R/4R113 62R/4

COMP4

R116 60.4R1%0402R116 60.4R1%0402

R118 60.4R1%0402R118 60.4R1%0402

COMP6

R120 60.4R1%0402R120 60.4R1%0402

COMP7

R123 60.4R1%0402R123 60.4R1%0402

COMP8

A A

5

R127 24.9R1%0402R127 24.9R1%0402

VTT_OUT_LEFT

VTT_OUT_RIGHT

4

VID7

VID_SELECT

R121 680R04R121 680R04

R125 680R04R125 680R04R124 X_680R04R124 X_680R04

VTT_OUT_RIGHT

3

R126 Mount 50 Ohm Impedance

R126 Open 60 Ohm Impedance

TEST_U1

TEST_J3

TEST_E5

MSID1COMP5

MSID0

IMPSEL

R112 1KR/0402R112 1KR/0402

R114 X_51R1%0402R114 X_51R1%0402

R115 1KR/0402R115 1KR/0402

R117 1KR/0402R117 1KR/0402

R119 62R0402R119 62R0402

R122 62R0402R122 62R0402

R126 51R1%0402R126 51R1%0402

2

VID_SELECT 25

VID7 25

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Intel LGA775 - GND

Intel LGA775 - GND

Intel LGA775 - GND

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

829

829

829

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 9

A

B

V_FSB_VTT

C

D

E

4 4

HBR#06,7

HIT#6

HITM#6

GTLVREF_NB

R135

R135

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

GTLCOMPP

GTLCOMPN

R136

R136

360R1%0402

360R1%0402

V_FSB_VTT

HA#[3..31]6

3 3

HADSTB#06

HADSTB#16

HADS#6

HBNR#6

HBPRI#6

HDBSY#6

HDEFER#6

HDRDY#6

HLOCK#6

HTRDY#6

HREQ#[0..4]6

HRS#[0..2]6

2 2

GTLVREF_NB8

1 1

C61

C61

C0.1U16Y0402

C0.1U16Y0402

HDBI#[0..3]6

CPURST#6,7

NBHCLK5

NBHCLK#5

C62

C62

C0.1U16Y0402

C0.1U16Y0402

180R1%04

180R1%04

M33

W35

W36

W34

AA36

AA34

AA32

W32

W31

W33

M34

M35

M32

M31

G27

AC29

AC30

G22

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

V32

V36

V34

V33

Y35

Y33

V31

R35

L35

K35

J32

K32

J33

K33

L36

L34

J34

T32

T31

R32

J35

N36

J36

C31

E35

D22

F22

U30

J25

H22

A17

U3A

U3A

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

GNDA1GNDA2GNDA8GND

VTT_1

A18

A19

A20

A21

B17

B18

B19

B20

VTT_2

VTT_3

VTT_4

VTT_5

VTT_6

VTT_7

VTT_8

VTT_9

P4M890 =>HA32,HA33

P4M890 =>HA32,HA33

GND

GND

GND

GND

GND

A3

GND

A10

A22

A25

A27

A29

A31

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

VTT_10

VTT_11

VTT_12

VTT_13

VTT_14

VTT_15

VTT_16

VTT_17

VTT_18

VTT_19

P4M890_Rev1.9->remove ha32,ha33

P4M890_Rev1.9->remove ha32,ha33

P4M900_Rev0.2

P4M900_Rev0.2

GND

GND

GNDB2GNDB3GNDB4GND

GNDC2GNDC3GNDC4GND

A33

A35

C5

B36

D21

E17

E18

E19

VTT_20

VTT_21

VTT_22

P4M900 only -->

P4M900 only -->

GND

GND

GND

D3

C26

C27

E20

E21

F17

F18

VTT_23

VTT_24

VTT_25

VTT_26

VTT_27

GNDD4GNDD5GNDD6GNDD8GND

D11

F19

F20

VTT_28

GND

D23

D24

F21

VTT_29

VTT_30

GND

GND

D29

G17

G18

G19

VTT_31

VTT_32

VTT_33

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

CPUSLPIN#

GND

GND

GND

D31

D32

D34

G20

G21

HD00#

HD01#

HD02#

VTT_34

VTT_35

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DPWR#

GNDE2GNDE4GND

HD#0

B35

HD#1

A36

HD#2

C33

HD#3

C32

HD#4

E31

HD#5

B34

HD#6

B33

HD#7

A34

HD#8

D30

HD#9

A30

HD#10

B31

HD#11

B30

HD#12

E30

HD#13

C29

HD#14

B29

HD#15

C30

HD#16

D36

HD#17

F36

HD#18

G36

HD#19

H34

HD#20

H35

HD#21

F35

HD#22

G35

HD#23

C36

HD#24

D35

HD#25

F34

HD#26

F33

HD#27

G34

HD#28

G33

HD#29

E33

HD#30

H32

HD#31

G32

HD#32

E28

HD#33

E29

HD#34

D28

HD#35

D27

HD#36

C28

HD#37

H28

HD#38

G28

HD#39

F28

HD#40

E27

HD#41

D26

HD#42

D25

HD#43

E25

HD#44

F25

HD#45

G25

HD#46

H26

HD#47

H25

HD#48

B23

HD#49

B25

HD#50

E23

HD#51

B27

HD#52

B28

HD#53

A28

HD#54

B24

HD#55

B26

HD#56

A26

HD#57

C23

HD#58

C22

HD#59

A23

HD#60

G23

HD#61

A24

HD#62

B22

HD#63

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

AB32

L31

GND

P4M900

P4M900

E6

E5

T4T4

HDSTBP#0 6

HDSTBN#0 6

HDSTBP#1 6

HDSTBN#1 6

HDSTBP#2 6

HDSTBN#2 6

HDSTBP#3 6

HDSTBN#3 6

-HAP0 6

SLP# 6,15

HD#[0..63] 6

GTL_DET=1 ,GTLVREF_NB=0.8V, H_TESTHIO=1.5V

GTL_DET=0 ,GTLVREF_NB=0.75V, H_TESTHIO=1.2V

+12V

For dual core

GTL_DET8

H_TESTHI06

X_N-2N7002_SOT23

X_N-2N7002_SOT23

R128

R128

10KR/4

10KR/4

Q4

Q4

VCCP

DS

G

VCC3

DS

G

R129

R129

390R1%0402

390R1%0402

Q3

Q3

N-2N7002_SOT23

N-2N7002_SOT23

R132

R132

X_249R1%0402-LF

X_249R1%0402-LF

V_FSB_VTT

C52 0.01U25Y/4C52 0.01U25Y/4

C53 0.01U25Y/4C53 0.01U25Y/4

C54 10U10Y/8C54 10U10Y/8

C55 10U10Y/8C55 10U10Y/8

C56 10U10Y/8C56 10U10Y/8

C57 10U10Y/8C57 10U10Y/8

C58 10U10Y/8C58 10U10Y/8

C59 C0.1U16Y0402C59 C0.1U16Y0402

C60 C0.1U16Y0402C60 C0.1U16Y0402

V_FSB_VTT

R130

R130

124R1%/4

124R1%/4

R131

R131

210R1%/04

210R1%/04

VCC3

R133

R133

X_110R1%0402

X_110R1%0402

R134

R134

X_61.9R1%0402-LF

X_61.9R1%0402-LF

GTLVREF_NB

B01-4M9005-V01 FOR P4M900

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

P4M900-1(HOST)

P4M900-1(HOST)

P4M900-1(HOST)

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

A

B

C

D

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

E

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

929

929

929

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 10

A

VCC_DDR

B

C

D

E

4 4

MD[0:63]16

3 3

2 2

DQM[0:7]16

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD62

MD63

AF35

AG34

AJ36

AK35

AF34

AG35

AJ34

AK34

AG32

AF32

AH30

AJ31

AF31

AH32

AH31

AJ32

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AJ22

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

U3B

U3B

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

AA24

AB24

VCCMEM

VCCMEM

AC24

AD16

VCCMEM

VCCMEM

AD17

AD18

VCCMEM

VCCMEM

AD19

AD20

VCCMEM

VCCMEM

AD21

AD22

VCCMEM

VCCMEM

AD23

AD24

VCCMEM

VCCMEM

AJ28

AJ26

VCCMEM

VCCMEM

AK25

AK27

VCCMEM

VCCMEM

AK29

AL26

VCCMEM

VCCMEM

AL28

AL30

VCCMEM

VCCMEM

AM25

AM27

VCCMEM

VCCMEM

AM29

AM31

VCCMEM

VCCMEM

AN26

AN27

VCCMEM

VCCMEM

AN31

AN33

VCCMEM

VCCMEM

AP30

AR26

VCCMEM

VCCMEM

AR33

AT25

VCCMEM

VCCMEM

MEMVREF0

MEMVREF1

AT28

AT31

VCCMEM

VCCMEM

SRAS#

SCAS#

SWE#

DQS0+

DQS0-

DQS1+

DQS1-

DQS2+

DQS2-

DQS3+

DQS3-

DQS4+

DQS4-

DQS5+

DQS5-

DQS6+

DQS6-

DQS7+

DQS7-

MCLKI

MCLKO+

MCLKO-

MEMDET

DMCOMP

AT35

BA0

BA1

VCCMEM

BA2

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

AR28

AP29

AP33

AT29

AR30

AR29

AT30

AN30

AP31

AR31

AT32

AP32

AN32

AN29

AR32

AT33

AR25

AN28

AR27

AP28

AT27

AP27

AT24

AP26

AT34

AP34

AR34

AN34

AT26

AP25

AR24

AN25

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

AB34

AB35

AB36

AG29

AJ18

AF36

AM33

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

CKEA0

CKEA1

CKEA2

CKEA3

MCLKIT

M_CLKO+MD61

M_CLKO-

MEMDET

DMCOMP

MVREF_NB

1: DDR2

0: DDR1

BA0 16

BA1 16

BA2 16

MAA[0:13] 16

-SRASA 16

-SCASA 16

-SWEA 16

-CS0 16

-CS1 16

-CS2 16

-CS3 16

CKEA0 16

CKEA1 16

CKEA2 16

CKEA3 16

ODT0 16

ODT1 16

ODT2 16

ODT3 16

-DQS0 16

-DQS0# 16

-DQS1 16

-DQS1# 16

-DQS2 16

-DQS2# 16

-DQS3 16

-DQS3# 16

-DQS4 16

-DQS4# 16

-DQS5 16

-DQS5# 16

-DQS6 16

-DQS6# 16

-DQS7 16

-DQS7# 16

R137 22R/4R137 22R/4

R138 22R/4R138 22R/4

VCC_DDR

R141 1KR0402R141 1KR0402

R142 301R1%0402R142 301R1%0402

VCC_DDR

NOTE: DQS/DQS# => OTHER:W:S:W:OTHER=15:10:5:10:15

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

MCLKIT 5

MCLKOT 5

MCLKOC 5

C99 X_C5P50N0402C99 X_C5P50N0402

C102 X_C5P50N0402C102 X_C5P50N0402

Near to NB chip

C63

C63

C4700P50X6

C4700P50X6

C90

C90

C0.1U25Y

C0.1U25Y

VCC_DDR

C65 C5P50N0402C65 C5P50N0402

C66

C66

C64

C64

C4700P50X6

C4700P50X6

C0.1U25Y

C0.1U25Y

C91

C91

C0.1U25Y

C0.1U25Y

C67

C67

C0.1U25Y

C0.1U25Y

C71 C5P50N0402C71 C5P50N0402

C72 C5P50N0402C72 C5P50N0402

C73 C5P50N0402C73 C5P50N0402

C74 C5P50N0402C74 C5P50N0402

C75 C5P50N0402C75 C5P50N0402

C76 C5P50N0402C76 C5P50N0402

C77 C5P50N0402C77 C5P50N0402

C78 C5P50N0402C78 C5P50N0402

C79 C5P50N0402C79 C5P50N0402

C80 C5P50N0402C80 C5P50N0402

C81 C5P50N0402C81 C5P50N0402

C82 C5P50N0402C82 C5P50N0402

C83 C5P50N0402C83 C5P50N0402

C84 C5P50N0402C84 C5P50N0402

C85 C5P50N0402C85 C5P50N0402

C86 C5P50N0402C86 C5P50N0402

C87 C5P50N0402C87 C5P50N0402

C88 C5P50N0402C88 C5P50N0402

C89 C5P50N0402C89 C5P50N0402

PULL DOWN GND OR PULL UP +1.8VDIMM

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0 16

BA1 16

BA2 16

-SRASA 16

-SCASA 16

-SWEA 16

CLOSE TO DIMM

VCC_DDR

C94 C0.1U16Y0402C94 C0.1U16Y0402

C95 C0.1U16Y0402C95 C0.1U16Y0402

C96 C0.1U16Y0402C96 C0.1U16Y0402

NEAR PM890

VCC_DDR

R139

R139

150R1%0402

150R1%0402

MVREF_NB

R140

R140

150R1%0402

150R1%0402

C108

C108

C104

C104

C106

C106

C1000P50X0402

C1000P50X0402

C1000P50X0402

Close to ball

C1000P50X0402

C1000P50X0402

C1000P50X0402

VCC_DDR

C97 C0.1U16Y0402C97 C0.1U16Y0402

C98 C0.1U16Y0402C98 C0.1U16Y0402

C100 C0.1U16Y0402C100 C0.1U16Y0402

C101 C0.1U16Y0402C101 C0.1U16Y0402

C105 C0.1U16Y0402C105 C0.1U16Y0402

C107 C0.1U16Y0402C107 C0.1U16Y0402C103 X_C5P50N0402C103 X_C5P50N0402

C109 C0.1U16Y0402C109 C0.1U16Y0402

C110 C0.1U16Y0402C110 C0.1U16Y0402

NEAR DIMM

GNDE7GND

GND

GNDF1GNDF2GNDF4GNDF5GNDF6GNDF7GND

GND

1 1

A

E9

E34

E36

GND

GND

GND

GND

GND

GND

GND

GNDG1GNDG2GNDG4GNDG7GND

GND

GNDH2GNDH4GNDH7GND

GND

GND

GND

GND

GND

F10

F14

F23

F26

F27

F29

F30

F32

F24

G11

G29

B

GNDJ2GNDJ4GNDJ5GNDJ6GND

GND

J7

P4M900

H23

H24

H27

H31

H36

H33

P4M900

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

P4M900-2(MEM)

P4M900-2(MEM)

P4M900-2(MEM)

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

C

D

http://www.msi.com.tw

MS-7331

MS-7331

MS-7331

E

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Tuesday, September 19, 2006

Sheet

Sheet

Sheet

10 29

10 29

10 29

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 11

4

1.6V

R599

R599

1.54KR1%0402

IF USE 8237S

5 5

4 4

3 3

2 2

1 1

LVREF_NB => 0.45V

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x

Disable all TEST mode

TESTIN_NB

FOR P4M900 DO NOT STUFF R144

CP6 X_COPPERCP6 X_COPPER

VCC3

FB2 X_120L600m_250FB2 X_120L600m_250

C22U6.3X1206

REFER AP372

VCC3

REFER AP382

VCC3

REFER AP382

VCC3

REFER AP372

VCC3

REFER AP372

REFER AP372

C22U6.3X1206

CP7 X_COPPERCP7 X_COPPER

FB3 X_120L600m_250FB3 X_120L600m_250

C22U6.3X1206

C22U6.3X1206

CP8 X_COPPERCP8 X_COPPER

FB4 X_120L600m_250FB4 X_120L600m_250

C22U6.3X1206

C22U6.3X1206

CP9 X_COPPERCP9 X_COPPER

FB5 X_120L600m_250FB5 X_120L600m_250

C22U6.3X1206

C22U6.3X1206

CP10 X_COPPERCP10 X_COPPER

FB6 X_120L600m_250FB6 X_120L600m_250

CP11 X_COPPERCP11 X_COPPER

VCC3

FB7 X_120L600m_250FB7 X_120L600m_250

C22U6.3X1206

C22U6.3X1206

C22U6.3X1206

C22U6.3X1206

1.54KR1%0402

R598

R598

20R1%0402

20R1%0402

LVREF_NB

R146

R146

1KR1%0402

1KR1%0402

LVREF_NB => 0.625V

R144 X_4.7KR0402R144 X_4.7KR0402

C124

C124

C123

C123

C1000P50X0402

C1000P50X0402

C130

C130

C1000P50X0402

C1000P50X0402

C133

C133

C1000P50X0402

C1000P50X0402

C136

C136

C137

C137

C1000P50X0402

C1000P50X0402

C140

C140

C139

C139

C1000P50X0402

C1000P50X0402

C142

C142

C143

C143

C1000P50X0402

C1000P50X0402

4

C131

C131

C134

C134

C111

C111

C0.1U16Y0402

C0.1U16Y0402

VCC_DDR

VCCA33PE

C125

C125

C0.1U16Y0402

C0.1U16Y0402

VCCA33HCK

C132

C132

C1U16Y

C1U16Y

VCCA33MCK

C135

C135

C1U16Y

C1U16Y

VCCA33PE01

C138

C138

C0.1U16Y0402

C0.1U16Y0402

VCCA33PE1

C141

C141

C0.1U16Y0402

C0.1U16Y0402

VCCA33PE00

C144

C144

C0.1U16Y0402

C0.1U16Y0402

R147 270R1%/4R147 270R1%/4

1.6V

R148 340R1%/4R148 340R1%/4

GCLK_NB5

PCIRST#123,26

-PWROK_NB14

VLAD0

VLAD015

VLAD1

VLAD115

VLAD2

VLAD215

VLAD3

VLAD315

VLAD4

VLAD415

VLAD5

VLAD515

VLAD6

VLAD615

VLAD7

VLAD715

VBE0

VBE015

UPSTB

UPSTB15

-UPSTB

-UPSTB15

DNSTB

DNSTB15

-DNSTB

-DNSTB15

UPCMD

UPCMD15

DNCMD

DNCMD15

LVREF_NB

LCOMPP

1.6V

+1.5VSUS

-SUSST14

TESTIN_NB

VCCA33HCK

VCCA33MCK

VCCA33PE00

VCCA33PE01

VCCA33PE

VCCA33PE1

+1.5VSUS

LCOMPN

AP1

AN3

AR4

AN2

AN1

AP5

AN5

AN4

AR3

AR1

AR5

AP4

AM5

AD13

AD14

AD15

M12

M13

M14

M15

M16

M20

M21

M22

M23

M24

W12

W25

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AE6

AH5

AH3

AC32

AD29

AE7

AH6

AH4

3

AT3

AT2

AT1

AL6

AL5

AL4

N12

N25

P12

P25

R12

T12

T25

U12

U25

V12

Y12

Y25

G6

AF7

H6

3

N13

U3C

U3C

VD00

VD01

VCC33PEX

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTIN#

RESET#

PWROK

VCCA33HCK

VCCA33MCK

VCCA33PEX0

VCCA33PEX1

VCCA33PEXCK

VCCA33PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

GND

GND

K4

K2

R13

N14

P13

VCC33PEX

VCC33PEX

VCC33PEX

GNDK5GNDK7GND

K31

T13

U13

V13

VCC33PEX

VCC33PEX

VCC33PEX

GND

GND

GNDL2GNDL7GND

K34

K36

VCC3

W13

Y13

AA13

AB13

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GND

GNDL5GND

L32

L33

AC13

AJ1

AJ2

VCC33PEX

VCC33PEX

VCC33PEX

GNDM5GNDM7GND

M2

AJ3

AJ4

AJ5

AJ6

AJ7

AK1

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDN2GNDN5GNDN7GNDP2GNDP7GND

GNDP5GND

M36

AK3

AK4

AK2

AK5

AK6

AK7

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PEXRX00+/DVP0D11

PEXRX00-/DVP0D10

PEXRX01+/DVP0D09

PEXRX01-/DVP0D08

PEXRX02+/DVP0D07

PEXRX02-/DVP0D06

PEXRX03+/DVP0CLK

PEXRX03-/DVPTVCLKR

PEXRX04+/DVP0D05

PEXRX04-/DVP0D04

PEXRX05+/DVP0D03

PEXRX05-/DVP0D02

PEXRX06+/DVP0D01

PEXRX06-/DVP0D00

PEXRX07+/DVP0DE

PEXRX07-/DVP0HS

PEXRX08+/DVP1D11

PEXRX08-/DVP1D10

PEXRX09+/DVP1D09

PEXRX09-/DVP1D08

PEXRX10+/DVP1D07

PEXRX10-/DVP1D06

PEXRX11+/DVP1CLK

PEXRX11-/DVP1D05

PEXRX12+/DVP1D04

PEXRX12-/DVP1D03

PEXRX13+/DVP1D02

PEXRX13-/DVP1D01

PEXRX14+/DVP1D00

PEXRX14-/DVP1DE

PEXRX15+/DVP1HS

PEXRX15-/DVP1VS

PEXWAKE#

PEXHPSCI#

PEXPMESCI#

PEXCOMP0

PEXCOMP1

PEXCOMP2

GND

GND

GND

GND

P6

P14

P15

P16

P17

P18

PEXTX00+

PEXTX00-

PEXTX01+

PEXTX01-

PEXTX02+

PEXTX02-

PEXTX03+

PEXTX03-

PEXTX04+

PEXTX04-

PEXTX05+

PEXTX05-

PEXTX06+

PEXTX06-

PEXTX07+

PEXTX07-

PEXTX08+

PEXTX08-

PEXTX09+

PEXTX09-

PEXTX10+

PEXTX10-

PEXTX11+

PEXTX11-

PEXTX12+

PEXTX12-

PEXTX13+

PEXTX13-

PEXTX14+

PEXTX14-

PEXTX15+

PEXTX15-

PEXTX16+

PEXTX16-

PEXRX16+

PEXRX16-

PEXCLK+

PEXCLK-

INTR#

PEXDET

TCSEN#

PEXREXT0

PEXREXT1

PEXREXT2

GND

GND

P19

P20

P4M900

P4M900

B1

C1

D1

E1

H1

J1

K1

L1

L4

M4

M1

N1

N4

P4

P1

R1

T1

U1

U4

V4

V1

W1

W4

Y4

Y1

AA1

AB1

AC1

AC4

AD4

AD1

AE1

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

2

PEDET

TCSEN#

PE0RCOMP0

PE0RCOMP1

PE0REXT0

PE0REXT1

PE1RCOMP

PE1REXT

2

PE0TX0+ 17

PE0TX0- 17

PE0TX1+ 17

PE0TX1- 17

PE0TX2+ 17

PE0TX2- 17

PE0TX3+ 17

PE0TX3- 17

PE0TX4+ 17

PE0TX4- 17

PE0TX5+ 17

PE0TX5- 17

PE0TX6+ 17

PE0TX6- 17

PE0TX7+ 17

PE0TX7- 17

PE0TX8+ 17

PE0TX8- 17

PE0TX9+ 17

PE0TX9- 17

PE0TX10+ 17

PE0TX10- 17

PE0TX11+ 17

PE0TX11- 17

PE0TX12+ 17

PE0TX12- 17

PE0TX13+ 17

PE0TX13- 17

PE0TX14+ 17

PE0TX14- 17

PE0TX15+ 17

PE0TX15- 17

PE0RX0+ 17

PE0RX0- 17

PE0RX1+ 17

PE0RX1- 17

PE0RX2+ 17

PE0RX2- 17

PE0RX3+ 17

PE0RX3- 17

PE0RX4+ 17

PE0RX4- 17

PE0RX5+ 17

PE0RX5- 17

PE0RX6+ 17

PE0RX6- 17

PE0RX7+ 17

PE0RX7- 17

PE0RX8+ 17,21

PE0RX8- 17,21

PE0RX9+ 17,21

PE0RX9- 17,21

PE0RX10+ 17,21

PE0RX10- 17,21

PE0RX11+ 17,21

PE0RX11- 17,21

PE0RX12+ 17,21

PE0RX12- 17,21

PE0RX13+ 17,21

PE0RX13- 17,21

PE0RX14+ 17,21

PE0RX14- 17,21

PE0RX15+ 17,21

PE0RX15- 17,21

PECLK_NB 5

PECLK_NB# 5

PIRQ#H 13

PEWAKE# 14,17

PEHPSCI 15

PEPMESCI 14

R151 249R1%0402R151 249R1%0402

R152 249R1%0402R152 249R1%0402

R153 10.7KR1%0402R153 10.7KR1%0402

R154 10.7KR1%0402R154 10.7KR1%0402

R155 249R1%0402R155 249R1%0402

R156 10.7KR1%0402R156 10.7KR1%0402

1.6V

C113 C0.1U16Y0402C113 C0.1U16Y0402

C114 C0.1U16Y0402C114 C0.1U16Y0402

C112 C0.1U16Y0402C112 C0.1U16Y0402

C115 C0.1U16Y0402C115 C0.1U16Y0402

C116 C0.1U16Y0402C116 C0.1U16Y0402

Decoupling capacitors

1.6V

C117 C4.7U6.3X5-1C117 C4.7U6.3X5-1

1 2

C118 C4.7U6.3X5-1C118 C4.7U6.3X5-1

1 2

C119 C4.7U6.3X5-1C119 C4.7U6.3X5-1

1 2

C120 C4.7U10Y0805C120 C4.7U10Y0805

C121 C4.7U10Y0805C121 C4.7U10Y0805

C122 C4.7U6.3X5-1C122 C4.7U6.3X5-1

1 2

C126 C2.2U6.3X5C126 C2.2U6.3X5

C127 C2.2U6.3X5C127 C2.2U6.3X5

C128 C2.2U6.3X5C128 C2.2U6.3X5

C129 C2.2U6.3X5C129 C2.2U6.3X5

under NB( solder side)

VCC3

PEDET

R149 4.7KR0402R149 4.7KR0402

VCC3

TCSEN#