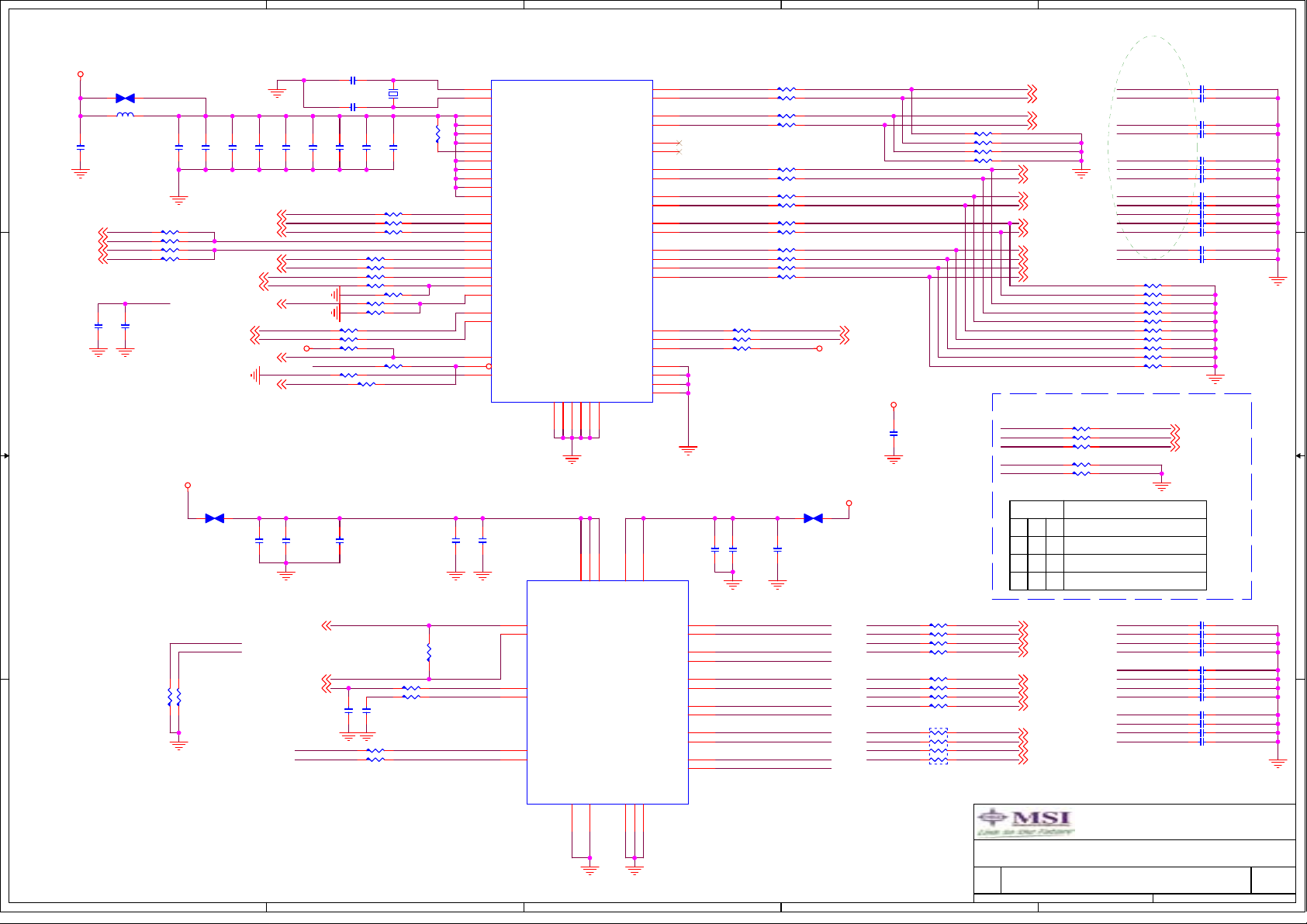

MSI MS-7318 Schematics Version: 100

A

B

C

D

E

MS7318M1 Version: 100

TITLE

4 4

Cover Sheet

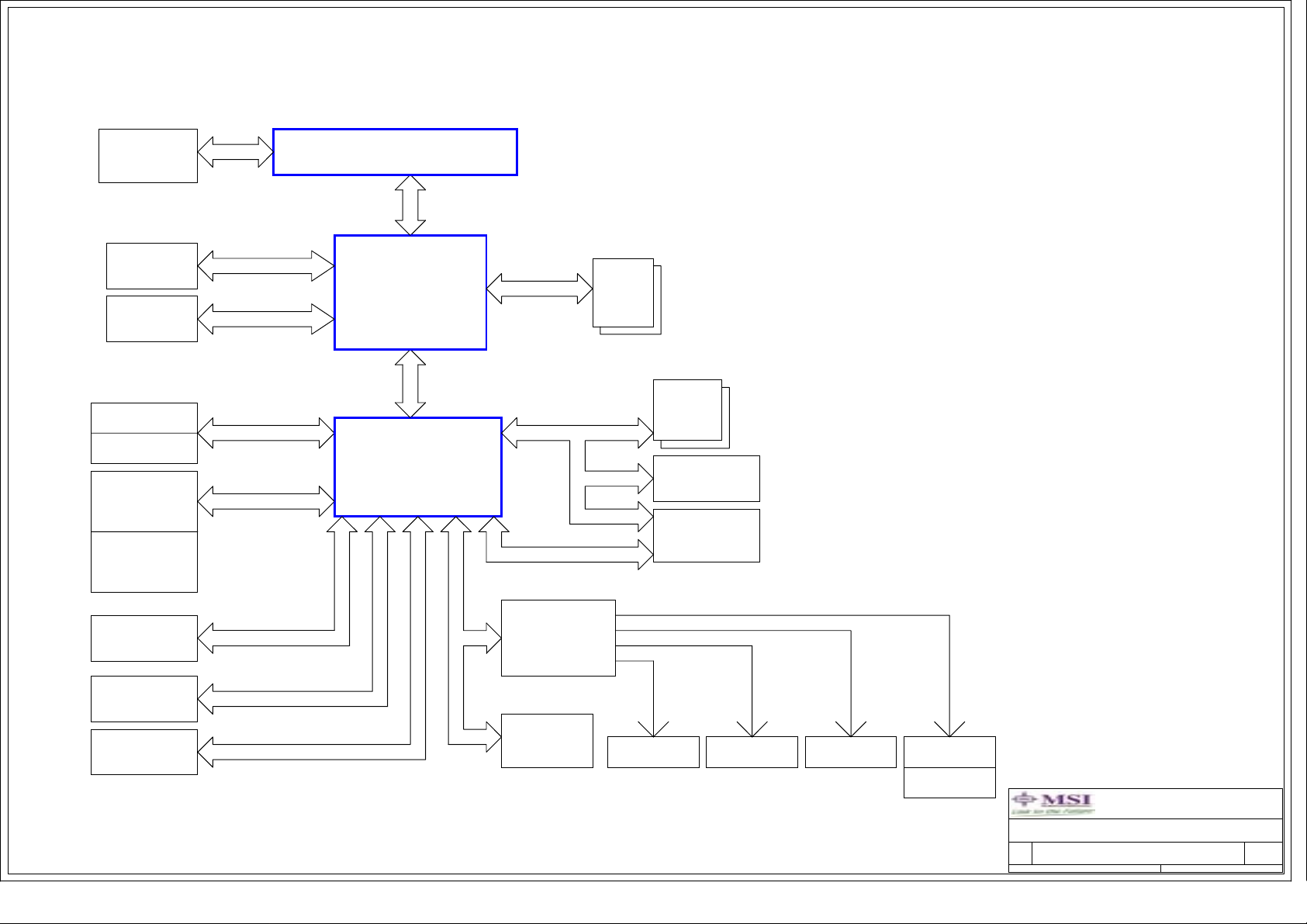

Block Diagram

PWR Map / CLOCK Map

GPIO/Memory/PCI/HW Config.

Clock Gen .

SHEET

1

2

3

4

5

CPU:

Intel LGA775

(Support Conroe E6300/E6400/E6700/E6800,

Prescott 500 Sequence, Cedar Mill,

Smithfield, Celeron D)

System Chipset:

VIA PT890CE (North Bridge)

VIA VT8251L (South Bridge)

Processor (LGA775)

North Bridge PT890CE

3 3

MEM-DDRII SLOT 1 & 2

PCI-Express Slot x16 & x1

South Bridge VT8251L

PCI SLOT 1 & 2

6-8

9-12

13

14

15-17

18

On Board Chipset:

CLOCK - ICS953002 + ICS9P936

LPC Super I/O - W83627DHG

BIOS - LPC ROM

HD Audio ALC888

LAN - Realtek 8201CL colay RT8110SC

IEEE1394 - VT6308P

USB-Rear & Front Conn.

P-IDE & SATA

19-20

21-22

E-SATA JMB360

Main Memory:

e-SATA JMB360

23

single-channel - DDRII*2 533

2 2

SIO W83627DHG HW monotor,FAN,LPT,COM,KB,MOS,FDD,LPC

IEEE-1394_VT6308P & 1394 port

LAN PHY RTL8201CL & RTL8110SC & LAN port

24-27

28-29

30-32

Expansion Slots:

PCI Express X16 * 1

PCI 2.3 Slot * 1 (Medion 2 master)

HD Audio ALC888 & Audio jacks

MS7 ACPI Controller

33-34

35

PCI 2.3 Slot * 1

PCI Express X1 * 1

Power Regulators DDR2 & VTT & Other

Standby power and USB dual power

VRM11 PWM ISL6312 & 3 Phase MosFET

1 1

Power Conn, Front Panel & BIOS

Manual Part & Holes

A

B

36-38

39-40

41-42

43-44

45

PWM VRD11 :

Intersil 6312 3 Phase

Title

Cover Sheet

Size Document Number Rev

MS-7318-0B-060828E 100

C

D

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

145Monday, August 28, 2006

E

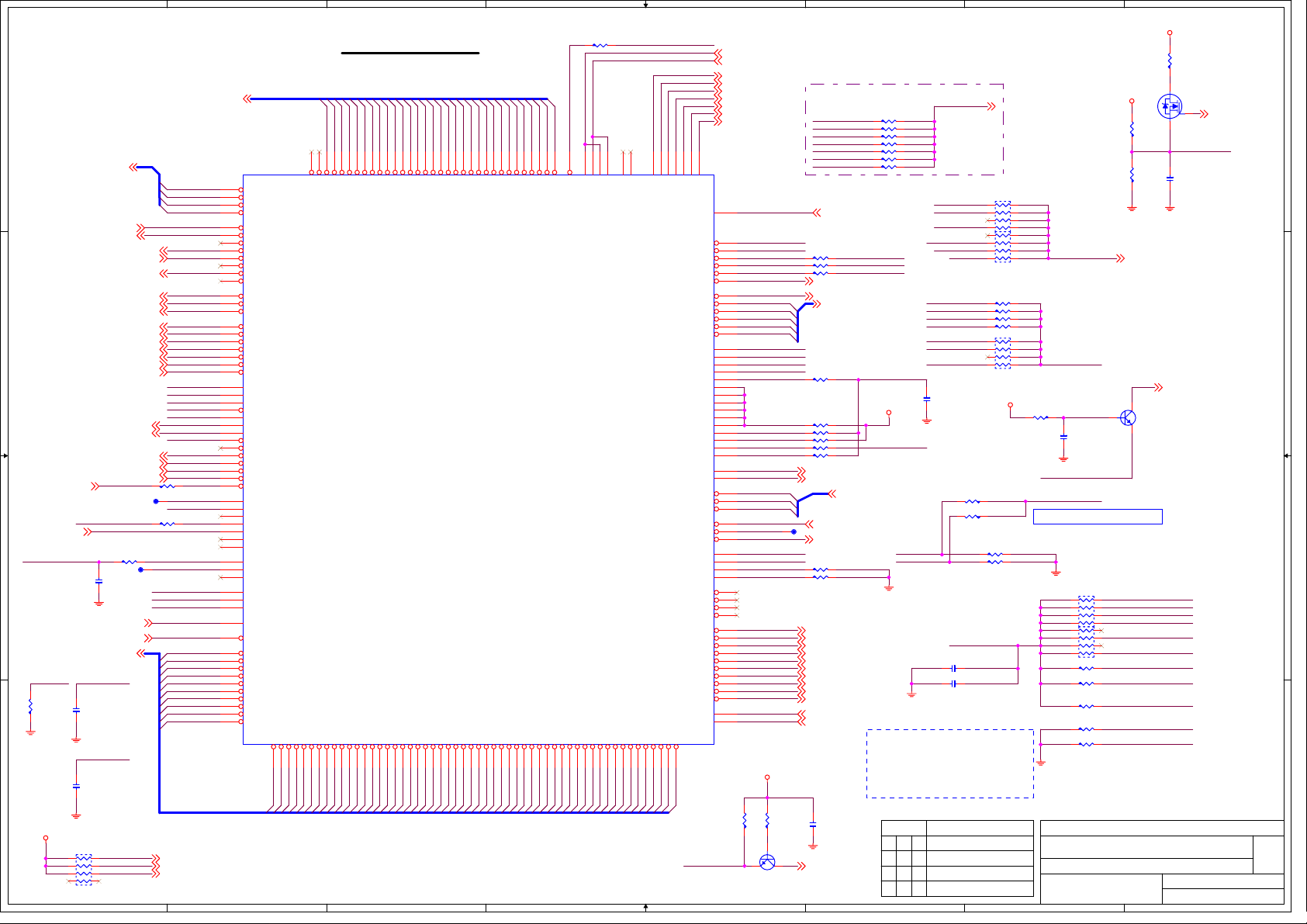

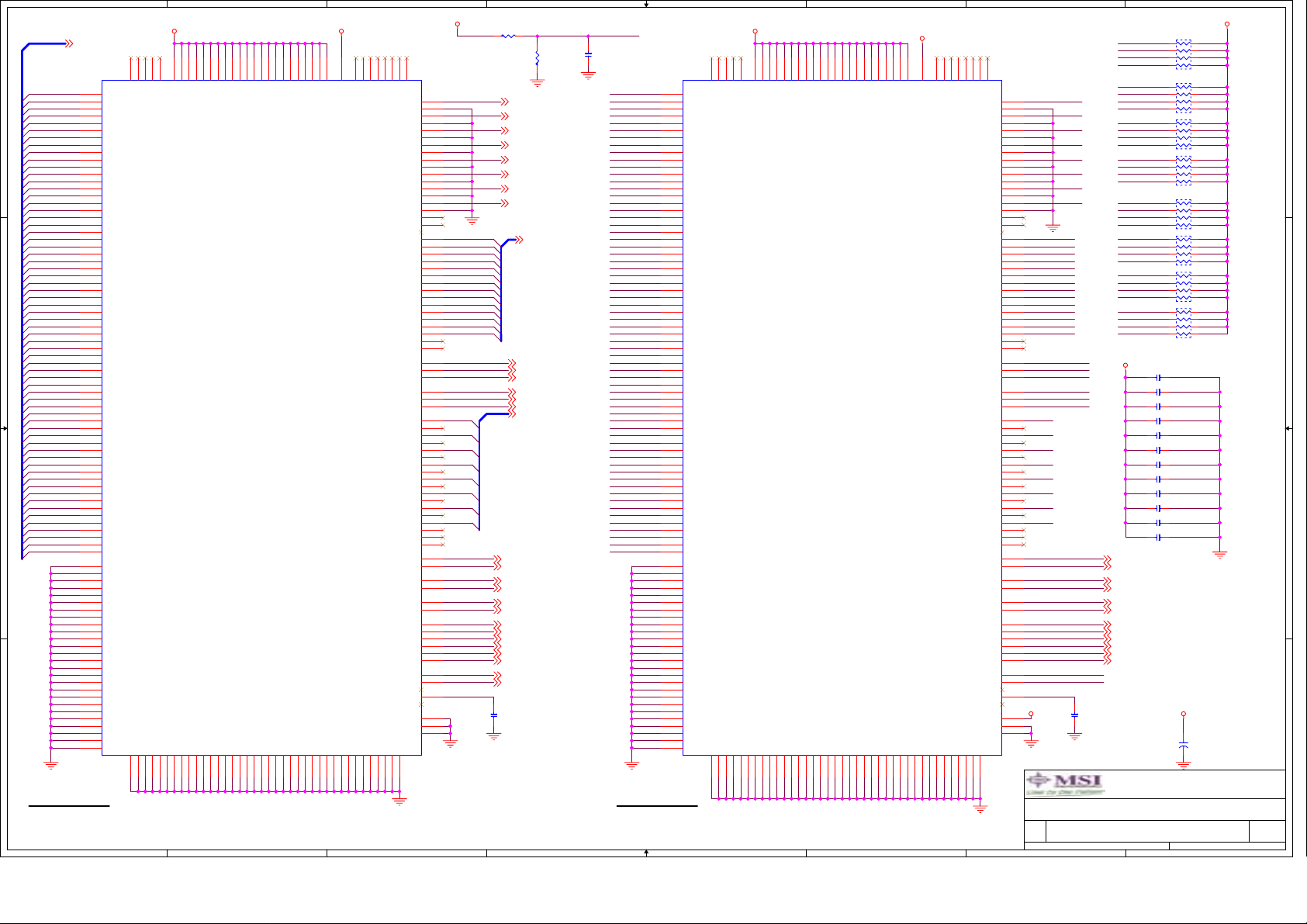

Block Diagram

1

VRD 11

Intersil 6312

Intel LGA775 Processor

3-Phase PWM

FSB

PCI-Express

X16

PCI-Express

X1

IDE Primary

A A

IDE Secondary

Rear USB

X16

X1

UltraDMA 33/66/100

USB

VIA - PT890CE

V-Link

VT8251L

single channel

PCI BUS

2 DDRII

DIMM

Modules

PCI Slot

1 & 2

IEEE 1394

VT6308P

USB Port 0,1

USB Port 2,3

Front USB

PHY

LAN

1G :RT8110SC

10/100:VT8201CL

USB Port 4,5

USB Port 6,7

ALC888

SATA 1,2

E-SATA

JMB360

AZ Link

SATA

PCI_E 1X

LPC Bus

LPC SIO

Winbond

83627DHG

FLASH

SerialFloopy

Parallel Keyboard

Mouse

Title

Block Diagram

Size Document Number Rev

MS-7318-0B-060828E 100

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

245Monday, August 28, 2006

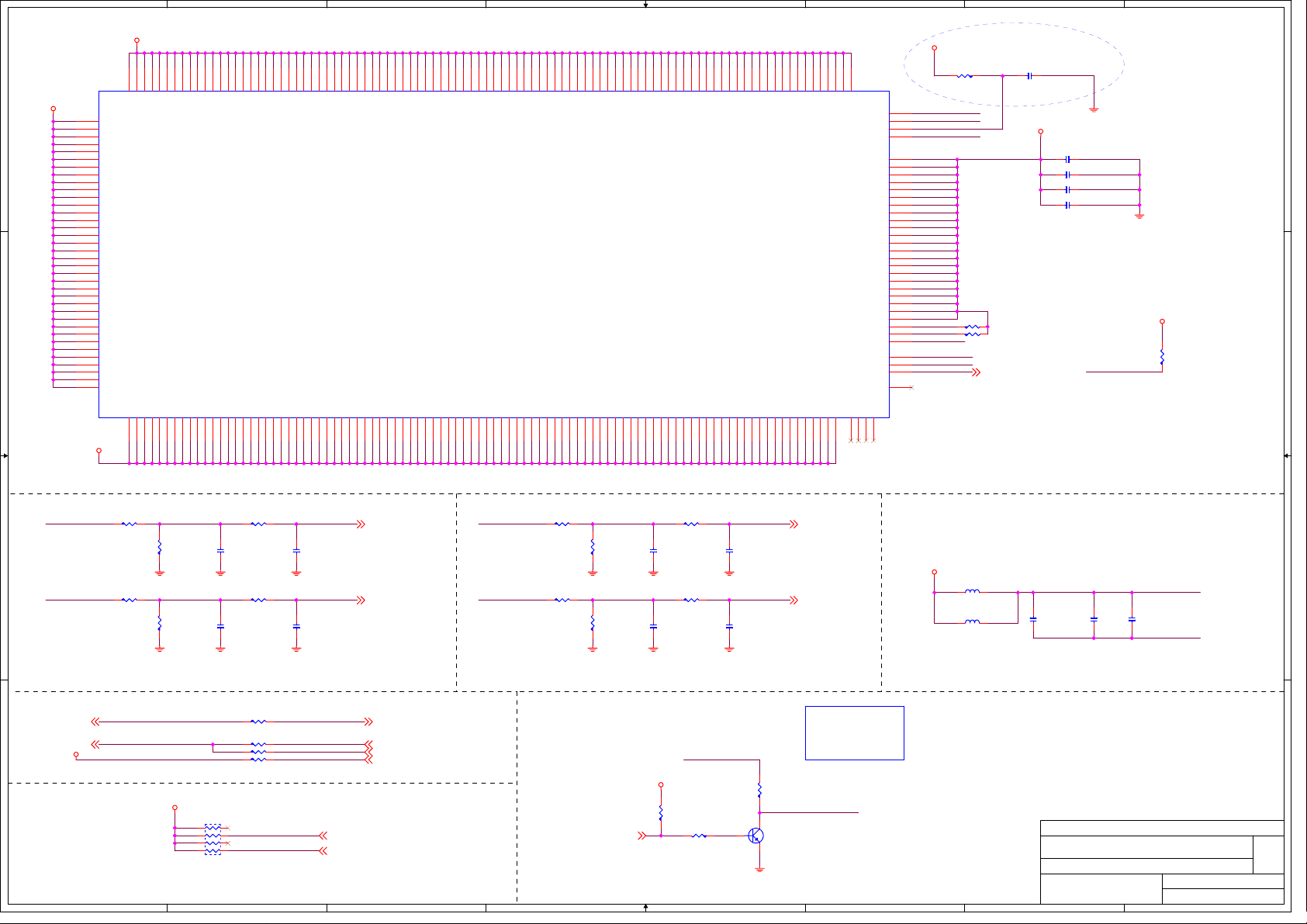

1

PCI Config.

DEVICE

PCI Slot 1

MCP1 INT Pin

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#B

PIRQ#C

PIRQ#D

PREQ#0

PGNT#0

PREQ#1

PGNT#1

IDSEL

AD20

AD21

CLOCKREQ#/GNT#

CK_PCI_CLK0

CK_PCI_CLK1

CLK GEN Pin Out

11

14

PIRQ#A

PCI Slot 2

PIRQ#C

PIRQ#D

PIRQ#A

PREQ#2

PGNT#2

AD22

CK_PCI_CLK2

17

PIRQ#B

1394

LAN

PIRQ#D

PIRQ#A

PREQ#3

PGNT#3

PREQ#4

PGNT#4

AD23

AD24

1394_PCLK

PCI_CLK_LAN

13

13

PIRQ#A also link to NB PIN H13

PIRQ#H also link to NB PIN B6

A A

PCI RESET DEVICE

Signals Target

PCIRST#

PCIRST#2

Source

VT8237A

MS7

MS7

MS7

1394 & SPIO & BIOSPCIRST#1

PCI slot 1-2

NB_RST# MS7 NB_RST#

HDRST#

MS7

Primary, Scondary IDE

Rsmrst# MS7 VT8237A

PCIE_Reset#

VT8237A PCIE 1-2

DDR DIMM Config.

Title

Size Document Number Rev

1

Date: Sheet

MICRO-START INT'L CO.,LTD.

GPIO/Memory/PCI/HW Config.

MS-7318-0B-060828E 100

of

345Monday, August 28, 2006

5

4

3

2

1

SB-VT5251LCE

(External pullup / pulldown straps are required to select “H” / “L”)

Strap Pins for VT8251L Version CE Configuration

Signal Description

D D

SPKR

ACSDOUT0

Pin#

AF05

R01

SEEDI B13 Use Serial L: Enable. Use external EEPROM

ACSYNC LPC FWH

R04

PDCS1# AC25

C C

PDDACK#

SUSA#

AB23

W01

Strap Pins for North Bridge (“NB”) Configuration

PDCS3# AA23 NB Configuration ATeCon PDCS3# signal state is reflected on

AD27 PDA2 NB Configuration

PDA1 AC26 NB Configuration

GPIOD /

AC05 NB Configuration

PCGNTB

B B

GPIOB /

AE01 GPIOB/PCREQB signal state is

PCREQB

PDA0, AE03

GPIOA/PCREQA

GPIOC/PCGNTA

Strap Pins

Function

CPU Frequency

Strapping

Auto Reboot

L: Enable CPU Frequency Strapping

H: Disable CPU Frequency Strapping

Default setting: Disable

L: Enable Auto Reboot

H: Disable Auto Reboot .

Default setting: Disable

External LAN

EEPROM

H: Disable. Do not use external EEPROM

Default setting: Enable (pull low) sInc

Up Mode

Vlink auto compensation

PCI Express

Debugging

Mode

L: Enable PCI Express debugging mode logntiaired

H: Disable PCI Express debugging mode

Default setting: Disable

Notebook /

Desktop LAN Reset

NB Configuration

NB Configuration

AF03

L: Enable LPC FWH Command

H: Disable LPC FWH Command

Default setting: Disable

L: Enable SATA spin up mode iel SATA Spin

H: Disable SATA spin up mode

Default setting: Disable

L: Notebook LAN reset

H: Desktop LAN reset hnoideequ

signal pin VD7 during power up for

North Bridge configuration.

PDA2 signal state is reflected on

signal pin VD6 during power up for

North Bridge configuration.

PDA1 signal state is reflected on

signal pin VD5 during power up for

North Bridge configuration. DAR

NGPIOD/PCGNTB signal state is

reflected on signal pin VD3 during

power up for North Bridge

configuration.

reflected on signal pin VD2

during power up for North

Bridge configuration.

PDA0, GPIOA/PCREQA and

GPIOC/PCGNTA signal states

are reflected on signal pins

VD4, VD1 and VD0 during

power up for North Bridge

configuration.

A A

Title

Strap Pins

Size Document Number Rev

MS-7318-0B-060828E 100

5

4

3

2

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

445Monday, August 28, 2006

1

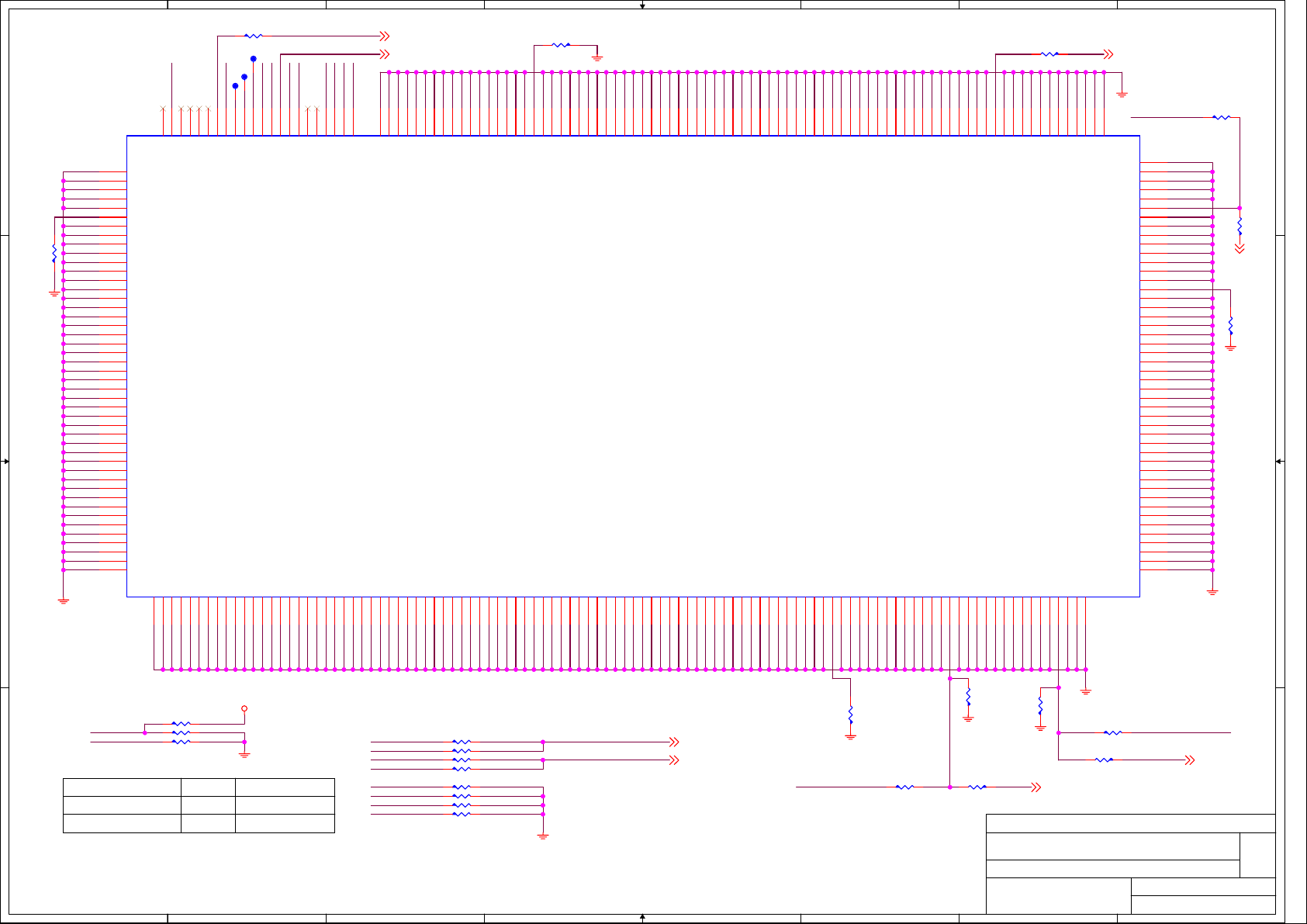

5

4

3

2

1

Ce = 2 CL - Ci - Cs

= ( 2 x 32 ) - 5 - 3

= 56

VCC3

CP5

1 2

X_COPPER

D D

C0.1U16Y0402

X_C22U10Y1206

C C

SEL24_48

FB1 X_80L3_70_0805

C137

FWH_PCLK27,44

SIO_33MHZ24

1394_PCLK28

PCI_CLK_LAN31

C0.1U16Y0402

C150

VCC3V

21

C147

C0.1U16Y0402

R84 22R0402

R65 22R0402

R83 22R0402

R61 X_22R0402

VCC3V

C139

C10U10Y0805

C206

C205

C0.1U16Y0402

CK_48M_SIOCLK24

SMBCK13,14,16,23,35,41

SMBDT13,14,16,23,35,41

C207

C0.1U16Y0402

GUICK12

SB14MHZ16

CK_PCI_CLK018

CK_PCI_CLK118

CK_PCI_CLK218

SB_PCLK17

USBCLK15

VRM_GD35,41

C146

C0.1U16Y0402

SB_PCLK SBPCLK

USBCLK

SMBCK

SMBDT

VCC3

1=24MHz , 0=48MHz

FP_RST#35,43

C145

C0.1U16Y0402

C0.1U16Y0402

GUICK

SB14MHZ

R137 33R0402

R143 33R0402

R86 1KR0402

VCC3V

R130 475R1%0402

FP_RST#

C156 C56P50N

C158 C56P50N

C0.1U16Y0402

R64 0R0402

MODE

0 = DESKTOP MODE

VCC_DDR

CP35

1 2

X_COPPER

C615

B B

C0.1U16Y0402

C586

C0.1U16Y0402

C0.1U16Y0402

CK_XIN

Y5 14.318MHZ32P_D

CK_XOUT

1 2

1KR0402

C142

C143

C0.1U16Y0402

R88 22R0402

R87 22R0402

R85 22R0402

R82 22R0402

R81 22R0402

R80 22R0402

R63 22R0402

R77 1KR0402

R62 22R0402

R76 4.7KR0402

SMBCK_R

SMBDT_R

R78 X_4.7KR0402

FP_RST#_R

ICS953002DFLF-T_SSOP56-RH

VDD1.8

C589

TURBO#

FS0

FS1

FS2

FS3

PCICLK2

PCICLK3

PCICLK4

MODE

SEL24_48

VRM_GD

IREF

C609

X_C22U10Y1206

U8

6

X1

7

X2

1

VDDA

3

VDDREF

10

VDDPCI

16

VDDPCI#16

20

*Turbo#

22

VDD48

26

VDD3V66

39

VDDPCIEX#39

45

VDDPCIEX

49

VDDCPU

4

**FSL0/REF0

5

FSL1/REF1

11

**FSL2/PCICLK0

12

**FS3/~PCICLK1

13

PCICLK2

14

PCICLK3

17

PCICLK4

18

PCICLK5

23

**Mode0/48MHz

24

*Sel24_48#/24_48MHz

31

SCLK

48

SDATA

9

VTTPWR_GD/PD#

21

Reset#

55

IREF

Ver : D

C594

C10U10Y0805

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2_ITP/PCIEXT0

CPUCLKC2_ITP/PCIEXC0

PCIEXT1

PCIEXC1

PCIEXT2

PCIEXC2

PCIEXT3

PCIEXC3

PCIEXT4

**FS4/3V66_1

**ITP_EN/3V66_2

GNDPCI#15

GNDPCI#19

GND48

GNDPCIEX

GND3V66

25

32

30

40

21

10

27

PCIEXC4

3V66_0

GND#2

GNDREF

26

PCIEXT5/CPU_STOP#*

PCIEXC5/PCI_PCIEX_STOP#*

GNDCPU

GND#5656GNDPCIEX#40

52

U23

RCPUCLK

54

RCPUCLK#

53

RNBHCLK

51

RNBHCLK#

50

47

46

RPECLK1

44

RPECLK1#

43

RPECLK2

42

RPECLK2#

41

RPECLK_NB

38

RPECLK_NB#

37

RPECLK_SB PECLK_SB

36

RPECLK_SB#

35

RPECLK3

34

RPECLK3#

33

VCLK_R

29

FS4

28

ITP

27

2

8

15

19

C603

C0.1U16Y0402

1

R129 33R0402

R128 33R0402

R127 33R0402

R126 33R0402

R142 33R0402

R141 33R0402

R140 33R0402

R139 33R0402

R160 33R0402

R159 33R0402

R133 33R0402

R132 33R0402

R134 33R0402

R135 33R0402

R136 22R0402

R74 22R0402

R75 X_4.7KR0402

AVDD2.5

C614

C0.1U16Y0402

VCLK

GCLK_NB

VCC3

CP36

1 2

X_COPPER

C613

C10U10Y0805

CPUCLK

CPUCLK#

NBHCLK

NBHCLK#

PECLK1

PECLK1#

PECLK2

PECLK2#

PECLK_NB

PECLK_NB#

PECLK_SB#

PECLK3

PECLK3#

VCLK 17

GCLK_NB 11

+2.5V

VCC3

C124

C0.1U16Y0402

R156 51R1%0402R79

R153 51R1%0402C144

R155 51R1%0402

R154 51R1%0402

CLOCK STRAPPING

FS0

FS1

FS2

FS3

FS4

0

0 0 133 MHZ (533)

CPUCLK 6

CPUCLK# 6

NBHCLK 9

NBHCLK# 9

PECLK1 14

PECLK1# 14

PECLK2 14

PECLK2# 14

PECLK_NB 11

PECLK_NB# 11

PECLK_SB 17

PECLK_SB# 17

PECLK3 23

PECLK3# 23

R68 10KR0402

R67 10KR0402

R66 10KR0402

R58 10KR0402

R69 10KR0402

BSEL

02

1

FSB FREQUENCY

267 MHZ (1067)000

01 200 MHZ (800)

1

VCLK

GCLK_NB

CK_48M_SIOCLK

USBCLK

CK_PCI_CLK1

CK_PCI_CLK2

CK_PCI_CLK0

SB_PCLK

1394_PCLK

SIO_33MHZ

FWH_PCLK

PCI_CLK_LAN

GUICK

SB14MHZ

R171 51R1%0402

R170 51R1%0402

R164 51R1%0402

R163 51R1%0402

R162 51R1%0402

R165 51R1%0402

R158 51R1%0402

R157 51R1%0402

R151 51R1%0402

R152 51R1%0402

BSEL0

BSEL1

BSEL2

TABLE

C210 X_C10P50N0402

C151 X_C10P50N0402

C114 X_C10P50N0402

C115 X_C10P50N0402

C135 X_C10P50N0402

C130 X_C10P50N0402

C136 X_C10P50N0402

C129 X_C10P50N0402

C131 X_C10P50N0402

C118 X_C10P50N0402

C132 X_C10P50N0402

C111 X_C10P50N0402

C134 X_C10P50N0402

C133 X_C10P50N0402

BSEL0 6

BSEL1 6

BSEL2 6

MCLKOT

MCLKOC

R623

X_4.7KR0402

A A

R618

X_4.7KR0402

MCLKOT10

MCLKOC10

MCLKIT10

C5P50N0402

SMBCK

SMBDT

MCLKOT

X_200R0402

MCLKOC

MCLKIT

C585

R598 33R0402

R593 33R0402

R621

R599 22R0402

R597 22R0402

C581

C5P50N0402

FB_OUTT

FB_OUTC

SMB_CK_R

SMB_DT_R

ICS9P936AFLF_SSOP28-LF

3

4

11

12

16

15

BUF_INT

BUF_INC

FB_OUTT

FB_OUTC

SDATA

SCLK

VDD2.5/1.8#21

VDD2.5/1.8#10

AGND

AGND#25

2

25

VDD2.5/1.8

9

AVDD2.5

AVDD2.5#26

GND

GND#28

GND#22

28

22

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

5

6

7

8

13

14

18

17

20

19

24

23

DCLKA0

DCLKA#0

DCLKB2

DCLKB#2

DCLKA1

DCLKA#1

DCLKB1

DCLKB#1

DCLKB0

DCLKB#0

DCLKA2

DCLKA#2

DCLKB2

R613 10R0402

DCLKB#2

R603 10R0402

DCLKA1 MDCLKA#1

R595 10R0402

DCLKA#1

R589 10R0402

DCLKA0

R616 10R0402

DCLKA#0

R614 10R0402

DCLKB#1

R600 10R0402

DCLKB1

R601 10R0402

DCLKA2

DCLKA#2

DCLKB0

DCLKB#0

RN50

1

3

5

7

8P4R-10R0402

2

4

6

8

Title

MDCLKB2 13

MDCLKB#2 13

MDCLKA1 13

MDCLKA#1 13

MDCLKA0 13

MDCLKA#0 13

MDCLKB#1 13

MDCLKB1 13

MDCLKA2 13

MDCLKA#2 13

MDCLKB0 13

MDCLKB#0 13

MICRO-START INT'L CO.,LTD.

MDCLKB#2

MDCLKB2

MDCLKA1

MDCLKA0

MDCLKA#0

MDCLKB0

MDCLKB#0

MDCLKA#2

MDCLKA2

MDCLKB#1

MDCLKB1

C591 X_C10P50N0402

C598 X_C10P50N0402

C564 X_C10P50N0402

C580 X_C10P50N0402

C605 X_C10P50N0402

C601 X_C10P50N0402

C593 X_C10P50N0402

C588 X_C10P50N0402

C599 X_C10P50N0402

C602 X_C10P50N0402

C583 X_C10P50N0402

C587 X_C10P50N0402

CLOCK GEN & BUFFER

Size Document Number Rev

MS-7318-0B-060828E 100

5

4

3

2

Date: Sheet

1

of

545Monday, August 28, 2006

8

D D

HDBI#[0..3]9

HDBI#0

HDBI#1

HDBI#2

HDBI#3

CPU_GTLREF27

HIERR#7

FERR#7,17

STPCLK#17

HINIT#17,44

HDBSY#9

HDRDY#9

HTRDY#9

HADS#9

HLOCK#9

C C

15 // 10 / 10 / 10 //15

SLP#17

CPU_GTLREF37

VTT_OUT_RIGHT

B B

A A

X_C0.1U16Y0402

N5R

R427

X_1K/4

V_FSB_VTT

C408

CPU_GD

C398

X_1000P/16V/X7R/4

CPURST#

C242

X_1000P/16V/X7R/4

RN13

470R/8P4R/4

1

3

5

7

8

HBNR#9

HBPRI#9

HDEFER#9

THERMDA24,25

THERMDC24,25

PROCHOT#7

IGNNE#17

SLP#

R461 1K/0402

T11

CPU_GD7,35

CPURST#7,9

HD#[0..63]9

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

BSEL1

2

BSEL2

4

BSEL0

6

8

HIT#9

HITM#9

SMI#17

A20M#17

R433 0R/4

T14

R22951R/4

BSEL1 5

BSEL2 5

BSEL0 5

FERR#

STPCLK#

HINIT#

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

H_TESTHI13

N5R

TEST_C9VTT_OUT_LEFT

CPU_BOOT

BSEL0

BSEL1

BSEL2

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

7

CPU SIGNAL BLOCK

HA#[3..33]9

HA#29

HA#30

HA#31

HA#32

HA#33

AJ6

AJ5

AH5

AH4

AG5

AG4

D20

A35#

D48#

G22

HD#47

A34#

D47#

D22

HD#46

A33#

D46#

E22

HD#45

A32#

D45#

G21

HD#44

A31#

D44#

F21

HD#43

AG6

A30#

D43#

E21

HD#42

AD3

AD1

AC1

AG1

AH2

G11

D19

C20

AB2

AB3

AF1

AE1

AL1

AK1

AE8

AL2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

CPU1A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

HD#53

7

D53#

C14

HD#52

D52#

C15

HD#51

D51#

A14

HD#50

D50#

D17

HD#49

D49#

HD#48

HA#28

AF4

A29#

D42#

F20

HD#41

HA#27

AF5

A28#

D41#

E19

HD#40

HA#26

AB4

A27#

D40#

E18

HD#39

HA#25

AC5

A26#

D39#

F18

HD#38

6

HA#22

HA#24

HA#23

HA#20

HA#19

HA#21

AB5

AA5

AD6

AA4

A25#

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

D38#

D37#

D36#

D35#

D34#

D33#

F17

E16

E15

G17

G18

G16

HD#34

HD#33

HD#37

HD#32

HD#36

HD#35

N12-7750020-A10

6

HA#18

HA#16

HA#15

HA#17

AB6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D32#

D31#

D30#

D29#

F15

G15

G14

HD#29

HD#31

HD#28

HD#30

F14

HA#14

D28#

G13

HD#27

HA#13

D27#

E13

HD#26

HA#12

D26#

HD#25

D13

HA#11

D25#

F12

HD#24

HA#10

HA#8

HA#7

HA#9

U6

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D24#

D23#

D22#

D21#

F11

E10

D10

HD#20

HD#23

HD#21

HD#22

HA#5

HA#3

HA#6

HA#4

L5

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

D11

HD#17

HD#18

HD#19

HD#16

HD#15

5

R459 62R/4

AC2

AN3

DBR#

RSVD

D14#

D13#

D12#D8D11#

B12

C12

HD#11

HD#13

HD#14

HD#12

5

AN6

AN4

AN5

RSVD

VCC_SENSE

D10#

B10

A11

C11

HD#9

HD#10

AJ3

AK3

ITP_CLK1

ITP_CLK0

VSS_SENSE

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

HD#5

HD#6

HD#7

HD#8

VTT_OUT_RIGHT

VID2

VID6

VID3

VID4

VID5

AM5

AL4

AK4

AL6

VID6#

VID5#

VID4#

VID3#

GTLREF0

PCREQ#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

HD#1

HD#4

HD#3

HD#2

HD#0

4

VCC_VRM_SENSE 41

VSS_VRM_SENSE 41

VID6 41

VID5 41

VID4 41

VID3 41

VID2 41

VID1 41

VID0 41

VID1

VID0VID0

AM3

AL5

AM2

VID2#

VID1#

VID0#

H1

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

G5

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

RSVD

G6

RSVD

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

ZIF-SOCK775-15u

R469

62R/4

THERMTRIP#

AP339E

4

CPU_GTLREF0

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

HRS#2

HRS#1

HRS#0

HBR#0

H_COMP3

H_COMP2

H_COMP1

H_COMP0

NMI_SB

INTR

V_FSB_VTT

R450

2.7KR0402

Q27 2N3904_SOT23

VID PULL-HI

VID1

VID2

VID3

VID4

VID0

VID5

VID6

CPU_GTLREF0 7

R441 X_0R0402

R455 X_0R0402

R435 X_0R0402

H_BPM#0 8

PECI 24

HREQ#[0..4] 9

R379 62R/4

R226 62R/4

R453 62R/4

R213 62R/4

R394 130R/1%/4

R388 X_62R/4

CPUCLK# 5

CPUCLK 5

HRS#[0..2] 9

-HAP1 9

T13

HBR#0 7,9

R443 60.4R/1%/4

R242 60.4R/1%/4

HADSTB#1 9

HADSTB#0 9

HDSTBP#3 9

HDSTBP#2 9

HDSTBP#1 9

HDSTBP#0 9

HDSTBN#3 9

HDSTBN#2 9

HDSTBN#1 9

HDSTBN#0 9

NMI_SB 17

INTR 17

C411

0.1u/16V/4

2 1

TRIP# 17

3

H_COMP3

H_COMP2

VTT_OUT_RIGHT

H_TESTHI12

SMI#

H_TESTHI11

NMI_SB

INTR

H_TESTHI10

HINIT#

SLP#

H_TESTHI13

H_TESTHI9

IGNNE#

STPCLK#

A20M#

C405

0.1U/16V/Y5V/4

R449 X_100R/1%/4

R386 X_100R/1%/4

VTT_OUT_RIGHT

C414 0.1U/16V/Y5V/4

C424 0.1U/16V/Y5V/4

R398 680R/4

R413 680R/4

R412 680R/4

R429 680R/4

R416 680R/4

R422 680R/4

R417 680R/4

H_TESTHI8

H_TESTHI9

TEST_C9

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT

Prescott / Cedar Mill

LL_ID[1:0] = 00

GTLREF_SEL = 0

VTT_SEL = 1

BSEL

02

1

FSB FREQUENCY

267 MHZ (1067)000

0

01 200 MHZ (800)

1

0 0 133 MHZ (533)

3

VTT_OUT_RIGHT 7,8,24

RN36 62R/8P4R/4

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN32 62R/8P4R/4

R432 X_62R/4

R442 62R/4

R437 X_62R/4

R384 62R/4

1

2

3

4

5

6

7

8

RN35

62R/8P4R/4

VCCP

R438 60.4R/1%/4

R390 60.4R/1%/4

TABLE

2

VCC3

VCC3

R211

X_110R/1%/4

R212

X_61.9R/1%/4

VTT_OUT_LEFT

R481

X_2.2K/4

THERMTRIP#

VTT_OUT_LEFT

VTT_OUT_LEFT

C416

X_0.1U/16V/Y5V/4

VTT_OUT_LEFT 7,8

CE

B

Q31

X_2N3904_SOT23

FOR DUAL CORE CPU

RN33 51R/8P4R/4

1

2

3

4

5

6

7

8

1

2

3

4

51R/8P4R/4

5

6

7

8

R439 60.4R1%0402

R470 60.4R1%0402

R454 60.4R1%0402

R445 60.4R1%0402

R446 60.4R1%0402

PLACE BPM TERMINATION NEAR CPU

Micro Star Restricted Secret

Title

Intel LGA775 - Signals

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

2

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_BPM#2

RN37

H_BPM#4

H_TDO

H_TMS

H_TDI

H_TCK

H_TRST#

MS-7318-0B-060828E

1

R208

X_249R/1%/4

Q12

X_2N7002_SOT23

GTLREF_SEL 8,9

H_TESTHI0

C238

X_0.1U/16V/Y5V/4

RSMRST# 17,35

Last Revision Date:

Monday, August 28, 2006

Sheet

645

1

Rev

100

of

8

7

6

5

4

3

2

1

VCCP

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

W29

W28

W27

W26

W25

W24

W23

U26

U27

U28

U29

U30

VCCP

D D

C C

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

U23

U24

U25

N30

N23

N24

N25

N26

N27

N28

N29

M24

M25

M26

M27

M28

M29

M30

K27

K28

K29

K30

M23

T23

T24

T25

T26

T27

T28

T29

J30

K23

K24

K25

K26

AN9

AN8

AN30

AN29

AN26

HS11HS22HS33HS4

4

AN25

+1.5V

H_VCCA

A23

H_VSSA

B23

D23VCC

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

VTT_SEL VTT_SEL

F27

F29

ZIF-SOCK775-15u

R216 0R/4

R219 0R/4

R221 0R/4

7293

有上件

C241 1U/16V/Y5V/6

V_FSB_VTT

CAPS FOR FSB GENERIC

VTT_SEL 37

C256 0.1U/16V/Y5V/4

C254 1U/16V/Y5V/6

C245 10U/10V/Y5V/8

C243 X_10U10Y/8

R215

X_1K/4

VCC3

N12-7750020-A10

VTT_OUT_RIGHT CPU_GTLREF0

B B

VTT_OUT_RIGHT CPU_GTLREF1

R418 124R/1%/4 R380 X_124R/1%/4

R415

210R/1%/4

R423 124R/1%/4

R428

210R/1%/4

R393 10R/4

C393

1U/16V/Y5V/6

R410 10R/4

C395

1U/16V/Y5V/6

C390

220P/50V/NPO/4

C392

220P/50V/NPO/4

CPU_GTLREF0 6

CPU_GTLREF1 8

VTT_OUT_LEFT

R383

X_210R/1%/4

V_FSB_VTT CPU_GTLREF3

R223 X_124R/1%/4

R222

X_210R/1%/4

R376 X_10R/4

C389

X_1U/16V/Y5V/6

R227 X_10R/4

C240

X_1U/16V/Y5V/6

CPU_GTLREF2

C385

X_220P/50V/NPO/4

C246

X_220P/50V/NPO/4

CPU_GTLREF2 6

CPU_GTLREF3 6

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

V_FSB_VTT

L10

10uH/125mA/8

L9

10uH/125mA/8

C259

X_C1U16Y/6

10U/10V/Y5V/1206

C257

H_VCCA

C255

10U/10V/Y5V/1206

H_VSSA

CPU_GTLREF = 0.63 * VTT CPU_GTLREF = 0.63 * VTT

R484

680R/4

Q32

2N3904_SOT23

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_PWG

Micro Star Restricted Secret

Title

Intel LGA775 - Power

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

3

http://www.msi.com.tw

2

MS-7318-0B-060828E

Last Revision Date:

Monday, August 28, 2006

Sheet

745

1

Rev

100

of

VTT_OUT_RIGHT6,8,24

VTT_OUT_LEFT6,8

V_FSB_VTT

A A

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

8

RN38

1

3

5

7

62R/8P4R/4

R426 130R/1%/4

R420 300R/4

R385 62R/4

R230 62R/4

2

4

6

8

7

HIERR#

FERR#

PROCHOT#

CPU_GD

HBR#0

CPURST#

HIERR# 6

FERR# 6,17

PROCHOT# 6

CPU_GD 6,35

HBR#0 6,9

CPURST# 6,9

6

VTT_OUT_RIGHT

VCC5_SB

R490

1K/4

VID_GD#35,41

5

R491

1K/4

4

8

7

6

5

4

3

2

1

R214 0R/4

T6 R209 X_0R/4

T7

T8

E5R

CS_GTLREF

COMP7

D D

A12

A15

A18

A2

A21

A24

A6

A9

R231

1K/4

C C

B B

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

AB1

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AB7

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

CPU1C

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AC4

RSVD

VSS

AE30

AE4

AE3

COMP7

VSS

AE5

AE7

RSVD

RSVDD1RSVD

VSS

VSS

AF10

D14

VSS

AF13

E23

RSVD

VSS

AF16

E24

RSVDE5RSVDE6RSVDE7RSVD

CS_GTLREF

VSS

VSS

VSS

VSS

AF17

AF20

AF23

AF24

F23

VSS

AF25

IMPSEL

AF26

COMP8

B13

H2

RSVDF6RSVD

GTLVREF1

VSS

VSS

VSS

AF27

AF28

GTLVREF_NB

CPU_GTLREF1

J3R

COMP4

J2

RSVDJ3RSVDN4RSVD

COMP4

VSS

VSS

VSS

AF3

AF29

AF30

P5

VSS

AF6

COMP5

MSID1

T2

COMP5

VSS

AF7

MSID0

COMP6

W1

Y3

MSID1V1MSID0

VSS

VSS

AG10

AG13

AG16

GTLVREF_NB 9

CPU_GTLREF1 7

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

COMP6

VSS

VSS

VSS

VSS

VSS

AG7

AG17

AG20

AG23

AG24

VSS

AH1

VSS

VSS

AH10

VSS

AH13

VSS

AH16

V30

VSS

AH17

AH20

V29

VSSV3VSS

VSS

VSS

AH23

V28

VSS

VSS

AH24

V27

AH3

V26

VSS

VSS

AH6

R458 0R/4

V25

V24

V23

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

AH7

AJ10

AJ13

AJ16

AJ17

VSS

VSS

AJ20

VSS

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

R30

VSS

AJ29

R29

VSS

VSS

AJ30

R28

AJ4

R27

VSS

VSS

AJ7

VSS

VSS

R26

VSS

VSS

AK10

R25

VSS

VSS

AK13

R24

VSS

VSS

AK16

R23

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

AK2

AK17

AK20

VSS

VSS

AK23

P30

VSS

AK24

P29

VSS

VSS

AK27

P28

VSS

VSS

AK28

P27

VSS

VSS

AK29

P26

VSS

VSS

AK30

P25

AK5

VSS

VSS

P24

VSS

VSS

AK7

P23

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL10

AL13

AL16

AL17

AL20

AL23

VSS

AL24

VSS

AL27

L30

VSS

AL28

L29

VSSL3VSS

VSS

AL3

AL7

VSS

L28

VSS

VSS

AM1

L27

L26

VSS

VSS

AM10

AM13

VSS

VSS

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

AM23

K5

VSSK7VSS

VSS

VSS

AM24

K2

VSS

AM27

VSS

AM28

VSS

AM4

VID7#

AM7

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

H26

H27

H28

H29

VSS

VSS

VSS

GTLREF_SEL

VSS

VSS

VSS

VSS

AN2

AN17

AN20

AN23

H25

VSS

VSS

AN24

H24

VSS

VSS

AN27

H23

VSS

VSS

AN28

H19

H20

H21

H22

VSS

VSS

VSS

VSS

VID_SELECT

VSSB1VSS

VSS

B11

B14

AN7

GTLREF_SEL 6,9

VTT_OUT_LEFT

H17

H18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

R395 51R/4

G1R

R399

X_0R/4

H_BPM#06

R217

X_0R/4

V_FSB_VTT

MSID0

MSID1

R456 X_62R/4

R451 62R/4

R465 62R/4

MSID1

A A

2005 Perf FMB 0 0

2005 Value FMB 0 1 / NC

8

7

N12-7750020-A10

MSID0

0 ~ 1.2"

7 / 10 / 7

COMP4

COMP5

COMP6

COMP7

COMP8

J3R

E5R

IMPSEL

R457 Mount 50 Ohm Impedance

R457 Open 60 Ohm Impedance

R396 60.4R/1%/4

R452 60.4R/1%/4

R472 60.4R/1%/4

R434 60.4R/1%/4

R243 24.9R/1%/4

R409 1K/4

R375 1K/4

R364 51R1%0402

6

VTT_OUT_LEFT

VTT_OUT_RIGHT

5

VTT_OUT_LEFT 6,7

VTT_OUT_RIGHT 6,7,24

4

R431

X_0R/4

VTT_OUT_RIGHT

R425 680R/4

3

R419

X_0R/4

R391

X_62R/4

R414

0R/4

VID7

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

R397 1K/4

VID7 41

R392

0R/4

VTT_OUT_RIGHT

VRD_VIDSELVRD_VIDSEL

Micro Star Restricted Secret

Intel LGA775- GND

MS-7318-0B-060828E

Last Revision Date:

Monday, August 28, 2006

Sheet

2

VRD_VIDSEL 41

Rev

100

845

of

1

A

U17A

HA#3

HA#[3..33]6

4 4

3 3

HADSTB#06

HADSTB#16

HADS#6

HBNR#6

HBPRI#6

HBR#06,7

HDBSY#6

HDEFER#6

HDRDY#6

HIT#6

HITM#6

HLOCK#6

HTRDY#6

HREQ#[0..4]6

A

C338

C1U16Y

HRS#[0..2]6

HDBI#[0..3]6

C337

C1U16Y

CPURST#6,7

NBHCLK5

NBHCLK#5

C345

X_C1U16Y

R343

180R1%0402

GTLVREF_NB

V_FSB_VTT

2 2

C334

C0.1U16Y0402

C82 C83 Solder side

1 1

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

GTLCOMPP

GTLCOMPN

R337

360R1%0402

M33

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

W35

V32

V36

V34

W36

W34

AA36

V33

AA34

Y35

Y33

AA32

W32

V31

W31

Y31

AB31

R35

W33

L35

K35

J32

M34

K32

J33

K33

L36

L34

J34

M35

T32

T31

R32

M32

M31

J35

N36

J36

C31

E35

G27

D22

F22

AC29

AC30

U30

J25

G22

H22

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

NC#HA32#

NC#HA33#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

A17

A18

A19

VTT

VTT

VTT

PT890CE

GNDA1GNDA2GNDA8GND

GND

A3

A20

A10

B

A21

B17

B18

B19

B20

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

A22

A25

A27

A29

A31

B

V_FSB_VTT

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

Rev1.9

GND

GND

GND

GNDB2GNDB3GNDB4GND

GNDC2GNDC3GNDC4GND

GND

GND

GND

GNDD4GNDD5GNDD6GNDD8GND

GND

GND

C5

A33

A35

B36

D3

C26

C27

D11

D23

D24

F21

G17

VTT

VTT

GND

GND

D29

D31

C

G18

G19

G20

G21

HD00#

VTT

VTT

VTT

VTT

HD01#

HD02#

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTB0P#

HDSTB0N#

HDSTB1P#

HDSTB1N#

HDSTB2P#

HDSTB2N#

HDSTB3P#

HDSTB3N#

HADSTB0N#

DPWR#

GND

GND

GNDE2GNDE4GND

D32

D34

C

B35

A36

C33

C32

E31

B34

B33

A34

D30

A30

B31

B30

E30

C29

B29

C30

D36

F36

G36

H34

H35

F35

G35

C36

D35

F34

F33

G34

G33

E33

H32

G32

E28

E29

D28

D27

C28

H28

G28

F28

E27

D26

D25

E25

F25

G25

H26

H25

B23

B25

E23

B27

B28

A28

B24

B26

A26

C23

C22

A23

G23

A24

B22

E22

A32

B32

C35

C34

G26

E26

C24

C25

T35

L31

CP29

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

X_COPPER

1 2

1

T16

X_TP25

HD#[0..63] 6

HDSTBP#0 6

HDSTBN#0 6

HDSTBP#1 6

HDSTBN#1 6

HDSTBP#2 6GTLVREF_NB8

HDSTBN#2 6

HDSTBP#3 6

HDSTBN#3 6

GTLREF_SEL6,8

-HAP1 6

D

V_FSB_VTT

C343 C0.01U25X0402

C335 C0.01U25X0402

C331 C0.1U16Y0402

C340 C0.1U16Y0402

V_FSB_VTT

C653 C10U10Y0805

C650 C10U10Y0805

C647 C10U10Y0805

C649 X_C10U10Y0805

C654 X_C10U10Y0805

Solder side

R346

X_8.2KR0402

Q23

X_N-2N7002_SOT23

for dual code CPU

MEC1

VCCP+12V

R344

X_390R1%0402

DS

G

NB Heatsink

U2_1

MEC1

HS-MS7059

V_FSB_VTT

R325

124R1%0402

R327

210R1%0402

GTLVREF_NB

MEC2

E

MEC2

GND

E6

E5

D

Title

PT890CE-1(HOST)

Size Document Number Rev

MS-7318-0B-060828E 100

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

945Monday, August 28, 2006

E

A

VCC_DDR

4 4

MD0

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

AF35

AG34

AJ36

AK35

AF34

AG35

AJ34

AK34

AG32

AF32

AH30

AJ31

AF31

AH32

AH31

AJ32

AK33

AL36

AP35

AL34

AL35

AM35

AT36

AM34

AK24

AL23

AM24

AJ22

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AL20

AM20

AL18

AM18

AR17

AT16

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AT18

AT21

AR21

AT19

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AT12

AP12

AH36

AF30

AN36

AN23

AN20

AT15

AP21

AT13

MD[0:63]13

3 3

2 2

DQM[0:7]13

U17B

MD00

MD01

MD02

MD03

MD04

MD05

MD06

MD07

MD08

MD09

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

AA24

AB24

VCCMEM

VCCMEM

AC24

AD16

VCCMEM

VCCMEM

AD17

AD19

AD18

VCCMEM

VCCMEM

AD21

AD20

VCCMEM

VCCMEM

VCCMEM

AD23

AD22

VCCMEM

VCCMEM

AD24

AJ26

VCCMEM

VCCMEM

AJ28

VCCMEM

AK25

AK27

VCCMEM

VCCMEM

AK29

AL26

VCCMEM

VCCMEM

AL28

AL30

VCCMEM

VCCMEM

B

AM25

AM27

VCCMEM

VCCMEM

AM29

AM31

VCCMEM

VCCMEM

AN26

AN27

AN31

VCCMEM

VCCMEM

AN33

AP30

VCCMEM

VCCMEM

VCCMEM

AR26

C512

C4.7U10X50805-RH

AT35

AR33

AT25

AT28

AT31

BA0

BA1

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

VCCMEM

BA2

MA00

MA01

MA02

MA03

MA04

MA05

MA06

MA07

MA08

MA09

MA10

MA11

MA12

MA13

SRAS#

SCAS#

SWE#

CS0#

CS1#

CS2#

CS3#

CKE0

CKE1

CKE2

CKE3

ODT0

ODT1

ODT2

ODT3

DQS0+

NC#DQS0-

DQS1+

NC#DQS1-

DQS2+

NC#DQS2-

DQS3+

NC#DQS3-

DQS4+

NC#DQS4-

DQS5+

NC#DQS5-

DQS6+

NC#DQS6-

DQS7+

NC#DQS7-

MCLKI

MCLKO+

MCLKO-

MEMVREF0

MEMVREF1

MEMDET

DMCOMP

C431

C4.7U10X50805-RH

C4.7U10X50805-RH

BA0

AR28

BA1

AP29

BA2

AP33

MAA0

AT29

MAA1

AR30

MAA2

AR29

MAA3

AT30

MAA4

AN30

MAA5

AP31

MAA6

AR31

MAA7

AT32

MAA8

AP32

MAA9

AN32

MAA10

AN29

MAA11

AR32

MAA12

AT33

MAA13

AR25

-SRASA

AN28

-SCASA

AR27

-SWEA

AP28

AT27

AP27

AT24

AP26

CKEA0

AT34

CKEA1

AP34

CKEA2

AR34

CKEA3

AN34

AT26

AP25

AR24

AN25

AP381

AJ35

AH35

AH33

AH34

AR36

AP36

AR22

AP23

AP18

AN18

AP15

AR15

AP20

AR20

AR12

AR13

MCLKIT

AB34

M_CLKO+

AB35

M_CLKO-

AB36

MVREF_NB

AG29

AJ18

MEMDET

Pull-high: DDR2

Pull-down: DDR1

MEMDET

AF36

AM33

C522

C462

C4.7U10X50805-RH

C4.7U10X50805-RH

BA0 13

BA1 13

BA2 13

MAA[0:13] 13

-SRASA 13

-SCASA 13

-SWEA 13

-CS0 13

-CS1 13

-CS2 13

-CS3 13

CKEA0 13

CKEA1 13

CKEA2 13

CKEA3 13

ODT0 13

ODT1 13

ODT2 13

ODT3 13

-DQS0 13

-DQS1 13

-DQS2 13

-DQS3 13

-DQS4 13

-DQS5 13

-DQS6 13

-DQS7 13

R482 22R0402

R475 22R0402

R492 1KR0402

R508 301R1%0402

C

C497

C4700P16X0402

VCC_DDR

D

VCC_DDR

C4700P16X0402

C527

C4700P16X0402

C526

C549

C4700P16X0402

Test Point

(Place near their respective balls of NB)

C472 C5P50N0402

C473 C5P50N0402

C454 C5P50N0402

C456 C5P50N0402

C453 C5P50N0402

C471 C5P50N0402

C488 C5P50N0402

C457 C5P50N0402

C477 C5P50N0402

C492 C5P50N0402

C491 C5P50N0402

C460 C5P50N0402

C486 C5P50N0402

C442 C5P50N0402

C458 C5P50N0402

C490 C5P50N0402

C478 C5P50N0402

C489 C5P50N0402

C476 C5P50N0402

C439 C5P50N0402

C554

C4700P16X0402

C545

C0.1U16Y0402

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0

BA1

BA2

-SRASA

-SCASA

-SWEA

C551

C529

C1U16Y

PULL DOWN GND OR PULL UP +1.8VDIMM

CLOSE TO DIMM

NOTE: DQS/DQS# => OTHER:W:S:W:OTHER=15:10:5:10:15

MCLKO+/- as short as passable

MCLKIT = DCLKx + 2 "

MCLKIT 5

MCLKOT 5

MCLKOC 5

C420 X_C5P50N0402

C422 X_C5P50N0402

C417 X_C5P50N0402

Near to NB chip

VCC_DDR

VCC_DDR

R444

150R1%0402

MVREF_NB

R440

150R1%0402

VCC_DDR

NEAR PT890CE

C400

C1000P16X0402

C1000P16X0402

Close to ball

C548 C0.1U16Y0402

C534 C0.1U16Y0402

C547 C0.1U16Y0402

C533 C0.1U16Y0402

C552 C0.1U16Y0402

C535 C0.1U16Y0402

C550 C0.1U16Y0402

C532 C0.1U16Y0402

NEAR DIMM

VCC_DDR

C553 C0.1U16Y0402

C546 C0.1U16Y0402

C530 C0.1U25Y

C402

C397

C1000P16X0402

Solder side

C669

C670

C1U16Y

C1U16Y

C666

C1U16Y

Solder side

C673

C1U16Y

E

C668

C1U16Y

C671

C1U16Y

C672

C1U16Y

GNDE7GND

GND

E9

E34

PT890CE

GND

GNDF1GNDF2GNDF4GNDF5GNDF6GNDF7GND

E36

GND

GND

GND

GND

GND

GND

GND

GNDG1GNDG2GNDG4GNDG7GND

GND

GNDH2GNDH4GNDH7GND

GND

GND

GND

GND

GND

F10

F14

F23

F26

F27

F29

F30

F32

F24

G11

B

G29

H23

GNDJ2GNDJ4GNDJ5GNDJ6GND

GND

H24

H27

H31

J7

H36

H33

C

D

Title

PT890CE-2(MEM)

Size Document Number Rev

MS-7318-0B-060828E 100

Date: Sheet

MICRO-START INT'L CO.,LTD.

of

10 45Monday, August 28, 2006

E

1 1

A

4

VCC3

3

2

1

VCC3

W13

Y13

AA13

AB13

AC13

AJ1

AJ2

AJ3

AJ4

AJ5

VCC33PEX

VCC33PEX

VCC33PEX

GNDM5GNDM7GND

M2

M36

AJ6

AJ7

AK1

AK2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

GNDN2GNDN5GNDN7GNDP2GNDP7GND

GNDP5GND

P6

AK3

AK4

AK5

VCC33PEX

VCC33PEX

VCC33PEX

GND

P14

P15

AK6

AK7

VCC33PEX

VCC33PEX

PEXWAKE#

PEXHPSCI#

PEXPMESCI#

PEXCOMP0

PEXCOMP1

PEXREXT0

PEXREXT1

PEXCOMP2

PEXREXT2

GND

GND

GND

P16

P17

P18

PEXTX00+

PEXTX00-

PEXTX01+

PEXTX01-

PEXTX02+

PEXTX02-

PEXTX03+

PEXTX03-

PEXTX04+

PEXTX04-

PEXTX05+

PEXTX05-

PEXTX06+

PEXTX06-

PEXTX07+

PEXTX07-

PEXTX08+

PEXTX08-

PEXTX09+

PEXTX09-

PEXTX10+

PEXTX10-

PEXTX11+

PEXTX11-

PEXTX12+

PEXTX12-

PEXTX13+

PEXTX13-

PEXTX14+

PEXTX14-

PEXTX15+

PEXTX15-

PEXRX00+

PEXRX00PEXRX01+

PEXRX01PEXRX02+

PEXRX02PEXRX03+

PEXRX03PEXRX04+

PEXRX04PEXRX05+

PEXRX05PEXRX06+

PEXRX06PEXRX07+

PEXRX07PEXRX08+

PEXRX08PEXRX09+

PEXRX09PEXRX10+

PEXRX10PEXRX11+

PEXRX11PEXRX12+

PEXRX12PEXRX13+

PEXRX13PEXRX14+

PEXRX14PEXRX15+

PEXRX15-

PEXTX16+

PEXTX16-

PEXRX16+

PEXRX16-

PEXCLK+

PEXCLK-

INTR#

PEXDET

TCSEN#

GND

GND

P19

P20

B1

C1

D1

E1

H1

J1

K1

L1

L4

M4

M1

N1

N4

P4

P1

R1

T1

U1

U4

V4

V1

W1

W4

Y4

Y1

AA1

AB1

AC1

AC4

AD4

AD1

AE1

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

PEDET

TCSEN#

PE0RCOMP0

PE0RCOMP1

PE0REXT0

PE0REXT1

PE1RCOMP

PE1REXT

3

PE0TX0+ 14

PE0TX0- 14

PE0TX1+ 14

PE0TX1- 14

PE0TX2+ 14

PE0TX2- 14

PE0TX3+ 14

PE0TX3- 14

PE0TX4+ 14

PE0TX4- 14

PE0TX5+ 14

PE0TX5- 14

PE0TX6+ 14

PE0TX6- 14

PE0TX7+ 14

PE0TX7- 14

PE0TX8+ 14

PE0TX8- 14

PE0TX9+ 14

PE0TX9- 14

PE0TX10+ 14

PE0TX10- 14

PE0TX11+ 14

PE0TX11- 14

PE0TX12+ 14

PE0TX12- 14

PE0TX13+ 14

PE0TX13- 14

PE0TX14+ 14

PE0TX14- 14

PE0TX15+ 14

PE0TX15- 14

PE0RX0+ 14

PE0RX0- 14

PE0RX1+ 14

PE0RX1- 14

PE0RX2+ 14

PE0RX2- 14

PE0RX3+ 14

PE0RX3- 14

PE0RX4+ 14

PE0RX4- 14

PE0RX5+ 14

PE0RX5- 14

PE0RX6+ 14

PE0RX6- 14

PE0RX7+ 14

PE0RX7- 14

PE0RX8+ 14

PE0RX8- 14

PE0RX9+ 14

PE0RX9- 14

PE0RX10+ 14

PE0RX10- 14

PE0RX11+ 14

PE0RX11- 14

PE0RX12+ 14

PE0RX12- 14

PE0RX13+ 14

PE0RX13- 14

PE0RX14+ 14

PE0RX14- 14

PE0RX15+ 14

PE0RX15- 14

PETP1 14

PETN1 14

PERP1 14

PERN1 14

PECLK_NB 5

PECLK_NB# 5

PIRQ#H 15

PEWAKE# 14,16

PEHPSCI# 17

PEPMESCI# 16

FB21 X_120L600m_250

CP27 X_COPPER

C381

C22U10Y1206

VCC3 VCC3 VCC3

FB13 X_120L600m_250

CP19 X_COPPER

VCCA33PE1 VCCA33PE01 VCCA33MCK

C363

C22U10Y1206

21

1 2

VCCA33PE VCCA33PE00 VCCA33HCK

C367

C1000P16X0402

21

1 2

C356

C1000P16X0402

+1.5V

R430

1KR1%0402

430R1%0402

LVREF_NB

R411

LVREF_NB => 0.45V

VCC3

R312 4.7KR0402

R310 4.7KR0402

R295 249R1%0402

R361 249R1%0402

R299 10.7KR1%0402

R358 10.7KR1%0402

R356 249R1%0402

R354 10.7KR1%0402

T13

U13

V13

R13

N13

N14

P13

U17C

5 5

4 4

+1.5V

3 3

2 2

1 1

VLAD017

VLAD117

VLAD217

VLAD317

VLAD417

VLAD517

VLAD617

VLAD717

VBE017

UPSTB17

-UPSTB17

DNSTB17

-DNSTB17

UPCMD17

DNCMD17

R421 270R1%0402

R424

340R1%0402

GCLK_NB5

+1.5VSUS

-SUSST16

NB_RST#35

-PWROK_NB16

+1.5VSUS

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0

UPSTB

-UPSTB

DNSTB

-DNSTB

UPCMD

DNCMD

LVREF_NB

LCOMPP

LCOMPN

+1.5V

TESTIN_NB

VCCA33HCK

VCCA33MCK

VCCA33PE00

VCCA33PE01

VCCA33PE

VCCA33PE1

4

AN3

AT3

AR4

AN2

AN1

AP5

AN5

AN4

AT2

AR3

AR1

AT1

AR5

AP4

AM5

AD13

AD14

AD15

M12

M13

M14

M15

M16

M20

M21

M22

M23

M24

N12

N25

R12

U12

U25

W12

W25

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AE6

AH5

AH3

AF7

AC32

AD29

AE7

AH6

AH4

AP1

AL6

AL5

AL4

P12

P25

T12

T25

V12

Y12

Y25

VD00

VD01

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTIN#

RESET#

PWROK

VCCA33HCK

VCCA33MCK

G6

VCCA33PEX0

VCCA33PEX1

VCCA33PEXCK

VCCA33PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

H6

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

VCC33PEX

GND

GND

K4

K2

VCC33PEX

VCC33PEX

VCC33PEX

GNDK5GNDK7GND

K31

K34

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PT890CE

GND

GND

GNDL2GNDL7GND

GNDL5GND

K36

VCC33PEX

VCC33PEX

VCC33PEX

GND

L32

L33

VCC3 VCC3

C370

C0.1U25Y

C359

C0.1U25Y

FB3 X_120L600m_250

C297

C22U10Y1206

FB17 X_120L600m_250

CP23 X_COPPER

C368

C22U10Y1206

C394

C0.1U16Y0402

1 2

1 2

C396

C1U16Y

21

C303

C1000P16X0402

21

C355

C1000P16X0402

Solder side

2

FB24 X_120L600m_250

CP31 X_COPPER

C300

C0.1U25Y

C365

C0.1U25Y

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x

Disable all TEST mode

TESTIN_NB

C430

C22U10Y1206

R495 4.7KR0402

R488 X_4.7KR0402

21

1 2

C429

C1000P16X0402

FB23 X_120L600m_250

CP30 X_COPPER

C436

C22U10Y1206

21

1 2

C435

C1000P16X0402

Title

Size Document Number Rev

Date: Sheet

VCC_DDR

PT890CE-1(PCIE)

MS-7318-0B-060828E 100

+1.5V

C667 C4.7U10Y0805

C659 X_C4.7U10Y0805CP9 X_COPPER

C652 C4.7U10Y0805

C655 X_C4.7U10Y0805

C437

C0.1U25Y

C663 C2.2U6.3X5

C665 C2.2U6.3X5

C651 C2.2U6.3X5

C662 C2.2U6.3X5

under NB( solder side)

+1.5V

C399 C0.1U16Y0402

C403 C0.1U16Y0402

C401 C0.1U16Y0402

C438

C0.1U25Y

C286 C0.1U16Y0402

C404 C0.1U16Y0402

Decoupling capacitors

VCC3

C373

C0.1U16Y0402

MICRO-START INT'L CO.,LTD.

of

1

11 45Monday, August 28, 2006

A

B

C

D

E

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y30

Y32

Y34

Y36

AA2

AA4

AA5

AA7

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA31

AA33

AA35

AB2

AB4

AB5

AB7

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC2

AC5

AC6

AC7

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AD2

AD5

AD32

AE2

AE5

AE32

AE34

AF2

AF3

AF5

AG2

AG3

AG4

AG5

AG30

AG31

AG33

AG36

Y5

Y6

Y7

V_FSB_VTT

U17E

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AJ19

D

M17

PT890CE

GND

AJ23

AJ20

VTT

GND

M18

AJ33

VTT

GND

M19

VTT

GND

AK17

N18

AK18

VTT

GND

N19

AK22

VTT

GND

N20

VTT

GND

AK32

+1.5V

T24

R24

N22

N23

N24

P24

N21

VTT

GND

AK36

U24

V24

W24

Y24

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

AL3

AL7

AL15

AL16

AL17

AL19

AL22

AL24

AL33

Title

Size Document Number Rev

Date: Sheet

AE14

VTT

VTT

VCC15

AE16

VCC15

GND

AM2

GND

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

AM36

GND

AN12

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AN13

AE18

AE20

AE21

AE22

AJ10

AJ11

AJ12

AJ13

AJ14

AK9

AK10

AK11

AK12

AK13

AK15

AL8

AL9

AL10

AL11

AL12

AL14

AM7

AM8

AM9

AM10

AM11

AM12

AM13

AN7

AN8

AN9

AN10

AN11

AP7

AP8

AP9

AP10

AP11

AR7

AR8

AR9

AR10

AT7

AT8

AT9

AT10

AN17

AN19

AN35

AP2

AP3

AP6

AP16

AP22

AP24

AR2

AR6

AR16

AR23

AR35

AT4

AT11

AT14

AT17

AT20

AT22

AT23

+

12

EC52

X_CD470U6.3EL11-RH-1

+1.5V

C664 C0.1U25Y

C661 C0.1U25Y

C656 C0.1U25Y

C660 C0.1U25Y

C658 C0.1U25Y

MICRO-START INT'L CO.,LTD.

PT890CE-4(VLINK)

MS-7318-0B-060828E 100

E

of

12 45Monday, August 28, 2006

VCC3 VCC3

C657

C1U16Y

4 4

Solder side

U17D

AP381

AM1

NC#AM1

AM3

NC#AM3

AT5

NC#AT5

AM6

NC#AM6

AL2

NC#AL2

AL1

NC#AL1

AN6

NC#AN6

AT6

NC#AT6

T15

X_TP25

3 3

1

VCCDAC1

VCCDAC2

R321 X_80.6R1%0402

PIRQ#A15,18,31

GUICK5

2 2

R305 0R0402

R307 0R0402

VCCPLL1

VCCPLL2

VCCPLL3

VCC3

FB7 X_120L600m_250

CP13 X_COPPER

1 2

21

VCCDAC1

C324

C1000P16X0402

C313

C1U16Y

AM4

C14

D14

E14

E12

F12

A13

A12

B13

B12

C13

H13

B8

A6

D12

A16

A15

A14

B16

B15

B14

NC#AM4

NC#C14

NC#D14

NC#E14

HSYNC

VSYNC

VCCA33DAC1

VCCA33DAC2

GNDADAC1

GNDADAC2

NC#C13

INTA#

GPO0

GPOUT

XIN

VCCA33PLL1

VCCA33PLL2

VCCA33PLL3

GNDAPLL1

GNDAPLL2

GNDAPLL3

GND

P21

N15

GND

P22

P23

N16

N17

VCC33GFX

VCC33GFX

VCC33GFX

GND

GNDR2GND

GND

GND

P35

P33

U18

U19

GND

GND

GNDR5GNDR6GNDR7GND

R4

U20

U21

GND

PT890CE

GND

U22

U23

U31

U33

V14

V15

V16

V17

V18

V19

V20

V22

V21

V23

V30

V35

W14

W15

W16

W17

W18

W19

W20

W21

W22

W23

GND

GND

GND

GND

GNDV2GNDV5GNDV7GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDW2GNDW5GNDW7GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GNDT2GNDT4GNDT5GNDT7GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

T14

T15

T16

T17

T18

T19

R14

R15

R16

R17

R18

R19

R20

R21

R23

R30

R31

R22

FD4 1: 24bit / 0:2 x 12 bit DVI interface

FD5 Dedicated DVI port configuration 0:TMDS 1:TV-encoder

FD6 Dedicated DVI port 0:disable 1:enable

FD7 GFX clock select(VCK/LCDCK/ECK) 0:refer internal PLL 1:from external

FD10 CPUCK/MCK clock select 0from NB 1:from external

T20

GNDU2GNDU5GNDU7GND

T21

T22

T23

T34

T36

U14

FD[0:1:2:3:8:9:11] Reserved

Y2

GND

GND

U15

D13

F13

C12

GND

GND

FPDEN0

FPDET0

DISPCLKO

DISPCLKI

GND

GND

U16

U17

FP00

GND

FP01

FP02

FP03

FP04

FP05

FP06

FP07

FP08

FP09

FP10

FP11

NC#C6

NC#A5

FPCLK0

FPHS0

FPVS0

SPCLK1

SPCLK2

SPD1

SPD2

BUSY#

ENBLT

ENVDD

H11

D10

C11

C10

E10

G10

F11

C9

E8

B7

F9

C7

C6

A5

B9

D9

A9

E11

B10

C8

G13

A7

E13

AC35

H12

G12

A11

B11

FD07

FD08

FD09

FD10

DISPCLK0

DISPCLK1

FD08R

FD09

FD07

FD10

R323 4.7KR0402

R320 4.7KR0402

R483 0R0402

R318 22R0402

VCC3

R313 X_0R0402

1

2

3

4

5

6

7

8

RN26

8P4R-10KR0402

VCC5

-AGPBZ 17

EC23

+

1 2

FD08