Page 1

5

4

3

2

1

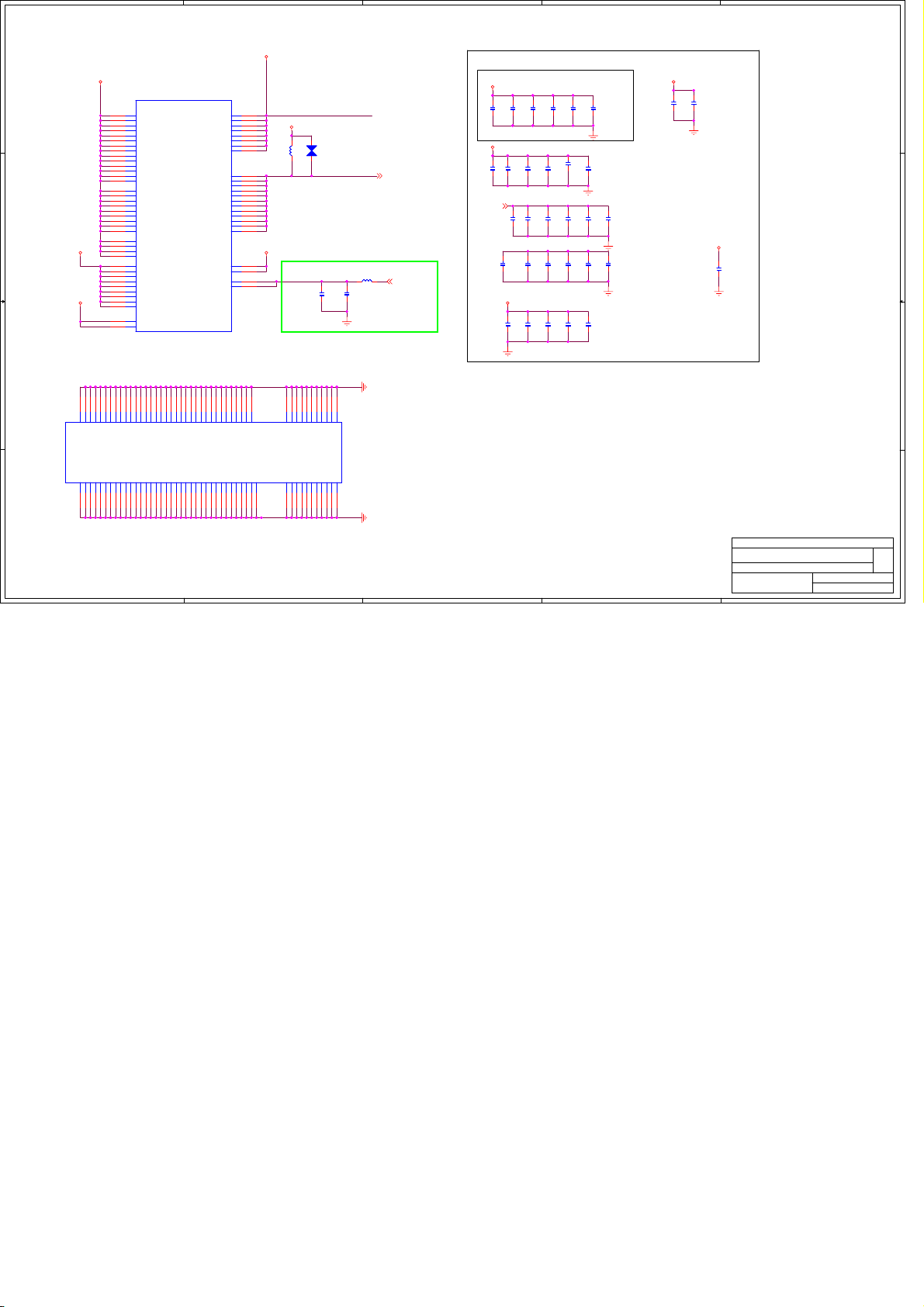

MSI

D D

MS-7214 Ver:1.0

CPU:

AMD 940 Athlon 64/Athlon 64 FX

System Chipset:

NVIDIA C51PV / C51G

NVIDIA MCP 51

On Board Chipset:

LPC Super I/O -- W83627EHF REV:C

LAN -- VSC8201 / RTL8201CL

AZALIA Codec --ALC880

BIOS --LPC FLASH ROM 4M

C C

Main Memory:

DDR * 4 (Max 4GB)

Expansion Slots:

PCI-E X 16 *1

PCI-E X 1 *1

PCI 2.2 Slot X 1

PWM:

Controller--Intersil ISL6566CR 3 Phase

B B

Title Page

Cover Sheet 1

Block Diagram

2

3GPIO SPEC

4,5,6AMD 940

System Memory

/ DDR Terminations

7,8

C51-G 9-11

MCP51 12-15

PCI Slot 1&2

PCI-Express X 16 & X1 PORT

W627EHF LPC I/O / BIOS

LAN - VSC8201 / RTL8201CL

Azalia Audio - ALC880

1394 Controller-VT6307

USB connectors

K8 PWM ISL6566CR

MS-6 ACPI Controller & MS-6+

KB/MS/LPT/COM/TPM/EMI

ATA 66/100/133 Connectors

ATX Connector / Front Panel

TV-OUT

VGA / DVI

Manual Parts

POWER OK MAP

POWER MAP

RESET MAP

MANUAL PARTS

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Cover Sheet

Cover Sheet

Cover Sheet

Document Number

Document Number

Document Number

5

4

3

2

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7214

MS-7214

MS-7214

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

135

135

135

of

of

of

Rev

Rev

Rev

0C

0C

0C

Page 2

5

4

3

2

1

BLOCK DIAGRAM

D D

C C

PRIMARY IDE

SECONDARY IDE

X4 - SATA CONN

B B

PS2/KBRD CONN

POWER

SUPPLY

CONNECTOR

PEX X16, PEX X1

ATA 133

INTEGRATED SATA 1/2

SIO

LPC SUPER I/O

W83627EHF

VREG

PCI EXPRESS

LPC BUS 33MHZ

LPC HDR

4MB FLASH

SOCKET 940

K8

NFORCE

CRUSH 51

468 BGA

NFORCE

MCP 51

508 BGA

HT 16X16 1GHZ

HT 8X8 1GHZ

128-BIT 200/266/333/400MHZ

AZAILIA/AC97

X8 USB2

SVDIO CONN

VGA CONN

DVI CONN

PCI 33MHZ

Realtek 8201CL

Realtek ALC 880 rev C (Azalia, 7.1Channel)

USB2 PORTS 0-1

USB2 PORTS 2-3

USB2 PORTS 4-5

USB2 PORTS 6-7

DDR SDRAM CONN 0

DDR SDRAM CONN 1

1394-VT6307

PCI SLOT 1

Mini PCI SLOT1

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

Block Diagram

Block Diagram

Block Diagram

MS-7214

MS-7214

MS-7214

1

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

of

2

of

2

of

2

Rev

Rev

Rev

0C

0C

0C

35

35

35

Page 3

5

4

3

2

1

C-51G GPIO FUNCTION

D D

NAME Function Description

GPIO_1

GPIO_2/CPU_SLP*

GPIO_3/CPU_CLKRUN*

GPIO_4/SUS_STAT* MII_phy reset

C C

VSET2 VSET1 VSET0 Voltage

B B

NC

NC

BIOS WRITE PROTECT

0

(Reserved)

1.65V

1.6V

1.55V

Vcore Adjust

1

11

11

00

0

1 1 1 1.5V

SIO GPIO FUNCTION

NAME Function Description

GPSA1 VSET0 ( CPU Vcore Control )

GPSB1

GPSB2

GP13

GP14

GP16

GP17

GP32

GP33

GP44

GP45

GP57/PSOUT#

GP56/PSIN

GP53/PSON# PS_ON# (ATX_PWR_ON#)

VSET1 ( CPU Vcore Control )

VSET2 ( CPU Vcore Control )

FOR BIOS

FOR BIOS

VSET2 ( CPU Vcore Control )

NC

NC

NC

NC

NC

PSOUT# (PWRBTN#)

PSIN (FP_RST#)

A A

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

5

4

3

2

http://www.msi.com.tw

GPIO SPEC

GPIO SPEC

GPIO SPEC

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

0C

0C

0C

of

of

of

335

335

335

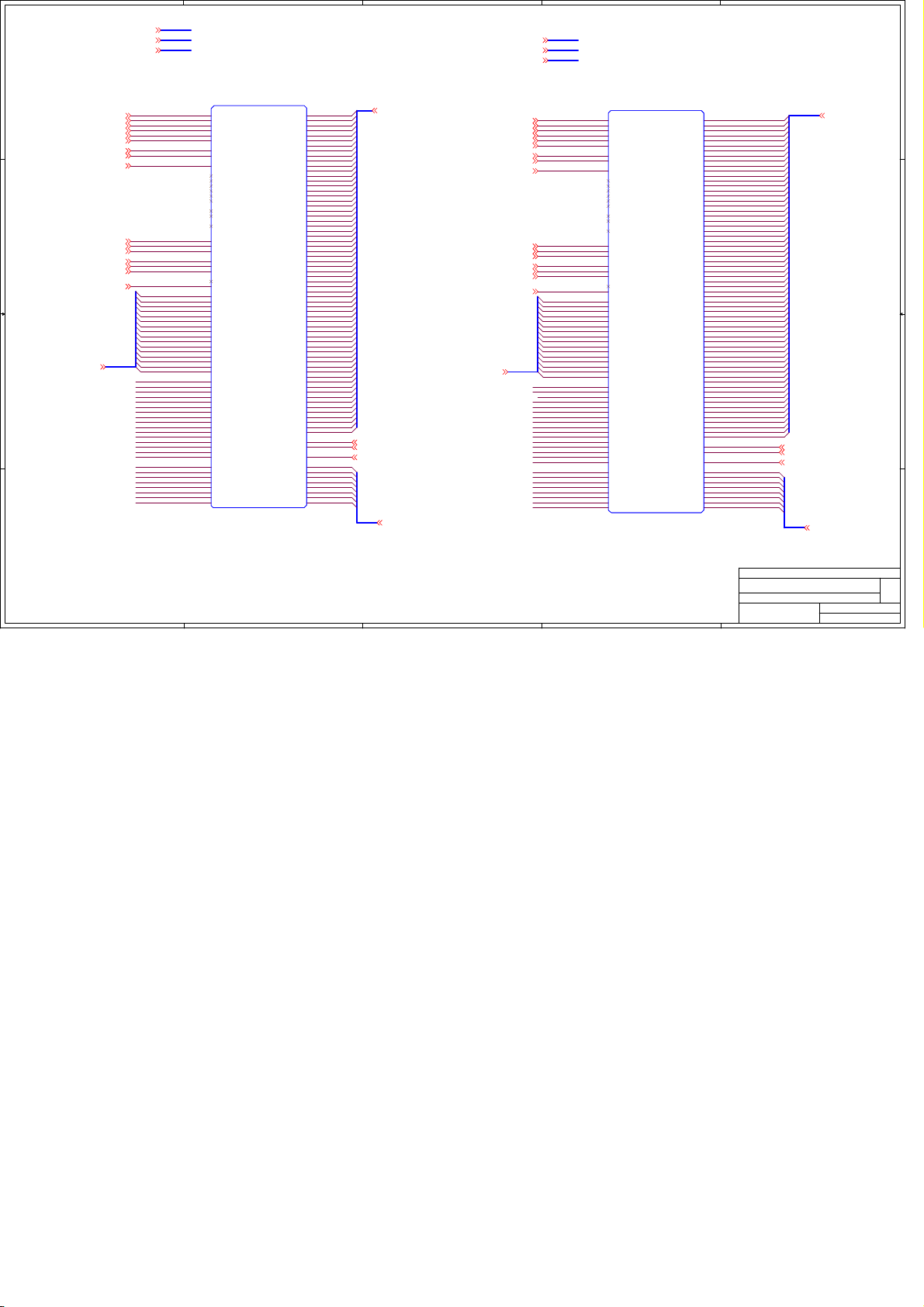

Page 4

5

C259

C259

C4.7U10Y0805

C4.7U10Y0805

HT_CLKIN_H19

HT_CLKIN_L19

HT_CLKIN_H09

HT_CLKIN_L09

R195 47.5R1%0402R195 47.5R1%0402

R196 47.5R1%0402R196 47.5R1%0402

HT_CTLIN_H09

HT_CTLIN_L09

HT_CADIN_H15

HT_CADIN_L15

HT_CADIN_H14

HT_CADIN_L14

HT_CADIN_H13

HT_CADIN_L13

HT_CADIN_H12

HT_CADIN_L12

HT_CADIN_H11

HT_CADIN_L11

HT_CADIN_H10

HT_CADIN_L10

HT_CADIN_H9

HT_CADIN_L9

HT_CADIN_H8

HT_CADIN_L8

HT_CADIN_H7

HT_CADIN_L7

HT_CADIN_H6

HT_CADIN_L6

HT_CADIN_H5

HT_CADIN_L5

HT_CADIN_H4

HT_CADIN_L4

HT_CADIN_H3

HT_CADIN_L3

HT_CADIN_H2

HT_CADIN_L2

HT_CADIN_H1

HT_CADIN_L1

HT_CADIN_H0

HT_CADIN_L0

C250

C250

C0.1U16X

C0.1U16X

HT_CADIN_H[15..0]

HT_CADIN_L[15..0]

HT_CADOUT_H[15..0]

HT_CADOUT_L[15..0]

C251

C251

C4.7U10Y0805

C4.7U10Y0805

CPU_M_VREF

C244

C244

C1000P50X

C1000P50X

5

C263

C263

C252

C252

C600

C0.22U16X

C0.22U16X

C600

C0.22U16X

C0.22U16X

CPU1A

CPU1A

HYPERTRANSPORT

HYPERTRANSPORT

L0_CLKOUT_H(1)

L0_CLKOUT_H(0)

L0_CADOUT_H(15)

L0_CADOUT_L(15)

L0_CADOUT_H(14)

L0_CADOUT_L(14)

L0_CADOUT_H(13)

L0_CADOUT_L(13)

L0_CADOUT_H(12)

L0_CADOUT_L(12)

L0_CADOUT_H(11)

L0_CADOUT_L(11)

L0_CADOUT_H(10)

L0_CADOUT_L(10)

L0_CADOUT_H(9)

L0_CADOUT_L(9)

L0_CADOUT_H(8)

L0_CADOUT_L(8)

L0_CADOUT_H(7)

L0_CADOUT_L(7)

L0_CADOUT_H(6)

L0_CADOUT_L(6)

L0_CADOUT_H(5)

L0_CADOUT_L(5)

L0_CADOUT_H(4)

L0_CADOUT_L(4)

L0_CADOUT_H(3)

L0_CADOUT_L(3)

L0_CADOUT_H(2)

L0_CADOUT_L(2)

L0_CADOUT_H(1)

L0_CADOUT_L(1)

L0_CADOUT_H(0)

L0_CADOUT_L(0)

L0_CLKOUT_L(1)

L0_CLKOUT_L(0)

L0_CTLOUT_H(1)

L0_CTLOUT_L(1)

L0_CTLOUT_H(0)

L0_CTLOUT_L(0)

C4.7U10Y0805

C4.7U10Y0805

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

L0_CLKIN_H(1)

L0_CLKIN_L(1)

L0_CLKIN_H(0)

L0_CLKIN_L(0)

L0_CTLIN_H(1)

L0_CTLIN_L(1)

L0_CTLIN_H(0)

L0_CTLIN_L(0)

L0_CADIN_H(15)

L0_CADIN_L(15)

L0_CADIN_H(14)

L0_CADIN_L(14)

L0_CADIN_H(13)

L0_CADIN_L(13)

L0_CADIN_H(12)

L0_CADIN_L(12)

L0_CADIN_H(11)

L0_CADIN_L(11)

L0_CADIN_H(10)

L0_CADIN_L(10)

L0_CADIN_H(9)

L0_CADIN_L(9)

L0_CADIN_H(8)

L0_CADIN_L(8)

L0_CADIN_H(7)

L0_CADIN_L(7)

L0_CADIN_H(6)

L0_CADIN_L(6)

L0_CADIN_H(5)

L0_CADIN_L(5)

L0_CADIN_H(4)

L0_CADIN_L(4)

L0_CADIN_H(3)

L0_CADIN_L(3)

L0_CADIN_H(2)

L0_CADIN_L(2)

L0_CADIN_H(1)

L0_CADIN_L(1)

L0_CADIN_H(0)

L0_CADIN_L(0)

0B 06/01/09 Modify

VCC3

R444

R444

4.7K

4.7K

CPU_THRIP# CPU_THRIP_C#

VCC3

C253

C253

_C10P25N0402/0.25

_C10P25N0402/0.25

R443

R443

19.6K1%

19.6K1%

R445

R445

34.8K1%

34.8K1%

D S

HT_CADIN_H[15..0]9

HT_CADIN_L[15..0]9

HT_CADOUT_H[15..0]9

HT_CADOUT_L[15..0]9

D D

VCC1_2HT

VCC1_2HT

C C

B B

VCC_DDR

R163

R163

_15R1%0805-1

_15R1%0805-1

R164

R164

_15R1%0805-1

_15R1%0805-1

A A

CPU_THRIP#12

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

BSS138

BSS138

Q53

Q53

G

4

C601

C601

_C10P25N0402/0.25

_C10P25N0402/0.25

HT_CLKOUT_H1 9

HT_CLKOUT_L1 9

HT_CLKOUT_H0 9

HT_CLKOUT_L0 9

HT_CTLOUT_H0 9

HT_CTLOUT_L0 9

HT_CADOUT_H15

HT_CADOUT_L15

HT_CADOUT_H14

HT_CADOUT_L14

HT_CADOUT_H13

HT_CADOUT_L13

HT_CADOUT_H12

HT_CADOUT_L12

HT_CADOUT_H11

HT_CADOUT_L11

HT_CADOUT_H10

HT_CADOUT_L10

HT_CADOUT_H9

HT_CADOUT_L9

HT_CADOUT_H8

HT_CADOUT_L8

HT_CADOUT_H7

HT_CADOUT_L7

HT_CADOUT_H6

HT_CADOUT_L6

HT_CADOUT_H5

HT_CADOUT_L5

HT_CADOUT_H4

HT_CADOUT_L4

HT_CADOUT_H3

HT_CADOUT_L3

HT_CADOUT_H2

HT_CADOUT_L2

HT_CADOUT_H1

HT_CADOUT_L1

HT_CADOUT_H0

HT_CADOUT_L0

4

3

2 1

C238

C238

VCC_DDR

R212

R212

39.2R1%

39.2R1%

R213

R213

39.2R1%

39.2R1%

C237C3900P50X C237C3900P50X

9 8

11 10

13 12

VDDA25VDDA_25

C3900P50X

C3900P50X

R166

R166

_169R1%-1

_169R1%-1

R203 300R1%R203 300R1%

R211 300R1%R211 300R1%

CPU_STRAP_HI_E11

CPU_STRAP_LO_F11

TP12TP12

R159 300RR159 300R

R160 300RR160 300R

TP13TP13

0B 12/12 Modify

CPU_PWRGD

07 VDD

147

U21DU21D

CPU_RST#

07 VDD

147

U21EU21E

HT_STOP#

07 VDD

147

U21FU21F

3

SM_THERMDB18

SM_THERMDA18

CPUCLKIN

CPUCLKIN#

C229

C229

X_C1000P50X

X_C1000P50X

TP28TP28

TP22TP22

TP18TP18

TP27TP27

TP3TP3

TP15TP15

CPU_M_VREF

07 VDD

1 2

07 VDD

3 4

07 VDD

5 6

C236

C236

C4.7U16Y1206

C4.7U16Y1206

TP1TP1

TP2TP2

TP8TP8

TP10TP10

TP9TP9

TP6TP6

TP21TP21

147

U21AU21A

147

U21BU21B

147

U21CU21C

C0.22U16X

C0.22U16X

C248

C248

CPU_PWRGD_C

HT_STOP_C#

CPU_RST_C#

CPU_PRESENT_L

COREFB+23

COREFB-23

CPU_VTT_SENSE

CPU_TEST25_H

CPU_TEST25_L

VDDA25

C242

C242

C3300P50X

C3300P50X

COREFB+

COREFB-

CPU_PWRGD_C

CPU_RST_C#

HT_STOP_C#

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AL10

AJ10

AH10

AL9

A5

G2

G1

E12

F12

AH11

AJ11

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AG9

AG8

AH7

AJ6

L14 80L3_40_0805L14 80L3_40_0805

CPU_CLK9

CPU_CLK#9

TP17TP17

VCC_DDR

C637

C637

C4.7U16Y1206

C4.7U16Y1206

CPU_PWRGD9

CPU_RST#9

ATX_PWR_OK10,13,24,27

R502 0R502 0

HT_STOP#9

C656

C656

x_C1000P50X

x_C1000P50X

CPU1D

CPU1D

MISC

MISC

VDDA1

VDDA2

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_L

RESET_L

CPU_PRESENT_L

THERMTRIP_L

SIC

PROCHOT_L

SID

TDI

TRST_L

TCK

TMS

DBREQ_L

VDDIO_FB_H

VDD_FB_H

VDDIO_FB_L

VDD_FB_L

VTT_SENSE

M_VREF

M_ZN

M_ZP

TEST29_H

TEST25_H

TEST29_L

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST28_H

TEST7

TEST28_L

TEST6

TEST5

TEST4

TEST3

TEST2

CPU_PRESENT_L

CPU_TEST25_H

CPU_TEST25_L

07 VDD

C636

C636

C4.7U16Y1206

C4.7U16Y1206

0B 06/04/25 Modify

2

VID(5)

VID(4)

VID(3)

VID(2)

VID(1)

VID(0)

DBRDY

PSI_L

HTREF1

HTREF0

TEST24

TEST23

TEST22

TEST21

TEST20

TEST27

TEST26

TEST10

TEST8

07 VDD

2

TDO

VCC_DDR

1

3

5

7

R501 300RR501 300R

VDDA25

D2

VID4

D1

VID3

C1

VID2

E3

VID1

E2

VID0

E1

CPU_THRIP_C#

AK7

AL7

AK10

B6

AK11

AL11

CPU_PSI_L

F1

V8

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

R202 1KRR202 1KR

R167 510RR167 510R

R170 510RR170 510R

R503 0R0805-LFR503 0R0805-LF

X_R455 x_0R0805-LFX_R455 x_0R0805-LF

RN9

RN9

CPU_RST_C#

2

CPU_PWRGD_C

4

6

HT_STOP_C#

8

8P4R-330R

8P4R-330R

CPU_THRIP_C#

RN81KRN8

CPU_PWRGD

1 2

CPU_RST#

3 4

HT_STOP#

5 6

7 8

1K

VCC_DDR

TP7TP7

CPU_VDDIOFB_H

CPU_VDDIOFB_L

R210 300RR210 300R

R158

R158

300R

300R

TP19TP19

VCC_DDR

TP5TP5

TP24TP24

C317

TP14TP14

TP26TP26

TP20TP20

TP25TP25

TP23TP23

VCC_DDR

VCC_DDR

GND 6,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30

3VDUAL VCC_DDR

C317

C1000P50X

C1000P50X

TP4TP4

TP11TP11

R205

R205

300R

300R

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

ATHLON64 HT I/F CTRL & DEBUG

ATHLON64 HT I/F CTRL & DEBUG

ATHLON64 HT I/F CTRL & DEBUG

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

1

VID[0..4] 23

VCC_DDR

R204

R204

300R

300R

C318

C318

VCC1_2HT

C1000P50X

C1000P50X

R208 44.2R1%R208 44.2R1%

R209 44.2R1%R209 44.2R1%

R161

R161

80.6R1%

80.6R1%

CPU_STRAP_LO_F11 CPU_STRAP_HI_E11

C634

C634

C635

C635

x_C1000P50X

x_C1000P50X

x_C1000P50X

x_C1000P50X

0B 12/12 Modify

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Sheet

Sheet

Sheet

of

435

of

435

of

435

1

Rev

Rev

Rev

0A

0A

0A

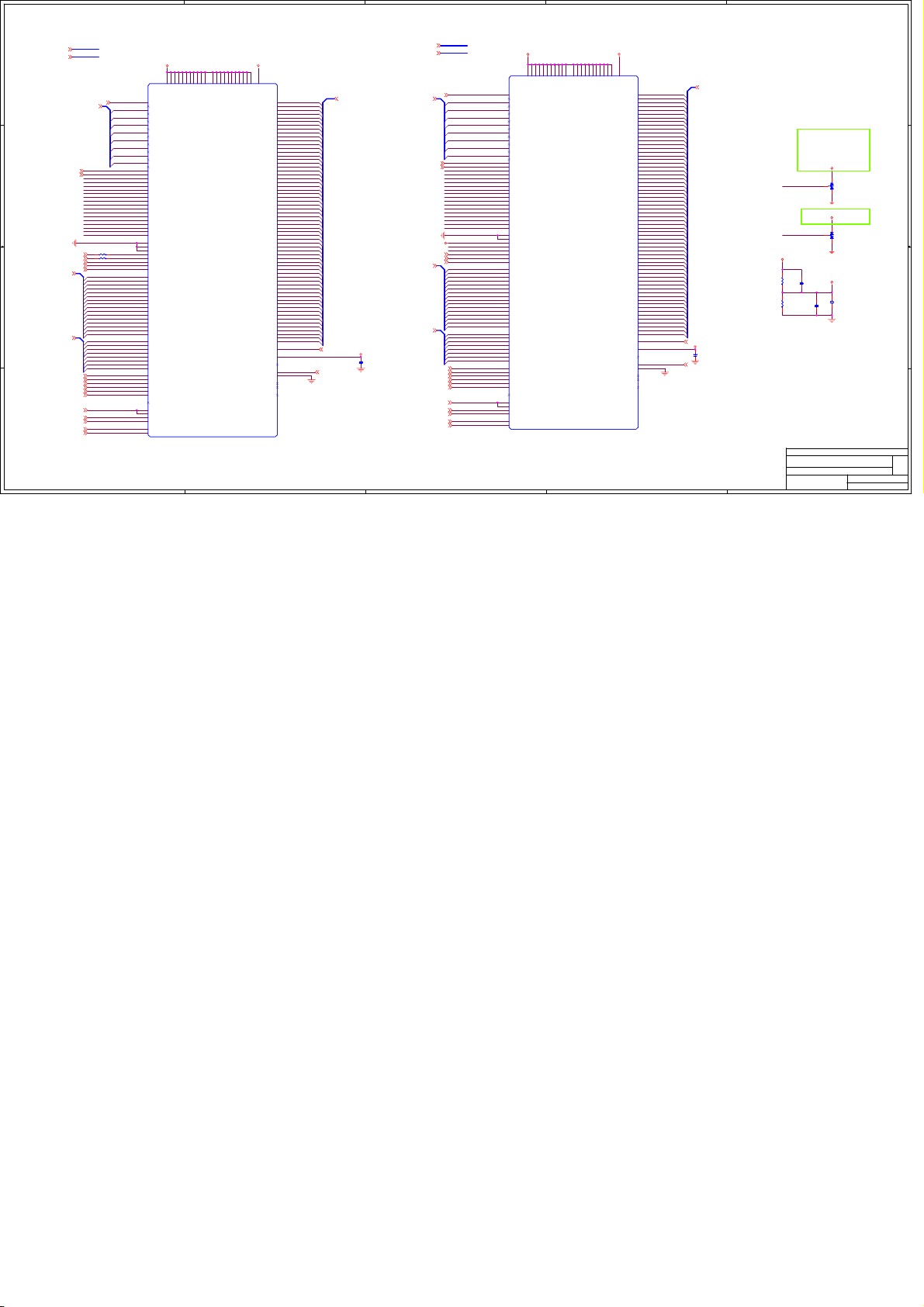

Page 5

5

4

3

2

1

MEM_MA_DQS_L[7..0]7

MEM_MA_DQS_H[7..0]7

MEM_MA_DM[7..0]7

D D

CPU1B

CPU1B

MEMORY INTERFACE A

AG21

AG20

AC25

AA24

AC28

AE20

AE19

AD27

AA25

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AJ25

AH29

G19

H19

U27

U26

G20

G21

V27

W27

N25

Y27

L27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

T25

U25

T27

W24

D29

C29

C25

D25

E19

F19

F15

G15

B29

E24

E18

H15

MA0_CLK_H(2)

MA0_CLK_L(2)

MA0_CLK_H(1)

MA0_CLK_L(1)

MA0_CLK_H(0)

MA0_CLK_L(0)

MA0_CS_L(1)

MA0_CS_L(0)

MA0_ODT(0)

MA1_CLK_H(2)

MA1_CLK_L(2)

MA1_CLK_H(1)

MA1_CLK_L(1)

MA1_CLK_H(0)

MA1_CLK_L(0)

MA1_CS_L(1)

MA1_CS_L(0)

MA1_ODT(0)

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK(2)

MA_BANK(1)

MA_BANK(0)

MA_CKE(1)

MA_CKE(0)

MA_ADD(15)

MA_ADD(14)

MA_ADD(13)

MA_ADD(12)

MA_ADD(11)

MA_ADD(10)

MA_ADD(9)

MA_ADD(8)

MA_ADD(7)

MA_ADD(6)

MA_ADD(5)

MA_ADD(4)

MA_ADD(3)

MA_ADD(2)

MA_ADD(1)

MA_ADD(0)

MA_DQS_H(7)

MA_DQS_L(7)

MA_DQS_H(6)

MA_DQS_L(6)

MA_DQS_H(5)

MA_DQS_L(5)

MA_DQS_H(4)

MA_DQS_L(4)

MA_DQS_H(3)

MA_DQS_L(3)

MA_DQS_H(2)

MA_DQS_L(2)

MA_DQS_H(1)

MA_DQS_L(1)

MA_DQS_H(0)

MA_DQS_L(0)

MA_DM(7)

MA_DM(6)

MA_DM(5)

MA_DM(4)

MA_DM(3)

MA_DM(2)

MA_DM(1)

MA_DM(0)

MEMORY INTERFACE A

MA_DATA(63)

MA_DATA(62)

MA_DATA(61)

MA_DATA(60)

MA_DATA(59)

MA_DATA(58)

MA_DATA(57)

MA_DATA(56)

MA_DATA(55)

MA_DATA(54)

MA_DATA(53)

MA_DATA(52)

MA_DATA(51)

MA_DATA(50)

MA_DATA(49)

MA_DATA(48)

MA_DATA(47)

MA_DATA(46)

MA_DATA(45)

MA_DATA(44)

MA_DATA(43)

MA_DATA(42)

MA_DATA(41)

MA_DATA(40)

MA_DATA(39)

MA_DATA(38)

MA_DATA(37)

MA_DATA(36)

MA_DATA(35)

MA_DATA(34)

MA_DATA(33)

MA_DATA(32)

MA_DATA(31)

MA_DATA(30)

MA_DATA(29)

MA_DATA(28)

MA_DATA(27)

MA_DATA(26)

MA_DATA(25)

MA_DATA(24)

MA_DATA(23)

MA_DATA(22)

MA_DATA(21)

MA_DATA(20)

MA_DATA(19)

MA_DATA(18)

MA_DATA(17)

MA_DATA(16)

MA_DATA(15)

MA_DATA(14)

MA_DATA(13)

MA_DATA(12)

MA_DATA(11)

MA_DATA(10)

MA_DQS_H(8)

MA_DQS_L(8)

MA_CHECK(7)

MA_CHECK(6)

MA_CHECK(5)

MA_CHECK(4)

MA_CHECK(3)

MA_CHECK(2)

MA_CHECK(1)

MA_CHECK(0)

MEM_MA0_CLK_H27,8

MEM_MA0_CLK_L27,8

MEM_MA0_CLK_H17,8

MEM_MA0_CLK_L17,8

MEM_MA0_CLK_H07,8

MEM_MA0_CLK_L07,8

MEM_MA0_CS_L17,8

MEM_MA0_CS_L07,8

MEM_MA0_ODT07,8

C C

MEM_MA_CAS_L7,8

MEM_MA_WE_L7,8

MEM_MA_RAS_L7,8

MEM_MA_BANK27,8

MEM_MA_BANK17,8

MEM_MA_BANK07,8

MEM_MA_CKE07,8

MEM_MA_ADD[15..0]7,8

B B

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CS_L1

MEM_MA0_CS_L0

MEM_MA0_ODT0

MEM_MA_CAS_L

MEM_MA_WE_L

MEM_MA_RAS_L

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_CKE0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

MA_DATA(9)

MA_DATA(8)

MA_DATA(7)

MA_DATA(6)

MA_DATA(5)

MA_DATA(4)

MA_DATA(3)

MA_DATA(2)

MA_DATA(1)

MA_DATA(0)

MA_DM(8)

AE14

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

MEM_MA_DATA18

C26

MEM_MA_DATA17

G23

MEM_MA_DATA16

F23

MEM_MA_DATA15

E22

MEM_MA_DATA14

E21

MEM_MA_DATA13

F17

MEM_MA_DATA12

G17

MEM_MA_DATA11

G22

MEM_MA_DATA10

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

MEM_MA_DQS_H8

J28

MEM_MA_DQS_L8

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

MEM_MA_DATA63

MEM_MA_DATA62

MEM_MA_DATA61

MEM_MA_DATA60

MEM_MA_DATA59

MEM_MA_DATA58

MEM_MA_DATA57

MEM_MA_DATA56

MEM_MA_DATA55

MEM_MA_DATA54

MEM_MA_DATA53

MEM_MA_DATA52

MEM_MA_DATA51

MEM_MA_DATA50

MEM_MA_DATA49

MEM_MA_DATA48

MEM_MA_DATA47

MEM_MA_DATA46

MEM_MA_DATA45

MEM_MA_DATA44

MEM_MA_DATA43

MEM_MA_DATA42

MEM_MA_DATA41

MEM_MA_DATA40

MEM_MA_DATA39

MEM_MA_DATA38

MEM_MA_DATA37

MEM_MA_DATA36

MEM_MA_DATA35

MEM_MA_DATA34

MEM_MA_DATA33

MEM_MA_DATA32

MEM_MA_DATA31

MEM_MA_DATA30

MEM_MA_DATA29

MEM_MA_DATA28

MEM_MA_DATA27

MEM_MA_DATA26

MEM_MA_DATA25

MEM_MA_DATA24

MEM_MA_DATA23

MEM_MA_DATA22

MEM_MA_DATA21

MEM_MA_DATA20

MEM_MA_DATA19

MEM_MA_DATA9

MEM_MA_DATA8

MEM_MA_DATA7

MEM_MA_DATA6

MEM_MA_DATA5

MEM_MA_DATA4

MEM_MA_DATA3

MEM_MA_DATA2

MEM_MA_DATA1

MEM_MA_DATA0

MEM_MA_DM8

MEM_MA_CHECK7

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA_DATA[63..0] 7

MEM_MA_DQS_H8 7

MEM_MA_DQS_L8 7

MEM_MA_DM8 7

MEM_MA_CHECK[7..0] 7

A A

5

4

MEM_MB_DQS_L[7..0]7

MEM_MB_DQS_H[7..0]7

MEM_MB_DM[7..0]7

CPU1C

CPU1C

MEMORY INTERFACE B

AK19

AE30

AC31

AD29

AE29

AB31

AD31

AC29

AC30

AB29

AA31

AA28

AE31

AA29

AA30

AK13

AK17

AK23

AH17

AK29

AJ19

A18

A19

U31

U30

AL19

AL18

C19

D19

W29

W28

N31

M31

M29

N28

N29

N30

P29

P31

R29

R28

R31

R30

T31

T29

U29

U28

AJ13

AJ17

AL23

AL28

AL29

D31

C31

C24

C23

D17

C17

C14

C13

AJ14

AJ23

C30

A23

B17

B13

MB0_CLK_H(2)

MB0_CLK_L(2)

MB0_CLK_H(1)

MB0_CLK_L(1)

MB0_CLK_H(0)

MB0_CLK_L(0)

MB0_CS_L(1)

MB0_CS_L(0)

MB0_ODT(0)

MB1_CLK_H(2)

MB1_CLK_L(2)

MB1_CLK_H(1)

MB1_CLK_L(1)

MB1_CLK_H(0)

MB1_CLK_L(0)

MB1_CS_L(1)

MB1_CS_L(0)

MB1_ODT(0)

MB_CAS_L

MB_WE_L

MB_RAS_L

MB_BANK(2)

MB_BANK(1)

MB_BANK(0)

MB_CKE(1)

MB_CKE(0)

MB_ADD(15)

MB_ADD(14)

MB_ADD(13)

MB_ADD(12)

MB_ADD(11)

MB_ADD(10)

MB_ADD(9)

MB_ADD(8)

MB_ADD(7)

MB_ADD(6)

MB_ADD(5)

MB_ADD(4)

MB_ADD(3)

MB_ADD(2)

MB_ADD(1)

MB_ADD(0)

MB_DQS_H(7)

MB_DQS_L(7)

MB_DQS_H(6)

MB_DQS_L(6)

MB_DQS_H(5)

MB_DQS_L(5)

MB_DQS_H(4)

MB_DQS_L(4)

MB_DQS_H(3)

MB_DQS_L(3)

MB_DQS_H(2)

MB_DQS_L(2)

MB_DQS_H(1)

MB_DQS_L(1)

MB_DQS_H(0)

MB_DQS_L(0)

MB_DM(7)

MB_DM(6)

MB_DM(5)

MB_DM(4)

MB_DM(3)

MB_DM(2)

MB_DM(1)

MB_DM(0)

MEMORY INTERFACE B

MB_DATA(63)

MB_DATA(62)

MB_DATA(61)

MB_DATA(60)

MB_DATA(59)

MB_DATA(58)

MB_DATA(57)

MB_DATA(56)

MB_DATA(55)

MB_DATA(54)

MB_DATA(53)

MB_DATA(52)

MB_DATA(51)

MB_DATA(50)

MB_DATA(49)

MB_DATA(48)

MB_DATA(47)

MB_DATA(46)

MB_DATA(45)

MB_DATA(44)

MB_DATA(43)

MB_DATA(42)

MB_DATA(41)

MB_DATA(40)

MB_DATA(39)

MB_DATA(38)

MB_DATA(37)

MB_DATA(36)

MB_DATA(35)

MB_DATA(34)

MB_DATA(33)

MB_DATA(32)

MB_DATA(31)

MB_DATA(30)

MB_DATA(29)

MB_DATA(28)

MB_DATA(27)

MB_DATA(26)

MB_DATA(25)

MB_DATA(24)

MB_DATA(23)

MB_DATA(22)

MB_DATA(21)

MB_DATA(20)

MB_DATA(19)

MB_DATA(18)

MB_DATA(17)

MB_DATA(16)

MB_DATA(15)

MB_DATA(14)

MB_DATA(13)

MB_DATA(12)

MB_DATA(11)

MB_DATA(10)

MB_DATA(9)

MB_DATA(8)

MB_DATA(7)

MB_DATA(6)

MB_DATA(5)

MB_DATA(4)

MB_DATA(3)

MB_DATA(2)

MB_DATA(1)

MB_DATA(0)

MB_DQS_H(8)

MB_DQS_L(8)

MB_DM(8)

MB_CHECK(7)

MB_CHECK(6)

MB_CHECK(5)

MB_CHECK(4)

MB_CHECK(3)

MB_CHECK(2)

MB_CHECK(1)

MB_CHECK(0)

MEM_MB0_CLK_H27,8

MEM_MB0_CLK_L27,8

MEM_MB0_CLK_H17,8

MEM_MB0_CLK_L17,8

MEM_MB0_CLK_H07,8

MEM_MB0_CLK_L07,8

MEM_MB0_CS_L17,8

MEM_MB0_CS_L07,8

MEM_MB0_ODT07,8

MEM_MB_CAS_L7,8

MEM_MB_WE_L7,8

MEM_MB_RAS_L7,8

MEM_MB_BANK27,8

MEM_MB_BANK17,8

MEM_MB_BANK07,8

MEM_MB_CKE07,8

MEM_MB_ADD[15..0]7,8

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CS_L1

MEM_MB0_CS_L0

MEM_MB0_ODT0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

AH13

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

MEM_MB_DATA63

MEM_MB_DATA62

MEM_MB_DATA61

MEM_MB_DATA60

MEM_MB_DATA59

MEM_MB_DATA58

MEM_MB_DATA57

MEM_MB_DATA56

MEM_MB_DATA55

MEM_MB_DATA54

MEM_MB_DATA53

MEM_MB_DATA52

MEM_MB_DATA51

MEM_MB_DATA50

MEM_MB_DATA49

MEM_MB_DATA48

MEM_MB_DATA47

MEM_MB_DATA46

MEM_MB_DATA45

MEM_MB_DATA44

MEM_MB_DATA43

MEM_MB_DATA42

MEM_MB_DATA41

MEM_MB_DATA40

MEM_MB_DATA39

MEM_MB_DATA38

MEM_MB_DATA37

MEM_MB_DATA36

MEM_MB_DATA35

MEM_MB_DATA34

MEM_MB_DATA33

MEM_MB_DATA32

MEM_MB_DATA31

MEM_MB_DATA30

MEM_MB_DATA29

MEM_MB_DATA28

MEM_MB_DATA27

MEM_MB_DATA26

MEM_MB_DATA25

MEM_MB_DATA24

MEM_MB_DATA23

MEM_MB_DATA22

MEM_MB_DATA21

MEM_MB_DATA20

MEM_MB_DATA19

MEM_MB_DATA18

MEM_MB_DATA17

MEM_MB_DATA16

MEM_MB_DATA15

MEM_MB_DATA14

MEM_MB_DATA13

MEM_MB_DATA12

MEM_MB_DATA11

MEM_MB_DATA10

MEM_MB_DATA9

MEM_MB_DATA8

MEM_MB_DATA7

MEM_MB_DATA6

MEM_MB_DATA5

MEM_MB_DATA4

MEM_MB_DATA3

MEM_MB_DATA2

MEM_MB_DATA1

MEM_MB_DATA0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DM8

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB_DQS_H8 7

MEM_MB_DQS_L8 7

MEM_MB_DM8 7

MEM_MB_DATA[63..0] 7

MEM_MB_CHECK[7..0] 7

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

ATHLON64 DDR MEMORY I/F

ATHLON64 DDR MEMORY I/F

ATHLON64 DDR MEMORY I/F

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

3

2

http://www.msi.com.tw

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Rev

Rev

Rev

0A

0A

0A

of

535

of

535

of

535

Page 6

5

4

3

2

1

VCCP

D D

C C

B B

VTT_DDR

AA8

AA10

AA12

AA14

AA16

AA18

AB7

AB9

AB11

AC4

AC5

AC8

AC10

AD2

AD3

AD7

AD9

AE10

AF7

AF9

AG4

AG5

AG7

AH2

AH3

E10

F11

G10

G12

H11

H23

J12

J14

J16

J18

J20

J22

J24

K11

K13

K15

K17

K19

K21

K23

L10

L12

Y17

Y19

C209

C209

C0.22U16X

C0.22U16X

CPU1F

CPU1F

VDD1

VDD1

C243

C243

C0.22U16X

C0.22U16X

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS240

VSS241

C213

C213

C4.7U10Y0805

C4.7U10Y0805

A3

A7

A9

A11

AA4

AA5

AA7

AA9

AA11

AA13

AA15

AA17

AA19

AA21

AA23

AB2

AB3

AB8

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AC21

AC23

AD8

AD10

AD12

AD14

AD16

AD20

AD22

AD24

AE4

AE5

AE9

AE11

AF2

AF3

AF8

AF10

AF12

AF14

AF16

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

Y14

Y16

C219

C219

C4.7U10Y0805

C4.7U10Y0805

A4

VDD1

A6

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

B3

VDD28

B5

VDD29

B7

VDD30

C2

VDD31

C4

VDD32

C6

VDD33

C8

VDD34

D3

VDD35

D5

VDD36

D7

VDD37

D9

VDD38

E4

VDD39

E6

VDD40

E8

VDD41

VDD42

F5

VDD43

F7

VDD44

F9

VDD45

VDD46

G6

VDD47

G8

VDD48

VDD49

VDD50

H7

VDD51

VDD52

VDD53

J8

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

K7

VDD62

K9

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

L4

VDD71

L5

VDD72

L8

VDD73

VDD74

VDD75

VDD150

VDD151

C232

C232

C10P16N

C10P16N

C208

C208

C10P16N

C10P16N

VCCP

CPU1G

CPU1G

VDD2

VDD2

L14

VDD1

L16

VDD2

L18

VDD3

M2

VDD4

M3

VDD5

M7

VDD6

M9

VDD7

M11

VDD8

M13

VDD9

M15

VDD10

M17

VDD11

M19

VDD12

N8

VDD13

N10

VDD14

N12

VDD15

N14

VDD16

N16

VDD17

N18

VDD18

P7

VDD19

P9

VDD20

P11

VDD21

P13

VDD22

P15

VDD23

P17

VDD24

P19

VDD25

R4

VDD26

R5

VDD27

R8

VDD28

R10

VDD29

R12

VDD30

R14

VDD31

R16

VDD32

R18

VDD33

R20

VDD34

T2

VDD35

T3

VDD36

T7

VDD37

T9

VDD38

T11

VDD39

T13

VDD40

T15

VDD41

T17

VDD42

T19

VDD43

T21

VDD44

U8

VDD45

U10

VDD46

U12

VDD47

U14

VDD48

U16

VDD49

U18

VDD50

U20

VDD51

V9

VDD52

V11

VDD53

V13

VDD54

V15

VDD55

V17

VDD56

V19

VDD57

V21

VDD58

W4

VDD59

W5

VDD60

W8

VDD61

W10

VDD62

W12

VDD63

W14

VDD64

W16

VDD65

W18

VDD66

W20

VDD67

Y2

VDD68

Y3

VDD69

Y7

VDD70

Y9

VDD71

Y11

VDD72

Y13

VDD73

Y15

VDD74

Y21

VDD75

C249

C249

C1000P50X

C1000P50X C0.22U16X

AK20

VSS1

AK22

VSS2

AK24

VSS3

AK26

VSS4

AK28

VSS5

AK30

VSS6

AL5

VSS7

B4

VSS8

B9

VSS9

B11

VSS10

B14

VSS11

B16

VSS12

B18

VSS13

B20

VSS14

B22

VSS15

B24

VSS16

B26

VSS17

B28

VSS18

B30

VSS19

C3

VSS20

D14

VSS21

D16

VSS22

D18

VSS23

D20

VSS24

D22

VSS25

D24

VSS26

D26

VSS27

D28

VSS28

D30

VSS29

E11

VSS30

F4

VSS31

F14

VSS32

F16

VSS33

F18

VSS34

F20

VSS35

F22

VSS36

F24

VSS37

F26

VSS38

F28

VSS39

F30

VSS40

G9

VSS41

G11

VSS42

H8

VSS43

H10

VSS44

H12

VSS45

H14

VSS46

H16

VSS47

H18

VSS48

H22

VSS49

H24

VSS50

H26

VSS51

H28

VSS52

H30

VSS53

J4

VSS54

J5

VSS55

J7

VSS56

J9

VSS57

J11

VSS58

J13

VSS59

J15

VSS60

J17

VSS61

J19

VSS62

J21

VSS63

J23

VSS64

K2

VSS65

K3

VSS66

K8

VSS67

K10

VSS68

K12

VSS69

K14

VSS70

K16

VSS71

K18

VSS72

K20

VSS73

K22

VSS74

Y18

VSS75

VCC_DDR VCC_DDR

C233

C233

C558

C558

C1000P50X

C1000P50X

C0.22U16X/B

C0.22U16X/B

C571

C571

C0.22U16X/B

C0.22U16X/B

VCCP

AA20

AA22

AB13

AB15

AB17

AB19

AB21

AB23

AC12

AC14

AC16

AC18

AC20

AC22

AD11

AD23

AE12

AF11

L20

L22

M21

M23

N20

N22

P21

P23

R22

T23

U22

V23

W22

Y23

C336

C336

C0.22U16X

C0.22U16X

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

C366

C366

C4.7U10Y0805

C4.7U10Y0805

CPU1H

CPU1H

VDD3

VDD3

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

C223

C223

C4.7U10Y0805

C4.7U10Y0805

VCC1_2HTC

VLDT_RUN_A

VTT_DDR

C322

N17

N19

N21

N23

P2

P3

P8

P10

P12

P14

P16

P18

P20

P22

R7

R9

R11

R13

R15

R17

R19

R21

R23

T8

T10

T12

T14

T16

T18

T20

T22

U4

U5

U7

U9

U11

U13

U15

U17

U19

U21

U23

V2

V3

V10

V12

V14

V16

V18

V20

V22

W9

W11

W13

W15

W17

W19

W21

W23

Y8

Y10

Y12

W7

Y20

Y22

C322

C4.7U16Y1206

C4.7U16Y1206

GND 4,7,8,9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24,25,26,27,28,29,30

VCC_DDR

VCCP

C580

C580

C0.22U16X/B

C0.22U16X/B

VCCP

C569

C569

C22U6.3X1206/B

C22U6.3X1206/B

C576

C576

C22U6.3X1206/B

C22U6.3X1206/B

C590

C590

C0.22U16X/B

C0.22U16X/B

C567

C567

C22U6.3X1206/B

C22U6.3X1206/B

C582

C582

C22U6.3X1206/B

C22U6.3X1206/B

CPU1I

CPU1I

VDDIO

VDDIO

AJ4

VLDT_A1

AJ3

VLDT_A2

AJ2

VLDT_A3

AJ1

VLDT_A4

D12

VTT1

C12

VTT2

B12

VTT3

A12

VTT4

AB24

VDDIO1

AB26

VDDIO2

AB28

VDDIO3

AB30

VDDIO4

AC24

VDDIO5

AD26

VDDIO6

AD28

VDDIO7

AD30

VDDIO8

AF30

VDDIO9

M24

VDDIO10

M26

VDDIO11

M28

VDDIO12

M30

VDDIO13

P24

VDDIO14

P26

VDDIO15

P28

VDDIO16

P30

VDDIO17

T24

VDDIO18

T26

VDDIO19

T28

VDDIO20

T30

VDDIO21

V25

VDDIO22

V26

VDDIO23

V28

VDDIO24

V30

VDDIO25

Y24

VDDIO26

Y26

VDDIO27

Y28

VDDIO28

Y29

VDDIO29

C585

C585

C0.22U16X/B

C0.22U16X/B

C22U6.3X1206/B

C22U6.3X1206/B

C4.7U10Y0805

C4.7U10Y0805

H6

VLDT_B1

H5

VLDT_B2

H2

VLDT_B3

VTT_DDR

H1

VLDT_B4

AK12

VTT5

AJ12

VTT6

AH12

VTT7

AG12

VTT8

AL12

VTT9

K24

VSS1

K26

VSS2

K28

VSS3

K30

VSS4

L7

VSS5

L9

VSS6

L11

VSS7

L13

VSS8

L15

VSS9

L17

VSS10

L19

VSS11

L21

VSS12

L23

VSS13

M8

VSS14

M10

VSS15

M12

VSS16

M14

VSS17

M16

VSS18

M18

VSS19

M20

VSS20

M22

VSS21

N4

VSS22

N5

VSS23

N7

VSS24

N9

VSS25

N11

VSS26

N13

VSS27

N15

VSS28

C552

C552

C553

C553

C0.01U50X/B

C0.01U50X/B

_C10P25N0402/0.25/B

_C10P25N0402/0.25/B

C565

C565

C561

C561

C575

C575

C258

C258

C22U6.3X1206/B

C22U6.3X1206/B

C22U6.3X1206/B

C22U6.3X1206/B

C240

C240

C566

C566

C0.22U16X/B

C0.22U16X/B

C4.7U10Y0805

C4.7U10Y0805 C0.01U50X/B

VCC1_2HT

C22U6.3X1206/B

C22U6.3X1206/B

C570

C22U6.3X1206/B

C22U6.3X1206/B

C306

C306

C0.22U16X

C0.22U16X

C562

C562

C197

C197

C22U6.3X1206

C22U6.3X1206

C591

C591

C0.22U16X

C574

C574

C22U6.3X1206/B

C22U6.3X1206/B

C584

C584

C22U6.3X1206/B

C22U6.3X1206/B

C588

C588

C0.01U50X/B

C189

C189

C22U6.3X1206

C22U6.3X1206

C554

C554

C22U6.3X1206/B

C22U6.3X1206/B

C373

C373

_C10P25N0402/0.25

_C10P25N0402/0.25

C579

C579

C22U6.3X1206/B

C22U6.3X1206/BC570

C555

C555

C22U6.3X1206/B

C22U6.3X1206/B

C22U6.3X1206

C22U6.3X1206

C203

C203

A A

VTT_DDR

C369

C369

C0.22U16X

C0.22U16X

C362

C362

C0.22U16X

C0.22U16X

5

C350

C350

C4.7U10Y0805

C4.7U10Y0805

C354

C354

C4.7U10Y0805

C4.7U10Y0805

C295

C295

C10P16N

C10P16N

C321

C321

C10P16N

C10P16N

C316

C316

C1000P50X

C1000P50X

4

3

2

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

ATHLON64 PWR & GND

ATHLON64 PWR & GND

ATHLON64 PWR & GND

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Sheet

Sheet

Sheet

1

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

of

635

of

635

of

635

Rev

Rev

Rev

0A

0A

0A

Page 7

5

4

3

2

1

VDDR_VREF

C211

C211

C0.1U25Y

C0.1U25Y

MEM_MB_DQS_H[7..0]5

MEM_MB_DQS_L[7..0]5

MEM_MB_DM8

MEM_MB_DM85

MEM_MB_DM[7..0]5

MEM_MB_DQS_H85

MEM_MB_DQS_L85

MEM_MB_ADD[15..0]5,8

MEM_MB_CHECK[7..0]5

MEM_MB0_CLK_H05,8

MEM_MB0_CLK_L05,8

MEM_MB0_CLK_H15,8

MEM_MB0_CLK_L15,8

MEM_MB0_CLK_H25,8

MEM_MB0_CLK_L25,8

MEM_MB_DM7

MEM_MB_DM6

MEM_MB_DM5

MEM_MB_DM4

MEM_MB_DM3

MEM_MB_DM2

MEM_MB_DM1

MEM_MB_DM0

MEM_MB_DQS_H8

MEM_MB_DQS_L8

MEM_MB_DQS_H7

MEM_MB_DQS_L7

MEM_MB_DQS_H6

MEM_MB_DQS_L6

MEM_MB_DQS_H5

MEM_MB_DQS_L5

MEM_MB_DQS_H4

MEM_MB_DQS_L4

MEM_MB_DQS_H3

MEM_MB_DQS_L3

MEM_MB_DQS_H2

MEM_MB_DQS_L2

MEM_MB_DQS_H1

MEM_MB_DQS_L1

MEM_MB_DQS_H0

MEM_MB_DQS_L0

VCC3

SMB_MEMCLK

SMB_MEMDATA

MEM_MB_BANK2

MEM_MB_BANK25,8

MEM_MB_BANK1

MEM_MB_BANK15,8

MEM_MB_BANK0

MEM_MB_BANK05,8

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CHECK7

MEM_MB_CHECK6

MEM_MB_CHECK5

MEM_MB_CHECK4

MEM_MB_CHECK3

MEM_MB_CHECK2

MEM_MB_CHECK1

MEM_MB_CHECK0

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB_CKE0

MEM_MB_CKE05,8

MEM_MB_RAS_L

MEM_MB_RAS_L5,8

MEM_MB_CAS_L

MEM_MB_CAS_L5,8

MEM_MB0_CS_L0

MEM_MB0_CS_L05,8

MEM_MB0_CS_L1

MEM_MB0_CS_L15,8

3

VCC_DDR

69

172

178

184

187

189

197

64

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD1067VDD11

DIMM 1

ADDR=1010001B

VCC3

78

170

175

181

191

194

72

238

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

VDDQ1075VDDQ11

VDDSPD

ERR_OUT_L

PAR_IN

DIMM1DIMM1

MEM_MB_DATA63

236

DQ63

MEM_MB_DATA62

235

DQ62

MEM_MB_DATA61

230

DQ61

MEM_MB_DATA60

229

DQ60

MEM_MB_DATA59

117

DQ59

MEM_MB_DATA58

116

DQ58

MEM_MB_DATA57

111

DQ57

MEM_MB_DATA56

110

DQ56

MEM_MB_DATA55

227

DQ55

MEM_MB_DATA54

226

DQ54

MEM_MB_DATA53

218

DQ53

MEM_MB_DATA52

217

DQ52

MEM_MB_DATA51

108

DQ51

MEM_MB_DATA50

107

DQ50

MEM_MB_DATA49

99

DQ49

MEM_MB_DATA48

98

DQ48

MEM_MB_DATA47

215

DQ47

MEM_MB_DATA46

214

DQ46

MEM_MB_DATA45

209

DQ45

MEM_MB_DATA44

208

DQ44

MEM_MB_DATA43

96

DQ43

MEM_MB_DATA42

95

DQ42

MEM_MB_DATA41

90

DQ41

MEM_MB_DATA40

89

DQ40

MEM_MB_DATA39

206

DQ39

MEM_MB_DATA38

205

DQ38

MEM_MB_DATA37

200

DQ37

MEM_MB_DATA36

199

DQ36

MEM_MB_DATA35

87

DQ35

MEM_MB_DATA34

86

DQ34

MEM_MB_DATA33

81

DQ33

MEM_MB_DATA32

80

DQ32

MEM_MB_DATA31

159

DQ31

MEM_MB_DATA30

158

DQ30

MEM_MB_DATA29

153

DQ29

MEM_MB_DATA28

152

DQ28

MEM_MB_DATA27

40

DQ27

MEM_MB_DATA26

39

DQ26

MEM_MB_DATA25

34

DQ25

MEM_MB_DATA24

33

DQ24

MEM_MB_DATA23

150

DQ23

MEM_MB_DATA22

149

DQ22

MEM_MB_DATA21

144

DQ21

MEM_MB_DATA20

143

DQ20

MEM_MB_DATA19

31

DQ19

MEM_MB_DATA18

30

DQ18

MEM_MB_DATA17

25

DQ17

MEM_MB_DATA16

24

DQ16

MEM_MB_DATA15

141

DQ15

MEM_MB_DATA14

140

DQ14

MEM_MB_DATA13

132

DQ13

MEM_MB_DATA12

131

DQ12

MEM_MB_DATA11

22

DQ11

MEM_MB_DATA10

21

DQ10

MEM_MB_DATA9

13

DQ9

MEM_MB_DATA8

12

DQ8

MEM_MB_DATA7

129

DQ7

MEM_MB_DATA6

128

DQ6

MEM_MB_DATA5

123

DQ5

MEM_MB_DATA4

122

DQ4

MEM_MB_DATA3

10

DQ3

MEM_MB_DATA2

9

DQ2

MEM_MB_DATA1

4

DQ1

MEM_MB_DATA0

3

DQ0

MEM_MB_WE_L

73

WE_L

VDDR_VREF

1

VREF

102

TEST

MEM_MB0_ODT0

195

ODT0

77

ODT1

55

68

19

NC1

2

VDDQ1

VDDQ2

VDDQ3

MEM_MB_DATA[63..0] 5

MEM_MB_WE_L 5,8

VDDR_VREF

C207

C207

C0.1U25Y

C0.1U25Y

MEM_MB0_ODT0 5,8

SMB_MEM_CLK

SMB_MEM_DATA

VCC_DDR

R152

R152

56.2R1%

56.2R1%

R153

R153

56.2R1%

56.2R1%

Title

Title

Title

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

0B 12/12 Modify

VCC3

2

3

D21

D21

BAV99W_SOT323

BAV99W_SOT323

1

VCC3

2

3

D20

D20

BAV99W_SOT323

BAV99W_SOT323

1

VDDR_VREF

C220

C220

C0.1U16X

C0.1U16X

VDDR_VREF

C214

C214

C205

C205

C1000P50X

C1000P50X

C0.1U16X

C0.1U16X

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

FIRST LOGICAL DDR DIMM

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Sheet

Sheet

Sheet

1

Rev

Rev

Rev

0A

0A

0A

735

735

735

of

of

of

MEM_MA_DQS_H[7..0]5

MEM_MA_DQS_L[7..0]5

D D

MEM_MA_DM85

MEM_MA_DM[7..0]5

MEM_MA_DQS_H85

C C

B B

MEM_MA_DQS_L85

SMB_MEM_DATA13

MEM_MA_BANK25,8

MEM_MA_BANK15,8

MEM_MA_BANK05,8

MEM_MA_ADD[15..0]5,8

MEM_MA_CHECK[7..0]5

MEM_MA0_CLK_H05,8

MEM_MA0_CLK_L05,8

MEM_MA0_CLK_H15,8

MEM_MA0_CLK_L15,8

MEM_MA0_CLK_H25,8

MEM_MA0_CLK_L25,8

MEM_MA_CKE05,8

MEM_MA_RAS_L5,8

MEM_MA_CAS_L5,8

A A

MEM_MA0_CS_L05,8

MEM_MA0_CS_L15,8

MEM_MA_DQS_H8

MEM_MA_DQS_L8

MEM_MA_DQS_H7

MEM_MA_DQS_L7

MEM_MA_DQS_H6

MEM_MA_DQS_L6

MEM_MA_DQS_H5

MEM_MA_DQS_L5

MEM_MA_DQS_H4

MEM_MA_DQS_L4

MEM_MA_DQS_H3

MEM_MA_DQS_L3

MEM_MA_DQS_H2

MEM_MA_DQS_L2

MEM_MA_DQS_H1

MEM_MA_DQS_L1

MEM_MA_DQS_H0

MEM_MA_DQS_L0

R276 33RR276 33R

SMB_MEM_CLK13

R270 33RR270 33R

MEM_MA_BANK2

MEM_MA_BANK1

MEM_MA_BANK0

MEM_MA_ADD15

MEM_MA_ADD14

MEM_MA_ADD13

MEM_MA_ADD12

MEM_MA_ADD11

MEM_MA_ADD10

MEM_MA_ADD9

MEM_MA_ADD8

MEM_MA_ADD7

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD2

MEM_MA_ADD1

MEM_MA_ADD0

MEM_MA_CHECK6

MEM_MA_CHECK5

MEM_MA_CHECK4

MEM_MA_CHECK3

MEM_MA_CHECK2

MEM_MA_CHECK1

MEM_MA_CHECK0

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA_CKE0

MEM_MA_RAS_L

MEM_MA_CAS_L

MEM_MA0_CS_L0

MEM_MA0_CS_L1

5

MEM_MA_DM8

MEM_MA_DM7

MEM_MA_DM6

MEM_MA_DM5

MEM_MA_DM4

MEM_MA_DM3

MEM_MA_DM2

MEM_MA_DM1

MEM_MA_DM0

SMB_MEMCLK

SMB_MEMDATA

VCC_DDR

172

178

184

187

189

197

64

69

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD753VDD859VDD9

164

DQS17_H

165

DQS17_L

232

DQS16_H

233

DQS16_L

223

DQS15_H

224

DQS15_L

211

DQS14_H

212

DQS14_L

202

DQS13_H

203

DQS13_L

155

DQS12_H

156

DQS12_L

146

DQS11_H

147

DQS11_L

134

DQS10_H

135

DQS10_L

125

DQS9_H

126

DQS9_L

46

DQS8_H

45

DQS8_L

114

DQS7_H

113

DQS7_L

105

DQS6_H

104

DQS6_L

93

DQS5_H

92

DQS5_L

84

DQS4_H

83

DQS4_L

37

DQS3_H

36

DQS3_L

28

DQS2_H

27

DQS2_L

16

DQS1_H

15

DQS1_L

7

DQS0_H

6

DQS0_L

101

SA2

240

SA1

239

SA0

120

SCL

119

SDA

54

BA2

190

BA1

71

BA0

173

A15

174

A14

196

A13

176

A12

57

A11

70

A10

177

A9

179

A8

58

A7

180

A6

60

A5

61

A4

182

A3

63

A2

183

A1

188

A0

168

CB7

167

CB6

162

CB5

161

CB4

49

CB3

48

CB2

43

CB1

42

CB0

185

CK0_H

186

CK0_L

137

CK1_H

138

CK1_L

220

CK2_H

221

CK2_L

18

RESET_L

52

CKE0

171

CKE1

192

RAS_L

74

CAS_L

193

S0_L

76

S1_L

VDD1067VDD11

DIMM 3

ADDR=1010000B

VCC3

238

78

170

175

181

191

194

72

VDDQ1

VDDQ2

DIMM2DIMM2

VDDQ3

VDDQ4

VDDQ5

VDDQ651VDDQ756VDDQ862VDDQ9

VDDQ1075VDDQ11

VDDSPD

ERR_OUT_L

PAR_IN

MEM_MA_DATA63

236

DQ63

MEM_MA_DATA62

235

DQ62

MEM_MA_DATA61

230

DQ61

MEM_MA_DATA60

229

DQ60

MEM_MA_DATA59

117

DQ59

MEM_MA_DATA58

116

DQ58

MEM_MA_DATA57

111

DQ57

MEM_MA_DATA56

110

DQ56

MEM_MA_DATA55

227

DQ55

MEM_MA_DATA54

226

DQ54

MEM_MA_DATA53

218

DQ53

MEM_MA_DATA52

217

DQ52

MEM_MA_DATA51

108

DQ51

MEM_MA_DATA50

107

DQ50

MEM_MA_DATA49

99

DQ49

MEM_MA_DATA48

98

DQ48

MEM_MA_DATA47

215

DQ47

MEM_MA_DATA46

214

DQ46

MEM_MA_DATA45

209

DQ45

MEM_MA_DATA44

208

DQ44

MEM_MA_DATA43

96

DQ43

MEM_MA_DATA42

95

DQ42

MEM_MA_DATA41

90

DQ41

MEM_MA_DATA40

89

DQ40

MEM_MA_DATA39

206

DQ39

MEM_MA_DATA38

205

DQ38

MEM_MA_DATA37

200

DQ37

MEM_MA_DATA36

199

DQ36

MEM_MA_DATA35

87

DQ35

MEM_MA_DATA34

86

DQ34

MEM_MA_DATA33

81

DQ33

MEM_MA_DATA32

80

DQ32

MEM_MA_DATA31

159

DQ31

MEM_MA_DATA30

158

DQ30

MEM_MA_DATA29

153

DQ29

MEM_MA_DATA28

152

DQ28

MEM_MA_DATA27

40

DQ27

MEM_MA_DATA26

39

DQ26

MEM_MA_DATA25

34

DQ25

MEM_MA_DATA24

33

DQ24

MEM_MA_DATA23

150

DQ23

MEM_MA_DATA22

149

DQ22

MEM_MA_DATA21

144

DQ21

MEM_MA_DATA20

143

DQ20

MEM_MA_DATA19

31

DQ19

MEM_MA_DATA18

30

DQ18

MEM_MA_DATA17

25

DQ17

MEM_MA_DATA16

24

DQ16

MEM_MA_DATA15

141

DQ15

MEM_MA_DATA14

140

DQ14

MEM_MA_DATA13

132

DQ13

MEM_MA_DATA12

131

DQ12

MEM_MA_DATA11

22

DQ11

MEM_MA_DATA10

21

DQ10

MEM_MA_DATA9

13

DQ9

MEM_MA_DATA8

12

DQ8

MEM_MA_DATA7

129

DQ7

MEM_MA_DATA6

128

DQ6

MEM_MA_DATA5

123

DQ5

MEM_MA_DATA4

122

DQ4

MEM_MA_DATA3

10

DQ3

MEM_MA_DATA2

9

DQ2

MEM_MA_DATA1

4

DQ1

MEM_MA_DATA0MEM_MA_CHECK7

3

DQ0

MEM_MA_WE_L

73

WE_L

VDDR_VREF

1

VREF

102

TEST

MEM_MA0_ODT0

195

ODT0

77

ODT1

55

68

19

NC1

4

MEM_MA_DATA[63..0] 5

MEM_MA_WE_L 5,8

MEM_MA0_ODT0 5,8

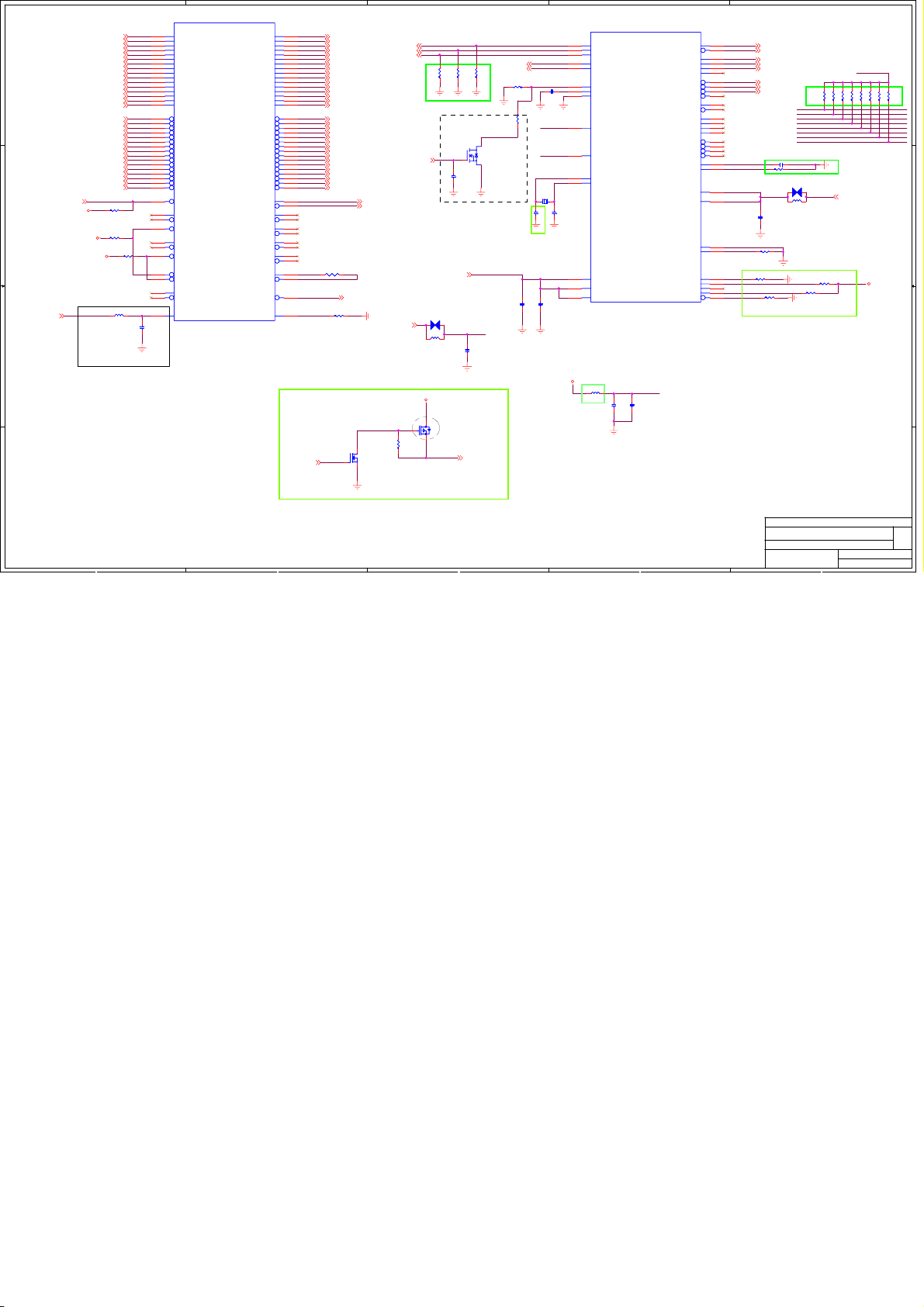

Page 8

5

4

3

2

1

MEM_MA_ADD[15..0]5,7

C319

C319

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

VCC_DDRVCC_DDR

C254

C254

C267

C267

C275

C275

C265

C0.1U16X

C0.1U16X

C265

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

MEM_MA_ADD15

C556 C22P50N0402/BC556 C22P50N0402/B

MEM_MA_ADD14

VTT_DDR

MEM_MA_ADD15

RN13 8P4R-47R0402RN13 8P4R-47R0402

1

MEM_MA_ADD14

MEM_MB_ADD12

MEM_MB_ADD9

D D

MEM_MA_BANK05,7

MEM_MB0_CS_L05,7

MEM_MA_RAS_L5,7

MEM_MB_WE_L5,7

MEM_MB_RAS_L5,7

MEM_MA_BANK15,7

MEM_MB0_CS_L15,7

C C

MEM_MA_ADD12

MEM_MB_ADD11

MEM_MA_ADD11

MEM_MA_ADD9

MEM_MB_ADD6

MEM_MA_ADD6

MEM_MA_ADD5

MEM_MB_ADD5

MEM_MB_ADD3

MEM_MA_ADD2

MEM_MB_ADD1

MEM_MB_ADD2

MEM_MA_BANK0

MEM_MB0_CS_L0

MEM_MA_RAS_L

MEM_MB_WE_L

MEM_MA_ADD0

MEM_MB_RAS_L

MEM_MA_ADD10

MEM_MA_BANK1

MEM_MB_ADD13

MEM_MB0_CS_L1

2

3

4

5

6

7

8

RN14 8P4R-47R0402RN14 8P4R-47R0402

1

2

3

4

5

6

7

8

RN16 8P4R-47R0402RN16 8P4R-47R0402

1

2

3

4

5

6

7

8

RN18 8P4R-47R0402RN18 8P4R-47R0402

1

2

3

4

5

6

7

8

RN21 8P4R-47R0402RN21 8P4R-47R0402

1

2

3

4

5

6

7

8

RN20 8P4R-47R0402RN20 8P4R-47R0402

1

2

3

4

5

6

7

8

RN24 8P4R-47R0402RN24 8P4R-47R0402

1

2

3

4

5

6

7

8

MEM_MA0_CLK_H25,7

MEM_MA0_CLK_L25,7

MEM_MA0_CLK_H15,7

MEM_MA0_CLK_L15,7

MEM_MA0_CLK_H05,7

MEM_MA0_CLK_L05,7

MEM_MB0_CLK_H25,7

MEM_MB0_CLK_L25,7

MEM_MB0_CLK_H15,7

MEM_MB0_CLK_L15,7

MEM_MB0_CLK_H05,7

MEM_MB0_CLK_L05,7

MEM_MA0_CLK_H2

MEM_MA0_CLK_L2

MEM_MA0_CLK_H1

MEM_MA0_CLK_L1

MEM_MA0_CLK_H0

MEM_MA0_CLK_L0

MEM_MB0_CLK_H2

MEM_MB0_CLK_L2

MEM_MB0_CLK_H1

MEM_MB0_CLK_L1

MEM_MB0_CLK_H0

MEM_MB0_CLK_L0

C325

C325

C1.5P50N0402

C1.5P50N0402

C245

C245

C1.5P50N0402

C1.5P50N0402

C288

C288

C1.5P50N0402

C1.5P50N0402

C324

C324

C1.5P50N0402

C1.5P50N0402

C246

C246

C1.5P50N0402

C1.5P50N0402

C284

C284

C1.5P50N0402

C1.5P50N0402

C557 C22P50N0402/BC557 C22P50N0402/B

MEM_MA_ADD13

C597 C22P50N0402/BC597 C22P50N0402/B

MEM_MA_ADD12

C559 C22P50N0402/BC559 C22P50N0402/B

MEM_MA_ADD11

C564 C22P50N0402/BC564 C22P50N0402/B

MEM_MA_ADD10

C594 C22P50N0402/BC594 C22P50N0402/B

MEM_MA_ADD9

C563 C22P50N0402/BC563 C22P50N0402/B

MEM_MA_ADD8

C573 C22P50N0402/BC573 C22P50N0402/B

MEM_MA_ADD7

C568 C22P50N0402/BC568 C22P50N0402/B

MEM_MA_ADD6

C572 C22P50N0402/BC572 C22P50N0402/B

MEM_MA_ADD5

C577 C22P50N0402/BC577 C22P50N0402/B

MEM_MA_ADD4

C583 C22P50N0402/BC583 C22P50N0402/B

MEM_MA_ADD3

C578 C22P50N0402/BC578 C22P50N0402/B

MEM_MA_ADD2

C587 C22P50N0402/BC587 C22P50N0402/B

MEM_MA_ADD1

C581 C22P50N0402/BC581 C22P50N0402/B

MEM_MA_ADD0

C593 C22P50N0402/BC593 C22P50N0402/B

MEM_MA_CAS_L

C595 C22P50N0402/BC595 C22P50N0402/B

MEM_MA_WE_L

C592 C22P50N0402/BC592 C22P50N0402/B

MEM_MA_RAS_L

C589 C22P50N0402/BC589 C22P50N0402/B

MEM_MA_BANK2

C560 C22P50N0402/BC560 C22P50N0402/B

MEM_MA_BANK1

C596 C22P50N0402/BC596 C22P50N0402/B

MEM_MA_BANK0

C586 C22P50N0402/BC586 C22P50N0402/B

Decoupling Between Processor and DIMMs

Layout: Spread out on VTT pour

VTT_DDR

C310

C310

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MB_ADD13

MEM_MB_ADD12

MEM_MB_ADD11

MEM_MB_ADD10

MEM_MB_ADD9

MEM_MB_ADD8

MEM_MB_ADD7

MEM_MB_ADD6

MEM_MB_ADD5

MEM_MB_ADD4

MEM_MB_ADD3

MEM_MB_ADD2

MEM_MB_ADD1

MEM_MB_ADD0

MEM_MB_CAS_L

MEM_MB_WE_L

MEM_MB_RAS_L

MEM_MB_BANK2

MEM_MB_BANK1

MEM_MB_BANK0

C299

C299

C307

C307

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C264

C264

C271 C22P50N0402C271 C22P50N0402

C270 C22P50N0402C270 C22P50N0402

C304 C22P50N0402C304 C22P50N0402

C274 C22P50N0402C274 C22P50N0402

C276 C22P50N0402C276 C22P50N0402

C300 C22P50N0402C300 C22P50N0402

C277 C22P50N0402C277 C22P50N0402

C283 C22P50N0402C283 C22P50N0402

C279 C22P50N0402C279 C22P50N0402

C281 C22P50N0402C281 C22P50N0402

C285 C22P50N0402C285 C22P50N0402

C292 C22P50N0402C292 C22P50N0402

C287 C22P50N0402C287 C22P50N0402

C294 C22P50N0402C294 C22P50N0402

C290 C22P50N0402C290 C22P50N0402

C301 C22P50N0402C301 C22P50N0402

C302 C22P50N0402C302 C22P50N0402

C298 C22P50N0402C298 C22P50N0402

C296 C22P50N0402C296 C22P50N0402

C273 C22P50N0402C273 C22P50N0402

C303 C22P50N0402C303 C22P50N0402

C293 C22P50N0402C293 C22P50N0402

C286

C286

C0.1U16X

C0.1U16X

VCC_DDR

MEM_MB_ADD[15..0]5,7

RN12 8P4R-47R0402RN12 8P4R-47R0402

MEM_MA_CKE05,7

MEM_MB_BANK25,7

MEM_MA_BANK25,7

B B

MEM_MB_BANK15,7

MEM_MB_BANK05,7

MEM_MA_WE_L5,7

MEM_MB_CAS_L5,7

MEM_MA0_CS_L05,7

MEM_MA_CAS_L5,7

MEM_MB_CKE05,7

MEM_MA0_CS_L15,7

MEM_MA0_ODT05,7

MEM_MB0_ODT05,7

A A

5

MEM_MA_CKE0

MEM_MB_BANK2

MEM_MA_BANK2

MEM_MA_ADD7

MEM_MB_ADD7

MEM_MB_ADD8

MEM_MA_ADD8

MEM_MA_ADD4

MEM_MA_ADD3

MEM_MA_ADD1

MEM_MB_ADD4

MEM_MB_ADD0

MEM_MB_BANK1

MEM_MB_ADD10

MEM_MB_BANK0

MEM_MA_WE_L

MEM_MB_CAS_L

MEM_MA0_CS_L0

MEM_MA_CAS_L

MEM_MB_CKE0

MEM_MB_ADD15

MEM_MB_ADD14

MEM_MA0_CS_L1

MEM_MA0_ODT0

MEM_MA_ADD13

MEM_MB0_ODT0

RN15 8P4R-47R0402RN15 8P4R-47R0402

RN17 8P4R-47R0402RN17 8P4R-47R0402

RN19 8P4R-47R0402RN19 8P4R-47R0402

RN22 8P4R-47R0402RN22 8P4R-47R0402

RN11 8P4R-47R0402RN11 8P4R-47R0402

RN23 8P4R-47R0402RN23 8P4R-47R0402

VTT_DDR

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

4

0B 06/01/23 Modify

For EMI

VCC_DDR

C643

C643

X_0.1u/16V/4

X_0.1u/16V/4

VTT_DDR

VCCP

C639

C639

C638

C638

X_0.1u/16V/4

X_0.1u/16V/4

X_0.1u/16V/4

X_0.1u/16V/4

VCCP VTT_DDR

C644

C644

X_0.1u/16V/4

X_0.1u/16V/4

C650

C650

C649

C649

X_0.1u/16V/4

X_0.1u/16V/4

X_0.1u/16V/4

X_0.1u/16V/4

VTT_DDR

C645

C645

X_0.1u/16V/4

X_0.1u/16V/4

C0.1U16X

C0.1U16X

C640

C640

X_0.1u/16V/4

X_0.1u/16V/4

VCCP

C651

C651

X_0.1u/16V/4

X_0.1u/16V/4

3

VTT_DDR

C255

C255

C0.1U16X

C0.1U16X

C261

C261

C0.1U16X

C0.1U16X

C309

C309

C0.1U16X

C0.1U16X

C641

C641

X_0.1u/16V/4

X_0.1u/16V/4

VCCP

C646

C646

X_0.1u/16V/4

X_0.1u/16V/4

VCC_DDR

C652

C652

X_0.1u/16V/4

X_0.1u/16V/4

C215

C215

C0.1U16X

C0.1U16X

C305

C305

C653

C653

X_0.1u/16V/4

X_0.1u/16V/4

VCC1_2VCC1_2HT

C241

C241

C0.1U16X

C0.1U16X

C278

C278

C0.1U16X

C0.1U16X

C642

C642

X_0.1u/16V/4

X_0.1u/16V/4

C647

C647

X_0.1u/16V/4

X_0.1u/16V/4

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C217

C217

C282

C282

C648

C648

X_0.1u/16V/4

X_0.1u/16V/4

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C272

C348

C289

C289

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C344

C344

C297

C297

C348

C0.1U16X

C0.1U16X

VTT_DDR

C338

C338

C0.1U16X

C0.1U16X

C313

C313

C1000P50X

C1000P50X

C377

C377

X_C10P50N0402

X_C10P50N0402

C262

C262

C0.1U16X

C0.1U16X

C331

C331

X_C10P50N0402

X_C10P50N0402

C333

C333

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

For EMI

X_C10P50N0402

X_C10P50N0402

VCC_DDR

C326

C326

C225

C225

C272

C216

C0.1U16X

C0.1U16X

C280

C280

C0.1U16X

C0.1U16X

C376

C376

X_C10P50N0402

X_C10P50N0402

C216

C367

C367

C363

C363

C0.1U16X

C0.1U16X

C0.1U16X

C0.1U16X

C384

C384

X_C10P50N0402

X_C10P50N0402

VCC_DDR

C382

C382

C239

C239

C383

X_C10P50N0402

X_C10P50N0402

C10P50N0402

C10P50N0402

2

C383

X_C10P50N0402

X_C10P50N0402

Micro Star Restricted Secret

Micro Star Restricted Secret

Micro Star Restricted Secret

Title

Title

Title

DDR Terminatior

DDR Terminatior

DDR Terminatior

Document Number

Document Number

Document Number

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

Taipei Hsien, Taiwan

http://www.msi.com.tw

http://www.msi.com.tw

http://www.msi.com.tw

MS-7214

MS-7214

MS-7214

Last Revision Date:

Last Revision Date:

Last Revision Date:

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Tuesday, May 30, 2006

Sheet

Sheet

Sheet

835

835

835

1

Rev

Rev

Rev

0A

0A

0A

of

of

of

Page 9

5

U10F

U10F

?

C545

C545

0.1u/25V/6

0.1u/25V/6

W24

W21

W23

W20

W22

W19

Y23

V24

U22

R24

P24

P22

N22

Y21

V21

T21

R18

P16

N20

M17

Y22

V23

U21

R23

P23

P21

N21

Y20

U20

R19

P17

N19

N18

T23

T22

R21

R20

M23

M22

Y19

N16

T13

?

HT_CPU_RXD0_P

HT_CPU_RXD1_P

HT_CPU_RXD2_P

HT_CPU_RXD3_P

HT_CPU_RXD4_P

HT_CPU_RXD5_P

HT_CPU_RXD6_P

HT_CPU_RXD7_P

HT_CPU_RXD8_P

HT_CPU_RXD9_P

HT_CPU_RXD10_P