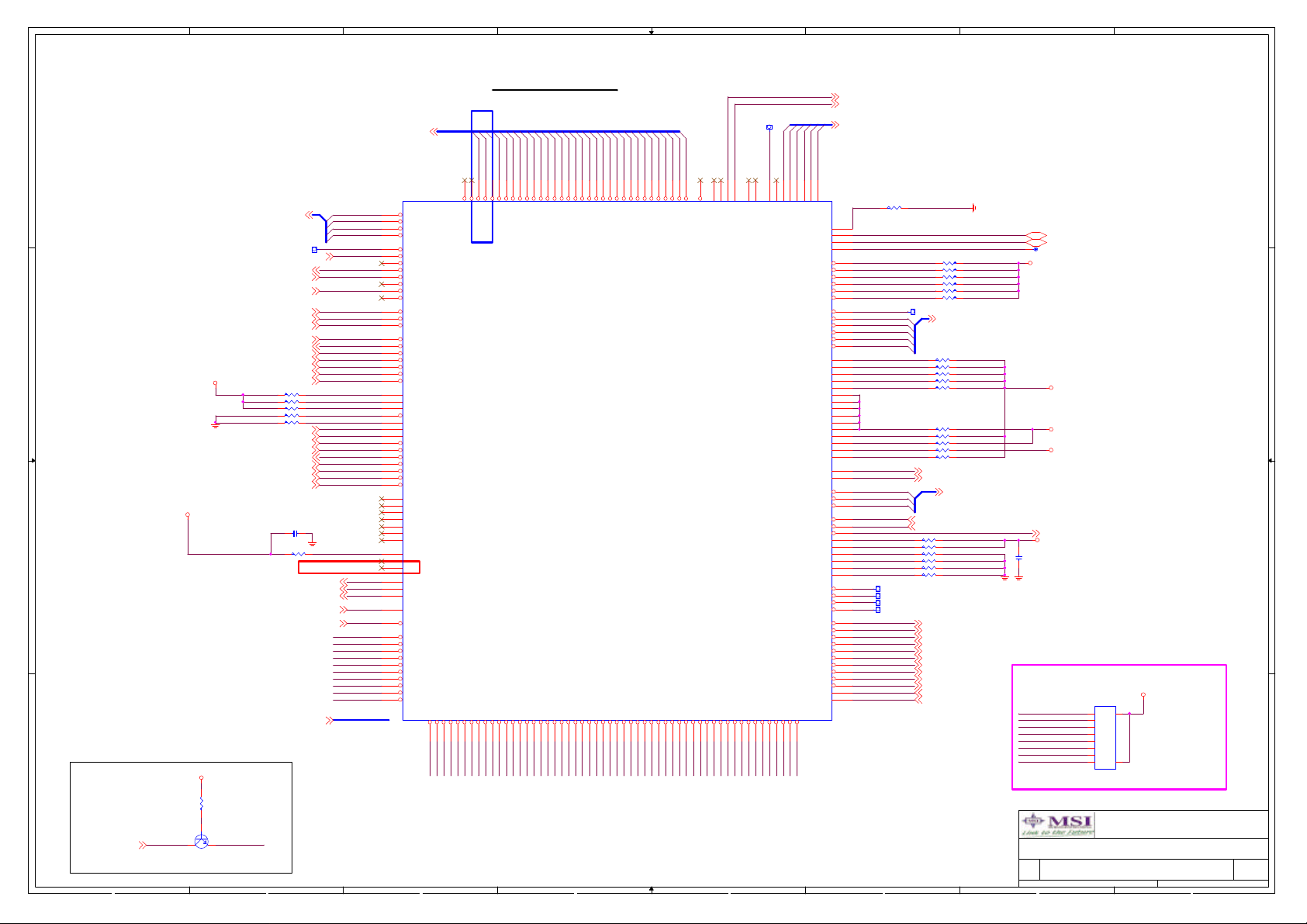

Page 1

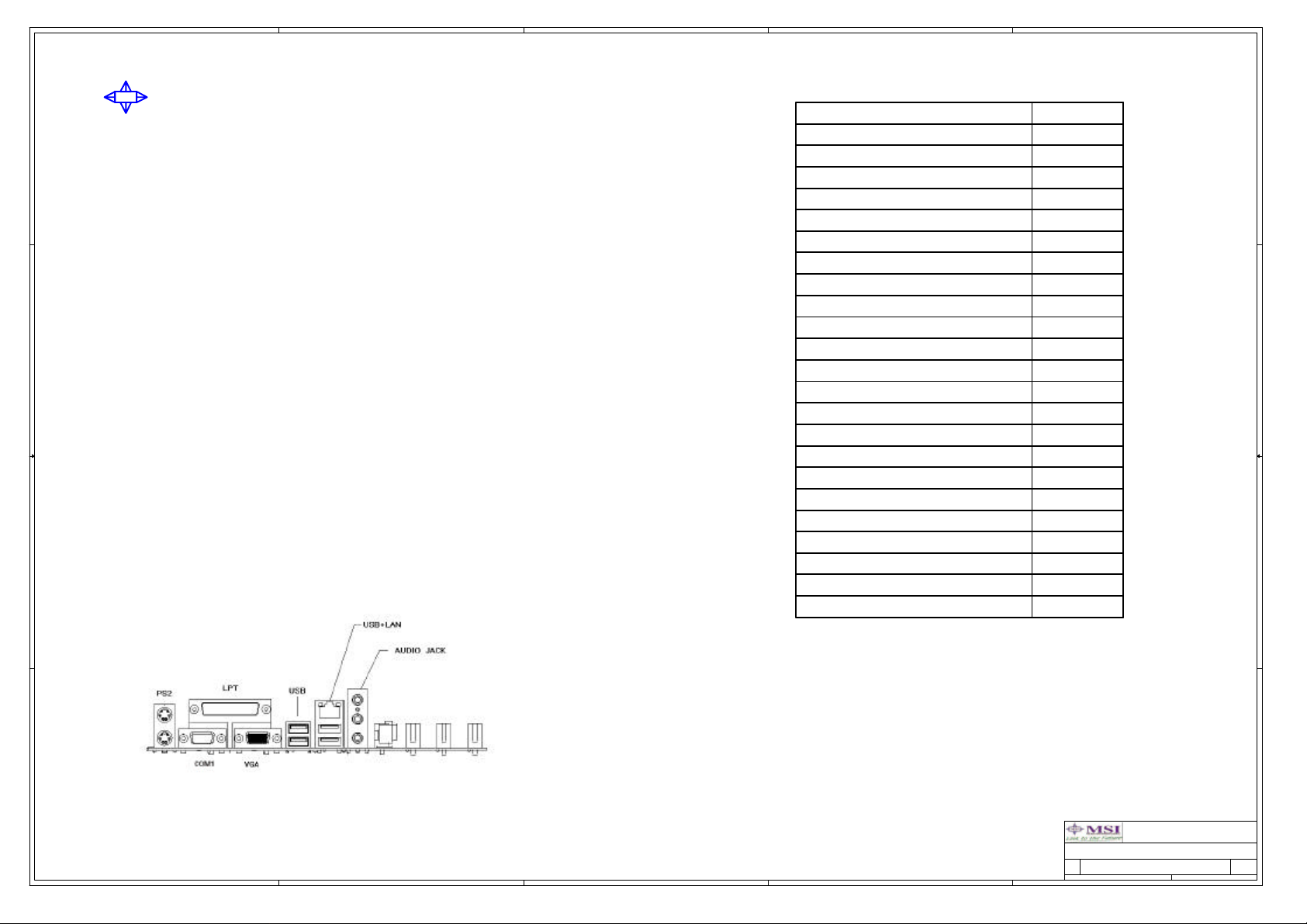

A

B

C

D

E

MSI

MS-7211 Ver:0A

4 4

CPU:

Intel Prescott LGA775 -Mainstream CPU

System Chipset:

North Bridge : VIA P4M800 Ver:CE

South Bridge : VIA VT8237R Plus

On Board Chipset:

LPC Super I/O -- W83627EHF

LAN --- RTL 8100C (10/100) / 8110SB (Giga)

AC'97 Codec --Realtek ALC655

BIOS --LPC FLASH ROM

3 3

CLOCK Chip :

CLOCK Generator --

Realtek RTM862-520

/ ICS ICS950917AF

Main Memory:

DDR * 2 (Max 2GB)

Expansion Slots:

PCI 2.3 SLOT * 2

PWM:

VRM10.1 Intersil 6566 3Phase

2 2

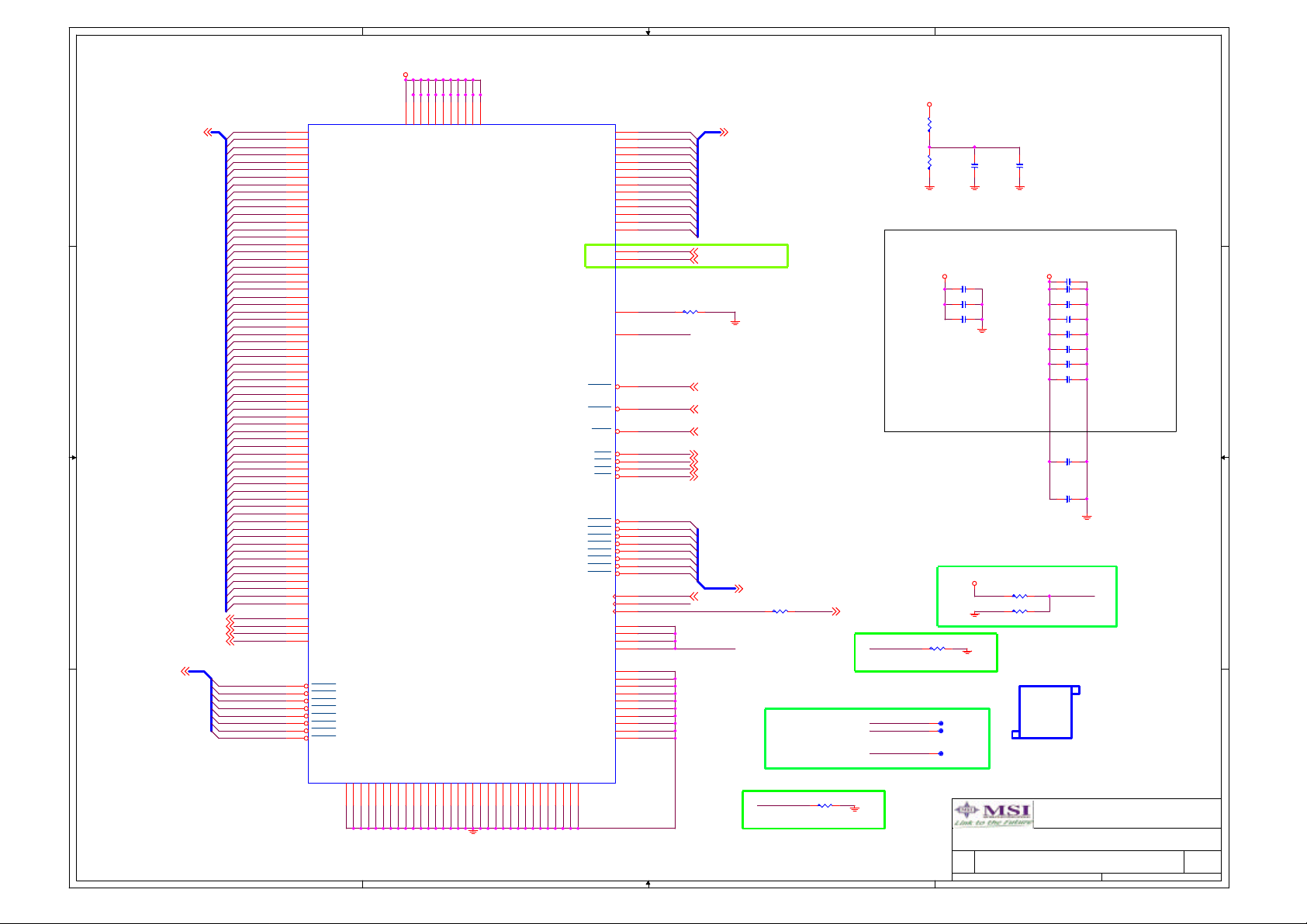

CHIPSET P4M800_CE + VT8237_PLUS

TITLE

COVER SHEET

BLOCK DIAGRAM

PWR And CLOCK Map

GPIO/MEMORY/PCI/HW STRPPING

PROCESSOR ( Intel LGA775)

NORTH BRIDGE P4M800_CE

DIMM1&2

DIMM1&2 Terminations

AGP SLOT

VGA Connector

Clock Generator RTM862-520 / ICS950917AF

SOUTH BRIDGE (VT8237R Plus)

PCI Slot 1 & 2

Realtek 8100C/8110SB

Super I/O & FAN 83627EHF-D

AC97 Realtek ALC655

IDE Connectors , KB/MS

USB Connectors

COM / Parallel Port

MS7 ACPI Controller

VRM 10.1 - Intersil 6566_3 Phases

ATX & F_Panel & BIOS

PCB Components & EMI

SHEET

8,9,10,11

17,18,19

1

2

3

4

5,6,7

12

13

14

15

16

20

21

22

23

24

25

26

27

28

29

30

1 1

Title

Size Document Number Rev

Custom

A

B

C

D

Date: Sheet of

MICRO-START INT'L CO.,LTD.

COVER SHEET

MS-7211 0A

E

1 32Thursday, July 28, 2005

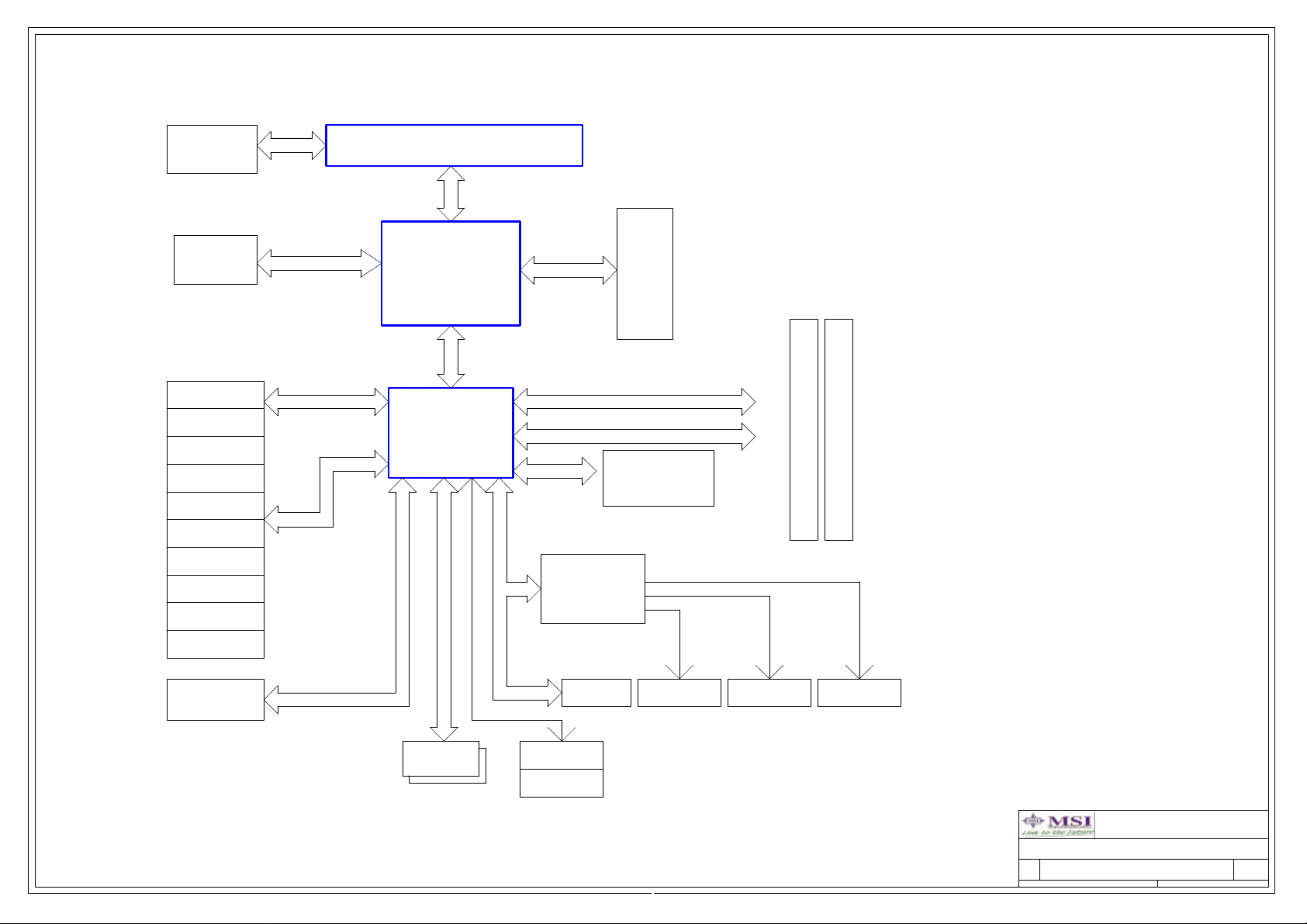

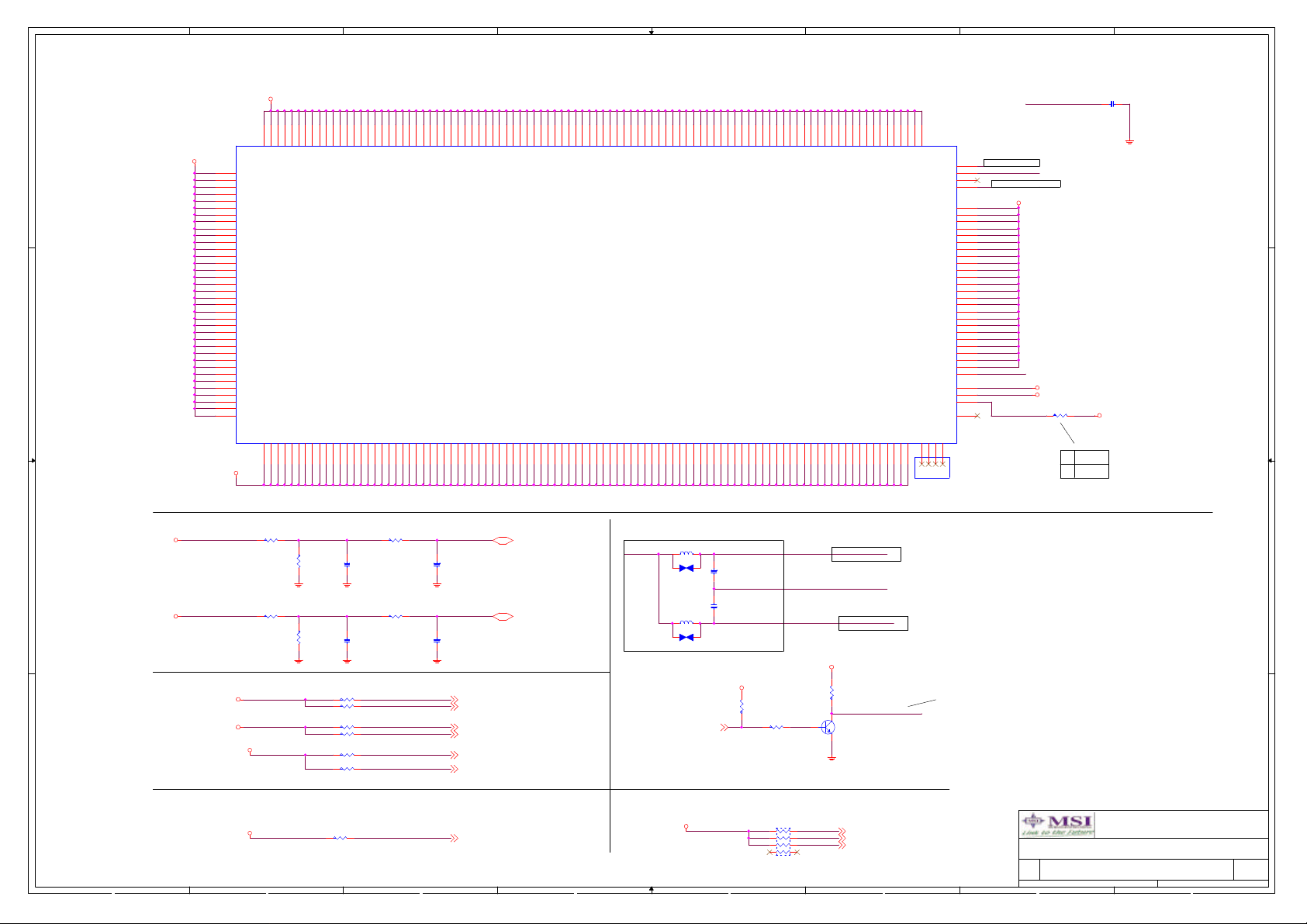

Page 2

VRM 10.1

Intersil 6566

3Phase

Block Diagram

Intel Prescott Processor-LGA775

FSB

mainstream

TDP=84W

Iccmax=78A

Icctdc=68A

1

AGP 1.5V

Connector

IDE Primary

IDE Secondary

A A

USB Port 0

USB Port 1

USB Port 2

2X/4X/8X

UltraDMA 33/66/100

USB

P4M800_CE

VCORE= +2.5VNB

VDIMM= +2.5VDIMM

VDDQ= +1.5VAGP

VLINK= +2.5V

VT8237_PLUS

VCC25= +2.5V

VCC33= +3.3V

V-Link/8bits/S533M

LPC Bus

64bit DDR

PCI

2 DDR

DIMM

Modules

PCI CNTRL

PCI ADDR/DATA

LAN

Realtek

8100C/8110SB

PCI Slot 1

PCI Slot 2

USB Port 3

USB Port 4

LPC SIO

USB Port 5

Winbond

83627EHF

USB Port 6

USB Port 7

AC'97 Codec

AC'97 Link

LPC FLASH

ROM

FDD

Parallel

Serial

X2

SATA prot1 and

port2

KEYBOARD

MOUSE

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

1

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

2 32Thursday, July 28, 2005

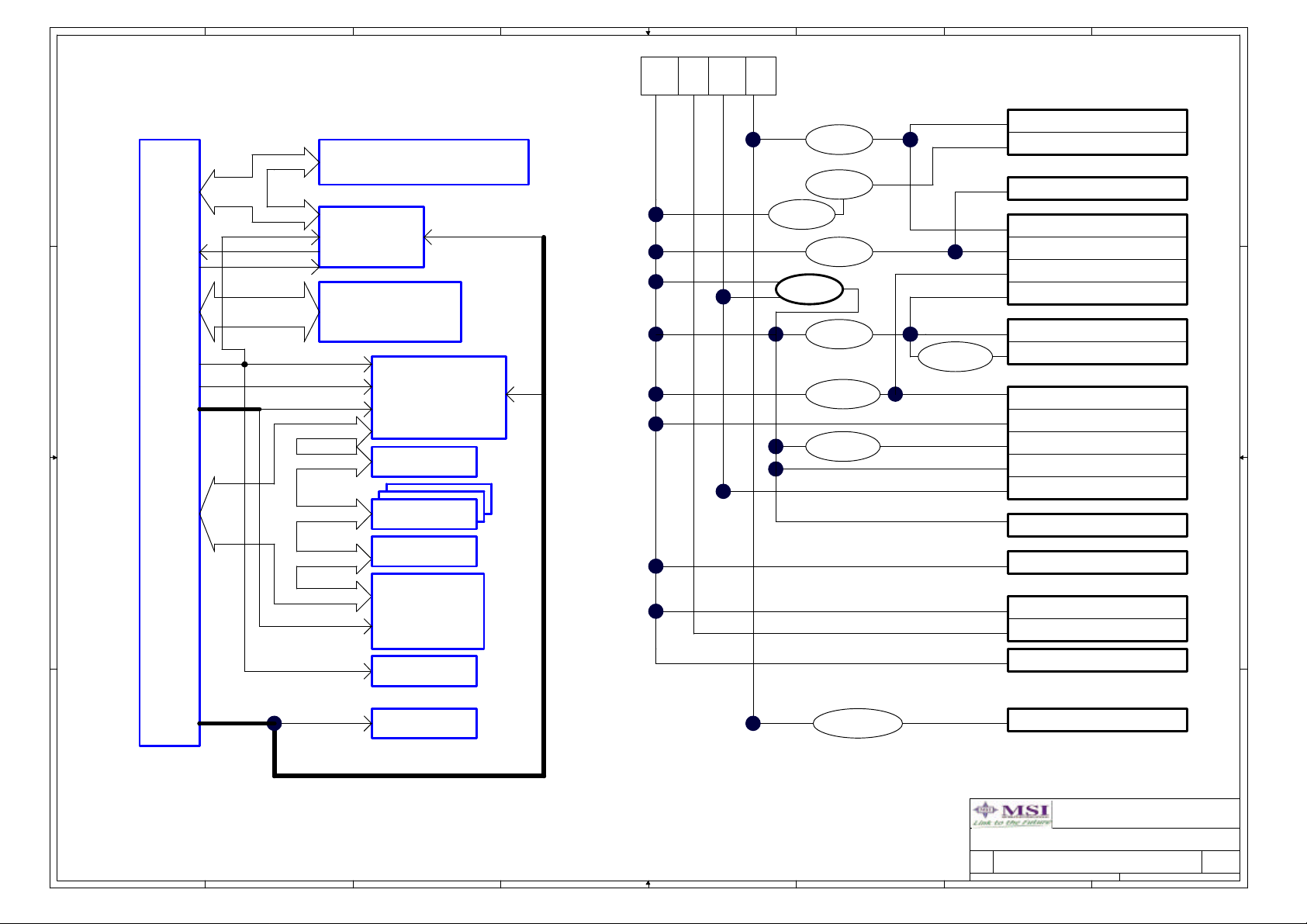

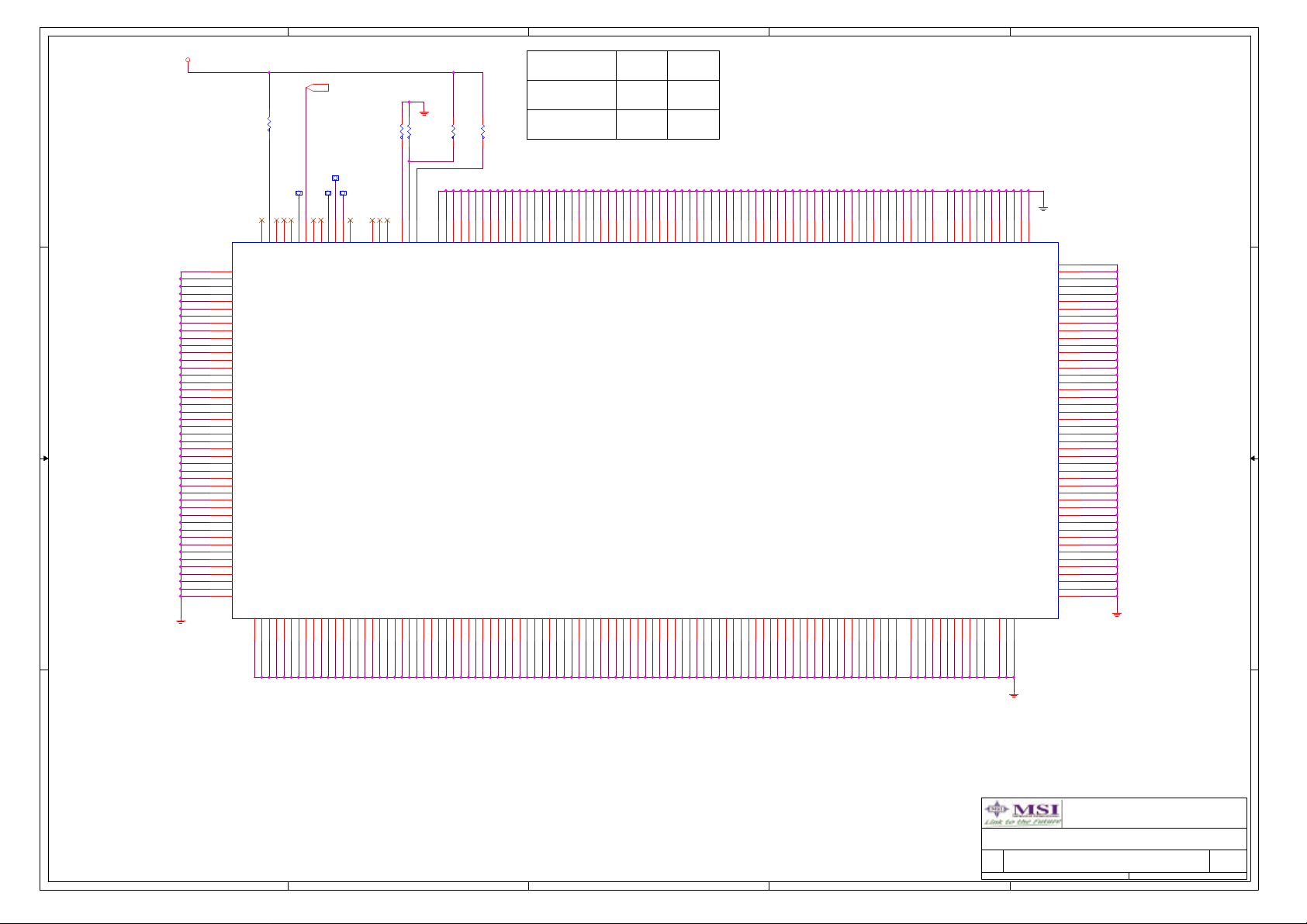

Page 3

8

7

6

5

4

3

2

1

P4M800 PLATFORM CLOCK GENERATOR MAP

3.3V 5V 5VSB 12V

P4M800_CE PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP 1.2V~1.425V

D D

VRM

PROCESSOR 1.2V

Intel LGA775 Processor

CPU HOST

CLK

GUICK

DCLKO

DCLKI

NB

P4M800_CE

GCLK_NB 66MHz

CLOCK GENERATOR

MEM CLK

0~5/CLK#0~5

C C

14.318MHZ

33MHz

48MHZ

B B

25MHZ from Crystal

SIO48MHZ

2 DDR DIMM

SB14MHz

APIC

USB

SPCLK

FWH_CLK

PCI CLK 1~2

SIOPCLK

Modules

VT8237R_PLUS

FWH

PCI Slot 1~2

Realtek 8100C/8110SB

LPC SIO

Winbond

83627EHF-E

VCLK

1.2V VREG

2.5V VREG

1.5V VREG

3VSB VREG

DDR 2.5V

VREG

2.5V VREG

2.5VSB

VREG

VTT 1.25V

VREG

AGP SLOT 1.5V

NORTH BRIDGE VCCP

NORTH BRIDGE VCC_AGP

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

3A

DDR DIMM1 / DIMM2 / DIMM3 2.5V

DDR VTT 1.25V

550mA

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

Vlink=70mA

150mA

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN VCC3_SB

FWH 3.3V

LPC SUPER I/O 3.3V

LPC SUPER I/O VCC5

10mA

120mA

AC97XIN

AGP CLK

ALC655

AGP SLOT

AC97 VDD5

VREG

CK-409 3.3V

AC97 VDD5

+12V : 0.1U 25V X 5

A A

+12V_MOS: 4.7U 35V X 1

1U 16V X 2

1000U 16V X 4

Title

PWR And CLOCK Map

Size Document Number Rev

Custom

8

7

6

5

4

3

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

2

3 32Thursday, July 28, 2005

1

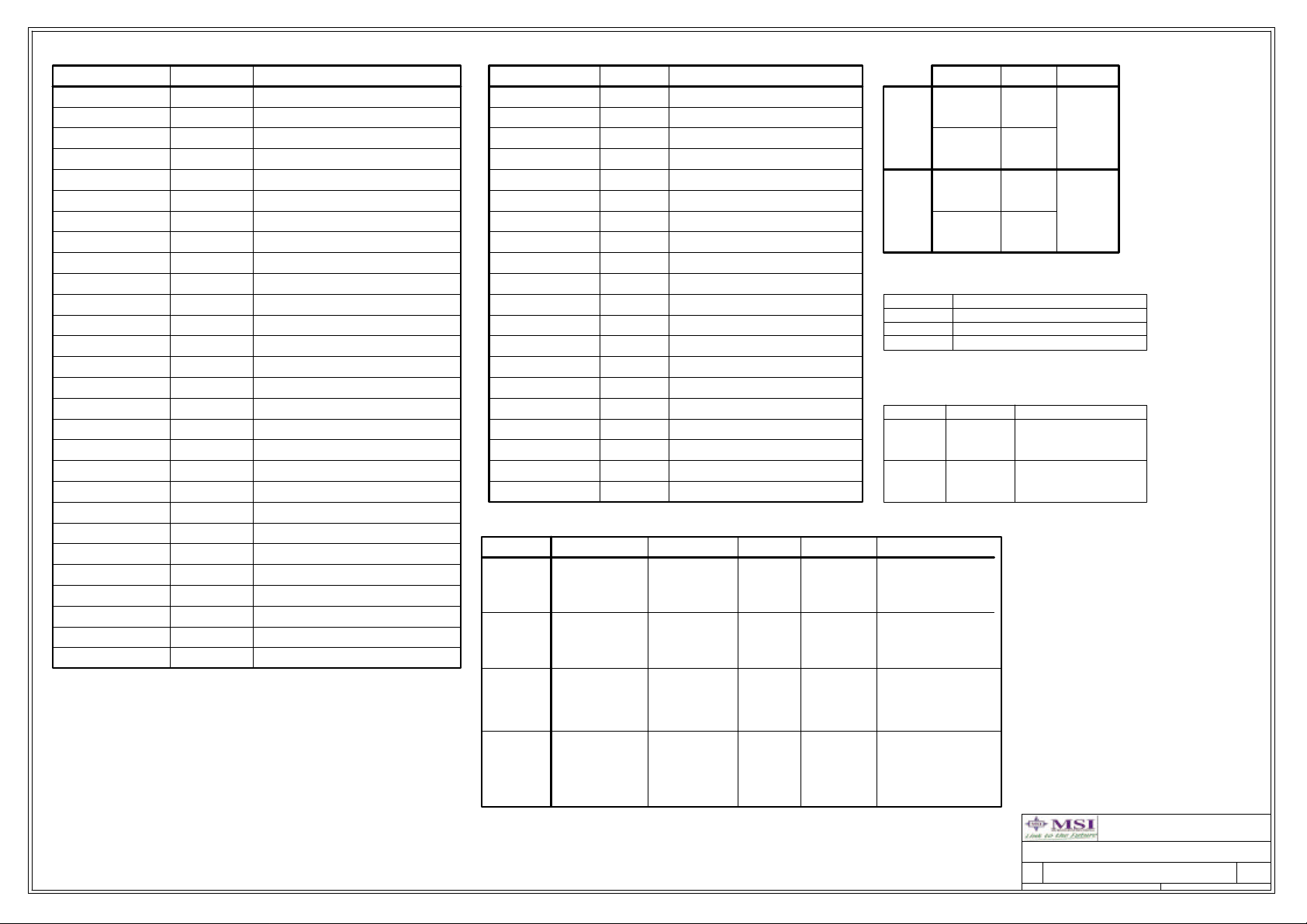

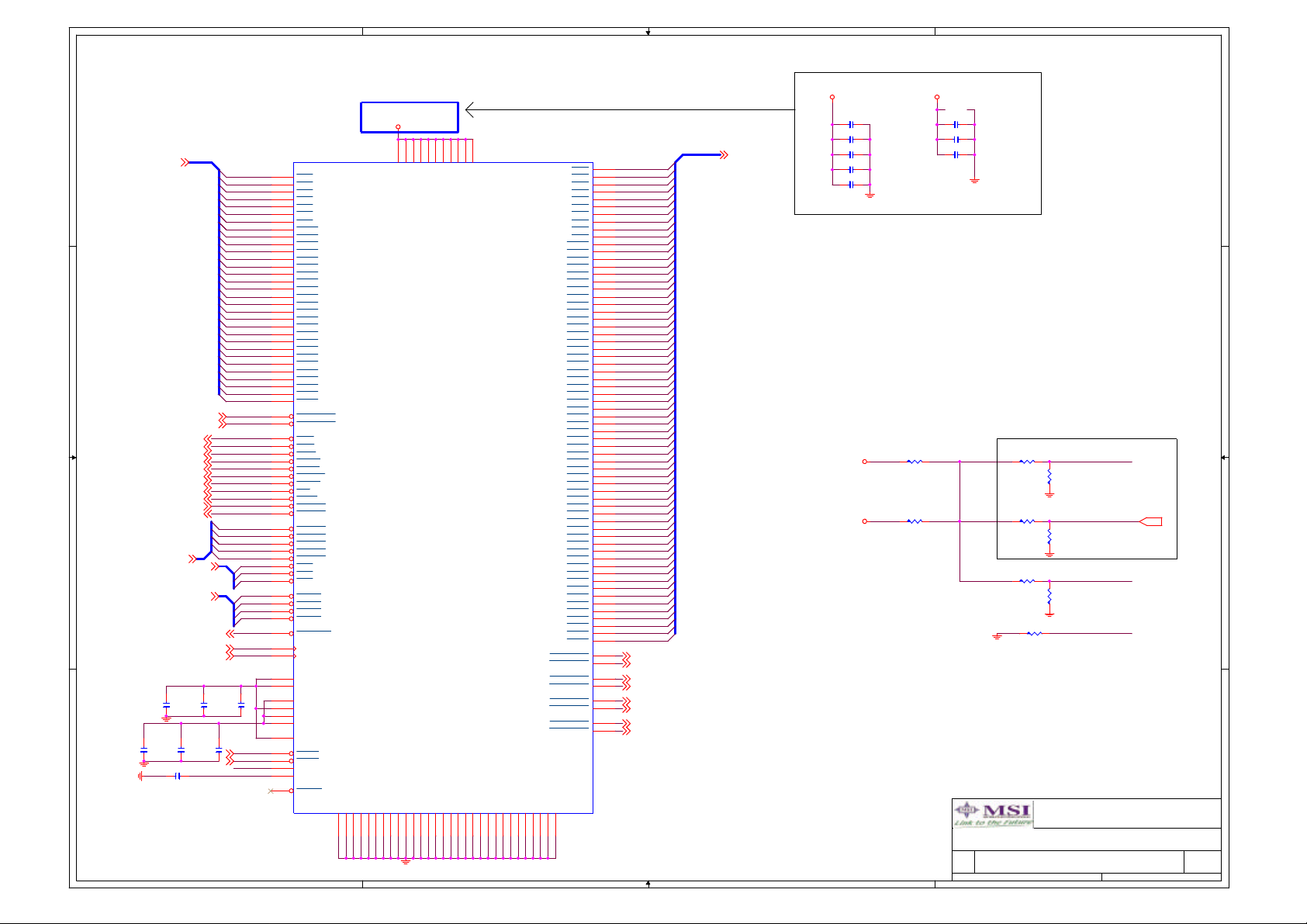

Page 4

1

VT8237R_PLUS GPIO Function Define

PIN NAME Function define

GPO0 (VDDS)

GPO1(VDDS)

GPO2/SUSA#

(VDDS)

GPO3/SUSST#(VDDS)

GPO4/SUSCLK(VDDS)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5

GPO8/GPI8/VGATE

*

GPO9/GPI9/UDPWREN

*

GPO10/GPI10/PICD0

*

GPO11/GPI11/PICD1

*

GPO12/GPI12/INTE#

*

GPO13/GPI13/INTF#

*

GPO14/GPI14/INTG#

*

GPO15/GPI15/INTH#

*

GPO20/GPI20

/ACSDIN2/PCS0#

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

A A

GPO22/GPI22/GHI#

GPO23/GPI23/DPSLP

/GPIOAGPO24/GPI24

GPO25/GPI25

GPO26/GPI26/SMBDT2

(VDDS)

GPO27/GPI27/SMBCK2

(VDDS)

GPO28/GPI28/VIDSEL

GPO29/GPI29/VRDSLP

GPO30/GPI30

GPO31/GPI31

/GPIOB

/GPIOC

/GPIOD

Default

Function

GPO0

GPO1 4.7K ohm Pull up to VCC3_SB

SUSA#

SUSST#

SUSCLK

CPUSTP#

PCISTP#

GPO7

GPI8

UDPWREN

GPI10

GPI11

GPI12

GPI13

GPI14

GPI15

GPI20/ACSDIN2

GPI21/ACSDIN3

GPI22

GPI23

GPI24

GPI25

SMBDT2

SMBCK2

GPO28

/VIDSEL

GPO29

/VRDSLP

GPI30

GPI31

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

ohm Pull up to VCC3

8.2K

4.7K ohm Pull up to VCC3

NC

1K ohm Pull up to VCC3

1K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

4.7K ohm Pull down

4.7K ohm Pull down

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

BSEL1

4.7K ohm Pull down

ohm Pull up to VCC3_SB

2.7K

ohm Pull up to VCC3_SB

2.7K

SATA_LED

4.7K ohm Pull down

BSEL0

4.7K ohm Pull down

PIN NAME Function define

GPI0

(VBAT)

GPI1

(VSUS3)

GPI2/EXTSMI#

(VSUS3)

GPI3/RING#

(VSUS3)

GPI4/LID#

(VSUS3)

GPI5/BATLOW# (VDDS)

GPI6/AGPBZ

GPI7/REQ5

GPI8/VGATE

*

GPI9/UDPWREN

*

GPI10/PICD0

*

GPI11/PICD1

*

GPI12/INTE#

*

GPI13/INTF#

*

GPI14/INTG#

*

GPI15/INTH# GPI15

*

GPI16/INTRUDER#

(VBAT)

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/APICCLK

PCI Config.

DEVICE

PCI Slot 1 PCIREQ#1 AD19 PCI_CLK1

PCI Slot 2 PCIREQ#2 AD20

Default

Function

GPI0

GPI1

EXTSMI#

RING#

LID#

BATLOW#

AGPBZ

GPI7

GPI8

UDPWREN

GPI10

GPI11

GPI12

GPI13

GPI14

INTRUDER#

CPUMISS

AOLGP1

APICCLK

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

ohm Pull up to VBAT

1M

ATADET0=>Detect IDE1 ATA100/66

4.7K ohm Pull up to VCC3_SB

RING#

4.7K ohm Pull up to VCC3_SB

ATADET1=>Detect IDE2 ATA100/66

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

NC

1K ohm Pull up to VCC3

1K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

8.2K ohm Pull up to VCC3

1M ohm Pull up to VBAT

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to

APICCLK

VCC3_SB

IDSEL

PCIGNT#1

PCIGNT#2

CLOCKREQ#/GNT# CLK GEN PIN OUTMCP1 INT Pin

PCI_CLK2

USB

Rear

Front

Port DATA +/-

I1394_USB1

LAN_USB1

JUSB1

JUSB2

USB1USB1+

USB0USB0+

USB2USB2+

USB3USB3+

USB4USB4+

USB6USB6+

USB5USB5+

USB7USB7+

PCI RESET DEVICE

Signals Target

PCIRST#1

PCIRST#2

HD_RST#

PCI slot 1-2

NB , Super I/O , LPC, LAN

Primary, Scondary IDE

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2

14

15

1010000B

1010001B

CLOCKADDRESS

DCLKA0/MDCLKA#0

DCLKA1/MDCLKA#1

DCLKA2/MDCLKA#2

DCLKA3/MDCLKA#3

DCLKA4/MDCLKA#4

DCLKA5/MDCLKA#5

OC#

OC#1

( OC#0~3 )

OC#4

( OC#4~7 )

LAN 8110SB

PIRQ#E

PCIREQ#0

PCIGNT#0

1

AD17 LAN_CLK

11

Title

GPIO/MEMORY/PCI/HW STRPPING

Size Document Number Rev

Custom

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

4 32Thursday, July 28, 2005

Page 5

8

7

6

5

4

3

2

1

CPU SIGNAL BLOCK

VCC_VRM_SENSE [28]

VSS_VRM_SENSE [28]

AN4

RSVD

RSVD

D12#D8D11#

C11

HD#11

AN5

B10

HD#10

AN6

AJ3

AK3

ITP_CLK1

VSS_SENSE

VCC_SENSE

D10#

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A11

A10

HD#9

HD#8

HD#7

HD#6

TP3

AM7

VID7#

ITP_CLK0

HD#4

HD#5

V ID5

V ID4

AM5

AL4

AK4

VID6#

VID5#

VID4#

VID_SELECT

GTLREF_SEL

TESTHI12

TESTHI11

TESTHI10

LINT1/NMI

LINT0/INTR

HD#3

HD#2

HD#1

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

AG1

AE1

AK1

AE8

AH2

AE6

AA2

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AL1

AL2

G10

D16

A20

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

HA#[3..33][8]

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

U5A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

HD#53

C14

HD#52

D52#

HD#51

HA#6

HA#8

HA#4

HA#5

HA#7

HA#19

HA#20

HA#21

HA#25

A29#

D42#

HD#41 HA#28

HA#22

HA#23

A24#

D37#

HD#36

AA5

G17

A23#

D36#

AD6

A22#

D35#

G18

HD#35

AA4

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E16

E15

HD#33

HD#34

G16

HD#32

HA#18

D32#

HD#31

HA#17

AB6

D31#

F15

G15

HD#30

HA#26

HA#27

HA#24

AF4

AF5

AB4

AC5

AB5

A28#

A27#

A26#

A25#

D41#

D40#

D39#

D38#

F20

F18

F17

E19

E18

HD#39

HD#38

HD#40

HD#37

HA#30

HA#31

HA#29

HA#32

HA#33

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

A35#

A34#

A33#

A32#

A31#

A30#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D17

HD#49

D20

HD#48

G22

HD#47

D22

HD#46

E22

HD#45

G21

HD#44

F21

HD#43

E21

HD#42

A14

C15

HD#50

HA#16

HA#14

HA#12

HA#13

HA#15

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D30#

D29#

D28#

D27#

D26#

D25#

F14

E13

D13

G14

G13

HD#28

HD#25

HD#26

HD#27

HD#29

HA#11

F12

HD#24

HA#10

U6

D24#

F11

HD#23

HA#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

HD#20

HD#21

HD#18

HD#19

HD#22

HD#17

HA#3

L5

HD#16

D11

HD#15

AC2

C12

HD#14

DBR#

D14#

B12

HD#13

AN3

D13#

HD#12

D D

IERR#[6]

X_1KR

CPU_GD[6,27]

CPURST#[6,8]

8P4R-51R

8P4R-51R

8P4R-51R

8P4R-51R

8P4R-51R

H_BSL0[6,16]

H_BSL1[6,16]

H_BSL2[6]

HDBI#0

HDBI#1

HDBI#2

HDBI#3

-EDRDY

IERR#

CPU_BOOT

HDBI#[0..3][8]

TP14

FERR#[6,19]

STPCLK#[19]

HINIT#[19]

HDBSY#[8]

HDRDY#[8]

HTRDY#[8]

HADS#[8]

HLOCK#[8]

RN6B

RN4A

RN6A

RN4C

RN6D

CPU_TMPA[22]

VTIN_GND[22]

THERMTRIP#[6,29]

CPUMISS[18]

PROCHOT#[6]

HBNR#[8]

HIT#[8]

HITM#[8]

HBPRI#[8]

HDEFER#[8]

3 4

1 2

1 2

5 6

7 8

IGNNE#[19]

SMI#[19]

SLP#[19]

C30 X_C0.1U25Y

R56

HD#[0..63][8]

B

C C

VTT_OUT_RIGHT

VTT_OUT_RIGHT

V TT_OUT_RIGHT

B B

A A

don't support willameter

VCCP

R43

X_4.7KR

B

THERM# P ROCHOT#

THERM#[18,22]

8

C E

Q4 X_N-MMBT3904_NL_SOT23

7

6

5

4

V ID0

V ID3

V ID2

V ID1

AL6

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

GTLREF0

GTLREF1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

ZIF-SOCK775-15u

B4

HD#0

VID[0..5] [28]

R32 62R0402

AN7

H1

H2

H29

H_BPM#5

AG3

H_BPM#4

AF2

H_BPM#3

AG2

H_BPM#2

AD2

H_BPM#1

AJ1

H_BPM#0

AJ2

G5

HREQ#4

J6

HREQ#3

K6

HREQ#2

M6

HREQ#1

J5

HREQ#0

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

H_TESTHI2_7

F25

H_TESTHI1

W3

H_TESTHI0

F26

RSVD_AK6

AK6

RSVD_G6

G6

G28

F28

HRS#2

A3

HRS#1

F5

HRS#0

B3

U3

U2

F3

H_COMP5

T2

H_COMP4

J2

H_COMP3

R1

H_COMP2

G2

H_COMP1

T1

H_COMP0

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

CPU_GTLREF0

CPU_GTLREF1

GTLREF_SEL

RN3A

RN4B 8P4R-51R

RN4D

RN6C

RN3B

RN3C

R50 62R

RN13A

RN13B

RN13D

RN13C

-HAP1

-HAP0

R59 60.4R1%

R65 60.4R1%

R62 60.4R1%

R75 60.4R1%

R60 60.4R1%

R86 60.4R1%

PLACE RESISTORS OUTSIDE SOCKET

TP6

CAVITY IF NO ROOM FOR VARIABLE

TP7

RESISTOR DON'T PLACE

TP4

TP5

3

TP9

HREQ#[0..4] [8]

1 2

3 4

7 8

5 6

R84 62R

R55 62R

R85 62R

R44 X_62R

R74 X_62R

CPUCLK# [16]

CPUCLK [16]A20M#[19]

HRS#[0..2] [8]

-HAP1 [8]

-HAP0 [8]

HADSTB#1 [8]

HADSTB#0 [8]

HDSTBP#3 [8]

HDSTBP#2 [8]

HDSTBP#1 [8]

HDSTBP#0 [8]

HDSTBN#3 [8]

HDSTBN#2 [8]

HDSTBN#1 [8]

HDSTBN#0 [8]

NMI_SB [19]

INTR [19]

12

34

8P4R-51R

78

8P4R-51R

56

8P4R-51R

34

8P4R-51R

56

8P4R-62R

8P4R-62R

8P4R-62R

8P4R-62R

CPU_GTLREF0 [6]

CPU_GTLREF1 [6]

TP8

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT

HBR#0 [6,8]

VTT_OUT_LEFT

C24

X_C0.1U25Y

100

VTT_OUT_LEFT

SMI#

HINIT#

IGNNE#

STPCLK#

NMI_SB

SLP#

A20M#

I NTR

Title

INTEL LGA775 - SIGNALS

Size Document Number Rev

Custom

Date: Sheet of

2

RN8

1

5

1

5

2

2

3

3

4

4

6

6

7

7

8

8

9

10

9

10

10P8R-150R

MICRO-START INT'L CO.,LTD.

MS-7211 0A

5 32Thursday, July 28, 2005

1

Page 6

8

7

6

5

4

3

2

1

VCCP

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AE9

AD8

AC8

AB8

AA8

VCCP

U5B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

R66

R73

Y26

Y27

Y28

Y29

49.9R1%0402

49.9R1%0402

Y23

Y24

Y25

R69

100R1%0402

R72

100R1%0402

W30

W29

W28

W27

U29

U30

W23

W24

W25

W26

R70

10R0402-LF

C43

C1U6.3Y50402/80-20%

R71

10R0402-LF

C45

C1U6.3Y50402/80-20%

U26

U27

U28

D D

C C

VTT_OUT_RIGHT

B B

VTT_OUT_LEFT

VCCP

VTT_OUT_LEFT CPU_GTLREF1

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT

VTT_OUT_LEFT

A A

V TT_OUT_RIGHT

VTT_OUT_LEFT

V_FSB_VTT

R47 62R

R45 120R

R63 100R

R76 62R

R54 62R

R64 62R

CPURST#

P ROCHOT#

C PU_GD

HBR#0

IERR#

THERMTRIP#

PLACE AT SB END OF ROUTE

V_FSB_VTT

8

7

R61 62R

FERR#

6

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

VCC

U23

U24

U25

CPU_GTLREF0V TT_OUT_RIGHT

C42

C220P50N0402

C48

C220P50N0402

CPURST# [5,8]

PROCHOT# [5]

CPU_GD [5,27]

HBR#0 [5,8]

IERR# [5]

THERMTRIP# [5,29]

FERR# [5,19]

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

T30

N30

CPU_GTLREF0 [5]

CPU_GTLREF1 [5]

N23

N24

N25

N26

N27

N28

N29

M24

M25

M26

M27

M28

M29

M30

V_FSB_VTT H_VCCIOPLL

K27

K28

K29

K30

M23

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

L7

X_10U100m_0805

CP1

L11

X_10U100m_0805

T23

T24

T25

T26

T27

T28

T29

J30

K23

K24

K25

K26

12

C72

C1U16Y

C75

C1U16Y

AN9

H_VSSA

H_VCCA

AN8

AN30

AN29

B

AN26

B

HS11HS22HS33HS4

AN25

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

ZIF-SOCK775-15u

4

H_VCCA

H_VSSA

H_VCCIOPLL

VTT_PWG

V TT_OUT_RIGHT

VTT_OUT_LEFT

12

CP2

VCC5_SB

VID_GD#[27,28]

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

5

4

B

VTT_OUT_LEFT

R20

1KR

R17

10KR

RN27 8P4R-470R

1

2

3

4

5

6

7

8

R33

1.25V VTT_PWRGOOD

680R

VTT_PWG

Q1

N-MMBT3904_NL_SOT23

H_BSL1 [5,16]

H_BSL2 [5]

H_BSL0 [5,16]

3

V_FSB_VTT

C65 C10U10Y0805

CAPS FOR FSB GENERIC

B

V_FSB_VTT

VTT_SEL

B

VTT_OUT_RIGHT

VTT_OUT_LEFT

R87

X_1KR

VCC3

TEJ/PSC

0

1

RSVD

Title

INTEL LGA775 - POWER

Size Document Number Rev

Custom

Date: Sheet of

2

MICRO-START INT'L CO.,LTD.

MS-7211 0A

6 32Thursday, July 28, 2005

1

Page 7

1

VTT_OUT_RIGHT

VTT_OUT_RIGHT

GTLVREF_NB

2

3

4

5

MSID1 MSID0

05 Per FMB

0

0

TP12

F23

VSS

AF25

AF26

B13

RSVDF6RSVD

VSS

VSS

AF27

AF28

VSS

VSS

AF29

R57

R53

62R0402

62R0402

MSID1

MSID0

H_COMP6

Y3

RSVDJ3RSVDN4RSVDP5RSVDV1RSVDW1RSVD

VSS

VSS

VSS

VSS

VSS

VSS

AF3

AF6

AF7

AF30

AG10

AG13

AG16

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

AG17

AG20

AG23

R51

62R0402

A A

TP10

TP11 TP13

H_COMP7

AC4

AE3

AE4

D14

E23

AE30

RSVD

VSS

AE5

RSVD

VSS

AE7

RSVD

VSS

AF10

RSVDD1RSVD

VSS

VSS

AF13

AF16

E24

RSVD

VSS

AF17

RSVD

VSS

AF20

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF23

AF24

U5C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

AA23

VSS

AA24

VSS

AA25

VSS

AA26

B B

C C

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AA3

AA6

AA7

AB1

AB7

AC3

AC6

AC7

AD4

AD7

AE2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

VSS

AG24

R52

X__62R0402

VSS

VSS

AH1

AG7

AH10

VSS

VSS

AH13

VSS

AH16

R58

62R0402

V30

VSSV3VSS

VSS

VSS

AH17

AH20

05 Value FMB

V29

V28

V27

V26

V25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AH23

AH24

V24

V23

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

AJ10

AJ13

AJ16

AJ17

VSS

AJ20

AJ23

VSS

AJ24

VSS

AJ27

VSS

AJ28

VSS

R30

AJ29

VSS

R29

AJ30

VSS

VSS

R28

AJ4

VSS

VSS

R27

AJ7

VSS

VSS

0

R26

VSS

VSS

AK10

R25

VSS

VSS

AK13

R24

VSS

VSS

AK16

R23

VSS

VSS

AK17

AK2

1

P30

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

AK20

AK23

AK24

P29

VSS

VSS

AK27

P28

VSS

VSS

AK28

P27

AK29

P26

VSS

VSS

AK30

VSS

VSS

P25

AK5

VSS

VSS

P24

AK7

P23

VSS

VSS

AL10

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL13

AL16

AL17

AL20

AL23

AL24

AL27

VSS

L30

AL28

VSS

VSSL3VSS

VSS

AL3

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

AN1

VSS

VSS

AN10

VSS

AN13

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

AN16

AN17

VSS

H28

AN2

VSS

VSS

VSS

VSS

AN20

VSS

VSS

AN23

VSS

VSS

AN24

VSS

VSS

AN27

VSS

VSS

AN28

VSS

VSS

VSSB1VSS

B11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

B14

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

L26

VSS

VSS

AM13

L25

VSS

VSS

AM16

L24

VSS

VSS

AM17

L23

VSS

VSS

AM20

VSSK7VSS

VSS

AM23

K5

VSS

AM24

K2

VSS

AM27

VSS

AM28

VSS

AM4

L29

L28

L27

VSS

VSS

VSS

VSS

VSS

AL7

AM1

AM10

D D

Title

INTEL LGA775 - GND

Size Document Number R ev

A3

1

2

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

7 32Thursday, July 28, 2005

5

Page 8

4

3

2

1

VIA confirmed

V_FSB_VTT

D D

HA#[3..33][5]

C C

HADSTB#0[5]

HADSTB#1[5]

HADS#[5]

HBNR#[5]

HBPRI#[5]

HBR#0[5,6]

HDBSY#[5]

HDEFER#[5]

HDRDY#[5]

HIT#[5]

HITM#[5]

HLOCK#[5]

HTRDY#[5]

near NB

C0.01U50X

HREQ#[0..4][5]

near NB

C89

X_C0.01U50X

HRS#[0..2][5]

HDBI#[0..3][5]

CPURST#[5,6]

NBHCLK[16]

NBHCLK#[16]

C96

C284

C94

C0.01U50X

GTLVREF_NB

C280

GTLVREF_NB1

-HAP0[5]

-HAP1[5]

C0.01U50X

C286

HCOMPVREF

4

B B

C0.01U50X

C0.01U50X

C0.01U50X

A A

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

C281

-HAP0

-HAP1

HRCOMP

Y29

V27

AA29

Y27

Y26

AC27

AA28

AB27

AA27

AC29

AB29

AB28

AC26

AD29

T28

R28

N29

N28

P29

P27

R27

N26

T26

P26

R25

N27

N25

R29

T27

U26

T25

W28

R26

M29

M28

T29

K26

M25

U27

M26

L27

U29

L29

M24

W27

V28

V26

W29

V29

L26

M27

K25

C29

H27

B21

A21

D14

Y23

W23

R24

V24

F22

G24

F19

F16

L24

N24

W26

G25

G26

K24

P4M800 CE

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HADSTB0

HADSTB1

ADS

BNR

BPRI

BREQ

DBSY

DEFER

DRDY

HIT

HITM

HLOCK

HTRDY

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

RS0

RS1

RS2

HDBI0

HDBI1

HDBI2

HDBI3

CPURST

HCLK+

HCLK-

HAVREF0

HAVREF1

HDVREF0

HDVREF1

HDVREF2

HDVREF3

GTLVREF

HAP0

HAP1

HRCOMP

HCOMPVREF

DPWR

GND

GND

A16

A19

U19

T19

R19

P19

N19

M19

L19

L18

L17

L16

L15

HD0

GND

V18

GND

U18

HDSTB0P

HDSTB0N

HDSTB1P

HDSTB1N

HDSTB2P

HDSTB2N

HDSTB3P

HDSTB3N

GND

GND

GND

T18

AC28

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

L25

L28

E29

E26

E25

E22

B25

B28

B22

D15

D16

D19

H26

H29

GND

GND

GND

GND

P25

P28

Y25

Y28

P18

U28

U25

N18

R18

M18

3

D27

D26

A29

C26

C28

D28

A27

B29

A26

B26

D25

E24

A25

A28

D24

C25

K28

K29

J28

K27

J26

J29

J25

J27

F28

G29

G27

D29

E27

F27

E28

F29

E23

B24

C24

A24

A23

B23

A22

C23

F21

C22

E21

C21

D20

D21

F20

E20

B19

C19

B20

B18

C20

A20

C18

B17

B16

A17

C14

C15

A18

B15

B14

A15

B27

C27

H28

G28

D23

D22

C17

C16

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBP#0 [5]

HDSTBN#0 [5]

HDSTBP#1 [5]

HDSTBN#1 [5]

HDSTBP#2 [5]

HDSTBN#2 [5]

HDSTBP#3 [5]

HDSTBN#3 [5]

BY PASS CAP

HD#[0..63] [5]

V_FSB_VTT V_FSB_VTT

CB56

C10U10Y0805

CB63

C10U10Y0805

CB41

X_C0.1U25Y

CB54

C1U16Y

CB64

C1U16Y

Component Side

VCCP

V_FSB_VTT

2

R105

X_0R

R106

0R

CB131

C10U10Y0805

CB129

X_C0.1U25Y

CB134

C1U16YU6A

Solder Side

R109 49.9R1%

R112 49.9R1%

R110 100R1%

R102 20.5R1%

Title

P4M800-CPU

Size Document Number Rev

Custom

Date: Sheet of

MS-7211 0A

GTLVREF_NB1

R108

100R1%

GTLVREF_NB

R114

100R1%

HCOMPVREF

R111

49.9R1%

HRCOMP

MICRO-START INT'L CO.,LTD.

1

8 32Thursday, July 28, 2005

GTLVREF_NB

Page 9

4

3

2

1

VCC_DDR

VCC_DDR

W12

W13

W14

W15

W16

W17

W18

W19

VCC25MEM

VCC25MEM

VCC25MEM

GND

GND

GND

AH8

AH11

AH14

AH17

V19

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

GND

GND

GND

GND

AH20

AH23

AH25

GND

AH28

AF5

GND

M17

GND

3

N17

GND

MAA0

AF13

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

BA0

BA1

DMCOMP

MEMDET

SRAS

SCAS

SWE

CS0

CS1

CS2

CS3

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

MCLKIA

MCLKO-

MCLKO+

MEMVREF1

MEMVREF2

MEMVREF3

MEMVREF4

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

T17

R17

U17

T15

V17

V15

U15

R15

P17

AD15

AJ15

AJ16

AJ17

AF16

AG15

AE18

AF17

AE19

AJ14

AF20

AE21

AD7

AF12

AJ13

AE5

AE24

AE12

AF9

AF11

AD9

AF8

AG7

AF7

AF28

AJ27

AJ23

AJ19

AG11

AH7

AH3

AE3

AD26

AE26

AF26

AD23

AD17

AD11

AD8

M16

N16

P16

R16

T16

U16

V16

M15

N15

P15

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

R150 301R0402

MEMDET

-CS0

-CS1

-CS2

-CS3

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

DCLKI

MCLKO-

MAA[0:13] [12,13]

BA0 [12,13]

BA1 [12,13]

-SRASA [12,13]

-SCASA [12,13]

-SWEA [12,13]

-CS0 [12,13]

-CS1 [12,13]

-CS2 [12,13]

-CS3 [12,13]

-DQS[0:7] [12,13]

DCLKI [16]

DCLKO+

DCLKO as short as passable

DCLKI = DCLKx + 2 "

R143 22R0402

MVREF_NB

DCLKI

DCLKO [16]

MCLKO-

Test Point

(Place near their respective balls of NB)

C279 X_C5P50N

Near to NB chip

2

R131

100R

MVREF_NB

R132

C289

100R

C1000P50X

VCC_DDR VCC_DDR

Component Side

VCC_DDR

R101 X_10KR0402

Near to NB chip

DCLKI

DCLKO

MCLKO-

TP15

1

TP2

1

TP1

1

Title

P4M800-DDR

Size Document Number Rev

Custom

Date: Sheet of

MVREF_NB = 0.5* VCCDDR

C285

C1000P50X

C291

CB75

C10U10Y0805

CB48

X_C10U10Y0805

CB67

X_C1U16Y

C0.01U50X

CB132

C10U10Y0805

CB135

C10U10Y0805

CB138

C0.1U25Y

CB130

C1U16Y

CB141

X_C1U16Y

CB137

X_C1U16Y

CB133

C1U16Y

CB127

X_C10U10Y0805

CB145

X_C1U16Y

Solder Side

R326 X_1KR1%

R327 1KR1%

MEMDET

HEATSINK1

MCH

Heatsink

HS-MS7059

MICRO-START INT'L CO.,LTD.

MS-7211 0A

1

9 32Thursday, July 28, 2005

V11

GND

AE14

GND

AE16

GND

AE17

GND

AE20

AE23

W11

VCC25MEM

VCC25MEM

GND

GND

GND

AE28

AE25

VCC25MEM

VCC25MEM

GND

GND

AH5

AH2

AD28

AE27

AF27

AG28

AD27

AE29

AG27

AG29

AH29

AJ29

AG25

AJ25

AJ28

AH27

AH26

AJ26

AJ24

AG24

AJ22

AG21

AH24

AG23

AG22

AJ21

AH21

AJ20

AG18

AH18

AG20

AH19

AJ18

AG17

AJ12

AG12

AJ10

AJ9

AH12

AJ11

AG10

AH9

AG8

AJ7

AJ6

AH6

AG9

AJ8

AG5

AJ5

AH4

AJ4

AJ2

AH1

AG4

AF4

AG3

AJ1

AG1

AF2

AD3

AD1

AG2

AF3

AE1

AD2

AF21

AF23

AE22

AF24

AF29

AG26

AH22

AG19

AH10

AG6

AJ3

AF1

P4M800 CE

U6B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKE0

CKE1

CKE2

CKE3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

AE2

GND

AE8

GND

GND

AE11

4

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKEA0

CKEA1

CKEA2

CKEA3

D D

C C

B B

MD[0:63][12, 13]

CKEA0[12,13]

CKEA1[12,13]

CKEA2[12,13]

CKEA3[12,13]

-DQM[0:7][12,13]

A A

Page 10

4

VCC_AGP

M11

N11

P11

R11

GND

P13

GND

P14

R12

VCC15AGP

VCC15AGP

VCC15AGP

VCC15AGP

GND

GND

GND

GND

T12

R13

R14

T11

VCC15AGP

GND

GND

T14

T13

U12

VLAD[0:7][19]

D D

UPSTB[19]

-UPSTB[19]

UPCMD[19]

C C

+1.5VNB

B B

A A

VCC_DDR

R97

VSUS15

VSUS15

-SUSST[18]

PCIRST#2[21,22,27,29]

-PWROK_NB[18]

4.7KR

VBE0[19]

DNSTB[19]

-DNSTB[19]

DNCMD[19]

TESTIN_NB

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

LVREF_NB

LCOMPP

TESTIN_NB

AVDD1

AVDD2

V1

U2

Y2

Y3

T2

T3

AA2

AA1

U3

W2

W1

V2

V3

AA3

W3

V4

T4

U11

U10

V10

K10

K11

K12

K13

K15

K17

K19

K20

Y10

Y12

Y14

Y16

Y18

Y20

L10

N10

R10

W10

M20

P20

T20

V20

AC25

AB1

AB3

AF25

AC1

AB2

AA25

AD25

AA26

AD24

P4M800 CE

U6C

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPSTB+

UPSTBDNSTB+

DNSTBUPCMD

DNCMD

VLVREF

VLCOMPP

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

VSUS15

SUSST

TESTIN

RESET

PWROK

VCCA33HCK

VCCA33MCK

GNDAHCK

GNDAMCK

M12

GND

M13

GND

M14

GND

N12

GND

N13

GND

N14

GND

GND

P12

3

GD0/FPD10

GD1/FPD11

GD2/FP1CLK

GD3/FPD09

GD4/FPD08

GD5/FPD07

GD6/FPD06

GD7FPD05

GD8/FP1DET

GD9/FP1HS

GD10/FPD01

GD11/FPD23

GD12/FPD00

GD13/FPD22

GD14/FPD21

GD15/FPD20

GD16/FPD18

GD17/FPD17

GD18/FPD16

GD19/FPDE

GD20/FPD14

GD21/FPCLK

GD22/FPD13

GD23/FPD15

GD24/GDVP1D09

GD26/GDVP1D10

GD27/GDVP1D04

GD28/GDVP1D07

GD29/GDVP1D06

GD30/GDVP1D08

GD31/GDVP1DET

GC#BE0/FPD03

GC#BE1/SBPLDAT

GC#BE2/FPD19

GC#BE3/GDVP1D11

GFRAME/FPHS

GIRDY/SBPLCLK

GDEVSEL/FPVS

GSTOP/FP1CLK

GPAR/FP1VS

GWBF/FPCLK

GREQ/SBDDCCLK

GGNT/SBDDCDAT

GSERR/FP1DE

AGP8XDET

GST0/ENAVEE

GST1/ENAVDD

GST2/ENABLT

GSBSTBF/GDVP1D01

GSBSTBS/GDVP1D02

GADSTBF0/FPD04

GADSTBS0/FPD02

GADSTBF1/FPD12

GADSTBS1/FPDET

GSBA0/GDVP1VS

GSBA1/GDVP1DE

GSBA2/GDVP1D00

GSBA3/GDVP1HS

GSBA4/GDVP1D05

GSBA5/GDVP1D03

GSBA6/GDVP1CLK

GSBA7/GDVP1CLK

AGPVREF1

AGPVREF2

AGPCOMPN

AGPCOMPP

U13

GND

U14

GND

AGPBUSY

GND

GND

GND

V12

V13

V14

GND

GD25

GTRDY

GDBIH

GRBF

GDBIL

GCLK

P3

P4

R3

R4

R1

N2

P1

R2

M3

M1

N4

L3

L1

N5

K2

R6

J2

H3

H1

K4

G1

G2

K5

G3

J6

K6

J4

F2

J5

F3

H4

E1

M2

K1

J1

L6

L4

M5

K3

J3

M4

P6

G5

F4

B3

D5

C4

M6

H6

C5

E4

E3

F5

C1

C2

N1

N3

G4

F1

A1

A2

B1

C3

D1

D4

D2

D3

N6

G6

R5

A4

A3

T1

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

AGP8XDET 0=ENABLE

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPVREF

AGPVREF

AGPCOMPN

AGPCOMPP

GD[0:31] [14]

GBE0 [14]

GBE1 [14]

GBE2 [14]

GBE3 [14]

GFRAME [14]

GIRDY [14]

GTRDY [14]

GDEVSEL [14]

GSTOP [14]

GPAR [14]

DBIH [14]

RBF [14]

WBF [14]

GREQ [14]

GGNT [14]

GSERR [14]

DBIL [14]

AGP8X_DET_NB [14]

ST0 [14]

ST1 [14]

ST2 [14]

SB_STBF [14]

SB_STBS [14]

AD_STBF0 [14]

AD_STBS0 [14]

AD_STBF1 [14]

AD_STBS1 [14]

SBA[0:7]

SBA[0:7] [14]

GCLK_NB [16]

AGPBZ [19]

CB144

C0.1U25Y

2

12

CP3

X_COPPER

C79

C1U16Y

AGPVREF [14]

PUT CAP ON THE BOTTOM OF PIN AF7

CB76

C1000P50X

AGPCOMPN

R134

1

VCC VSUS15 Regulator

VCC3_SB VSUS15

U2

_LT1087S_SOT89

2

ADJ

1

R183

3.9KR1%

R190

1KR1%

+1.5VNB

+

C140

C10U16EL

C146

C10U10Y1206

VIN3VOUT

C152

C0.1U25Y

Solder Side

CP4

X_COPPER

VCC_AGP

CB136

C10U10Y0805

CB143

C1U16Y

CB142

X_C1U16Y

VCC3VCC3

12

FB2

X_220L2_50

AVDD2

C83

C1U16Y

+1.5VNB

R141

1.4KR1%

LVREF_NB

R149

1KR1%

LVREF_NB => VDD/4=0.625

CM2

X_C1000P50X

C293

X_C0.1U25Y

VCC_AGP

C126

C0.1U25Y

Component Side

VCC_AGP

60.4R1%

FB1

X_220L2_50

AVDD1

VCC_AGP

CB89

C0.1U25Y

CB84

C0.1U25Y

CB90

C0.1U25Y

CM1

X_C1000P50X

C143

C10U10Y1206

C288

C0.01U50X

C283

X_C0.1U25Y

C282

C10U10Y0805

C292

C0.1U25Y

C290

C0.1U25Y

C287

C1U16Y

CB128

C10U10Y0805

RN88

X_8P4R-0R

RN89

X_8P4R-0R

+1.5VNB

78

56

34

12

78

56

34

12

Strapping For NB_TEST Mode

TESTIN BISTIN RBF WBF

1 1 x x Disable all TEST mode

4

LCOMPP

3

R137 402R1%

AGPCOMPP

R136

60.4R1%

2

Title

P4M800-VLINK&GRAPHIC

Size Document Number Rev

Custom

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

1

10 32Thursday, July 28, 2005

Page 11

4

U6D

D D

FPD4

RN40

8P4R-4.7KR

1 2

3 4

5 6

7 8

FPD8[14]

C C

FPD8

C13

B13

A13

D13

E13

D12

C12

A12

B12

E12

B11

A11

E11

C11

A10

B10

E10

C10

D11

B9

DVP0D00/TVD00

DVP0D01/TVD01

DVP0D02/TVD02

DVP0D03/TVD03

DVP0D04/TVD04

DVP0D05/TVD05

DVP0D06/TVD06

DVP0D07/TVD07

DVP0D08/TVD08

DVP0D09/TVD09

DVP0D10/TVD10

DVP0D11/TVD11

GPO0

GPOUT

TVCLKR

DVP0DE/TVDE

DVP0HS/TVHS

DVP0VS/TVVS

DVP0CLK/TVCLK

DVP0DET

P4M800 CE

GFX power up strapping setting:

TVD4/DVP0D4 =>AGP Port Muxing

TVD5/DVP0D5 =>Dedicated DVI Port Configuration

TVD6/DVP0D6 =>Dedicated DVI Port Selection

TVD8/DVP0D8 =>External AGP Function Enable

TVD9/DVP0D9 =>PCI Signal Test Output Enable

B B

TVD10/DVP0D10 =>CPUCK/MCK Clock Select

TVD7/DVP0D7 =>GFX Clock Select(VCK/LCDCK/ECK)

0: Two 12-bit DVI interface

1: One 24-bit Panel interface

0: TMDS

1: TV Encoder

0: Disable

1: Enable

0: External

1: Internal

0: Disable

1: Enable

0: From NB

1: From External

0: Refer Internal PLL

1: From External

VCCPLL1

VCCPLL2

E7

D7

D8

C7

VCCA33PLL1

VCCA33PLL2

VCCA33DAC1

VCCA33DAC2

GNDB4GNDE2GNDE5GNDH2GNDH5GNDL2GNDL5GNDP2GNDP5GNDU1GNDU4GND

GNDB2GND

A14

FPD8

FPD4

VCCDAC1

VCCDAC2

VCC3

L13

L12

VCC33GFX

R118

X_1KR

R116

10KR

L14

RSET

VCC33GFX

VCC33GFX

HSYNC

VSYNC

SPCLK1

SPCLK2

SPD1

SPD2

DISPCLKI

DISPCLKO

GNDAPLL1

GNDAPLL2

GNDADAC2

GNDADAC1

Y1

VCC3

INTA

AR

AG

AB

XIN

R115

X_1KR

R113

10KR

B6

A5

B5

A6

B8

A8

A7

A9

D9

E9

D10

E8

C8

C9

B7

C6

D6

E6

3

AR [15]

AG [15]

AB [15]

RSET

R126

80.6R1%

HSYNC [15]

VSYNC [15]

GUICK [16]

PIRQ#A [14,17,20]

SPDCLK2 [15]

SPD2 [15]

R119

22R0402

VCC3

CB139

2

CP5

X_COPPER

CP8

X_COPPER

X_C1U16Y

CB140

C0.1U25Y

C98

X_C0.1U25Y

VCC3

12

FB3

X_220L2_50

VCCPLL1

FB6

X_220L2_50

VCCPLL2

CM3

X_C1000P50X

CM6

X_C1000P50X

C104

C1U16Y

VCC3 VCC3

12

C109

C1U16Y

CP6

X_COPPER

CP7

X_COPPER

VCC_DDR

12

C105

C1U16Y

12

C107

X_C1000P50X

C0.01U50X

C22

C69

X_C1U16Y

C111

C1U16Y

C84

C10U10Y0805

VCC3

FB4

X_220L2_50

1

VCCDAC1

FB5

X_220L2_50

VCCDAC2

CM4

X_C1000P50X

CM5

C1U16Y

A A

Title

P4M800-VGA

Size Document Number Rev

Custom

4

3

2

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

1

11 32Thursday, July 28, 2005

Page 12

8

7

6

5

4

3

2

1

SMBDATA_ISO[16,18,27]

SMBCLK_ISO[16,18,27]

D D

C C

B B

R42

1KR1%

R41

1KR1%

A A

VCC_DDR

MVREF_DIM

8

MAA[0:13][9,13]

MDCLKA3[16]

MDCLKA#3[16]

MDCLKA4[16]

MDCLKA#4[16]

MDCLKA5[16]

MDCLKA#5[16]

C26

C1000P50X

BA1[9,13]

-CS2[9,13]

-CS3[9,13]

-SWEA[9,13]

-SCASA[9,13]

-SRASA[9,13]

CKEA2[9,13]

CKEA3[9,13]

VCC_DDR

C27

C1000P50X

VCC_DDR

-CS2

-CS3

MDCLKA3

MDCLKA#3

MDCLKA4

MDCLKA#4

MDCLKA5

MDCLKA#5

SMBDATA_ISO

SMBCLK_ISO

MAA0

48

A0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0

BA1

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

-SWEA

-SCASA

-SRASA

CKEA2

CKEA3

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

SMBDATA_ISO

SMBCLK_ISO

MVREF_DIM

VCC_DDR VCC_DDR VCC_DDR

VDDQ15VDDQ22VDDQ30VDDQ54VDDQ62VDDQ77VDDQ96VDDQ

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10

118

A11

115

A12

167

A13

59

BA0

52

BA1

113

BA2

157

CS0

158

CS1

71

NC/CS2

163

NC/CS3

97

DQM0

107

DQM1

119

DQM2

129

DQM3

149

DQM4

159

DQM5

169

DQM6

177

DQM7

140

DQM8

63

WE

65

CAS

154

RAS

21

CKE0

111

CKE1

16

CK0/DNU

17

CK0/DNU

137

CK1

138

CK1

76

CK2/DNU

75

CK2/DNU

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

91

SDA

92

SCL

181

SA0

182

SA1

183

SA2

1

VREF

82

VDDID

184

VDDSPD

9

NC

10

NC/RESET

101

NC

102

NC

173

NC

103

NC/FETEN

CB26 C1U16Y

CB60 C68P50N

C0.1U25YCB42

CB32 C1000P50X

CB18 C47P50N

C0.1U25YCB12

C0.01U50XC90

7

VCC_DDR

104

112

128

136

143

156

164

172

180

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND3GND11GND18GND26GND34GND42GND50GND58GND66GND74GND81GND89GND93GND

100

108

VDD7VDD38VDD46VDD70VDD85VDD

GND

GND

GND

GND

GND

GND

116

124

132

139

145

152

C0.1U25YCB53

C0.1U25YCB21

C0.1U25YCB22CB69 X_C1000P50X

C0.1U25YCB31

C0.1U25YCB49

C0.1U25YCB5

C1U16YCB65

C0.1U25YCB52

C0.1U25YCB72

C0.1U25YCB68 C0.1U25YCB13

C1U16YCB44

X_C0.1U25YCB59

6

120

148

168

VDD

VDD

VDD

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

WP

GND

GND

DIMM-184_green

160

176

DIMM2

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

VCC_DDR

2

4

6

8

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

44

45

49

51

134

135

142

144

90

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DDR_WP

R139 4.7KR

C0.1U25YCB45

CB14 C68P50N

C100P50NCB38

C0.1U25YCB27

C1U16YCB17

VCC_DDR

104

112

128

136

143

156

164

172

VDDQ

VDDQ

180

VDDQ

VDD7VDD38VDD46VDD70VDD85VDD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

GND

GND

GND

100

116

124

132

Title

Size Document Number Rev

Custom

Date: Sheet of

MAA[0:13][9,13]

BA0[9,13]

BA1[9,13]BA0[9,13]

-CS0[9,13]

-CS1[9,13]

-DQM[0:7][9,13]

-SWEA[9,13]

-SCASA[9,13]

-SRASA[9,13]

CKEA0[9,13]

CKEA1[9,13]

MDCLKA0[16]

MDCLKA#0[16]

MDCLKA1[16]

MDCLKA#1[16]

MDCLKA2[16]

MDCLKA#2[16]

-DQS[0:7][9,13]

VCC_DDR

VCC_DDR

VCC_DDR

close to the middle of DIMM 1

CB10 C1000P50X

CB33 C1000P50X

X_C0.1U25YCB9

X_C0.1U25YCB6

X_C0.1U25YCB1

5

4

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0

BA1

-CS0

-CS1

-DQM0

-DQM1

-DQM2

-DQM3

-DQM4

-DQM5

-DQM6

-DQM7

-SWEA

-SCASA

-SRASA

CKEA0

CKEA1

-DQS0

-DQS1

-DQS2

-DQS3

-DQS4

-DQS5

-DQS6

-DQS7

SMBDATA_ISO

SMBCLK_ISO

MVREF_DIM

48

A0

VDDQ15VDDQ22VDDQ30VDDQ54VDDQ62VDDQ77VDDQ96VDDQ

43

A1

41

A2

130

A3

37

A4

32

A5

125

A6

29

A7

122

A8

27

A9

141

A10

118

A11

115

A12

167

A13

59

BA0

52

BA1

113

BA2

157

CS0

158

CS1

71

NC/CS2

163

NC/CS3

97

DQM0

107

DQM1

119

DQM2

129

DQM3

149

DQM4

159

DQM5

169

DQM6

177

DQM7

140

DQM8

63

WE

65

CAS

154

RAS

21

CKE0

111

CKE1

16

CK0/DNU

17

CK0/DNU

137

CK1

138

CK1

76

CK2/DNU

75

CK2/DNU

5

DQS0

14

DQS1

25

DQS2

36

DQS3

56

DQS4

67

DQS5

78

DQS6

86

DQS7

47

DQS8

91

SDA

92

SCL

181

SA0

182

SA1

183

SA2

1

VREF

82

VDDID

184

VDDSPD

9

NC

10

NC/RESET

101

NC

102

NC

173

NC

103

NC/FETEN

EMI

VCC_DDR

CB2 C68P50N

3

GND3GND11GND18GND26GND34GND42GND50GND58GND66GND74GND81GND89GND93GND

DIMM1

108

120

148

168

VDD

VDD

VDD

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

WP

GND

GND

GND

GND

GND

DIMM-184_green

139

145

152

160

176

MD0

2

MD1

4

MD2

6

MD3

8

MD4

94

MD5

95

MD6

98

MD7

99

MD8

12

MD9

13

MD10

19

MD11

20

MD12

105

MD13

106

MD14

109

MD15

110

MD16

23

MD17

24

MD18

28

MD19

31

MD20

114

MD21

117

MD22

121

MD23

123

MD24

33

MD25

35

MD26

39

MD27

40

MD28

126

MD29

127

MD30

131

MD31

133

MD32

53

MD33

55

MD34

57

MD35

60

MD36

146

MD37

147

MD38

150

MD39

151

MD40

61

MD41

64

MD42

68

MD43

69

MD44

153

MD45

155

MD46

161

MD47

162

MD48

72

MD49

73

MD50

79

MD51

80

MD52

165

MD53

166

MD54

170

MD55

171

MD56

83

MD57

84

MD58

87

MD59

88

MD60

174

MD61

175

MD62

178

MD63

179

44

45

49

51

134

135

142

144

DDR_WP

90

MICRO-START INT'L CO.,LTD.

DIMM1&2

MS-7211 0A

2

MD[0:63] [9,13]

12 32Thursda y, July 28, 2005

1

Page 13

A

B

C

D

E

DIMM1 & 2 Terminations

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

VTT_DDRVTT_DDR

RN36

8P4R-47R0402

RN42

8P4R-47R0402

RN39

8P4R-47R0402

RN43

8P4R-47R0402

RN44

8P4R-47R0402

RN45

8P4R-47R0402

RN34

8P4R-47R0402

RN26

8P4R-47R0402

RN22

8P4R-47R0402

RN21

8P4R-47R0402

RN30

8P4R-47R0402

RN28

8P4R-47R0402

RN35

8P4R-47R0402

4 4

3 3

2 2

MAA[0:13][9,12]

MD[0:63][9,12]

-DQS[0:7][9,12]

-DQM[0:7][9,12]

MAA[0:13]

MD[0:63]

-DQS[0:7]

-DQM[0:7]

MD0

1 2

MD4

3 4

MD5

5 6

MD1

7 8

-DQS0

1 2

-DQM0

3 4

MD2

5 6

MD6

7 8

MD7

1 2

MD3

3 4

MD8

5 6

MD12

7 8

MD9

1 2

MD13

3 4

-DQS1

5 6

-DQM1

7 8

MD14

1 2

MD15

3 4

MD10

5 6

MD11

7 8

CKEA1

CKEA1[9,12]

CKEA3[9,12]

CKEA2[9,12]

CKEA0[9,12]

CKEA3

CKEA2

CKEA0

MD17

MAA12

MAA11

MAA9

MAA7

-DQS2

-DQM2

MD22

MD18

MD25

MD29

-DQS3

-DQM3

MD42

MD46

MD43

MD47

-DQS4

MD34

-DQM4

MD38

MD39

MD35

MD40

MD44

MD20

MD16

MD21

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN2

8P4R-47R0402

RN5

8P4R-47R0402

RN7

8P4R-47R0402

RN10

8P4R-47R0402

RN14

8P4R-47R0402

RN15

8P4R-47R0402

RN16

8P4R-47R0402

RN17

8P4R-47R0402

RN18

8P4R-47R0402

RN24

8P4R-47R0402

RN37

8P4R-47R0402

RN32

8P4R-47R0402

RN33

8P4R-47R0402

-SRASA[9,12]

-SWEA[9,12]

-SCASA[9,12]

BA1[9,12]

BA0[9,12]

-CS0[9,12]

-CS2[9,12]

-CS1[9,12]

-CS3[9,12]

-SRASA

-SWEA

-SCASA

MD41

MD45

-DQS5

-DQM5

-DQM6

-DQS6

MD54

MD50

MD48

MD49

MD53

MD55

MD51

MD60

MD56

MD61

MD57

-DQM7

-DQS7

MD62

MD58

MD63

MD59

MAA13

MD32

MD36

MD33

MD37

MAA10

BA1

BA0

-CS0

-CS2

-CS1

-CS3

MD52

MAA3

MAA2

MAA1

MAA0

MAA5

MAA8

MAA6

MAA4

MD19

MD23

MD24

MD28

MD30

1 2

MD26

3 4

MD27

5 6

MD31

7 8

VTT_DDR VTT_DDR

1 1

C1U16YCB57

C1U16YCB50

C1U16YCB3

C1U16YCB19

C1U16YCB43

C1U16YCB34

C1U16YCB23

CB11 C68P50N

C1U16YCB28

A

C1U16YCB61

C1U16YCB70

C1U16YCB15

X_C1U16YCB24

X_C1U16YCB30

CB51 C1000P50X

X_C1U16YCB71

X_C1U16YCB62

X_C1U16YCB39

B

C

RN25

8P4R-47R0402

Title

DIMM1&2 Terminations

Size Document Number Rev

Custom

D

Date: Sheet of

MICRO-START INT'L CO.,LTD.

MS-7211 0A

E

13 32Thursda y, July 28, 2005

Page 14

A

B

C

D

E

+12V

+3.3V ==> 6A

+1.5VAGP ==>1A

+5V===>2A

+12V==>1A

+3.3AUX==>750mA

AGP1

B1

OVRCNT#

B2

+5V

B3

+5V

B4

USB+

B5

GND

B6

INTB#

B7

CLK

B8

REQ

B9

VCC3.3

ST0

ST2

RBF

GND

DBI_LO

SBA0#

VCC3.3

SBA2#

SB_STBF

GND

SBA4#

SBA6#

RESERVED

GND

VCC3_AUX

VCC3.3

AD31

AD29

VCC3.3

AD27

AD25

GND

AD_STBF1

AD23

VDDQ1.5V

AD21

AD19

GND

AD17

C#/BE2

VDDQ1.5V

IRDY

KEY

KEY

KEY

KEY

DEVEL

VDDQ1.5V

PERR

GND

SERR

C#/BE1

VDDQ1.5V

AD14

AD12

GND

AD10

AD8

VDDQ1.5V

AD_STBF0

AD7

GND

AD5

AGP3.0 Ver 0.95

AD3

VDDQ1.5V

AD1

VREF_CG

_SLOT-AGP124_red-2pitch

TYPEDET#

GC_AGP8X_DET

VCC3.3

MB_AGP8X_DET

VCC3.3

SB_STBS

RESERVED

RESERVED

VCC3.3

VCC3.3

AD_STBS1

C#/BE3

VDDQ1.5V

VDDQ1.5V

FRAME

VDDQ1.5V

C#/BE0

VDDQ1.5V

AD_STBS0

VDDQ1.5V

VREF_GC

INTA#

RST#

DBI_HI

SBA1#

SBA3#

SBA5#

SBA7#

AD30

AD28

AD26

AD24

AD22

AD20

AD18

AD16

TRDY

STOP

PME#

AD15

AD13

AD11

VCC3

CB91

C1U16Y

VCC5

+12V

B10

B11

B12

B13

B14

B15

B16

B17

B18

B19

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B50

B51

B52

B53

B54

B55

B56

B57

B58

B59

B60

B61

B62

B63

B64

B65

B66

VCC_AGP

4 4

PIRQ#B[17]

AGPCLK[16]

GREQ[10]

ST0[10]

ST2[10]

RBF[10]

DBIL[10]

SB_STBF[10]

PIRQ#B

GREQ

RBF

DBIL

SBA0

SB_STBF

SBA4

SBA6

VCC3_SB

GD31

3 3

AD_STBF1[10]

GBE2[10]

GIRDY[10]

GDEVSEL[10]

GSERR[10]

GBE1[10]

2 2

AD_STBF0[10]

GD29

GD27

GD25

AD_STBF1

GD23

GD21

GD19

GD17

GBE2

GIRDY

GDEVSEL