1

2

3

4

5

MS-7204

Version 30

Intel (R) Lakeport (GMCH) + ICH7 Chipset

Title

A A

B B

C C

D D

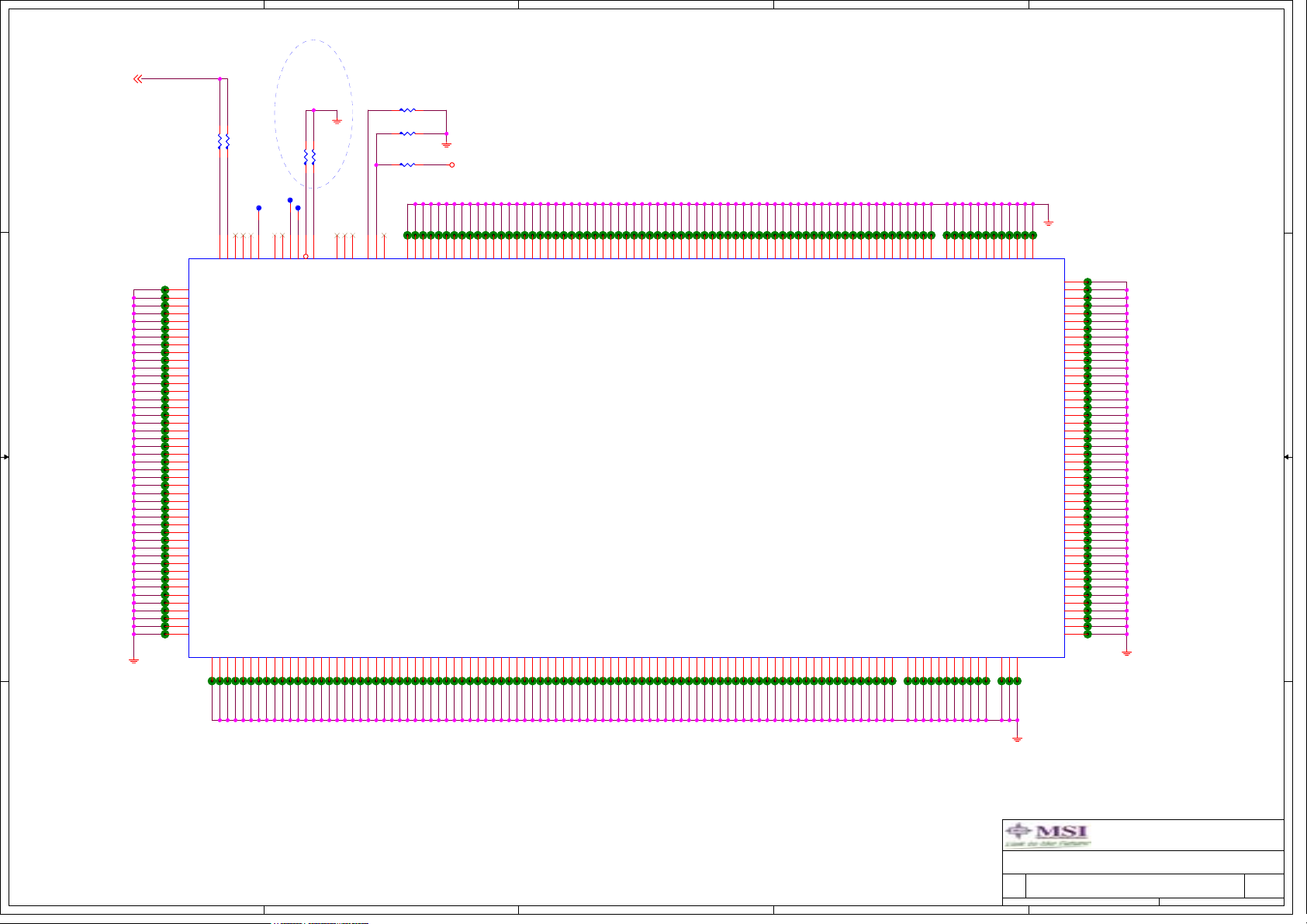

COVER SHEET

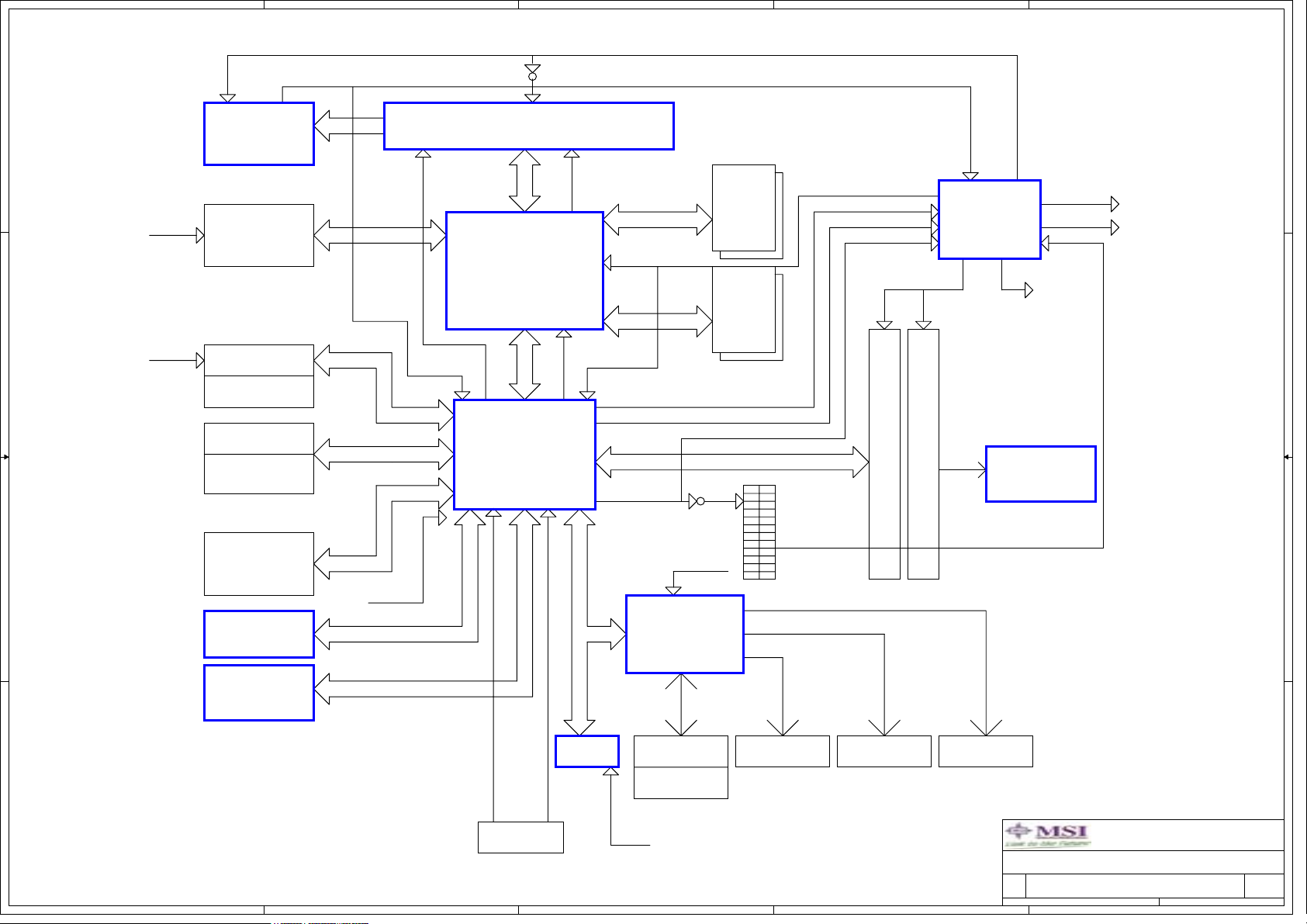

BLOCK DIAGRAM

Intel LGA775

Intel Lakeport

ICH7

ICS954119DF Clock Gen

LPC I/O - W83627DHF

LAN - INTEL 82562GZ/82573

IEEE1394 VT-6308P

Azalia CODEC-ALC888

Audio Jacks 19

USB CONNECTORS

DDR II DIMM 1 & 2 Channel A

DDR II DIMM 3 & 4 Channel B

DDR II VTT Decoupling

BTX ,Front Panel,IDE

MS7 ACPI Controller

Intersil 6312 3Phase

PCI Slot 1,2

Misc

HISTORY

PCIRST & POWER OK MAP 31

POWER MAP 32

History 33

PCI Routing Table

PCI Device

PCI Slot 1

PCI Slot 2

(Add MEDION SPEC)

1394.

LAN (INTERNAL)

1

AD16

AD17

AD20

AD19 4 D

AD24

0

1

3

5FAD21

INTERRUPTIDSEL REQ/GNT

2

Page

1

2

3 , 4 , 5

6 , 7 , 8 , 9

10,11,12

13

14

15FWH/FAN/SATA

16

17

18

20

21

22

23

24

25PCI -Express X16 Slot & X1 Slot

26

27

28

29

30

A

B

E

PCI CLK

PCI_CLK1

PCI_CLK0

PCI_CLK3

PCI_CLK4

1394_PCLK

Intel LGA775 Processor

CPU:

Intel - up to Conroe

System Chipset:

Intel Lakeport (945P)- GMCH (North Bridge)

Intel ICH7/7R/7DH (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM- 4M

Azalia Codec -- RLK- ALC888 7.1+2 channel

LPC Super I/O -- W83627DHF

LAN - INTEL 82562GZ/82573

1394 -- VIA- VT6308P with PHY

CLOCK -- ICS954119DF

Main Memory:

DDR II * 4 (Max 4GB)

Expansion Slots:

PCI EXPRESS X16 SLOT * 1

PCI EXPRESS X1 SLOT * 1

PCI 2.3 SLOT * 2

SATA *4

Intersil PWM:

Controller: HIP6312 3 Phase

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

COVER SHEET 3.0

133Friday, August 04, 2006

5

1

2

3

4

5

VRM_GD

VTT_PWG

A A

PCIRST_SLOT#

B B

C C

HD_RST#

VRM 11

Intersil 6312

3-Phase PWM

PCI

EXPRESS

X16

Connector

IDE Primary

IDE Primary

SERIAL ATA1

SERIAL ATA2

USB2.0

USB Port0~ 7

P.28

P.15

P.19

P.18

P.18

P.18

P.18

P.25

UltraDMA

33/66/100

USB

RSMRST#

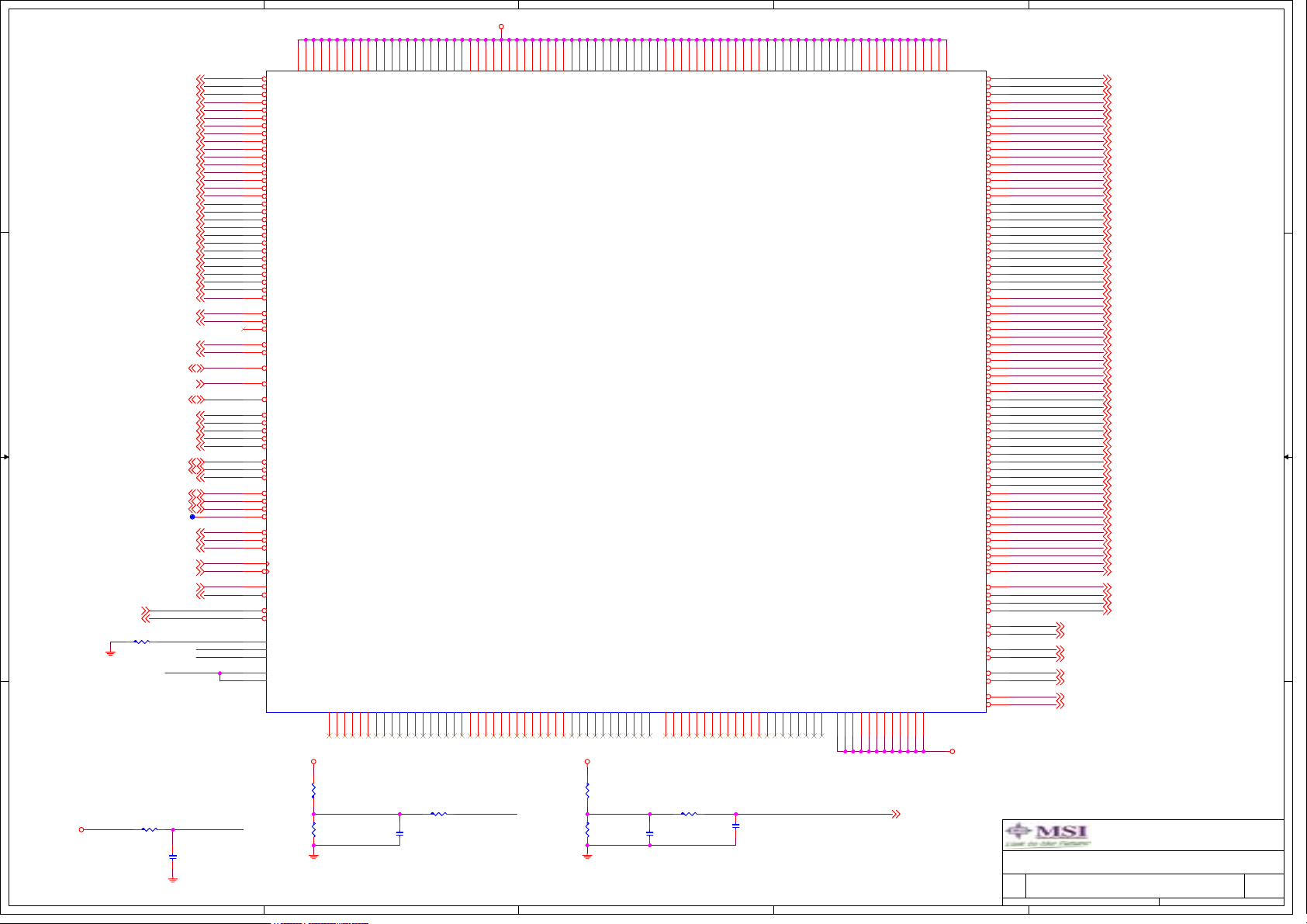

Intel LGA775 Processor

FSB

H_PWRGD

H_CPURST#

Lakeport-945P

P.6~9

DMI

PLRST#

VRM_GD

ICH7

P.10~12

PWR_GD

LPC Bus

P.3~5

CHANNEL A

CHANNEL B

SLP_S4#

SLP_S3#

Block Diagram

PCIRST_ICH7#

PCIRST_BUF#

2 DDR II

DIMM

Modules

P.20

2 DDR II

DIMM

Modules

P.21

PCI

ATX1

PWR_OK

PWR_GD

PCIRST_SLOT#

PCI Slot 1

PCI Slot 2

P.23 P.23

MS7

1394

VIA VT6308P

VID_GD

RSMRST#

HD_RST#

PCIRST_BUF#

P.26

RLK

Azalia Codec

LAN

Intel 82562EZ

D D

P.16

P.17

LAN

FWH

P.30

FP_RST#SW_ON#

JFP1

1

2

LPC SIO

W83627DHF

Keyboard

Mouse

PCIRST_ICH6#

3

P.14

P.14

P.14

Floopy Parallel Serial

P.14 P.18 P.18

4

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

Date: Sheet of

MICRO-START INT'L CO.,LTD.

BLOCK DIAGRAM 3.0

233Friday, August 04, 2006

5

1

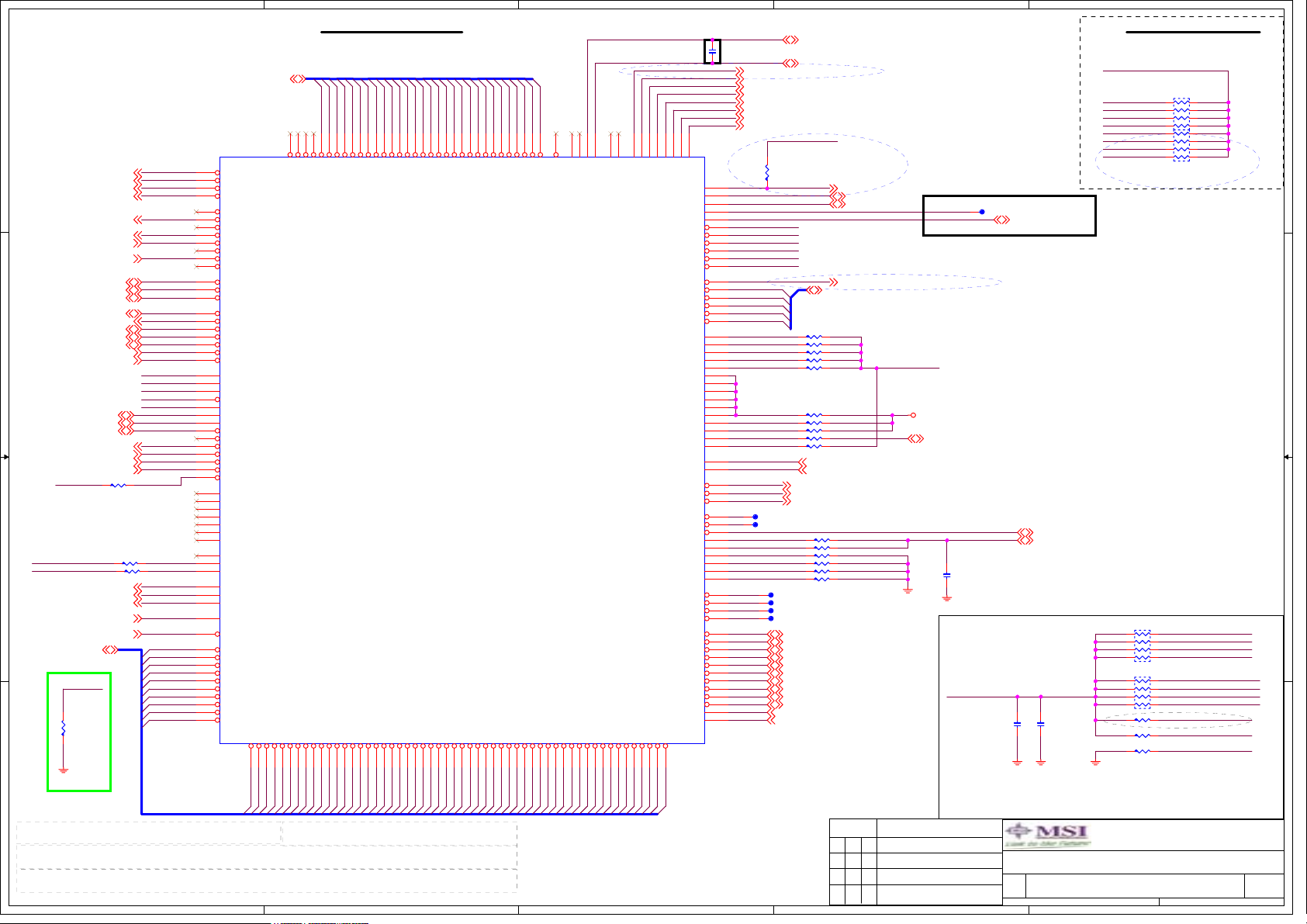

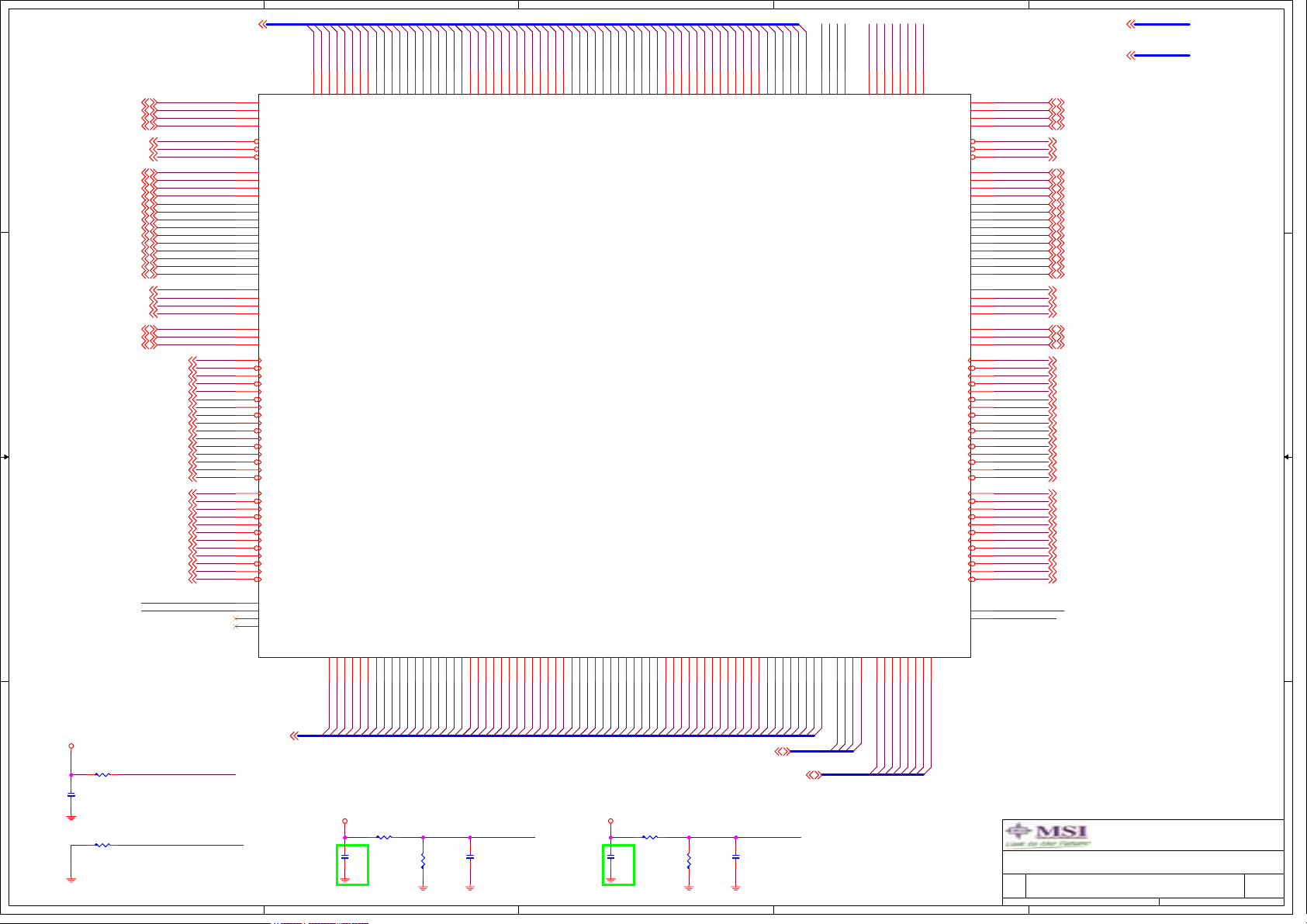

CPU SIGNAL BLOCK

H_A#[3..31]6

H_A#29

H_A#31

H_A#30

AJ5

G22

AH5

A34#

D47#

D22

H_D#46

AH4

A33#

D46#

E22

H_D#45

AG5

A32#

D45#

G21

H_D#44

AG4

A31#

D44#

F21

H_D#43

AG6

A30#

D43#

E21

H_D#42

H_A#28

A29#

D42#

H_D#41

A A

U11A

LL_ID1

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

TESTI_13

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

H_DBI#06

H_DBI#16

H_DBI#26

H_DBI#36

H_IERR#4

H_FERR#4,10

H_STPCLK#10

H_INIT#10

H_DBSY#6

H_DRDY#6

H_TRDY#6

H_ADS#6

H_LOCK#6

H_BNR#6

H_HIT#6

B B

C C

D D

H_HITM#6

H_BPRI#6

H_DEFER#6

H_THERMDA14

H_THERMDC14

TRMTRIP#4,10

H_PROCHOT#4

H_IGNNE#10

ICH_H_SMI#10

H_A20M#10

VTT_OUT_LEFT

VTT_OUT_RIGHT

VTT_OUT_RIGHT

H_FSBSEL04,8,13

H_FSBSEL14,8,13

H_FSBSEL24,8,13

H_PWRGD4,10

H_CPURST#4,6

H_D#[0..63]6

LL_ID1

R305

X_0R0402

R284

H_TESTHI13

62R0402

R291

X_62R0402

R303 62R0402

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

H_D#63

H_D#62

H_D#61

H_D#60

H_D#59

H_D#58

H_D#57

H_D#56

H_D#55

H_D#54

AJ6

A35#

D53#

D52#

D51#

D50#

D49#

D48#

B15

A14

C14

C15

D17

D20

H_D#49

H_D#47

H_D#50

H_D#52

H_D#53

H_D#51

H_D#48

AF4

F20

H_A#27

AF5

A28#

D41#

E19

H_D#40

H_A#26

AB4

A27#

D40#

E18

H_D#39

H_A#25

AC5

A26#

D39#

F18

H_D#38

H_A#24

AB5

A25#

D38#

F17

H_D#37

H_A#23

AA5

A24#

D37#

G17

H_D#36

2

H_A#22

AD6

A23#

D36#

G18

H_D#35

H_A#21

AA4

A22#

D35#

E16

H_D#34

H_A#20

H_A#19

A21#

A20#Y4A19#Y6A18#W6A17#

D34#

D33#

E15

G16

H_D#32

H_D#33

H_A#18

D32#

G15

H_D#31

H_A#17

AB6

D31#

F15

H_D#30

H_A#16

D30#

G14

H_D#29

H_A#10

H_A#15

H_A#11

H_A#12

H_A#13

H_A#14

U6

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

D24#

F14

F12

F11

E13

D13

G13

H_D#26

H_D#28

H_D#25

H_D#27

H_D#23

H_D#24

H_A#8

H_A#6

H_A#7

H_A#9

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D23#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

D10

H_D#22

H_D#20

H_D#21

H_D#19

3

VCC_VRM_SENSE

VSS_VRM_SENSE

H_A#5

H_A#3

H_A#4

AN6

L5

H_D#17

H_D#18

H_D#16

AN5

AN4

AC2

AN3

DBR#

VSS_SENSE

VCC_SENSE

VCC_MB_REGULATION

D14#

D13#

D12#D8D11#

D10#

B12

B10

D11

H_D#15

A11

C12

C11

H_D#9

H_D#10

H_D#12

H_D#11

H_D#14

H_D#13

AM7

AJ3

AK3

RSVD

ITP_CLK1

ITP_CLK0

VSS_MB_REGULATION

D9#

D8#

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

A10

H_D#6

H_D#5

H_D#7

H_D#8

H_D#4

AM5

AL4

VID6#

VID5#

GTLREF_SEL

H_D#1

H_D#2

H_D#3

AK4

VID4#

VID_SELECT

CS_GTLREF

LINT0/INTR

H_D#0

AL6

AM3

VID3#

GTLREF0

GTLREF1

PCREQ#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

FORCEPH

BCLK1#

BCLK0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

_ZIF-SOCK775-15u-in

B4

AL5

AM2

VID2#

VID1#

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

RSVD

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

VID0#

C377

C10U6.3X51206

VID7

VID6

VID5

VID4

VID3

VID2

VID1

VID0

AN7

H1

H2

H29

E24

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

H_TESTHI12

W2

H_TESTHI11

P1

H_TESTHI10

H5

H_TESTHI9

G4

H_TESTHI8

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

VID7 27

VID6 27

VID5 27

VID4 27

VID3 27

VID2 27

VID1 27

VID0 27

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_REQ#4

H_REQ#3

H_REQ#2

H_REQ#1

H_REQ#0

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

H_FORCEPH

RSVD_G6

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

VCC_VRM_SENSE 27

VSS_VRM_SENSE 27

VTT_OUT_RIGHT

R139

1KR0402

GTLREF_SEL

R301 62R0402

R290 62R0402

R281 62R0402

R274 62R0402

R275 62R0402

R183 62R0402

R304 62R0402

R184 62R0402

R321 X_62R0402

R272 X_62R0402

H_RS#2 6

H_RS#1 6

H_RS#0 6

TP18

TP20

R296 60.4R1%0402

R278 60.4R1%0402

R287 60.4R1%0402

R271 60.4R1%0402

R289 60.4R1%0402

R204 60.4R1%0402

TP11

TP8

TP10

TP12

H_ADSTB#1 6

H_ADSTB#0 6

H_DSTBP#3 6

H_DSTBP#2 6

H_DSTBP#1 6

H_DSTBP#0 6

H_DSTBN#3 6

H_DSTBN#2 6

H_DSTBN#1 6

H_DSTBN#0 6

H_NMI 10

H_INTR 10

REV:3.0

REV:3.0

VRD_VIDSEL 27

CPU_GTLREF0 4

CPU_GTLREF1 4

IO_PECI 14

H_REQ#[0..4] 6

CK_H_CPU# 13

CK_H_CPU 13

4

REV:3.0

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT 4,5

TP2

C370

C0.1U16Y0402

VTT_OUT_RIGHT

X_C0.1U16Y0402

VID7

VID3

VID6

VID1

VID2

VID5

VID0

VID4

MCH_GTLREF_CPU 6

H_BR#0 4,6

VTT_OUT_LEFT 4

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

1

3

5

7

1

3

5

7

C378

C371

C0.1U16Y0402

R309 X_62R0402

R315 62R0402

R308 62R0402

PLACE BPM TERMINATION NEAR CPU

5

VID Pull-Up Resistor

VTT_OUT_RIGHT

RN348P4R-680R

1

2

3

4

5

6

7

8

1

2

3

4

5

6

7

8

RN538P4R-680R

REV:3.0

RN33

RN31

2

4

6

8

8P4R-62R0402

2

4

6

8

8P4R-62R0402

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TMS

H_TDI

H_BPM#2

H_BPM#4

H_TDO

H_TRST#

H_TCK

The LL_ID[]1:0] signals are used to select the

correct loading slope for the processor.

ITPCLK[0:1] are copies of BCLK that are used only in processor systems where no debug

port is implemented on the system board.

The signal VID_SELECT(previously known as FC16, land number AN7) on the processor socket

should have a 62 ohm 5% pull-down resistor to ground.

1

LL_ID[]1:0]=00 for the P4 processor in the

775-land package.

2

BSEL

2

1

0

0

0

1 0 200 MHZ (800)

10133 MHZ (533)

0

0

3

TABLE

FSB FREQUENCY0

267 MHZ (1067)

4

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Intel LGA775 - Signals 3.0

333Friday, August 04, 2006

5

1

VCCP

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

U11B

VCCP

AF19

A A

B B

C C

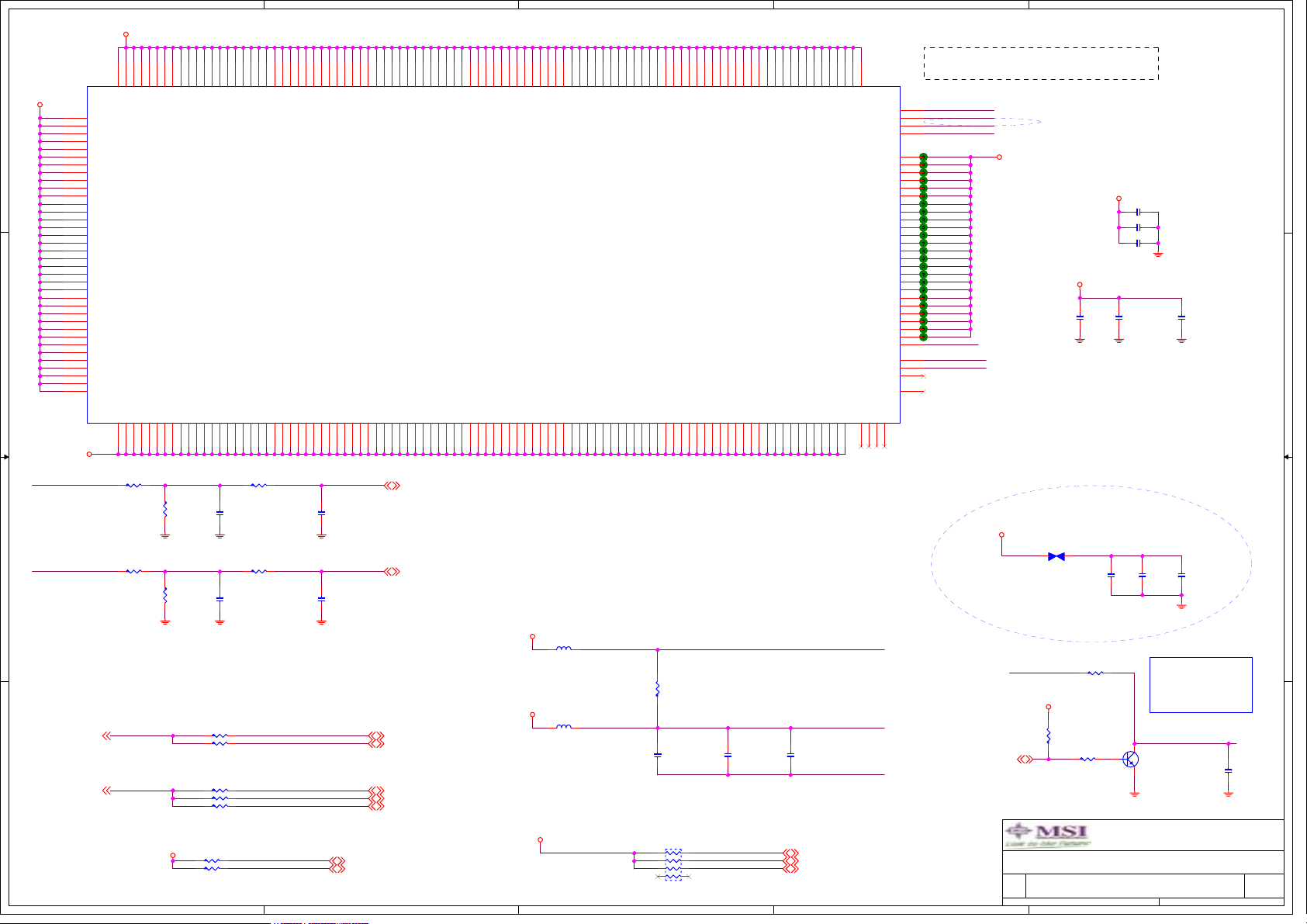

GTLREF VOLTAGE SHOULD BE

0.63*VTT = 0.756V

VTT_OUT_RIGHT3,5

VTT_OUT_LEFT3

D D

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

R279 124R1%0402

R285 124R1%0402

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y27

Y28

Y29

Y30

VTT_OUT_RIGHT

1

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

Y23

Y24

Y25

Y26

W30

R280

210R1%0402

R282

210R1%0402

R316 130R1%0402

R182 62R0402

R286 X_100R0402

R276 62R0402

R306 62R0402

V_FSB_VTT

R283 62R0402

R288 62R0402

W29

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

W26

W27

W28

VCC

VCC

VCC

VCC

W24

W25

C364

C1U6.3Y50402/80-20%

C369

C1U6.3Y50402/80-20%

VCC

VCC

W23

R273

10R0402

R277

10R0402

VCC

VCC

VCC

VCCU8VCCV8VCC

U30

VCC

VCC

VCC

VCC

U28

U29

TRMTRIP#

H_FERR#

VCC

VCC

VCC

VCC

U25

U26

U27

H_PROCHOT#

H_CPURST#

H_PWRGDVTT_OUT_LEFT

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

U23

U24

CPU_GTLREF0VTT_OUT_RIGHT

C362

C220P25N0402

CPU_GTLREF1VTT_OUT_LEFT

C363

C220P25N0402

H_BR#0

H_IERR#

AH27

AH26

AH28

AH29

AH30

AH8

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

T25

T26

T27

T28

T29

T30

H_PROCHOT# 3

H_CPURST# 3,6

H_PWRGD 3,10

H_BR#0 3,6

H_IERR# 3

TRMTRIP# 3,10

H_FERR# 3,10

2

AH9

AJ11

AJ12

AJ14

AJ15

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

VCC

T23

T24

CPU_GTLREF0 3

CPU_GTLREF1 3

2

AJ18

N30

3

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT_OUT_RIGHT

VTT_OUT_LEFT

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

N29

N28

N27

N26

N25

N24

N23

M30

M29

M26

M27

M28

V_FSB_VTT

V_FSB_VTT

V_FSB_VTT

K30

M23

M24

M25

L5

10uH/8/125mA/Rdc=0.7

R189

0R0805

L6 10uH/8/125mA/Rdc=0.7

C231

X_C1U10X

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

RN20

1

2

3

4

5

6

7

8

8P4R-470R0402

3

C229

C22U10X50805

H_FSBSEL1

H_FSBSEL0

H_FSBSEL2

AN8

AN9

AN25

AN26

AN29

AN30

H_VCCIOPLL

H_VCCA

C230

X_C10U10Y0805

H_VSSA

H_FSBSEL1 3,8,13

H_FSBSEL0 3,8,13

H_FSBSEL2 3,8,13

AN22

VCC

VCC

VCCA

VSSA

VCCPLL

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_SEL

RSVD

HS11HS22HS33HS4

4

A23

B23

D23

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

AA1

J1

F27

F29

_ZIF-SOCK775-15u-in

4

100mA

100mA

4

VccPLL for Ssmithfield define the support

future processor.

H_VCCA

H_VSSA

H_VCCPLL

H_VCCIOPLL

REV:3.0

V_FSB_VTT

V_FSB_VTT

C222 C10U10Y0805

C223 C10U10Y0805

C224 C10U10Y0805

CAPS FOR FSB GENERIC

V_FSB_VTT

C220

C0.1U16Y0402

VTT_PWG

VTT_OUT_RIGHT

VTT_OUT_LEFT

V_1P5_CORE

FSB GENERIC DECOUPLING

CP14

1 2

X_COPPER

C416

X_C1U6.3Y50402/80-20%

H_VCCPLL

REV:3.0

VTT_OUT_RIGHT

VID_GD#26,27

Title

Size Document Number Rev

Custom

Date: Sheet

R318 680R0402

VCC5_SB

R320

1KR0402

R322

10KR0402

MICRO-START INT'L CO.,LTD.

MS-7204-30-060804K1

Intel LGA775 - Power 3.0

5

C219

C0.1U16Y0402

C411

C0.01U10X0402

VTT_PWG SPEC :

High > 0.9V

Low < 0.3V

Trise < 150ns

VTT_PWG

Q37

N-MMBT3904_NL_SOT23

X__C1U6.3Y50402/80-20%

5

C221

C0.1U16Y0402

C421

C10U10Y0805

C384

433Friday, August 04, 2006

of

1

2

3

4

5

VTT_OUT_RIGHT3,4

A A

B B

C C

VTT_OUT_RIGHT

R300

60.4R1%0402

U11C

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

AA23

VSS

AA24

VSS

AA25

VSS

AA26

VSS

AA27

VSS

AA28

VSS

AA29

VSS

AA3

VSS

AA30

VSS

AA6

VSS

AA7

VSS

AB1

VSS

AB23

VSS

AB24

VSS

AB25

VSS

AB26

VSS

AB27

VSS

AB28

VSS

AB29

VSS

AB30

VSS

AB7

VSS

AC3

VSS

AC6

VSS

AC7

VSS

AD4

VSS

AD7

VSS

AE10

VSS

AE13

VSS

AE16

VSS

AE17

VSS

AE2

VSS

AE20

VSS

AE24

VSS

AE25

VSS

AE26

VSS

AE27

VSS

AE28

VSS

VSS

AE29

H_COMP7

H_COMP6

AE3

COMP6Y3COMP7

VSS

AE5

AE30

R311

60.4R1%0402

AE4

RSVD

VSS

VSS

AE7

AF10

TP3

D14

RSVDD1RSVD

VSS

VSS

AF13

E23

RSVD

VSS

AF16

R323

62R0402

TP13

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

AF17

AF20

REV:3.0

TP4

F23

VSS

VSS

VSS

AF23

AF24

AF25

F6

IMPSEL#

VSS

AF26

H_COMP8

B13

RSVD

VSS

AF27

AF28

R313

30R0402

VSS

VSS

AF3

AF29

P5

RSVDJ3RSVDN4RSVD

VSS

VSS

VSS

AF6

AF30

R295 62R0402

R299 62R0402

R302 X_62R0402

MSID0

MSID1

AC4

W1

RSVD

MSID[1]V1MSID[0]

VSS

VSS

VSS

VSS

AF7

AG10

AG13

AG16

AG17

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AG20

AG23

AG24

VSS

AH10

AH13

V_FSB_VTT

V30

VSS

VSS

VSS

AH16

AH17

AH20

V29

VSSV3VSS

VSS

VSS

AH23

H28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

VSS

B11

AN1

AN2

AN10

AN13

AN16

AN17

AN20

AN23

AN24

B14

AN27

AN28

H14

VSS

H13

VSS

H12

VSS

H11

VSS

H10

VSS

G1

VSS

F7

VSS

F4

VSS

F22

VSS

F19

VSS

F16

VSS

F13

VSS

F10

VSS

E8

VSS

E29

VSS

E28

VSS

E27

VSS

E26

VSS

E25

VSS

E20

VSS

E2

VSS

E17

VSS

E14

VSS

E11

VSS

D9

VSS

D6

VSS

D5

VSS

D3

VSS

D24

VSS

D21

VSS

D18

VSS

D15

VSS

D12

VSS

C7

VSS

C4

VSS

C24

VSS

C22

VSS

C19

VSS

C16

VSS

C13

VSS

C10

VSS

B8

VSS

B5

VSS

B24

VSS

B20

VSS

B17

VSS

_ZIF-SOCK775-15u-in

VSS

VSS

K2

L25

L24

L23

K5

VSS

VSS

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM16

AM17

AM4

AM20

AM23

AM24

AM27

AM28

V28

V27

V26

V25

V24

V23

VSS

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AJ10

AJ13

AJ16

AH24

AJ17

VSS

R30

R29

R28

R27

R26

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ7

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AK2

AK10

AK13

AK16

AK17

AK20

AK23

AK5

AK7

AL10

AL13

AK24

AK27

AK28

AK29

AL16

AK30

VSS

L30

L29

L28

L27

L26

VSSL3VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AL17

AL20

AL23

AM1

AL24

AL27

AL28

AM10

AM13

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

D D

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

1

2

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Intel LGA775- GND 3.0

533Friday, August 04, 2006

5

1

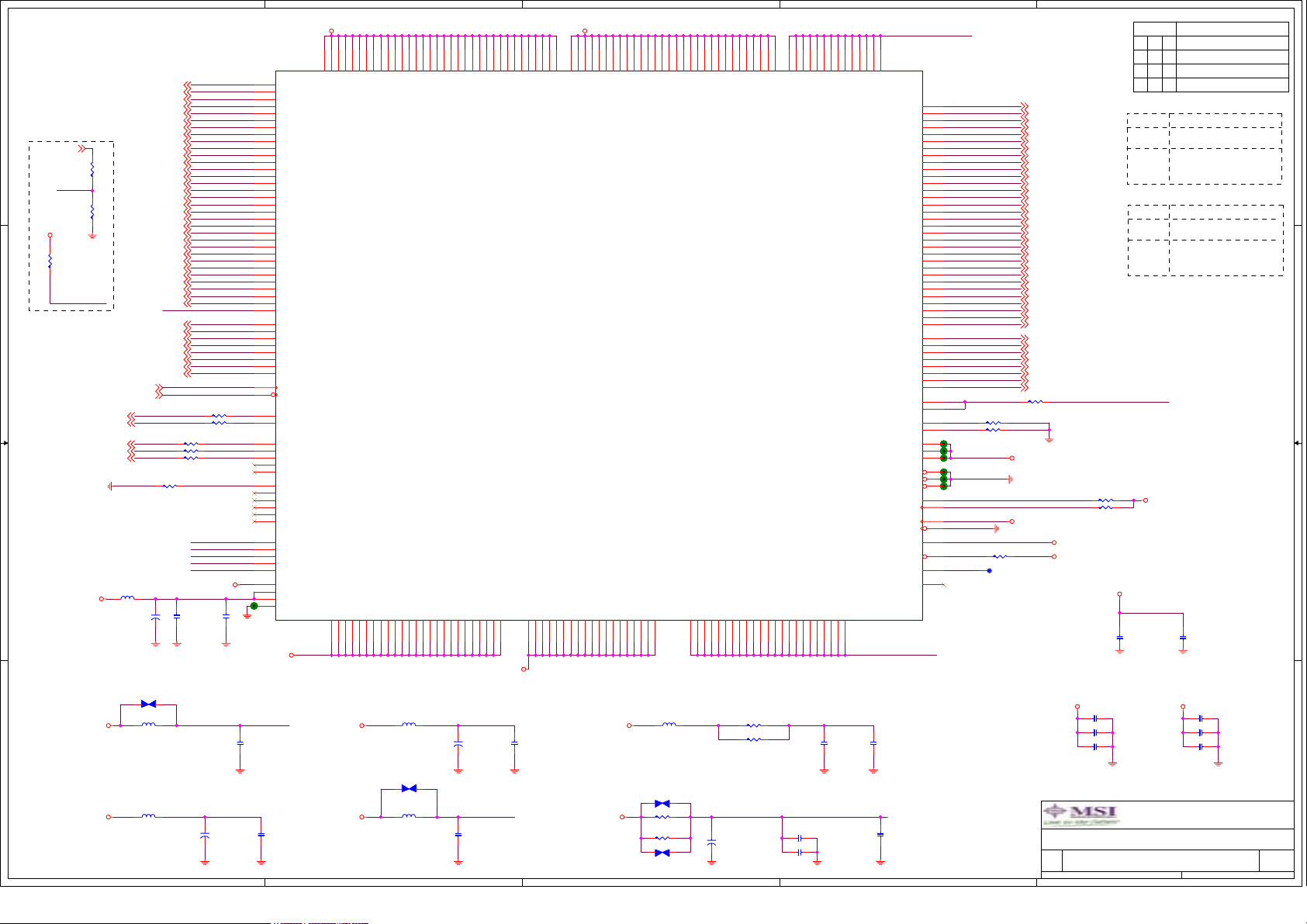

N17

P17

P18

P20

P21

AA22

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

AA35

AA42

V_FSB_VTT V_FSB_VTT

R228

301R1%0402

R232

84.5R1%0402-LF

HSWING VOLTAGE "10mil trace 7mil space"

place divider resistors near VTT.

K38

K35

M34

N35

R33

N32

N34

M38

N42

N37

N38

R32

R36

U37

R35

R38

V33

U34

U32

V42

U35

Y36

Y38

AA37

V32

Y34

M36

V35

AA41

D42

U39

U40

W42

E41

D41

K36

G37

E42

U41

W41

P40

W40

U42

V41

Y40

Y43

M31

M29

C30

AJ12

M18

A28

C27

B27

D27

D28

J39

J42

J37

F38

T40

T43

AJ9

U14A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

HBREQ0#

HBPRI#

HBNR#

HLOCK#

HADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HHIT#

HHITM#

HDEFER#

HTRDY#

HDBSY#

HDRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

HCPURST#

RSTIN#

ICH_SYNC#

HRCOMP

HSCOMP

HSWING

HDVREF

HACCVREF

H_A#3

H_A#33

H_A#4

H_A#43

H_A#5

H_A#53

H_A#6

H_A#63

H_A#7

H_A#73

H_A#8

H_A#83

A A

H_ADSTB#03

H_ADSTB#13

H_HIT#3

H_HITM#3

H_TRDY#3

H_DBSY#3

H_DRDY#3

R248

16.9R1%

60.4R1%0402

H_BR#03,4

H_BPRI#3

H_BNR#3

H_LOCK#3

H_ADS#3

CK_H_MCH13

CK_H_MCH#13

PWR_GD11,26

H_CPURST#3,4

R245

1

H_REQ#03

H_REQ#13

H_REQ#23

H_REQ#33

H_REQ#43

H_RS#03

H_RS#13

H_RS#23

MCH_GTLREF_CPU

B B

C C

PLTRST#10

ICH_SYNC#11

D D

V_FSB_VTT

H_A#93

H_A#103

H_A#113

H_A#123

H_A#133

H_A#143

H_A#153

H_A#163

H_A#173

H_A#183

H_A#193

H_A#203

H_A#213

H_A#223

H_A#233

H_A#243

H_A#253

H_A#263

H_A#273

H_A#283

H_A#293

H_A#303

H_A#313

TP23

ICH_SYNC#

HXRCOMP

HXSCOMP

HXSWING

C316

X_C2.2P25N0402

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

HXSCOMPV_FSB_VTT

2

AB21

AB22

AB23

AC22

AD14

AF6

AF7

AF8

AF9

AF10

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

L15

A43

U27

R27

M15

AA34

AA38

M11

AG25

AG26

HD_SWING S/B 0.22*VTT

C292

C0.01U25X0402

2

AF11

AF12

VCC

RSVRD

AJ24

AG27

R241

62R0402

3

V_1P5_CORE

AF13

AF14

AF30

AG2

AG3

AG4

AG5

AG6

AG7

AG8

AG9

AG10

AG11

AG12

AG13

AG14

AH1

AH2

AH4

AJ5

AJ13

AJ14

AK2

AK3

AK4

AK14

AK15

AK20

R15

R17

R18

R20

R21

R23

R24

U15

U17

U18

U19

U20

U21

U22

U23

U24

U25

U26

V15

V17

V18

V19

V20

V21

V22

V23

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AJ27

AL39

AK40

AW17

Y30

AY14

BC16

AD30

AC34

AW18

HXSWING MCH_GTLREF_CPU

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

Y33

V31

U30

AJ23

AJ26

AL29

AF31

AA30

AD31

AL20

AK21

AC30

R233

124R1%0402

R237

210R1%0402

RSVRD

NC

NC

NC

NC

NC

NC

NC

NC

NC

V30

AJ21

AJ29

AL26

AK27

AG29

GTLREF VOLTAGE SHOULD BE 0.63*VTT=0.756V

124 OHM OVER 210 RESISTORS

3

BC2NCBC1

BC43NCBC42

R244

10R0402

C305

C0.1U16Y0402

BB2NCBB1NCBA2

BB43

E35

C42

AW2

AV27NCAV26

AW26

C315

X_C220P25N0402

CAPS SHOULD BE PLACED NEAR MCH PIN

CAP for GTLREF inputs GMCH use 12mil trace,

isolate W 15mil space.

NCC2NC

B43NCB42NCB41

NCB3NCB2NC

A42

VCC

VCC

Y17

Y18

Y19

V25

V27

VCC

VCC

VCC

VCC

VCC

VCC

Y21

Y23

4

W17

W18

W19

W20

W22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y25

Y27

AA15

AA17

AA18

MCH_GTLREF_CPU 3

4

W24

AA19

W26

VCC

VCC

AA20

W27

Y15

VCC

VCC

VCC

VCC

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

HD_STBN3#

M17

P41

HD0#

M39

HD1#

VCC

P42

HD2#

M42

HD3#

N41

HD4#

M40

HD5#

L40

HD6#

M41

HD7#

K42

HD8#

G39

HD9#

J41

HD10#

G42

HD11#

G40

HD12#

G41

HD13#

F40

HD14#

F43

HD15#

F37

HD16#

E37

HD17#

J35

HD18#

D39

HD19#

C41

HD20#

B39

HD21#

B40

HD22#

H34

HD23#

C37

HD24#

J32

HD25#

B35

HD26#

J34

HD27#

B34

HD28#

F32

HD29#

L32

HD30#

J31

HD31#

H31

HD32#

M33

HD33#

K31

HD34#

M27

HD35#

K29

HD36#

F31

HD37#

H29

HD38#

F29

HD39#

L27

HD40#

M24

HD41#

J26

HD42#

K26

HD43#

G26

HD44#

H24

HD45#

K24

HD46#

F24

HD47#

E31

HD48#

A33

HD49#

E40

HD50#

D37

HD51#

C39

HD52#

D38

HD53#

D33

HD54#

C35

HD55#

D34

HD56#

C34

HD57#

B31

HD58#

C31

HD59#

C32

HD60#

D32

HD61#

B30

HD62#

D30

HD63#

K40

KDINV_0#

A38

HDINV_1#

E29

HDINV_2#

B32

HDINV_3#

K41

L43

F35

G34

J27

M26

E34

B37

(INTEL-QG82945G-A2-LF)

V_1P5_CORE

Title

Size Document Number Rev

Date: Sheet

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DSTBP#0 3

H_DSTBN#0 3

H_DSTBP#1 3

H_DSTBN#1 3

H_DSTBP#2 3

H_DSTBN#2 3

H_DSTBP#3 3

H_DSTBN#3 3

MS-7204-30-060804K1

Custom

Intel lakeport - CPU

5

H_D#0 3

H_D#1 3

H_D#2 3

H_D#3 3

H_D#4 3

H_D#5 3

H_D#6 3

H_D#7 3

H_D#8 3

H_D#9 3

H_D#10 3

H_D#11 3

H_D#12 3

H_D#13 3

H_D#14 3

H_D#15 3

H_D#16 3

H_D#17 3

H_D#18 3

H_D#19 3

H_D#20 3

H_D#21 3

H_D#22 3

H_D#23 3

H_D#24 3

H_D#25 3

H_D#26 3

H_D#27 3

H_D#28 3

H_D#29 3

H_D#30 3

H_D#31 3

H_D#32 3

H_D#33 3

H_D#34 3

H_D#35 3

H_D#36 3

H_D#37 3

H_D#38 3

H_D#39 3

H_D#40 3

H_D#41 3

H_D#42 3

H_D#43 3

H_D#44 3

H_D#45 3

H_D#46 3

H_D#47 3

H_D#48 3

H_D#49 3

H_D#50 3

H_D#51 3H_DEFER#3

H_D#52 3

H_D#53 3

H_D#54 3

H_D#55 3

H_D#56 3

H_D#57 3

H_D#58 3

H_D#59 3

H_D#60 3

H_D#61 3

H_D#62 3

H_D#63 3

H_DBI#0 3

H_DBI#1 3

H_DBI#2 3

H_DBI#3 3

MICRO-START INT'L CO.,LTD.

3.0

of

633Friday, August 04, 2006

5

1

SDQ_A[0..63]21

2

3

4

SDM_A[0:7]21

5

SDM_A[0:7]

SDQ_A0

SDQ_A2

SDQ_A4

SDQ_A9

SDQ_A10

SDQ_A5

SDQ_A1

SDQ_A3

SDQ_A8

SDQ_A7

SDQ_A6

AP3

AP2

AU3

AV4

AN1

U14B

SCS_A#021,23

SCS_A#121,23

A A

B B

C C

SCS_A#221,23

SCS_A#321,23

RAS_A#21,23

CAS_A#21,23

WE_A#21,23

MAA_A021,23

MAA_A121,23

MAA_A221,23

MAA_A321,23

MAA_A421,23

MAA_A521,23

MAA_A621,23

MAA_A721,23

MAA_A821,23

MAA_A921,23

MAA_A1021,23

MAA_A1221,23

MAA_A1321,23

SODT_A021,23

SODT_A121,23

SODT_A221,23

SODT_A321,23

SBS_A021,23

SBS_A121,23

SBS_A221,23

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

SBS_A0

SBS_A1

SBS_A2

SDQS_A021

SDQS_A#021

SDQS_A121

SDQS_A#121

SDQS_A221

SDQS_A#221

SDQS_A321

SDQS_A#321

SDQS_A421

SDQS_A#421

SDQS_A521

SDQS_A#521

SDQS_A621

SDQS_A#621

SDQS_A721

SDQS_A#721

SCLKA021

SCLKA#021

SCLKA121

SCLKA#121

SCLKA221

SCLKA#221

SCLKA321

SCLKA#321

SCLKA421

SCLKA#421

SCLKA521

SCLKA#521

SMPCOMP_N

SMPCOMP_P

RAS_A#

CAS_A#

WE_A#

BB37

SACS0#

BA39

SACS1#

BA35

SACS2#

AY38

SACS3#

BA34

SARAS#

BA37

SACAS#

BB35

SAWE#

BA32

SAMA0

AW32

SAMA1

BB30

SAMA2

BA30

SAMA3

AY30

SAMA4

BA27

SAMA5

BC28

SAMA6

AY27

SAMA7

AY28

SAMA8

BB27

SAMA9

AY33

SAMA10

AW27

SAMA11

BB26

SAMA12

BC38

SAMA13

AW37

SAODT0

AY39

SAODT1

AY37

SAODT2

BB40

SAODT3

BC33

SABA0

AY34

SABA1

BA26

SABA2

AU4

SADQS0

AR2

SADQS0#

BA3

SADQS1

BB4

SADQS1#

AY11

SADQS2

BA10

SADQS2#

AU18

SADQS3

AR18

SADQS3#

AU35

SADQS4

AV35

SADQS4#

AP42

SADQS5

AP40

SADQS5#

AG42

SADQS6

AG41

SADQS6#

AC42

SADQS7

AC41

SADQS7#

BB32

SACLK0

AY32

SACLK0#

AY5

SACLK1

BB5

SACLK1#

AK42

SACLK2

AK41

SACLK2#

BA31

SACLK3

BB31

SACLK3#

AY6

SACLK4

BA5

SACLK4#

AH40

SACLK5

AH43

SACLK5#

AL5

MCH_SRCOMP0

AJ6

MCH_SRCOMP1

AJ8

SMOCDCOMP0

AM3

SMOCDCOMP1

(INTEL-QG82945G-A2-LF)

AP4

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SBDQ0

SBDQ1

SBDQ2

SBDQ3

AL6

AL8

AP8

AP9

SDQ_A12

SDQ_A11

BA7

BB7

AU5

AU2

AW3

AY3

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

AL9

AP6

AV6

AU7

AJ11

AM10

SDQ_A13

AV1

AW4

SADQ12

SADQ13

SBDQ10

SBDQ11

AV12

AM11

SDQ_A14

SDQ_A15

SDQ_A16

BC6

AY7

AW12

SADQ14

SADQ15

SBDQ12

SBDQ13

AR5

AR7

AR12

SDQ_A18

SDQ_A17

AY10

BA12

SADQ16

SADQ17

SADQ18

SBDQ14

SBDQ15

SBDQ16

AR10

AM15

SDQ_A21

SDQ_A19

SDQ_A20

BB12

BA9

BB9

SADQ19

SADQ20

SBDQ17

SBDQ18

AV15

AM13

AM17

SDQ_A22

SDQ_A23

BC11

AY12

SADQ21

SADQ22

SADQ23

SBDQ19

SBDQ20

SBDQ21

AN12

AR13

SDQ_A25

SDQ_A24

SDQ_A26

AM20

AM18

AV20

SADQ24

SADQ25

SBDQ22

SBDQ23

AT15

AP15

AM24

SDQ_A28

SDQ_A27

AM21

AP17

SADQ26

SADQ27

SADQ28

SBDQ24

SBDQ25

SBDQ26

AV24

AM23

SDQ_A29

SDQ_A31

SDQ_A30

AR17

AP20

AT20

SADQ29

SADQ30

SBDQ27

SBDQ28

AP21

AR21

AM26

SDQ_A32

SDQ_A33

AP32

AV34

SADQ31

SADQ32

SADQ33

SBDQ29

SBDQ30

SBDQ31

AT24

AP24

SDQ_A34

SDQ_A36

SDQ_A35

AV38

AU39

AV32

SADQ34

SADQ35

SBDQ32

SBDQ33

AU27

AN29

AR31

SDQ_A37

SDQ_A38

AT32

AR34

SADQ36

SADQ37

SADQ38

SBDQ34

SBDQ35

SBDQ36

AP27

AM31

SDQ_A41

SDQ_A39

SDQ_A40

AU37

AR41

AR42

SADQ39

SADQ40

SBDQ37

SBDQ38

AP31

AR27

AU31

SDQ_A43

SDQ_A42

AN43

AM40

SADQ41

SADQ42

SADQ43

SBDQ39

SBDQ40

SBDQ41

AP35

AP37

SDQ_A44

SDQ_A45

SDQ_A46

AU41

AU42

AP41

SADQ44

SADQ45

SBDQ42

SBDQ43

AL35

AN32

AR35

SDQ_A47

SDQ_A48

AN40

AL41

SADQ46

SADQ47

SADQ48

SBDQ44

SBDQ45

SBDQ46

AU38

AM38

SDQ_A51

SDQ_A49

AL42

AF39

AE40

SADQ49

SADQ50

SBDQ47

SBDQ48

AJ34

AL34

AM34

SDQ_A53

SDQ_A52

AM41

AM42

SADQ51

SADQ52

SADQ53

SBDQ49

SBDQ50

SBDQ51

AF32

AF34

SDQ_A56

SDQ_A55

SDQ_A54

AF41

AF42

AD40

SADQ54

SADQ55

SBDQ52

SBDQ53

AJ32

AL31

AG35

SDQ_A57

SDQ_A58

AD43

AA39

SADQ56

SADQ57

SADQ58

SBDQ54

SBDQ55

SBDQ56

AD32

AC32

SDQ_A59

SDQ_A60

SDQ_A61

AA40

AE42

AE41

SADQ59

SADQ60

SBDQ57

SBDQ58

Y32

AA32

AD34

SDQ_A62

SDQ_A63

AB41

AB42

SADQ61

SADQ62

SADQ63

SBDQ59

SBDQ60

SBDQ61

AF35

AF37

SBDQ62

AC33

SCKE_A1

SCKE_A2

SCKE_A0

BB25

AY25

BC24

SACKE0

SACKE1

SBDQ63

BA14

AC35

SCKE_A3

BA25

SACKE2

SACKE3

SBCKE0

SBCKE1

SBCKE2

AY16

BA13

SDM_A0

SBCKE3

BB13

SDM_A6

SDM_A7

SDM_A3

SDM_A5

SDM_A2

SDM_A4

SDM_A1

AC40

AG40

AP39

AT34

AP18

BB10

AY2

AR3

SBCS0#

SBCS1#

SBCS2#

SADM7

SADM6

SADM5

SADM4

SADM3

SADM2

SADM1

SADM0

SBDM6

SBDM7

AJ39

AR38

AD39

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCLK0

SBCLK0#

SBCLK1

SBCLK1#

SBCLK2

SBCLK2#

SBCLK3

SBCLK3#

SBCLK4

SBCLK4#

SBCLK5

SBCLK5#

SMVREF1

SMVREF0

SBDM0

SBDM1

SBDM2

SBDM3

SBDM4

SBDM5

AW7

AL11

AP13

AP23

AR29

BA40

AW41

BA41

AW40

BA23

AY24

BB23

BB22

BB21

BA21

AY21

BC20

AY19

AY20

BA18

BA19

BB18

BA22

BB17

BA17

AW42

AY42

AV40

AV43

AU40

AW23

AY23

AY17

AM8

AM6

AV7

AR9

AV13

AT13

AU23

AR23

AT29

AV29

AP36

AM35

AG34

AG32

AD36

AD38

AM29

AM27

AV9

AW9

AL38

AL36

AP26

AR26

AU10

AT10

AJ38

AJ36

AM2

AM4

SCS_B#0

SCS_B#1

SCS_B#2

SCS_B#3

RAS_B#

CAS_B#

WE_B#

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

SBS_B0

SBS_B1

SBS_B2

MCH_VREF_B

MCH_VREF_A

SCKE_A[0:3]21,23

SCS_B#0 22,23

SCS_B#1 22,23

SCS_B#2 22,23

SCS_B#3 22,23

RAS_B# 22,23

CAS_B# 22,23

WE_B# 22,23

MAA_B0 22,23

MAA_B1 22,23

MAA_B2 22,23

MAA_B3 22,23

MAA_B4 22,23

MAA_B5 22,23

MAA_B6 22,23

MAA_B7 22,23

MAA_B8 22,23

MAA_B9 22,23

MAA_B10 22,23

MAA_B11 22,23MAA_A1121,23

MAA_B12 22,23

MAA_B13 22,23

SODT_B0 22,23

SODT_B1 22,23

SODT_B2 22,23

SODT_B3 22,23

SBS_B0 22,23

SBS_B1 22,23

SBS_B2 22,23

SDQS_B0 22

SDQS_B#0 22

SDQS_B1 22

SDQS_B#1 22

SDQS_B2 22

SDQS_B#2 22

SDQS_B3 22

SDQS_B#3 22

SDQS_B4 22

SDQS_B#4 22

SDQS_B5 22

SDQS_B#5 22

SDQS_B6 22

SDQS_B#6 22

SDQS_B7 22

SDQS_B#7 22

SCLKB0 22

SCLKB#0 22

SCLKB1 22

SCLKB#1 22

SCLKB2 22

SCLKB#2 22

SCLKB3 22

SCLKB#3 22

SCLKB4 22

SCLKB#4 22

SCLKB5 22

SCLKB#5 22

SCKE_A[0..3]

SDQ_B29

SDQ_B0

SDQ_B3

SDQ_B8

SDQ_B4

SDQ_B7

SDQ_B1

SDQ_B2

VCC_DDR

R252

C323

D D

C0.1U25Y

80.6R1%0402

R250

80.6R1%0402

SMPCOMP_N

1

SDQ_B[0..63]22

VCC_DDR VCC_DDR

SMPCOMP_P

C356

SDQ_B10

SDQ_B5

R253 1KR1%0402

C0.1U10Y

SDQ_B6

SDQ_B9

2

SDQ_B11

SDQ_B13

SDQ_B14

SDQ_B12

SDQ_B15

R255

1KR1%0402

SDQ_B17

SDQ_B20

SDQ_B16

SDQ_B19

SDQ_B18

SDQ_B22

SDQ_B21

PLACE CLOSE TO MCH

C334

C0.1U25Y

SDQ_B28

SDQ_B27

SDQ_B25

SDQ_B24

SDQ_B23

SDQ_B26

MCH_VREF_A MCH_VREF_B

SDQ_B31

SDQ_B32

SDQ_B30

SDQ_B33

SDQ_B36

SDQ_B34

SDQ_B35

SDQ_B37

SDQ_B39

SDQ_B43

SDQ_B42

SDQ_B40

SDQ_B44

SDQ_B41

SDQ_B38

R256 1KR1%0402

C345

C0.1U10Y

3

SDQ_B45

SDQ_B47

SDQ_B49

SDQ_B46

SDQ_B48 SDQ_A50

R258

1KR1%0402

SDQ_B51

SDQ_B50

SCKE_B[0..3]22,23

SDQ_B53

SDQ_B54

SDQ_B52

C335

C0.1U25Y

SDQ_B57

SDQ_B56

SDQ_B55

SDM_B[0..7]22

SDQ_B58

SDQ_B60

SDQ_B59

SDQ_B62

SDQ_B61

SDQ_B63

SCKE_B1

SCKE_B2

SCKE_B0

SCKE_B3

SDM_B7

SDM_B1

SDM_B0

SDM_B3

SDM_B4

SDM_B5

SDM_B2

SDM_B6

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Intel lakeport - Memory 3.0

733Friday, August 04, 2006

5

1

V_1P5_CORE VCC_DDR

AA26

AB17

AB18

U14C

EXPSLR

C264

I = 55mA

C253

.CD220U10EL7

G12

EXPARXP0

F12

EXPARXN0

D11

EXPARXP1

D12

EXPARXN1

J13

EXPARXP2

H13

EXPARXN2

E10

EXPARXP3

F10

EXPARXN3

J9

EXPARXP4

H10

EXPARXN4

F7

EXPARXP5

F9

EXPARXN5

C4

EXPARXP6

D3

EXPARXN6

G6

EXPARXP7

J6

EXPARXN7

K9

EXPARXP8

K8

EXPARXN8

F4

EXPARXP9

G4

EXPARXN9

M6

EXPARXP10

M7

EXPARXN10

K2

EXPARXP11

L1

EXPARXN11

U11

EXPARXP12

U10

EXPARXN12

R8

EXPARXP13

R7

EXPARXN13

P4

EXPARXP14

N3

EXPARXN14

Y10

EXPARXP15

Y11

EXPARXN15

F20

EXP_EN

Y7

DMI RXP0

Y8

DMI RXN0

AA9

DMI RXP1

AA10

DMI RXN1

AA6

DMI RXP2

AA7

DMI RXN2

AC9

DMI RXP3

AC8

DMI RXN3

B14

GCLKP

B16

GCLKN

F15

SDVOCTRLDATA

E15

SDVOCTRLCLK

SEL0

F21

BSEL0

SEL1

H21

BSEL1

SEL2

L20

BSEL2

AK17

RSV_TP[0]

AL17

RSV_TP[1]

K21

EXP_SLR

AK23

RSV_TP[2]

AK18

RSV_TP[3]

L21

RSV_TP[4]

L18

RSV_TP[5]

N21

RSV_TP[6]

C21

VCCAHPLL

B20

VCCAMPLL

C19

VCCADPLLA

B19

VCCADPLLB

B17

VCCA_EXPPLL

D19

VCC2

C18

VCCADAC

B18

VCCADAC

A18

VSSA_DAC

(INTEL-QG82945G-A2-LF)

V_FSB_VTT

I = 60mA

VCCA_MPLL

C285

_C1U6.3Y50402/80-20%

C295

C0.1U16X0402

EXP_A_RXP_025

EXP_A_RXN_025

EXP_A_RXP_125

EXP_A_RXN_125

A A

EXP_EN_HDR25

R111

0R0402

EXP_EN

R214

X_1.1KR1%0402

V_2P5_MCH

R219

X_1.1KR1%0402

EXP_EN

B B

should be

connected

SDVO_CTRL_DATA25

SDVO_CTRL_CLK25

C C

V_2P5_MCH

EXP_A_RXP_225

EXP_A_RXN_225

EXP_A_RXP_325

EXP_A_RXN_325

EXP_A_RXP_425

EXP_A_RXN_425

EXP_A_RXP_525

EXP_A_RXN_525

EXP_A_RXP_625

EXP_A_RXN_625

EXP_A_RXP_725

EXP_A_RXN_725

EXP_A_RXP_825

EXP_A_RXN_825

EXP_A_RXP_925

EXP_A_RXN_925

EXP_A_RXP_1025

EXP_A_RXN_1025

EXP_A_RXP_1125

EXP_A_RXN_1125

EXP_A_RXP_1225

EXP_A_RXN_1225

EXP_A_RXP_1325

EXP_A_RXN_1325

EXP_A_RXP_1425

EXP_A_RXN_1425

EXP_A_RXP_1525

EXP_A_RXN_1525

CK_PE_100M_MCH13

CK_PE_100M_MCH#13

H_FSBSEL03,4,13

H_FSBSEL13,4,13

H_FSBSEL23,4,13

L9 180L1500m_90

CD100U16EL7

DMI_TXP010

DMI_TXN010

DMI_TXP110

DMI_TXN110

DMI_TXP210

DMI_TXN210

DMI_TXP310

DMI_TXN310

SDVO_CTRL_DATA

SDVO_CTRL_CLK

R218 10KR0402

R215 10KR0402

R223 10KR0402

R220 1KR1%0402

V_2P5_DAC_FILTERED

+

12

C255

EXP_EN

R216 X_220R0402

R217 X_220R0402

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

V_2P5_MCH

C260

C0.1U16Y0402

C0.01U16X0402

I = 70mA

CP6

X_COPPER

V_1P5_CORE

D D

V_1P5_CORE V_1P5_CORE

L13

X_600L200m_500-1

L11

10U125m_0805-1

1

+

12

AA24

VCC

VCC

VCC

VTT

VTT

B23

A24

B24

V_1P5_CORE V_1P5_CORE

AB19

VCC

VTT

B25

VCC

VTT

AB20

AB24

VCC

VTT

B26

C23

2

AB25

AB26

AB27

AC15

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

D24

C25

C26

D23

L10

10U125m_0805-1

L14

X_600L200m_500-1

2

AC17

AC18

AC20

VCC

VCC

VCC

VTT

VTT

VTT

E23

E24

D25

CP7

X_COPPER

VCC

VTT

3

AE20

AD23

AD25

AD26

AE17

AE18

AE22

AE24

AE26

AE27

AF15

VCC

VTT

VCC

VCC

AF17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AF21

AF23

AF25

AF26

C294

C0.1U16X0402

VCC

VCC

AF19

AV23

AV21

VCCSM

VCCSM

VCC

VCC

AG18

AV31

VCCSM

VCC

AG19

AG20

AV42

AW13

VCCSM

VCCSM

VCC

VCC

AG21

AG22

AW20

AW15

VCCSM

VCCSM

VCC

VCC

AG23

AG24

VCCSM

VCC

AV18

AY43

VCC

VCCSM

VCC

VCC

VCC

AF27

AF29

AG15

AG17

AW21

AW24

VCCSM

VCC

AJ15

AJ17

AW29

VCCSM

VCCSM

VCC

VCC

AJ18

AW34

AW31

VCCSM

VCC

AJ20

AW35

VCCSM

VCCSM

AY41

BB16

VCCSM

BB20

BB24

VCCSM

VCCSM

VCC_EXP

AE4

AE3

BB28

BB33

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AE2

AD12

BB38

BB42

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD8

AD10

BC13

BC18

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD6

AD5

BC26

BC31

BC22

VCCSM

VCCSM

VCC_EXP

VCC_EXP

AD4

AD2

AD1

BC35

BC40

VCCSM

VCCSM

VCCSM

VCC_EXP

VCC_EXP

VCC_EXP

AC6

AC13

N5

VCC_EXP

VCC_EXP

AC5

AA13

N10

VCC_EXPN9VCC_EXPN7VCC_EXP

VCC_EXP

VCC_EXP

Y13

V13

AA5

N12

N11

VCC_EXP

VCC_EXP

VCC_EXP

VCC_EXPV9VCC_EXP

V10

R13

R11

R10

VCC_EXP

VCC_EXP

VCC_EXPR5VCC_EXP

VCC_EXPV7VCC_EXPV6VCC_EXP

V5

I = 45mA

L12 1U500m_0805

R206 1R1%

R210 1R1%

C263

C10U10Y0805

AD17

AD19

AD21

AC24

AC26

AC27

AD15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

F23

F27

E27

E26

VTT

VTT

VTT

J23

L23

K23

P23

N23

H23

G23

M23

V_1P5_CORE

I = 55mA

VCCA_DPLLA VCCA_GPLL

+

12

C252

.CD220U10EL7

4

V_1P5_PCIEXPRESS

U13

VCC_EXP

VCC_EXPU8VCC_EXPU7VCC_EXPU6VCC_EXP

EXPATXP0

EXPATXN0

EXPATXP1

EXPATXN1

EXPATXP2

EXPATXN2

EXPATXP3

EXPATXN3

EXPATXP4

EXPATXN4

EXPATXP5

EXPATXN5

EXPATXP6

EXPATXN6

EXPATXP7

EXPATXN7

EXPATXP8

EXPATXN8

EXPATXP9

EXPATXN9

EXPATXP10

EXPATXN10

EXPATXP11

EXPATXN11

EXPATXP12

EXPATXN12

EXPATXP13

EXPATXN13

EXPATXP14

EXPATXN14

EXPATXP15

EXPATXN15

DMI TXP0

DMI TXN0

DMI TXP1

DMI TXN1

DMI TXP2

DMI TXN2

DMI TXP3

DMI TXN3

EXP_COMPO

EXP_COMPI

HSYNC

VSYNC

RED

GREEN

BLUE

RED#

GREENB

BLUE#

DDC_DATA

DDC_CLK

DREFCLKINP

DREFCLKINN

IREF

EXTTS#

XORTEST

ALLZTEST

V_1P5_PCIEXPRESS

C262

C1U10X

D14

C13

A13

B12

A11

B10

C10

C9

A9

B7

D7

D6

A6

B5

E2

F1

G2

J1

J3

K4

L4

M4

M2

N1

P2

T1

T4

U4

U2

V1

V3

W4

W2

Y1

AA2

AB1

Y4

AA4

AB3

AC4

AC12

AC11

D17

C17

F17

K17

H18

G17

J17

J18

N18

N20

J15

H15

A20

J20

H20

K18

HSYNC

VSYNC

EXTTS

GPCOMP

R247 24.9R1%

R230 10KR

R222 10KR

V_2P5_MCH

R226 10KR0402

TP21

EXP_A_TXP_0 25

EXP_A_TXN_0 25

EXP_A_TXP_1 25

EXP_A_TXN_1 25

EXP_A_TXP_2 25

EXP_A_TXN_2 25

EXP_A_TXP_3 25

EXP_A_TXN_3 25

EXP_A_TXP_4 25

EXP_A_TXN_4 25

EXP_A_TXP_5 25

EXP_A_TXN_5 25

EXP_A_TXP_6 25

EXP_A_TXN_6 25

EXP_A_TXP_7 25

EXP_A_TXN_7 25

EXP_A_TXP_8 25

EXP_A_TXN_8 25

EXP_A_TXP_9 25

EXP_A_TXN_9 25

EXP_A_TXP_10 25

EXP_A_TXN_10 25

EXP_A_TXP_11 25

EXP_A_TXN_11 25

EXP_A_TXP_12 25

EXP_A_TXN_12 25

EXP_A_TXP_13 25

EXP_A_TXN_13 25

EXP_A_TXP_14 25

EXP_A_TXN_14 25

EXP_A_TXP_15 25

EXP_A_TXN_15 25

DMI_RXP0 10

DMI_RXN0 10

DMI_RXP1 10

DMI_RXN1 10

DMI_RXP2 10

DMI_RXN2 10

DMI_RXP3 10

DMI_RXN3 10

V_1P5_CORE

5

BSEL

0

1

2 FSB FREQUENCY

0

00

1

00

0

0

1

EXP_EN

State Description

LOW

HIGH

EXP_SLR (R46 and Normal high)

State Description

LOW

HIGH

V_1P5_PCIEXPRESS

V_2P5_MCH

C326

C10U10Y0805

V_2P5_MCH

V_2P5_MCH

R221 1KR

R229 1KR

V_1P5_CORE

CAPS for specific core MCH

VCC_DDR VCC_DDR

C407 C10U10Y0805

C379 C10U10Y0805

C375 C0.1U16Y0402

TABLE

267 MHZ (1067)

200 MHZ (800)

133 MHZ (533)

Only SDVO or PCI-e

operating

SDVO and PCI-e

operating

simultaneously

Only SDVO or PCI-e

operating

SDVO and PCI-e

operating

simultaneously

C332

C10U10Y0805

C393 C10U10Y0805

C394 C0.1U16Y0402

C406 C10U10Y0805

MCH MEMORY DECOUPLING

S6 X_COPPER

VCCA_HPLL

C286

C0.1U16X0402

I = 45mA

V_1P5_CORE

12

R211

X_0R0805

R427

X_0R0805

12

S7 X_COPPER

3

+

C254

CD220U10EL7

C266

C261 C10U10Y0805

V_1P5_PCIEXPRESSVCCA_DPLLB

I = 1.5A

C10U10Y0805

C258

C0.1U16Y0402

4

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

Date: Sheet

MICRO-START INT'L CO.,LTD.

Intel Lakeport-PCI EXPRESS

5

3.0

of

833Friday, August 04, 2006

1

AN26

AN24

AN23

AN21

AN20

AN18

AN17

AN15

AN13

AN4

AN2

AM39

AM37

AM36

AM33

AM9

AM7

AM5

AL43

AL37

A16

A22

A26

A31

A35

B11

B13

B21

B22

B28

B33

B38

C12

C14

C22

C40

D10

D16

D20

D21

E12

E13

E17

E18

E20

E21

E32

F13

F18

F26

F34

F42

G10

G13

G15

G18

G20

G21

G24

G27

G29

G31

G32

G35

G38

H12

H17

H26

H27

H32

U14D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C3

VSS

C5

VSS

C7

VSS

VSS

VSS

VSS

VSS

D2

VSS

D5

VSS

VSS

VSS

VSS

VSS

E3

VSS

E4

VSS

E7

VSS

E9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F2

VSS

F6

VSS

VSS

VSS

VSS

VSS

VSS

G3

VSS

G5

VSS

G7

VSS

G9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J2

VSS

J5

VSS

J7

VSS

J10

VSS

VSS

VSS

VSS

VSS

VSS

J12

J21

J24

J43

J38

J29

VSS

VSS

VSS

VSS

VSS

VSSK7VSSK6VSSK5VSSK3VSS

K13

K12

K10

VSS

VSS

VSS

VSS

K20

K15

K39

K37

K34

K32

K27

A A

B B

C C

2

AU17

AU15

AU13

AU12

AU9

AU6

AT31

AT27

AT26

AT23

AT21

AT18

AT17

AT12

AR43

AR39

AR37

AR32

AR24

AR20

AR15

AR6

AR1

AP38

AP34

AP29

AP12

AP10

AP7

AN42

AN31

AN27

AP5

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSL2VSS

L29

L26

L24

L13

L12

VSSM9VSSM8VSSM5VSSM3VSS

L31

L42

M10

VSS

M13

VSS

M20

VSS

M21

VSS

M35

VSS

M37

VSS

VSSN8VSSN6VSS

N2

N13

N15

N24

N26

N27

N29

N31

N33

N36

N39

VSS

VSSP3VSS

N43

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

3

V29

V26

V24

U29

R29

R26

D43

A40

BC9

BB41

BB39

BB34

BB19

BB14

BB11

BB6

BB3

BA42

BA4

AW10

AV37

AV17

AV10

AV2

AU34

AU32

AU29

AU26

AU24

AU21

AU20

VSS

VSS

VSS

VSS

VSS

VSS

VSSD1VSS

VSSA4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSR9VSSR6VSS

VSS

VSS

VSS

VSS

VSS

VSS

P26

P24

P15

P14

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSST2VSS

VSSU3VSSU5VSSU9VSS

VSS

VSS

VSS

VSS

VSS

VSSV2VSSV8VSS

VSS

VSS

P30

P29

P27

R12

R14

R30

R31

R34

R37

R39

T42

U12

U14

U31

U33

U36

U38

V11

V12

V14

V34

VSS

VSS

W21

V36

VSS

VSS

W23

VSS

VSS

V37

W25

V38

VSS

VSS

Y20

VSS

VSS

V39

4

Y29

Y26

Y24

Y22

VSS

VSS

VSS

VSS

VSS

VSSW3VSSY2VSSY5VSSY6VSSY9VSS

V43

5

AE19

AD29

AD27

AD24

AD22

AD20

AD18

AC29

AC25

AC19

AA29

AA27

AA25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Y12

Y14

Y31

Y35

Y37

Y39

VSS

VSS

AF20

AF22

AF24

AY1

BC4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL33

VSS

AL32

VSS

AL27

VSS

AL24

VSS

AL23

VSS

AL21

VSS

AL18

VSS

AL15

VSS

AL13

VSS

AL12

VSS

AL10

VSS

AL7

VSS

AL3

VSS

AL2

VSS

AL1

VSS

AK30

VSS

AK29

VSS

AK26

VSS

AK24

VSS

AJ37

VSS

AJ35

VSS

AJ33

VSS

AJ31

VSS

AJ30

VSS

AJ10

VSS

AJ7

VSS

AH42

VSS

AG39

VSS

AG38

VSS

AG37

VSS

AG36

VSS

AG33

VSS

AG31

VSS

AG30

VSS

AF43

VSS

AF38

VSS

AF36

VSS

AF33

VSS

AF5

VSS

AF3

VSS

AF2

VSS

AF1

VSS

AD42

VSS

AD37

VSS

AD35

VSS

AD33

VSS

AD13

VSS

AD11

VSS

AD9

VSS

AD7

VSS

AC39

VSS

AC38

VSS

AC37

VSS

AC36

VSS

AC31

VSS

AC23

VSS

AC21

VSS

AC14

VSS

AC10

VSS

AC7

VSS

AC3

VSS

AC2

VSS

AB43

VSS

AB2

VSS

AA36

VSS

AA33

VSS

AA31

VSS

AA23

VSS

AA21

VSS

AA14

VSS

AA12

VSS

AA11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

(INTEL-QG82945G-A2-LF)

AA8

L17

AF18

AE21

AE23

AE25

Y42

AA3

D D

Title

MS-7204-30-060804K1

Size Document Number Rev

Custom

1

2

3

4

Date: Sheet of

MICRO-START INT'L CO.,LTD.

Intel lakeport GND 3.0

933Friday, August 04, 2006

5

1

AD017,28

AD117,28

C_BE#017,28

C_BE#117,28

C_BE#217,28

C_BE#317,28

DEVSEL#17,28

FRAME#17,28

IRDY#17,28

TRDY#17,28

STOP#17,28

LOCK#28

SERR#28

PERR#17,28

PCI_PME#28

R193

33R0402-2

PREQ#028

PREQ#128

PREQ#228

PREQ#328

PREQ#417,28

PREQ#528

PGNT#028

PGNT#128

PGNT#328

PGNT#417

PGNT#528

PIRQ#A28

PIRQ#B28

PIRQ#C28

PIRQ#D17,28

PIRQ#E28

PIRQ#F28

PIRQ#G28

PIRQ#H28

IDE_IRQ24

AD217,28

AD317,28

AD417,28

AD517,28

AD617,28

AD717,28

AD817,28

AD917,28

AD1017,28

AD1117,28

AD1217,28

AD1317,28

AD1417,28

AD1517,28

AD1617,28

AD1717,28

AD1817,28

AD1917,28

AD2017,28

AD2117,28

AD2217,28

AD2317,28

AD2417,28

AD2517,28

AD2617,28

AD2717,28

AD2817,28

AD2917,28

AD3017,28

AD3117,28

PAR17,28

SERIRQ

PCIRSTICH#

A A

B B

PCIRST_ICH#25,26

C C

VCC3

R191 X_1KR0402-1

R190 X_1KR0402-1

VCC3_SB

If SPI not be

D D

used, should

be NC

PGNT#4

PGNT#5

7 8

5 6

3 4

1 2

ICH_PCLK13

C246

C10P25N0402

SERIRQ14

RN51

8P4R-10KR0402

GNT5 GNT4

0 1 Flash cycles routed to SPI

1 0 Flash cycles routed to PCI

1 1 Flash cycles routed to LPC

1

PGNT#4

PGNT#5

C18

A16

F18

E16

A18

E17

A17

A15

C14

E14

D14

B12

C13

G15

G13

E12

C11

D11

A11

A10

F11

F10

B15

C12

D12

C15

A12

F16

F14

F15

E10

E11

B10

B19

B18

C16

C17

E13

A13

D16

D17

F13

A14

AH21

AH16

E18

E9

D9

B9

A8

A6

C7

B6

E6

D6

A7

C9

A9

D7

C8

E7

D8

A3

B4

C5

B5

G8

F7

F8

G7

P5

P2

P6

R2

P1

2

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C/BE0#

C/BE1#

C/BE2#

C/BE3#

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

PCICLK

PCIRST#

REQ0#

REQ1#

REQ2#

REQ3#

GPIO22/REQ4#

GPIO1/REQ5#

GNT0#

GNT1#

GNT2#

GNT3#

GPIO48/GNT4#

GPIO17/GNT5#

PIRQA#

PIRQB#

PIRQC#

PIRQD#

GPIO2/PIRQE#

GPIO3/PIRQF#

GPIO4/PIRQG#

GPIO5/PIRQH#

SERIRQ

IDEIRQ

SPI_MOSI

SPI_MISO

SPI_CS#

SPI_CLK

SPI_ARB

VSS_0A4VSS_1

A23

2

VSS_2B1VSS_3B8VSS_4

3

U10A

AH28

A20M#

AG27

CPUSLP#

AG26

FERR#

AG22

IGNNE#

AF22

INIT#

AG21

INIT3_3V#

AF25

INTR

AH24

NMI

AF23

SMI#

AH22

STPCLK#

AG23

RCIN#

AE22

CPULAN PCI EXPRESSDIRECT MEDIA

PCI INTERFACE INTERRUPT

ICH 7

PART 1/3

SPI

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10C2VSS_11C6VSS_12

VSS_13

VSS_14

VSS_15

VSS_16

VSS_17E1VSS_18E2VSS_19E8VSS_20

VSS_21F3VSS_22F4VSS_23F5VSS_24

VSS_25

VSS_26

VSS_27G1VSS_28G2VSS_29G5VSS_30G6VSS_31G9VSS_32

F12

F27

B11

B14

B17

B20

B26

B28

D10

D13

D18

D21

D24

E15

F28

VSS_33

VSS_34

G14

G18

G21

3

A20GATE

THRMTRIP#

GPO49/CPUPWRGD

PLTRST#

PERN_1

PERP_1

PETN_1

PETP_1

PERN_2

PERP_2

PETN_2

PETP_2

PERN_3

PERP_3

PETN_3

PETP_3

PERN_4

PERP_4

PETN_4

PETP_4

PERN_5

PERP_5

PETN_5

PETP_5

PERN_6

PERP_6

PETN_6

PETP_6

DMI_0RXN

DMI_0RXP

DMI_0TXN

DMI_0TXP

DMI_1RXN

DMI_1RXP

DMI_1TXN

DMI_1TXP

DMI_2RXN

DMI_2RXP

DMI_2TXN

DMI_2TXP

DMI_3RXN

DMI_3RXP

DMI_3TXN

DMI_3TXP

DMI_CLKN

DMI_CLKP

DMI_ZCOMP

DMI_IRCOMP

LAN_CLK

LAN_RSTSYNC

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

EE_DIN

EE_DOUT

EE_SHCLK

VSS_35

VSS_36

VSS_37

VSS_38H3VSS_39H4VSS_40

H5

G24

G25

G26

AF26

AG24

C26

F26

F25

E28

E27

H26

H25

G28

G27

K26

K25

J28

J27

M26

M25

L28

L27

P26

P25

N28

N27

T25

T24

R28

R27

V26

V25

U28

U27

Y26

Y25

W28

W27

AB26

AB25

AA28

AA27

AD25