Cover Sheet 1

1

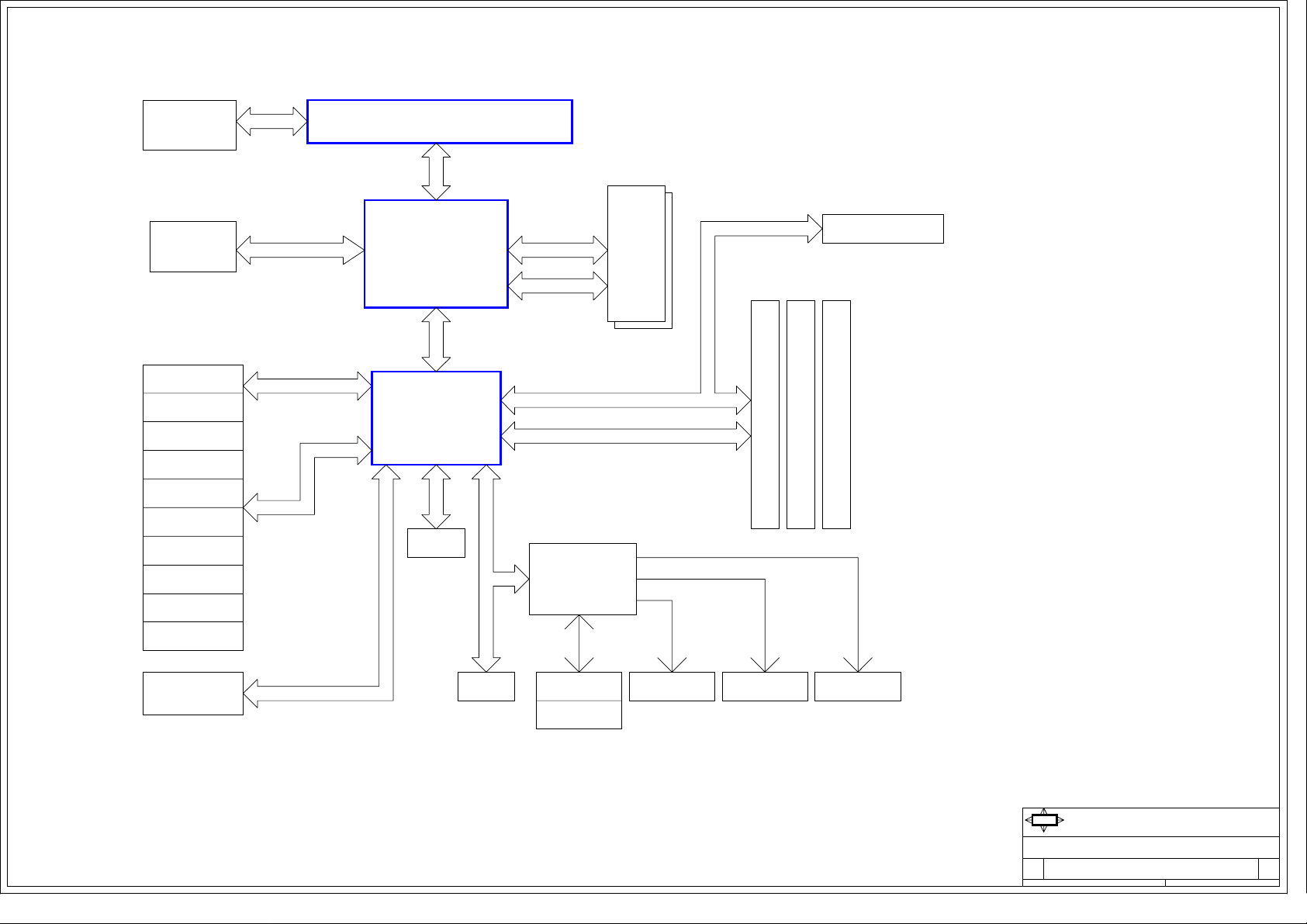

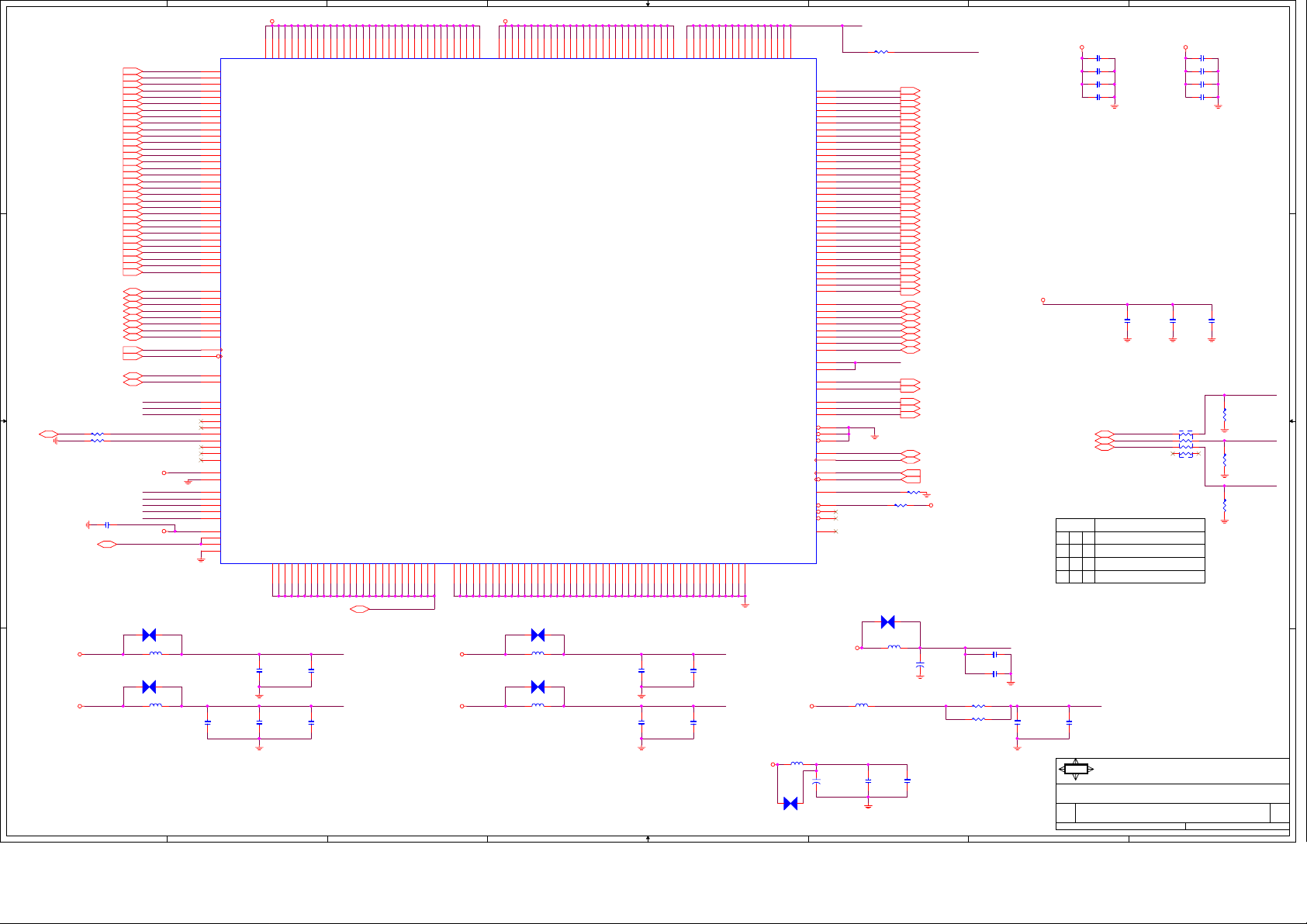

2Block Diagram

GPIO

History

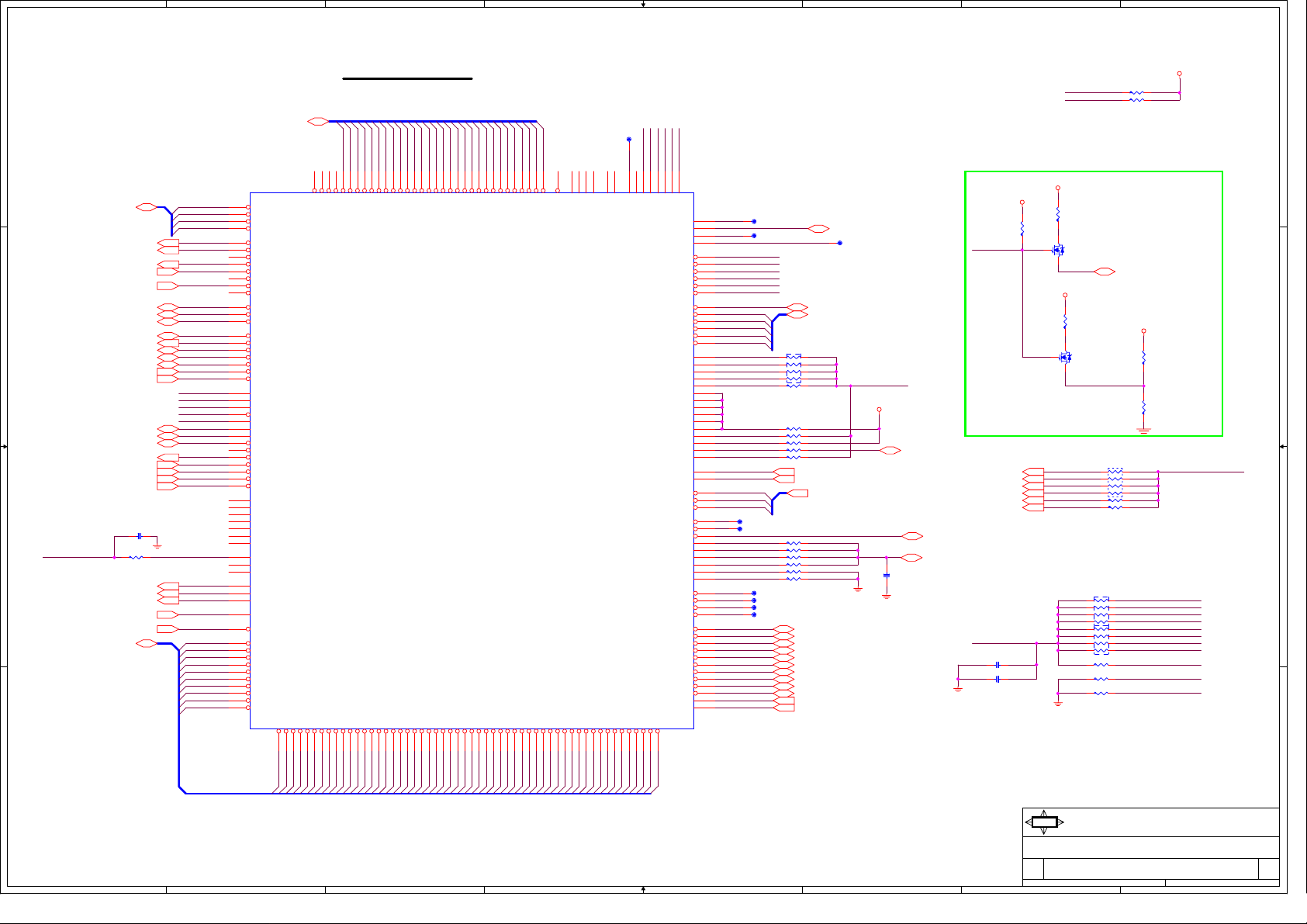

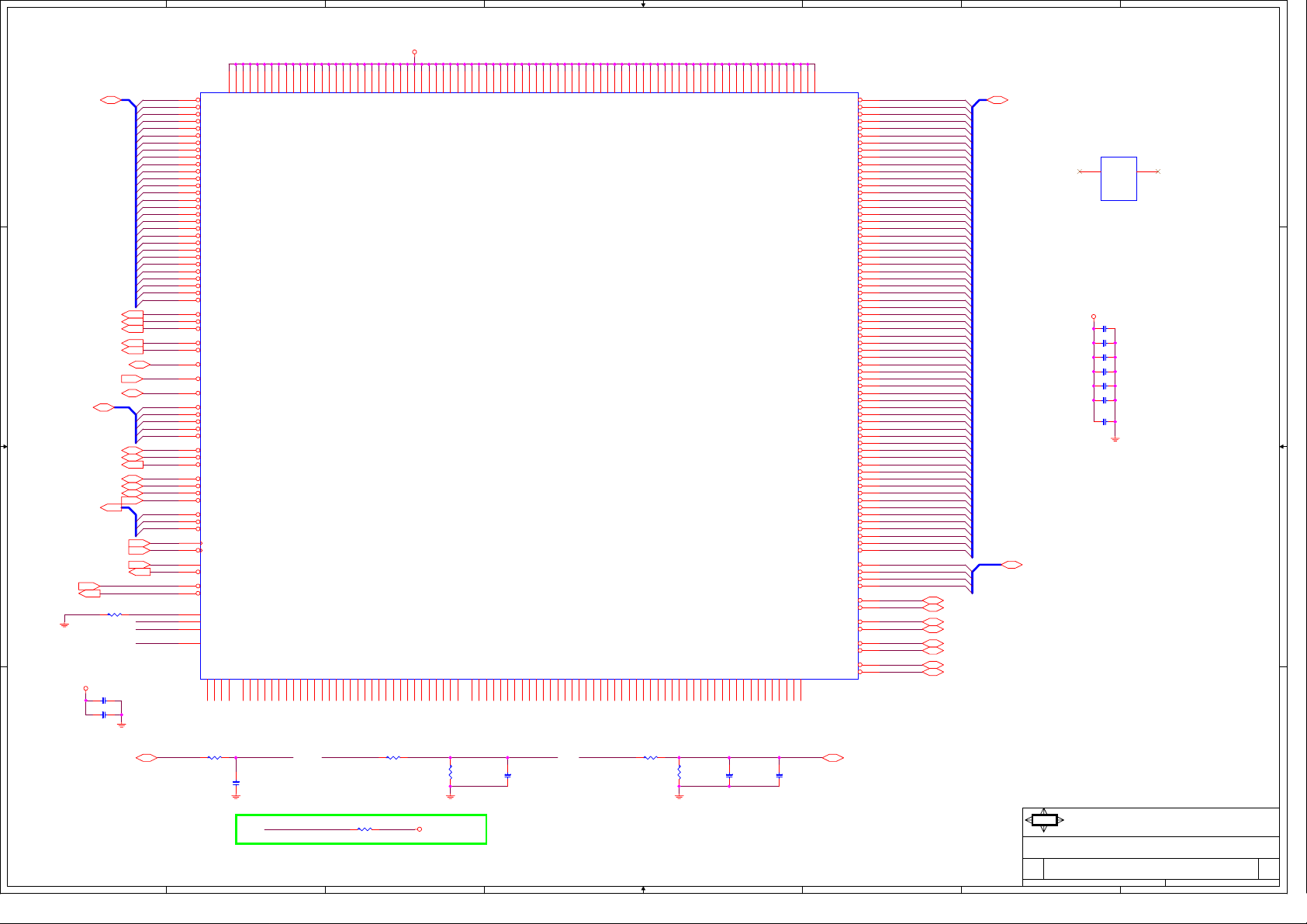

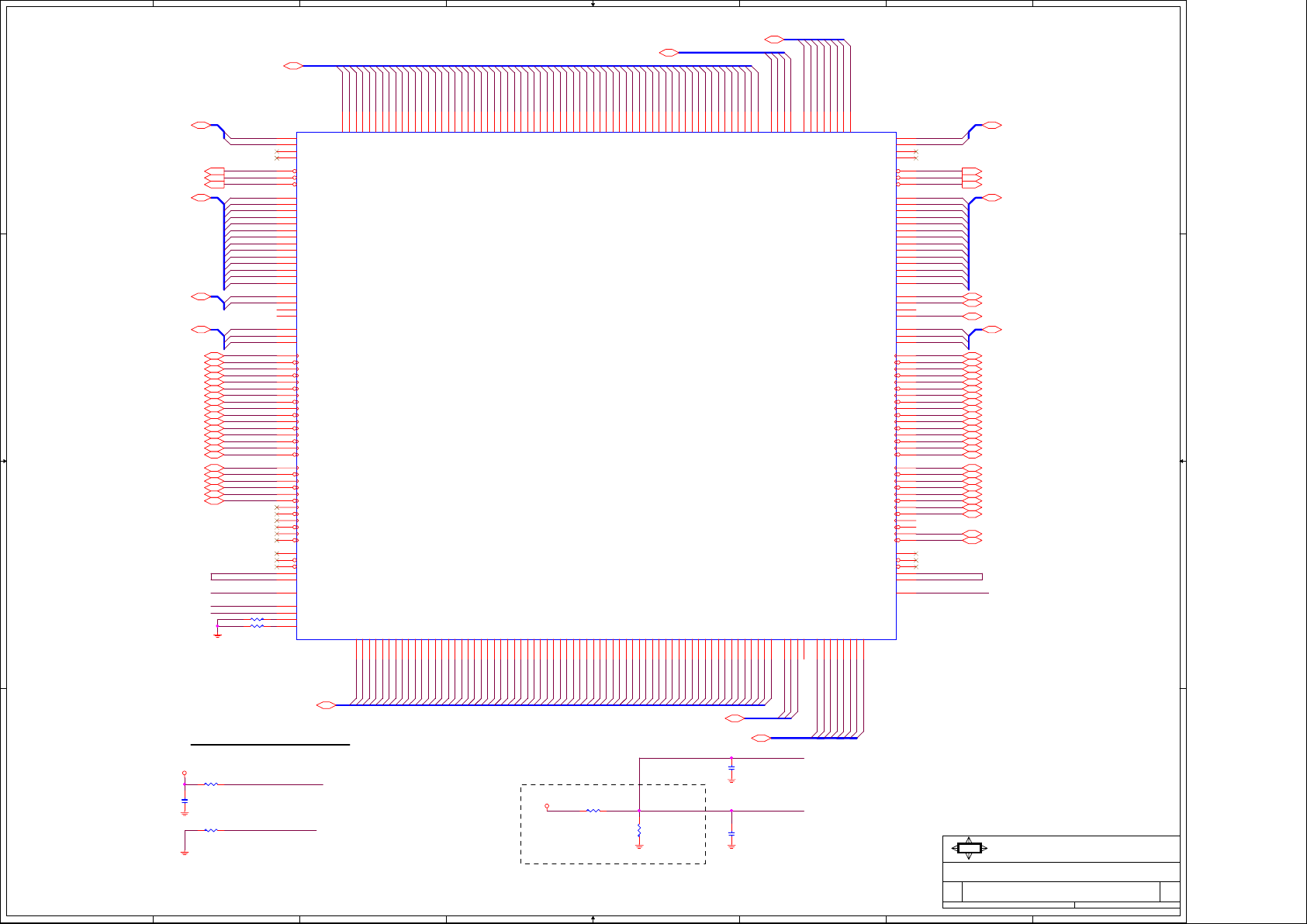

Intel LGA775 CPU

Intel 915P (North Bridge) 8-11

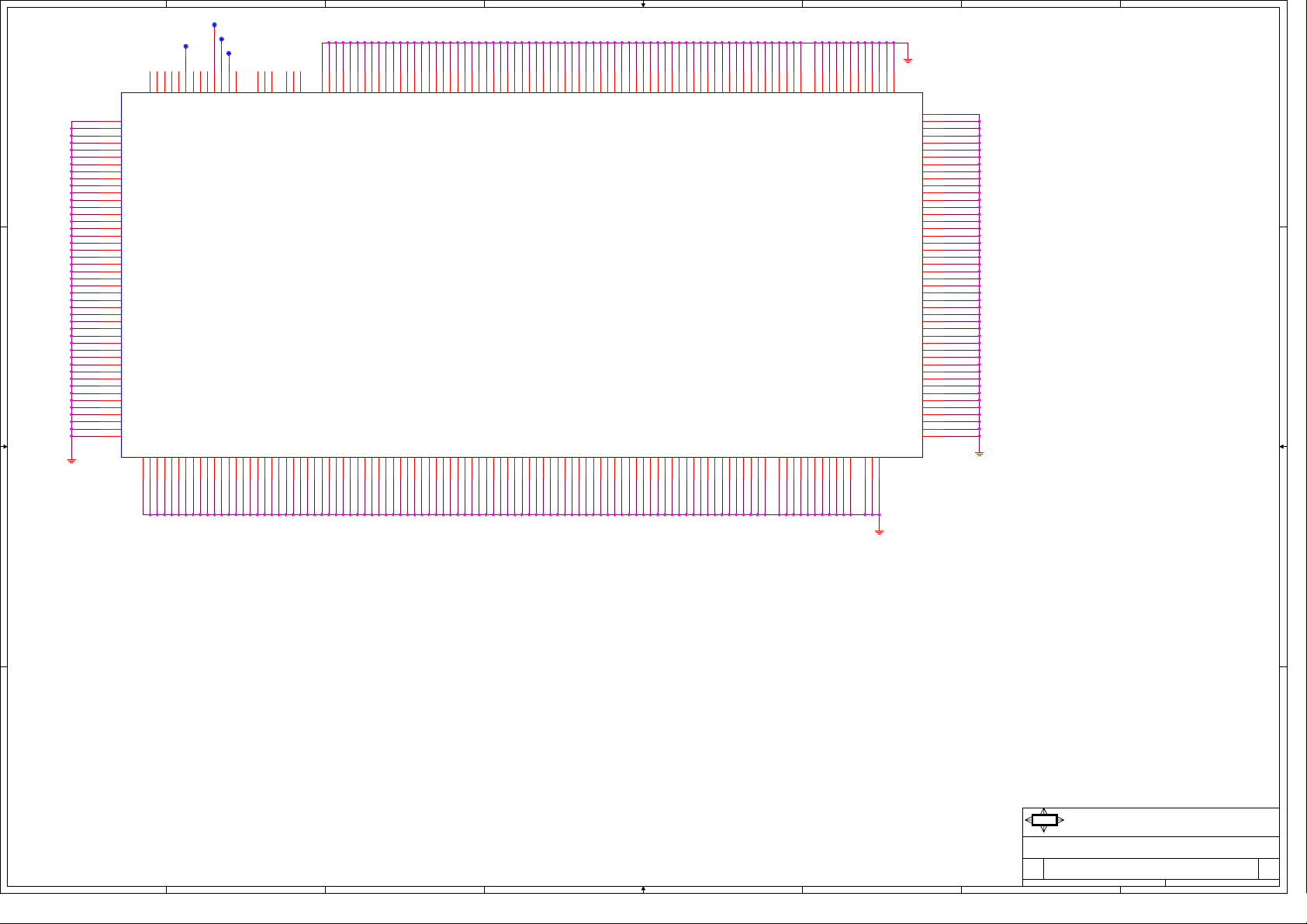

DDR I / II 12-13

DDR I / II Termination

Intel ICH6 (South Bridge)

Clock 954139

LPC I/O -W83627THF

AC97 Audio

PCI-E X16 Slot

AGR & PCI Slot 1 , 2

A A

ATA33/66/100 IDE & FWH

VGA CONNECTOR

USB Connectors

ATX & Front Panel

VRM

BCM4401

LAN Connector

EMI parts

3

4

5-7

14-15

16-18

19

20

21

22

23

24

25

26

27ACPI controller

28

29

30

31

32

MS(7140)

Intel (R) 915P (GMCH) + ICH6 Chipset

Intel LGA775 Processor

CPU:

Intel LGA775

System Chipset:

Intel 915P/G - GMCH (North Bridge)

Intel ICH6 (South Bridge)

On Board Chipset:

BIOS -- FWH EEPROM

AC'97 Codec -- AD1888

LPC Super I/O -- W83627THF

LAN --BCM4401

CLOCK --ICS954139

Main Memory:

DIMM * 4 (DDR*2,DDR2*2)

Expansion Slots:

PCI-E 16X SLOT * 1

PCI-E 1X SLOT * 1

AGR SLOT * 1

PCI SLOT * 2

PWM:

Version 100

Controller:

RT8800B

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

1

Date: Sheet

COVER SHEET

MS-7140

133Thursday, January 20, 2005

100

of

1

RT880B

2-Phase PWM

PCI-E x 16 & DDRII

4X/8X

Connector

IDE Primary

A A

USB Port 0

UltraDMA 33/66/100

Intel LGA775 Processor

FSB

Intel 915P

HUB

Link

ICH6

64bit DDR

Channel 1

64bit DDR

Channel 2

2 DDRI

DIMM

Modules

PCI CNTRL

PCI ADDR/DATA

PCI Slot 1

PCI Slot 2

Block Diagram

Broadcom 4401

AGP Slot

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

USB Port 4

SATA

LPC SIO

USB Port 5

Winbond

83627THF

USB Port 6

USB Port 7

AC'97 Codec

AC'97 Link

Flash

Keyboard

Mouse

Floopy Parallel Serial

1

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

MS-7140

233Thursday, January 20, 2005

of

100

1

ICH5

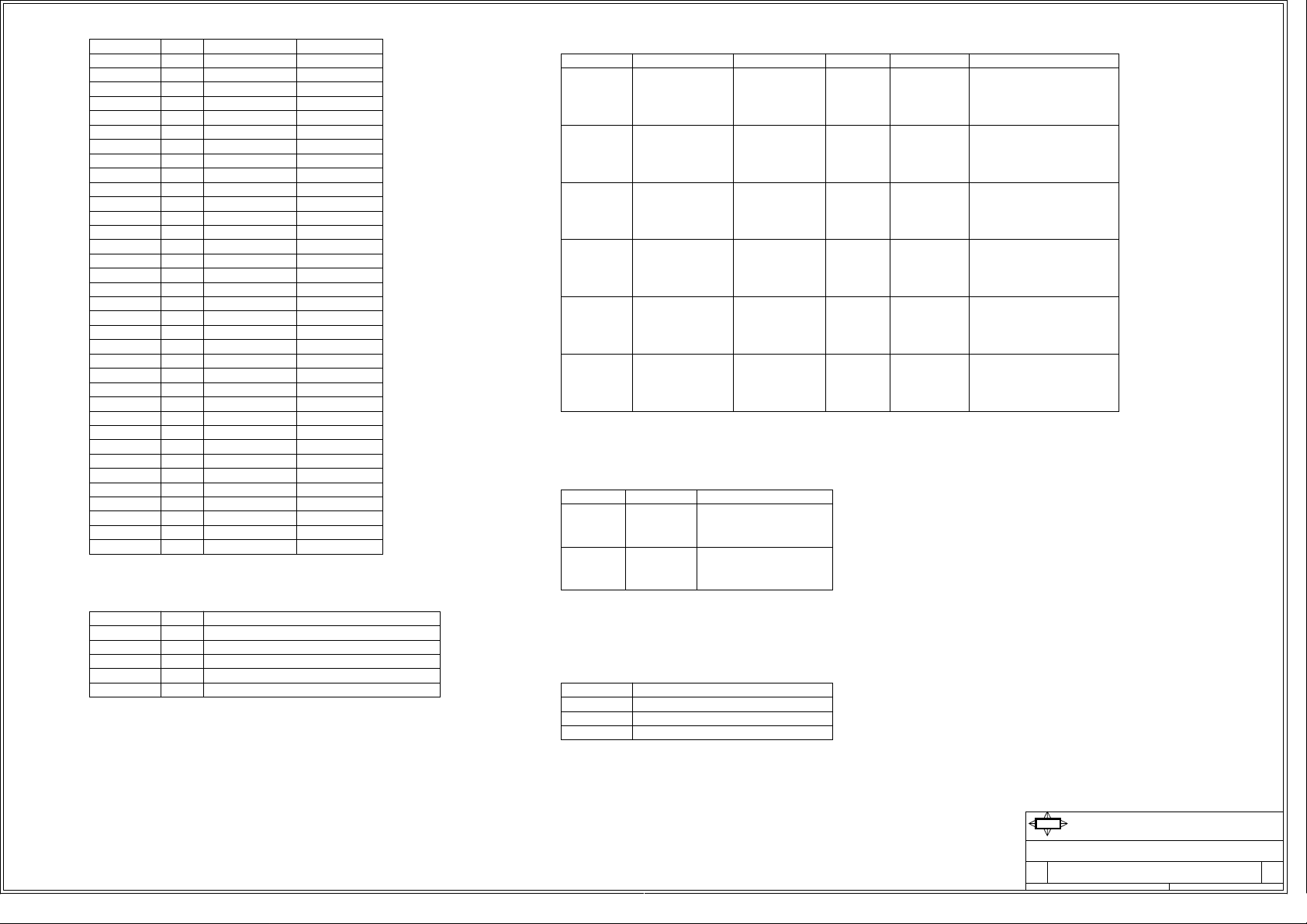

FunctionTypeGPIO Pin

GPIO 0

GPIO 1

GPIO 2

GPIO 3

GPIO 4

GPIO 5

GPIO 6

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16

GPIO 17

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22 GPO22

GPIO 23

PREQ#B

I

I

PREQ#B

I

PIRQ#E

I

PIRQ#F

I

PIRQ#G

PIRQ#H

I

GPI6

I

GPI7

I

CSA_PME#

I

OC4#

I

OC5#

I

SIO_SMI#

I

EXTSMI#

I

SIO_PME#

I

I OC#6

OC#7

I

PGNT#A

O

PGNT#B

O

O GPO18

BIOS_WP#

O

GPO20

O

O GPO21

OD

O

GPO23

GPIO 24 I/O GPIO24

GPIO 25 I/O

A A

*

GPIO 27

GPIO 28

GPIO 32

GPIO 33

GPIO 34

GPIO 40 PREQ#4

GPIO 41

GPIO 48

GPIO 49

LAN_DISABLE#

GPIO27

I/O

I/O GPIO28

I/O

GPIO32

I/O

GPIO33

I/O

GPIO34

I

GPI41

I

O PGNT#4

CPUPWRGD

OD

Power well

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

RESUME

RESUME

RESUME

RESUME

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

MAIN

default output

default output

default output

default output

default output

default output

default output

PCI Config.

DEVICE

PCI Slot 2

PCI Slot 3 PCI_REQ#2

PCI Slot 5

INTA#

INTB#

PCI_REQ#0PCI Slot 1

PCI_GNT#0

INTC#

INTD#

INTB#

INTC#

PCI_REQ#1 AD17 PCICLK1

PCI_GNT#1

INTD#

INTA#

INTC#

INTD#

PCI_GNT#2

INTA#

INTB#

INTD#

PCI_REQ#3PCI Slot 4 AD19

INTA# PCI_GNT#3

INTB#

INTC#

INTB#

INTC#

PCI_REQ#4 AD21 PCICLK4

PCI_GNT#4

INTD#

INTA#

DDR DIMM Config.

DEVICE

DIMM 1 MCLK_A0/MCLK_A0#

DIMM 2

1010000B

1010001B

CLOCKADDRESS

MCLK_A1/MCLK_A1#

MCLK_A2/MCLK_A2#

MCLK_B0/MCLK_B0#

MCLK_B1/MCLK_B1#

MCLK_B2/MCLK_B2#

IDSEL

AD16

AD18

CLOCKREQ#/GNT#

PCICLK0

PCICLK2

PCICLK3

CLK GEN PIN OUTMCP1 INT Pin

13 (PCI_CLK0)

14 (PCI_CLK1)

15 (PCI_CLK2)

16 (PCI_CLK3)

19 (PCI_CLK4)

FWH

Function

GPI 0

GPI 1

*

GPI 3

*

TypeGPIO Pin

PD_DET

I

I

SD_DET

Pull down through 1K ohms (unused)GPI 2

I

Pull down through 1K ohms (unused)

I

I

Pull down through 1K ohms (unused)GPI 4

PCI RESET DEVICE

Signals

PCIRST#1

HD_RST#

Springdale,LAN,FWH, Super I/O

PCI slot 1-3, AGP slotPCIRST#2

Primary, Scondary IDE

Target

MSI

Title

Size Document Number Rev

1

Date: Sheet

MICRO-STAR INt'L CO., LTD.

General Purpose Spec

MS-7140

333Thursday, January 20, 2005

of

100

8

7

6

5

4

3

2

1

93/08/5

1.Create MS7108 ver:0A circuit.

D D

C C

B B

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

HISTORY

MS-7140

2

433Thursday, January 20, 2005

1

100

of

8

7

6

5

4

3

2

1

R72

110R1%

R74

61.9R1%

2

4

6

8

VCC3

V_FSB_VTT

VTT_OUT_RIGHT

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TDI

H_BPM#2

H_BPM#4

H_TDO

H_TMS

H_TCK

H_TRST#

CPU SIGNAL BLOCK

H_EDRDY

R66 680R

H_PCREQ#

R57 680R

D D

CPU_BOOTVTT_OUT_RIGHT

HDBI#0

HDBI#1

HDBI#2

HDBI#3

H_EDRDY

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HDBI#[0..3]8

H_EDRDY8

H_IERR#6

FERR#6,16

STPCLK#16

HINIT#16

HDBSY#8

HDRDY#8

HTRDY#8

C C

B B

A A

HADS#8

HLOCK#8

HBNR#8

HITM#8

HBPRI#8

HDEFER#8

CPU_TMPA20

VTIN_GND20

TRMTRIP#6,16

H_PROCHOT#6

IGNNE#16

SMI#16

A20M#16

C25 X_C0.1U25Y

R46 X_1KR

H_FSBSEL06,10,19

H_FSBSEL16,10,19

H_FSBSEL26,10,19

H_PWRGD6,16

H_CPURST#6,8

HD#[0..63]8

HIT#8

SLP#16

G11

D19

C20

AB2

AB3

AD3

AD1

AF1

AC1

AG1

AE1

AL1

AK1

AE8

AL2

AH2

AE6

G10

D16

A20

AA2

G29

H30

G30

G23

B22

A22

A19

B19

B21

C21

B18

A17

B16

C18

A8

F2

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

M2

N2

P2

K3

L2

N5

C9

Y1

V2

N1

HA#[3..31]8

U4A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

B15

HD#53

TP2

VID5

VID2

VID4

VID0

VID1

AM5

AL4

AK4

AM7

AK3

VID6#

VID5#

VID7#

VID_SELECT

ITP_CLK1

ITP_CLK0

GTLREF_SEL

D7#A7D6#B7D5#B6D4#A5D3#C6D2#A4D1#C5D0#

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

VID3

AL6

AM3

AL5

AM2

VID4#

VID3#

VID2#

VID1#

VID0#

GTLREF0

GTLREF1

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

PCREQ#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

RSVD

RSVD

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP5

COMP4

COMP3

COMP2

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

B4

ZIF-SOCK775-15u

HD#0

AN7

H1

H2

H29

AG3

AF2

AG2

AD2

AJ1

AJ2

G5

J6

K6

M6

J5

K4

W2

P1

H5

G4

G3

F24

G24

G26

G27

G25

F25

W3

F26

AK6

G6

G28

F28

A3

F5

B3

U3

U2

F3

T2

J2

R1

G2

T1

A13

J17

H16

H15

J16

AD5

R6

C17

G19

E12

B9

A16

G20

G12

C8

L1

K1

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

H_PCREQ#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

HRS#2

HRS#1

HRS#0

H_COMP5

H_COMP4

H_COMP3

H_COMP2

H_COMP1

H_COMP0

TP1

CPU_GTLREF

TP9

GTLREF_SEL

RN8 8P4R-62R

1 2

3 4

5 6

7 8

R64 62R

R81 62R

R47 62R

R75 X_62R

R15 X_62R

R58 X_62R

CK_H_CPU# 19

CK_H_CPU 19

TP4

TP3

R49 X_60.4R1%

R60 X_60.4R1%

R51 100R1%

R68 100R1%

R48 60.4R1%

R91 60.4R1%

TP6

TP8

TP7

TP5

HADSTB#1 8

HADSTB#0 8

HDSTBP#3 8

HDSTBP#2 8

HDSTBP#1 8

HDSTBP#0 8

HDSTBN#3 8

HDSTBN#2 8

HDSTBN#1 8

HDSTBN#0 8

NMI 16

INTR 16

CPU_GTLREF 6

H_PCREQ# 8

HREQ#[0..4] 8

HRS#[0..2] 8

TP10

VTT_OUT_LEFT

V_FSB_VTT

VTT_OUT_RIGHT 6

H_BR#0 6,8

VTT_OUT_LEFT 6

C41

X_C0.1U25Y

VCCP

+12V

R73

619R1%

R83

10KR

GTLREF_SEL

N-2N7002_SOT23

N-2N7002_SOT23

VID329

VID129

VID429

VID229

VID029

VID529

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

VTT_OUT_RIGHT

C35 C0.1U25Y

C38 C0.1U25Y

G

R84

249R1%

G

DS

VCC3

VID3

VID1

VID4

VID2

VID0

VID5

DS

Q18

Q19

RN6 8P4R-51R

PLACE BPM TERMINATION NEAR CPU

MCH_GTLREF 8

H_TESTHI0

RN2

X_8P4R-680R

1

3

5

7

R25 X_680R

R26 X_680R

RN3 8P4R-51R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R44 X_49.9R1%

R43 X_49.9R1%

R42 49.9R1%

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AJ6

AJ5

AH5

AH4

AG5

AG4

AG6

AF4

AF5

AB4

AC5

AB5

AA5

AD6

AA4

AB6

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#Y4A19#Y6A18#W6A17#

D53#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

F21

F20

F18

A14

C14

HD#52

E22

C15

D17

D20

D22

G22

G21

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

F17

E21

E19

E18

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

F15

E16

E15

G17

G18

G16

G15

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

A16#W5A15#V4A14#V5A13#U4A12#U5A11#T4A10#

D29#

D28#

D27#

D26#

D25#

F14

E13

D13

G14

G13

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

U6

D24#

D23#

F12

F11

D10

HD#22

HD#23

A9#T5A8#R4A7#M4A6#L4A5#M5A4#P6A3#

D22#

D21#

D20#D7D19#E9D18#F9D17#F8D16#G9D15#

E10

HD#17

HD#18

HD#19

HD#20

HD#21

L5

HD#16

AN6

AC2

AN5

AN3

AN4

AJ3

DBR#

RSVD

RSVD

VSS_SENSE

VCC_SENSE

D14#

D13#

D12#D8D11#

D10#

D9#

D8#

B12

B10

A11

D11

HD#15

A10

C12

C11

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - Signals

2

MS-7140

533Thursday, January 20, 2005

1

100

of

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE9

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

AB8

AA8

VCCP

U4B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCW8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

Y8

Y30

Y23

Y24

Y25

Y26

Y27

Y28

Y29

W30

VCCP

D D

C C

7

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

AG8

AG30

AG29

AG28

AG27

AG26

AG25

AG22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCU8VCCV8VCC

VCC

VCC

VCC

VCC

VCC

VCC

U26

U27

U28

U29

U30

W23

W24

W25

W26

W27

W28

W29

AH28

AH29

AH30

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCT8VCC

VCC

VCC

T26

T27

T28

T29

T30

U23

U24

U25

VCC

VCC

AH8

T25

VCC

VCC

AH9

T24

VCC

VCC

6

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

AK22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCM8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCN8VCCP8VCCR8VCC

T23

N30

N23

N24

N25

N26

N27

N28

N29

M24

M25

M26

M27

M28

M29

M30

VCC

VCC

5

AK25

AK26

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCJ8VCCJ9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCK8VCCL8VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30

K23

K24

K25

K26

K27

K28

K29

K30

M23

4

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT_RIGHT

VTT_OUT_LEFT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

AN9

AN8

HS11HS22HS33HS4

4

AN25

AN26

AN29

AN30

H_VCCA

A23

H_VSSA

B23

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

VTT_PWG

AM6

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

3

V_FSB_VTT

R80 X_1KR

VTT_SEL

VCC3

0

1

TEJ/PSC

RSVD

2

V_FSB_VTT

1

C106 C10U10Y0805

C100 C10U10Y0805

C109 X_C10U10Y0805

CAPS FOR FSB GENERIC

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

VTT_OUT_RIGHT

VTT_OUT_LEFT CPU_GTLREF

B B

A A

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

VTT_OUT_LEFT5

VTT_OUT_RIGHT5

VTT_OUT_LEFT

8

R56 49.9R1%

R61 X_49.9R1%

R59

100R1%

PLACE AT CPU END OF ROUTE

R55 62R

R53 100R

R69 62R

V_FSB_VTT

C47

C0.1U25Y

R28 120R

H_CPURST#

H_PWRGD

H_BR#0

PLACE AT ICH END OF ROUTE

R54 62R

R52 62R

R45 62R

TRMTRIP#

FERR#

H_IERR#

7

C46

C220P50N

H_PROCHOT#VTT_OUT_RIGHT

H_CPURST# 5,8

H_PWRGD 5,16

H_BR#0 5,8

TRMTRIP# 5,16

FERR# 5,16

H_IERR# 5

CPU_GTLREF 5

6

V_FSB_VTT

L2 X_10U100m_0805

CP4

X_COPPER

VID_GD#27,29H_PROCHOT# 5

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

V_FSB_VTT

RN22

1

3

5

7

8P4R-470R

5

H_FSBSEL1

2

4

H_FSBSEL2

6

H_FSBSEL0

8

4

VTT_OUT_RIGHT

VCC5_SB

R40

1KR

R39 10KR

H_FSBSEL1 5,10,19

H_FSBSEL2 5,10,19

H_FSBSEL0 5,10,19

C99

X_C1U10Y

R27 680R

VTT_OUT_LEFT

R38

X_680R

3

C103

C10U10Y1206

1.25V VTT_PWRGOOD

VTT_PWG

Q10

N-SMBT3904_SOT23

H_VCCA

C102

X_C10U10Y1206

H_VSSA

C31

X_C1U10Y

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

Date: Sheet

2

Intel LGA775 CPU - Power

MS-7140

633Thursday, January 20, 2005

1

100

of

8

TP14

AC4

AE3

AE4

D14

E23

VSS

AE30

RSVD

VSS

AE5

RSVD

VSS

AE7

RSVD

VSS

AF10

RSVDD1RSVD

VSS

VSS

AF13

AF16

E24

RSVD

VSS

AF17

RSVD

VSS

U4C

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA30

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE2

AE20

AE24

AE25

AE26

AE27

AE28

A12

VSS

A15

VSS

A18

VSS

A2

VSS

A21

VSS

A24

VSS

A6

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA3

VSS

VSS

AA6

VSS

AA7

VSS

AB1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB7

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D D

C C

AE29

TP13

TP11

F23

RSVDE5RSVDE6RSVDE7RSVD

VSS

VSS

VSS

AF20

AF23

AF24

AF25

TP12

VSS

AF26

B13

RSVDF6RSVD

VSS

AF27

7

RSVDJ3RSVDN4RSVDP5RSVDV1RSVDW1RSVD

VSS

VSS

VSS

VSS

AF3

AF28

AF29

AF30

VSS

6

Y3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

V30

VSSY7VSSY5VSSY2VSSW7VSSW4VSSV7VSSV6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH1

AG7

AH10

AH13

AH16

AH17

AG24

VSSV3VSS

VSS

AH20

V29

V28

V27

V26

V25

V24

V23

VSS

VSS

VSS

VSS

VSS

VSS

VSSU7VSSU1VSST7VSST6VSST3VSSR7VSSR5VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH3

AH6

AH7

AJ10

AJ13

AH23

AJ16

AH24

R30

R29

R28

R27

R26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ4

AJ17

AJ20

AJ23

AJ7

AJ24

AJ27

AJ28

AJ29

AJ30

AK10

VSS

VSS

5

R25

R24

R23

P30

P29

P28

P27

P26

P25

P24

P23

VSS

VSS

VSS

VSSR2VSSP7VSSP4VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSN7VSSN6VSSN3VSSM7VSSM1VSSL7VSSL6VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AK2

AK13

AK16

AK17

AK20

AK5

AK7

AL10

AK23

AK24

AK27

AL13

AK28

AK29

AK30

L30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL16

AL17

AL20

AL23

AL24

AL27

AL28

VSSL3VSS

VSS

AL3

4

H26

H27

AN1

VSS

H28

VSS

VSS

VSS

VSSH3VSSH6VSSH7VSSH8VSSH9VSSJ4VSSJ7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AN2

AN10

AN13

AN16

AN17

AN20

AN23

VSS

VSS

K2

L26

L25

L24

L23

K5

VSS

VSS

VSS

VSS

VSSK7VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AM13

AM16

AM4

AM17

AM20

AM23

AM24

AM27

AM28

L29

L28

L27

VSS

VSS

VSS

AL7

AM1

AM10

3

H17

H18

H19

H20

H21

H22

H23

H24

H25

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSB1VSS

B11

B14

AN24

AN27

AN28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

2

1

B B

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel LGA775 CPU - GND

MS-7140

2

733Thursday, January 20, 2005

1

100

of

8

HA#3

HA#[3..31]5

D D

HADSTB#05

HADSTB#15

ICH_SYNC#17

HREQ#[0..4]5

PLTRST#16,27

H_PCREQ#5

HBPRI#5

HLOCK#5

HDEFER#5

HTRDY#5

HDBSY#5

HDRDY#5

H_EDRDY5

HRS#[0..2]5

CK_H_MCH19

CK_H_MCH#19

PWRGD_3V17,27

H_CPURST#5,6

V_1P5_CORE

C210

C206

H_BR#05,6

HADS#5

HIT#5

HITM#5

HBNR#5

ICH_SYNC#

R114

20R1%

C10U10Y0805

X_C10U10Y0805

V_FSB_VTT5,6,10,18,27

C C

B B

A A

H29

HA#4

K29

HA#5

J29

HA#6

G30

HA#7

G32

HA#8

K30

HA#9

L29

HA#10

M30

HA#11

L31

HA#12

L28

HA#13

J28

HA#14

K27

HA#15

K33

HA#16

M28

HA#17

R29

HA#18

L26

HA#19

N26

HA#20

M26

HA#21

N31

HA#22

P26

HA#23

N29

HA#24

P28

HA#25

R28

HA#26

N33

HA#27

T27

HA#28

T31

HA#29

U28

HA#30

T26

HA#31

T29

J31

N27

E31

R33

E30

M35

L33

M31

HREQ#0

F33

HREQ#1

E32

HREQ#2

H31

HREQ#3

G31

HREQ#4

F31

L34

N35

J35

N34

L35

M32

P33

HRS#0

K34

HRS#1

P34

HRS#2

J32

M23

M22

AG7

G24

AF7

M14

HRCOMP

B23

HSCOMP

D24

HSWING

A23

MCH_GTLREF

A24

60.4R1%

V_FSB_VTT HSCOMP V_FSB_VTTV_FSB_VTT HSWING MCH_GTLREF

R116

U7A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HAD_STB0#

HAD_STB1#

HPCREQ#

BREQ0#

BPRI#

BNR#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

DBSY#

DRDY#

HEDRDY#

RS0#

RS1#

RS2#

HCLKP

HCLKN

PWROK

CPURST#

RSTIN#

ICH_SYNC#

HDRCOMP

HDSCOMP

HDSWING

HDVREF

HS11HS33HS55HS7

AC11

AB11

VCCNCTF

7

7

Y20

Y19

Y17

VCCNCTF

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AJ21

AK21

AK24

C135

X_C2.2P50N

Y16

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AL21

W20

W16

VCCNCTF

RSVRD

AL20

AK18

U20

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AJ24

U16

T20

VCCNCTF

RSVRD

AJ23

AJ18

T19

T17

VCCNCTF

VCCNCTF

RSVRD

RSVRD

V31

AJ20

T16

AA13

VCCNCTF

VCCNCTF

RSVRD

RSVRD

V30

U30

AA14

VCCNCTF

VCCNCTF

RSVRD

RSVRD

V32

AA16

AA18

VCCNCTF

RSVRD

Y30

AB29

AA20

VCCNCTF

VCCNCTF

RSVRD

RSVRD

R31

AA21

AA22

VCCNCTF

RSVRD

R30

AA31

AA23

VCCNCTF

VCCNCTF

RSVRD

RSVRD

AA30

6

V_1P5_CORE

AA24

AB13

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AB24

N13

N14

N15

N16

N18

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

NC

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

RSVRD

AC12

AC13

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

HD_SWING VOLTAGE "10 MIL TRACE , 7 MIL

SPACE" HD_SWING S/B 1/4*VTT +/- 2%

PLACE DIVIDER RESISTOR NEAR VTT

R112

300R1%

RSVRD

AC22

R117

100R1%

N12NCN22NCN23NCN24

NC

P12NCP23NCP24

N20

N21

VCCNCTF

VCCNCTF

VCCNCTF

NC

R12NCR24

C137

C0.01U50X

5

P13

P14

P15

P17

P19

P21

P22

R13

R14

R15

R16

R18

R20

R22

R23

T13

T14

T15

T21

T23

T24

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

J12

T12

V12

Y12

U12

W12

AA12NCAB12

AC23NCAC24NCAN19

L19NCL12

P30

K12

AG6

AJ14

AL28

AH24

AD30

U13

VCCNCTF

NC

H17NCH15NCH12

4

U14

U22

U24

V13

V14

V15

V21

V23

V24

W13

W14

W22

W24

Y13

Y14

Y15

Y21

Y23

Y24

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

VCCNCTF

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DINV_0#

DINV_1#

DINV_2#

DINV_3#

HD_STBP0#

HD_STBN0#

HD_STBP1#

HD_STBN1#

HD_STBP2#

HD_STBN2#

HD_STBP3#

AP1

NC

B35

NC

NCB1NC

A34

HD_STBN3#

NC

(INTEL-915P-B1)

A2

NC

NC

NC

NC

NC

NC

NC

F24NCF12

E16

C16

G12

AR2NCAR1

AP35

AR35NCAR34

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

J33

H33

J34

G35

H35

G34

F34

G33

D34

C33

D33

B34

C34

B33

C32

B32

E28

C30

D29

H28

G29

J27

F28

F27

E27

E25

G25

J25

K25

L25

L23

K23

J22

J24

K22

J21

M21

H23

M19

K21

H20

H19

M18

K18

K17

G18

H18

F17

A25

C27

C31

B30

B31

A31

B27

A29

C28

A28

C25

C26

D27

A27

E24

B25

E34

J26

K19

B26

E33

E35

H26

F26

J19

F19

B29

C29

3

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HDSTBP#0 5

HDSTBN#0 5

HDSTBP#1 5

HDSTBN#1 5

HDSTBP#2 5

HDSTBN#2 5

HDSTBP#3 5

HDSTBN#3 5

HD#[0..63] 5

HDBI#[0..3] 5

2

U7_H

2

112

_

V_1P5_CORE

C201

C0.1U25Y

C187

C0.1U25Y

C280

C0.01U50Y5

C283

C0.1U25Y

C199

C0.1U25Y

C281

C10U10Y0805

C182

C10U10Y0805

1

GTLREF VOLTAGE SHOULD BE 0.67*VTT=0.8V

49.9R1%

R110

49.9 OHM OVER 100 RESISTORS

R109

100R1%

C130

X_C0.1U25Y

C133

C0.1U25Y

MCH_GTLREF 5

ICH_SYNC#ICH_SYNC#

8

7

R141 8.2KR

6

V_2P5_MCH

5

4

3

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

Intel Springdale - CPU Signals

MS-7140

2

833Thursday, January 20, 2005

1

100

of

8

7

6

5

4

3

2

1

DATA_A[0..63]12,15

DATA_A16

DATA_A21

DATA_A6

DATA_A0

DATA_A1

D D

C C

B B

SCS_A#[0..1]12,14

RAS_A#12,13,14

CAS_A#12,14

WE_A#12,14

MAA_A[0..13]12,13,14

ODT_A[0..1]12

SBS_A[0..2]12,13,14

DQS_A012,15

DQS_A#012,15

DQS_A112,15

DQS_A#112,15

DQS_A212,15

DQS_A#212,15

DQS_A312,15

DQS_A#312,15

DQS_A412,15

DQS_A#412,15

DQS_A512,15

DQS_A#512,15

DQS_A612,15

DQS_A#612,15

DQS_A712,15

DQS_A#712,15

P_DDR0_A12

N_DDR0_A12

P_DDR1_A12

N_DDR1_A12

P_DDR2_A12

N_DDR2_A12

SCS_A#0

SCS_A#1

RAS_A#

CAS_A#

WE_A#

MAA_A0

MAA_A1

MAA_A2

MAA_A3

MAA_A4

MAA_A5

MAA_A6

MAA_A7

MAA_A8

MAA_A9

MAA_A10

MAA_A11

MAA_A12

MAA_A13

ODT_A0

ODT_A1

SBS_A0

SBS_A1

DQS_A0

DQS_A#0

DQS_A1

DQS_A#1

DQS_A2

DQS_A#2

DQS_A3

DQS_A#3

DQS_A4

DQS_A#4

DQS_A5

DQS_A#5

DQS_A6

DQS_A#6

DQS_A7

DQS_A#7

P_DDR0_A

N_DDR0_A

P_DDR1_A

N_DDR1_A

P_DDR2_A

N_DDR2_A

SM_XSLEWIN

MCH_VREF_A

SMPCOMP_P

SMPCOMP_N

U7B

AR29

SACS0#

AP32

SACS1#

AR28

SACS2#

AN31

SACS3#

AP27

SARAS#

AN29

SACAS#

AN28

SAWE#

AP26

SAMA0

AR24

SAMA1

AL24

SAMA2

AP23

SAMA3

AR23

SAMA4

AP22

SAMA5

AN23

SAMA6

AP21

SAMA7

AN22

SAMA8

AN21

SAMA9

AM27

SAMA10

AM21

SAMA11

AR20

SAMA12

AP31

SAMA13

AP30

SAODT0

AN32

SAODT1

AP29

SAODT2

AP33

SAODT3

AR27

SABA0

AN27

SABA1

AN20

SABA2

AG1

SADQS0

AG2

SADQS0#

AL3

SADQS1

AL2

SADQS1#

AP7

SADQS2

AR7

SADQS2#

AF17

SADQS3

AG17

SADQS3#

AM30

SADQS4

AL29

SADQS4#

AG35

SADQS5

AG33

SADQS5#

AA34

SADQS6

AA35

SADQS6#

U34

SADQS7

U35

SADQS7#

AN26

SACK0

AP25

SACK0#

AM2

SACK1

AM3

SACK1#

AC34

SACK2

AC35

SACK2#

AN25

SACK3

AM24

SACK3#

AN3

SACK4

AN2

SACK4#

AC33

SACK5

AB34

SACK5#

AB33

SADDR1MA13

AH15

SARCVENOUT#

AE16

SARCVENIN#

AJ12

SMSLEWIN0

AK12

SMSLEWOUT0

AE7

SMVREF0

AG8

SMRCOMP1

AG4

SMRCOMP0

R40240.2R1%

AE5

SMOCDCOMP1

R40340.2R1%

AF5

SMOCDCOMP0

DATA_A2

AE3

AF3

AH3

SADQ0

SADQ1

SADQ2

SBDQ0

AH4

DATA_A10

DATA_A8

DATA_A3

DATA_A7

DATA_A4

DATA_A5

AJ2

AE2

AE1

AG3

SADQ3

SADQ4

SADQ5

SADQ6

SBDQ1

SBDQ2

SBDQ3

SBDQ4

AJ6

AL6

AN6

AG9

DATA_A14

DATA_A15

DATA_A12

DATA_A9

DATA_A11

DATA_A13

AH2

AK2

AK3

AN4

AP4

AJ1

AJ3

AP2

AP3

AR5

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

AJ8

AJ7

AL5

AL8

AH7

AL7

AM5

AF11

AE11

AG10

DATA_A24

DATA_A25

DATA_A18

DATA_A17

AP6

AP9

SADQ17

SADQ18

SBDQ15

SBDQ16

AF13

AG11

DATA_A26

DATA_A22

DATA_A23

DATA_A20

DATA_A19

AN9

AN5

AP5

AN8

AR8

AL17

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

AE13

AH12

AD14

AD15

AD12

AG14

DATA_A32

DATA_A31

DATA_A27

DATA_A29

DATA_A33

DATA_A30

DATA_A28

AJ17

AF19

AH18

AK16

AF16

AD17

AE19

AK27

AJ28

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

AL18

AF14

AK19

AF22

AE22

AH19

AH21

AD21

AD18

SCKE_A[0..3]12,13,14

DATA_A37

DATA_A34

DATA_A35

DATA_A36

AL31

AK31

AH27

AL27

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

AJ26

AL26

AF24

AF25

DATA_A45

DATA_A41

DATA_A40

DATA_A38

DATA_A39

AN30

AL30

AH33

AH35

SADQ38

SADQ39

SADQ40

SADQ41

SBDQ36

SBDQ37

SBDQ38

SBDQ39

AJ25

AL25

AF23

AD23

DATA_A49

DATA_A48

DATA_A43

DATA_A42

DATA_A44

DATA_A47

DATA_A46

AF33

AE33

AJ33

AJ34

AG32

AF34

AD31

AD35

SADQ42

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SBDQ40

SBDQ41

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

AJ31

AJ29

AF28

AK32

AK33

AG31

AG30

AG27

DQM_A[0..7]12,15

DQM_A6

DQM_A1

DQM_A4

DQM_A2

DQM_A7

DQM_A3

DQM_A5

DATA_A56

DATA_A61

DATA_A53

DATA_A54

DATA_A52

DATA_A51

DATA_A50

Y33

W34

AE35

AE34

AA32

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

AF27

AE27

AB26

AE31

AC26

DATA_A62

DATA_A57

DATA_A60

DATA_A58

DATA_A55

DATA_A59

Y35

V34

V33

R32

R34

W35

W33

T33

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

V28

V29

Y26

W29

AE29

AB27

AA28

AC28

DQM_A0

DATA_A63

SCKE_A1

SCKE_A0

SCKE_A3

SCKE_A2

AP19

AM18

AN18

AR19

AF2

AL1

AN7

AH16

AK29

AG34

AA33

T35

SACKE0

SACKE1

SACKE2

SACKE3

SADQ63

SBDQ61

SBDQ62

SBDQ63

SBCKE0

SBCKE1

SBCKE2

U26

AR9

AM9

W26

AA29

AP10

AN10

U33

SBCS0#

SBCS1#

SADM3

SADM4

SADM5

SADM6

SADM7

SBDDR1MA13

SBRCVENOUT#

SBRCVENIN#

SMSLEWIN1

SMSLEWOUT1

SBCS2#

SBCS3#

SBRAS#

SBCAS#

SBWE#

SBMA0

SBMA1

SBMA2

SBMA3

SBMA4

SBMA5

SBMA6

SBMA7

SBMA8

SBMA9

SBMA10

SBMA11

SBMA12

SBMA13

SBODT0

SBODT1

SBODT2

SBODT3

SBBA0

SBBA1

SBBA2

SBDQS0

SBDQS0#

SBDQS1

SBDQS1#

SBDQS2

SBDQS2#

SBDQS3

SBDQS3#

SBDQS4

SBDQS4#

SBDQS5

SBDQS5#

SBDQS6

SBDQS6#

SBDQS7

SBDQS7#

SBCK0

SBCK0#

SBCK1

SBCK1#

SBCK2

SBCK2#

SBCK3

SBCK3#

SBCK4

SBCK4#

SBCK5

SBCK5#

SADM0

SADM1

SADM2

SMVREF1

SBDM0

SBDM1

SBDM2

SBDM3

SBDM4

SBDM5

SBDM6

SBDM7

SBCKE3

AJ5

AH9

W31

AH31

AD24

(INTEL-915P-B1)

AH13

AG20

AG24

AN33

AM34

AP34

AN34

AN17

AP18

AP17

AM15

AR15

AN15

AL15

AP14

AM12

AP13

AL12

AN13

AR12

AP15

AP11

AR11

AL33

AM33

AL34

AL35

AK34

AR16

AN16

AN11

AK5

AL4

AK10

AH10

AK13

AL14

AD20

AF20

AH25

AG26

AH28

AH30

AB31

AC30

W27

Y28

AH22

AG23

AK9

AL9

AE26

AE25

AL23

AK22

AJ11

AL11

AD28

AD29

AD32

AK15

AN14

AF9

AE10

AE8

SCS_B#0

SCS_B#1

RAS_B#

CAS_B#

WE_B#

MAA_B0

MAA_B1

MAA_B2

MAA_B3

MAA_B4

MAA_B5

MAA_B6

MAA_B7

MAA_B8

MAA_B9

MAA_B10

MAA_B11

MAA_B12

MAA_B13

ODT_B0

ODT_B1

ODT_B3

SBS_B0

SBS_B1

SBS_B2SBS_A2

DQS_B0

DQS_B#0

DQS_B1

DQS_B#1

DQS_B2

DQS_B#2

DQS_B3

DQS_B#3

DQS_B4

DQS_B#4

DQS_B5

DQS_B#5

DQS_B6

DQS_B#6

DQS_B7

DQS_B#7

P_DDR0_B

N_DDR0_B

P_DDR1_B

N_DDR1_B

P_DDR2_B

N_DDR2_B

P_DDR3_B

N_DDR3_B

P_DDR5_B

N_DDR5_B

SM_YSLEWIN

MCH_VREF_B

SCS_B#[0..1] 13,14

RAS_B# 13,14

CAS_B# 13,14

WE_B# 13,14

MAA_B[0..13] 12,13,14

ODT_B0 13,14

ODT_B1 12,13,14

ODT_B3 12,14

SBS_B[0..2] 12,13,14

DQS_B0 13,15

DQS_B#0 13,15

DQS_B1 13,15

DQS_B#1 13,15

DQS_B2 13,15

DQS_B#2 13,15

DQS_B3 13,15

DQS_B#3 13,15

DQS_B4 13,15

DQS_B#4 13,15

DQS_B5 13,15

DQS_B#5 13,15

DQS_B6 13,15

DQS_B#6 13,15

DQS_B7 13,15

DQS_B#7 13,15

P_DDR0_B 13

N_DDR0_B 13

P_DDR1_B 13

N_DDR1_B 13

P_DDR2_B 13

N_DDR2_B 13

P_DDR3_B 13

N_DDR3_B 13

P_DDR5_B 13

N_DDR5_B 13

SCKE_B1

DATA_B42

DATA_B4

DATA_B5

DATA_B3

DATA_B0

DATA_B2

DATA_B6

DATA_B1

DATA_B[0..63]13,15

DATA_B14

DATA_B15

DATA_B21

DATA_B23

DATA_B11

DATA_B7

DATA_B8

DATA_B9

DATA_B17

DATA_B10

DATA_B16

DATA_B12

DATA_B13

DATA_B18

DATA_B19

DATA_B27

DATA_B20

DATA_B24

DATA_B22

DATA_B25

DATA_B26

DATA_B34

DATA_B32

DATA_B35

DATA_B36

DATA_B31

DATA_B30

DATA_B33

DATA_B28

DATA_B29

DATA_B37

DATA_B38

CPU STRAPPING RESISTORS

VCC_DDR

A A

ALL COMPONENTS CLOSE TO CPU

R153 80.6R1%

C190

X_C0.1U25Y

R151 80.6R1%

SMPCOMP_N

SMPCOMP_P

VCC_DDR

R156 1KR1%

DATA_B46

DATA_B47

DATA_B48

DATA_B52

DATA_B55

DATA_B40

DATA_B45

DATA_B39

DATA_B41

DATA_B43

DATA_B49

DATA_B44

SCKE_B[0..2]13,14

R155

1KR1%

DATA_B57

DATA_B54

DATA_B51

DATA_B56

DATA_B50

DATA_B53

DQM_B[0..7]13,15

SCKE_B0

DATA_B61

DATA_B63

DATA_B58

DATA_B60

DATA_B59

DATA_B62

MCH_VREF_B

C183

PLACE 0.1UF CAP CLOSE TO MCH

C0.1U25Y

MCH_VREF_A

PLACE 0.1UF CAP CLOSE TO MCH

C185

C0.1U25Y

SCKE_B2

PLACE CLOSE TO MCH

8

7

6

5

4

DQM_B2

DQM_B3

DQM_B1

DQM_B7

DQM_B6

DQM_B5

DQM_B0

DQM_B4

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

Date: Sheet

3

Intel Springdale - Memory Signals

2

MS-7140

933Thursday, January 20, 2005

1

100

of

8

EXP_A_RXP_022

EXP_A_RXN_022

EXP_A_RXP_122

EXP_A_RXN_122

EXP_A_RXP_222

EXP_A_RXN_222

CK_PE_100M_MCH19

CK_PE_100M_MCH#19

SDVO_CTRL_DATA22

SDVO_CTRL_CLK22

R127 1KR1%

R128 X_1KR1%

V_1P5_CORE

V_1P5_CORE

EXP_A_RXP_322

EXP_A_RXN_322

EXP_A_RXP_422

EXP_A_RXN_422

EXP_A_RXP_522

EXP_A_RXN_522

EXP_A_RXP_622

EXP_A_RXN_622

EXP_A_RXP_722

EXP_A_RXN_722

EXP_A_RXP_822

EXP_A_RXN_822

EXP_A_RXP_922

EXP_A_RXN_922

EXP_A_RXP_1022

EXP_A_RXN_1022

EXP_A_RXP_1122

EXP_A_RXN_1122

EXP_A_RXP_1222

EXP_A_RXN_1222

EXP_A_RXP_1322

EXP_A_RXN_1322

EXP_A_RXP_1422

EXP_A_RXN_1422

EXP_A_RXP_1522

EXP_A_RXN_1522

DMI_ITP_MRP_016

DMI_ITN_MRN_016

DMI_ITP_MRP_116

DMI_ITN_MRN_116

DMI_ITP_MRP_216

DMI_ITN_MRN_216

DMI_ITP_MRP_316

DMI_ITN_MRN_316

C164 C0.1U25Y

D D

C C

MEMTYPE

B B

V_2P5_DAC_FILTERED25

A A

EXP_A_RXP_0

EXP_A_RXN_0

EXP_A_RXP_1

EXP_A_RXN_1

EXP_A_RXP_2

EXP_A_RXN_2

EXP_A_RXP_3

EXP_A_RXN_3

EXP_A_RXP_4

EXP_A_RXN_4

EXP_A_RXP_5

EXP_A_RXN_5

EXP_A_RXP_6

EXP_A_RXN_6

EXP_A_RXP_7

EXP_A_RXN_7

EXP_A_RXP_8

EXP_A_RXN_8

EXP_A_RXP_9

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXN_10

EXP_A_RXP_11

EXP_A_RXN_11

EXP_A_RXP_12

EXP_A_RXN_12

EXP_A_RXP_13

EXP_A_RXN_13

EXP_A_RXP_14

EXP_A_RXN_14

EXP_A_RXP_15

EXP_A_RXN_15

DMI_ITP_MRP_0

DMI_ITN_MRN_0

DMI_ITP_MRP_1

DMI_ITN_MRN_1

DMI_ITP_MRP_2

DMI_ITN_MRN_2

DMI_ITP_MRP_3

DMI_ITN_MRN_3

CK_PE_100M_MCH

CK_PE_100M_MCH#

SDVO_CTRL_DATA

SDVO_CTRL_CLK

BSEL0

BSEL1

BSEL2

MTYPE

EXP_SLR

V_1P5_CORE

VCCA_HPLLVCCA_HPLL

VCCA_MPLL

VCCA_DPLLA

VCCA_DPLLB

VCCA_GPLL

V_2P5_MCH

V_2P5_DAC_FILTERED

CP7 X_COPPER

L5 X_0R0805

CP8 X_COPPER

L6 X_0R0805

L32 OPTION 0 ohm

L29 OPTION 0 ohm

U7C

E11

F11

J11

H11

F9

E9

F7

E7

B3

B4

D5

E5

G6

G5

H8

H7

J6

J5

K8

K7

L6

L5

P10

R10

M8

M7

N6

N5

P7

P8

R6

R5

U5

U6

T9

T8

V7

V8

V10

U10

A11

B11

K13

J13

H16

E15

D17

M16

F15

C15

A16

B15

C14

K15

L10

M10

A17

B17

A12

B13

A14

A13

E13

D13

F13

C160

X_C0.22U16Y

7

V_1P5_CORE VCC_DDR

AD9

AD8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AC10

AC9

AC8

AC7

EXPARXP0

EXPARXN0

EXPARXP1

EXPARXN1

EXPARXP2

EXPARXN2

EXPARXP3

EXPARXN3

EXPARXP4

EXPARXN4

EXPARXP5

EXPARXN5

EXPARXP6

EXPARXN6

EXPARXP7

EXPARXN7

EXPARXP8

EXPARXN8

EXPARXP9

EXPARXN9

EXPARXP10

EXPARXN10

EXPARXP11

EXPARXN11

EXPARXP12

EXPARXN12

EXPARXP13

EXPARXN13

EXPARXP14

EXPARXN14

EXPARXP15

EXPARXN15

DMI RXP0

DMI RXN0

DMI RXP1

DMI RXN1

DMI RXP2

DMI RXN2

DMI RXP3

DMI RXN3

GCLKINP

GCLKINN

SDVOCTRLDATA

SDVOCTRLCLK

BSEL0

BSEL1

BSEL2

RSVRD

RSVRD

MTYPE

EXP_SLR

RSVRD

RSVRD

RSVRD

DREFSSCLKINP

DREFSSCLKINN

VCCAHPLL

VCCAMPLL

VCCADPLLA

VCCADPLLB

VCCA3GPLL

VCCHV

VCCACRTDAC

VCCACRTDAC

VSSACRTDAC

AD10

VCC

VCC

VCC

VCC

VTT

VTT

VTT

H22

G22

G21

VCCA_HPLL

C150

X_C10U10Y0805

VCCA_MPLL

C149

X_C10U10Y0805

VCC

VCC

VCC

VTT

VTT

VTT

F22

F21

F20

VCC

VTT

E22

V_FSB_VTT5,6,8,18,27

VCC

VCC

VTT

VTT

E19

E21

E20

I=45mA

C148

C0.1U25Y

I=60mA

C151

C0.1U25Y

AC6

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

D22

D21

D20

D19

6

AB9

AB8

AB7

AB6

AC2

AC1

AB10

AC5

AC4

AC3

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VTT

VTT

VTT

VTT

VTT

VTT

VTT

C19

VTT

B21

B20

B19

B22

V_FSB_VTT

VTT

A22

A21

V_1P5_CORE

V_1P5_CORE

VTT

C22

C21

C20

5

AR26

AP28

AM28

AM26

AM25

AR33

AR31

AR22

AR18

AR14

AR10

AP24

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

T25

V25

V20

V16

V11

U25

U11

CP11 X_COPPER

L10 X_0R0805

CP10 X_COPPER

L9 X_0R0805

AP20

VCCSM

VSSNCTF

T18

AB4

AB5

VCC

VTT

A20

U18

AB3

AB2

AB1

W18

V19

V17

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCSM

VCCSM

VTT

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

A19

Y25

Y18

Y11

W25

W11

AB25

AA25

AA11

AC25

AM23

AP16

AN35

AM32

AM22

AM20

AM19

AM11

AM10

AK35

AM17

AM16

AM14

AP12

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

T11

P25

P11

R25

R11

N25

AD25

AM13

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

P16

P18

AA15

AA17

N17

N19

AA19

P20

R17

VCCA_DPLLA

C177

X_C10U10Y0805

C172

X_C10U10Y0805

R19

N11

M11

4

V_1P5_PCIEXPRESS

W1

VCC3GY9VCC3GY8VCC3GY7VCC3GY6VCC3GY5VCC3GY4VCC3GY3VCC3GY2VCC3GY1VCC3GW9VCC3GW8VCC3GW7VCC3GW6VCC3GW4VCC3GW3VCC3GW2VCC3G

C10

EXPATXP0

C9

EXPATXN0

A9

EXPATXP1

A8

EXPATXN1

C8

EXPATXP2

C7

EXPATXN2

A7

EXPATXP3

A6

EXPATXN3

C6

EXPATXP4

C5

EXPATXN4

C2

EXPATXP5

D2

EXPATXN5

E3

EXPATXP6

F3

EXPATXN6

F1

EXPATXP7

G1

EXPATXN7

G3

EXPATXP8

H3

EXPATXN8

H1

EXPATXP9

J1

EXPATXN9

J3

EXPATXP10

K3

EXPATXN10

K1

EXPATXP11

L1

EXPATXN11

L3

EXPATXP12

M3

EXPATXN12

M1

EXPATXP13

N1

EXPATXN13

N3

EXPATXP14

P3

EXPATXN14

P1

EXPATXP15

R1

EXPATXN15

R3

DMI TXP0

T3

DMI TXN0

T1

DMI TXP1

U1

DMI TXN1

U3

DMI TXP2

V3

DMI TXN2

V5

DMI TXP3

W5

DMI TXN3

Y10

EXPACOMPO

W10

EXPACOMPI

E12

CRTHSYNC

D12

CRTVSYNC

F14

CRTRED

D14

CRTGREEN

H14

CRTBLUE

G14

CRTREDB

E14

CRTGREENB

J14

CTRBLUEB

CRTDDCCLK

DREFCLKINP

DREFCLKINN

CRTIREF

PMEXTTS

PMBMBUSY#

TESTIN#

MCHDETECT

L14

M15

M13

M12

A15

K16

G16

R35

A35

V_1P5_CORE

L7 1U500m_0805

CRTDDCDATA

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

VSSNCTF

T22

V22

R21

Y22

U15

U21

U23

W15

W21

W23

(INTEL-915P-B1)

I=55mA

C171

C0.1U25Y

I=55mA

C170

C0.1U25Y

V_1P5_CORE

R148 24.9R1%

EXP_A_TXP_0

EXP_A_TXN_0

EXP_A_TXP_1

EXP_A_TXN_1

EXP_A_TXP_2

EXP_A_TXN_2

EXP_A_TXP_3

EXP_A_TXN_3

EXP_A_TXP_4

EXP_A_TXN_4

EXP_A_TXP_5

EXP_A_TXN_5

EXP_A_TXP_6

EXP_A_TXN_6

EXP_A_TXP_7

EXP_A_TXN_7

EXP_A_TXP_8

EXP_A_TXN_8

EXP_A_TXP_9

EXP_A_TXN_9

EXP_A_TXP_10

EXP_A_TXN_10

EXP_A_TXP_11

EXP_A_TXN_11

EXP_A_TXP_12

EXP_A_TXN_12

EXP_A_TXP_13

EXP_A_TXN_13

EXP_A_TXP_14

EXP_A_TXN_14

EXP_A_TXP_15

EXP_A_TXN_15

DMI_MTP_IRP_0

DMI_MTN_IRN_0

DMI_MTP_IRP_1

DMI_MTN_IRN_1

DMI_MTP_IRP_2

DMI_MTN_IRN_2

DMI_MTP_IRP_3

DMI_MTN_IRN_3

GRCOMP

HSYNC

VSYNC

VGA_RED

VGA_GREEN

VGA_BLUE

MCH_DDC_DATA

MCH_DDC_CLK

CK_96M_DREF_NB

CK_96M_DREF#_NB

DACREFSET

EXTTS

R140 X_10KR

CP13 X_COPPER

L11 X_0R0805

3

GRCOMP

EXP_A_TXP_0 22

EXP_A_TXN_0 22

EXP_A_TXP_1 22

EXP_A_TXN_1 22

EXP_A_TXP_2 22

EXP_A_TXN_2 22

EXP_A_TXP_3 22

EXP_A_TXN_3 22

EXP_A_TXP_4 22

EXP_A_TXN_4 22

EXP_A_TXP_5 22

EXP_A_TXN_5 22

EXP_A_TXP_6 22

EXP_A_TXN_6 22

EXP_A_TXP_7 22

EXP_A_TXN_7 22

EXP_A_TXP_8 22

EXP_A_TXN_8 22

EXP_A_TXP_9 22

EXP_A_TXN_9 22

EXP_A_TXP_10 22

EXP_A_TXN_10 22

EXP_A_TXP_11 22

EXP_A_TXN_11 22

EXP_A_TXP_12 22

EXP_A_TXN_12 22

EXP_A_TXP_13 22

EXP_A_TXN_13 22

EXP_A_TXP_14 22

EXP_A_TXN_14 22

EXP_A_TXP_15 22

EXP_A_TXN_15 22

DMI_MTP_IRP_0 16

DMI_MTN_IRN_0 16

DMI_MTP_IRP_1 16

DMI_MTN_IRN_1 16

DMI_MTP_IRP_2 16

DMI_MTN_IRN_2 16

DMI_MTP_IRP_3 16

DMI_MTN_IRN_3 16

HSYNC 25

VSYNC 25

VGA_RED 25

VGA_GREEN 25

VGA_BLUE 25

MCH_DDC_DATA 25

MCH_DDC_CLK 25

CK_96M_DREF_NB 19

CK_96M_DREF#_NB 19

R131 X_255R1%

V_2P5_MCH

+

CT2

X__CD100U16EL5

VCCA_GPLL_RVCCA_DPLLB

ANALOG FILTERS

V_1P5_PCIEXPRESS

C198

C184 C10U10Y0805

R132 1R1%

R139 1R1%

V_FSB_VTT

C10U10Y0805

VCCA_GPLL

C162

X_C10U10Y0805

2

VCC_DDR VCC_DDR

C159 C1U16Y0805

C174 C1U16Y0805

C143 C1U16Y0805

C122 C1U16Y0805

C134

X_C0.1U25Y

0

0

1

0

H_FSBSEL1

H_FSBSEL2

H_FSBSEL0

TABLE

PSB FREQUENCY

RESERVED

133 MHZ (533)

200 MHZ (800)

H_FSBSEL15,6,19

H_FSBSEL25,6,19

H_FSBSEL05,6,19

BSEL

2

1

0

0

0

0

0

1

I=45mA

C161

C0.1U25Y

1

C138 C1U16Y0805

C166 C1U16Y0805

C124 C1U16Y0805

C121 C1U16Y0805

C146

C139

C0.1U25Y

X_C0.1U25Y

BSEL1

R87

RN27

7 8

5 6

3 4

1 2

8P4R-10KR

X_2.49KR1%

BSEL2

R88

X_2.49KR1%

BSEL0

R89

X_2.49KR1%

V_2P5_MCH

L8

X_0.1U220m

CP9 X_COPPER

8

7

6

5

4

V_2P5_DAC_FILTERED

+

CT1

X__CD100U16EL5

C167

C0.1U25Y

MSI

C169

C0.01U50X

3

Title

Size Document Number Rev

Date: Sheet

2

MICRO-STAR INt'L CO., LTD.

Intel Grantsdale PCI-Express & RBG Signals

MS-7140

of

10 33Thursday, January 20, 2005

1

100

Loading...

Loading...