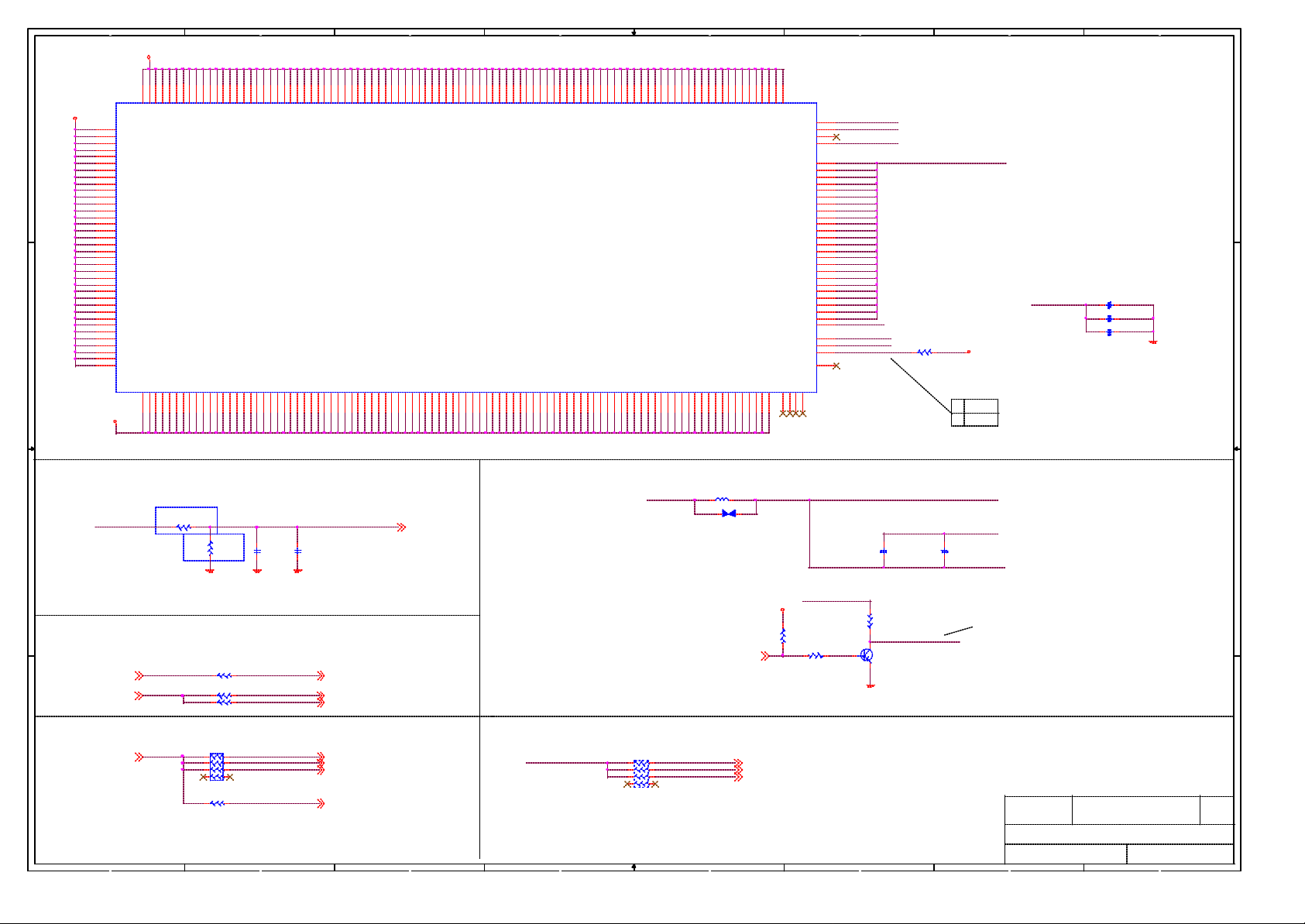

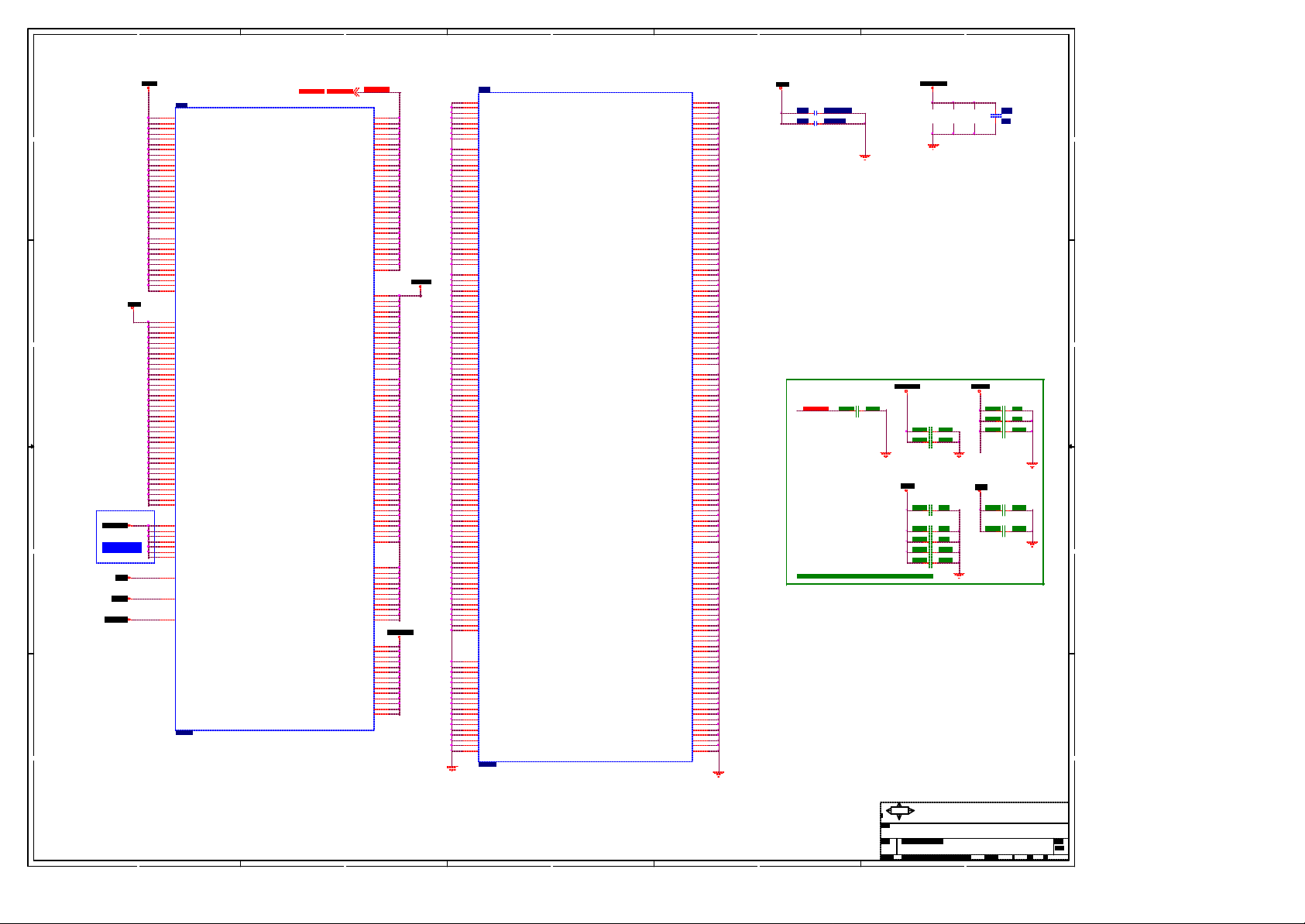

MSI MS-7138 Schematics

8

MS-7138

7

6

5

4

3

2

1

Version 100

02/21/2005 Update

Cover Sheet

1

D D

* Intel LGA775 Processor

*SIS 649 / 662 + 965 / 965L

*REALTEK 8100C/8110S PCI LAN + 8201CL

*Winbond 83627EHF I/O

*USB 2.0 support x8

*ALC 655 AC97 CODEC

Block Diagram

MAIN CLOCK GEN & DDR CLOCK BUFFER

LGA775 INTEL CPU Sockets

SIS 649 / 662

DDR SLOT

DDR TERMINATOR

SIS 965 / 965L

Realtek PHY 8201CL

C C

Realtek PCI Lan 8100C/8100S

PCI SLOT 1,2,3

ERP BOM Function Description

Opt :STD501/601-7138 SiS 649+965 W/O 1394, W/ SATA

IDE CONNECTOR

PCI EXPRESS X 16

AC'97 CODEC (ALC655)

USB CONNECTOR

AUDIO CONNECTOR & VGA

FAN

B B

LAN CONNECTOR & PS/2 CONNECTOR

LPC I/O (W83627EHF)

2

3

4 - 6

7 - 10

11

12

13 - 16

17

18

19

20

21

22

23

24

25

26

27

Title

28

29

30

31

32

MS7138

Cover Sheet

Sheet of

1 32

1

Rev

100

PARALLEL & SERIAL PORT

ACPI CONTROLLER

FRONT PANEL & ATX POWER CONNECOTR

VRM 10

Decoupling Capacitor

A A

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Wednesday, February 23, 2005

2

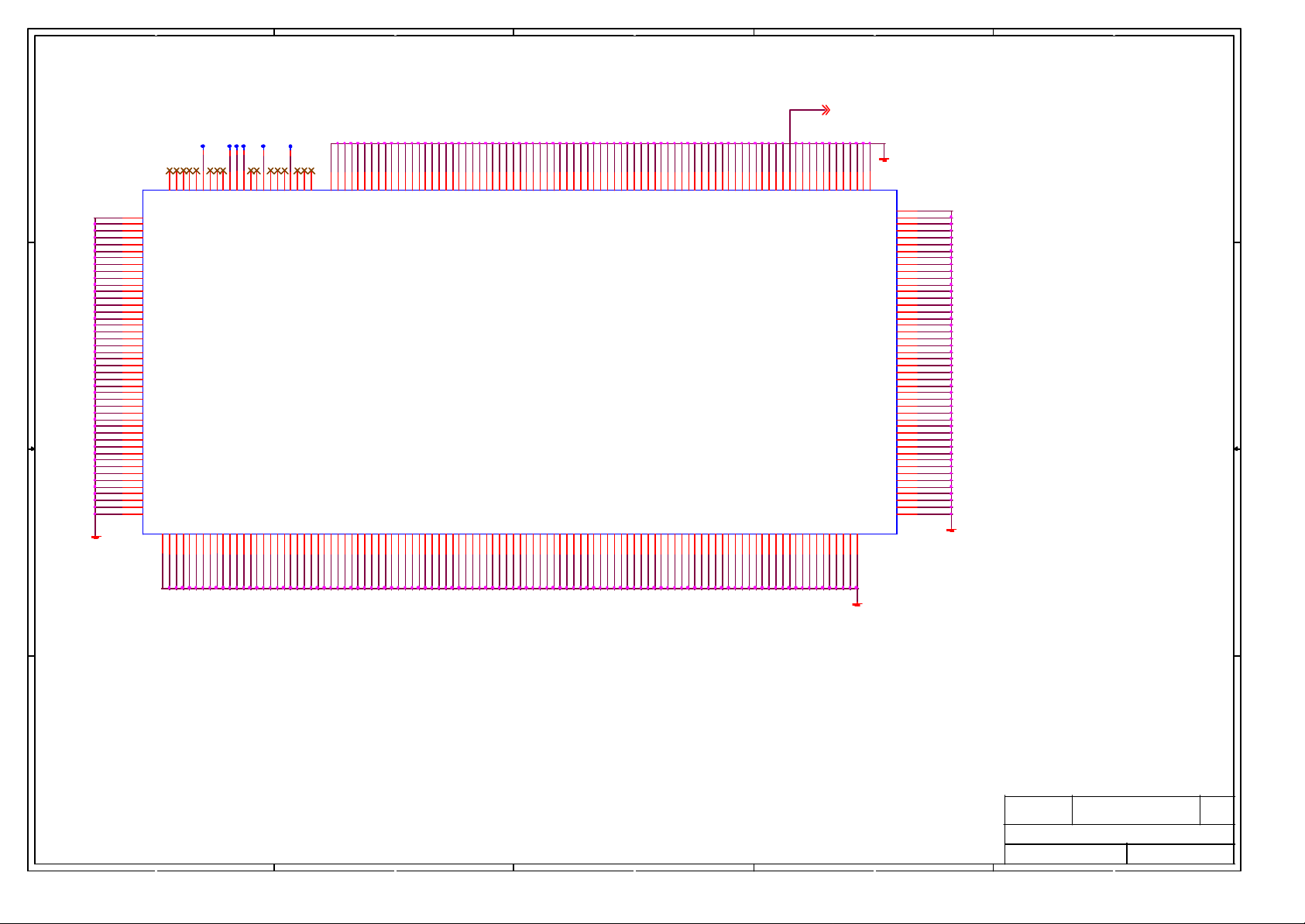

5

4

3

2

1

GPIO_0

GPIO_1

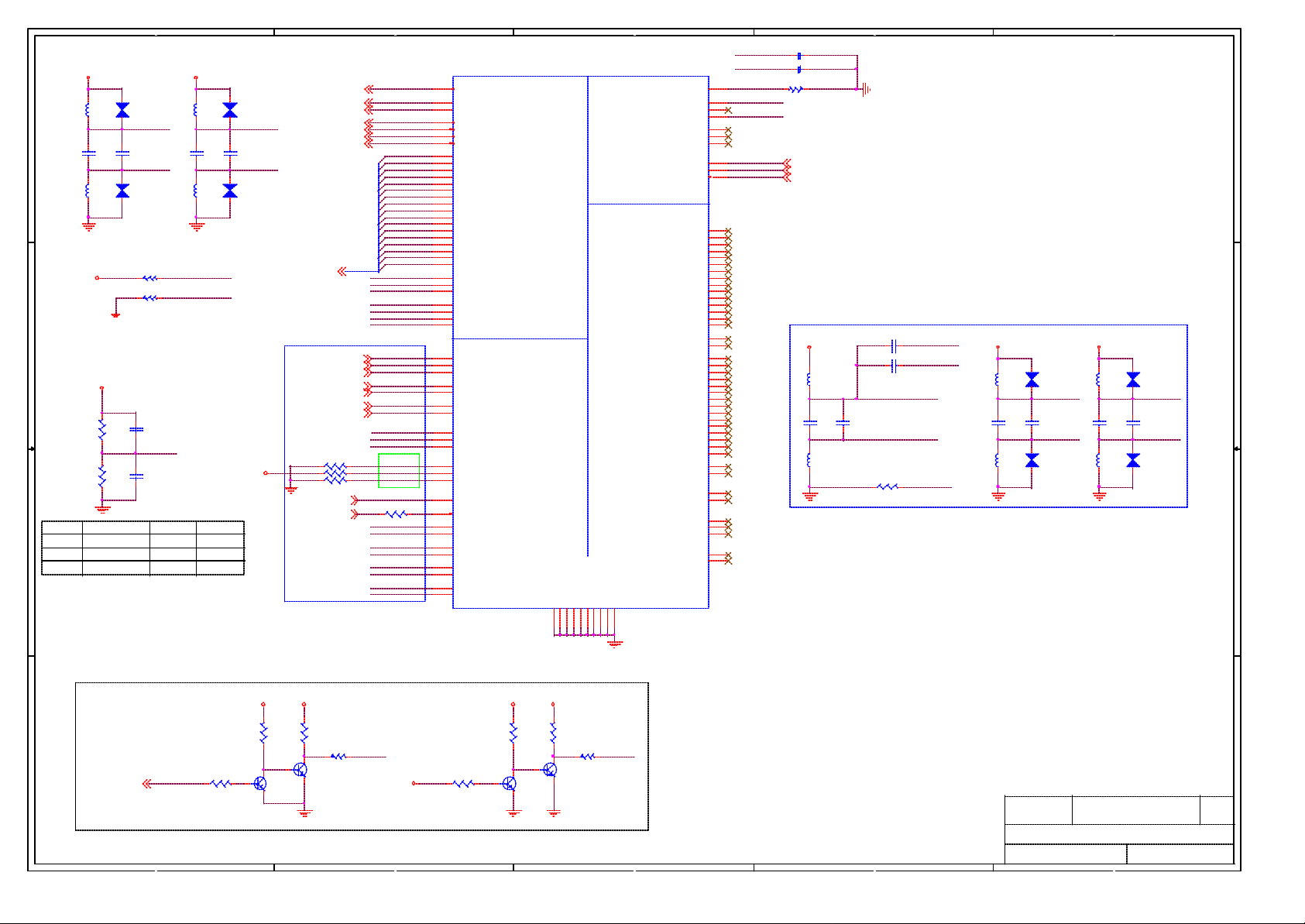

System Block Diagram

D D

GPIO_2

GPIO_3 EXTSMI#

GPIO_4

GPIO_5

LGA775

GPIO_6

GPI_7 RESUME

GPI_8 RING

GPI_9

GPI_10

GPIO_11

System Bus

800MHz

HOST BUS

P

C

I

|

C C

E

PCI-Express X 16

Graphic Interface

SIS 649

/

SIS 662

MEMORY BUS

DDR

333/400MHz

D

D

I

I

M

M

M

M

1

2

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

GPIO_22

GPIO_23

MuTIOL

Data Bus

up to

1GHz

USB 2.0 X 8 USB 2.0 AC-LINK

PCI 1, 2,3

8100C/8110S

KEYBOARD/

MOUSE

B B

PHY 8201CL

PCI BUS

GMII

ATA133

SIS 965

SATA SATA 1,2,3,4

AC'97

AUDIO CODEC

IDE 1,2

GPIO_24

PCI Config.

DEVICE

PCI Slot 2

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

I/O

I/O

I

I

I

I RESUME

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

PCI Slot 3 PCI_REQ#2 AD21

PIRQ#D

PIRQ#A

PIRQ#B

LPC BUS

PIRQ#C

LAN PIRQ#C PC I_REQ#3

FAN SPEED,VOTLAGE,TEMPERATURECPU_FAN SYS_FAN PWR_FAN

PCI RESET DEVICE

Signals

PCIRST#1

Northbridge,LAN,1394,S/IO,Flash Rom

LPC ROM

FAN CONTROL H/W MONITOR

LPC SUPER I/O

W83627EHF

PCI1~3PCIRST#2

A A

HDDRST#

Primary, Scondary IDE

Flash Rom protection

MAIN

MAIN

Boot Block protection

THERM#

MAIN

MAIN

MAIN

Pull-Up

MAIN

RESERVED

MAIN

RESERVED

RESERVED

RESUME

RESERVED

RESUME

RESERVED

RESUME

RESUME

Pull-Down

Pull-DownGPIO_12 RESUME

RESUME

Pull-Up

Pull-Down

RESUME

KBDAT

RESUME

KBCLK

RESUME

MSDAT

RESUME

MSCLK

RESUME

SMBCLK

MAIN

SMBDAT

MAIN

RESUME

RESERVED

RESUME

RESERVED

RESUME

RESERVED

RESERVED

Target

PCI_REQ#0PCI Slot 1

AD19

IDSEL

CLOCKREQ#/GNT#MCP1 INT Pin

PCICLK1

PCI_GNT#0

PCI_REQ#1 AD20 PCICLK2

PCI_GNT#1

PCICLK3

PCI_GNT#2

AD22 LAN_PCLK

PCI_GNT#3

GPIO Table on SIS965

GPIOS IR/CIR COM1,2 PRINTER FLOPPY

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, February 23, 2005

Title

MS7138

System Block Diagram

Sheet of

1

Rev

100

2 32

5

4

3

2

1

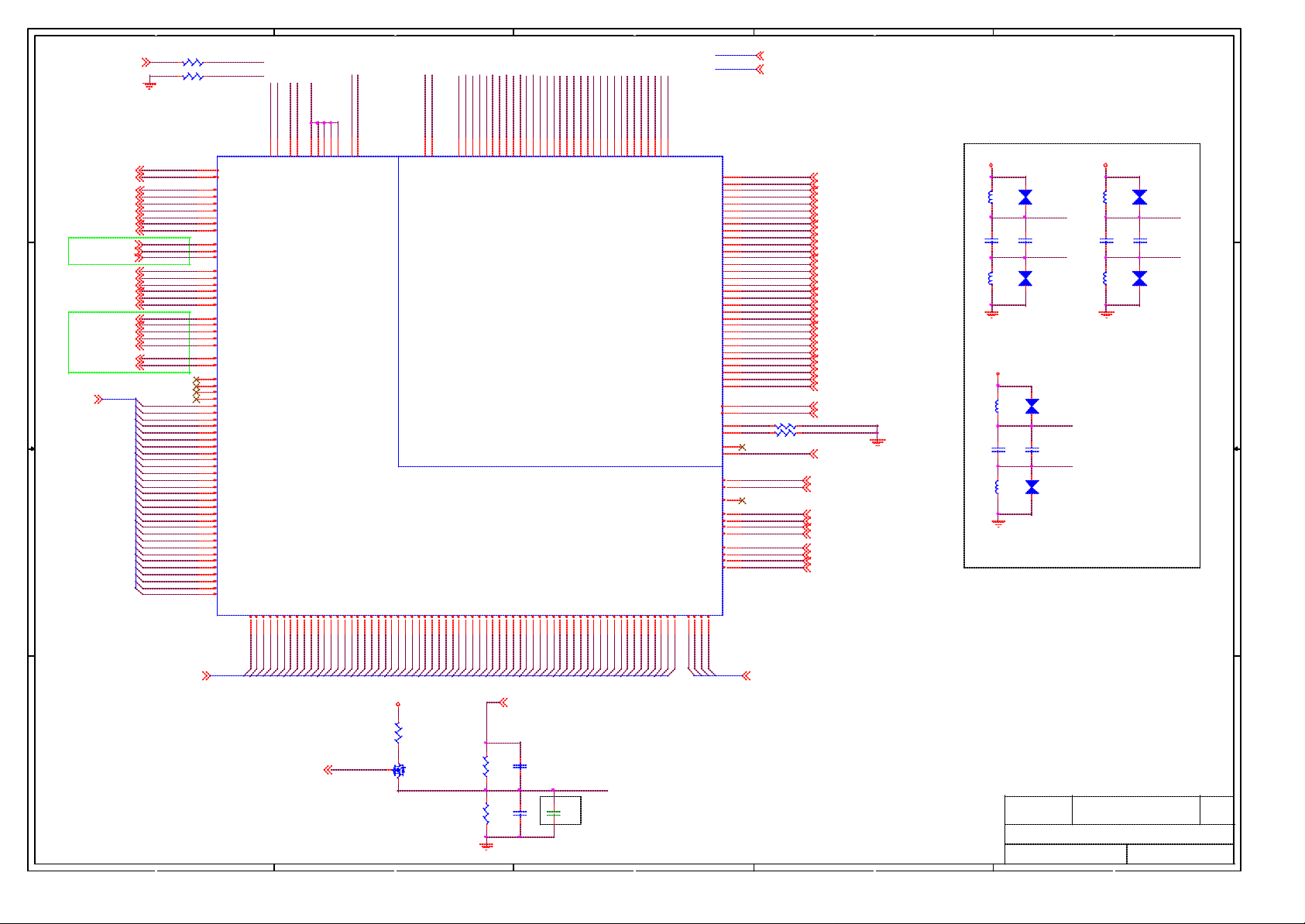

VCC3

VCC3

L39

VCCP

X_80_0805

R230

10K

1 2

VCC3 VCC3

C246

X_10p

VCCM

D D

C C

B B

CP41

X_COPPER

CB88

X_0.1u

R229

10K

Q47

2N3904S

C271

X_4.7U/0805

CB92

0.1u

CB42

0.1u

CB87

0.1u

C72

4.7U/0805

R241

10K

Q48

2N3904S

CB86

CB96

0.1u

0.1u

R234 475RST

FP_RST#4,29,30

CB51

0.1u

CB90

X_0.1u

VCC3

CB53

0.1u

CB95

0.1u

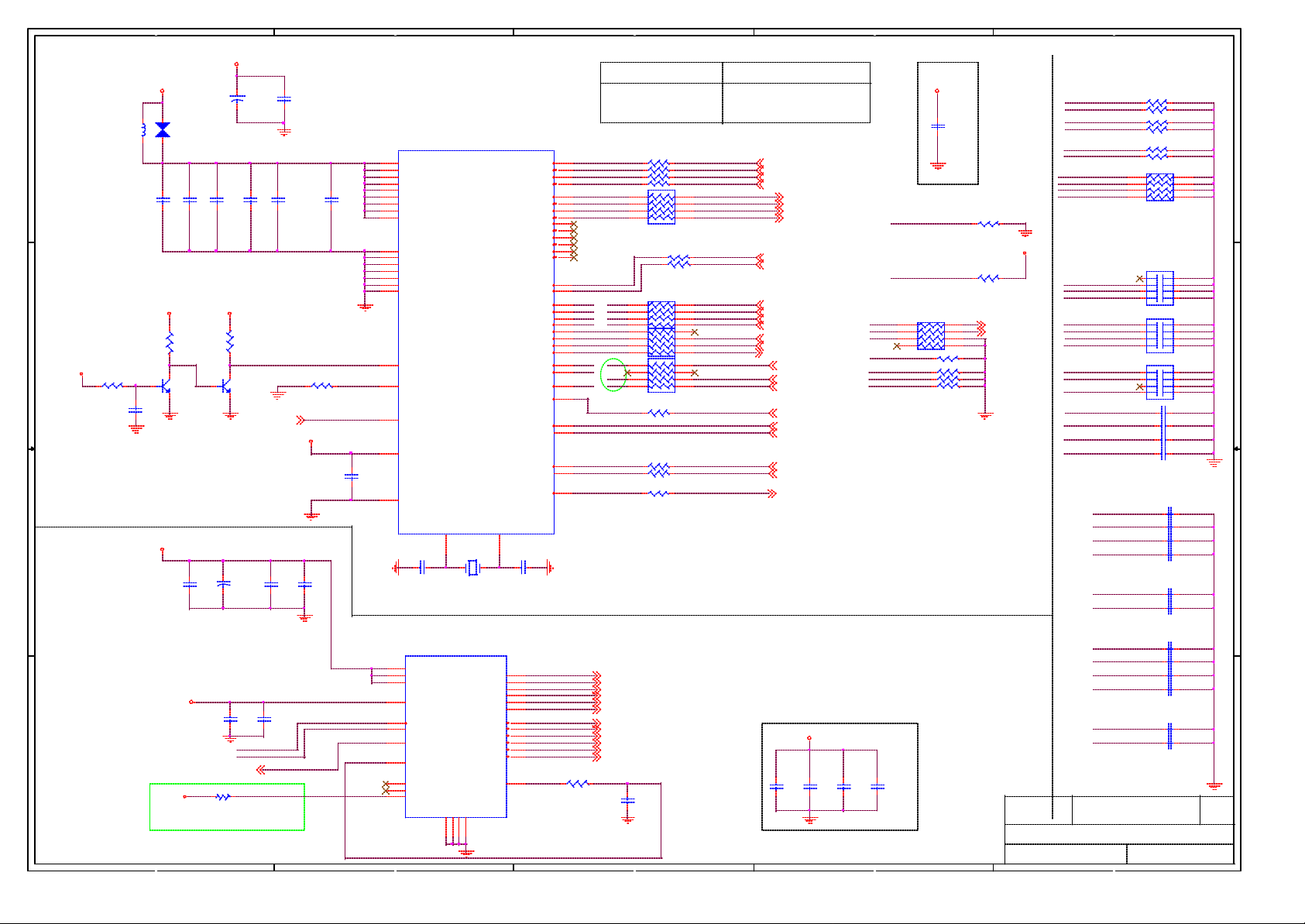

Main Clock Generato r

U17

ICS953401BF_SSOP56

1

VDDREF

11

VDDZ

12

VDDPCI

18

VDDPCI

25

VDD48

29

VDDPE

34

VDDPE

37

VDDPE

56

VDDCPU

5

GNDREF

8

GNDZ

17

GNDPCI

23

GNDPCI

28

GND48

42

GNDPE

53

GNDCPU

50

Vtt_PwrGd/PD#*/(CLK_Stop#)*

44

IREF

24

*(CPU_Stop#)/RESET#

48

VDDA

CB85

102p

45

GNDA

X1

6

C274

27p

Y2

14M-32pf-HC49S-D

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

PECLK0T

PECLK0C

PECLK1T

PECLK1C

PECLK2T

PECLK2C

PECLK3T_F

PECLK3C_F

PECLK4T_F

PECLK4C_F

ZCLK0

ZCLK1

**FS2/PCICLK0

**FS3/PCICLK1

**FS4/PCICLK2

*(PCI_Stop#)/PCICLK3

**Mode/PCICLK4

PECLKREQ#/PCICLK5

Test_mode/PCICLK6_F

PCICLK7_F

*FS0/REF1

**FS1/REF2

24_48MHz/SEL24_48#*

12_48MHz/SEL12_48#**

REF0

SCLK

SDATA

SATACLKT

SATACLKC

X2

7

C261

27p

FS2

0

0

0 133

0

0

55

54

52

51

CK_PE_SRC1

41

CK_PE_SRC1#

40

CK_PE_SRC2

39

CK_PE_SRC2#

38

36

35

33

32

31

30

9

10

13

14

15

16

19

20

21

22

3

4

REF0

2

27

43

49

47

46

26

R247

R248

R249

R250 33

1 2

3 4

5 6

7 8

RN50

8P4R-33

R282 22

R283

RN53

FS2

FS3

FS4

PCLK

MODE

PECLKREQ#

TMODE

FS0

FS1

MULTISEL

SEL12_48 OSC12

8P4R-33

PCLK

1 2

FS4

3 4

FS3

5 6

7 8

FS2

7 8

5 6

3 4

1 2

REF0 DCLK

7 8

5 6

FS0 REFCLK1 REFCLK1

3 4

FS1 REFCLK2

1 2

RN52 8P4R-33

R285

R245

R246

R284 22

FS0

FS1FS4

0 100

0

33

33

33

22

33

33

CPU

100

1

110 10 133 66 33100200

CPUCLK1

CPUCLK-1

CPUCLK0

CPUCLK-0

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

ZCLK0

ZCLK1

22

96XPCLK

SIOPCLK

LAN_PCLK

FWH_CLK

PCICLK1

PCICLK2

PCICLK3PCICLKF

RN54 8P4R-33

48MHz

SIO48M

SMBCLK

SMBDAT

SATACLK

SATACLK-

12MHz

SRC

ZCLK

AGP

661

133

66

133

100

CPUCLK1 7

CPUCLK-1 7

CPUCLK0 4

CPUCLK-0 4

CK_PE_100M_MCH 7

CK_PE_100M_MCH# 7

CK_PE_100M_16PORT 21

CK_PE_100M_16PORT# 21

ZCLK0 10

ZCLK1 13

96XPCLK 13

SIOPCLK 27

LAN_PCLK 18

FWH_CLK 27

PCICLK1 19

PCICLK2 19

PCICLK3 19,30

DCLK 10

REFCLK1 14

REFCLK2 22

SIO48M 27

SMBCLK 11,14,18,21,27,29

SMBDAT 11,14,18,21,27,29

SATACLK 15

SATACLK- 15

OSC12 15

PCIFS3

331

33

MULTISEL internal Pull-Up 120K

MULTISEL

SEL12_48

RN51

10K_8P4R

1 2

FS0

FS1

3 4

FS2

5 6

7 8

MODE

FS3

FS4

PECLKREQ#

VCC3

CB48

X_0.1u

EMI

R286 10K

0=48MHZ,1=24MHZ

R290 10K

0=48MHZ,1=12MHZ

R373 X_10K

R293 10K

R291 10K

R289 10K

VCC3

H_FSBSEL0 4,5

H_FSBSEL1 4,5,10

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SATACLK

SATACLK-

CK_PE_100M_MCH

CK_PE_100M_MCH#

CK_PE_100M_16PORT

CK_PE_100M_16PORT#

PCICLK3

PCICLK2

PCICLK1

FWH_CLK

LAN_PCLK

SIOPCLK

96XPCLK

REFCLK2

DCLK

SIO48M

OSC12

ZCLK0

ZCLK1

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK8

DDRCLK7

R239

R240

R237 49.9RST

R238

R232 49.9RST

R233 49.9RST

49.9RST

49.9RST

49.9RST

RN48

1 2

3 4

5 6

7 8

8P4R-51R

CN9 X_8P4C_10p

1 2

3 4

5 6

7 8

CN8 X_8P4C_10p

7 8

5 6

3 4

1 2

CN7 X_8P4C_10p

1 2

3 4

5 6

7 8

C294 X_10p

C293 X_10p

C291 X_10p

C292 X_10p

C96 X_10p

C68 X_10p

C74 X_10p

C98 X_10p

C66 X_10p

C64 X_10p

U7

CBVDD

VCCM

A A

VCC3

5

FWDSDCLKO8

R86 X_4.7K

option mounted

for RTM680-627

CB46

X_0.1u

SMBCLK

SMBDAT

CB52

0.1u

FWDSDCLKO

D2#/D6_SEL

12

23

10

22

20

18

21

4

3

7

8

9

ICS93732

VDD

VDD

VDD

AVDD

SCLK

SDATA

CLK_IN

FB_IN

NC

NC

NC

6

GND

111528

GND

GND

GND

Clock Buffer (DDR)

DDRCLK0

2

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

FB_OUT

DDRCLK3

4

DDRCLK2

13

17

DDRCLK1

DDRCLK8

24

DDRCLK7

26

DDRCLK-0

1

5

DDRCLK-3

DDRCLK-2

14

DDRCLK-1

16

DDRCLK-8

25

DDRCLK-7

27

R87

19

DDRCLK0 11

DDRCLK3 11

DDRCLK2 11

DDRCLK1 11

DDRCLK8 11

DDRCLK7 11

DDRCLK-0 11

DDRCLK-3 11

DDRCLK-2 11

DDRCLK-1 11

DDRCLK-8 11

DDRCLK-7 11

10

FB_OUT

C67

10p

3

CB43

X_0.1u

VCC3

CB50

X_0.1u

FOR EMI

CB40

X_0.1u

CB56

X_0.1u

Micro-Star

Document Number

Last Revision Date:

2

Wednesday, February 23, 2005

DDRCLK-0

DDRCLK-1

DDRCLK-2

DDRCLK-3

DDRCLK-8

DDRCLK-7

Title

C97 X_10p

C69 X_10p

C75 X_10p

C99 X_10p

C65 X_10p

C63 X_10p

MS7138

MAIN CLOCK GEN & BUFFER

Sheet of

1

3 32

Rev

100

8

D D

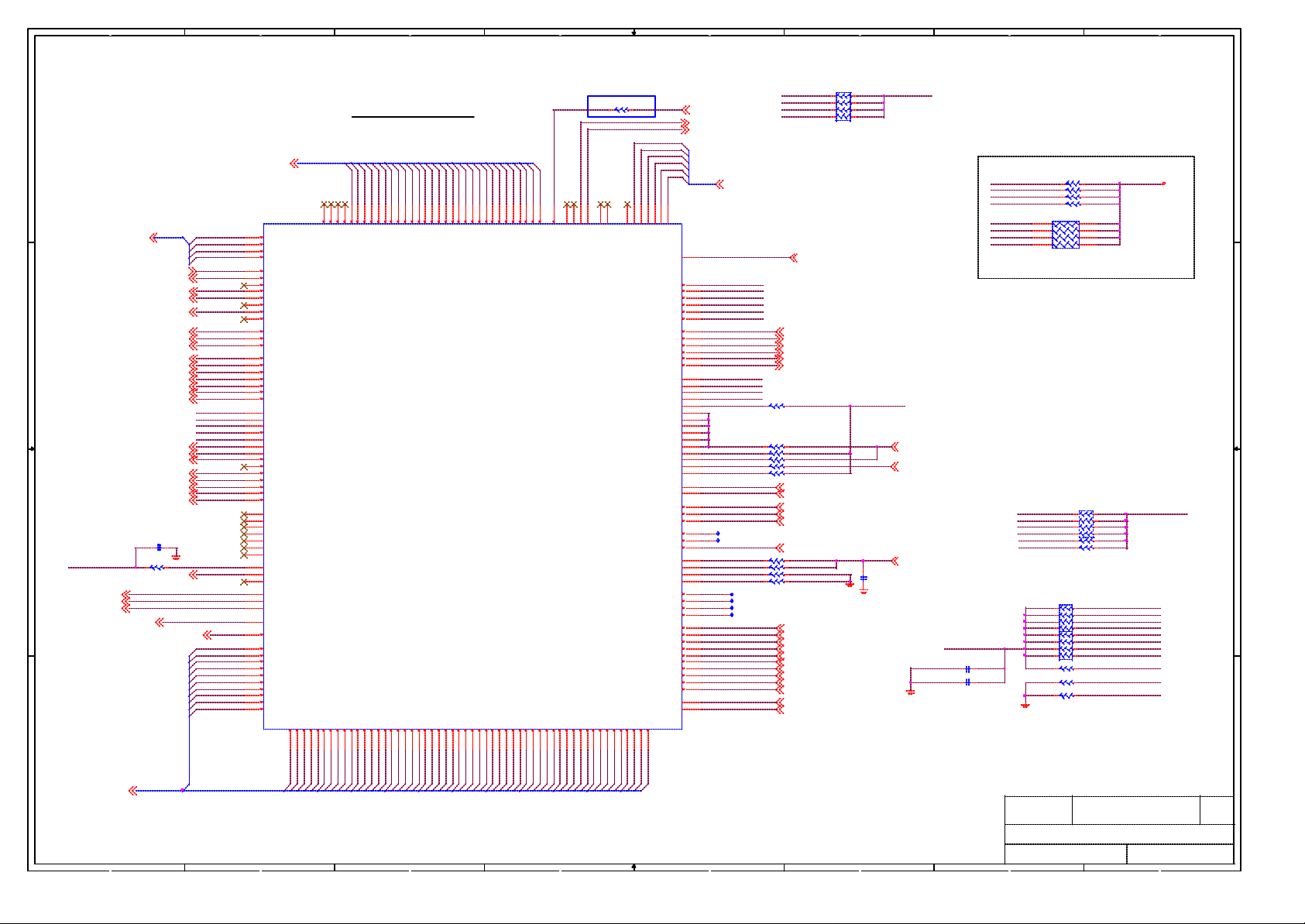

HDBI#[0..3]7

C C

CPU_TMPA27

VTIN_GND27

THERMTRIP#5,14

PROCHOT#5,14

HD#[0..63]7

C35 X_C0.1U25Y

R65 X_1KR

H_PWRGD5,7

HD#[0..63]

8

B B

VTT_OUT_RIGHT

H_FSBSEL03,5

H_FSBSEL13,5,10

H_FSBSEL25

A A

HDBI#0

HDBI#1

HDBI#2

HDBI#3

EDRDY#

EDRDY#7

IERR#5

FERR#5,14

STPCLK#14

HINIT#14

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HIT#7

HITM#7

HBPRI#7

HDEFER#7

CPUSLP#14

LL_ID031

H_TDI

H_TDO

H_TMS

H_TRST#

H_TCK

IGNNE#14

SMI#14

A20M#14,27

CPU_BOOT

LL_ID0 H_COMP1

H_PWRGD

CPURST#5,7

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31]7

G11

D19

C20

AD3

AD1

AC1

AG1

AH2

G10

D16

G29

H30

G30

G23

C21

C18

7

A8

F2

AB2

AB3

R3

M3

P3

H4

B2

C1

E3

D2

C3

C2

D4

E4

G8

G7

AF1

AE1

AL1

AK1

M2

AE8

AL2

N2

P2

K3

L2

N5

AE6

C9

A20

Y1

V2

AA2

N1

B22

A22

A19

B19

B21

B18

A17

B16

7

U6A

DBI0#

DBI1#

DBI2#

DBI3#

EDRDY#

IERR#

MCERR#

FERR#/PBE#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RSVD

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

BOOTSELECT

LL_ID0

LL_ID1

BSEL0

BSEL1

BSEL2

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

B15

HD#53

HA#[3..31]

D52#

D51#

C14

C15

HD#52

HD#51

D50#

A14

HD#50

CPU SIGNAL BLOCK

HA#31

HA#30

AJ6

AJ5

AH5

AH4

AG5

AG4

A35#

A34#

A33#

A32#

A31#

A30#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D17

D20

G22

D22

E22

G21

F21

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HA#29

AG6

A29#

D42#

E21

HD#42

HA#28

AF4

A28#

D41#

F20

HD#41

6

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

AF5

AB4

AC5

AB5

AA5

AD6

AA4Y4Y6W6AB6W5V4V5U4U5T4U6T5R4M4L4M5P6L5

A27#

A26#

A25#

A24#

A23#

A22#

A21#

A20#

A19#

A18#

A17#

D40#

D39#

D38#

D37#

D36#

D35#

D34#

D33#

D32#

D31#

D30#

E19

E18

F18

F17

G17

G18

E16

E15

G16

G15

F15

G14

HD#36

HD#30

HD#29

HD#38

HD#37

HD#35

6

HD#34

HD#33

HD#32

HD#31

HD#40

HD#39

HA#15

A16#

D29#

F14

HD#28

HA#14

A15#

D28#

G13

HD#27

HA#13

A14#

D27#

E13

HD#26

HA#12

A13#

D26#

D13

HD#25

HA#11

A12#

D25#

F12

HD#24

HA#10

HA#9

HA#8

HA#7

A9#

A8#

A11#

A10#

D24#

D23#

D22#

D21#

F11

D10

E10D7E9F9F8G9D11

HD#23

HD#22

HD#21

HD#20

HA#6

A7#

D20#

HD#19

HA#5

A6#

D19#

HD#18

HA#4

A5#

D18#

HD#17

HA#3

A4#

D17#

HD#16

A3#

D16#

HD#15

AC2

D15#

C12

HD#14

5

AN3

DBR#

D14#

D13#

B12D8C11

HD#13

HD#12

5

RSVD

D12#

R59 X1KR

VSS_SENSE

VCC_SENSE

AN4

AN5

AN6

AJ3

RSVD

VCC_SENSE

VSS_SENSE

D11#

D10#

D9#

D8#

B10

A11

A10A7B7B6A5C6A4C5B4

HD#7

HD#9

HD#8

HD#11

HD#10

AK3

ITP_CLK1

ITP_CLK0

D7#

D6#

D5#

HD#6

HD#5

HD#4

AM5

D4#

HD#3

VID5

AL4

RSVD

D3#

HD#2

VID3

VID4

AK4

AL6

VID5#

VID4#

LINT0/INTR

D2#

D1#

HD#0

HD#1

VID0

VID1

VID2

AM3

AL5

AM2

VID3#

VID2#

VID1#

VID0#

H1

GTLREF

AG3

BPM5#

AF2

BPM4#

AG2

BPM3#

AD2

BPM2#

AJ1

BPM1#

AJ2

BPM0#

G5

PCREQ#

J6

REQ4#

K6

REQ3#

M6

REQ2#

J5

REQ1#

K4

REQ0#

W2

TESTHI12

P1

TESTHI11

H5

TESTHI10

G4

TESTHI9

G3

TESTHI8

F24

TESTHI7

G24

TESTHI6

G26

TESTHI5

G27

TESTHI4

G25

TESTHI3

F25

TESTHI2

W3

TESTHI1

F26

TESTHI0

AK6

RSVD

G6

RSVD

G28

BCLK1#

F28

BCLK0#

A3

RS2#

F5

RS1#

B3

RS0#

U3

AP1#

U2

AP0#

F3

BR0#

R1

COMP3

G2

COMP2

T1

COMP1

A13

COMP0

J17

DP3#

H16

DP2#

H15

DP1#

J16

DP0#

AD5

ADSTB1#

R6

ADSTB0#

C17

DSTBP3#

G19

DSTBP2#

E12

DSTBP1#

B9

DSTBP0#

A16

DSTBN3#

G20

DSTBN2#

G12

DSTBN1#

C8

DSTBN0#

L1

LINT1/NMI

K1

D0#

ZIF-SOCK775-15u

4

FP_RST# 3,29,30

VCC_SENSE 31

VSS_SENSE 31

VID[0..5] 31

CPU_GTLREF

H_BPM#5

H_BPM#4

H_BPM#3

H_BPM#2

H_BPM#1

H_BPM#0

PCREQ#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

H_TESTHI12

H_TESTHI11

H_TESTHI10

H_TESTHI9

H_TESTHI8

H_TESTHI2_7

H_TESTHI1

H_TESTHI0

RSVD_AK6

RSVD_G6

HRS#2

HRS#1

HRS#0

T1

T2

BREQ#0

H_COMP3

H_COMP2

H_COMP0

T7

T8

T6

T5

HADSTB#1

HADSTB#0

HDSTB3

HDSTB2

HDSTB1

HDSTB0

HDSTB#3

HDSTB#2

HDSTB#1

HDSTB#0

NMI

INTR

4

H_TESTHI9

1 2

H_TESTHI10

3 4

H_TESTHI11

5 6

H_TESTHI12

7 8

CPU_GTLREF 5

PCREQ# 7

HREQ#4 7

HREQ#3 7

HREQ#2 7

HREQ#1 7

HREQ#0 7

R80 62R

R95 62R

R63 62R

R99 62R

R53 X_62R

R79 X_62R

CPUCLK-0 3

CPUCLK0 3

HRS#2 7

HRS#1 7

HRS#0 7

BREQ#0 5,7

R67 100R1%

R81 100R1%

R66 60.4R1%

R89 60.4R1%

PLACE RESISTORS OUTSIDE SOCKET

CAVITY IF NO ROOM FOR VARIABLE

RESISTOR DON'T PLACE

HADSTB#1 7

HADSTB#0 7

HDSTB3 7

HDSTB2 7

HDSTB1 7

HDSTB0 7

HDSTB#3 7

HDSTB#2 7

HDSTB#1 7

HDSTB#0 7

NMI 14

INTR 14

3

RN12

8P4R-62R

VTT_OUT_LEFT

3

VTT_OUT_LEFT

V_FSB_VTT 5,7,9,16,29

VTT_OUT_RIGHT 5

VTT_OUT_LEFT 5

C49

X_C0.1U25Y

CLOSED TO 965

VTT_OUT_RIGHT

C41 C0.1U25Y

C45 C0.1U25Y

2

STPCLK#

HINIT#

SMI#

CPUSLP#

A20M#

INTR

NMI

IGNNE#

R73 49.9RST

R71 49.9RST

R69 49.9RST

R75 49.9RST

RN15

7 8

5 6

3 4

1 2

8P4R-56

RN2

8P4R-680R

VID3

1

VID1

3

5

VID4

VID2

7

VID0

R51 680R

VID5

R50 680R

RN4 8P4R-51R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

RN6 8P4R-51R

R61 X49.9R1%

R57 X49.9R1%

R56 49.9R1%

PLACE BPM TERMINATION NEAR CPU

Micro-Star

Document Number

Last Revision Date:

Wednesday, February 23, 2005

2

Title

For 965

VTT_OUT_RIGHT

2

4

6

8

H_BPM#3

H_BPM#5

H_BPM#1

H_BPM#0

H_TDI

H_BPM#2

H_BPM#4

H_TDO

H_TMS

H_TCK

H_TRST#

MS7138

LGA775 CPU-1

Sheet of

1

VCCP

4 32

1

Rev

100

8

VCCP

AG21

AG19

AG18

AG15

AG14

AG12

AG11

AF9

AF8

AF22

AF21

AF19

AF18

AF15

AF14

AF12

AF11

AE23

AE22

AE21

AE19

AE18

AE15

AE14

AE12

AE11

AD8

AD30

AD29

AD28

AD27

AD26

AD25

AD24

AD23

AC8

AC30

AC29

AC28

AC27

AC26

AC25

AC24

AC23

U6B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AE9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AB8

VCC

AA8

VCC

VCC

VCC

VCC

Y29

Y30

Y8

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

W30W8Y23

Y24

Y25

Y26

Y27

Y28

VCCP

D D

C C

100 OHMS OVER 210 OHMS RESISTORS

VTT_OUT_LEFT CPU_GTLREF

B B

GTLREF VOLTAGE SHOULD BE

0.67*VTT = 0.8V

R78 49.9R1%

AG25

AG22

VCC

VCC

VCC

VCC

W28

W29

R74

100R1%

VCC

VCC

AG26

W27

VCC

VCC

AG27

W26

VCC

VCC

AG28

W25

AG29

VCC

VCC

W24

7

AG8

AG30

VCC

VCC

VCC

VCC

W23

C55

C0.1U25Y

6

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

AG9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

U26

U27

U28

U29

U30U8V8

VCC

VCC

VCC

VCC

VCC

VCC

U24

U25

C57

C220P50N

AH28

AH29

AH30

AH8

AH9

AJ11

AJ12

AJ14

AJ15

AJ18

AJ19

AJ21

AJ22

AJ25

AJ26

AJ8

AJ9

AK11

AK12

AK14

AK15

AK18

AK19

AK21

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

M25

M26

M27

M28

M29

M30M8N23

N24

N25

N26

N27

N28

N29

N30N8P8R8T23

T24

T25

T26

T27

T28

T29

T30T8U23

CPU_GTLREF 4

AK22

M24

VCC

VCC

AK25

M23

AK26

VCC

VCC

5

AK8

AK9

AL11

AL12

AL14

AL15

AL18

AL19

AL21

AL22

AL25

AL26

AL29

AL30

AL8

AL9

AM11

AM12

AM14

AM15

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J22

J23

J24

J25

J26

J27

J28

J29

J30J8J9

K23

K24

K25

K26

K27

K28

K29

K30K8L8

V_FSB_VTT

4

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCA

VSSA

RSVD

VCC-IOPLL

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTPWRGD

VTT_OUT

VTT_OUT

VTT_SEL

RSVD/VTT_PKGSENSE

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

AN9

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

PLACE COMPONENTS AS CLOSE AS POSSIBLE TO PROCESSOR SOCKET

TRACE WIDTH TO CAPS MUST BE SMALLER THAN 12MILS

L9 X_10U100m_0805

CP6

X_COPPER

HS1

HS2

HS3

HS4

AN25

AN26

AN29

AN30

AN8

123

4

3

A23

H_VCCA

H_VSSA

B23

D23

H_VCCA

C23

A25

A26

A27

A28

A29

A30

B25

B26

B27

B28

B29

B30

C25

C26

C27

C28

C29

C30

D25

D26

D27

D28

D29

D30

AM6

VTT_PWG

VTT_OUT_RIGHT

AA1

VTT_OUT_LEFT

J1

F27

F29

ZIF-SOCK775-15u

VTT_SEL

R103 X_1KR

C70

C10U10Y1206

V_FSB_VTT

VCC3

TEJ/PSC

0

1

RSVD

H_VSSA

C76

X_C1U10Y

H_VCCA

2

V_FSB_VTT

C71 C1U16Y0805

C81 10u/0805

C80 X_10u/0805

1

CAPS FOR FSB GENERIC

VTT_OUT_LEFT

5VSB

R40

PLACE AT CPU END OF ROUTE

VTT_OUT_RIGHT4

VTT_OUT_LEFT4

VTT_OUT_RIGHT

VTT_OUT_LEFT

R52 120R

R72 100R

R82 62R

PLACE AT ICH END OF ROUTE

A A

V_FSB_VTT4,7,9,16,29

V_FSB_VTT

8

RN49

1 2

3 4

5 6

7 8

8P4R-62R

R107 62R

PROCHOT#

H_PWRGD

BREQ#0

FERR#

THERMTRIP#

IERR#

CPURST#

7

PROCHOT# 4,14

H_PWRGD 4,7

BREQ#0 4,7

FERR# 4,14

THERMTRIP# 4,14

IERR# 4

CPURST# 4,7

FSBSEL RESISTOR CAN BE REMOVED IF ONLY TEJAS

AND CEDAR MILL ARE SUPPORTED

RN27

1

2

V_FSB_VTT

6

5

3

5

7

8P4R-470R

H_FSBSEL1

H_FSBSEL2

4

H_FSBSEL0

6

8

4

VID_GD29,31

H_FSBSEL1 3,4,10

H_FSBSEL2 4

H_FSBSEL0 3,4

1KR

R45

1KR

R42

680R

Q13

N-MMBT3904_SOT23

3

1.25V VTT_PWRGOOD

VTT_PWG

Micro-Star

Document Number

Last Revision Date:

Wednesday, February 23, 2005

2

Title

MS7138

LGA775 CPU-1

Sheet of

5 32

1

Rev

100

5

4

3

GTLREF_SEL 7

2

1

D D

AC4

AE3

AE4D1D14

U6C

RSVD

RSVD

A12

A15

A18

A2

A21

A24

A6

A9

AA23

AA24

AA25

AA26

AA27

AA28

AA29

AA3

AA30

AA6

AA7

C C

B B

AB23

AB24

AB25

AB26

AB27

AB28

AB29

AB30

AC3

AC6

AC7

AD4

AD7

AE10

AE13

AE16

AE17

AE20

AE24

AE25

AE26

AE27

AE28

AB1

AB7

AE2

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE29

AE30

AE5

AE7

AF10

T9

T11

T12

T10

E23

E24E5E6E7F23F6B13H2J2J3N4P5T2V1W1Y3Y7Y5Y2W7W4V7V6

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF13

AF16

AF17

AF20

AF23

AF24

AF25

AF26

RSVD

VSS

AF27

RSVD

VSS

AF28

T4

RSVD

VSS

AF29

RSVD

COMP4

VSS

VSS

AF3

AF30

RSVD

VSS

AF6

T3

RSVD

VSS

AF7

RSVD

COMP5

VSS

VSS

AG10

AG13

RSVD

VSS

AG16

RSVD

VSS

AG17

VSS

AG20

VSS

AG23

VSS

VSS

AG24

V30V3V29

V28

V27

V26

V25

V24

V23U7U1T7T6T3R7R5R30

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AH7

AJ10

AJ13

AJ16

AJ17

R29

R28

R27

R26

R25

R24

R23R2P7P4P30

P29

P28

P27

P26

P25

P24

P23N7N6N3M7M1L7L6L30L3L29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AJ7

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

VSS

VSS

AL23

VSS

VSS

AL24

VSS

VSS

AL27

VSS

VSS

AL28

L28

L27

L26

L25

L24

L23K7K5

VSS

VSS

AM13

VSS

VSS

AM16

VSS

VSS

AM17

VSS

VSS

AM20

VSS

VSS

AM23

VSS

VSS

AM24

VSS

VSS

AM27

VSS

VSS

AM28

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL3

AL7

AM1

AM10

H29H3H6H7H8H9J4J7K2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GTLREF_SEL

VSS

VSS

VID7#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VID_SELECT

VSS

VSS

AM4

AM7

AN1

AN10

AN13

AN16

AN17

AN2

AN20

AN23

AN24

AN27

AN28

AN7B1B11

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCK775-15u

B14

H14

H13

H12

H11

H10

G1

F7

F4

F22

F19

F16

F13

F10

E8

E29

E28

E27

E26

E25

E20

E2

E17

E14

E11

D9

D6

D5

D3

D24

D21

D18

D15

D12

C7

C4

C24

C22

C19

C16

C13

C10

B8

B5

B24

B20

B17

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

A A

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, February 23, 2005

MS7138

LGA775 CPU-1

Sheet of

1

Rev

100

6 32

5

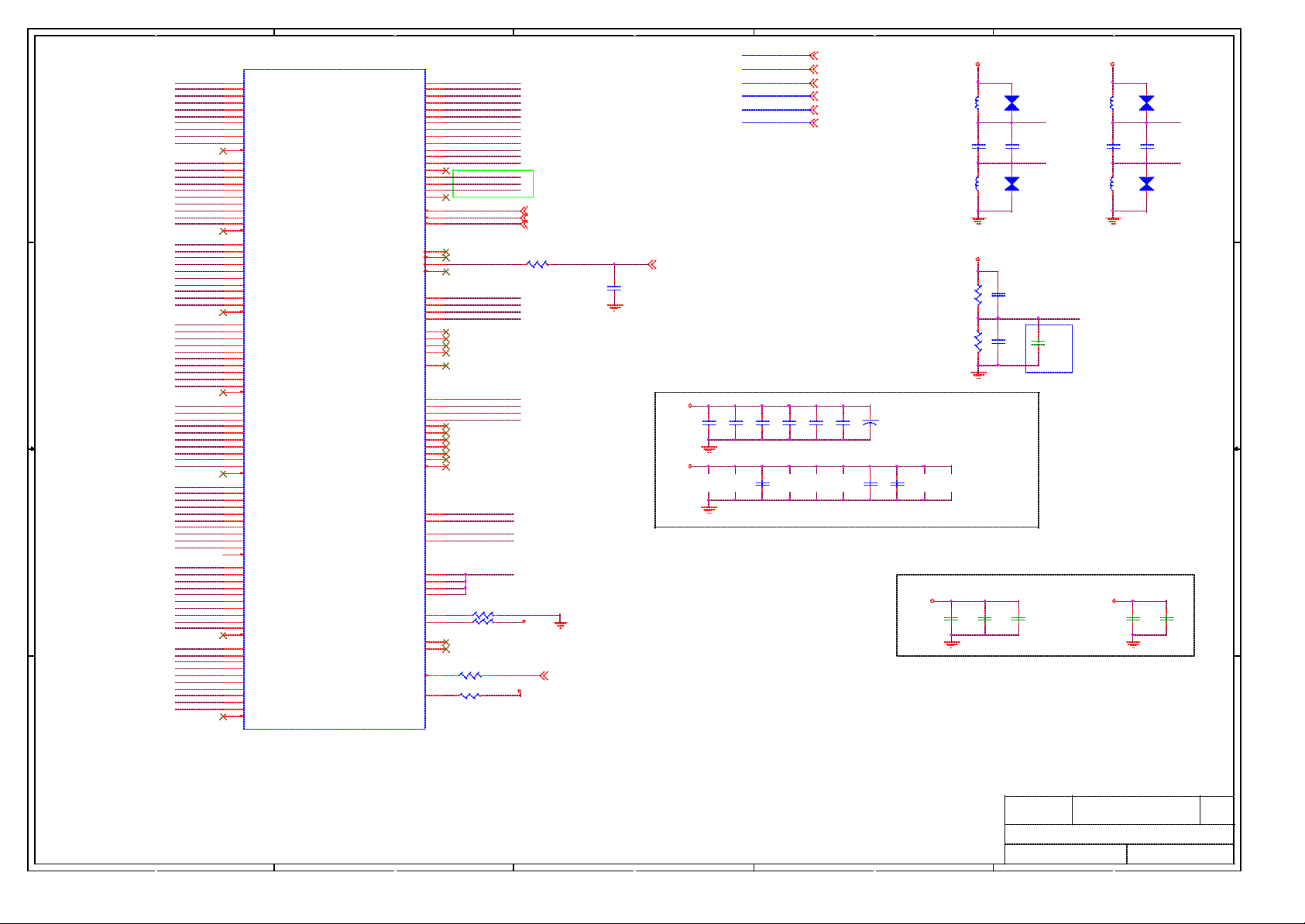

D34

C33

D32

C31

D35

C36

G29

D29

D33

H36

H35

H34

H32

G36

G33

H30

G32

H33

G31

D36

D31

H29

A12

B12

B31

J28

A34

B17

J27

B35

A31

B34

E30

B33

A33

A32

E29

J33

K28

L28

L29

J36

K29

K30

K32

J31

J30

J32

F36

F33

F35

F32

F34

F31

E32

E36

E33

F30

U12A

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS0#

RS1#

RS2#

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HASTB0#

HASTB1#

HA35#

HA34#

HA33#

HA32#

HA31#

HA30#

HA29#

HA28#

HA27#

HA26#

HA25#

HA24#

HA23#

HA22#

HA21#

HA20#

HA19#

HA18#

HA17#

HA16#

HA15#

HA14#

HA13#

HA12#

HA11#

HA10#

HA9#

HA8#

HA7#

HA6#

HA5#

HA4#

HA3#

649/662

HNCOMP

HPCOMP

A18

HD63#

HD62#

D18

C1XAVSS

F12

HD61#

D20

A20

C1XAVDD

E12

C1XAVSS

C1XAVDD

HD60#

HD59#

HD58#

A19

E18

C4XAVSS

D13

C4XAVSS

HD57#

A21

HVREF

C4XAVDD

C13

P25

M23

M21

M19

M17

HVREF0

HVREF1

HVREF2

HVREF3

C4XAVDD

Host

HD56#

HD55#

HD54#

HD53#

HD52#

HD51#

A22

D22

E20

B23

C23

A23

A24

HVREF4

HD50#

B21

V_FSB_VTT4,5,9,16,29

D D

CPUCLK13

CPUCLK-13

HLOCK#4

HDEFER#4

HTRDY#4

CPURST#4,5

H_PWRGD4,5

HBPRI#4

BREQ#04,5

HRS#04

HRS#14

HRS#24

HADS#4

HDRDY#4

HDBSY#4

HBNR#4

HREQ#04

HREQ#14

HREQ#24

HREQ#34

C C

B B

HREQ#44

HADSTB#04

HADSTB#14

HA#[3..31]4

R122 14R1%

R125 100RST

CPUCLK1

CPUCLK-1

HLOCK#

HDEFER#

HTRDY#

CPURST#

H_PWRGD

HBPRI#

BREQ#0

HRS#0

HRS#1

HRS#2

HADS#

HITM#

HITM#4

HIT#

HIT#4

HDRDY#

HDBSY#

HBNR#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HADSTB#0

HADSTB#1

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HNCOMP

HPCOMP

A16

B16

HPCOMP

HD49#

HD48#

B19

J16

HNCOMP

HD47#

HD46#

E16

H16

HD45#

D16

HD44#

E17

4

HD43#

HD42#

G17

H18

HD41#

J18

HD40#

H20

PCIEAVSS

EXP_A_RXN_0

EXP_A_RXN_1

EXP_A_RXP_1

PERp0

PERn0

PERp1

EXP_A_RXN_3

EXP_A_RXN_2

EXP_A_RXP_2

EXP_A_RXP_3

PERn1

PERp2

PERn2

PERp3

PCIEAVDD

EXP_A_RXP_0

L7L8M5M6N7N8P5P6R7R8T5T6U7U8V5V6W7W8Y5Y6AA7

AJ1

AJ2

PCIEAVDD

PCIEAVSS

PCI Express

HD39#

HD38#

HD37#

HD36#

HD35#

HD34#

HD33#

HD32#

HD31#

HD30#

HD29#

HD28#

HD27#

HD26#

H19

J20

J19

G19

G21

H21

E21

H22

J21

J22

E23

G23

H23

H24

EXP_A_RXN_4

EXP_A_RXN_5

EXP_A_RXP_4

EXP_A_RXP_5

PERn3

PERp4

PERn4

PERp5

PERn5

HD25#

HD24#

HD23#

HD22#

HD21#

E25

H25

J25

H26

EXP_A_RXN_6

EXP_A_RXN_7

EXP_A_RXP_6

EXP_A_RXP_7

EXP_A_RXP_8

PERp6

PERn6

PERp7

PERn7

HD20#

HD19#

HD18#

HD17#

H28

G27

E27

H27

J26

EXP_A_RXN_8

EXP_A_RXN_9

EXP_A_RXP_10

EXP_A_RXP_9

PERp8

PERn8

PERp9

PERn9

PERp10

HD16#

HD15#

HD14#

HD13#

HD12#

A25

D24

E24

A27

EXP_A_RXP_11

EXP_A_RXP_12

EXP_A_RXN_10

EXP_A_RXN_11

EXP_A_RXN_12

AA8

AB5

AB6

AC7

AC8

PERn10

PERp11

PERn11

PERp12

PERn12

HD11#

HD10#

HD9#

HD8#

HD7#

B25

A26

C25

D26

D28

3

EXP_A_RXP_13

EXP_A_RXP_14

EXP_A_RXP_15

EXP_A_RXN_13

EXP_A_RXN_14

AD5

AD6

AF5

AF6

AH4

PERp13

PERn13

PERp14

PERn14

PERp15

HD6#

HD5#

HD4#

HD3#

HD2#

A28

A29

C29

E28

D30

EXP_A_RXN_15

AH5

PERn15

PETp10

PETn10

PETp11

PETn11

PETp12

PETn12

PETp13

PETn13

PETp14

PETn14

PETp15

PETn15

REFCLK+

REFCLK-

PCIERSET0

PCIERSET1

PCREQ#

EDRDY#

HDSTBN3#

HDSTBN2#

HDSTBN1#

HDSTBN0#

HDSTBP3#

HDSTBP2#

HDSTBP1#

HDSTBP0#

DBI3#

DBI2#

HD1#

HD0#

C19

E19

B29

A30

PETp0

PETn0

PETp1

PETn1

PETp2

PETn2

PETp3

PETn3

PETp4

PETn4

PETp5

PETn5

PETp6

PETn6

PETp7

PETn7

PETp8

PETn8

PETp9

PETn9

PME#

INTX#

DBI1#

J23

NC0

DBI0#

C27

EXP_A_TXP_0

M3

EXP_A_TXN_0

N3

N1

EXP_A_TXP_1

EXP_A_TXN_1

P1

EXP_A_TXP_2

P3

EXP_A_TXN_2

R3

EXP_A_TXP_3

R1

T1

EXP_A_TXN_3

EXP_A_TXP_4

T3

EXP_A_TXN_4

U3

EXP_A_TXP_5

U1

EXP_A_TXN_5

V1

V3

EXP_A_TXP_6

EXP_A_TXN_6

W3

EXP_A_TXP_7

W1

EXP_A_TXN_7

Y1

EXP_A_TXP_8

Y3

AA3

EXP_A_TXN_8

EXP_A_TXP_9

AA1

EXP_A_TXN_9

AB1

EXP_A_TXP_10

AB3

EXP_A_TXN_10

AC3

AC1

EXP_A_TXP_11

EXP_A_TXN_11

AD1

EXP_A_TXP_12

AD3

EXP_A_TXN_12

AE3

EXP_A_TXP_13

AE1

AF1

EXP_A_TXN_13

EXP_A_TXP_14

AF3

EXP_A_TXN_14

AG3

EXP_A_TXP_15

AG1

EXP_A_TXN_15

AH1

CK_PE_100M_MCH

L1

CK_PE_100M_MCH#

L2

AH3

AJ3

E11

F11

H_PCREQ#

C35

H_EDRDY#

C34

A17

HDSTB#3

E22

HDSTB#2

H17

J24

HDSTB#1

HDSTB#0

B27

HDSTB3

C21

HDSTB2

J17

G25

HDSTB1

HDSTB0

E26

EXP_A_RXP_[0..15] 21

EXP_A_RXN_[0..15] 21

EXP_A_TXP_0 21

EXP_A_TXN_0 21

EXP_A_TXP_1 21

EXP_A_TXN_1 21

EXP_A_TXP_2 21

EXP_A_TXN_2 21

EXP_A_TXP_3 21

EXP_A_TXN_3 21

EXP_A_TXP_4 21

EXP_A_TXN_4 21

EXP_A_TXP_5 21

EXP_A_TXN_5 21

EXP_A_TXP_6 21

EXP_A_TXN_6 21

EXP_A_TXP_7 21

EXP_A_TXN_7 21

EXP_A_TXP_8 21

EXP_A_TXN_8 21

EXP_A_TXP_9 21

EXP_A_TXN_9 21

EXP_A_TXP_10 21

EXP_A_TXN_10 21

EXP_A_TXP_11 21

EXP_A_TXN_11 21

EXP_A_TXP_12 21

EXP_A_TXN_12 21

EXP_A_TXP_13 21

EXP_A_TXN_13 21

EXP_A_TXP_14 21

EXP_A_TXN_14 21

EXP_A_TXP_15 21

EXP_A_TXN_15 21

CK_PE_100M_MCH 3

R207 499R1%

R208 124R1%

CK_PE_100M_MCH# 3

INTA# 10,13,19

PCREQ# 4

EDRDY# 4

HDSTB#3 4

HDSTB#2 4

HDSTB#1 4

HDSTB#0 4

HDSTB3 4

HDSTB2 4

HDSTB1 4

HDSTB0 4

2

VCC1_8 VCC1_8

L20

CP13

X_COPPER

C1XAVDD

X_80S/0603

CB68

C124

0.1u

X_103P

C1XAVSS

CP14

L21

X_COPPER

X_80S/0603

VCC1_8

CP9

L17

X_COPPER

C4XAVDD

X_80S/0603

CB63

C118

0.1u

X_103P

C4XAVSS

CP8

L15

X_80S/0603

X_COPPER

1

L36

X_80S/0603

C223

X_103P

L35

X_80S/0603

CP29

X_COPPER

PCIEAVDD

CB84

0.1u

PCIEAVSS

CP28

X_COPPER

Closed to SIS649

HD#34

HD#33

HD#32

R102

169R1%

HD#31

HD#30

HD#29

HD#28

HD#23

HD#24

HD#25

HD#20

HD#27

HD#21

HD#22

HD#26

V_FSB_VTT 4,5,9,16,29

C89

R93

X_103P

100R1%

C100

0.1u

HD#19

HD#12

HD#15

HD#13

HD#18

HD#14

HD#17

HD#16

HVREF

C377

0.1u

Please this capacitor

under 649/662 solder side.

HD#11

HD#10

HD#9

HD#8

HD#7

HD#6

3

HD#5

HD#4

HD#3

HD#2

HD#1

HD#0

HDBI#2

HDBI#3

HDBI#0

HDBI#1

HDBI#[0..3] 4

Title

Micro-Star

Document Number

Last Revision Date:

2

Wednesday, February 23, 2005

MS7138

SIS 649-Host & AGP

Sheet of

1

Rev

100

7 32

HD#54

HD#56

HD#59

HD#62

HD#58

HD#61

HD#60

HD#63

HD#[0..63]4

A A

5

GTLREF_SEL6

HD#57

HD#55

HD#53

HD#52

HD#50

HD#49

HD#48

HD#46

HD#47

HD#43

VCCP

HD#41

HD#42

4

HD#40

R104

619R1%

2N7002S

Q27

HD#38

HD#37

HD#36

HD#35

HD#39

HD#44

HD#45

HD#51

5

M34

N36

R36

R33

M36

M35

N33

N32

W36

R32

U36

U32

U33

AB35

AB34

W33

W32

AA32

AB36

AA33

AA36

AH30

AJ32

AM30

AN30

AG29

AH32

AM32

AN32

AJ30

AL32

AK32

AH24

AH23

AH21

AM20

AJ24

AJ23

AJ21

AH22

AM22

AJ22

AK22

AM19

AT18

AT16

AR16

AT19

AN19

AN17

AM17

AR18

AT17

AP18

AN15

AM15

AM13

AT12

AP16

AT15

AT13

AN13

AT14

AP14

AR14

AT11

AN11

AR9

AR12

AP12

AP10

AM11

AR10

AT10

U12B

MD0A

MD1A

MD2A

MD3A

MD4A

MD5A

P35

MD6A

P34

MD7A

DQM0A

P36

DQS0A

DQS0A#

T35

MD8A

T34

MD9A

V34

MD10A

MD11A

MD12A

T36

MD13A

V36

MD14A

V35

MD15A

DQM1A

DQS1A

DQS1A#

Y36

MD16A

Y35

MD17A

MD18A

MD19A

MD20A

MD21A

MD22A

MD23A

Y34

DQM2A

DQS2A

DQS2A#

MD24A

MD25A

MD26A

MD27A

MD28A

MD29A

MD30A

MD31A

DQM3A

DQS3A

DQS3A#

MD32A

MD33A

MD34A

MD35A

MD36A

MD37A

MD38A

MD39A

DQM4A

DQS4A

DQS4A#

MD40A

MD41A

MD42A

MD43A

MD44A

MD45A

MD46A

MD47A

DQM5A

DQS5A

DQS5A#

MD48A

MD49A

MD50A

MD51A

MD52A

MD53A

MD54A

MD55A

DQM6A

DQS6A

DQS6A#

MD56A

MD57A

MD58A

AP9

MD59A

MD60A

MD61A

MD62A

AT9

MD63A

DQM7A

DQS7A

DQS7A#

649/662

RMD0

RMD1

RMD2

RMD3

RMD4

RMD5

RMD6

RMD7

RDQM0

D D

C C

B B

RDQS0

RMD8

RMD9

RMD10

RMD11

RMD12

RMD13

RMD14

RMD15

RDQM1

RDQS1

RMD16

RMD17

RMD18

RMD19

RMD20

RMD21

RMD22

RMD23

RDQM2

RDQS2

RMD24

RMD25

RMD26

RMD27

RMD28

RMD29

RMD30

RMD31

RDQM3

RDQS3

RMD32

RMD33

RMD34

RMD35

RMD36

RMD37

RMD38

RMD39

RDQM4

RDQS4

RMD40

RMD41

RMD42

RMD43

RMD44

RMD45

RMD46

RMD47

RDQM5

RDQS5

RMD48

RMD49

RMD50

RMD51

RMD52

RMD53

RMD54

RMD55

RDQM6

RDQS6

RMD56

RMD57

RMD58

RMD59

RMD60

RMD61

RMD62

RMD63

RDQM7

RDQS7

4

MA0A

MA1A

MA2A

MA3A

MA4A

MA5A

MA6A

MA7A

MA8A

MA9A

MA10A

MA11A

MA12A

MA13A

MA14A

MA15A

NC

NC

RASA#

CASA#

WEA#

NC

NC

FWDSDCLKOA

FWDSDCLKOA#

CS0A#

CS1A#

CS2A#

CS3A#

ODT0A

ODT1A

ODT2A

ODT3A

NC

CKE0A

CKE1A

CKE2A

CKE3A

NC

NC

NC

NC

NC

NC

NC

D1XAVDD

D1XAVSS

D4XAVDD

D4XAVSS

DDRVREF0

DDRVREF1

DDRVREF2

DDRVREF3

DDRCOMP

DDRCOMN

OCDVREFP

OCDVREFN

S3AUXSW#

DRAM_SEL

AP33

AN33

AT34

AR34

AR35

AP34

AP35

AM33

AP36

AN36

AT33

AR32

AP32

AM35

AN34

AM34

AM29

AM36

AT32

AP30

AT31

K36

K35

K34

L36

AM31

AN29

AN31

AT29

AR30

AP28

AT30

AR28

AJ33

AH34

AJ36

AL34

AL33

AH36

AH35

AK34

AL36

AJ34

AK35

AK36

A13

B13

AH28

AJ28

AE19

AE23

AC25

V25

AJ29

AH29

AR8

AT8

R164 22

F13

B11

R171 4.7K

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA11

RMA12

RMA14

RMA15

RMA16

RSRAS#

RSCAS#

RSWE#

RCS-0

RCS-1

RCS-2

RCS-3

CKE0

CKE1

CKE2

CKE3

DLLAVDD

DLLAVSS

DDRAVDD

DDRAVSS

DDRVREF0

R124 36R1%

R123 36R1%

S3AUXSW#

RSRAS# 11,12

RSCAS# 11,12

RSWE# 11,12

R117 22

VCCM

VCCM

FWDSDCLKOFWDSDCLKA

S3AUXSW# 29

C108

10p

3

FWDSDCLKO 3

DIMM DECOUPLING

VCCM

VCCM

C84

X_0.1u

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

RMA[0..16]

RCS-[0..3]

CKE[0..3]

C139

0.1u

C153

0.1u

C44

0.1u

RMD[0..63] 11,12

RDQM[0..7] 11,12

RDQS[0..7] 11,12

RMA[0..16] 11,12

RCS-[0..3] 11,12

CKE[0..3] 11

C159

0.1u

C122

X_1u

C125

X_1u

2

VCC1_8 VCC1_8

CP12

L19

X_COPPER

DLLAVDD DDRAVDD

X_80S/0603

C120

CB66

0.1u

X_103P

DLLAVSS

CP10

X_COPPER

L18

X_80S/0603

VCCM

R109

150RST

R108

150RST

C103

X_4.7U/0805

C22

C168

0.1u

0.1u

Place these capacitors under SIS649 solder side

VCCM VCC1_8

C380

X_0.1u

C107

X_103P

C111

0.01uF

place under 649/662 solder side

C381

C378

X_0.1u

X_0.1u

DDRVREF0

C376

X_0.1u

1

L30

X_80S/0603

C175

X_103P

L29

X_80S/0603

DDRAVSS

C384

X_1u

CP22

X_COPPER

CB82

0.1u

CP20

X_COPPER

C383

X_1u

A A

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, February 23, 2005

MS7138

SIS 649-Memory

Sheet of

1

Rev

100

8 32

5

4

3

2

1

B18

VSS

B20

VSS

B22

VSS

B24

VSS

B26

VSS

B28

VSS

B30

VSS

B32

VSS

C17

VSS

E31

VSS

E35

VSS

F17

VSS

F19

VSS

F21

VSS

F23

VSS

F25

VSS

F27

VSS

F29

VSS

G16

VSS

G18

VSS

G20

VSS

G22

VSS

G24

VSS

G26

VSS

G28

VSS

G30

VSS

G35

VSS

H31

VSS

J29

VSS

J35

VSS

K1

VSS

K7

VSS

K8

VSS

K17

VSS

K19

VSS

K21

VSS

K23

VSS

K25

VSS

K27

VSS

K31

VSS

L3

VSS

L4

VSS

L5

VSS

L6

VSS

L9

VSS

L30

VSS

L32

VSS

L33

VSS

L35

VSS

M1

VSS

M2

VSS

M4

VSS

M7

VSS

M8

VSS

M9

VSS

M27

VSS

M31

VSS

M32

VSS

N2

VSS

N4

VSS

N5

VSS

N6

VSS

N9

VSS

N30

VSS

N35

VSS

P2

VSS

P4

VSS

P7

VSS

P8

VSS

P9

VSS

P27

VSS

P31

VSS

R2

VSS

R4

VSS

R5

VSS

R6

VSS

R9

VSS

R30

VSS

R35

VSS

T2

VSS

T4

VSS

T7

VSS

T8

VSS

T9

VSS

T27

VSS

T31

VSS

U2

VSS

U4

VSS

U5

VSS

U6

VSS

U9

VSS

U30

VSS

U35

VSS

V2

VSS

V4

VSS

V7

VSS

V8

VSS

V9

VSS

V27

VSS

V31

VSS

T16

VSS

T17

VSS

T18

VSS

T19

VSS

T20

VSS

T21

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U21

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V21

VSS

Ground

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

PVDDH

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

A14

VTT

A15

VTT

B14

VTT

B15

VTT

C14

VTT

C15

VTT

D14

VTT

D15

VTT

E14

VTT

E15

VTT

F14

VTT

F15

VTT

G14

VTT

G15

VTT

H14

VTT

H15

VTT

J14

VTT

J15

VTT

K14

VTT

K15

VTT

N15

VTT

N16

VTT

N17

VTT

N18

VTT

N19

VTT

P15

VTT

P16

VTT

P17

VTT

P18

VTT

P19

VTT

Y13

Y14

Y15

AA13

AA14

AA15

AB13

AB14

AB15

AC13

AC14

AC15

AD13

AD14

AD15

AD9

AE8

AE9

AF8

AF9

AG7

AG8

AG9

AH7

AH8

AH9

AJ6

AJ7

AJ8

AJ9

AK6

AK7

AK8

AK9

AL6

AL7

AL8

AL9

AM7

AM8

AN2

AN5

AN7

AP1

AR3

AR4

AT5

R15

R16

R17

R18

R19

R20

R21

T15

U15

V15

W15

N13

N14

P13

P14

R13

R14

T13

T14

U13

U14

V13

V14

W13

W14

V23

VCCM

V24

VCCM

W23

VCCM

W24

VCCM

D D

C C

B B

A A

Y23

VCCM

Y24

VCCM

AA23

VCCM

AA24

VCCM

AB23

VCCM

AB24

VCCM

AC19

VCCM

AC20

VCCM

AC21

VCCM

AC22

VCCM

AC23

VCCM

AC24

VCCM

AD19

VCCM

AD20

VCCM

AD21

VCCM

AD22

VCCM

AD23

VCCM

AD24

VCCM

AG34

VCCM

AG35

VCCM

AN35

VCCM

AP31

VCCM

AR21

VCCM

AR23

VCCM

AR25

VCCM

AR27

VCCM

AR29

VCCM

AR31

VCCM

AR33

VCCM

N20

IVDD

N21

IVDD

N22

IVDD

N23

IVDD

N24

IVDD

P20

IVDD

P21

IVDD

P22

IVDD

P23

IVDD

P24

IVDD

R22

IVDD

R23

IVDD

R24

IVDD

T22

IVDD

T23

IVDD

T24

IVDD

U22

IVDD

U23

IVDD

U24

IVDD

V22

IVDD

W22

IVDD

Y22

IVDD

AA22

IVDD

AB16

IVDD

AB17

IVDD

AB18

IVDD

AB19

IVDD

AB20

IVDD

AB21

IVDD

AB22

IVDD

AC16

IVDD

AC17

IVDD

AC18

IVDD

AD16

IVDD

AD17

IVDD

AD18

IVDD

H7

VDDVB1.8

H8

VDDVB1.8

H9

VDDVB1.8

J7

VDDVB1.8

J8

VDDVB1.8

J9

VDDVB1.8

K9

VDDVB1.8

A9

VDD3.3

A10

AUX1.8

A11

AUX3.3

Power

W2

VSS

W4

VSS

W5

VSS

W6

VSS

W9

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W30

VSS

W35

VSS

Y2

VSS

Y4

VSS

Y7

VSS

Y8

VSS

Y9

VSS

Y16

VSS

Y17

VSS

Y18

VSS

Y19

VSS

Y20

VSS

Y21

VSS

Y27

VSS

Y31

VSS

AA2

VSS

AA4

VSS

AA5

VSS

AA6

VSS

AA9

VSS

AA16

VSS

AA17

VSS

AA18

VSS

AA19

VSS

AA20

VSS

AA21

VSS

AA30

VSS

AA35

VSS

AB2

VSS

AB4

VSS

AB7

VSS

AB8

VSS

AB9

VSS

AB27

VSS

AB31

VSS

AC2

VSS

AC4

VSS

AC5

VSS

AC6

VSS

AC9

VSS

AC30

VSS

AC35

VSS

AD2

VSS

AD4

VSS

AD7

VSS

AD8

VSS

AD27

VSS

AD31

VSS

AE2

VSS

AE4

VSS

AE5

VSS

AE6

VSS

AE7

VSS

AE30

VSS

AE35

VSS

AF2

VSS

AF4

VSS

AF7

VSS

AF28

VSS

AF31

VSS

AG2

VSS

AG4

VSS

AG5

VSS

AG6

VSS

AG12

VSS

AG14

VSS

AG16

VSS

AG18

VSS

AG20

VSS

AG22

VSS

AG24

VSS

AG26

VSS

AG30

VSS

AH2

VSS

AH6

VSS

AH31

VSS

AJ4

VSS

AJ5

VSS

AJ35

VSS

AK2

VSS

AK4

VSS

AK11

VSS

AK13

VSS

AK15

VSS

AK17

VSS

AK19

VSS

AK21

VSS

AK23

VSS

AK25

VSS

AK27

VSS

AK29

VSS

AK31

VSS

AL1

VSS

AL10

VSS

AL12

VSS

AL14

VSS

AL16

VSS

AL18

VSS

AL20

VSS

AL22

VSS

AL24

VSS

AL26

VSS

AL28

VSS

AL30

VSS

AL35

VSS

AM3

VSS

AM5

VSS

AR11

VSS

AR13

VSS

AR15

VSS

AR17

VSS

AR19

VSS

MSI

MICRO-STAR INt'L CO., LTD.

SIS 649 POWER, GND

MS7138

5

4

3

2

1

5

VCC1_8 VCC1_8

ZCLK03

CP27

L34

X_COPPER

D D

X_80S/0603

X_80S/0603

VCC1_8

C C

Z1XAVDD

CB83

C184

0.1u

X_0.1u

Z1XAVSS Z4XAVSS

L33

CP26

X_COPPER

R202 56R

R199 56R

VCC1_8

C170

R205

150RST

X_0.1u

ZVREF

C186

R212

49.9RST

0.1u

L32

X_80S/0603

C172

X_0.1u

L31

X_80S/0603

ZCMP_N

ZCMP_P

CP25

X_COPPER

Z4XAVDD

CB81

0.1u

CP23

X_COPPER

VCC3

Open for 649/662 co-layout

Short for 662

ZUREQ13

ZDREQ13

ZSTB013

ZSTB-013

ZSTB113

ZSTB-113

ZAD[16..0]13

ROUT24

GOUT24

HSYNC24

VSYNC24

DDC1CLK24

DDC1DATA24

R130 G_4.7K

R134 G_4.7K

R135 G_4.7K

DCLK3

INTA#7,13,19

Enable Disable

RSYNC

LSYNC

B B

CSYNC VB

VGA

panel link

1

1

1

0

0

0

4

AK1

ZCLK0

ZUREQ

ZDREQ

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

BOUT24

VCOMP

VRSET

VVBWN

LSYNC

RSYNC

CSYNC

R153

DACAVDD

DACAVSS

DACAVDD

DACAVSS

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

G_0

AN6

AM6

AM4

AR5

AN4

AM2

AN1

AN3

AM1

AR2

AN8

AR6

AR7

C10

D10

AL3

AK3

AT4

AT3

AL5

AP5

AK5

AL4

AP4

AP3

AL2

AP2

AP6

AP7

AP8

AT6

AT7

C6

C7

D7

C8

B10

C9

F10

E10

D9

D6

A6

B7

A7

A8

B8

B9

E8

E9

E6

E7

F7

649/662

ZCLK

ZUREQ

ZDREQ

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZAD16

ZVREF

ZCMP_N

ZCMP_P

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

VCOMP

VVBWN

VRSET

LSYNC

RSYNC

CSYNC

VOSCI

INTA#

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

MuTIOL

VGA

VSS

VSS

VSS

VSS

VSS

B5B6C3D1E5F3G1H5J3

3

RSMRST#

C161 X_C0.1U25Y

MS7_POK

U12C

F9

ENTEST

G6

TESTMODE0

G7

TESTMODE1

F6

TESTMODE2

G8

TRAP0

G9

TRAP1

F8

TRAP2

E13

AUXOK

C11

PWROK

D12

PCIRST#

D5

VADE

D2

VAD0

C1

VAD1

C2

VAD2

B2

VAD3

B3

VAD4

G4

VAD5

G5

VAD6

E4

VAD7

D3

VAD8

D4

VAD9

A3

VAD10

C4

VAD11

F5

VAGCLK

K4

VAGCLKN

A4

VAVSYNC

B4

VAHSYNC

H4

VBDE

J4

VBD0

J1

VBD1

J2

VBD2

H2

VBD3

H1

VBD4

G3

VBD5

F1

VBD6

F2

VBD7

F4

VBD8

E1

VBD9

E2

VB

VSS

VSS

VSS

VSS

VSS

C12

VBD10

VBD11

VBGCLK

VBGCLKN

VBVSYNC

VBHSYNC

VBCTL0

VBCTL1

VBHCLK

VBCAD

VBCLK

AGPIO2

AGPIO3

E3

G2

K6

H3

K2

K3

H6

A5

C5

J5

J6

K5

ENTEST

TMODE0

TMODE2

RSMRST#

MS7_POK

PCIRST1#

C119 X_C0.1U25Y

R145 4.7KR

RSMRST# 14,17,27,29

MS7_POK 14,29

PCIRST1# 18,21,27,29

Reserved for SIS662

VCC1_8 VCC3 VCC3

L23

80S/0603

C135

G_0.1u

L22

80S/0603

2

C130 G_0.1u

C133 G_0.1u

DACAVDD

C134

G_1u

DACAVSS

R142 G_130RST

VVBWN

VCOMP

VRSET

L26

X_80S/0603

C144

X_0.1u

L27

X_80S/0603

CP17

X_COPPER

ECLKAVDD

CB75

G_0.1u

ECLKAVSS

CP18

X_COPPER

1

L24

X_80S/0603

C138

X_0.1u

L25

X_80S/0603

CP15

X_COPPER

DCLKAVDD

CB73

G_0.1u

DCLKAVSS

CP16

X_COPPER

BSEL function for 775 CPU

R151

R176

10K

10K

TMODE0

A A

H_FSBSEL1

H_FSBSEL13,4,5

R150 10K

5

Q34

N-MMBT3904_SOT23

R159 33

Q35

N-MMBT3904_SOT23

VCCP

4

R152

N-MMBT3904_SOT23

10K

Q36

VCC3

R180

10K

VCC3VCC3 VCC3

R165

10K

R157 33

Q37

N-MMBT3904_SOT23

TMODE2

Title

Micro-Star

Document Number

Last Revision Date:

3

2

Wednesday, February 23, 2005

MS7138

SIS 649-Power & HyperZip

Sheet of

1

Rev

100

10 32

Loading...

Loading...