Page 1

8

7

6

5

4

3

2

1

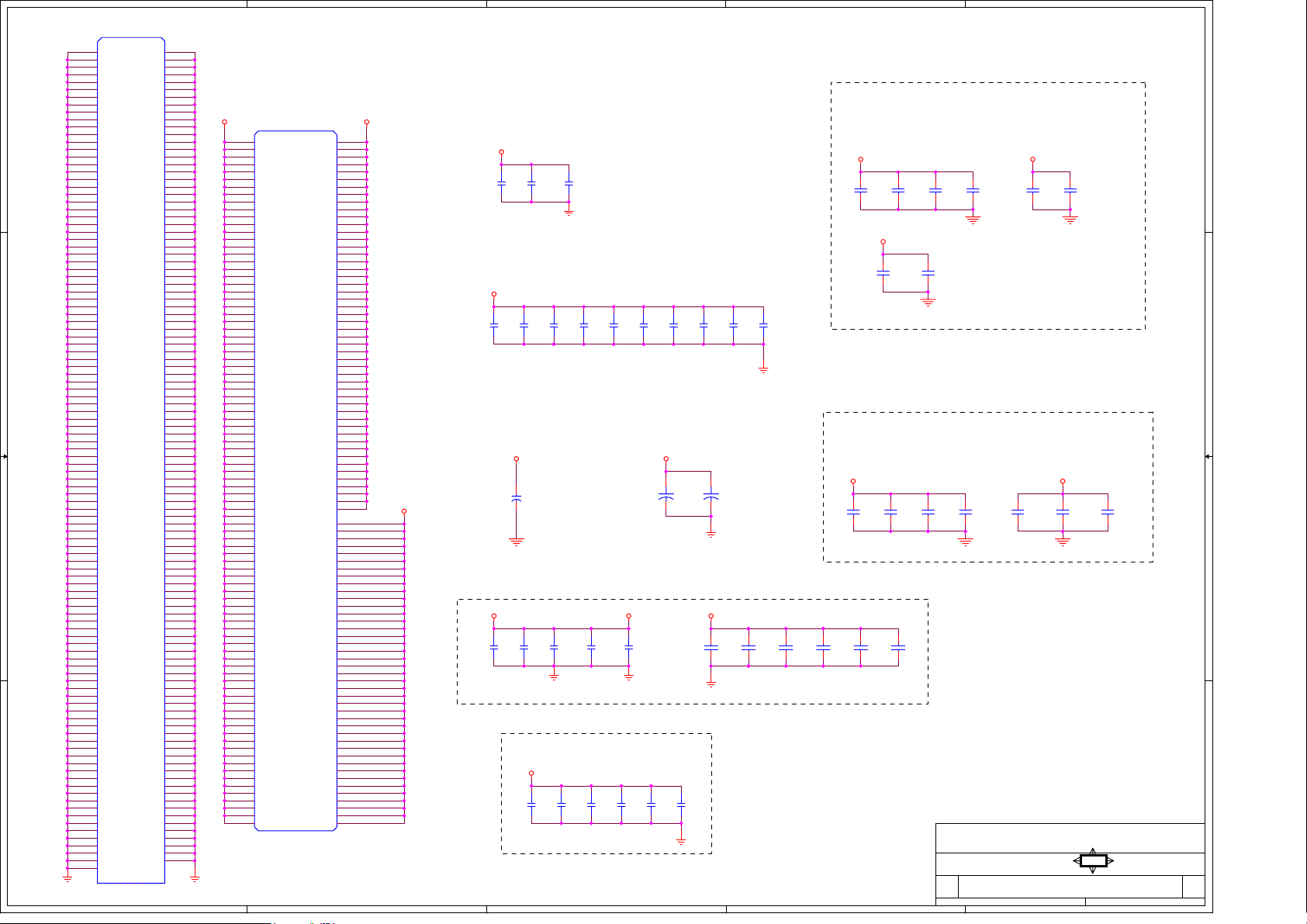

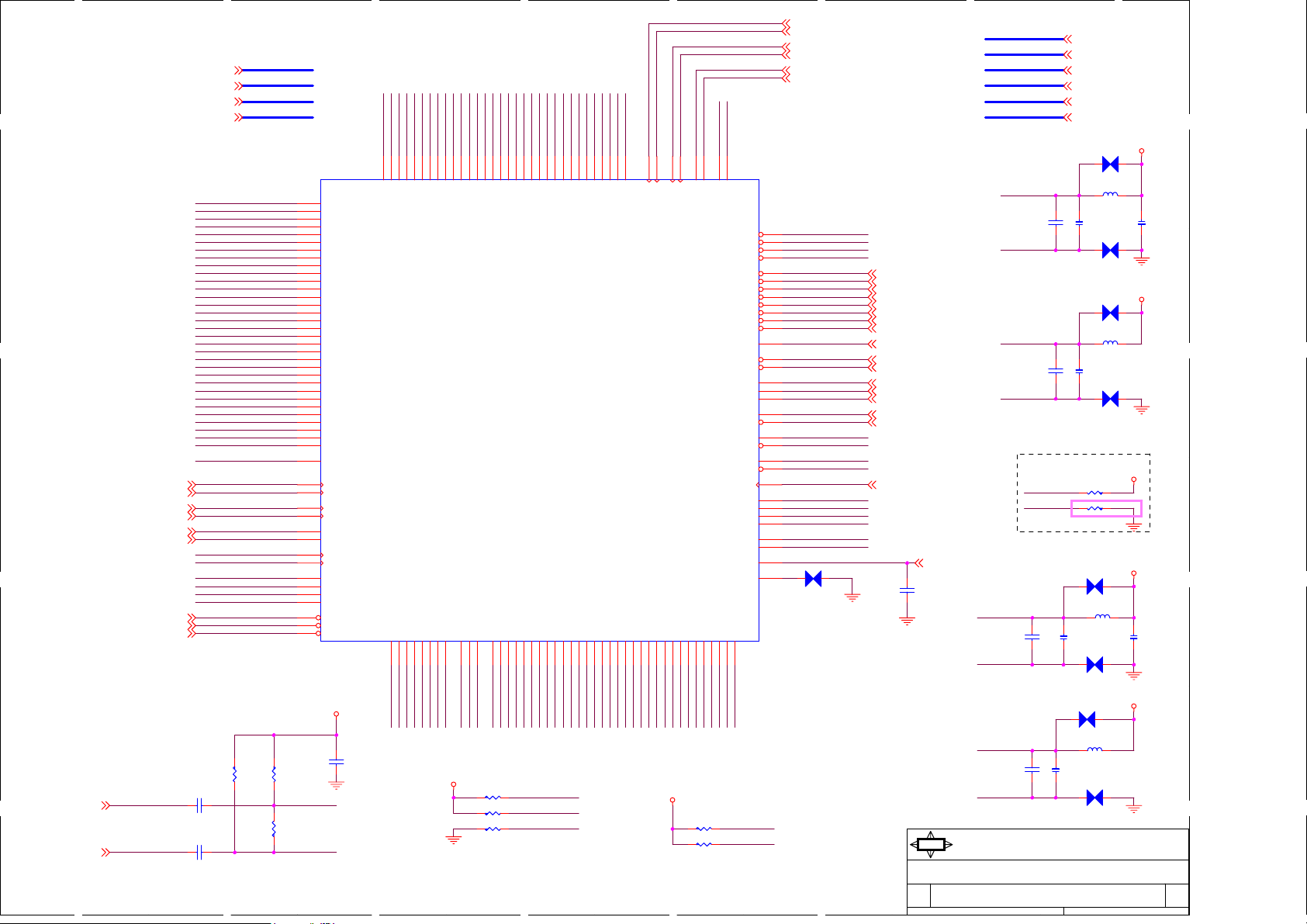

MS-7112

Cover Sheet

Block Diagram

D D

* AMD K8 Socket754

*SIS 760GX + 964

*REALTEK RTL8201CL LAN

*Winbond 83687THF I/O

*USB 2.0 support x8

*ALC 655 AC97 CODEC

MAIN CLOCK GEN

AMD K8 Socket754

DDR SLOT 1, 2

DDR TERMINATOR

SIS 760GX

SIS 964

AGP SLOT

C C

ERP BOM Function Description

PCI SLOT 1, 2 & CNR

LAN RTL8201CL

PS2 & VGA Connectors

IDE CONNECTORS

USB CONNECTORS

AC'97 CODEC

1

2

3

4 - 6

7

8 - 9

10 - 13

14 - 17

18

19

20

21

22

23

24

LPC SI/O W83687THF

B B

PARALLEL & SERIAL Ports

Regulators & Fan Connectors

ACPI CONTROLLER

VRM N2101

ATX POWER CON & FRONT PANEL

Decoupling Capacitor

A A

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Monday, August 23, 2004

2

Title

MS-7112

Cover Sheet

25

26

27

28

29

30

31

Sheet of

131

1

Rev

0A

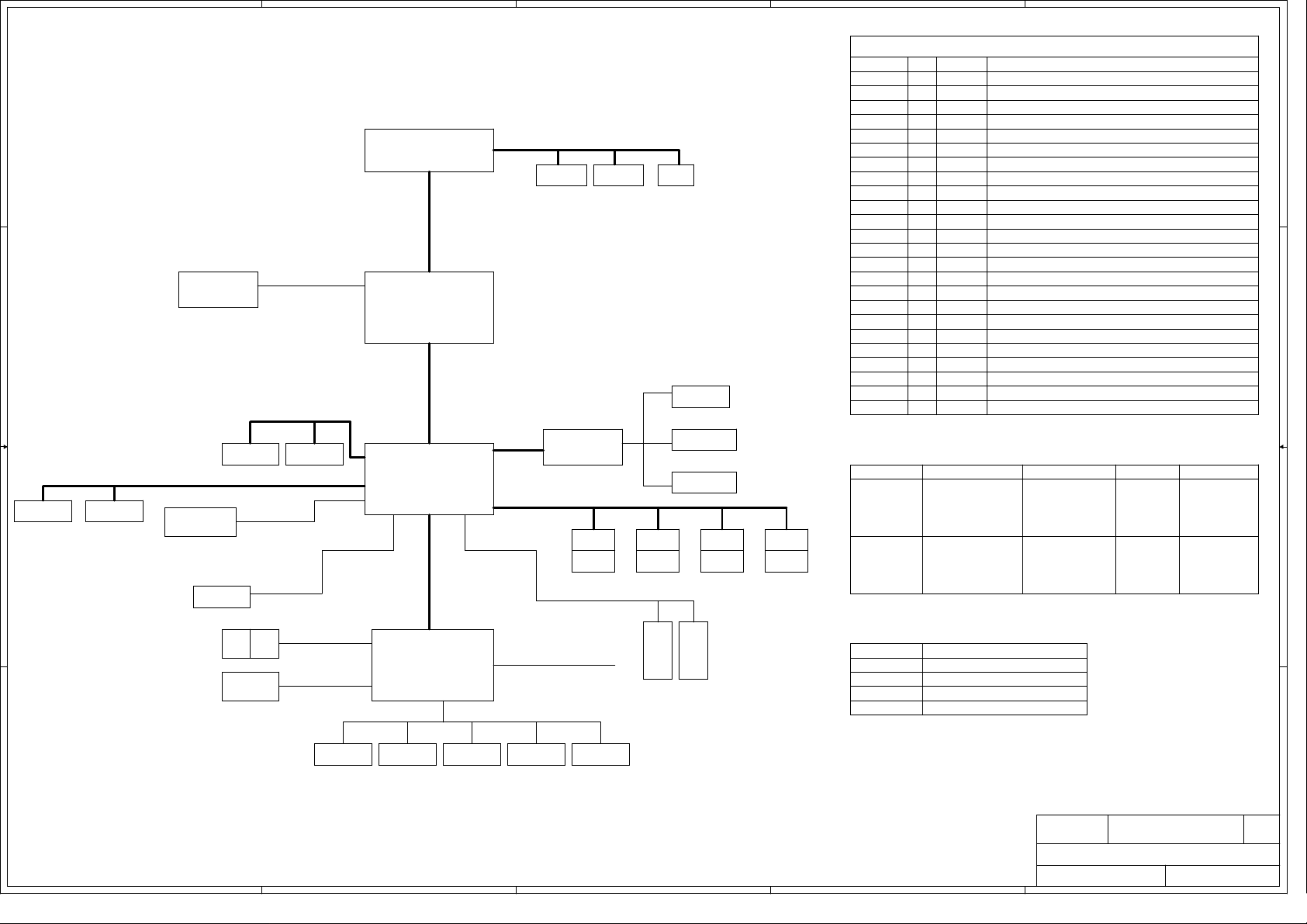

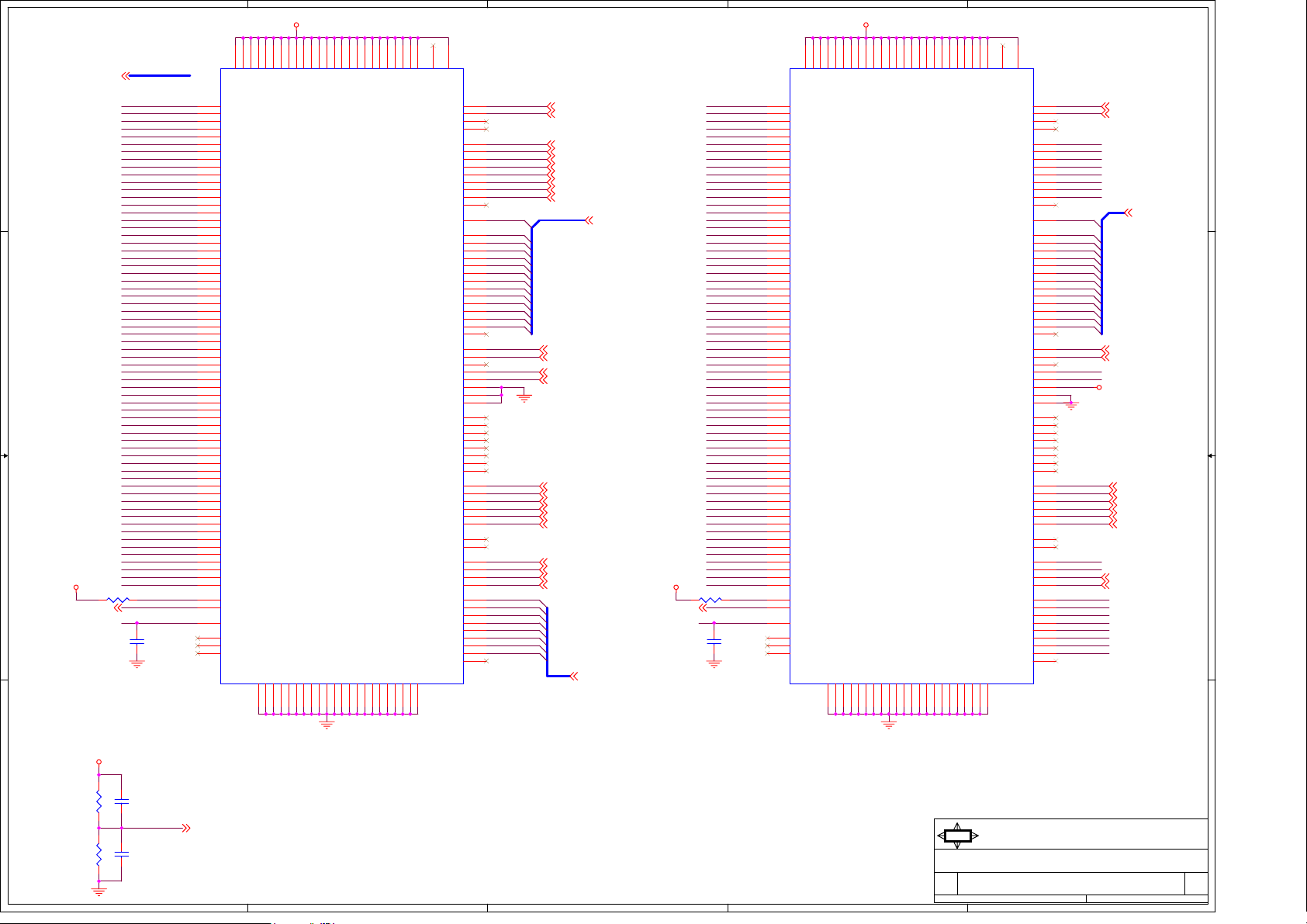

Page 2

5

4

3

2

1

GPIO Table on SIS964

GPIO_0

GPIO_1

System Block Diagram

D D

DDR SDRAM

K8 754

DDR1 DDR2

RTT

GPIO_2

GPIO_3

GPIO_4

GPIO_5

GPIO_6

GPI_7 RESUME

GPI_8 RING

GPI_9

GPI_10

Host Bus

Support Dual Monitor

VGA

1.5 V ONLY

AGP SLOT

SIS 760GX

C C

GPIO_11

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

GPIO_21

Support Max to six-PCI Devices

HYPERZIP

ANALOG IN

GPIO_22

GPIO_23

GPIO_24

MAIN

I/O

MAIN

I/O

I/O

MAIN

I/O

MAIN

MAIN

I/O

MAIN

I/O

MAIN

I/O

I/O

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O

I/O

RESUME

I/O

RESUME

I/O

RESUME

O

RESUME

O

RESUME

O

RESUME

MAIN

OD

MAIN

OD

I

RESUME

I

RESUME

I

RESUME

I RESUME

NC

CPU fan initia l speed control reserved

THERM#

GPIO3, pull-down reserved

GPIO4, pull-down reserved

NC

NC

NC

NC

NC

NC

NCGPIO_12 RESUME

NC

S3AUXSW#

KBDAT

KBCLK

MSDAT

MSCLK

SMBCLK

SMBDAT

EESK

EEDI

DDEO

EECS

PCI SLOT 2 PCI SLOT 1

AC'97

AUDIO CODEC

SIS 964

IDE 1

B B

IDE 2

KEYBOARD

/MOUSE

Lan

FAN1 FAN2

PS/2

FAN CONTROL

MII

LPC BUS

H/W MONITOR

USB 0

USB 1

LPC SUPER I/O

LEGACY

ROM

GPIOS IR/CIR

A A

5

4

C O M P RINTER FLOPPY

ANALOG OUT

MIC

USB 2 USB 3

USB 5

SATA_1

3

USB 4

SATA_2

USB 6

USB 7

PCI Config.

DEVICE

PCI Slot 2

PIRQ#B

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

PCI RESET DEVICE

Signals

PCIRST#1

PCIRST_964

HDDRST#

2

Northbridge,S/IO

PCI1~2PCIRST#2

AGP

Primary, Sco n dary IDE

Target

IDSEL

PCI_REQ#0PCI Slot 1 AD17

CLOCKREQ#/GNT#MCP1 INT Pin

PCICLK1

PCI_GNT#0

PCI_REQ#1 AD18 PCICLK2

PCI_GNT#1

Micro-Star

Document Number

Last Revision Date:

Monday, August 23, 2004

Title

MS-7112

System Block Diagram

Sheet of

1

231

Rev

0A

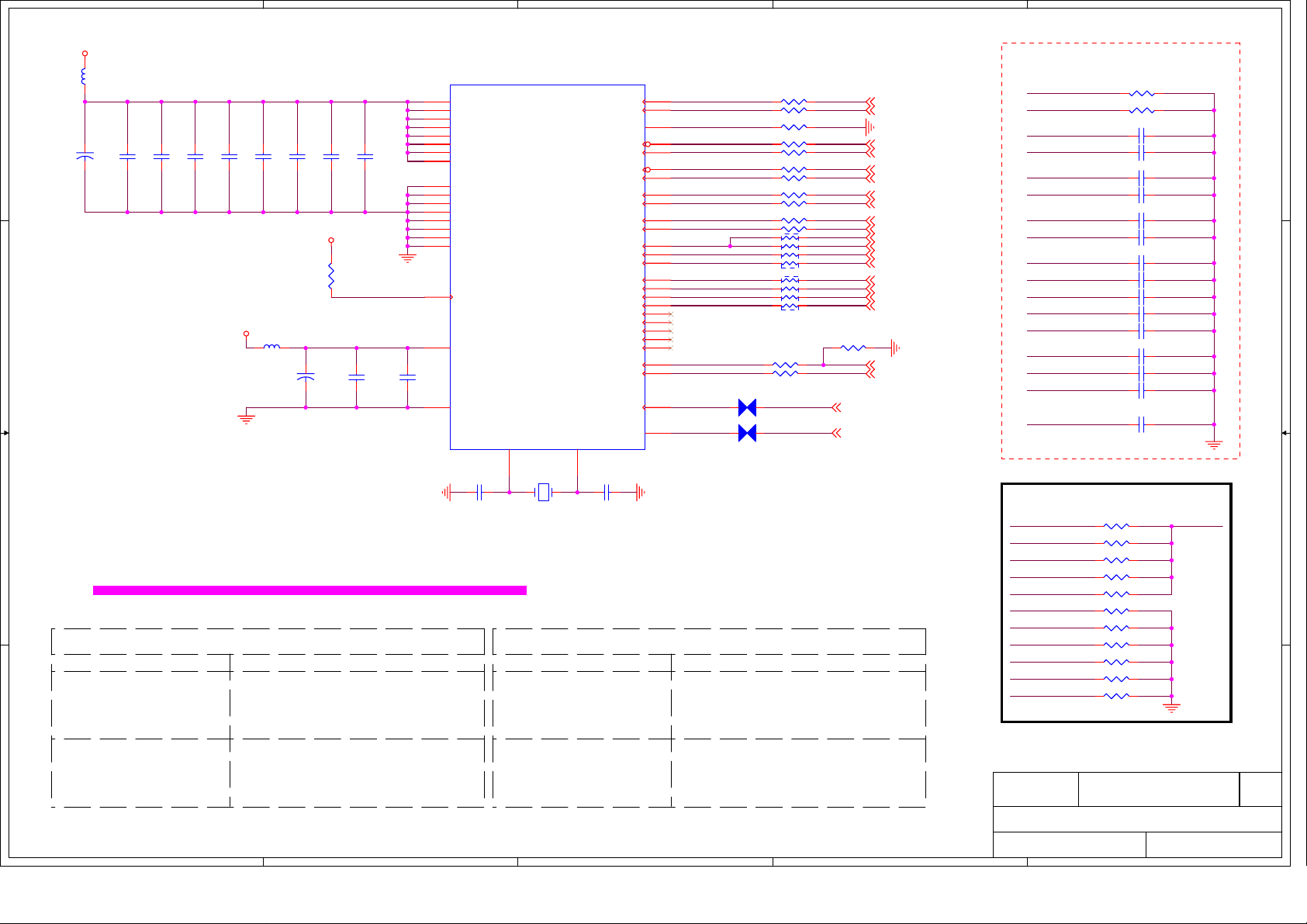

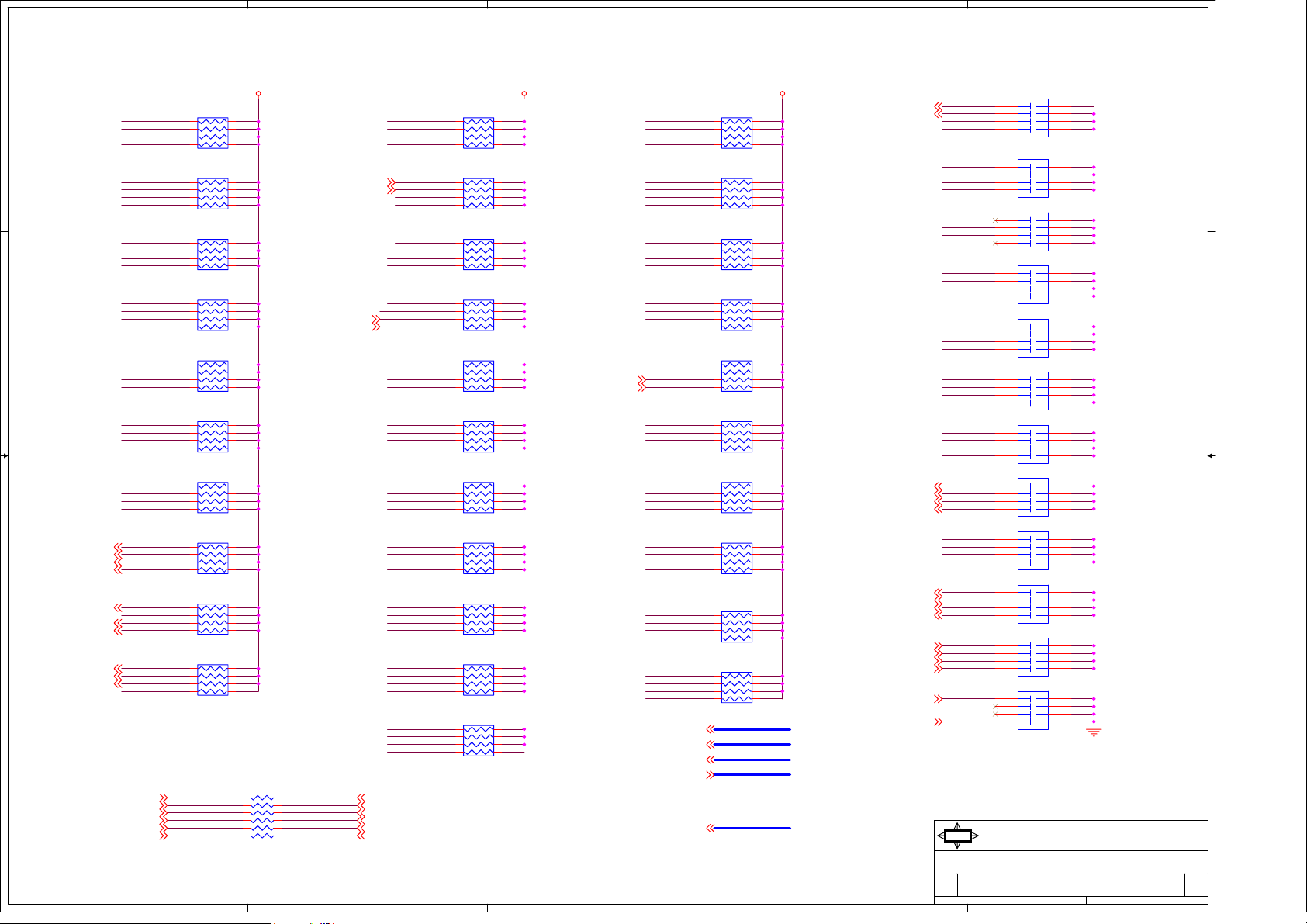

Page 3

5

4

3

2

1

VCC3

L13

1uH-1206-1A

D D

CE2

10U/0805

C C

B B

CB65

104P

CB64

104P

VCC3_DVDD

CB51

104P

CB55

104P

VCC3

CB63

104P

FB12

120_600mA

CE1

10U/0805

CB62

104P

CB53

104P

VCC3

VCC3_AVDD

CB54

C1000p50x

R190

X_10K

CB61

X_104P

Reset#

CB52

104P

U10

1

VDDREF

11

VDDZ

12

VDDPCI

19

VDDPCI

28

AVDD48

29

VDDAGP

39

VDDCPU

47

VDDSRC

5

GNDREF

8

GNDZ

18

GNDPCI

24

GNDPCI

25

GND48

32

GNDAGP

40

GNDCPU

44

GND

48

Reset#

36

AVDD

*12_48MHz/SEL_12_48MHz

**~24_48MHz/SEL_24_48MHz

35

* INTERNAL PULL-HIGH Resistor

AGND

** INTERNAL PULL-lOW Resistor

~ This output have 1.5X Drive Strength

RTM862-760

X1

6

C280

27P

14M-32pf-HC49S-D

Trace Width 10mils.

Y2

SRCCLKT

SRCCLKC

IREF

CPUCLK8T1

CPUCLK8C1

CPUCLK8T0

CPUCLK8C0

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

~**FS0/REF0

~*FS1/REF1

**Mode/REF2

**FS2/PCICLK_F0

**FS3/PCICLK_F1

PCICLK0

PCICLK1

*(PCI_STOP#)/PCICLK3

*(CPU_STOP#)/PCICLK4

*(CLK_STOP#)/PCICLK5

PCICLK2

PCICLK6

SCLK

SDATA

X2

7

C271

27P

SATACLKC

46

SATACLKC-

45

IREF

43

CPUCLK1C_H

42

CPUCLK1C_L

41

CPUCLK0C_H

38

CPUCLK0C_L

37

AGPCLKC0

31

AGPCLKC1

30

ZCLKC0

9

ZCLKC1

10

FS0

2

FS1

3

Mode

4

FS2

14

FS3

15

PCICLKC1 PCICLK1

16

PCICLKC2

17

20

21

22

23

13

SEL12_48M

27

SEL_24_48

26

34

33

Damping Resistors

Place near to the

Clock Outputs

R180 33

R170 33

R176

R177

R178

R182

R183

R185

R184

R229

R230

7 8

5 6

3 4

1 2

RN71 22_8P4R

7 8

5 6

3 4

1 2

RN70

R197

R203

CP59 X_Copper

33_8P4R

R191

22

22

CP61X_Copper

475RST

15

15

15

15

22

22

22

22

SMBCLK 7,15,19,28

SMBDAT 7,15,19,28

SATACLK 16

SATACLK- 16

CPUCLK1 10

CPUCLK-1 10

CPUCLK0 5

CPUCLK-0 5

AGPCLK0 10

AGPCLK1 18

ZCLK0 12

ZCLK1 14

VOSCIE 11

VGACLK 12

AC97CLK 24

SB14MHZ 15

SIOPCLK 25

PCICLK1 19

PCICLK2 19

96XPCLK 14

62

OSC12 16

SIO48M 25

CLK Table for SiS760 ( Different clock generator with different frequency defin table)

SiS 760 CLOCK

Bit 4

Bit 3 Bit 2 Bit 1 Bit 0

(FS3)

0

0 133.33100.00

0 100.99

0

0

0

0

0

0

0

0

0

0

1

0

A A

1 35.00

1

0

1

0

1 0

0

0

1

0

1

0

1

(FS1) (MHz)

(FS2)

0

0

0

0

1

0

1

0

0

1

1

0

1

1

0

0

0

0

1

0

1

0

1

0

0

1

1

1

1

5

(FS0)

0

1

0

1

0

1

0

1

0

1

0

1

0

1

VCO

(MHz)

800.00

807.92

800.00

807.92

799.98

803.94

699.99

707.22

799.98

833.30

799.98

807.90

800

807.92

999.96

999.96

CPU

(MHz)

200.00

201.98

133.99

233.33

235.74

160.00

166.66

266.66

269.30

200

201.98

166.66

166.66

SRC

(MHz)

100.00

100.99

100.00

100.99

100.00

100.49

100.00

101.03

100.00

104.16

100.00

100.99

100.00

100.99

100.00

100.00

ZCLK

134.65

133.33

133.33

133.99

140.00

141.44

133.33

134.11

133.33

134.65

133.33

134.65

125.00

142.85

AGPCLK

(MHz)

66.67

67.33

67.33134.65

66.67

67.00

70.00

70.72

66.67

69.44

66.67

67.33

66.67

67.33

66.66

66.66

4

PCI

(MHz)

33.33

33.66

33.66

33.33

33.50

35.00

35.36

33.33

34.72

33.33

33.66

33.33

33.66

33.33

33.33

Bit 3

Bit 4 ZCLKSRC

0

1

0

1

0

10 68.67

0

1

0

1

0

1

0

1

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Bit 1

(FS1)

0

0 68.67

0

0

1

033.33

101

0

1133.33

0

0

1

1

1

1

1

0

0 34.33

0

0

1

0

1

0

0

1

0

1

11

1

1

1

SiS 760 CLOCK

Bit 0

(FS0) (MHz)

0

1

0

1

0

1

0

1

00

1

0

1

1

0

1

3

CPU

VCO

CPU

(MHz)

824.00 103.00

103.00

840.00

105.00

206.0066.670

824.00

840.00

210.00

823.98

137.33

839.98

140.00

240.33

720.99

734.99

245.0001

823.98

164.80

839.98

168.00

823.98

279.99

839.98

824.00

206.00

840.00

210.00

1029.96

171.66

1049.96

174.99

(MHz) (MHz)

140.00

105.00

103.00

137.33

105.00

103.00

137.33

105.00

144.201

103.00

105.00

147.00

103.00

137.33

105.00

140.00

103.00

137.33274.66

105.00

140.00

103.00

137.33

105.00

140.00

103.00

128.74

105.00

131.24

AGPCLKBit 2

(MHz)(FS3)

70.00

70.00140.00

68.66

70.00140.00

72.10

73.50

68.66

70.00

68.66

70.00

68.67

70.00

68.66

70.00

PCI

(MHz)(FS2)

34.33137.33

35.00

34.33

35.00

34.33

35.00

36.05

36.75

34.33

35.00

34.33

35.00

34.33

35.00

2

By-Pass Capacitors

Place near to the Clock Outputs

SATACLK

SATACLK-

CPUCLK1

CPUCLK-1

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

96XPCLK

SIOPCLK

PCICLK2

SIO48M

SB14MHZ

VGACLK

VOSCIE

AC97CLK

R179 49.9RST

R169 49.9RST

C250 X_10P

C251 X_10P

C252 X_10P

C253 X_10P

C296 X_10P

C297 X_10P

C304 X_10P

C301 X_10P

C302 X_10P

C303 X_10P

C273 X_10P

C300 X_10P

C298 X_10P

C295 X_10P

C299 X_10P

Internal Pull Up / Down 120 K Ohm

SEL12_48M

FS0

FS1

FS2

FS3

FS0

FS1

FS2

FS3

Mode

SEL_24_48

Micro-Star

Document Number

Last Revision Date:

Monday, August 23, 2004

R186 2.7K

R223 2.7K

R236 2.7K

R231 X_2.7K

R238 X_2.7K

R227 X_2.7K

R228 X_2.7K

R232 2.7K

R239 2.7K

R237 2.7K

R200 2.7K

Title

MS-7112

MAIN CLOCK GEN

VCC3_DVDD

Desktop

Sheet of

1

331

Rev

0A

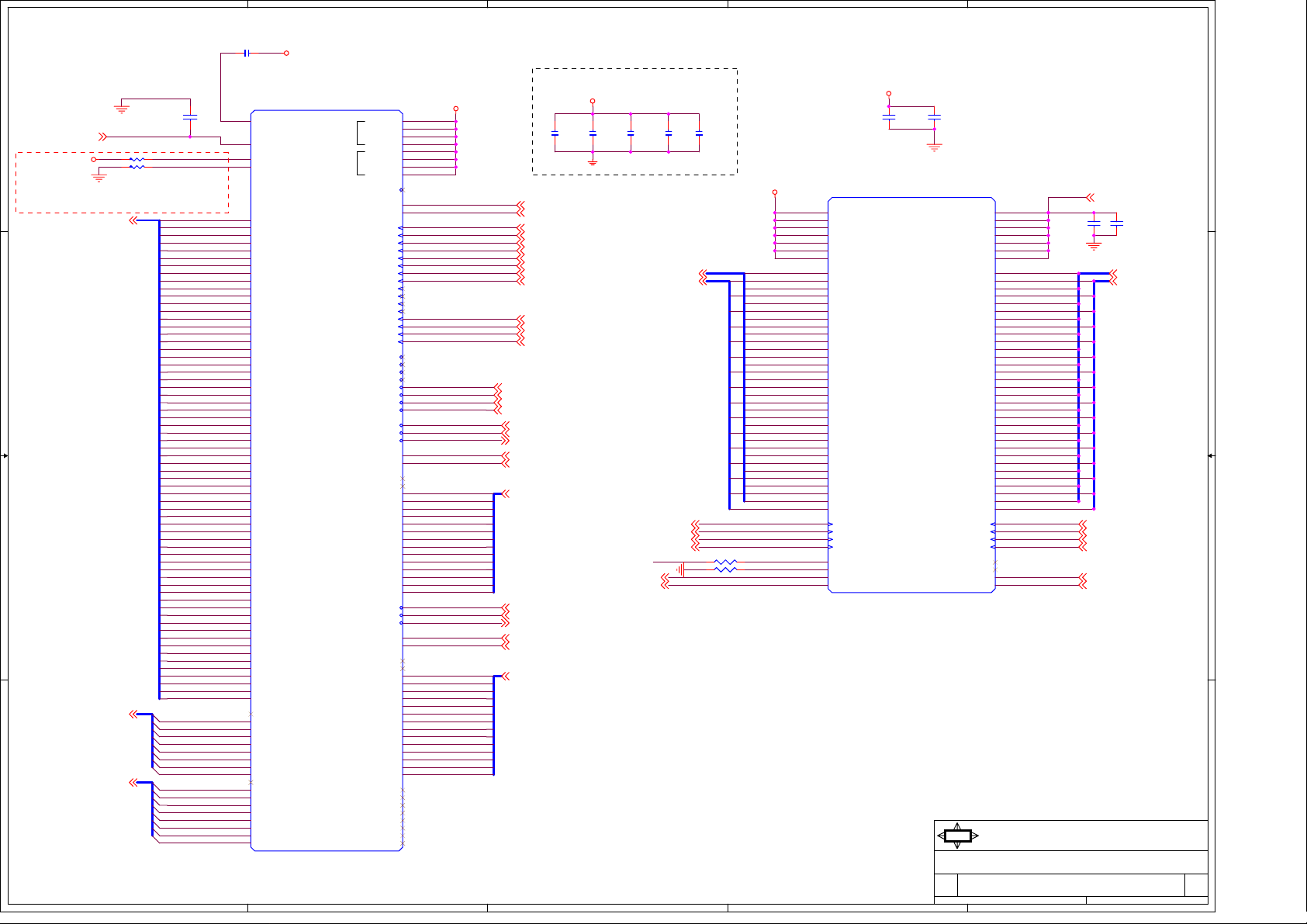

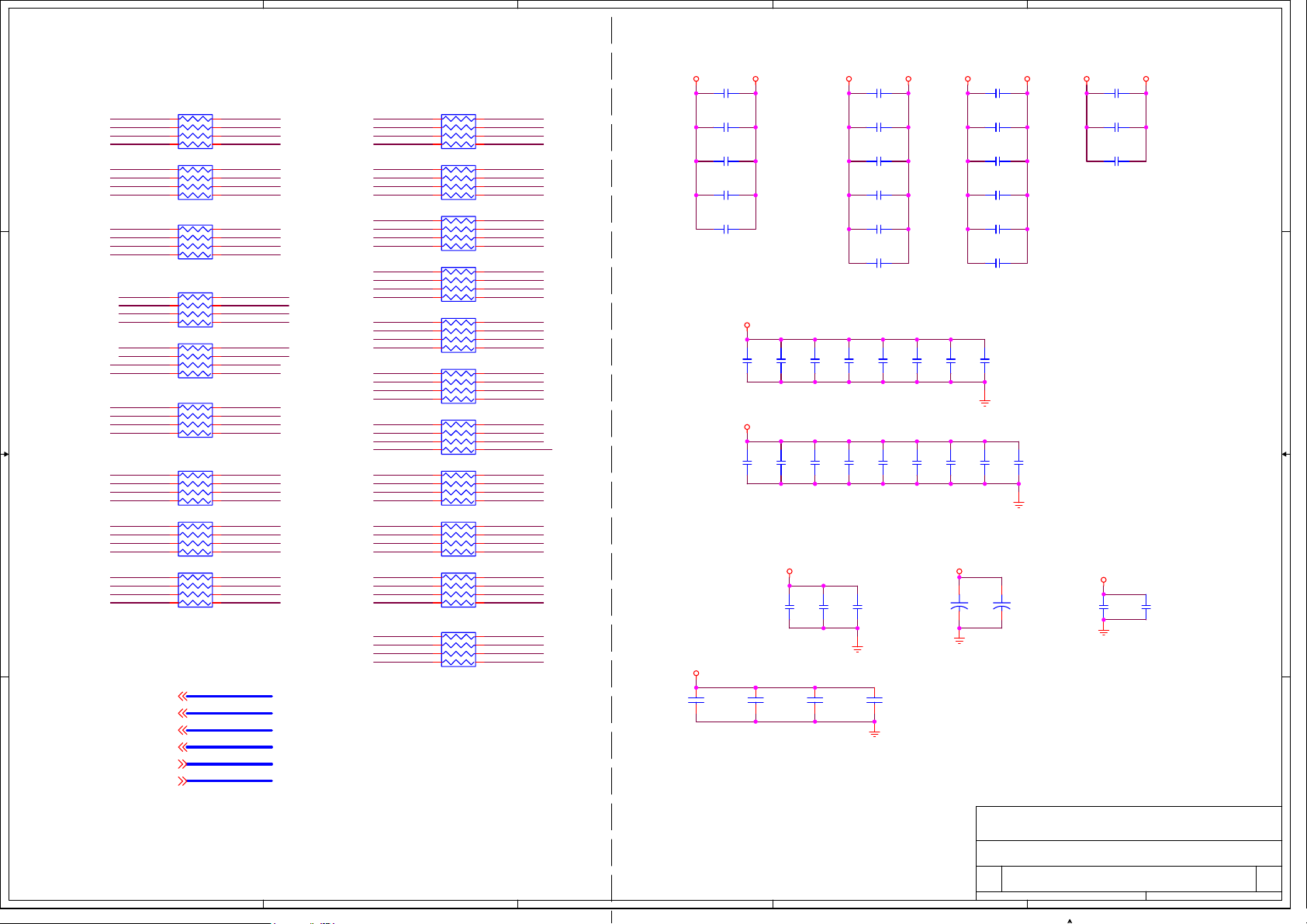

Page 4

5

4

3

2

1

C35

X_C1000p50x

DDR_VREF routed as 40~50 mils

trace wide , Space>25 mils

D D

C C

B B

A A

DDR_VREF7

VCCM

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

MD[63..0]9

MEMDM[7..0]9

-MDQS[7..0]9

DDR_VREF

R56 15RST

R57 15RST

5

C47

X_C1000p50x

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

MEMDM7

MEMDM6

MEMDM5

MEMDM4

MEMDM3

MEMDM2

MEMDM1

MEMDM0

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

AE13

AG12

AG3

AE2

AH3

AH9

AG5

AH5

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

AA1

AG1

AH7

AH13

AB1

AJ13

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AJ4

AF1

AJ3

AJ5

AJ6

AJ7

AJ9

A13

A14

AJ2

AJ8

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

VTT_DDR

CPU1B

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

X_1u

MCKE0 7,8

MCKE1 7,8

MEMCLK_H7 7,8

MEMCLK_L7 7,8

MEMCLK_H6 7,8

MEMCLK_L6 7,8

MEMCLK_H5 7,8

MEMCLK_L5 7,8

MEMCLK_H4 7,8

MEMCLK_L4 7,8

MEMCLK_H1 7,8

MEMCLK_L1 7,8

MEMCLK_H0 7,8

MEMCLK_L0 7,8

-MCS3 7,8

-MCS2 7,8

-MCS1 7,8

-MCS0 7,8

-MSRASA 7,8

-MSCASA 7,8

-MSWEA 7,8

MEMBANKA1 7,8

MEMBANKA0 7,8

MAA[13..0] 7,8

-MSRASB 7,8

-MSCASB 7,8

-MSWEB 7,8

MEMBANKB1 7,8

MEMBANKB0 7,8

MAB[13..0] 7,8

C119

VCCM

C96

X_1u

3

Bottom Side

X_1u

C67

X_1u

CADIP[0..15]10

CLKIP110

CLKIN110

CLKIP010

CLKIN010

VLDT0

CTLIP010

CTLIN010

X_1u

C115

R38 49.9RST

R37 49.9RST

C42

VDD_12_A

CADIP15

CADIN15

CADIP14

CADIN14

CADIP13

CADIN13

CADIP12

CADIN12

CADIP11

CADIN11

CADIP10

CADIN10

CADIP9

CADIN9

CADIP8

CADIN8

CADIP7

CADIN7

CADIP6

CADIN6

CADIP5

CADIN5

CADIP4

CADIN4

CADIP3

CADIN3

CADIN2

CADIP1

CADIN1

CADIP0

CADIN0

CTLIP1

CTLIN1

D29

D27

D25

C28

C26

R25

U27

U26

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

U29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

W25

R27

R26

R29

B29

B27

T25

V25

T27

T28

V29

V27

V28

Y29

Y25

Y27

Y28

T29

CPU1A

N12-7540031-L06

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

2

VDD_12_A

HYPER TRANSPORT - LINK0

WIDTH 200MILS, AS CLOSE AS POSSIBLE TO THE

PROCESSOR AND THEN AS 20MILS TRACES IN THE

PIN FILED

C124

C123

X_0.22u

0.22u

VLDT0_B PINS SHOULD BE CONNECTED TO A

SIGNAL 4.7UF CAPACITOR ROUTED WITH A 100

MILS WIDE TRACE

VLDT0

AH29

VLDT0_B6

AH27

VLDT0_B5

AG28

VLDT0_B4

AG26

VLDT0_B3

AF29

VLDT0_B2

AE28

VLDT0_B1

AF25

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

MSI

Title

Size Document Number Rev

Date: Sheet

N26

N27

L25

M25

L26

L27

J25

K25

G25

H25

G26

G27

E25

F25

E26

E27

N29

P29

M28

M27

L29

M29

K28

K27

H28

H27

G29

H29

F28

F27

E29

F29

J26

J27

J29

K29

N25

P25

P28

P27

CADOP15

CADON15

CADOP14

CADON14

CADOP13

CADON13

CADOP12

CADON12

CADOP11

CADON11

CADOP10

CADON10

CADOP9

CADON9

CADOP8

CADON8

CADOP7

CADON7

CADOP6

CADON6

CADOP5

CADON5

CADOP4

CADON4

CADOP3

CADON3

CADOP2CADIP2

CADON2

CADOP1

CADON1

CADOP0

CADON0

CLKOP1

CLKON1

CLKOP0

CLKON0

CTLOP0

CTLON0

K8 DDR & HT

MS-7112

<OrgName>

C41

C4.7U16X1206

CLKOP1 10

CLKON1 10

CLKOP0 10

CLKON0 10

CTLOP0 10

CTLON0 10

1

VLDT0 5

C43

X_0.22uf

CADOP[0..15] 10

CADON[0..15] 10CADIN[0..15]10

431Monday, August 23, 2004

of

0A

Page 5

5

4

3

2

1

VCCA_PLL trace length from the VR1 to the PGA must be 0.75".

Place al filters close to the PGA.

Keep all power and signal trce away from the VR1.

Place a cut in the GND plane around the VCCA_PLL regulator circuit.

D D

LAYOUT: Ro ute V DDA tr ace approx. 50 mils wide

(use 2x25 mil tr aces t o exit ball field) and 500 mils

long.

FB1 180nH/1210

C33

X_C1000p50x

C50

C1000p50x

GND

C51

C1000p50x

CPUCLK03

CPUCLK-03

8/28 AMD CHANGE THE PULL-UP POWER

C56

0.22uf

CPU_VDDA_25

C49

475P/0805

-CPURST10

-LDTSTOP10

COREFB_H29

VCCM

COREFB_L29

C48 3900P

C57 3900P

VCCM

VTT_DDR

VCC2.5

3

Differential , "10:10:5:10:10".

Near CPU in 0.5" .

VCC2.5

C52

C53

3900P

0.22uf

AH25

VDDA1

AJ25

VDDA2

AF20

CPU_GD

L0_REF1

L0_REF0

X_C1000p50xC34

VDDIO_SENSE

R36

R35 820 R39

R34 820

R55 1K

R54 1K

7 8

169RST

3 4

5 6

1 2

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

RN5

X_1K-8P4R

CLKIN_H

CLKIN_L

RESET_L

AE18

PWROK

AJ27

LDTSTOP_L

AF27

L0_REF1

AE26

L0_REF0

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AJ21

CLKIN_H

AH21

CLKIN_L

AJ23

NC_AJ23

AH23

NC_AH23

AE24

NC_AE24

AF24

NC_AF24

C16

VTT_A5

AG15

VTT_B5

AH17

DBRDY

C15

NC_C15

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

C18

NC_C18

A19

NC_A19

A28

KEY1

AJ28

KEY0

AE23

NC_AE23

AF23

NC_AF23

AF22

NC_AF22

AF21

NC_AF21

C1

FREE29

J3

FREE31

R3

FREE33

AA2

FREE35

D3

FREE1

AG2

FREE37

B18

FREE4

AH1

FREE38

AE21

FREE41

C20

FREE7

AG4

FREE11

C6

FREE12

AG6

FREE13

AE9

FREE14

AG9

FREE40

11223344556677889910101111121213131414151516

CPU1C

G_FBCLKOUT_H

G_FBCLKOUT_L

2

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

A20

A26

A27

AG13

AF14

AG14

AF15

AE15

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

16

Title

Size Document Number Rev

Date: Sheet

THRMTRIP#

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

FBCLKOUT_H

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

MSI

Near SB/SiS964

R202

1K

C258

C10u10y_1206

VID4

CP51 X_Copper

VID3

VID2

VID1

VID0

LAYOUT: Route

FBCLKOUT_H/L differentially

with 20/8/5/ 8 / 2 0 s pacing and

80.6RST

trace width. ( In CPU

breakout => ro u t e d 5:5:5 )

8/28 AMD CHANGE THE PULL-UP POWER

R63 1K

RN6

VID0

7 8

VID2

5 6

VID1

3 4

VID3

1 2

X_8P4R-4.7K

VID4

R27 X_4.7K

K8 HDT & MISC

MS-7112

THRMTRIP# 15,28

CPU_TMPA 25

VTIN_GND 25

VID[0..4] 25

VCCM

VCC2.5

<OrgName>

1

C25

104P

531Monday, August 23, 2004

C135

X_475P/0805

of

0A

-LDTSTOP

PS_OUT#28,30

C C

B B

R72

1K

Q15

2N7002S

VCC2.5

CPU_GD28

VLDT0

VLDT04

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

VDDA_25

R32 44.2RST

R33 44.2RST

HDT Connectors

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

NC_C21

NC_AJ18

NC_AG17

NC_D18

NC_C19

NC_B19

NC_D20

NC_AH18

NC_AG18

A A

R28 X_56

R31 X_1K

1 2

3 4

5 6

7 8

RN40 X_56-8P4R

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R29 X_1K

R30 X_1K

5

VCC2.5

RN4

1K-8P4R

1K-8P4R

RN41

LAYOUT: Locate close to Clawhammer socket.

VTT_DDR

C46

475P/0805

4

Page 6

5

CPU1E

5

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

20

GROUND

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

VCCP VCCM

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

GND

AC15

H18

H22

H24

G13

AB14

G15

AA15

H16

AB16

G17

AA17

AC17

AE17

AB18

AD18

AG19

G19

AC19

AA19

H20

M20

AB20

AD20

G21

N21

R21

U21

W21

AA21

AC21

M22

AB22

AD22

G23

N23

R23

U23

W23

AA23

AC23

D24

M24

AB24

AD24

AH24

AE25

B20

E21

J23

F26

V10

K14

Y14

J15

K16

Y16

J17

F18

K18

Y18

E19

J19

F20

K20

P20

T20

V20

Y20

J21

L21

F22

K22

P22

T22

V22

Y22

E23

L23

B24

F24

K24

P24

T24

V24

Y24

K26

P26

V26

CPU1D

L7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

N7

VDD10

L9

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD39

VDD38

VDD37

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

D2

VSS10

AF2

GND

AA10

AE16

W20

AA20

AC20

AE20

AG20

AJ20

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

W24

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

AB17

AD17

AA18

AC18

AB19

AD19

AF19

AA8

AB9

B14

G20

R20

U20

D21

H21

K21

M21

P21

V21

B22

E22

G22

N22

R22

U22

D23

H23

K23

P23

V23

E24

G24

N24

R24

U24

B25

C25

B26

D26

H26

M26

C27

B28

D28

G28

H15

B16

G18

D19

H19

K19

N20

VSS11

W6

VSS12

Y7

VSS13

VSS14

VSS15

VSS16

J12

VSS17

VSS18

Y15

VSS19

VSS20

J18

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

F21

VSS32

VSS33

VSS34

VSS35

VSS36

T21

VSS37

VSS38

Y21

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

J22

VSS45

L22

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

F23

VSS57

VSS58

VSS59

VSS60

T23

VSS61

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

J24

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

F15

VSS187

VSS188

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

F19

VSS213

VSS214

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

VSS222

17171818191920

D D

C C

B B

A A

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

EMI

LAYOUT: Place 1 capacitor every 1-1.5"

along VDD_CORE perimiter.

VCCP

C81

C85

X_6.8p

C0.01u50x

LAYOUT: Place 6 EMI caps along bottom right side of Clawhammer,

2 in middle of HT link, and 12 along bottom left side of Clawhammer.

VCCP

C22

C76

C72

X_6.8p

X_6.8p

LAYOUT: Loca t e close to

Clawhammer socket.

VTT_DDR VTT_DDR

+

EC4

VCCP

C31

X_475P/0805

X_C100u16d6

VCCM VCCM VCCM

C66

C166

475P/0805

475P/0805

GND

3

1u

C37

GND

C62

C38

C65

X_6.8p

X_6.8p

LAYOUT: Place one 1210 10uF capacitor

on each end of the VTT island.

C184

C399

X_475P/0805

X_475P/0805_B

X_6.8p

CT1

10u/0805

GND

C69

X_6.8p

X_6.8p

12

+

C394

104P_B

2

1

CPU

Place on inside of CPU Cavity ( 5 * 0.22uF/0603

X7R high-freq decoupling Cap. )

VCCP

C84

C89

C83

C0.22u10x

X_C0.22u10x

VCCP

C92

104P

X_6.8p

+

CT3

10u/0805

C80

C403

104P_B

C90

X_6.8p

X_6.8p

GND

C186

X_104P

LAYOUT: Place 1000pF capacitors

between VRM & CPU

RECOMMEND 4 PLACEDIN TOP SOCKET CAVITY

AND 2 ON THE BOTTOM DIRECTLY UNDER SOCKET CAVITY

X_C10u10y_1206

C86

C149

104P

C91

X_C10u10y_1206

C188

X_104P

C10u10y_1206

C141

104P

C74

12

GND

GND

C0.22u10x

C93

104P

C10u10y_1206

C82

C88

X_C0.22u10x

C95

VCCP

C395

C0.22u10x_B

VCCPVCCP

C397

C396

C10u10y_1206_B

X_C10u10y_1206_B

C400

C0.22u10x_B

C401

X_C10u10y_1206_B

LAYOUT: Place beside processor.

VCCM

C70

C94

C402

C398

0.22uf_B

4

0.22uf

0.22uf_B

3

C45

0.22uf

0.22uf

0.22uf

C111

GND

Title

Size Do cu ment Number Rev

2

Date: Sheet

<OrgName>

MSI

K8 POWER & GND

MS-7112

1

631Monday, August 23, 2004

0A

of

Page 7

5

VCCM VCCM

4

SYSTEM MEMORY

3

2

1

108

120

148

DR_MD[63..0 ]8,9

D D

C C

B B

R114 4.7K

-MSWEA4,8

DR_MD[63..0]

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

DDR_VREF

C29

X_C1000p50x

VDD07VDD138VDD246VDD370VDD485VDD5

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

SLAVE ADDRESS = 1010000B

102

NC4

Place 104p Cap. near the DIMM

168

VDD6

VDD7

VDD8

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

104

112

128

136

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

VDDQ7

VDDQ8

184

DDR DIMM

SOCKET

VSS14

100

116

124

143

VDDQ9

VDDQ10

VSS15

VSS16

132

156

164

VDDQ11

VDDQ12

PIN

VSS17

VSS18

139

145

172

VDDQ13

VSS19

152

180

VDDQ14

VSS20

160

82

15

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

SDA

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

176

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SA0

SA1

SA2

157

158

71

163

5

14

25

36

56

67

78

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

MCKE0

21

MCKE1

111

-MSCASA

65

-MSRASA

154

DR_MEMDM0

97

DR_MEMDM1

107

DR_MEMDM2

119

DR_MEMDM3

129

DR_MEMDM4

149

DR_MEMDM5

159

DR_MEMDM6

169

DR_MEMDM7

177

140

DDR1

DDR400-CH

-MCS0

-MCS1

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

MAA13

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

SMBCLK

SMBDAT

MEMCLK_H5

MEMCLK_L5

MEMCLK_H0

MEMCLK_L0

MEMCLK_H7

MEMCLK_L7

-MCS0 4,8

-MCS1 4,8

-DR_MDQS0 8,9

-DR_MDQS1 8,9

-DR_MDQS2 8,9

-DR_MDQS3 8,9

-DR_MDQS4 8,9

-DR_MDQS5 8,9

-DR_MDQS6 8,9

-DR_MDQS7 8,9

MAA[13..0]

MAA[13..0] 4,8

MEMBANKA0 4,8

MEMBANKA1 4,8

SMBCLK 3,15,19,28

SMBDAT 3,15,19,28

MEMCLK_H5 4,8

MEMCLK_L5 4,8

MEMCLK_H0 4,8

MEMCLK_L0 4,8

MEMCLK_H7 4,8

MEMCLK_L7 4,8

MCKE0 4,8

MCKE1 4,8

-MSCASA 4,8

-MSRASA 4,8

Place 104p and 1000p Cap.

near the DIMM

DR_MEMDM[7..0] 8,9

VCCMVCCM

R119 4.7K

-MSWEB4,8

C36

104P

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

DDR_VREF

94

95

98

99

12

13

19

20

105

106

109

110

23

24

28

31

114

117

121

123

33

35

39

40

126

127

131

133

53

55

57

60

146

147

150

151

61

64

68

69

153

155

161

162

72

73

79

80

165

166

170

171

83

84

87

88

174

175

178

179

90

63

101

102

108

120

148

168

VDD07VDD138VDD246VDD370VDD485VDD5

VDD6

VDD7

VDD8

2

DQ0

4

DQ1

6

DQ2

8

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

WP(NC)

WE#

1

VREF

9

NC2

NC3

SLAVE ADDRESS = 1010001B

NC4

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

DDR DIMM

SOCKET

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

104

112

128

VDDQ7

100

116

136

VDDQ8

VDDQ9

184

VSS14

VSS15

124

143

VDDQ10

VSS16

132

156

139

164

VDDQ11

VDDQ12

PIN

VSS17

VSS18

145

172

VDDQ13

VSS19

152

180

VDDQ14

VSS20

160

82

15

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A10_AP

SDA

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

NC(RESET#)

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

176

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SA0

SA1

SA2

157

158

71

163

-DR_MDQS0

5

-DR_MDQS1

14

-DR_MDQS2

25

-DR_MDQS3

36

-DR_MDQS4

56

-DR_MDQS5

67

-DR_MDQS6

78

-DR_MDQS7

86

47

167

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

SMBCLK

92

SMBDAT

91

181

182

183

44

45

49

51

134

135

142

144

MEMCLK_H4

16

MEMCLK_L4

17

MEMCLK_H1

137

MEMCLK_L1

138

MEMCLK_H6

76

MEMCLK_L6

75

173

10

MCKE0

21

MCKE1

111

-MSCASB

65

-MSRASB

154

DR_MEMDM0

97

DR_MEMDM1

107

DR_MEMDM2

119

DR_MEMDM3

129

DR_MEMDM4

149

DR_MEMDM5

159

DR_MEMDM6

169

DR_MEMDM7

177

140

DDR2

DDR400-CH

-MCS2

-MCS3

MAB13

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

-MCS2 4,8

-MCS3 4,8

MAB[13..0] 4,8

MEMBANKB0 4,8

MEMBANKB1 4,8

VCCM

MEMCLK_H4 4,8

MEMCLK_L4 4,8

MEMCLK_H1 4,8

MEMCLK_L1 4,8

MEMCLK_H6 4,8

MEMCLK_L6 4,8

-MSCASB 4,8

-MSRASB 4,8

VCCM

A A

R21

1KST

R24

1KST

C21

X_104P

DDR_VREF

C26

104P

5

DDR_VREF 4

MSI

Title

Size Do cument Number Rev

4

3

2

Date: Sheet

<OrgName>

DDR DIMM1, 2

MS-7112

1

731Monday, August 23, 2004

0A

of

Page 8

5

DDR Terminations

4

3

2

1

VTT_DDRVTT_DDRVTT_DDR

D D

C C

B B

-MSCASA4,7

-MSCASB4,7

-MSWEB4,7

-MSRASA4,7

-MSRASB4,7

-MSWEA4,7

A A

DR_MD59

DR_MD63

DR_MD58

DR_MD62

-DR_MDQS7

DR_MEMDM7

DR_MD57

DR_MD61

DR_MD56

DR_MD60

DR_MD51

DR_MD55

DR_MD50

DR_MD54

-DR_MDQS6

DR_MEMDM6

MAA13

MAB13

DR_MD53

DR_MD52

DR_MD49

DR_MD48

DR_MD47

DR_MD46

DR_MD43

DR_MD42

DR_MEMDM5

-DR_MDQS5

-MCS0

-MCS04,7

-MCS2

-MCS24,7

-MCS1

-MCS14,7

-MCS3

-MCS34,7

-MSCASA

DR_MD41

-MSCASB

-MSWEB

-MSRASA

-MSRASB

-MSWEA

DR_MD45

The Processor pins and resistor

are less than 1" in length.

MEMCLK_H54,7

MEMCLK_H44,7

MEMCLK_H74,7

MEMCLK_H64,7

MEMCLK_H14,7 MEMCLK_L1 4,7

MEMCLK_H04,7 MEMCLK_L0 4,7

5

RN65 47-8P4R

7 8

5 6

3 4

1 2

RN64 47-8P4R

7 8

5 6

3 4

1 2

RN61 47-8P4R

7 8

5 6

3 4

1 2

RN59 47-8P4R

7 8

5 6

3 4

1 2

RN57 47-8P4R

7 8

5 6

3 4

1 2

RN55 47-8P4R

7 8

5 6

3 4

1 2

RN53 47-8P4R

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

RN52 47-8P4R

RN50 47-8P4R

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

RN49 47-8P4R

MEMCLK_H5

MEMCLK_H4

MEMCLK_H7

MEMCLK_H6

MEMCLK_H1

MEMCLK_H0

R43 120RST

R42 120RST

R62 120RST

R61 120RST

R49 120RST

R50 120RST

MEMBANKB14,7

MEMBANKA14,7

MEMCLK_L5

MEMCLK_L4

MEMCLK_L7

MEMCLK_L6

MEMCLK_L1

MEMCLK_L0

MEMBANKA04,7

MEMBANKB04,7

MEMCLK_L5 4,7

MEMCLK_L4 4,7

MEMCLK_L7 4,7

MEMCLK_L6 4,7

4

-DR_MDQS4

DR_MD37

DR_MD33

DR_MD36

DR_MD32

MAB10

MAB0

MAA10

MAA0

MAA1

MAB1

MAB2

MAA2

DR_MD31

DR_MD27

DR_MD30

DR_MD26

MAB3

MAA3

DR_MEMDM3

MAA4

-DR_MDQS3

DR_MD25

MAB4

MAA6

DR_MD29

DR_MD28

MAA5

MAA8

DR_MD24

MAB6

MAB5

DR_MD19

DR_MD44

DR_MD40

DR_MD39

DR_MD35

DR_MD38

DR_MD34

DR_MEMDM4

RN47 47-8P4R

7 8

5 6

3 4

1 2

RN46 47-8P4R

7 8

5 6

3 4

1 2

RN44 47-8P4R

7 8

5 6

3 4

1 2

RN42 47-8P4R

7 8

5 6

3 4

1 2

RN39 47-8P4R

7 8

5 6

3 4

1 2

RN38 47-8P4R

7 8

5 6

3 4

1 2

RN36 47-8P4R

7 8

5 6

3 4

1 2

RN35 47-8P4R

7 8

5 6

3 4

1 2

RN34 47-8P4R

7 8

5 6

3 4

1 2

RN32 47-8P4R

7 8

5 6

3 4

1 2

RN31 47-8P4R

7 8

5 6

3 4

1 2

MAB[13..0]4,7

MAA[13..0]4,7

RN28 47-8P4R

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

RN27 47-8P4R

RN25 47-8P4R

7 8

5 6

3 4

1 2

RN22 47-8P4R

7 8

5 6

3 4

1 2

RN19 47-8P4R

7 8

5 6

3 4

1 2

RN16 47-8P4R

7 8

5 6

3 4

1 2

RN14 47-8P4R

7 8

5 6

3 4

1 2

RN11 47-8P4R

7 8

5 6

3 4

1 2

RN9 47-8P4R

7 8

5 6

3 4

1 2

RN7 47-8P4R

7 8

5 6

3 4

1 2

DR_MD[63..0]

MAB[13..0]

MAA[13..0]

DR_MEMDM[7..0]

-DR_MDQS[7..0]

2

DR_MD23

MAA7

MAA11

MAA9

MAA12

DR_MD22

MAB8

MAB7

DR_MD18

MAB9

DR_MEMDM2

MAB11

DR_MD21

-DR_MDQS2

DR_MD17

MAB12

DR_MD16

DR_MD20

MCKE04,7

MCKE14,7

DR_MD11

DR_MD15

DR_MD10

DR_MD14

DR_MEMDM1

DR_MD13

-DR_MDQS1

DR_MD12

DR_MD9

DR_MD8

DR_MD3

DR_MD6

DR_MD7

DR_MD2

-DR_MDQS0

DR_MEMDM0

DR_MD1

DR_MD5

DR_MD4

DR_MD0

DR_MD[63..0 ]7,9

DR_MEMDM[7..0]7,9

-DR_MDQS[7..0]7,9

3

-MCS34,7

-MCS24,7

-MSCASA4,7

-MCS14,7

-MCS04,7

-MSCASB4,7

-MSRASB4,7

-MSRASA4,7

-MSWEB4,7

-MSWEA4,7

MEMBANKA14,7

MEMBANKB14,7

MEMBANKA04,7

MEMBANKB04,7

MCKE14,7

MCKE04,7

MAB13

MAA13

MAA12

MAB12

MAB9

MAB11

MAA1

MAB1

MAB3

MAA3

MAB2

MAA2

MAB6

MAA6

MAA4

MAB4

MAA7

MAA8

MAA5

MAB5

MAA0

MAA10

MAB0

MAB10

MAA9

MAA11

MAB7

MAB8

-MSRASB

-MSRASA

-MSWEB

-MSWEA

MSI

Title

Size Do cument Number Rev

Date: Sheet

CN21

12

34

56

78

X_8P4C-22P

CN6

12

34

56

78

X_8P4C-22P

CN14

12

34

56

78

X_8P4C-22P

CN13

12

34

56

78

X_8P4C-22P

CN12

12

34

56

78

X_8P4C-22P

CN9

12

34

56

78

X_8P4C-22P

CN15

12

34

56

78

X_8P4C-22P

CN20

12

34

56

78

X_8P4C-22P

CN8

12

34

56

78

X_8P4C-22P

CN18

12

34

56

78

X_8P4C-22P

CN16

12

34

56

78

X_8P4C-22P

CN4

12

34

56

78

X_8P4C-22P

<OrgName>

DDR Terminations Part 1

MS-7112

1

831Monday, August 23, 2004

0A

of

Page 9

5

4

3

2

1

DDR Terminations

VCCM VCCM VCCM VCCMVTT_DDR VTT_DDRVTT_DDRVTT_DDR

C32

RN8 10-8P4R

MD0

D D

C C

B B

MEMDM3 DR_MEMDM3

1 2

MD4

3 4

MD5

5 6

MD1

7 8

RN10 10-8P4R

MEMDM0

1 2

-MDQS0

3 4

MD2

5 6

MD7 DR_MD7

7 8

RN12 10-8P4R

MD6 DR_MD6

1 2

MD3

3 4

MD8

5 6

MD9

7 8

RN15 10-8P4R

MD12

1 2

-MDQS1 -DR_MDQS1

3 4

MD13 DR_MD13

5 6

MEMDM1 DR_MEMDM1

7 8

RN18 10-8P4R

MD14

1 2

MD10

3 4

MD15

5 6

MD11

7 8

RN26 10-8P4R

MD21 DR_MD21

1 2

MEMDM2 DR_MEMDM2

3 4

MD18 DR_MD18

5 6

MD22 DR_MD22

7 8

RN21 10-8P4R

MD20

1 2

MD16

3 4

MD17

5 6

-MDQS2

7 8

RN30 10-8P4R

MD23

1 2

MD19 DR_MD19

3 4

MD24

5 6

MD28 DR_MD28

7 8

RN33 10-8P4R

MD29

1 2

MD25

3 4

-MDQS3

5 6

7 8

-MDQS[7..0]4

-DR_MDQS[7..0]7,8

DR_MD[63..0]7,8

MD[63..0]4

MEMDM[7..0]4

A A

DR_MEMDM[7..0]7,8

DR_MD0

DR_MD4

DR_MD5

DR_MD1

DR_MEMDM0

-DR_MDQS0

DR_MD2

DR_MD3

DR_MD8

DR_MD9

DR_MD12

DR_MD14

DR_MD10

DR_MD15

DR_MD11

DR_MD20

DR_MD16

DR_MD17

-DR_MDQS2

DR_MD23

DR_MD24

DR_MD29

DR_MD25

-DR_MDQS3

-MDQS[7..0]

-DR_MDQS[7..0]

DR_MD[63..0]

MD[63..0]

MEMDM[7..0]

DR_MEMDM[7..0]

RN37 10-8P4R

MD26

1 2

MD30

3 4

MD27

5 6

MD31

7 8

RN43 10-8P4R

MD32

1 2

MD36

3 4

MD33

5 6

MD37

7 8

RN45 10-8P4R

-MDQS4 -DR_MDQS4

1 2

MEMDM4 DR_MEMDM4

3 4

MD34 DR_MD34

5 6

MD38 DR_MD38

7 8

RN48 10-8P4R

MD39 DR_MD39

1 2

MD40

3 4

MD35

5 6

MD44

7 8

RN51 10-8P4R

MD41 DR_MD41

1 2

-MDQS5

3 4

MD45 DR_MD45

5 6

MEMDM5 DR_MEMDM5

7 8

RN54 10-8P4R

MD42 DR_MD42

1 2

MD43

3 4

MD46 DR_MD46

5 6

MD47

7 8

RN56 10-8P4R

MD49 DR_MD49

1 2

MD48

3 4

MD52 DR_MD52

5 6

MD53 DR_MD53

7 8

RN58 10-8P4R

MEMDM6

1 2

-MDQS6

3 4

MD54

5 6

MD50 DR_MD50

7 8

RN60 10-8P4R

MD55

1 2

MD51

3 4

MD56

5 6

MD60 DR_MD60

7 8

RN63 10-8P4R

MD61

1 2

MD57

3 4

MEMDM7 DR_MEMDM7

5 6

-MDQS7 -DR_MDQS7

7 8

RN66 10-8P4R

MD62 DR_MD62

1 2

MD58

3 4

MD63

5 6

MD59

7 8

DR_MD26

DR_MD30

DR_MD27

DR_MD31

DR_MD32

DR_MD36

DR_MD33

DR_MD37

DR_MD40

DR_MD35

DR_MD44

-DR_MDQS5

DR_MD43

DR_MD47

DR_MD48

DR_MEMDM6

-DR_MDQS6

DR_MD54

DR_MD55

DR_MD51

DR_MD56

DR_MD61

DR_MD57

DR_MD58

DR_MD63

DR_MD59

X_0.22uF

C133

X_0.22uF

C182

X_0.22uF

C30

X_0.22uF

C122

X_0.22uF

VTT_DDR

1u

1u

C87

C75

C108

VTT_DDR

1u

C63

1u

C134

C138

VTT_DDR

C54

C118

X_C1000p50x

VTT_DDR

C44

475P/0805

C106

475P/0805

LAYOUT: Add 100pF and 1000pF on VTT fill near

1u

C78

1u

C140

C176

X_C1000p50x

GND

C157

475P/0805

1u

1u

C68

X_1u

C107

X_1u

C77

1u

C61

1u

C109

X_1u

C98

X_1u

C97

C73

X_C1000p50x

GND

1u

X_1u

C180

475P/0805

1u

C99

1u

C145

VTT_DDR

Clawhammer and near DIMMs (both sides).

5

4

3

2

C103

1u

C40

X_1u

C136

X_1u

C139

1u

C131

X_1u

C147

1u

1u

1u

C110

C137

GND

1u

1u

1u

C153

C169

C160

GND

C150

X_1u

C163

1u

C171

X_1u

VTT_DDR

12

12

+

+

EC23

GND

C100u16d6

Title

EC10

C100u16d6

0.22uf

0.22uf

C55

C113

GND

<OrgName>

DDR Terminations Part 2

Size Document Number Rev

MS-7112

Date: Sheet

931Monday, August 23, 2004

1

0A

of

Page 10

8

A

D D

C C

CLKON14

CLKOP14

CLKON04

CLKOP04

CTLON04

CTLOP04

B B

-LDTSTOP5

LDTREQ#15

-CPURST5

CPUCLK-13

CPUCLK13

7

CADON0

CADOP0

CADON1

CADOP1

CADON2

CADOP2

CADON3

CADOP3

CADON4

CADOP4

CADON5

CADOP5

CADON6

CADOP6

CADON7

CADOP7

CADON8

CADOP8

CADON9

CADOP9

CADON10

CADOP10

CADON11

CADOP11

CADON12

CADOP12

CADON13

CADOP13

CADON14

CADOP14

CADON15

CADOP15

LRCOMP

CPUCLK1_CL

CPUCLK1_CH

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

-LDTSTOP

LDTREQ#

-CPURST

R101

75

CADIN[0..15]

CADIP[0..15]

CADOP[0..15]

CADON[0..15]

R102

N27

P27

M29

N29

L27

M27

K29

L29

H29

J29

G27

H27

F29

G29

E27

F27

N24

P24

M25

N25

L26

M26

K24

L24

H26

J26

G24

H24

F25

G25

E26

F26

C28

J25

K25

J27

K27

D29

E29

A11

A12

C11

B11

C12

B12

E11

D12

D11

R104

75

CPUCLK1_CL

169RST

CPUCLK1_CH

LRCAD_N0

LRCAD_P0

LRCAD_N1

LRCAD_P1

LRCAD_N2

LRCAD_P2

LRCAD_N3

LRCAD_P3

LRCAD_N4

LRCAD_P4

LRCAD_N5

LRCAD_P5

LRCAD_N6

LRCAD_P6

LRCAD_N7

LRCAD_P7

LRCAD_N8

LRACD_P8

LRCAD_N9

LRCAD_P9

LRCAD_N10

LRCAD_P10

LRCAD_N11

LRCAD_P11

LRCAD_N12

LRCAD_P12

LRCAD_N13

LRCAD_P13

LRCAD_N14

LRCAD_P14

LRCAD_N15

LRCAD_P15

LRCOMP

LRCLK_N1

LRCLK_P1

LRCLK_N0

LRCLK_P0

LRCTLN

LRCTLP

HTCLKN

HTCLKP

HTAVDD

HTAVSS

HTPHYAVDD

HTPHYAVSS

LDTSTOP#

LDTREQ#

LDTRESET#

CADIN[0..15]4

CADIP[0..15]4

CADOP[0..15]4

CADON[0..15]4

C179

3900P

C175

3900P

NB1A

SiS760GX

VDD_12_A

CB20

104P

6

CADIP10

CADIP11

CADIN12

CADIN13

CADIN15

CADIN14

CADIP13

CADIP14

CADIP15

D24

E23

F22

D25

E24

LTCAD_P15

LTCAD_P14

LTCAD_P13

LTCAD_N15

LTCAD_N14

HOST_RX

CADIN10

CADIP12

CADIN11

D21

F19

D18

F23

D22

F20

D19

LTCAD_P12

LTCAD_P11

LTCAD_P10

LTCAD_N13

LTCAD_N12

LTCAD_N11

LTCAD_N10

HOST_TX

CADIP9

CADIN9

E17

E18

LTCAD_P9

LTCAD_N9

CADIP8

CADIN8

F16

F17

LTCAD_P8

LTCAD_N8

5

CADIP7

CADIN7

A24

A25

LTCAD_P7

LTCAD_N7

CADIP6

CADIN6

C23

C24

LTCAD_P6

LTCAD_N6

CADIP5

CADIN5

A22

A23

LTCAD_P5

LTCAD_N5

CADIP4

CADIN4

C21

C22

LTCAD_P4

LTCAD_N4

CADIP3

CADIN3

C19

C20

LTCAD_P3

LTCAD_N3

CADIP2

CADIN2

A18

A19

LTCAD_P2

LTCAD_N2

CADIP1

CADIN1

C17

C18

LTCAD_P1

LTCAD_N1

CADIP0

CADIN0

A16

A17

LTCAD_P0

LTCAD_N0

4

A20

E20

E21

A21

LTCLK_P0

LTCLK_P1

LTCLK_N1

LTCLK_N0

760-1

AGP

SBA7D2SBA6G5SBA5D3SBA4F4SBA3F5SBA2E4SBA1B3SBA0D5ST0C5ST1A5ST2B4AAD0V5AAD1U6AAD2U1AAD3U4AAD4U3AAD5T5AAD6T3AAD7T6AAD8R2AAD9P1AAD10R5AAD11P3AAD12P4AAD13N2AAD14P6AAD15N3AAD16L3AAD17K2AAD18K5AAD19K6AAD20K3AAD21J4AAD22J1AAD23J5AAD24G2AAD25H4AAD26G3AAD27F1AAD28F2AAD29H6AAD30E1AAD31

GAD18

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

AGPST0

SBA0

SBA1

VDD_12_A

R77 100

R76 49.9RST

R75 49.9RST

AGPST2

AGPST1

GAD0

GAD1

GAD2

GAD3

GAD4

GAD6

GAD5

LRCOMP

LTCOMPN

LTCOMPP

GAD7

GAD8

GAD10

GAD9

GAD16

GAD15

GAD12

GAD17

GAD14

GAD11

GAD13

GAD24

GAD21

GAD23

GAD19

GAD20

GAD25

GAD22

VCC2.5

R98 1K

R94 1K

C25

C26

LTCTLP

LTCTLN

PIPE#/ADBIH

AGPCOMP_P

AGPCOMP_N

AGPVSSREF

GAD27

GAD26

GAD28

LTCOMPN

LTCOMPP

A27

B28

LTCOMP_P

LTCOMP_N

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

GC_DET#

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

E3

GAD29

GAD30

GAD31

LDTREQ#

-CPURST

H3

L4

N5

R4

A6

B6

L6

L1

M4

M5

M1

M2

N6

C4

A3

D6

G6

E6

C1

C2

T2

R1

J2

H1

AA1

V2

V3

AA4

AA5

AA2

AA3

V1

V4

3

CLKIN0 4

CLKIP0 4

CLKIN1 4

CLKIP1 4

CTLIN0 4

CTLIP0 4

GC/BE#3

GC/BE#2

GC/BE#1

GC/BE#0

DBIH

DBIL

ADSTB0

ADSTB#0

ADSTB1

ADSTB#1

AGPRCOMP

AGPRCOMN

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

CP55

X_Copper

2

GAD[0..31]

SBA[0..7]

GC/BE#[0..3]

AGPST[0..2]

ADSTB[0..1]

ADSTB#[0..1]

A4XAVDD

A4XAVSS

GREQ# 18

GGNT# 18

GFRAME# 18

GIRDY# 18

GTRDY# 18

GDEVSEL# 18

GSERR# 18

GSTOP# 18

GPAR 18

RBF# 18

WBF# 18

GCDET# 18

DBIH 18

DBIL 18

SBSTB 18

SBSTB# 18

A1XAVDD

A1XAVSS

AGP3.0 = 50 ohm

AGPCLK1 3

GVREFGC 18

C211

104P

MSI

Title

Size Document Number Rev

Date: Sheet of

AGPRCOMN

AGPRCOMP

HTPHYAVDD

CB23

104P

HTPHYAVSS

HTAVDD

CB26

104P

HTAVSS

<OrgName>

SiS 760 -1 Host / AGP

MS-7112

CB25

104P

CB21

104P

GAD[0..31] 18

SBA[0..7] 18

GC/BE#[0..3] 18

AGPST[0..2] 18

ADSTB[0..1] 18

ADSTB#[0..1] 18

X_Copper

FB5

X_120_600mA

CB95

C1000p50x_B

X_Copper

X_Copper

FB3

X_120_600mA

CB94

C1000p50x_B

X_Copper

R128 49.9RST

R129 43.RST

CP13

X_Copper

FB4

X_120_600mA

CB24

C1000p50x

CP53

X_Copper

CP17

X_Copper

FB6

X_120_600mA

CB27

C1000p50x

CP15

X_Copper

CP16

CP14

CP11

CP12

10 31Monday, August 23, 2004

1

VDDQ

VCC3

VCC3

VCC3

C173

C10u10y_1206

VCC3

C167

C10u10y_1206

0A

A

Page 11

8

A

NB1B

AA27

DQB0

AB28

DQB1

AB29

DQB2

AC29

DQB3

AB26

DQB4

AA26

D D

C C

B B

AA25

Y25

Y24

AA29

AF28

AH28

AG27

AH27

AF26

AE25

AD25

AD24

AE26

AG29

AC27

AD29

AD28

AD27

AE29

AC26

AC25

AB24

AE27

AF29

AJ27

AG26

AJ26

AG25

AH25

AG24

AF24

AE23

AF23

AJ24

AJ15

AG16

AH16

AJ16

AE16

AD16

AF17

AD17

AE18

AJ17

AG11

AJ11

AG12

AH12

AF11

AD11

AE12

AD12

AE13

AJ12

AG15

AJ14

AH14

AJ13

AE15

AF15

AF14

AD14

AF13

AG13

AJ10

AH10

AJ9

AG9

AF10

AE10

AD10

AF9

AD9

AH8

DQB5

DQB6

DQB7

DQMB0

DDRBSTB0

DQB8

DQB9

DQB10

DQB11

DQB12

DQB13

DQB14

DQB15

DQMB1

DDRBSTB1

DQB16

DQB17

DQB18

DQB19

DQB20

DQB21

DQB22

DQB23

DQMB2

DDRBSTB2

DQB24

DQB25

DQB26

DQB27

DQB28

DQB29

DQB30

760 -2

DQB31

DQMB3

DDRBSTB3

DQB32

DQB33

DQB34

DQB35

DQB36

DQB37

DQB38

DQB39

DQMB4

DDRBSTB4

DQB40

DQB41

DQB42

DQB43

DQB44

DQB45

DQB46

DQB47

DQMB5

DDRBSTB5

DQB48

DQB49

DQB50

DQB51

DQB52

DQB53

DQB54

DQB55

DQMB6

DDRBSTB6

DQB56

DQB57

DQB58

DQB59

DQB60

DQB61

DQB62

DQB63

DQMB7

DDRBSTB7

SiS760GX

8

7

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

WEB

RASB

CASB

SDCLKBN0

SDCLKBN1

SDCLKBP0

SDCLKBP1

CKEB

CSB

DRAMTRAP0

DRAMTRAP1

DRAMTRAP2

DRAMTRAP3

DDRVREFB0

DDRVREFB1

ECLKAVDD

ECLKAVSS

VOSCIE

AJ21

AG22

AH22

AJ23

AH23

AD22

AF22

AD21

AG21

AE21

AE20

AF20

AH20

AJ20

AH18

AG19

AJ19

AG18

AD19

AG17

AD18

AF19

AG20

W26

Y26

Y27

Y28

AJ8

Y29

W28

W29

W27

6

DDRVREFA

DDRVREFB

VOSCIE

CP54 X_Copper

CP52 X_Copper

ECLKAVDD

ECLKAVSS

VOSCIE 3

5

4

3

2

1

SiS760 without Local Frame Buffer

1. Vref -Tie ground (R47,R48 open)

2. MD,DQS,MA,CLK - floation

3. OVDDM connect to VCC3

4. SiS760 seven pins of VBTRAP[3:0],

ECLKAVDD/AVSS, VOSCIE must connect on

board

VCC3

CP8

X_Copper

ECLKAVDD

CB7

104P

ECLKAVSS

FB2

X_120_600mA

CB9

C1000p50x

CP9

X_Copper

C144

X_C10u10y_1206

SiS760 without Local Frame Buffer

Vref -Tie ground

MSI

Title

Size Document Number Rev

7

6

5

4

3

Date: Sheet

2

<OrgName>

SiS 760-2 Frame Buffer

MS-7112

11 31Monday, August 23, 2004

0A

of

1

A

Page 12

8

A

7