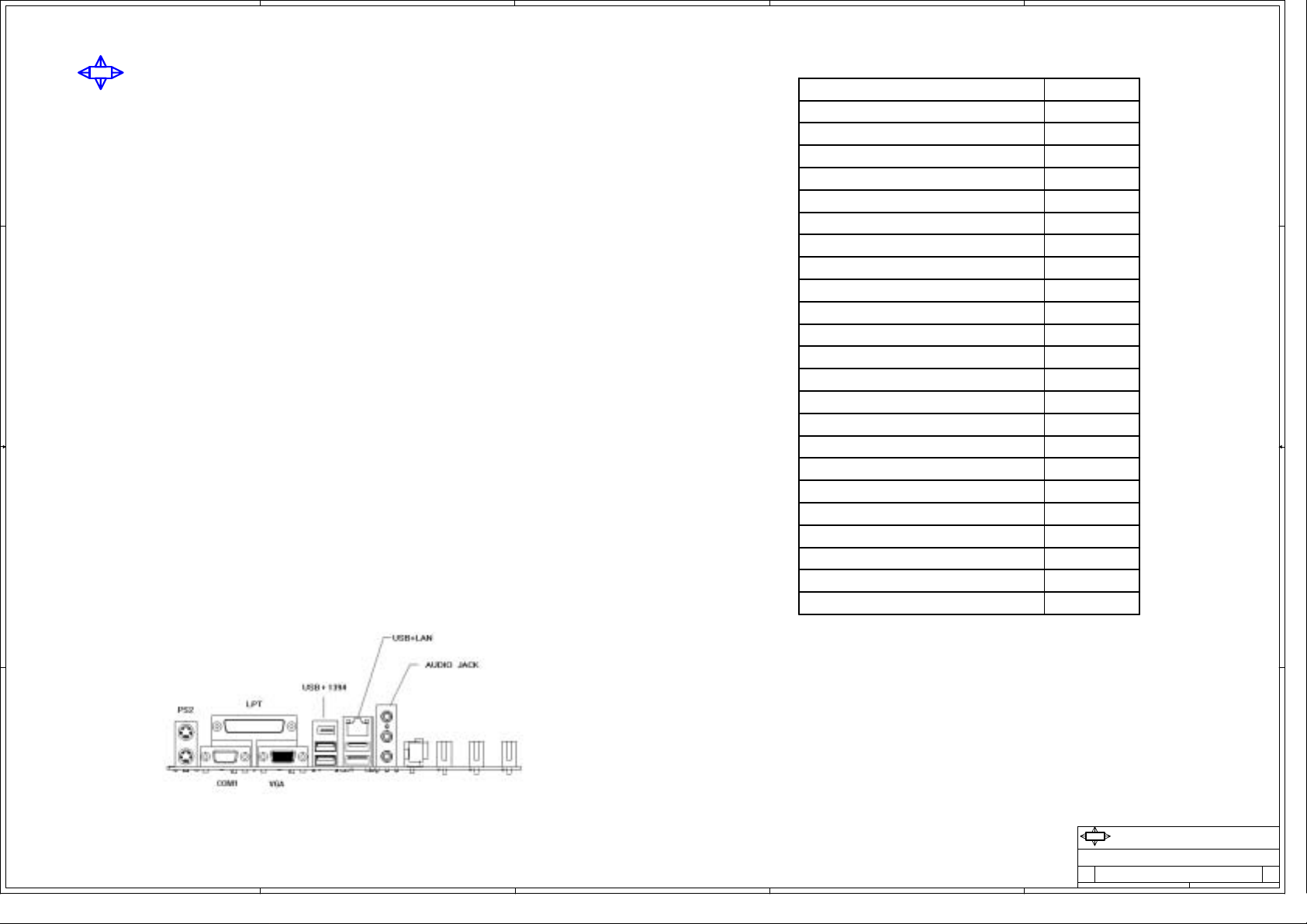

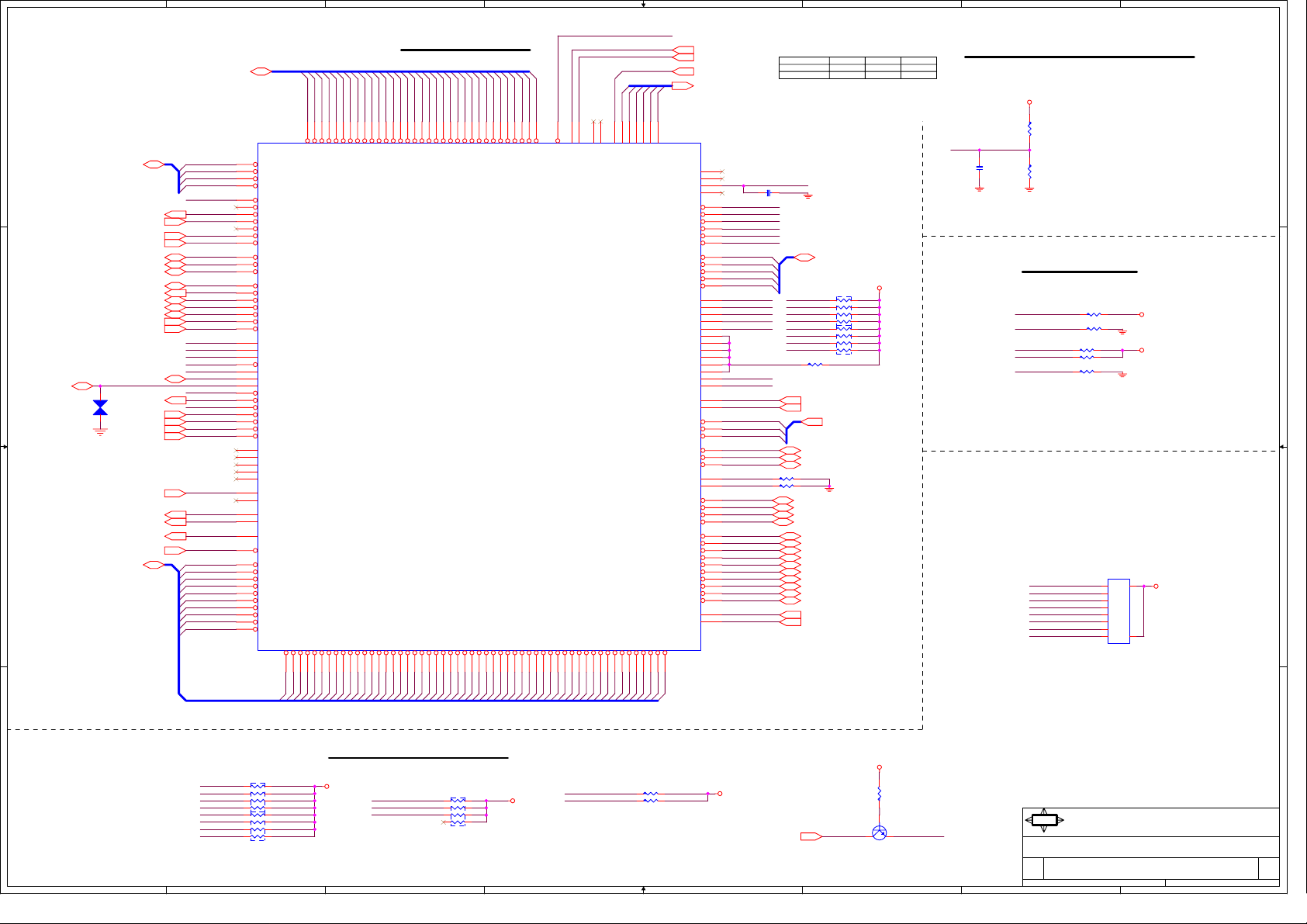

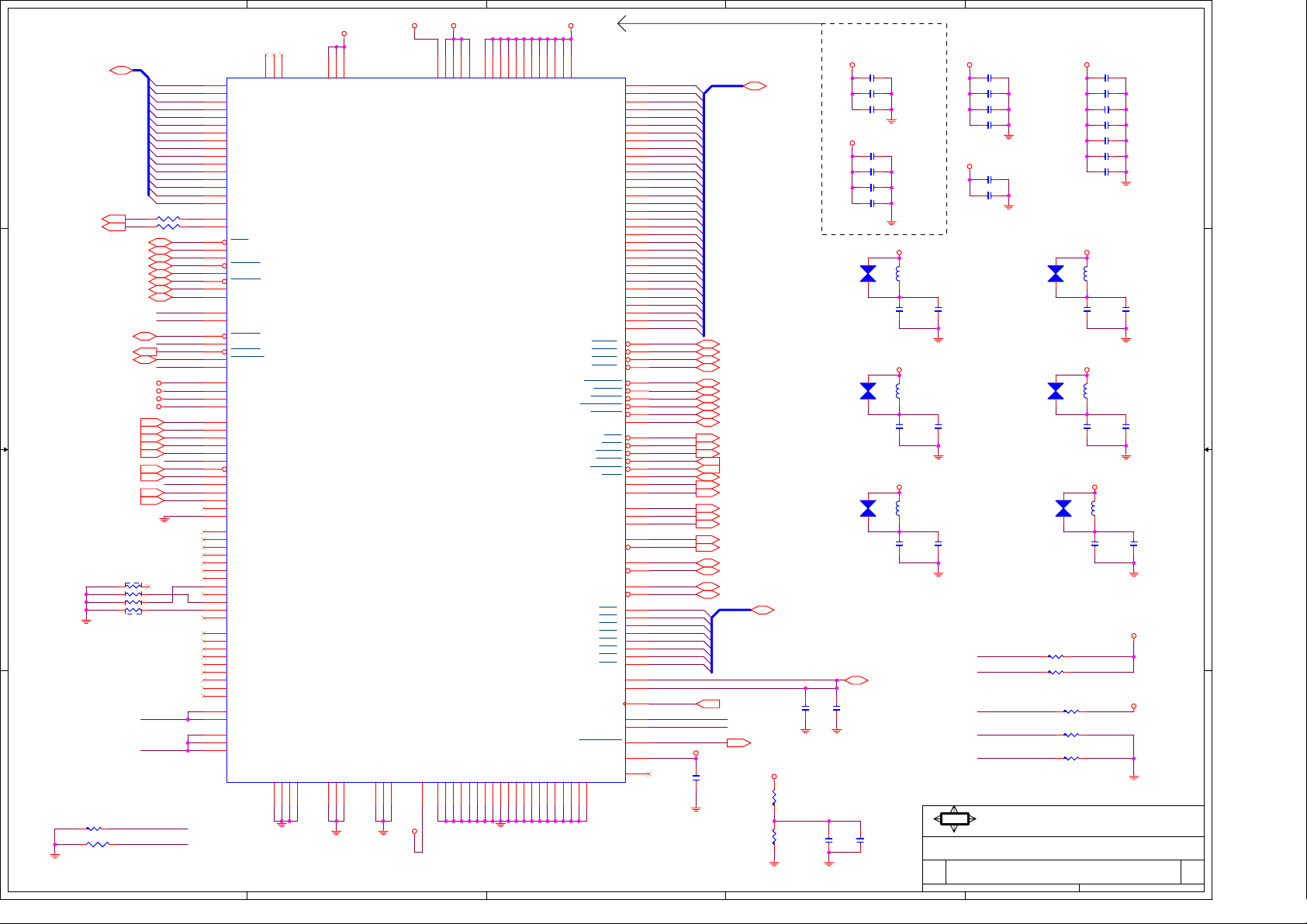

MSI MS-7055 Schematics

A

B

C

D

E

MSI

4 4

MS-7055 Ver:1.0A

CPU:

Intel Northwood/Prescott

(FMB1.5)

System Chipset:

PM800/PT800/PT880/PM880

VIA 8237 (South Bridge)

On Board Chipset:

LPC Super I/O -- W83697HF

LAN -- RTL8110S/8100C

IEEE1394 -- VT6307

AC'97 Codec --ALC655

BIOS --ISA FLASH ROM

3 3

CLOCK Chip :

CLOCK Generator --ICS 950911

CLOCK Buffer -- ICS93733CF

Main Memory:

DDR * 2 (Max 2GB)

Expansion Slots:

PCI2.3 SLOT * 3

PWM:

Intersil 6556B

2 2

CHIPSET PM800 + 8237

TITLE

Cover Sheet

Block Diagram

PWR map/CLOCK map

GPIO/MEMORY/PCI/HW STRPPING

PROCESSOR (SOCKET478)

NORTH BRIDGE (PM800/PM880)

DIMM1 / DIMM2

DDR TERMINATIONS

AGP SLOT

VGA Connector

CLOCK & BUFFER SYNTHESIZER

SOUTH BRIDGE (VT8237)

PCI SLOTS

1394a PCI Controller

LAN RTL8110S/8100C

SIO & H/W monitor & FAN

ALC655 / Connectors

IDE & KB/MS & IrDA

USB CONNECTORS

COM1/COM2/LPT & WOL/WOM

MS7 ACPI controller

VRM10 - INTERSIL 6556B

ATX & F-Panel & BIOS

SHEET

1

2

3

4

5,6

7,8,9,10

11

12

13

14

15

16,17,18

19

20

21

22

23

24

25

26

27

28

29

1 1

MICRO-STAR INt'L CO., LTD.

MSI

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

COVER SHEET

Wednesday, April 21, 2004

MS-7055

E

131

1.0A

of

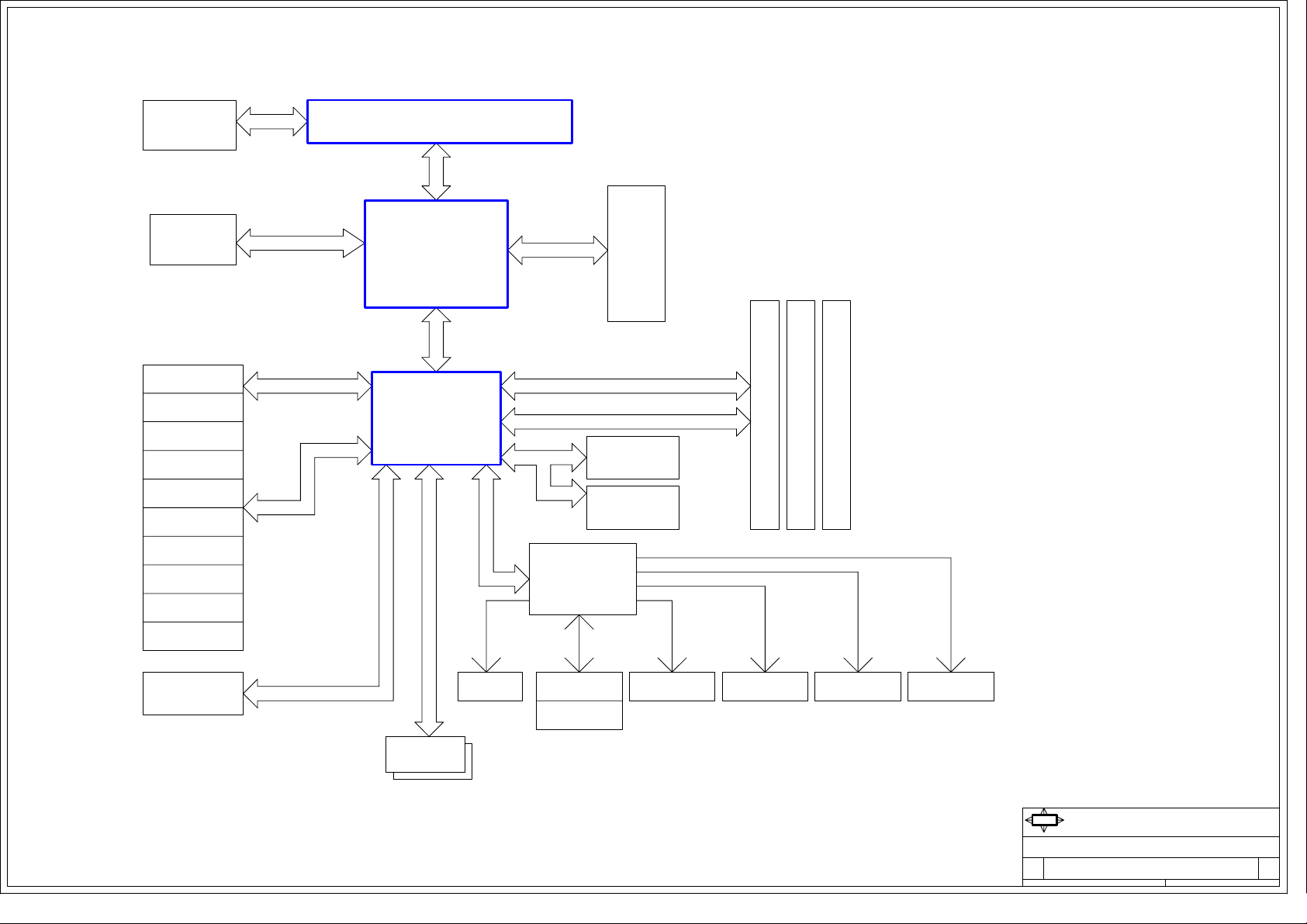

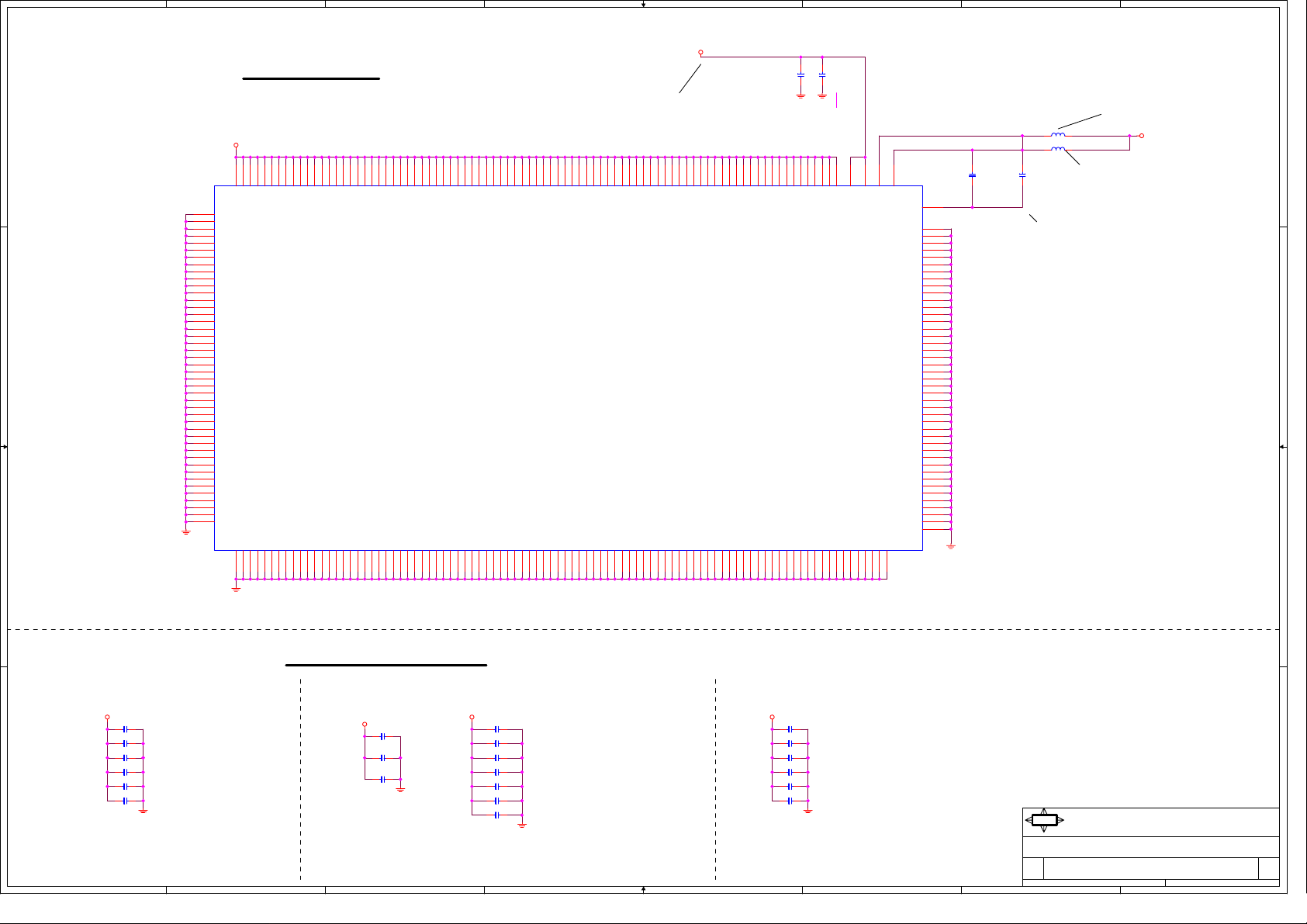

Block Diagram

1

VRM 10

Intersil

Intel mPAG478B Processor

3-Phase PWM

FSB

AGP 1.5V

Connector

2X/4X/8X

PM800

64bit DDR

2 DDR

DIMM

Modules

V-Link

IDE Primary

IDE Secondary

A A

USB Port 0

UltraDMA 33/66/100

VT8237

PCI BUS

USB Port 1

USB Port 2

USB

LPC Bus

USB Port 3

PCI CNTRL

PCI ADDR/DATA

LAN

Realtek

8100C

IEEE1394

VT6307

2Port

PCI Slot 1

PCI Slot 2

PCI Slot 3

USB Port 4

LPC SIO

USB Port 5

Winbond

83697HF

USB Port 6

USB Port 7

AC'97 Codec

AC'97 Link

SATA prot1 and

port2

ISA FLASH

ROM

KEYBOARD

MOUSE

FDD

1

Parallel

Serial

X2

IrDA

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

BLOCK DIAGRAM

Wednesday, April 21, 2004

MS-7055

231

of

1.0A

8

7

6

5

4

3

2

1

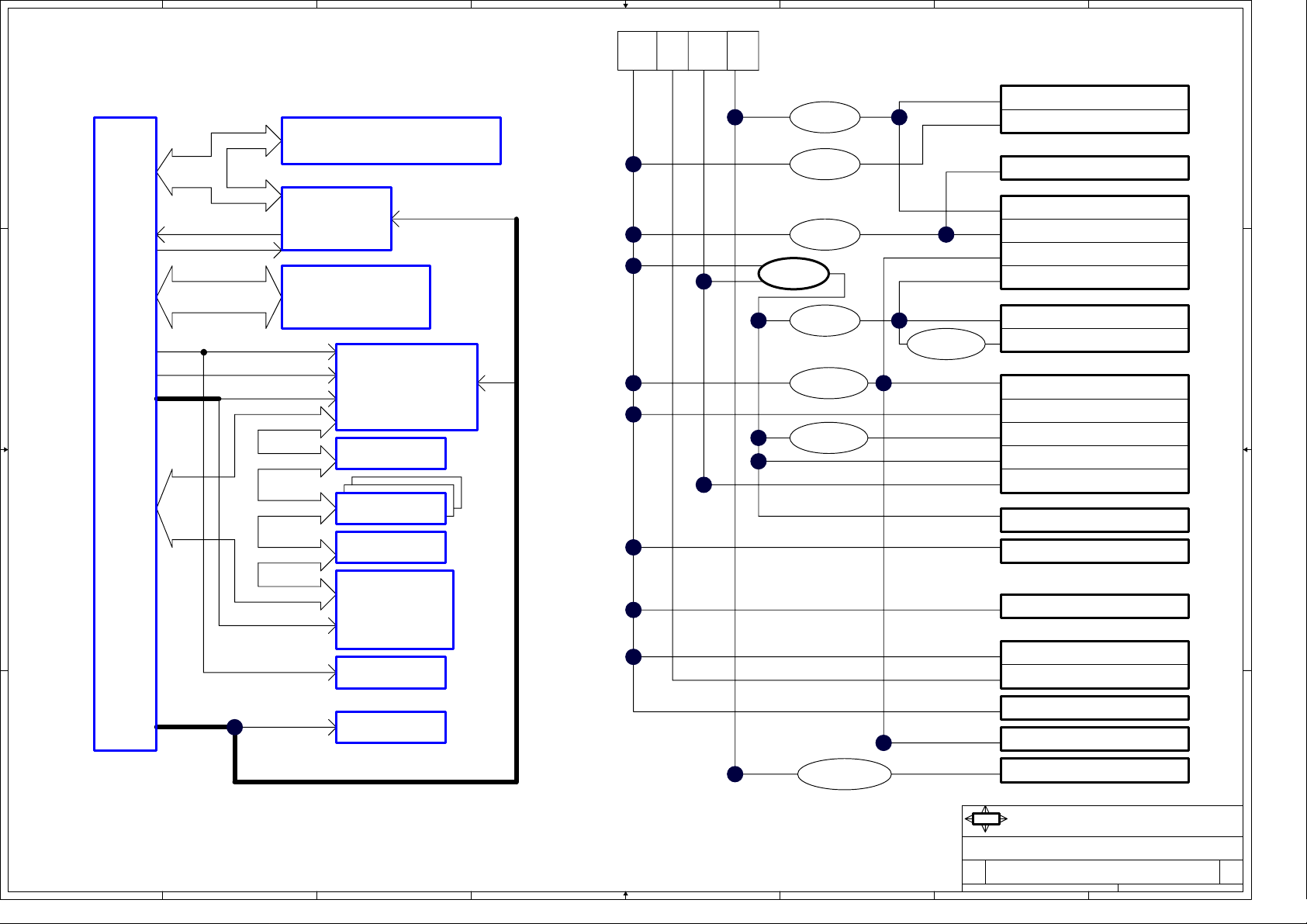

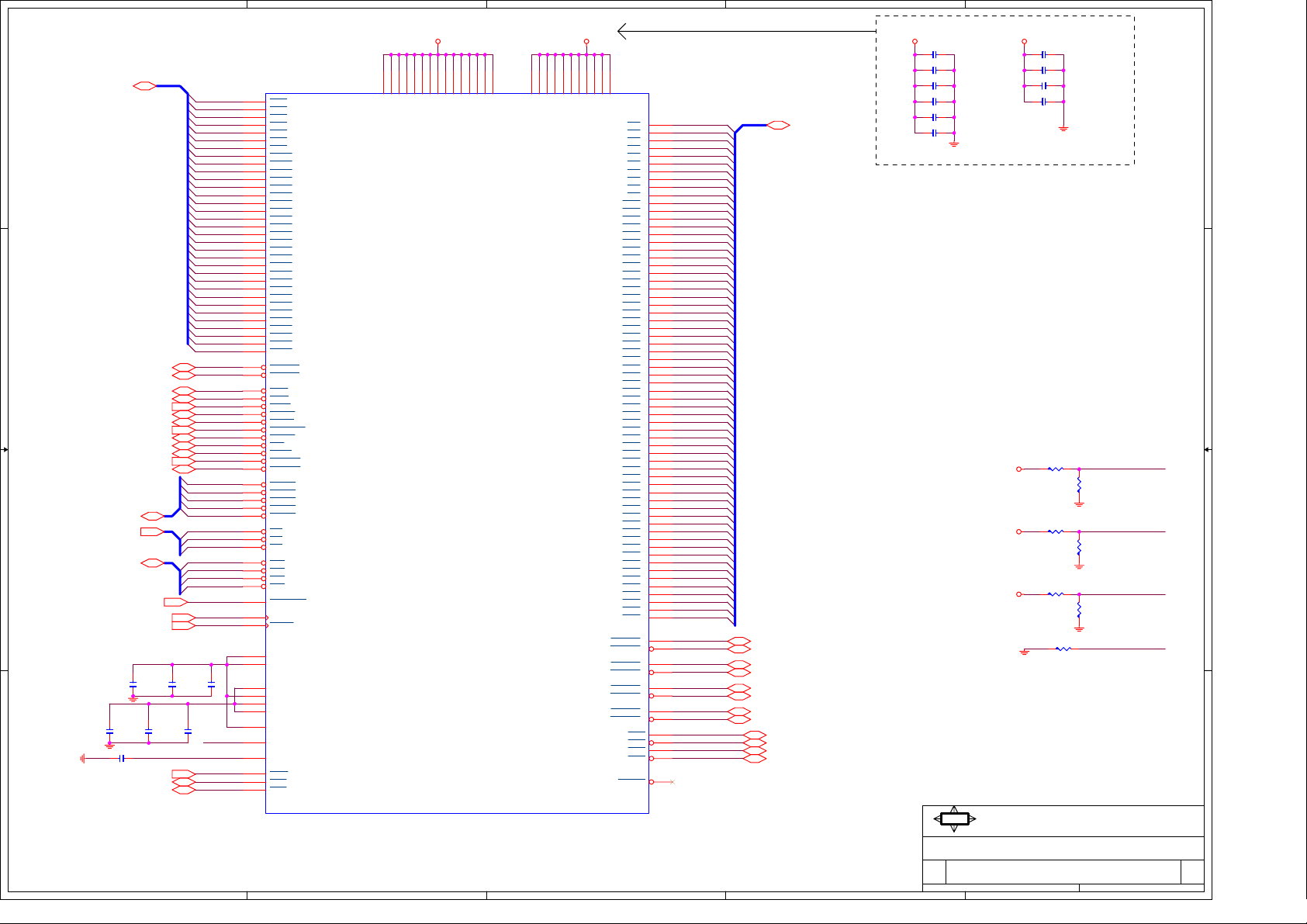

PT800 PLATFORM CLOCK GENERATOR MAP

3.3V 5V 5VSB 12V

PT800 PLATFORM POWER DELIVERY MAP

PROCESSOR VCCP

D D

VRM

PROCESSOR 1.2V

Intel mPAG478B Processor

CPU HOST

CLK

DCLKO

NB

PM880

AGP CLK

1.2V VREG

1.5V VREG

DCLKI

CLOCK

GENERATOR

MEM CLK

0~5/CLK#0~5

C C

14.318MHZ

2 DDR DIMM

Modules

3VSB VREG

DDR 2.5V

VREG

VTT 1.25V

VREG

APIC

48MHZ

VT8237

2.5V VREG

PCI CLK

2.5VSB

PCI CLK 4

PCI CLK 0~3

IEEE1394

PCI Slot 1~3

VREG

AGP SLOT 1.5V

NORTH BRIDGE VCCP

NORTH BRIDGE VCC_AGP

NORTH BRIDGE +2.5V

NORTH BRIDGE SYSEM MEMORY

VCC_DDR

DDR DIMM1 / DIMM2 / DIMM3 2.5V

DDR VTT 1.25V

SOUTH BRIDGE +2.5V

SOUTH BRIDGE VCC3

SOUTH BRIDGE RESUME 2.5V_SB

SOUTH BRIDGE RESUME VCC3_SB

SOUTH BRIDGE RTC 3.3V

LAN-PHY VCC3_SB

B B

PCI CLK

48MHZ

LAN 8100C

LPC SIO

Winbond

83627HF

PCI 1394 VCC3

FWH 3.3V

LPC SUPER I/O 3.3V

AC97

AGP CLK

A A

8

7

AGP SLOT

6

AC97 VDD5

VREG

Title

Size Document Number Rev

5

4

3

Date: Sheet

LPC SUPER I/O VCC5

CK-409 3.3V

CK-409 AND BUFFER +2.5V

AC97 VDD5

MSI

MICRO-STAR INt'L CO., LTD.

PWR AND CLOCK MAP

Wednesday, April 21, 2004

2

MS-7055

1.0A

331

of

1

1

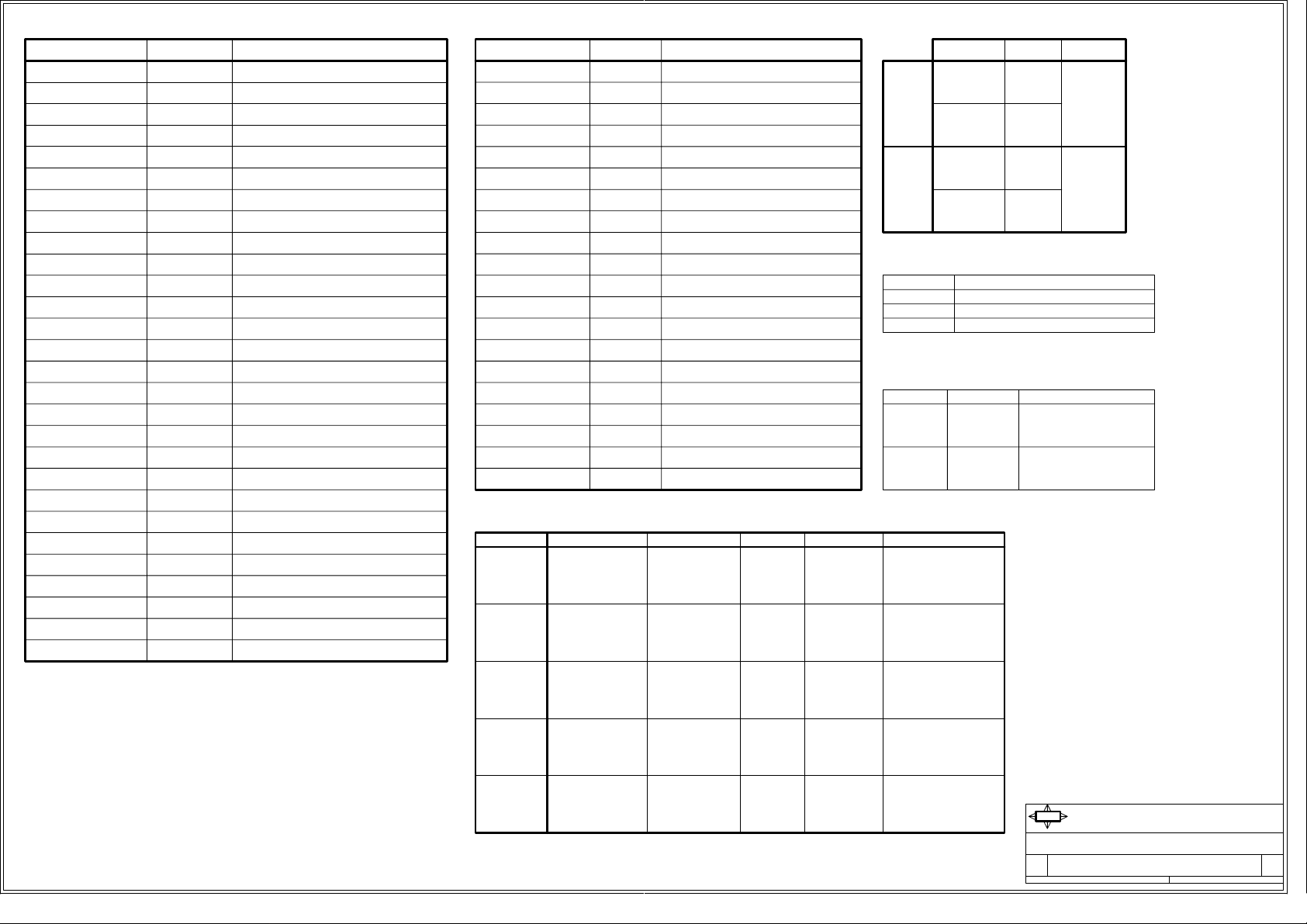

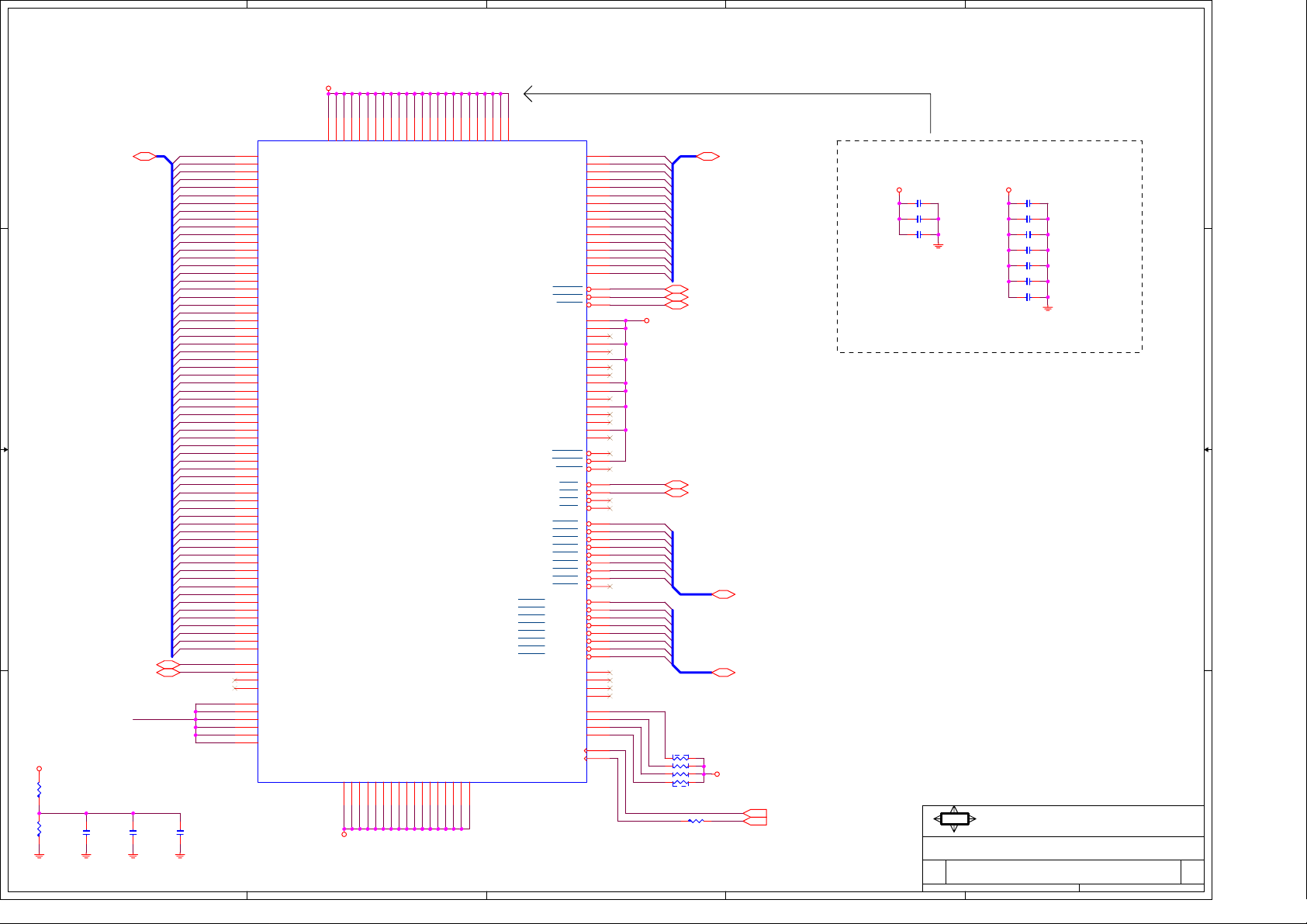

VT8237 GPIO Function Define

PIN NAME Function define

GPO0 (VDDS)

GPO1(VDDS)

GPO2/SUSA#

(VDDS)

GPO3/SUSST#(VDDS)

GPO4/SUSCLK(VDDS)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5

GPO8/GPI8/VGATE

*

GPO9/GPI9/UDPWREN

*

GPO10/GPI10/PICD0

*

GPO11/GPI11/PICD1

*

GPO12/GPI12/INTE#

*

GPO13/GPI13/INTF#

*

GPO14/GPI14/INTG#

*

GPO15/GPI15/INTH#

*

GPO20/GPI20

/ACSDIN2/PCS0#

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

A A

GPO22/GPI22/GHI#

GPO23/GPI23/DPSLP

/GPIOAGPO24/GPI24

GPO25/GPI25

GPO26/GPI26/SMBDT2

(VDDS)

GPO27/GPI27/SMBCK2

(VDDS)

GPO28/GPI28/VIDSEL

GPO29/GPI29/VRDSLP

GPO30/GPI30

GPO31/GPI31

/GPIOB

/GPIOC

/GPIOD

Default

Function

GPO0

GPO1 GPO1 SYS_FAN GPO Control

SUSA#

SUSST#

SUSCLK

CPUSTP#

PCISTP#

GPO7

GPI8

UDPWREN

GPI10

GPI11

GPI12

GPI13

GPI14

GPI15

GPI20/ACSDIN2

GPI21/ACSDIN3

GPI22

GPI23

GPI24

GPI25

SMBDT2

SMBCK2

GPO28

/VIDSEL

GPO29

/VRDSLP

GPI30

GPI31

CPU_FAN GPO ControlGPO0

4.7K ohm Pull up to VCC3_SB

SUSST#

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

2.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

10K ohm Pull down

1K ohm Pull up to VCC3

1K ohm Pull up to VCC3

INTE# 2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5INTH#

4.7K ohm Pull down

4.7K ohm Pull down

4.7K ohm Pull up to VCC3

4.7K ohm Pull up to VCC3

BSEL1

4.7K ohm Pull down

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3_SB

SATA_LED

4.7K ohm Pull down

BSEL0

4.7K ohm Pull down

PIN NAME Function define

GPI0

(VBAT)

GPI1

(VSUS3)

GPI2/EXTSMI#

(VSUS3)

GPI3/RING#

(VSUS3)

GPI4/LID#

(VSUS3)

GPI5/BATLOW# (VDDS)

GPI6/AGPBZ

GPI7/REQ5

GPI8/VGATE

*

GPI9/UDPWREN

*

GPI10/PICD0

*

GPI11/PICD1

*

GPI12/INTE#

*

GPI13/INTF#

*

GPI14/INTG#

*

GPI15/INTH# GPI15

*

GPI16/INTRUDER#

(VBAT)

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/APICCLK

PCI Config.

DEVICE

PCI Slot 1

PCI Slot 2

PCI Slot 3 PCIREQ#2 AD19

Default

Function

GPI0

GPI1

EXTSMI#

RING#

LID#

BATLOW#

AGPBZ

GPI7

GPI8

UDPWREN

GPI10

GPI11

GPI12

GPI13

GPI14

INTRUDER#

CPUMISS

AOLGP1

APICCLK

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#C

PIRQ#D

PIRQ#A

PIRQ#B

PIRQ#D

PIRQ#A

PIRQ#B

PIRQ#C

PIRQ#E

4.7K ohm Pull up to VBAT

ATADET0=>Detect IDE1 ATA100/66

4.7K ohm Pull up to VCC3_SB

RING#

4.7K ohm Pull up to VCC3_SB

ATADET1=>Detect IDE2 ATA100/66

4.7K ohm Pull up to VCC3_SB

4.7K ohm Pull up to VCC3

2.7K ohm Pull up to VCC5

4.7K ohm Pull up to VCC3

10K ohm Pull down

1K ohm Pull up to VCC3

1K ohm Pull up to VCC3

INTE# 2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5

2.7K ohm Pull up to VCC5INTH#

1M ohm Pull up to VBAT

4.7K ohm Pull up to VCC3_SB

THRM#

4.7K ohm Pull up to VCC3

APICCLK

PCIREQ#0

IDSEL

AD17PIRQ#B

CLOCKREQ#/GNT#

PCI_CLK0

PCIGNT#0

PCIREQ#1 AD18 PCI_CLK1

PCIGNT#1

PCI_CLK2

PCIGNT#2

PCIREQ#3IEEE1394 AD22

1394PCLK

PCIGNT#3

USB

Rear

Front

Port DATA +/-

I1394_USB1

LAN_USB1

JUSB1

JUSB2

USB1USB1+

USB0USB0+

USB2USB2+

USB3USB3+

USB4USB4+

USB6USB6+

USB5USB5+

USB7USB7+

PCI RESET DEVICE

Signals Target

PCIRST#1

PCIRST#2

HD_RST#

PCI slot 1-3

NB , Super I/O , LAN , 1394

Primary, Scondary IDE

DDR DIMM Config.

DEVICE

DIMM 1

DIMM 2

1010000B

1010001B

CLK GEN PIN OUTMCP1 INT Pin

14 (PCICLK1)

15 (PCICLK2)

16 (PCICLK3)

17 (PCICLK4)

CLOCKADDRESS

DCLKA0/MDCLKA#0

DCLKA1/MDCLKA#1

DCLKA2/MDCLKA#2

DCLKB0/MDCLKB#0

DCLKB1/MDCLKB#1

DCLKB2/MDCLKB#2

OC#

OC#1

( OC#0~3 )

OC#4

( OC#4~7 )

LAN

PIRQ#H

PCIREQ#4 AD29 LANPCLK

PCIGNT#4

1

20 (PCICLK5)

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

General Purpose Spec

Wednesday, April 21, 2004

MS-7055

431

of

1.0A

8

7

6

5

4

3

2

1

E24

D17#

H22

AE25A5A4

DBR#

D16#

D15#

D25

J21

D14#

VCC_SENSE

D13#

D23

DBRESET

VSS_SENSE

D12#

D11#

C26

H21

VCC_SENSE 28

VSS_SENSE 28

VID1

VID0

AE4

AE5

VID1#

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

A23

B22

B21

CPU_VID_GD 28

VID[0..5] 28

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

D0#

ZIF-SOCKET478

{Priority}

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI1

TESTHI0

HRS#2

HRS#1

HRS#0

AP#1

AP#0

HBR#0

COMP1

COMP0

NMI_SB

INTR

C54 220P

TESTHI5

VID[0..5]

VID2

VID4

VID3

VID5

AD26

AC26

AE1

AE2

AE3

AD2

AD3

VID4#

VID3#

VID2#

VID5#

ITP_CLK1

ITP_CLK0

VIDPWRGD

D10#

D9#

D8#

D7#

D6#

D5#

D4#

D3#

G22

B25

C24

C23

B24

D22

C21

A25

VIDPWRGD DC Specifications

VIL

VIH

It must rout to the enable pin of PWM and CK-409.

VIDGD to Vccp delay time is from 1ms to 10ms.

VIDGD rising time is 150ns.

GTLREF

X7R

TESTHI8

TESTHI1

TESTHI11

TESTHI9

DBRESET

TESTHI0

TESTHI12

CPURST#

R101

R20

61.9RST

R105

61.9RST

DP#3 7

DP#2 7

DP#1 7

DP#0 7

0.9

HREQ#[0..4] 7

62

CPUCLK# 15

CPUCLK 15

HRS#[0..2] 7

AP#1 7

AP#0 7

HBR#0 7

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI_SB 18

INTR 18

Min MaxTyp

VCCP

12

34

56

78

12

34

56

78

RN6

8P4R-62

RN45

8P4R-62

CPU GTL REFERNCE VOLTAGE BLOCK

0.3

0.63*VCCP => PM800/PM880

VCCP

R88

GTLREF

0.63*Vccp

C57

104P

X7R

100RST

R90

169RST

CPU ITP BLOCK

INTR

SMI#

A20M#

HINIT#

STPCLK#

NMI_SB

SLP#

IGNNE#

R58 X_150

R61 680

R62 X_39

R19 X_75

R59 X_27

10P8R-150

VCCP

VCCP

RN3

1

5

1

2

2

3

3

4

4

6

6

7

7

8

8

9

9510

VCCP

10

ITP_TDI

ITP_TRST#

ITP_TMS

ITP_TDO

ITP_TCK

CPU SIGNAL BLOCK

HA#[3..35]7

HA#17

A18#

D33#

M23

HA#16

A17#

D32#

H25

HA#15

A16#

D31#

K23

HA#14

A15#

D30#

J24

HA#13

A14#

D29#

L22

HA#12

A13#

D28#

M21

HA#11

A12#

D27#

H24

HA#25

HA#34

A35#

D50#

U24

HA#33

A34#

D49#

U26

A33#

D48#

HA#32

A32#

D47#

T23

HA#28

A31#

A30#

A29#

A28#

A27#

A26#

D46#

D45#

D44#

D43#

D42#

D41#

T22

T25

T26

R24

R25

P24

R21

D D

CPU1A

HDBI#0

HDBI#[0..3]7

FERR#18

STPCLK#18

HINIT#18

RSP#7

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HIT#7

HITM#7

HBPRI#7

C C

VTIN_GND22

CP1

X_COPPER

B B

HDEFER#7

CPU_TMPA22

12

CPUMISS17

IGNNE#18

SMI#18

A20M#18

SLP#18

BOOTSELECT28

BSEL015,17

BSEL115,17

CPU_GD27,28

CPURST#7

HD#[0..63]7

HDBI#1

HDBI#2

HDBI#3

IERR#

FERR#

STPCLK#

HINIT#

RSP#

HDBSY#

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

THERMTRIP#

CPUMISS

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

AC3

AF26

AB26

AE21

AF24

AF25

AD1

AE26

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

G25

P26

V21

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

HA#35

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

BOOTSELECT

OPTIMIZED/COMPAT#

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

D52#

D51#

V22

U21

V25

U23

HA#27

HA#30

HA#26

HA#29

HA#31

HA#24

A25#

D40#

N25

HA#23

A24#

D39#

N26

HA#22

A23#

D38#

M26

HA#21

A22#

D37#

N23

HA#20

A21#

D36#

M24

HA#19

A20#

D35#

P21

HA#18

A19#

D34#

N22

HA#10

A11#

D26#

G26

A10#

D25#

HA#9

L21

A9#

D24#

HA#8

D26

A8#

D23#

HA#7

F26

A7#

D22#

HA#6

E25

A6#

D21#

HA#5

F24

A5#

D20#

HA#4

F23

A4#

D19#

HA#3

A3#

D18#

G23

HD#0

HD#1

HD#6

HD#4

HD#3

HD#5

HD#7

HD#8

HD#52

HD#53

HD#50

HD#51

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#40

HD#41

HD#38

HD#39

HD#36

HD#37

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

HD#25

HD#24

HD#23

HD#22

HD#21

HD#20

HD#18

HD#19

HD#16

HD#17

HD#15

HD#14

HD#12

HD#13

HD#10

HD#11

HD#9

CPU STRAPPING RESISTORS

RN5

A A

TESTHI10

8

BPM#4

BPM#3

BPM#5

BPM#2

BPM#1

IERR#

BPM#0

8P4R-62

7

12

34

56

78

12

34

56

78

8P4R-62

RN1

VCCP

FERR#

THERMTRIP#

PROCHOT#

6

RN4

8P4R-62

12

VCCP

34

56

78

ALL COMPONENTS CLOSE TO CPU

CPU_GD

HBR#0

5

HD#2

VCCP

R99

300

R63

220

VCCP

4

THERM#17

THERM# PROCHOT#

R7

4.7K

B

C E

Q3 2N3904S

3

MSI

Title

Size Document Number Rev

Date: Sheet

2

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Signals

Wednesday, April 21, 2004

MS-7055

531

of

1

1.0A

8

7

6

5

4

3

2

1

VCC_VID

CPU VOLTAGE BLOCK

VID Voltage is from 1.14V to 1.32V.

It is derived from 3.3V.

It should be able to source 150mA.

D D

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

CPU1B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA23

C C

B B

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B23

B20

B26B4B8

C11

C13

AF19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C15

C17C2C19

C22

C25C5C7C9D12

It drives the power logic of BSEL[1:0] and VID[5:0].

VID to VIDGD delay time is from 1ms to 10ms.

VID to VIDGD deassertion time is 1ms for max.

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D14

D16

D18

D20

D21D3D24D6D8E1E11

VCC

VSS

C12

C14

C16

C18

C20C8D11

D13

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E4

E26

D15

D17

VCC

VCC

VSS

VSS

E7E9F10

D19D7D9

VCC

VSS

F12

VCC

VSS

F14

VCC

VSS

VCC_VID

E10

E12

VCC

VSS

F16

F18F2F22

VCC

VSS

105P

E14

VCC

VSS

C18

E16

E18

VCC

VSS

F25F5F8

VCC

VSS

E20E8F11

VCC

VCC

VSS

VSS

Near processor

F13

F15

VCC

VCC

VSS

VSS

G21G6G24

G3H1H23

1.2V 150mA

C9

104P

F17

F19

F9

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

AF4

VSS

H26H4J2

VCC-VID

VSS

AF3

VSS

J22

AD20

VCC-VIDPRG

VSS

VSS

J25J5K21

AE23

VSSA

VCCA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

ZIF-SOCKET478

{Priority}

CPU_IOPLL

C59

X_106P/1206

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VSSA

The ESL is less than 5nH, and the ESR is less than 0.3ohm.

L8

L7

C60

106P/1206

It support DC current if 100mA.

10U100m_0805

10U100m_0805

DC voltage drop should

be less than 70mV.

VCCP

CPU DECOUPLING CAPACITORS

ON THE INSIDE OF SOCKET ON THE EDGE

VCCP

A A

8

C44

X_106P/1206

C31

X_106P/1206

C37

X_106P/1206

C56

X_106P/1206

C41

X_106P/1206

C48

X_106P/1206

7

VCCP

CT7

C100U2.5SP

CT8

C220U2SP

CT9

C220U2SP

6

VCCP VCCP

C39

X_106P/0805

C35

X_106P/0805

C49

X_106P/0805

C51

X_106P/0805

C53

X_106P/0805

C50

X_106P/0805

C52

X_106P/0805

5

4

C40

X_106P/0805

C42

X_106P/0805

C43

X_106P/0805

C45

X_106P/0805

C46

X_106P/0805

C36

X_106P/0805

MSI

Title

Size Document Number Rev

3

Date: Sheet

2

MICRO-STAR INt'L CO., LTD.

Intel mPGA478B - Power

Wednesday, April 21, 2004

MS-7055

631

1

1.0A

of

A

HA#[3..35]5

4 4

3 3

HADSTB#05

HADSTB#15

HADS#5

HBNR#5

HBPRI#5

HBR#05

HDBSY#5

HDEFER#5

HDRDY#5

HIT#5

HITM#5

HLOCK#5

HTRDY#5

HREQ#[0..4]5

HRS#[0..2]5

2 2

1 1

HDBI#[0..3]5

near NB

near NB

103P

C100

CPURST#5

NBHCLK#15

NBHCLK15

C102

103P

GTLVREF_NB1

C281

103PC101

RSP#5

AP#05

AP#15

GTLVREF_NB

103P-B

C105

103P

103P-B

HCOMPVREF

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

HBR#0

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

CPURST#

103P-B

C282

HRCOMP

C280

G18

G22

G14

B22

A20

A21

B21

E23

C21

D21

E22

C22

E21

D22

C25

C24

D24

E24

E25

B26

B23

E26

D25

E27

C23

D27

D28

C27

C28

E28

A22

C26

A19

C18

C16

E18

B19

E17

C19

C17

D19

C20

D20

E19

B18

D18

B17

B13

H19

H11

H14

H17

F20

F21

F22

F26

F27

F28

F16

F18

F19

M5

M6

F15

F23

F25

F24

A6

J3

A5

K6

K7

J7

U9A

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HA34

HA35

ADSTB0

ADSTB1

ADS

BNR

BPRI

BREQ0

DBSY

DEFFER

DRDY

HIT

HITM

HLOCK

HTRDY

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

RS0

RS1

RS2

DBI0

DBI1

DBI2

DBI3

CPURST

HCLK

HCLK

HAVREF0

HAVREF1

HDVREF0

HDVREF1

HDVREF2

HDVREF3

GTLREF

HRCOMP

HCOMPVREF

RSP/RESEVE

AP0/RESEVE

AP1/RESEVE

B

VCCP VCCP

C29

F29

H27

N13

N14

N15

N16

N17

N18

N19

N20

R13

T13

U13

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

P13

VTT

R14

T14

U14

V14

VTT

VTT

VTT

VTT

P20

VTT

P18

P19

VTT

VTT

C

P14

P15

P16

P17

VTT

VTT

VTT

VTT

DSTBP0

DSTBN0

DSTBP1

DSTBN1

DSTBP2

DSTBN2

DSTBP3

DSTBN3

RESEVE/DP0

RESEVE/DP1

RESEVE/DP2

RESEVE/DP3

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

DPWR

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

G10

D9

C9

B9

F10

B7

A9

F9

E7

E9

F7

C7

A8

C8

D7

A7

D16

E16

B14

D15

E15

C14

E14

C15

D12

C13

B12

B10

C11

B11

A10

C12

H6

G7

J4

G6

H5

G3

H4

G4

K1

J5

H1

J6

J1

J2

K4

K3

C3

C4

B4

D3

A4

C5

D4

E4

E2

E3

F3

F4

C2

F1

G1

F2

F8

D8

E13

D13

H3

H2

D1

E1

B6

D6

C6

E6

G15

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

BY PASS CAP

HD#[0..63] 5

HDSTBP#0 5

HDSTBN#0 5

HDSTBP#1 5

HDSTBN#1 5

HDSTBP#2 5

HDSTBN#2 5

HDSTBP#3 5

HDSTBN#3 5

DP#0 5

DP#1 5

DP#2 5

DP#3 5

D

VCCP VCCP

CB78

106P/0805

CB96

106P/0805

CB97

106P/0805

CB77

104P

CB95

105P

CB94

105P

Solder Side

E

CB164

X_106P/0805-B

CB170

X_106P/0805-B

CB166

X_104P-B

CB168

X_105P-B

Component Side

VCCP

VCCP

VCCP

R169 100RST

R181 100RST

R176 100RST

R160 20.5RST

R167

169RST

R183

169RST

R168

49.9RST

GTLVREF_NB1

GTLVREF_NB

HCOMPVREF

HRCOMP

MSI

Title

Size Document Number Rev

A

B

C

D

Date: Sheet

MICRO-STAR INt'L CO., LTD.

NORTH BRIDGE

Wednesday, April 21, 2004

MS-7055

731

E

1.0A

of

A

B

C

D

E

VCC_DDR

4 4

U9B

MD0

MD[0:63]11,12

3 3

2 2

CKEA011,12

CKEA111,12

MVREF_NB

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

CKEA0

CKEA1

M36

M33

M34

W35

W34

AB36

AC34

AD32

AE35

AC33

AC36

AE36

AE34

AR34

AP33

AP32

AR31

AT34

AR33

AT32

AP31

AN26

AM25

AN24

AR23

AT27

AT26

AT23

AP23

AP21

AM20

AR19

AL20

AT21

AR20

AT19

AP19

AT17

AN16

AT15

AN15

AP17

AR17

AP16

AP15

M35

AK17

AK22

AE29

W29

B36

D34

E33

C35

C36

E34

E36

K33

K35

K34

K36

V36

R36

U33

V33

R35

R29

MDA0

MDA1

MDA2

F35

MDA3

MDA4

MDA5

MDA6

MDA7

MDA8

MDA9

MDA10

MDA11

MDA12

MDA13

L36

MDA14

MDA15

T35

MDA16

T36

MDA17

MDA18

MDA19

MDA20

MDA21

MDA22

MDA23

MDA24

MDA25

MDA26

MDA27

MDA28

MDA29

MDA30

MDA31

MDA32

MDA33

MDA34

MDA35

MDA36

MDA37

MDA38

MDA39

MDA40

MDA41

MDA42

MDA43

MDA44

MDA45

MDA46

MDA47

MDA48

MDA49

MDA50

MDA51

MDA52

MDA53

MDA54

MDA55

MDA56

MDA57

MDA58

MDA59

MDA60

MDA61

MDA62

MDA63

T33

CKEA0

CKEA1

CKEA2

L34

CKEA3

MVREF5

MVREF4

MVREF3

MVREF2

MVREF1

J29

MVREF0

VCC_DDR

1 1

R203

100

MVREF_NB

R202

100

MVREF_NB = 0.5* VCCDDR

C109

475P/0805

C110

102P

A

C279

102P-B

P24

R24

N24

VCC3

VCC3

VCC3

VCC25MEM

P21

VCC_DDR

T24

U24

V24

W24

Y24

AA24

AB24

AC24

N21

N22

AD19

AD20

AD21

AD22

AD23

AD24

AK32

AK33

AP34

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC25MEM/MAC0

VCC25MEM/MAC1

VCC25MEM/MAC3

VCC25MEM/MAC5

VCC25MEM/MAC8

VCC25MEM/MAC9

VCC25MEM/MAC11

VCC25MEM/MAC14

VCC25MEM/SCASC

RESEVE/QBMMEA0

RESEVE/QBMMEA1

RESEVE/QBMSBA0

RESEVE/QBMSBA1

VCC25MEM/QBMMEB0

VCC25MEM/QBMMEB1

VCC25MEM/QBMSBB0

VCC25MEM/QBMSBB1

VCC25MEM

VCC25MEM

AC23

AP36

VCC3

DQMA0/MPDA0

DQMA1/MPDA1

DQMA2/MPDA2

DQMA3/MPDA3

DQMA4/MPDA4

DQMA5/MPDA5

DQMA6/MPDA6

DQMA7/MPDA7

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

SRASA

SCASA

SWEA

MAC2

MAC4

MAC6

MAC7

MAC10

MAC12

MAC13

MAC15

SRASC

SWEC

CSA0

CSA1

CSA2

CSA3

DQSA0

DQSA1

DQSA2

DQSA3

DQSA4

DQSA5

DQSA6

DQSA7

DQSA8

DCLKIA

DCLKOA

MAA0

AJ33

MAA1

AH35

MAA2

AH34

MAA3

AD33

MAA4

AD36

MAA5

AB34

MAA6

AB35

MAA7

V32

MAA8

W36

MAA9

V35

MAA10

AT36

MAA11

AT31

MAA12

AT35

MAA13

U36

MAA14

T34

MAA15

AT20

AP26

AN25

AR26

AE31

AB32

AA35

Y36

AA34

W30

Y31

R33

R31

N36

AF31

AH31

AE32

P33

M30

AN22

AN30

AN29

AP30

-CS0

AT25

-CS1

AR25

AP29

AP25

-DQS0

D35

-DQS1

L31

-DQS2

U34

-DQS3

AD34

-DQS4

AT33

-DQS5

AT24

-DQS6

AN20

-DQS7

AR16

AH36

-DQM0

D36

-DQM1

L33

-DQM2

V34

-DQM3

AD35

-DQM4

AN32

-DQM5

AP24

-DQM6

AP20

-DQM7

AT16

G36

G35

G33

G34

F36

F34

F33

F32

A32

B31

DCLKI

DCLKO_

DCLKO as short as passable

DCLKI = DCLKx + 2 "

C

N23

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

VCC25MEM

P22

P23

R23

T23

U23

V23

W23

Y23

AA23

AB23

AC18

AC19

AC20

AC21

AC22

B

BYPASS CAP

-SRASA 11,12

-SCASA 11,12

-SWEA 11,12

VCC_DDR

-CS0 11,12

-CS1 11,12

DEMO CIRCUIT LEAVE AS NC

RN57

X_8P4R-0

7 8

5 6

3 4

1 2

R128 22

MAA[0:15] 11,12

-DQS[0:7] 11,12

-DQM[0:7] 11,12

DEMO CIRCUIT PULL HIGH

VCC_DDR

DCLKI 15

DCLKO 15

VCC_DDR VCC_DDR

CB6

106P/0805

CB69

106P/0805

CB114

105P

Component Side

MSI

Title

Size Document Number Rev

D

Date: Sheet

CB167

X_106P/0805-B

CB172

X_106P/0805-B

CB161

X_104P-B

CB165

X_105P-B

CB171

X_105P-B

CB169

X_105P-B

CB163

X_106P/0805-B

Solder Side

MICRO-STAR INt'L CO., LTD.

NORTH BRIDGE

Wednesday, April 21, 2004

MS-7055

831

E

1.0A

of

A

AA2

AA3

VLAD[0:15]18

4 4

VIIN18

VIOUT18

UPSTB18

-UPSTB18

DNSTB18

-DNSTB18

UPCMD18

DNCMD18

3 3

-SUSST17

PCIRST#220,21,22,27

-PWROK_NB17

HSYNC14

VSYNC14

PIRQ#A13,16,19

GUICK15

SPDCLK214

2 2

1 2

3 4

5 6

7 8

1 1

R175

4.7K

R173 80.6RST

R199 X_0

R198 X_0

VBE018

VPAR18

AVDD1

AVDD2

AVDD3

AVDD4

AR14

AB14

AG14

SPD214

RN93

8P4R-4.7K

VCCDAC

VCCPLL

BISTIN

A

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VLAD8

VLAD9

VLAD10

VLAD11

VLAD12

VLAD13

VLAD14

VLAD15

LVREF_NB

LCOMPP

TESTIN_NB

DFTIN_NB

AVDD1

AVDD2

AVDD3

AVDD4

RSET

BISTIN

RSET

AR8

AN10

AR11

AR7

AM11

AP11

AM7

AN6

AP12

AM12

AR6

AN13

AP13

AN7

AM10

AM9

AN9

AN12

AP10

AM6

AN14

AM13

AP14

AP8

AP7

AT6

AP5

AP6

AT7

AP9

AL7

C31

D32

D31

AA5

AA4

AB5

AB6

AA6

M4

M1

L1

R1

R3

R2

U4

U3

V7

U2

N5

V6

T4

T3

N4

N3

W1

W2

Y3

Y2

Y5

Y6

Y7

V1

W4

W3

Y4

V2

V4

V3

V5

W5

T5

P4

P3

P6

AB4

VD0

VD1

VD2

RES2

RES3

VD3

VD4

VD5

VD6

VD7

VD8

VD9

VD10

VD11

VD12

VD13

VD14

VD15

RESERVE/VIIN

RESERVE/VIOUT

VBE

VPAR

UPSTB

UPSTB

DNSTB

DNSTB

UPCMD

DNCMD

VLREF

VCOMPP

SUSST

TESTIN NB

RESET

PWROK

DFTIN

AVDD1

AVDD2

AVDD3

AVDD4

AR

AB

AG

HSYNC

VSYNC

RSET

INTA

XIN

BISTIN

SPD2

SPDCLK2

DISPCLKO

DISPCLKI

TVD00/DVP0D00

TVD01/DVP0D01

TVD02/DVP0D02

TVD03/DVP0D03

TVD04/DVP0D04

TVD05/DVP0D05

TVD06/DVP0D06

TVD07/DVP0D07

TVD08/DVP0D08

TVD09/DVP0D09

TVD10/DVP0D10

TVD11/DVP0D11

TVVS/DVP0VS

TVHS/DVP0HS

TVDE/DVP0DE

VTCLK/DVP0DCLK

TVCLKIN/DVP0DET

SPD1

SPDCLK1

GPO0

GPOUT

DACAVDD1

DACAVDD2

VCCPLL1

VCCPLL2

VCCPLL3

AGND1

M3

E31

RES1

AGND2

AGND4

AGND3

L2

M2

V13

VCC4

DACAGND3

R4

VCC3

Y13

VCC4

DACAGND2

P5

W13

T6

VCC4

DACAGND1

B

VCC_DDR

NBVCC15 VCC_AGP

C

D

E

BYPASS CAP

Component Side Solder Side

VIA-PM800

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

GCBE0

GCBE1

GCBE2

GCBE3

GFRAME

GIRDY

GTRDY

GSTOP

GPAR

GREQ

GGNT

GSERR

SBSTBF

SBSTBS

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

GCLK

VSUS15

TCLK

VSS

AR5

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

RBF

WBF

DBIL

ST0

ST1

ST2

U9C

AT2

AP2

AP4

AT5

AR4

AT1

AN5

AT4

AM1

AP3

AR1

AM4

AL2

AN2

AL1

AP1

AJ3

AJ1

AJ4

AK6

AH1

AH2

AK4

AH3

AG5

AJ6

AH5

AG2

AH4

AF3

AG6

AF1

AN4

AL3

AK2

AK5

AL4

AL5

AK3

AK1

AM3

AN3

AE7

AB2

AD4

AD5

AN1

AF4

AG4

AB1

AD6

AE5

AE6

AD3

AD1

AT3

AR3

AG3

AG1

AC1

AC4

AC3

AD2

AE2

AE3

AE4

AE1

AF7

AD7

N7

AB3

AC6

AL14

AT14

W6

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

AGPVREF

AGPVREF

AGPNCOMP0

AGPPCOMP0

1.5VSB

GD[0:31]

GBE0 13

GBE1 13

GBE2 13

GBE3 13

GFRAME 13

GIRDY 13

GTRDY 13

GDEVSEL 13

GSTOP 13

GPAR 13

RBF 13

WBF 13

GREQ 13

GGNT 13

GSERR 13

DBIH 13

DBIL 13

AGP8X_DET_NB 13

ST0 13

ST1 13

ST2 13

SB_STBF 13

SB_STBS 13

AD_STBF0 13

AD_STBS0 13

AD_STBF1 13

AD_STBS1 13

SBA[0:7]

GCLK_NB 15

BC1

104P

GD[0:31] 13

SBA[0:7] 13

AGP8xdet 0=enable

AGPBZ 18

NBVCC15

R192

1.2KST

LVREF_NB

R194

768RST

AD14

AD15

AA13

AB13

VCC1

AC13

AD13

AC15

AC14

AB14

AA14

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

AD16

AD17

AD18

AC16

AC17

Y14

W14

VCC2

VCC2

VCC2

VCC2

VCC1

VCC25MEM

GDEVSEL

DBIH/PIPE

AGP8XDET

ADSTBF0

ADSTBS0

ADSTBF1

ADSTBS1

AGPVREF0

AGPVREF1

AGPNCOMP

AGPPCOMP

AGPBUSY

GNDPLL1

GNDPLL2

GNDPLL3

VDD

P2

N6N1N2

AE12

A29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AR27

AR30

AR32

AR35

AT8

AT11

VSS

VSS

VSS

VSS

VSS

VSS

AR2

AR14

AR15

AR18

AR21

AR24

VSS

VSS

VSS

VSS

VSS

VSS

AM30

AM32

AM34

AM36

AN8

AN11

NBVCC15

LVREF_NB => VDD/4=0.625

B

C

VCC_AGP

NBVCC15

12

CP10

X_COPPER

C97

X_102P

VCC3

12

CP5

X_COPPER

C78

X_102P

12

CP9

X_COPPER

C91

X_102P

AGPVREF 13

CB183

104P-B

CB116

102P

PUT CAP ON THE BOTTOM OF PIN AF7

105P/0805

C107

C108

104P

D

VCC_AGP

CB125

104P

CB117

104P

CB118

104P

CB98

106P/0805

CB99

106P/0805

CB88

104P

CB100

105P

VCC3

CB182

X_106P/0805-B

CB180

106P/0805-B

CB176

X_105P-B

CB173

X_105P-B

CB179

106P/0805-B

CB181

105P-B

VCC3 VCC3

DFTIN_NB

TESTIN_NB

CP14

X_COPPER

CP12

X_COPPER

CP11

X_COPPER

R131 4.7K

R130 4.7K

FB5

X_220L2_50_0805

AVDD1

CM3

105P/0805

FB1

X_220L2_50_0805

AVDD2

CM1

105P/0805

FB4

X_220L2_50_0805

AVDD4

CM2

105P/0805

AGPNCOMP0

AGPPCOMP0

LCOMPP

MSI

Title

Size Document Number Rev

Date: Sheet

MICRO-STAR INt'L CO., LTD.

NORTH BRIDGE

Wednesday, April 21, 2004

MS-7055

NBVCC15

12

FB8

X_220L2_50_0805

VCCDAC

C104

X_102P

NBVCC15

12

FB7

X_220L2_50_0805

VCCPLL

C99 CM5

X_102P

VCC3VCC3

12

FB6

X_220L2_50_0805

AVDD3

C98

X_102P

R193

60.4RST

R191

60.4RST

R222

360

E

931

CB177

106P/0805-B

CB162

106P/0805-B

CB174

104P-B

CB175

105P-B

CB160

105P-B

CB159

X_105P-B

CB178

106P/0805-B

CM6

105P/0805

105P/0805

CM4

105P/0805

VCC_DDR

VCC_AGP

of

1.0A

Loading...

Loading...