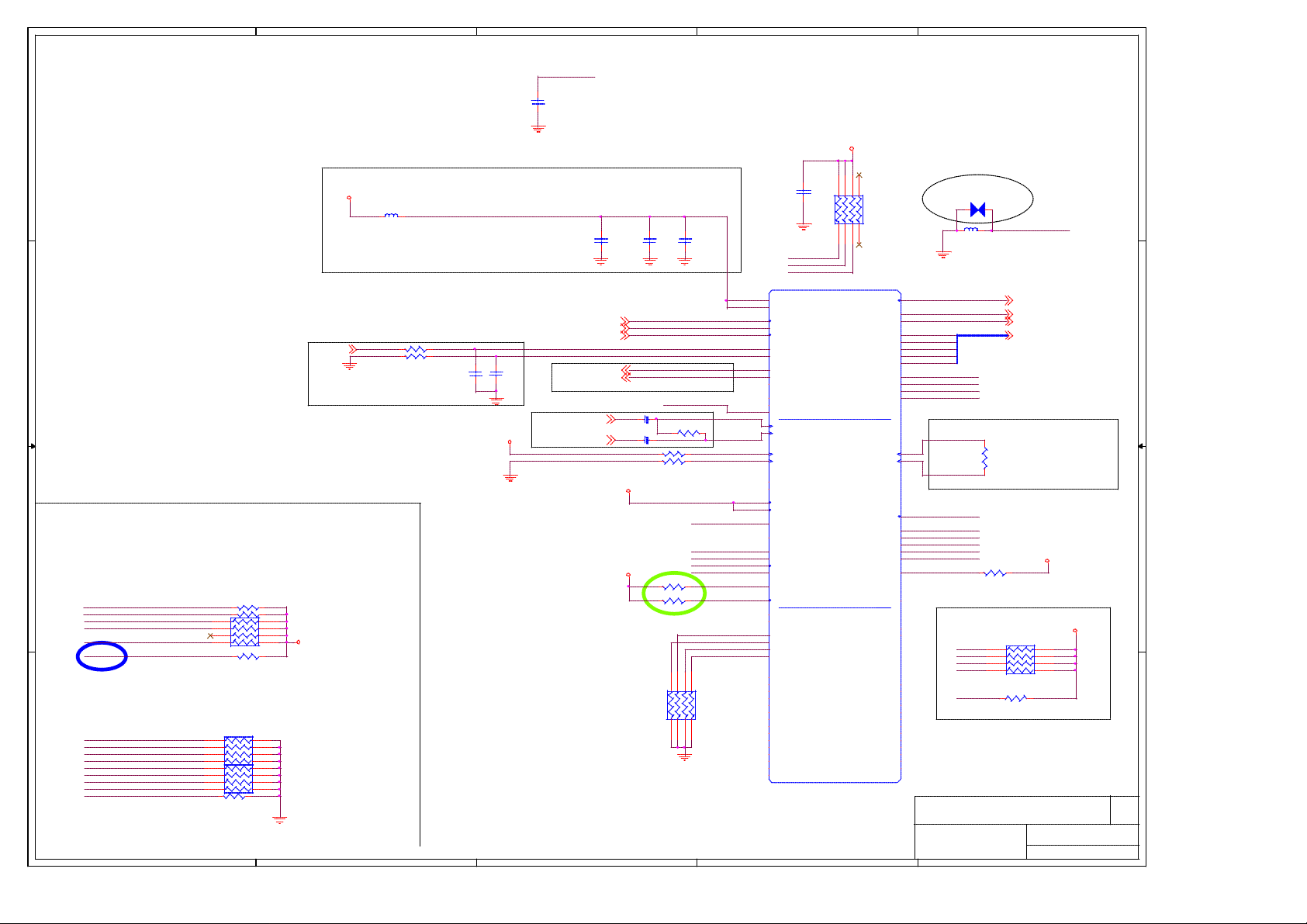

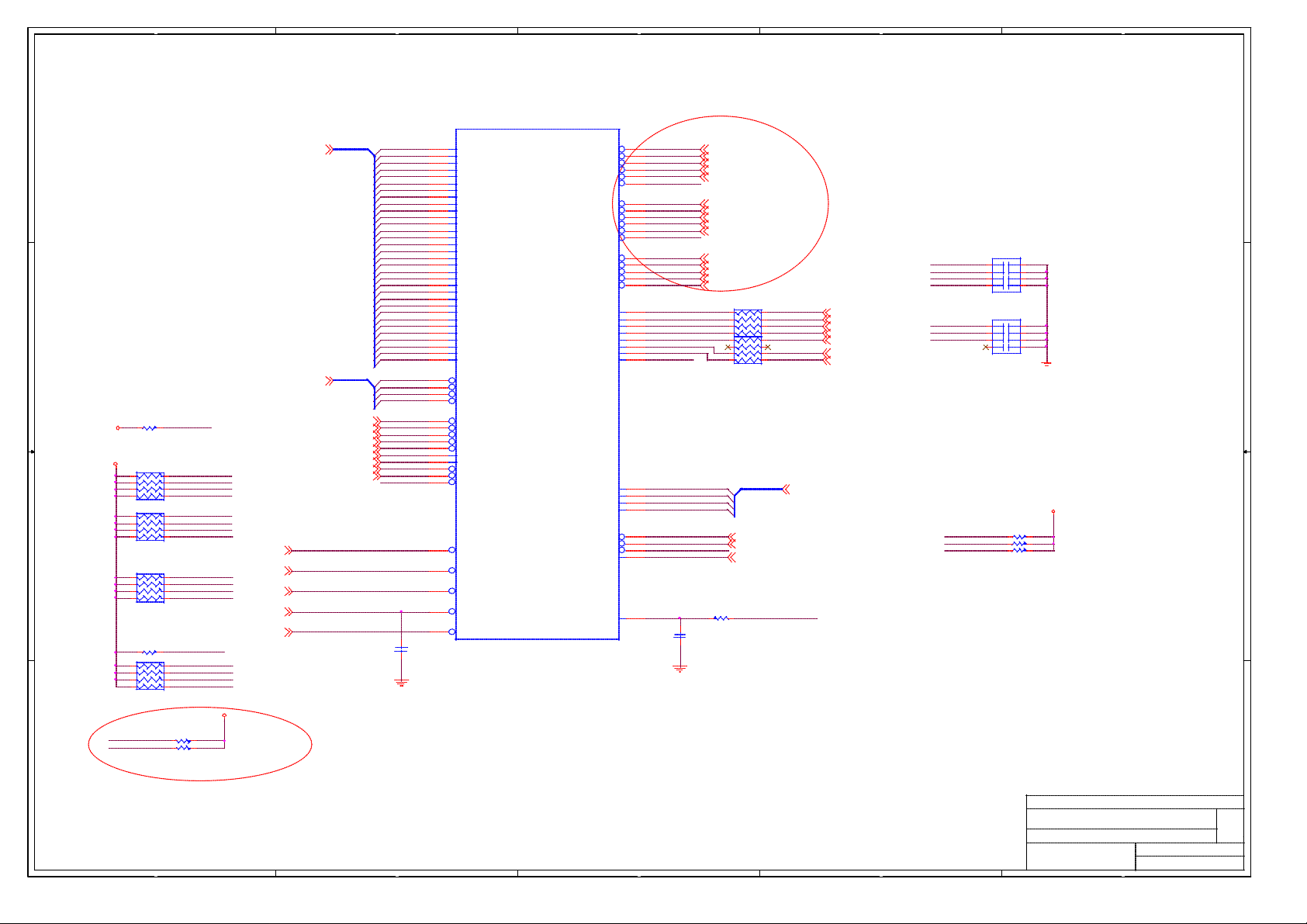

MSI MS-7034 Schematics

5

4

3

2

1

MS-7034 VER:10A Micro ATX

Version 10A

05/26/2004 Update

*AMD PGA 754 K8-Processor (DDR 400)

*nFORCE3 250Gb

D D

*Winbond 83627THF S/IO

*VT6306 1394a OHCI Link Layer Controller

*RTL 8110S Giga & RTL8100C 10/100 Bit LAN Support

*AC'97 Codec ALC655

*USB 2.0 support (8 ports integrated into nFORCE3)

*SATA*2 nFORCE3 250Gb

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 3

C C

*DDR DIMM * 2

*Vcore Jumpless support

Title

Cover Sheet

Block Diagram

GPIO SPEC

AMD K8 -> 754 PGA Socket

nFORCE3 CK8S-1000

System Memory

DDR DIMM 1 & 2

DDR Terminations R & C

DDR Damping R & Bypass Cap.

AGP SLOT 8X

PCI Connectors * 3

IDE ATA 66/100/133 Connectors * 2

LPC I/O W83627THF & Floppy

LPT/COM Port

FAN & BIOS

Keyboard/Mouse Connectors

LAN RTL8201BL & RTL8110S

1394a Controller VT6306

AC'97 Codec ALC655

Front USB Port *2

Rear USB Port *2

SYSTEM VOLTAGE REGULATOR

ACPI Power CONTROLLER (MS-6)

K8 Vcore

B B

Front Panel & POWER OK CIRCUIT

Decoupling Cap.

POWER MAP

History-01

Page

1

2

3

4,5,6

7~12

13

14

15

16

17,18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

History-02 36

OPTION PARTS

37

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

1

Cover Sheet

MS-7034

Last Revision Date:

Sheet

Rev

10A

Wednesday, May 26, 2004

1 39

of

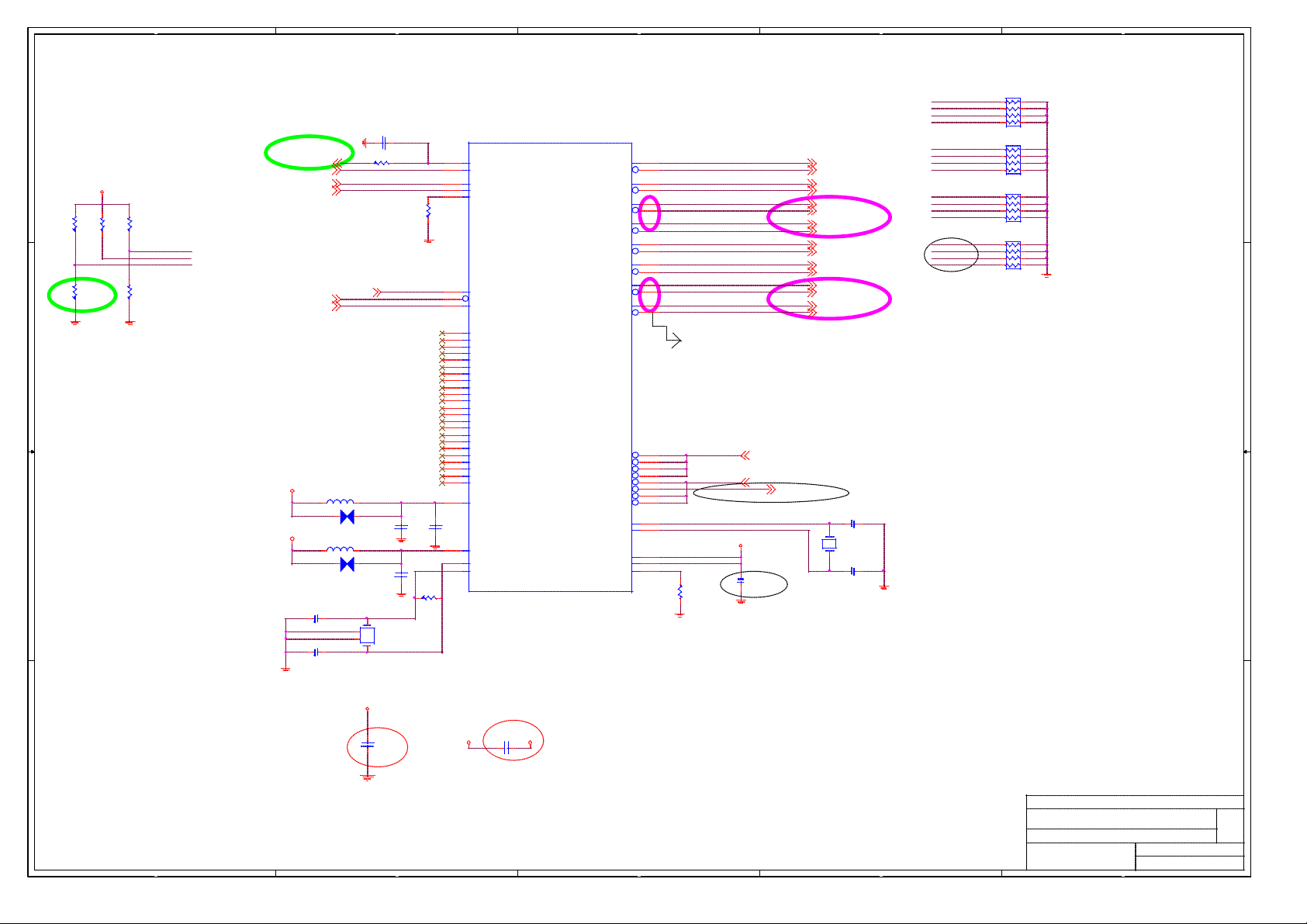

5

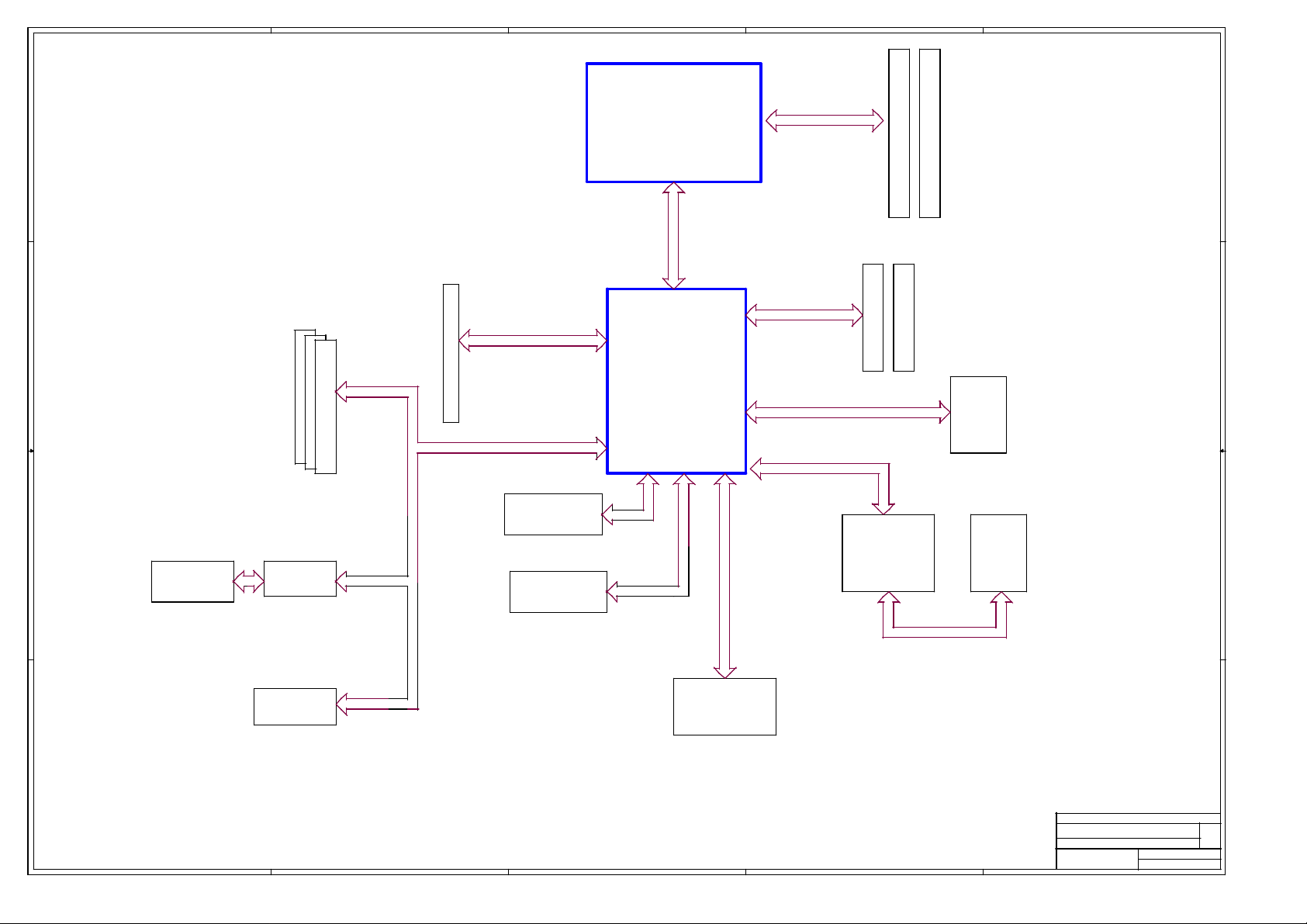

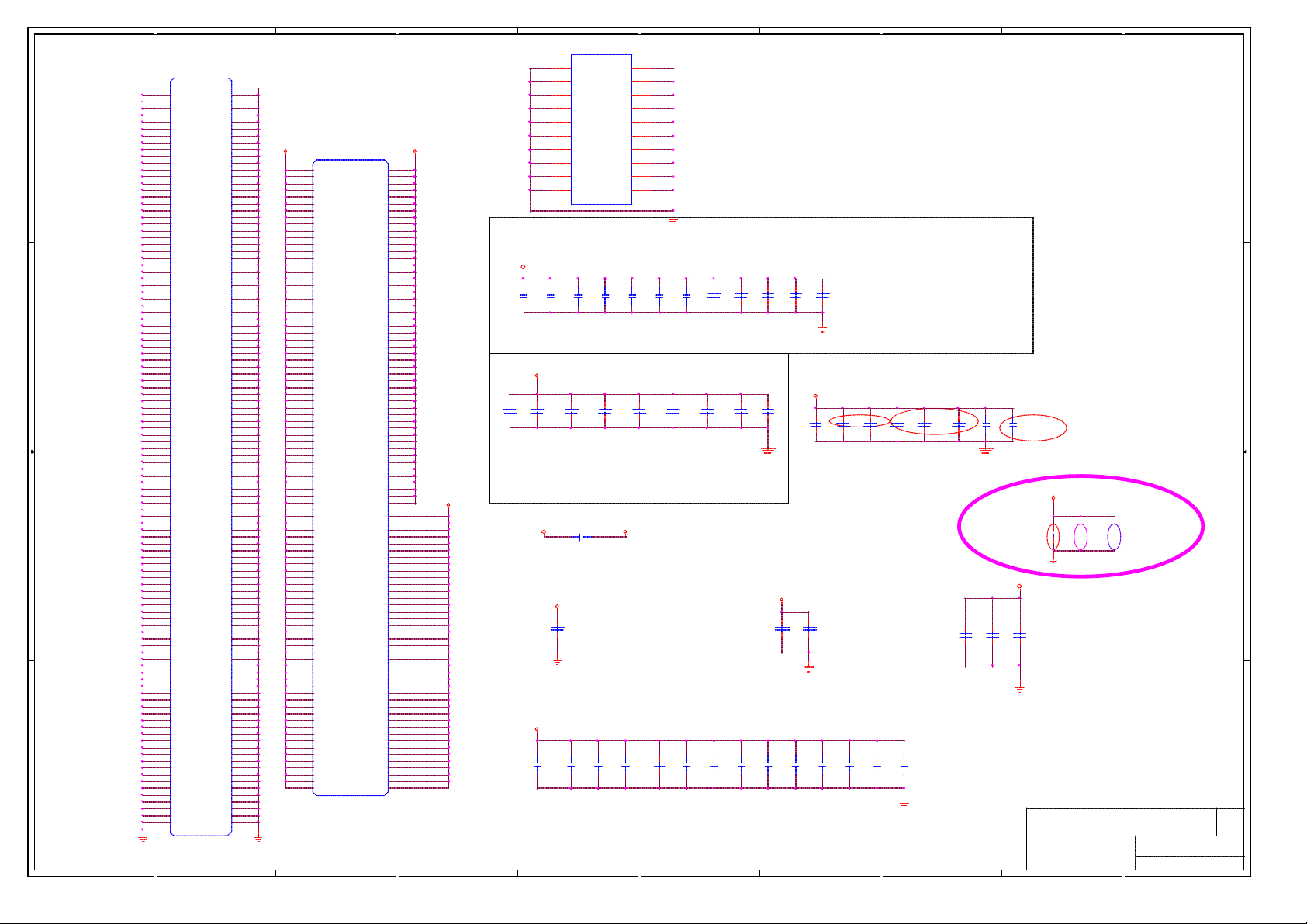

nFORCE3

4

3

2

1

250Gb

DDR400

AMD K8 Socket 754

D D

Block

Diagram

HT

IDE Slot

==>ATA66,100,133 *2

A

G

AGP 8X /Fast Write

C C

5 PCI Slots

P

S

L

O

T

nFORCE3 250Gb

Dual ATA

100/133

MII BUS 10/100 LAN PHY

LPC BUS

PCI-33

Codec ALC655

B B

1394

Front-Port *2

1394 Host

Controller

VT6306

SERIAL ATA *2

AC97

USB

SUPER I/O

W83627THF

DDR * 2

(RTL8201BL)

(Reserved)

ROM

X BUS

Giga Bit LAN

RTL8110S/8100C

A A

5

4

3

Dual USB 1.1 OHCI

/2.0 EHCI 8 Ports

==> Front-Port *4 ,

Back-Port *4

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Block Diagram

MS-7034

1

Last Revision Date:

Sheet

Rev

Monday, May 10, 2004

2 39

of

10A

5

4

3

2

1

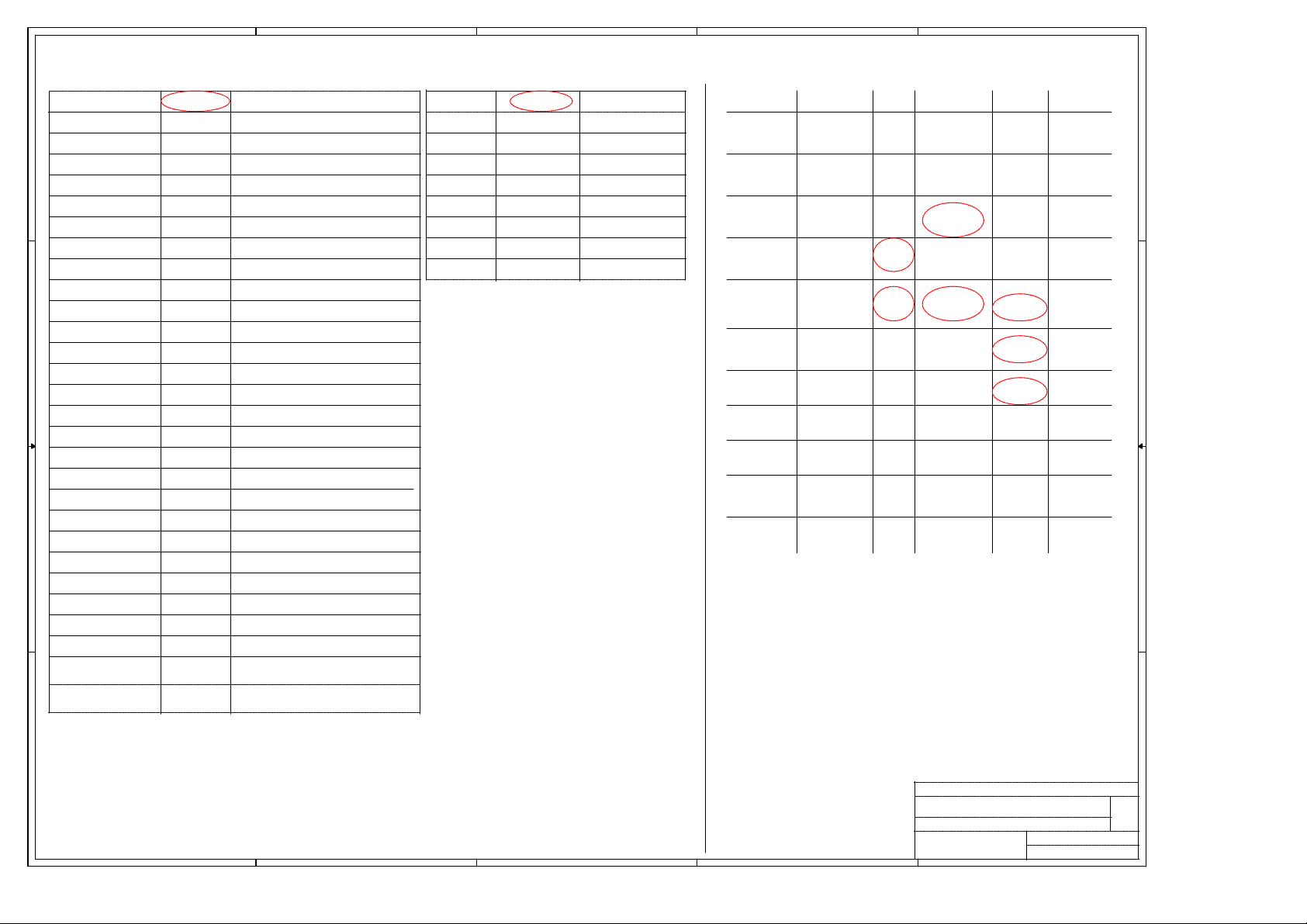

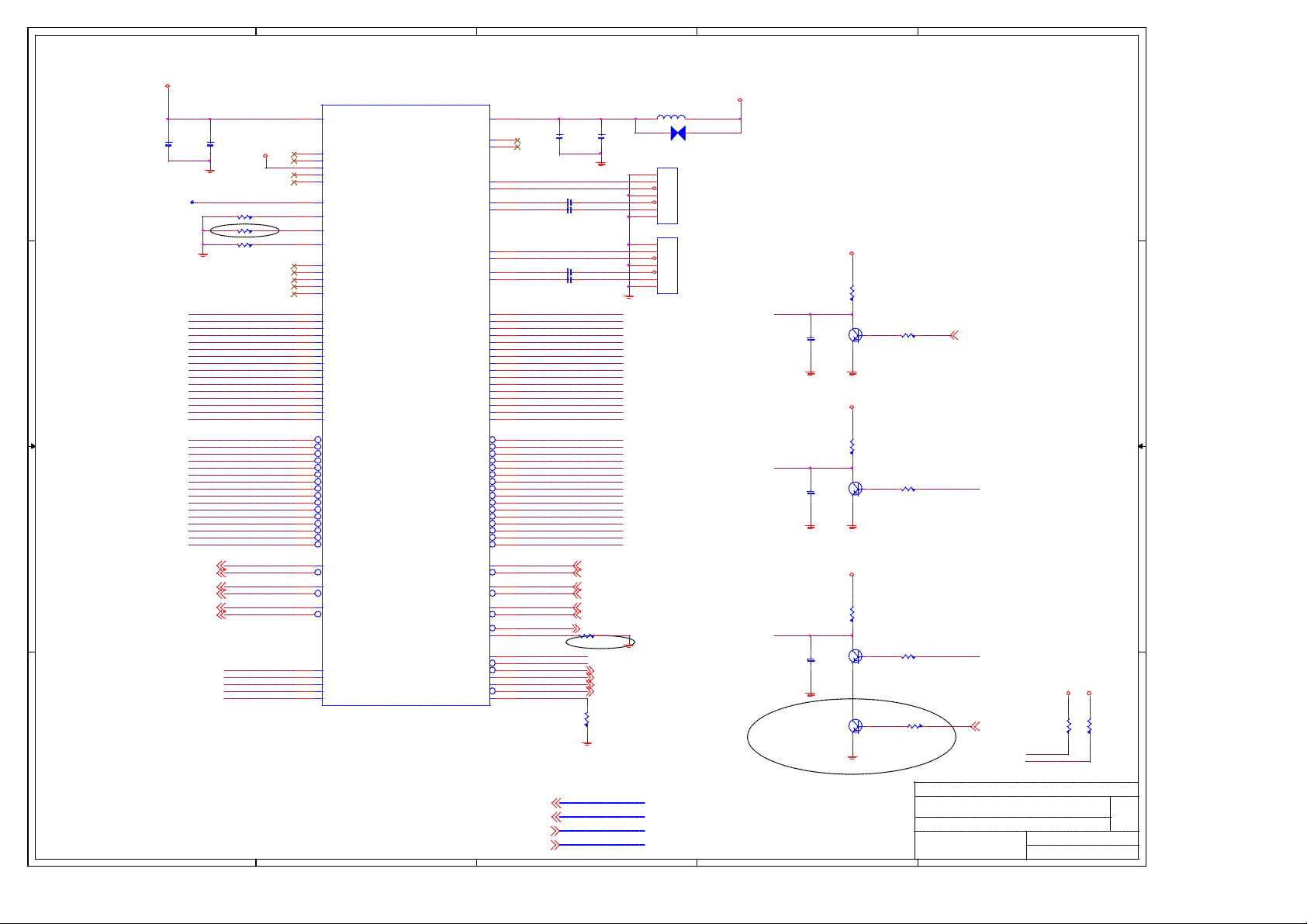

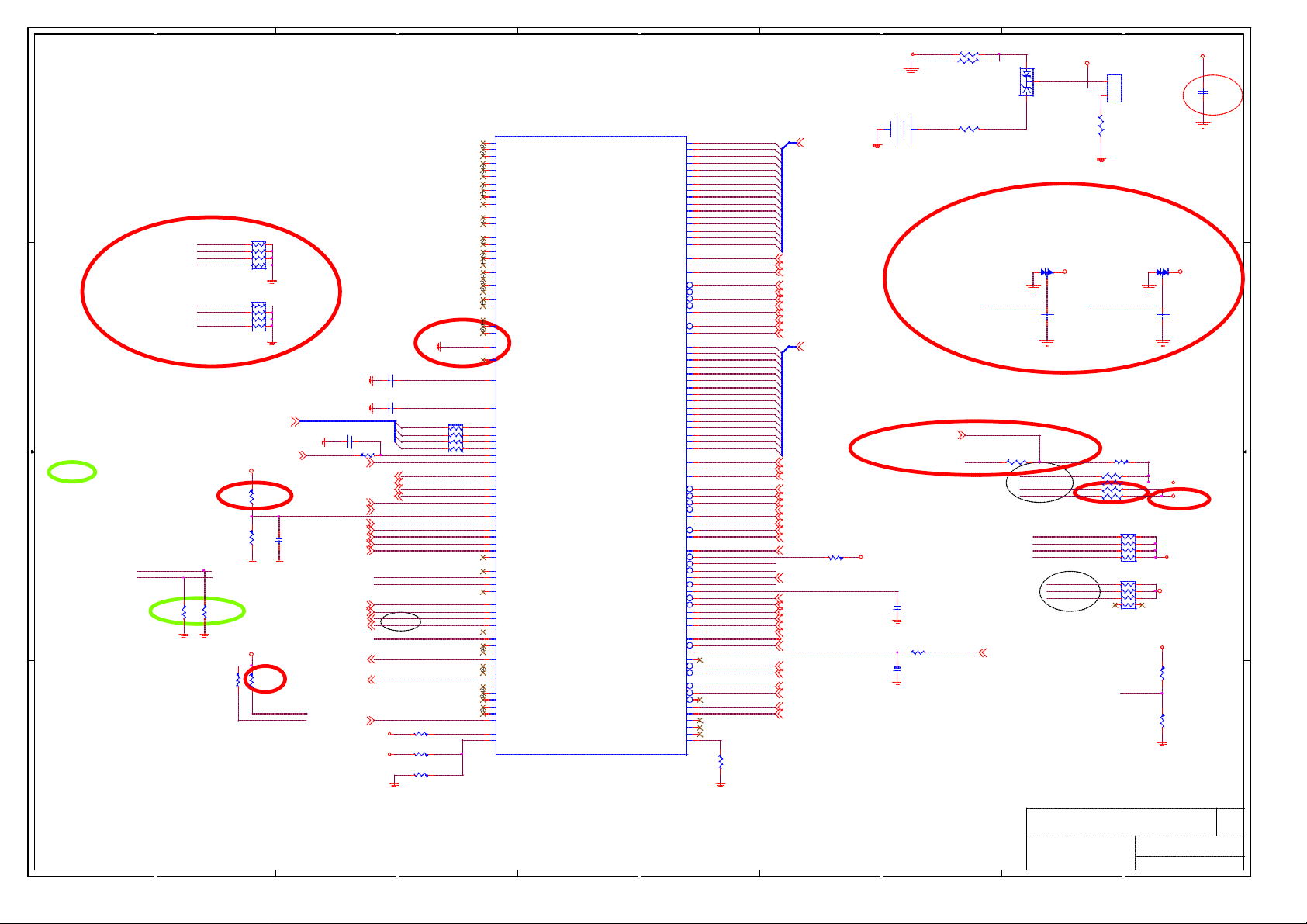

CK8S-1000 GPIO FUNCTION

NAME

GPIO1

D D

(page#11)

GPIO2

GPIO4

GPIO5

GPIO6

LID#/GPIO7

GPIO8

GPIO9

GPIO10/HT1_REQ#

GPIO11/STOP_AGPCLK#

GPIO12

C C

GPIO13/ASF0

GPIO14/ASF1

GPIO15

GPIO16

GPIO17

GPIO18

MII_RXER/GPIO21

RI#/GPIO30

SPDIF/GPIO51

FANRPM/GPIO52

B B

FANCTL0/GPIO53

FANCTL1/GPIO54

BUF_14MHZ/GPIO55

CPU_SLP/GPIO56

SLP_S1/GPIO57

SPIO_20/SATALED*

Pin

Y6

AE2

E14

D14

F12

E8

B15

B14

B17

E11

E13

F13

B7

F8

D3

D2

C4

AN33

B5

B16

E6

D5

C5

B6

C3

C8

E4

Function define RESET

ATADET0=>Detect IDE1 ATA100/66

ATADET1=>Detect IDE2 ATA100/66

VSET0

(Vocre Adjust)

VSET1

(Vocre Adjust)

NA

NA

NA

NA

VSET2

(Vocre Adjust)

NA

NA

Pull Up to 3.3V (BIOS protect)

1394 Enable/Disable

NA

NA

NA

NA

NA

NA (Exteranl Pull up to 3VDUAL)

NA (Exteranl Pull up to VCC3)

NA

NA

NA

NA

NA (Exteranl Pull up to 3VDUAL)

NA

SATA_LED#

S/IO GPIO Function Define

NAME Pin

GPBX/GP13

GPAY/GP15

GPSA1/GP10

GPSA2/GP17

GPX1/GP12

GPY2/GP14

GPSB1/GP11

GPSB2/GP16

125

123

128

121

126

124

127

122

Function define

DLED#4

DLED#2

DLED1

DLED4

DLED#3

DLED#1

DLED2

DLED3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

Giga-Bit

LAN

1394 INT#D(PIRQ#D) AD28

FWH

SIO

MS6 PCIRST#4

INT#

INT#A(PIRQ#A)

INT#B(PIRQ#B)

INT#C(PIRQ#C)

INT#D(PIRQ#D)

INT#B(PIRQ#B)

INT#C(PIRQ#C)

INT#D(PIRQ#D)

INT#A(PIRQ#A)

INT#C(PIRQ#C)

INT#D(PIRQ#D)

INT#A(PIRQ#A)

INT#B(PIRQ#B)

IDSEL

AD22

AD23

AD24

INT#E(PIRQ#E) AD29

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#2

PGNT#2

PREQ#4

PGNT#4

PREQ#3

PGNT#3

CLOCK

PCICLK0

PCICLK1

PCICLK2

PCICLK5

PCICLK3

PCICLK4

PCICLK6

PCIRST#1

PCIRST#1

PCIRST#1

PCIRST#3

PCIRST#2

PCIRST#3

PCIRST#3

USB_OC5#/GPIO26 D17 LAN_RST#

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

GPIO Spec.

MS-7034

Last Revision Date:

Monday, May 10, 2004

Sheet

3 39

1

Rev

10A

of

5

4

3

2

1

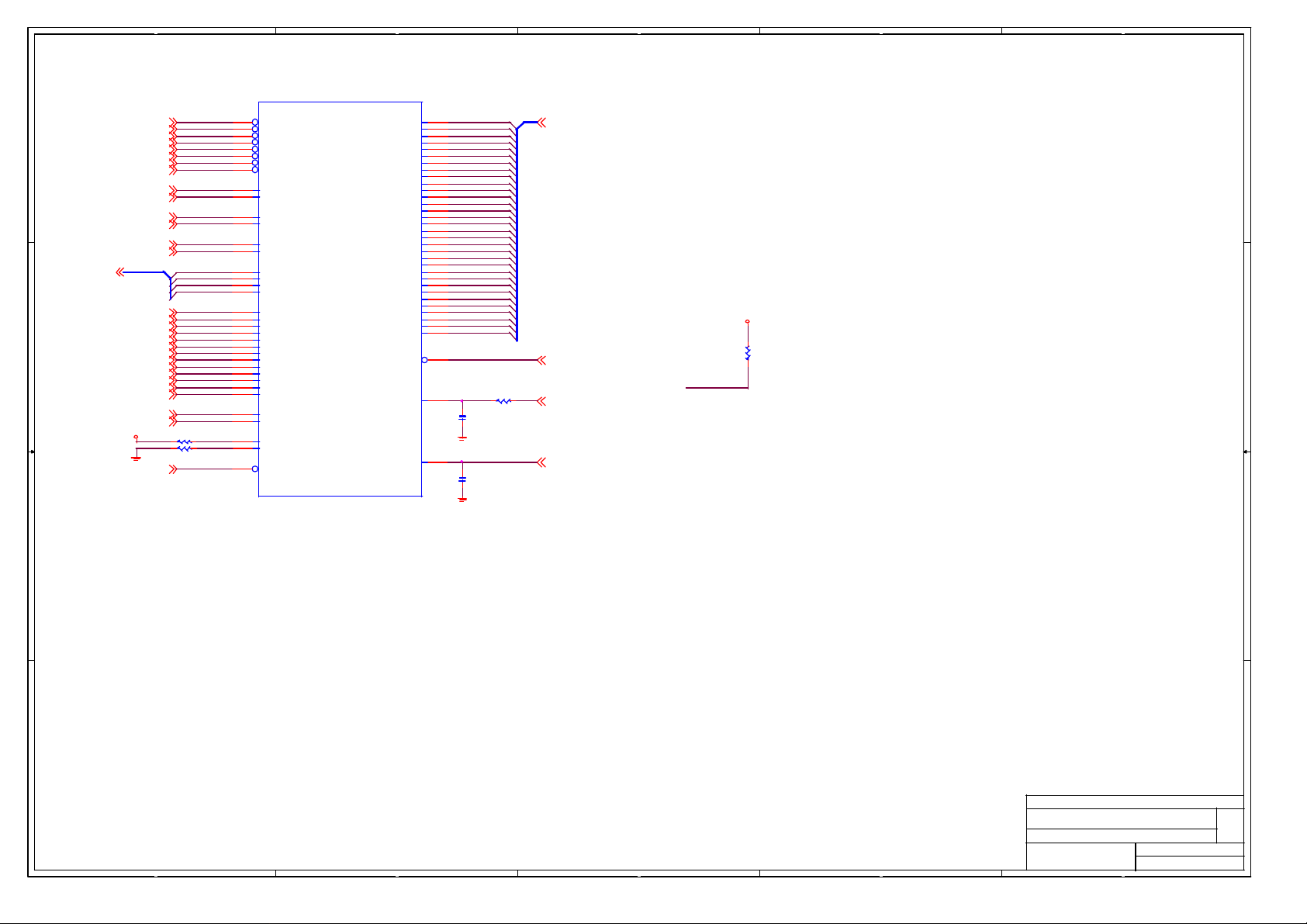

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

C53

X_102P

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

U1B

RSVD_MEMADDA15

RSVD_MEMADDA14

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMORY INTERFACE

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMRESET_L

MEMCKEA

MEMCKEB

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA3

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0 <13,14>

MCKE1 <13,14>

MEMCLK_H[7..0]

MEMCLK_L[7..0]

-MCS[3..0]

-MCS[3..0] <13,14>

-MSRASA <13,14>

-MSCASA <13,14>

-MSWEA <13,14>

MEMBANKA1 <13,14>

MEMBANKA0 <13,14>

MAA[13..0] <13,14>

-MSRASB <13,14>

-MSCASB <13,14>

-MSWEB <13,14>

MEMBAKB1 <13,14>

MEMBAKB0 <13,14>

MAB[13..0] <13,14>

MEMCLK_H[7..0] <13,14>

MEMCLK_L[7..0] <13,14>

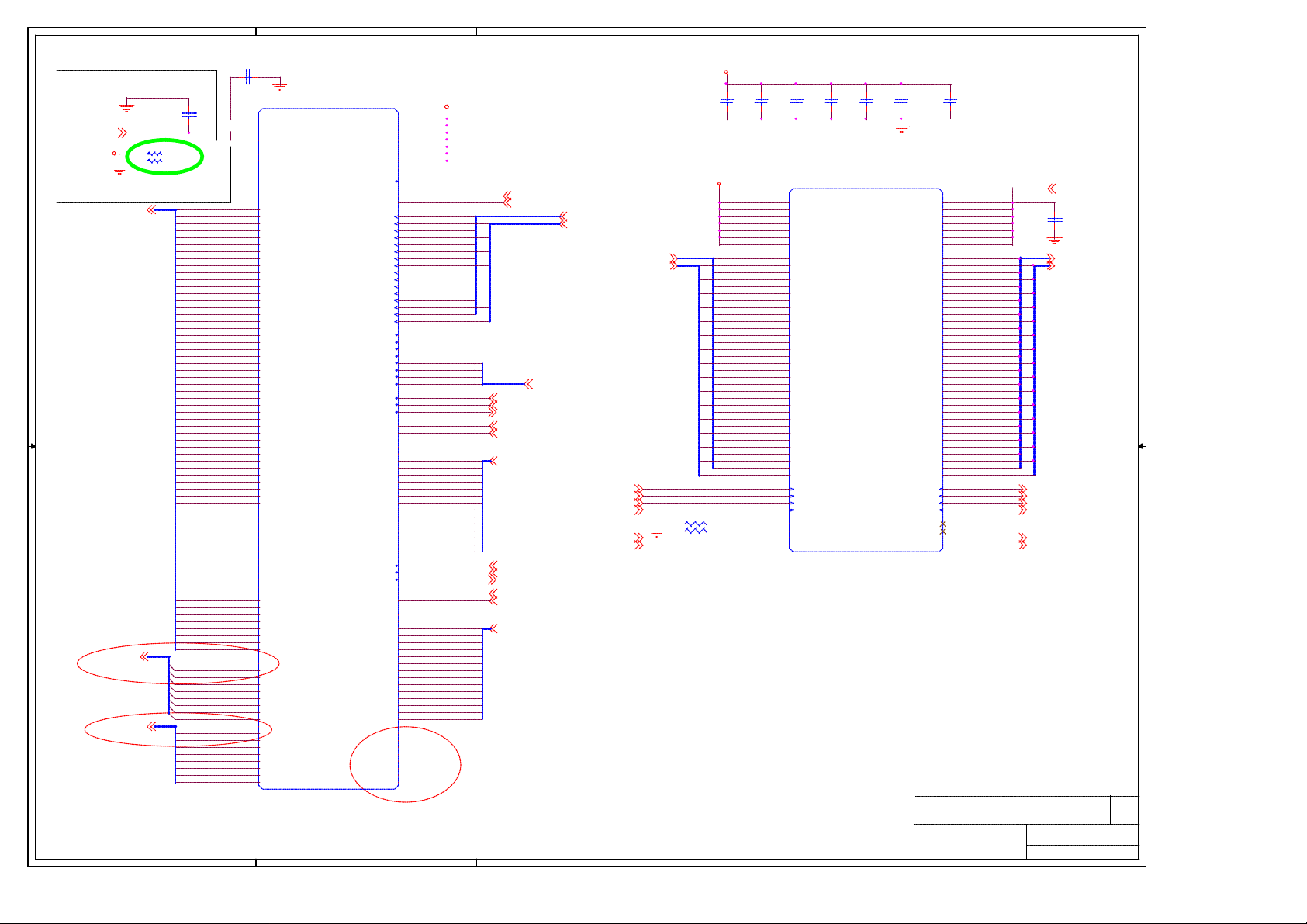

CADIP[0..15]<7>

CADIN[0..15]<7>

CLKIP1<7>

CLKIN1<7>

CLKIP0<7>

CLKIN0<7>

CTLIP0<7>

CTLIN0<7>

3

VLDT0

VREF routed as 40~50 mils trace wide ,

Space>25 mils

D D

DDR_VREF<13>

VDD_25_SUS

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

R67 44.2R1%

R66 44.2R1%

C1000P50X

nVIDIA check@010693

MD[63..0]<15>

C C

B B

DM[7..0]<15>

-MDQS[7..0]<15>

A A

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

5

VDD_12_A

VDD_12_A

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP1

CLKIN1

CLKIP0

R56 49.9R1%

R58 49.9R1%

CLKIN0

CTLIP0

CTLIN0

C179

X_0.22u

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP1

CADIP0

CTLIP1

CTLIN1

C177

C0.22U16Y

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

T27

T28

V29

U29

V27

V28

Y29

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

Y25

W25

Y27

Y28

R27

R26

T29

R29

C178

C0.22U16Y

U1A

N12-7540010-F02

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

HYPER TRANSPORT - LINK0

2

C171

X_0.22u

C170

C172

C0.22U16Y

C0.22U16Y

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

Title

Document Number

C284

C0.22U16YC39

AH29

AH27

AG28

AG26

AF29

AE28

AF25

CADOP15

N26

CADON15

N27

CADOP14

L25

CADON14

M25

CADOP13

L26

CADON13

L27

CADOP12

J25

CADON12

K25

CADOP11

G25

CADON11

H25

CADOP10

G26

CADON10

G27

CADOP9

E25

CADON9

F25

CADOP8

E26

CADON8

E27

CADOP7

N29

CADON7

P29

CADOP6

M28

CADON6

M27

CADOP5

L29

CADON5

M29

CADOP4

K28

CADON4

K27

CADOP3

H28

CADON3

H27

CADOP2CADIP2

G29

CADON2

H29

CADOP1

F28

CADON1

F27

CADOP0

E29

CADON0

F29

CLKOP1

J26

CLKON1

J27

CLKOP0

J29

CLKON0

K29

N25

P25

CTLOP0

P28

CTLON0

P27

Micro Star Restricted Secret

K8 DDR & HT

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7034

VLDT0

VLDT0 <5>

CADOP[0..15] <7>

CADON[0..15] <7>

CLKOP1 <7>

CLKON1 <7>

CLKOP0 <7>

CLKON0 <7>

CTLOP0 <7>

CTLON0 <7>

Last Revision Date:

Monday, May 24, 2004

Sheet

1

C92

C4.7U10Y0805

4 39

of

Rev

10A

5

D D

4

C62

X_102P

VDDIO_SENSE

3

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

2

1

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

VCC2_5

LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil

VCC2_5

C C

VLDT0<4>

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

HDT Test Port Signal .

B B

DBREQ_L

DBRDY

TMS

TDI

TCK

TRST_L

NC_AG18

NC_AH18

A A

NC_AJ18

NC_AG17

NC_D18

NC_C19

NC_B19

NC_D20

NC_C21

5

R36 X_1KR

R37 X_1KR

3 4

5 6

7 8

R322 1KR

1 2

3 4

5 6

7 8

1 2

3 4

5 6

7 8

R65 1KR

X_8P4R-1KR1 2

RN42

VCC2_5

RN11

8P4R-1KR

8P4R-1KR

RN43

traces to exit ball field) and 500 mils long.

FB1 0.18U450m_1210

VLDT0

R55 44.2R1%

R57 44.2R1%

4

CPU_VDDA_25

C101

C1000P50X

VDD_25_SUS

C103

C1000P50X

C4.7U10Y0805

CPURST#<7>

CPU_GD<7>

LDTSTOP#<7>

COREFB_H<31>

COREFB_L<31>

Differential , "10:10:5:10:10" .

CPUCLK0_H<7>

Near CPU in 0.5" .

CPUCLK0_L<7>

3

C48

L0_REF1

L0_REF0

C61 C0.039U16X

C60 C0.039U16X

R39 820R

VTT_DDR_SUS

VCC2_5

nVIDIA check@010693

C55

X_C0.22U16Y

CPURST#

CPU_GD

LDTSTOP#

VDDIO_SENSE

R48 10P

R63 680R

R62 680R

3 4

5 6

7 8

C44

C1000P50X

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

RN13

X_8P4R-1KR

1 2

CLKIN_H

CLKIN_L

C4.7U10Y0805

AH25

VDDA1

AJ25

VDDA2

AF20

RESET_L

AE18

PWROK

AJ27

LDTSTOP_L

AF27

L0_REF1

AE26

L0_REF0

A23

COREFB_H

A24

COREFB_L

B23

CORE_SENSE

AE12

VDDIOFB_H

AF12

VDDIOFB_L

AE11

VDDIO_SENSE

AJ21

CLKIN_H

AH21

CLKIN_L

AJ23

NC_AJ23

AH23

NC_AH23

AE24

NC_AE24

AF24

NC_AF24

C16

VTT_A5

AG15

VTT_B5

AH17

DBRDY

C15

NC_C15

E20

TMS

E17

TCK

B21

TRST_L

A21

TDI

C18

NC_C18

A19

NC_A19

A28

KEY1

AJ28

KEY0

AE23

NC_AE23

AF23

NC_AF23

AF22

NC_AF22

AF21

NC_AF21

C1

FREE29

J3

FREE31

R3

FREE33

AA2

FREE35

D3

FREE1

AG2

FREE37

B18

FREE4

AH1

FREE38

AE21

FREE41

C20

FREE7

AG4

FREE11

C6

FREE12

AG6

FREE13

AE9

FREE14

AG9

FREE40

C45

CPURST#

CPU_GD

LDTSTOP#

2

1 2

3 4

5 6

U1C

THERMTRIP_L

G_FBCLKOUT_H

G_FBCLKOUT_L

RN10

8P4R-330R

7 8

THERMDA

THERMDC

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

A20

A26

A27

AG13

VID4

AF14

VID3

AG14

VID2

AF15

VID1

AE15

VID0

AG18

AH18

AG17

AJ18

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

TDO

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

CP6 X_COPPER

FB3

X_120S/0603

THRM#

THERMDA_CPU

THERMDC_CPU

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

FBCLKOUT_H

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

LAYOUT: Route

FBCLKOUT_H/L differentially

R38

with 20/8/5/8/20 spacing and

80.6R1%R40 820R

trace width. ( In CPU

breakout => routed 5:5:5 )

R64

X_1KR

VID0

1 2

VID1

3 4

VID2

5 6

VID3

7 8

X_8P4R-4.7K

VID4

R29 X_4.7K

Micro Star Restricted Secret

K8 HDT & MISC

020493

THERMDC_CPU

THRM# <30>

THERMDA_CPU <20>

THERMDC_CPU <20>

VID[4..0] <31>

VDD_25_SUS

RN6

MS-7034

Last Revision Date:

Monday, May 24, 2004

Sheet

1

VCC2_5

5 39

of

Rev

10A

5

4

3

2

1

U1F

1

U1E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

D D

C C

B B

A A

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

AA10

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

AE16

VSS20

J18

VSS21

G20

VSS22

R20

VSS23

U20

VSS24

W20

VSS25

AA20

VSS26

AC20

VSS27

AE20

VSS28

AG20

VSS29

AJ20

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

M21

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

AD21

VSS40

AG21

VSS41

B22

VSS42

E22

VSS43

G22

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

AG29

VSS50

AA22

VSS51

AC22

VSS52

AG22

VSS53

AH22

VSS54

AJ22

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

AB23

VSS64

AD23

VSS65

AG23

VSS66

E24

VSS67

G24

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

W24

VSS73

AA24

VSS74

AC24

VSS75

AG24

VSS76

AJ24

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

M26

VSS83

T26

VSS84

Y26

VSS85

AD26

VSS86

AF26

VSS87

AH26

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

G28

VSS92

F15

VSS187

H15

VSS188

AB17

VSS206

AD17

VSS207

B16

VSS208

G18

VSS209

AA18

VSS210

AC18

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

AB19

VSS217

AD19

VSS218

AF19

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

GND

GROUND

5

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

VCORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

GND

H18

B20

E21

H22

J23

H24

F26

V10

G13

K14

Y14

G15

J15

H16

K16

Y16

G17

J17

F18

K18

Y18

E19

G19

J19

F20

H20

K20

M20

P20

T20

V20

Y20

G21

J21

L21

N21

R21

U21

W21

F22

K22

M22

P22

T22

V22

Y22

E23

G23

L23

N23

R23

U23

W23

B24

D24

F24

K24

M24

P24

T24

V24

Y24

K26

P26

V26

U1D

L7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

N7

VDD10

L9

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDD19

VDD20

VDD21

VDD22

VDD23

VDD24

VDD25

VDD26

VDD27

VDD28

VDD29

VDD30

VDD31

VDD32

VDD33

VDD34

VDD35

VDD36

VDD39

VDD38

VDD37

VDD40

VDD41

VDD42

VDD43

VDD44

VDD45

VDD46

VDD47

VDD48

VDD49

VDD50

VDD51

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

VDD59

VDD60

VDD61

VDD62

VDD63

VDD64

VDD65

VDD66

VDD67

VDD68

VDD69

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

VDD77

VDD78

VDD79

VDD80

VDD81

VDD82

VDD83

VDD84

VDD85

VDD86

VDD87

VDD88

VDD89

VDD90

VDD91

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

VCORE

LAYOUT: Place 6 EMI caps along bottom right side of Clawhammer,

2 in middle of HT link, and 12 along bottom left side of Claw-hammer.

VCORE

C122

VCORE

C86

C0.22U16Y

VDD_25_SUS VTT_DDR_SUS

VDD_25_SUS

GND

2

GND

3

GND

4

GND

5

GND

6

GND

7

GND

8

GND

9

GND

10

GND

C123

C121

{nopop}

C1U10Y

C1U10Y

In CPU.

C34

C180P50N

C0.22U16Y

C43

X_0.22u

{nopop}

Place between DIMN1 & 2

VDD_25_SUS

C79

X_C0.1U25Y

GND

C120

C82

{nopop}

X_0.22u

X_4.7u/0805

C1U10Y

11

GND

12

GND

13

GND

14

GND

15

GND

16

GND

17

GND

18

GND

19

GND

20

GND

GND

C107

{nopop}

C111

{nopop}

C1U10Y

C188

C8.2P50N

C110

C106

C1U10Y

C119

C180P50N C399

X_6.8pF

C85

C0.22U16Y

C1U10Y

22U

LAYOUT: Place beside processor.

0.22u

3

{nopop}

C160

C0.1U25Y

C176

X_4.7u/0805

C93

C51

X_4.7u/0805

C63

C28

C0.22U16Y

C157

0.22u

22U

C137

C46

22U

C116

22U

C115

22U

GND

VCORE

C105

C8.2P50N

X_C0.22U16Y/BACK

X_C8.2P50N/BACKC78

solder side

C184

C0.22U16Y C398

VTT_DDR_SUS

C42

C50

C4.7U10Y0805

104P

GND

C94

C132

X_C4.7U10Y0805

104P

C131

X_C0.22U16Y

C71

BACK decoupling Cap.

X_22U/BACK

C401

X_22U/BACK

C180

X_C0.22U16Y

2

C396

X_22U/BACK

solder side

C54

X_0.22u

C0.22U16Y

GND

C403

C145

C4.7U10Y0805

X_C0.1U16X

C402

X_22U/BACK

C96

C0.1U16X

BACK

C400

X_6.8pF

close to C457

solder side

VDD_25_SUS

C197

GND

C397

X_6.8pF

solder side

VDD_25_SUS

C405

X_104P

close to C29

solder side

GND

C77

X_104P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C395

X_104P

K8 POWER & GND

close to C456

solder side

C404

X_104P

Reserved for EMI

MS-7034

Last Revision Date:

Monday, May 10, 2004

Sheet

1

6 39

of

Rev

10A

5

4

3

2

1

VCC1_6

U2A

PBGA708_CK8G

AJ26

SP_VDD

D D

C C

B B

C300

C0.1U25Y

TP_SP_TEST1

C299

3VDUAL

C0.1U25Y

TP_SP_TEST1

R168 12.7KR1%

R187 8.66KR1%

R169 0R

12/24 NVIDIA RECOMMEND

CADIP0 CADOP0

CADIP1

CADIP2

CADIP3

CADIP4

CADIP5

CADIP6

CADIP7

CADIP8

CADIP9

CADIP10

CADIP11

CADIP12

CADIP13

CADIP14

CADIP15

CADIN0

CADIN1

CADIN2

CADIN3

CADIN4

CADIN5

CADIN6

CADIN7

CADIN8

CADIN9

CADIN10

CADIN11

CADIN12

CADIN13

CADIN14

CADIN15

CLKIP0<4>

CLKIN0<4>

CLKIP1<4>

CLKIN1<4>

CTLIP0<4>

CTLIN0<4>

CPUVDD_EN

HTVDD_EN

HT_VLD#

MEM_VLD#

CPU_VLD#

A21

B21

C24

E21

F21

AL30

AL29

AL27

AJ29

AK28

AK25

AL26

AM25

AJ25

AP18

AP17

AN16

AP15

AN13

AP12

AP11

AN10

AL18

AJ16

AJ15

AL15

AJ13

AL12

AJ12

AJ10

AN18

AN17

AM16

AN15

AM13

AN12

AN11

AM10

AM18

AK16

AK15

AM15

AK13

AM12

AK12

AJ11

AP14

AN14

AJ14

AK14

AP9

AN9

A2

C2

B1

B4

B2

NC1

NC3

V3P3_DEEP

NC5

SLP_DEEP#

SP_TEST

SP_TERM

SP_RBIA S

SP_TEST_CLK

NC7

NC8

NC9

NC10

NC11

HT1_TXD0

HT1_TXD1

HT1_TXD2

HT1_TXD3

HT1_TXD4

HT1_TXD5

HT1_TXD6

HT1_TXD7

HT1_TXD8

HT1_TXD9

HT1_TXD10

HT1_TXD11

HT1_TXD12

HT1_TXD13

HT1_TXD14

HT1_TXD15

HT1_TXD0*

HT1_TXD1*

HT1_TXD2*

HT1_TXD3*

HT1_TXD4*

HT1_TXD5*

HT1_TXD6*

HT1_TXD7*

HT1_TXD8*

HT1_TXD9*

HT1_TXD10*

HT1_TXD11*

HT1_TXD12*

HT1_TXD13*

HT1_TXD14*

HT1_TXD15*

HT1_TXCLK0

HT1_TXCLK0*

HT1_TXCLK1

HT1_TXCLK1*

HT1_TXCTL

HT1_TXCTL*

CPUVDD_EN

HT1VDD_EN

HT1_VLD*

MEM_VLD*

CPU_VLD*

?

A A

1 OF 7

CK8S

SP_3.3V

NC12

NC13

SP_TX0+

SP_TX0-

SP_RX0SP_RX0+

SP_TX1+

SP_TX1-

SP_RX1SP_RX1+

HT1_RXD0

HT1_RXD1

HT1_RXD2

HT1_RXD3

HT1_RXD4

HT1_RXD5

HT1_RXD6

HT1_RXD7

HT1_RXD8

HT1_RXD9

HT1_RXD10

HT1_RXD11

HT1_RXD12

HT1_RXD13

HT1_RXD14

HT1_RXD15

HT1_RXD0*

HT1_RXD1*

HT1_RXD2*

HT1_RXD3*

HT1_RXD4*

HT1_RXD5*

HT1_RXD6*

HT1_RXD7*

HT1_RXD8*

HT1_RXD9*

HT1_RXD10*

HT1_RXD11*

HT1_RXD12*

HT1_RXD13*

HT1_RXD14*

HT1_RXD15*

HT1_RXCLK0

HT1_RXCLK0*

HT1_RXCLK1

HT1_RXCLK1*

HT1_RXCTL

HT1_RXCTL*

HT1_STOP*

HT1_RSET

CPU_SLP*/GPIO

THERMTRIP*/GPIO

CPU_RST*

CPU_PWROK

CPU_CLK

CPU_CLK*

CPU_COMP

AP24

AK27

AM27

AP26

AN26

AN27

AP27

AN28

AM29

AP29

AN29

AL1

AM1

AN1

AN2

AN4

AN5

AN6

AM7

AM4

AL5

AJ5

AL6

AJ7

AJ8

AK10

AM9

AL2

AM2

AP1

AP2

AP4

AP5

AP6

AN7

AM3

AL4

AK5

AK6

AK7

AK8

AK9

AL9

AN3

AP3

AM6

AM5

AN8

AP8

AK17

AL3

C3

AJ19

AL20

AK19

AN19

AM19

AP20

CADOP1

CADOP2

CADOP3

CADOP4

CADOP5

CADOP6

CADOP7

CADOP8

CADOP9

CADOP10

CADOP11

CADOP12

CADOP13

CADOP14

CADOP15

CADON0

CADON1

CADON2

CADON3

CADON4

CADON5

CADON6

CADON7

CADON8

CADON9

CADON10

CADON11

CADON12

CADON13

CADON14

CADON15

LDTSTOP#

HT_RSET

CPU_SLP#

OVT1#

CPURST#

CPU_GD

CPUCLK0_H

CPUCLK0_L

CPU_COMP

C283

C0.1U25Y

2200PC280

2200PC281

2200PC269

2200PC270

CLKOP0 <4>

CLKON0 <4>

CLKOP1 <4>

CLKON1 <4>

CTLOP0 <4>

CTLON0 <4>

LDTSTOP# <5>

C271

X_C0.1U25Y

TXP1

TXN1

RXN1

RXP1

TXP2

TXN2

RXN2

RXP2

24.9R1%

R201

CPURST# <5>

CPU_GD <5>

CPUCLK0_H <5>

CPUCLK0_L <5>

R188

549R1%

L10 300L700m_250_0805

CP8 X_COPPER

SATA1

1

GND

2

HT+

3

HT-

4

GND

5

HR-

6

HR+

7

GND

CONN-SATA_white

SATA2

1

GND

2

HT+

3

HT-

4

GND

5

HR-

6

HR+

7

GND

CONN-SATA_white

12/23 A02 CHANGE

VCC3

MEM_VLD#

C374

X_C0.1U25Y

N-MMBT3904_SOT23

CPU_VLD#

C350

X_C0.1U25Y

N-MMBT3904_SOT23

HT_VLD#

C351

C0.1U25Y

N-MMBT3904_SOT23

N-MMBT3904_SOT23

Q30

Q27

Q29

3VDUAL

3VDUAL

3VDUAL

CE

R284

R260

R252

4.7KR

4.7KR

4.7KR

Q37

B

R283

1KR

R262

1KR

R278

1KR

R905

1K

SLP_S5# <11,30>

CPUVDD_EN

HTVDD_EN

HT_PWRGD <30>

OVT1#

CPU_SLP#

VCC3 3VDUAL

R196

4.7KR

R254

X_4.7KR

CADIP[0..15]<4>

CADIN[0..15]<4>

CADOP[0..15]<4>

CADON[0..15]<4>

5

4

CADIP[0..15]

CADIN[0..15]

CADOP[0..15]

CADON[0..15]

3

2

Micro Star Restricted Secret

Title

nFORCE3-1(HDT)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7034

Last Revision Date:

Monday, May 24, 2004

Sheet

7 39

1

Rev

10A

of

5

4

3

2

1

U2B

PBGA708_CK8G

M33

AD32

AC33

AB30

AC30

AG33

AG29

AC29

AH29

AG31

AK34

AJ33

AJ32

AH33

P32

P33

N33

T33

T32

U32

U33

R33

R34

V33

L33

M32

L34

N32

M34

R29

T30

U30

U29

P34

R32

R30

AGP_SBA0*

AGP_SBA1*

AGP_SBA2*

AGP_SBA3*

AGP_SBA4*

AGP_SBA5*

AGP_SBA6*

AGP_SBA7*

AGP_SBSTBF

AGP_SBSTBS

AGP_ADSTBF0

AGP_ADSTBS0

AGP_ADSTBF1

AGP_ADSTBS1

AGP_CBE0

AGP_CBE1

AGP_CBE2

AGP_CBE3

AGP_ST0

AGP_ST1

AGP_ST2

AGP_RBF

AGP_WBF

AGP_FRAME

AGP_IRDY

AGP_TRDY

AGP_REQ

AGP_GN T

AGP_STOP

AGP_DEVSEL

AGP_PAR

AGP_DBI1

AGP_DBI0

AGP_CAL_VDDQ

AGP_CAL_GND

AGP_8XDE*

SBA0<16>

SBA1<16>

AD_STBF0<16>

AD_STBS0<16>

AD_STBF1<16>

AD_STBS1<16>

GC/BE#[3..0]

GDEVSEL<16>

VDDQ

SBA2<16>

SBA3<16>

SBA4<16>

SBA5<16>

SBA6<16>

SBA7<16>

SB_STBF<16>

SB_STBS<16>

ST0<16>

ST1<16>

ST2<16>

RBF<16>

WBF<16>

GFRAME<16>

GIRDY<16>

GTRDY<16>

GREQ<16>

GGNT<16>

GSTOP<16>

GPAR<16>

DBIH<16>

DBIL<16>

GC/BE#0

GC/BE#1

GC/BE#2

GC/BE#3

R224 51.1R1%

R227 51.1R1%

D D

GC/BE#[3..0]<16>

C C

AGP8XDET#<16>

2 OF 7

CK8S

AGP_AD0

AGP_AD1

AGP_AD2

AGP_AD3

AGP_AD4

AGP_AD5

AGP_AD6

AGP_AD7

AGP_AD8

AGP_AD9

AGP_AD10

AGP_AD11

AGP_AD12

AGP_AD13

AGP_AD14

AGP_AD15

AGP_AD16

AGP_AD17

AGP_AD18

AGP_AD19

AGP_AD20

AGP_AD21

AGP_AD22

AGP_AD23

AGP_AD24

AGP_AD25

AGP_AD26

AGP_AD27

AGP_AD28

AGP_AD29

AGP_AD30

AGP_AD31

AGP_PME*

AGP_CLK

APG_VREF

AA33

AA32

AB32

Y33

AB33

Y32

AC32

W33

V32

AE32

AD33

AF33

AE33

AG32

AF32

AH32

AJ30

AF31

AF29

AE30

AF30

AD30

AD29

AC31

AA29

AA30

Y29

Y31

Y30

W30

V30

U31

E26

W32

V29

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

AGP_PME#

R221 22R

C313

C10P50N

C306

C0.1U25Y

GAD[31..0] <16>

AGP_PME# <16>

AGP_CLK <16>

AGPVREF_GC<16>

AGP_PME#

3VDUAL

R272

4.7KR

?

B B

A A

Micro Star Restricted Secret

Title

nFORCE3-2(AGP8X)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

MS-7034

1

Last Revision Date:

Monday, May 24, 2004

Sheet

8 39

Rev

10A

of

5

4

3

2

1

U2C

PBGA708_CK8G

D D

C C

AD[31..0]<17,18,24,25>

C_BE#[3..0]<17,18,24,25>

8P4R-8.2KR

RN72

RN71

8P4R-8.2KR

RN74

8P4R-8.2KR

PCI_PME#

12

34

56

78

12

34

56

78

12

34

56

78

DEVSEL#

TRDY#

IRDY#

FRAME#

SERR#

PERR#

STOP#

CLKRUN#

PREQ#0

PREQ#1

PREQ#2

PREQ#3

DEVSEL#<17,18,24,25>

PCI_PME#<17,18,24>

AGPRST#<16>

PCIRST#1<17,18>

PCIRST#2<25>

PCIRST#1

PCIRST#2

PCIRST#3<20,22,24>

R271 8.2KR

3VDUAL

VCC3

B B

PCIRST#4<30>

R213 8.2KR

RN69

8P4R-8.2KR

PIRQ#A

PIRQ#C

12

PIRQ#D

34

PIRQ#E

56

PIRQ#B

78

VCC3

AD0

C33

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

FRAME#

FRAME#<17,18,24,25>

IRDY#

IRDY#<17,18,24,25>

TRDY#

TRDY#<17,18,24,25>

STOP#

STOP#<17,18,24,25>

DEVSEL#

PAR

PAR<17,18,24,25>

SERR#

SERR#<17,18,24>

PERR#

PERR#<17,18,24,25>

PCI_PME#

CLKRUN#

PCI_AD0

D30

PCI_AD1

E33

PCI_AD2

C31

PCI_AD3

D34

PCI_AD4

F28

PCI_AD5

B33

PCI_AD6

E32

PCI_AD7

B31

PCI_AD8

D33

PCI_AD9

A32

PCI_AD10

C34

PCI_AD11

E31

PCI_AD12

B34

PCI_AD13

D32

PCI_AD14

E34

PCI_AD15

G32

PCI_AD16

F33

PCI_AD17

G33

PCI_AD18

H32

PCI_AD19

H34

PCI_AD20

H33

PCI_AD21

H30

PCI_AD22

J30

PCI_AD23

J34

PCI_AD24

K33

PCI_AD25

J29

PCI_AD26

J33

PCI_AD27

K30

PCI_AD28

K29

PCI_AD29

K32

PCI_AD30

L32

PCI_AD31

G29

PCI_CBE0*

B32

PCI_CBE1*

F34

PCI_CBE2*

J32

PCI_CBE3*

J31

PCI_FRAME*

G30

PCI_IRDY*

F29

PCI_TRDY*

F31

PCI_STOP*

F30

PCI_DEVSEL*

F32

PCI_PAR

A33

PCI_SERR

C32

PCI_PERR*

F26

PCI_PME*

B24

PCI_CLKRUN*

P29

PCI_RST0*

L30

PCI_RST1*

C25

PCI_RST2*

K5

PCI_RST3*

H6

PCI_RST4*

?

C7

X_33P

3 OF 7

CK8S

PCI_REQ0*

PCI_REQ1*

PCI_REQ2*

PCI_REQ3*

PCI_REQ4*

PCI_REQ5*

PCI_GNT0*

PCI_GNT1*

PCI_GNT2*

PCI_GNT3*

PCI_GNT4*

PCI_GNT5*

PCI_INTW*

PCI_INTX*

PCI_INTY*

PCI_INTZ*

PCI_INTE*

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

PCI_CLK6

PCI_CLKFB

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME*

LPC_DRQ0*

LPC_DRQ1*

SERIRQ

PCI_CLK7

PREQ#0

C29

E29

D27

D26

A30

A31

E27

D29

E28

C26

B29

B30

M30

N29

M29

N30

P30

A29

C28

B28

B27

A27

B26

A26

B25

H1

H2

H3

G2

F2

J3

F1

G3

E2

PREQ#0 <17>

PREQ#1

PREQ#1 <17>

PREQ#2

PREQ#2 <18>

PREQ#3

PREQ#3 <25>

PREQ#4

PREQ#4 <24>

PREQ#5

PGNT#0

PGNT#0<17>

PGNT#1

PGNT#1<17>

PGNT#2

PGNT#2<18>

PGNT#3

PGNT#3<25>

PGNT#4

PGNT#4<24>

PGNT#5

PIRQ#A

PIRQ#A <16,17,18>

PIRQ#B

PIRQ#B <16,17,18>

PIRQ#C

PIRQ#C <17,18>

PIRQ#D

PIRQ#D <17,18,25>

PIRQ#E

PIRQ#E <24>

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

PCI_CLK6

PCICLKFB

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_DRQ#

FLASH_CS#

SERIRQ

PCI_CLK7 PCICLKFB

R249 22R

C332

X_10P

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

RN75

8P4R-22R

RN78

8P4R-22R

LPC_AD[3..0] <20,22>

LPC_FRAME# <20,22>

LPC_DRQ# <20>

SERIRQ <20>

PCICLK0 <17>

PCICLK1 <17>

PCICLK2 <18>

PCICLK3 <25>

PCICLK4 <22>

PCICLK5 <24>

PCICLK6 <20>

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLK5

PCI_CLK6

LPC_DRQ#

FLASH_CS#

SERIRQ

CN22

1 2

3 4

5 6

7 8

8P4C-10P50N

CN23

1 2

3 4

5 6

7 8

8P4C-10P50N

R235 8.2KR

R237 8.2KR

R236 8.2KR

VCC3

PREQ#5

PREQ#4

A A

R257 8.2KR

R256 8.2KR

5

Micro Star Restricted Secret

Title

nFORCE3-3(PCI&LPC)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

4

3

2

http://www.msi.com.tw

MS-7034

1

Last Revision Date:

Monday, May 24, 2004

Sheet

9 39

Rev

10A

of

5

BUF_SIO_CLK_SELECT

0=14.318MHZ

1=24MHZ(default)

AC_RST#(BUF_125_25MHZ SELECT)

0=25MHZ

1=125MHZ(default)

AC_SYNC

0=RESEVED

1=NORMAL MODE

(default)

D D

AC_24<26> USBP2 <28>

AC_BITCLK<26>

VCC3

R264

8.2KR

R261

X_8.2KR

R255

8.2KR

AC_RST#

SB_SPDO

AC_SYNC

R267

X_8.2KR

R308

8.2KR

Stuff by nVIDIA

check@010693

C C

[AC_SYNC, EE_DATAO] straps [0,0] for "No External SATA PHY". Please remove R355 and stuff R373.@010693

AC_SDOUT<26>

AC_SDIN0<26>

SB_SPDO<26>

AC_RST#<26>

AC_SYNC<26>

VCC3

L11 X_300L700m_250_0805

CP9 X_COPPER

3VDUAL

B B

L12 X_300L700m_250_0805

CP10 X_COPPER

C359 C18P50N

C360 C18P50N

C371

X_10P

R280 22R

SB_SPDO

AC_RST#

AC_SYNC

C345

104P

Y4

32.768KHZ12.5P_D

4

4 OF 7

CK8S

USB_OC1*/GPIOAUX

USB_OC2*/GPIOAUX

USB_OC3*/GPIOAUX

USB_OC4*/GPIOAUX

USB_OC5*/GPIOAUX

USB_OC6*/GPIOAUX

USB_OC7*/GPIOAUX

+3.3V_USB_DUAL

+3.3V_USB_DUAL

C330

104P

R903

R281

8.2KR

AJ24

AJ23

AJ22

AJ21

AJ20

AK24

AK23

AK22

AK20

AL23

AL21

AM24

AM23

AM22

AM21

AN24

AN23

AN22

AN21

AN25

AP23

AP21

AM28

C15

C16

F17

F16

E15

B16

E16

E17

E1

C324

X_105P

C1

A11

B11

U2D

PBGA708_CK8G

AC97_CLK

AC_BITCLK

AC_SDATA_OU T

AC_SDATA_IN0

AC_SDATA_IN1

SPDIF

AC_RESET*

AC_SYNC

NC14

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC26

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

+3.3V_PLL

+3.3V_PLL_DUAL

XTALIN_RTC

XTALOUT_RTC

?

X_10M

3

D20

USB0

C20

USB0*

E22

USB1

F22

USB1*

D21

USB2

C21

USB2*

E23

USB3

F23

USB3*

E24

USB4

F24

USB4*

E25

USB5

F25

USB5*

A20

USB6

B20

USB6*

A23

USB7

B23

USB7*

USB signal are worse than others

D18

USB_OC0*

E18

B18

C17

XTALIN

XTALOUT

USB_RBIA S

A18

D17

B22

C22

B19

C19

D24

E19

A17

R263

732R1%

LAN_RST#

USBP2

USBN2

USBP3

USBN3

USBP0

USBN0

USBP1

USBN1

USBP6

USBN6

USBP7

USBN7

USBP4

USBN4

USBP5

USBN5

USBN2 <28>

USBP3 <28>

USBN3 <28>

USBP0 <27>

USBN0 <27>

USBP1 <27>

USBN1 <27>

USBP6 <28>

USBN6 <28>

USBP7 <28>

USBN7 <28>

USBP4 <27>

USBN4 <27>

USBP5 <27>

USBN5 <27>

2

USBP0

USBN0

USBP1

USBN1

USBN3

USBP3

USBN2

USBP2

USBN5

USBP5

USBN4

USBP4

front side USB port

USBP7

USBN7

USBP6

USBN6

front side USB port

RN83

12

34

56

78

8P4R-15KR

RN76

12

34

56

78

8P4R-15KR

RN79

12

34

56

78

8P4R-15KR

RN80

12

34

56

78

8P4R-15KR

1

Swap(U2.A20, B20, A23, B23, C21, D21, E23, F23 to front side USB port)

& (U2.C20, D20, E22, F22, E24, F24, F25, E25 to rear side USB port)for EMI modify @011993

USB_OC#1 <28>

USB_OC#5 <27>

LAN_RST# <24>

020493

C368 C18P50N

3VDUAL

Y3

25MHZ18P_D-1

C369 C18P50N

C411

X_C0.1U25Y/BACK

solder side

VCC3

C386

C352

A A

X_104P

close to Y2 for EMI @011993

5

4

VCC3 VCC

X_104P

close to RN14 @020393

Micro Star Restricted Secret

Title

nFORCE3-4(AC97&USB)

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

MS-7034

1

Last Revision Date:

Monday, May 24, 2004

Sheet

10 39

Rev

10A

of

5

D D

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXD3

RN66

12

34

56

78

X_8P4R-10KR

MII_RX_ER

MII_RXCTL

MII_TXCLK

MII_RXCLK

RN68

12

34

56

78

X_8P4R-10KR

C C

No stuff RTL8201BL=>must pull

down@930106

MII_TXD[3..0]<24>

R294

10KR

3VDUAL

MII_TXCLK<24>

R186

1KRST

R170

1KR

C282

C0.1U25Y

LAN_EEDO LAN_EE_CLK

0 0

001

1

1 1

No stuff RTL8201BL=>MII_VREF must pull down@930106

MII_VREF:R186=1KRST @930427

B B

(EXTRNAL SATA SELECT)

NO EXTERNAL SATA PHY

RSPI INTERFACE FOR EXTERNAL

SATA PHY

RESERVED

RESERVED

SATA STRAPS

LAN_EE_CLK

LAN_EE_DO

R295

10KR

3VDUAL

R171

R268

1.5KR

2.2KR

MII_MDIO

LID#

MII:R186=1KRST, R171=1.5K

A A

RGMII:R186=1.56KRST, R171=2.2K

MII_TXCLK

MII_TXCTL<24>

MII_RXCLK<24>

MII_RXCTL<24>

C273

R181 22R

MII_RXD0<24>

MII_RXD1<24>

MII_RXD2<24>

MII_RXD3<24>

MII_RX_ER<24>

MII_COL<24>

MII_MDIO<24>

MII_CRS<24>

MII_MDC<24>

ATADET0<19>

ATADET1<19>

VSET0<22>

VSET1<22>

VSET2<22>

BIOS_DIS#<22>

SATALED#<32>

X_10P

3VDUAL

VCC3

4

C322

X_10P

C274

X_10P

RN67 8P4R-0R

MII_TXD0

MII_TXD1

MII_TXD2

MII_TXD3

MII_TXCTL

MII_RXD0

MII_RXD1

MII_RXD2

MII_RXD3

MII_RXCLK

MII_RXCTL

MII_RX_ERMII_RX_ER

MII_COL

MII_MDIO

MII_CRS

MII_MDC

LAN_EE_CLK

LAN_EE_DO

ATADET0

ATADET1

VSET0

VSET1

020493

LID#

VSET2

BIOS_DIS#

SATALED#

R299 10KR

R211 60.4R1%

R212 60.4R1%

SATAREF

7 8

5 6

3 4

1 2

AP31

AP32

AL32

AL31

AM31

AP33

AN32

AN34

AM33

AM34

AL33

AP34

AM32

AJ27

AN33

AK31

AK33

AN31

AL34

AK32

B12

A12

B13

C13

AE2

E14

D14

F12

B15

B14

B17

E11

E13

F13

AG1

N6

N5

P5

P6

N3

N2

P3

P2

P1

R3

R2

J5

M2

K2

L3

L2

L1

L6

L5

M5

M6

M3

M1

J2

R1

K6

E3

J1

K3

Y6

E8

B7

F8

D3

D2

C4

E4

E9

U2E

PBGA708_CK8G

SATA_TD0 / TXD0

SATA_TD1 / TXD1

SATA_TD2 / TXD2

SATA_TD3 / TXD3

SATA_TD4 / TXD4

SATA_TD5 / TXD5

SATA_TD6 / TXD6

SATA_TD7 / TXD7

SATA_TD8 / TXD8

SATA_TD9 / TXD9

SATA_CTL_T / NC

SATA_TCK / TBC

SATA_COMWAKE / RXD0

SATA_RD0 / RXD1

SATA_RD1 / RXD2

SATA_RD2 / RXD3

SATA_RD3 / RXD4

SATA_RD4 / RXD5

SATA_RD5 / RXD6

SATA_RD6 / RXD7

SATA_RD7 / RXD8

SATA_RD8 / RXD9

SATA_RD9 / RXD_VALID

SATA_PHY_RDY / RBC1

SATA_CTL_R / NC

SATA_RCK / ASIC_CLK

SATA_VREF

SATA_COMINIT / RBC0

SATA_CLK

BUF_25MHZ

G/MII_TXD0

G/MII_TXD1

G/MII_TXD2

G/MII_TXD3

G/MII_TXCLK

G_TXCTL/MII_TXEN

G/MII_RXD0

G/MII_RXD1

G/MII_RXD2

G/MII_RXD3

G/MII_RXCLK

G_RXCTL/MII_RXDV

MII_VREF

MII_RXER

MII_COL

G/MII_MDIO

MII_CRS

G/MII_MDC

MII_PWRDWN

EE_SEL

EE_CLK

EE_DATAO

EE_DATAI

GPIO_1

GPIO_2

GPIO_4

GPIO_5

GPIO_6

LID*/GPIO_7

GPIO_8

GPIO_9

GPIO_10

GPIO_11

GPIO_12

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

SPIO_20/SATALED*

LLB*

IDE_COMP

?

CK8S

5 OF 7

3

IDE_DATA_P0

IDE_DATA_P1

IDE_DATA_P2

IDE_DATA_P3

IDE_DATA_P4

IDE_DATA_P5

IDE_DATA_P6

IDE_DATA_P7

IDE_DATA_P8

IDE_DATA_P9

IDE_DATA_P10

IDE_DATA_P11

IDE_DATA_P12

IDE_DATA_P13

IDE_DATA_P14

IDE_DATA_P15

IDE_ADDR_P0

IDE_ADDR_P1

IDE_ADDR_P2

IDE_CS1_P*

IDE_CS3_P*

IDE_DACK_P*

IDE_IOW_P*

IDE_INTR_P

IDE_DREQ_P

IDE_IOR_P*

IDE_RDY_P

IDE_DATA_S0

IDE_DATA_S1

IDE_DATA_S2

IDE_DATA_S3

IDE_DATA_S4

IDE_DATA_S5

IDE_DATA_S6

IDE_DATA_S7

IDE_DATA_S8

IDE_DATA_S9

IDE_DATA_S10

IDE_DATA_S11

IDE_DATA_S12

IDE_DATA_S13

IDE_DATA_S14

IDE_DATA_S15

IDE_ADDR_S0

IDE_ADDR_S1

IDE_ADDR_S2

IDE_CS1_S*

IDE_CS3_S*

IDE_DACK_S*

IDE_IOW_S*

IDE_INTR_S

IDE_DREQ_S

IDE_IOR_S*

IDE_RDY_S

A20GATE/GPIO

INTRUDER*

EXT_SMI*

RI*/GPIO

SPKR

PWRBTN*

SUSCLK

SIO_PME*/GPIO

KBRDRSTIN*/GPIO

SMB_CLK0

SMB_DATA0

SMB_CLK1

SMB_DATA1

3.3V_VBAT

SMB_ALERT*

BUF_SIO_CLK

BUF_14MHZ/GPIO

THERM*

RSTBTN*

SLP_S5*

SLP_S3*

SLP_S1*

PWRGD_SB

PWRGD

FANRPM/GPIO

FANCTL0/GPIO

FANCTL1/GPIO

TEST

V1

V5

U6

U1

U3

T3

T5

R6

R5

T6

T2

U2

V3

U5

V6

V2

Y1

Y5

AA3

AA1

AA2

W6

W2

W5

W3

Y3

Y2

AD1

AC1

AC3

AD5

AC6

AB5

AA6

AB3

AB2

AA5

AB6

AC5

AD6

AC2

AD3

AD2

AF3

AE3

AF2

AF1

AG3

AG5

AE5

AG6

AE6

AF5

AF6

A20GATE

F9

INTRUDER#

D11

EXTSMI#

A5

RI#

B5

SPKR

E10

PWRBTN#_1

C6

D1

SIO_PME#

C11

KBRST#

A3

SMB_MEM_CLK

H5

SMB_MEM_DATA

G5

SMBCLK1

B10

SMBDATA1

B9

F11

SMB_ALERT#

C10

A4

B6

OVT#

F7

FP_RST#

A8

SLP_S5#

D9

SLP_S3#

C7

C8

RSMRST#

D6

PW_OK

B3

E6

D5

C5

B8

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

R276

1KR

PDD[0..15] <19>

PDA0 <19>

PDA1 <19>

PDA2 <19>

PDCS#1 <19>

PDCS#3 <19>

PDDACK# <19>

PDIOW# <19>

IRQ14 <19>

PDREQ <19>

PDIOR# <19>

PIORDY <19>

SDD[0..15] <19>

SDA0 <19>

SDA1 <19>

SDA2 <19>

SDCS#1 <19>

SDCS#3 <19>

SDDACK# <19>

SDIOW# <19>

IRQ15 <19>

SDREQ <19>

SDIOR# <19>

SIORDY <19>

A20GATE <20>

R266 1MR

SPKR <32>

SIO_PME# <20>

KBRST# <20>

SMB_MEM_CLK <13>

SMB_MEM_DATA <13>

SMBCLK1 <30>

SMBDATA1 <30>

VBAT

SMB_ALERT# <20>

OVT# <20>

FP_RST# <32>

SLP_S5# <7,30>

SLP_S3# <20,30>

RSMRST# <30>

PW_OK <30,32>

VBAT

2

5VSB

VBAT1

BAT-2P_SO41

R269 22R

12

C342

X_C10P50N

C362

X_C10P50N

R316 560R

R315 1.5KR

S-BAT54C_SOT23

R305 1KR

PWRBTN#<20,32>

SIO_24M

D15

VBAT

12

3

ESD Diode close to DIMM slot@051793

D17

X_BAV99W

3VDUAL 3VDUAL

2

1

3

SMB_MEM_CLK SMB_MEM_DATA

C443

X_5p

PWRBTN#_1

R904 20K

PWRBTN#

SMBCLK1

SMBDATA1

SMB_MEM_CLK

SMB_MEM_DATA

SMB_ALERT#

SIO_PME#

RI#

EXTSMI#

R342 2.7KR

R343 2.7KR

R344 2.7KR

R345 2.7KR

KBRST#

OVT#

A20GATE

SIO_24M <20>

BOOT MODE SELECT

0=User Mode Boot Init table

1=Safe Mode Boot Init table(default)

1

JBAT1

1

2

3

N31+N33,1*3

R314

1KR

close to VBAT1 for EMI @011993

D18

X_BAV99W

R265

330R

RN84 8P4R-10KR

12

34

56

78

RN81 8P4R-10KR

12

34

VCC3

56

78

VCC3

SPKR

231

C444

X_5p

3VDUAL

VCC3

3VDUAL

R289

10KR

R297

X_10KR

VCC3

C323

X_104P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

nFORCE3-5(SATA&GMII&IDE)

MS-7034

Last Revision Date:

Tuesday, May 25, 2004

Sheet

1

11 39

Rev

10A

of

5

4

3

2

1

Connect to VCC by 100R from nVIDIA AP

note(External SATA Related Electrical

Overstress)@031893

C419

D D

Connect to GND by nVIDIA AP note(External SATA

Related Electrical Overstress)@031693

solder side

12/23 A02 CHANGE

C C

VCC3 VDD_12_A VDDQ

C325

C318

C0.1U25Y

C0.1U25Y

B B

VCC1_6 3VDUAL

C289

C0.1U25Y

C290

C0.1U25Y

D0G-2310903-I05:DIS,EMI/ESD protection for

I/O,INPAQ/MLVS0603M07,235p/205p(1KHz/1MHz),7Vac/9Vdc,±20%

D0G-2310903-I05:DIS,EMI/ESD protection for

I/O,INPAQ/MLVS0603M04,300p,4Vac/5Vdc,20%

X_235p

C315

C0.1U25Y

C0.1U25Y

R332

100R

VCC3

3VDUAL

X_C0.1U25Y

C288

VCC

3VDUAL

1_6VDUAL

C334

C0.1U25Y

C291

E30

AA4

A14

D12

E20

D15

C30

H29

H4

V31

V4

AD31

AD4

AF4

E5

M31

L4

R4

D8

C23

F27

G6

AK30

AJ28

F15

F19

F4

F5

F6

C309

C0.1U25Y

C406

X_300p

solder side

U2G

PBGA708_CK8G

+5V

+5V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

+3.3V

VDD_SATAD

VDD_SATAD

+3.3V_DUAL

+3.3V_DUAL

+3.3V_DUAL

+3.3V_DUAL

+3.3V_DUAL

+3.3V_DUAL

+5V_DUAL

+5V_DUAL

+1.6V_DUAL

+1.6V_DUAL

+1.6V_DUAL

?

C238

C0.1U25Y

C0.1U25Y

C266

CK8S

7 OF 7

X_C0.1U25Y

C272

C0.1U25Y

C412

X_300p

C409

C361

C0.1U25Y

R31

+1.5V

U34

+1.5V

Y34

+1.5V

AA31

+1.5V

AC34

+1.5V

AF34

+1.5V

AG30

+1.5V

AJ34

+1.5V

AG2

+1.6V

AH2

+1.6V

AH3

+1.6V

AH5

+1.6V

AH6

+1.6V

AJ1

+1.6V

AJ2

+1.6V

AJ3

+1.6V

AJ4

+1.6V

AK1

+1.6V

AK2

+1.6V

AK3

+1.6V

AK4

+1.6V

AL8

+1.2V_HT

AL11

+1.2V_HT

AL14

+1.2V_HT

AL17

+1.2V_HT

AK18

+1.2V_HT

C407

X_300p

solder side

C394

C0.1U25Y

VDDQ

VCC1_6

VDD_12_A

C303

C0.1U25Y

C316

C0.1U25Y

C294

C0.1U25Y

VCC 1_6VDUAL

C331

C0.1U25Y

C372

C0.1U25Y

A34

A24

A15

C27

C18

C14

C12

D31

D23

E12

F20

F18

F14

F10

H31

L31

L29

N22

N21

N20

N19

N18

N17

N16

N15

N14

N13

P31

P22

P21

P20

P19

P18

P17

P16

P15

P14

P13

R22

R21

R20

R19

R18

R17

R16

R15

R14

R13

T29

T22

T21

T20

T19

T18

T17

T16

T15

T14

T13

U22

U21

U20

U19

U18

U17

U16

U15

U14

U13

A9

A6

A1

C9

D4

E7

F3

J6

J4

M4

P4

U4

U2F

PBGA708_CK8G

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

?

6 OF 7

CK8S

V34

GND

V22

GND

V21

GND

V20

GND

V19

GND

V18

GND

V17

GND

V16

GND

V15

GND

V14

GND

V13

GND

W29

GND

W22

GND

W21

GND

W20

GND

W19

GND

W18

GND

W17

GND

W16

GND

W15

GND

W14

GND

W13

GND

Y22

GND

Y21

GND

Y20

GND

Y19

GND

Y18

GND

Y17

GND

Y16

GND

Y15

GND

Y14

GND

Y13

GND

Y4

GND

AA34

GND

AA22

GND

AA21

GND

AA20

GND

AA19

GND

AA18

GND

AA17

GND

AA16

GND

AA15

GND

AA14

GND

AA13

GND

AB29

GND

AB22

GND

AB21

GND

AB20

GND

AB19

GND

AB18

GND

AB17

GND

AB16

GND

AB15

GND

AB14

GND

AB13

GND

AC4

GND

AD34

GND

AE29

GND

AG34

GND

AG4

GND

AH30

GND

AJ31

GND

AJ18

GND

AJ17

GND

AJ9

GND

AJ6

GND

AK29

GND

AK26

GND

AK21

GND

AK11

GND

AL24

GND

AM30

GND

AM26

GND

AM20

GND

AM17

GND

AM14

GND

AM11

GND

AM8

GND

AN30

GND

AN20

GND

AP30

GND

VCORE

VCC3 1_6VDUALVDDQ

C420

C421

X_300p

C422

X_300p

X_300p

A A

VDD_12_A

VCORE

C417

X_C0.1U25Y

solder side

solder side; Reserved for EMI closed to C408

5

solder side

4

C252

C0.22U16Y

C408

X_C0.22U16Y

solder side

Close to CK8S side

Return Path for Vcore at CK8S side

3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

nFORCE3-6/7(POWER&GND)

MS-7034

Last Revision Date:

Wednesday, May 26, 2004

Sheet

1

12 39

Rev

10A

of

Loading...

Loading...