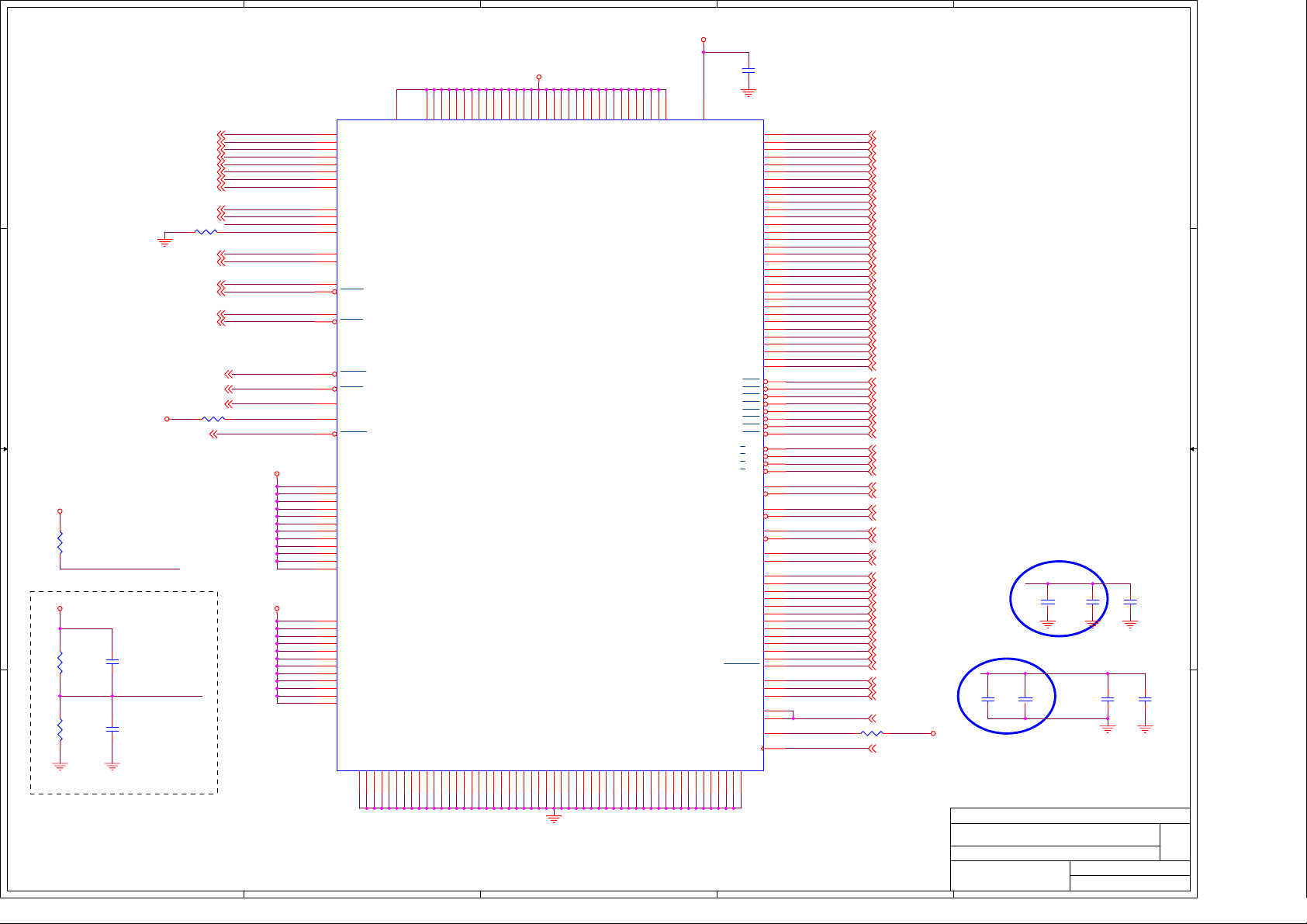

MSI MS-7021 Schematics

5

4

3

2

1

MS-7021 ATX

*AMD PGA 462 Processor

D D

*VIA KT600 / VT8237/VT8237 Chipset

(DDR 400 / AGP 8X / VLink 8X)

*Winbond 83697HF-VF LPC I/O

*RTC8201B LAN PHY

*RTL655 6 channel H/W Audio

*USB 2.0 support (integrated into VT8235/VT8237)

*Jump Less support

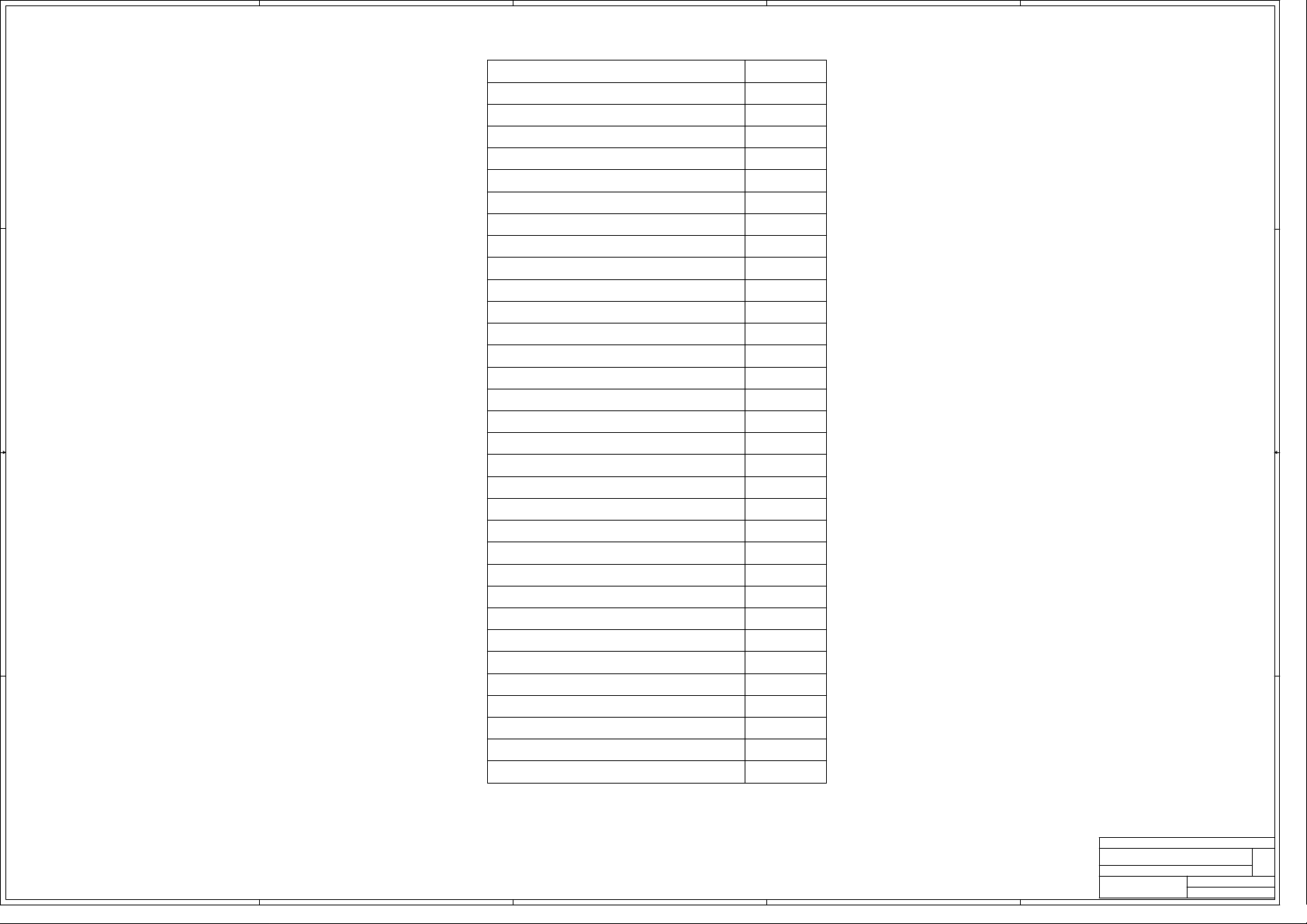

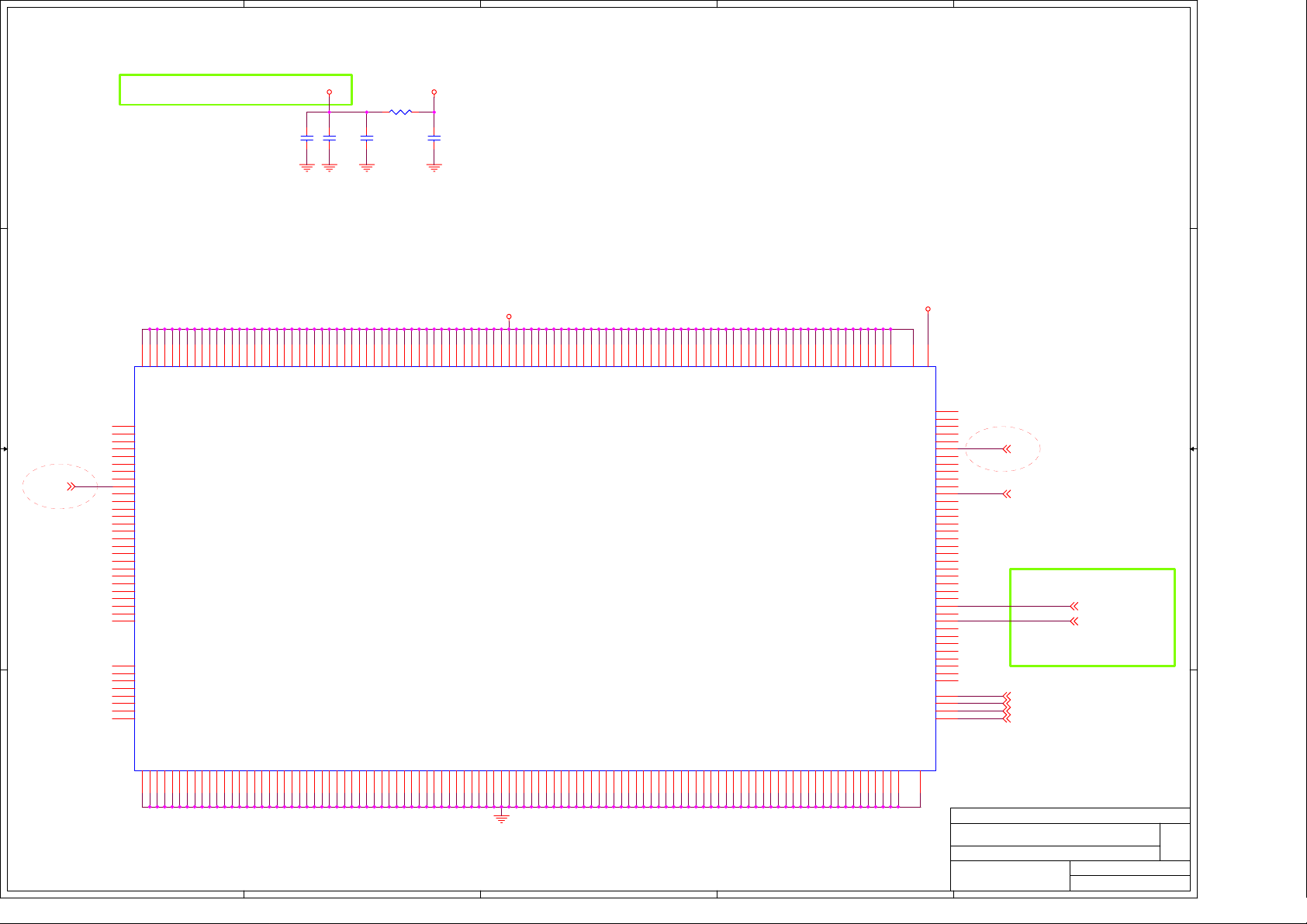

Title Page

Cover Sheet 1

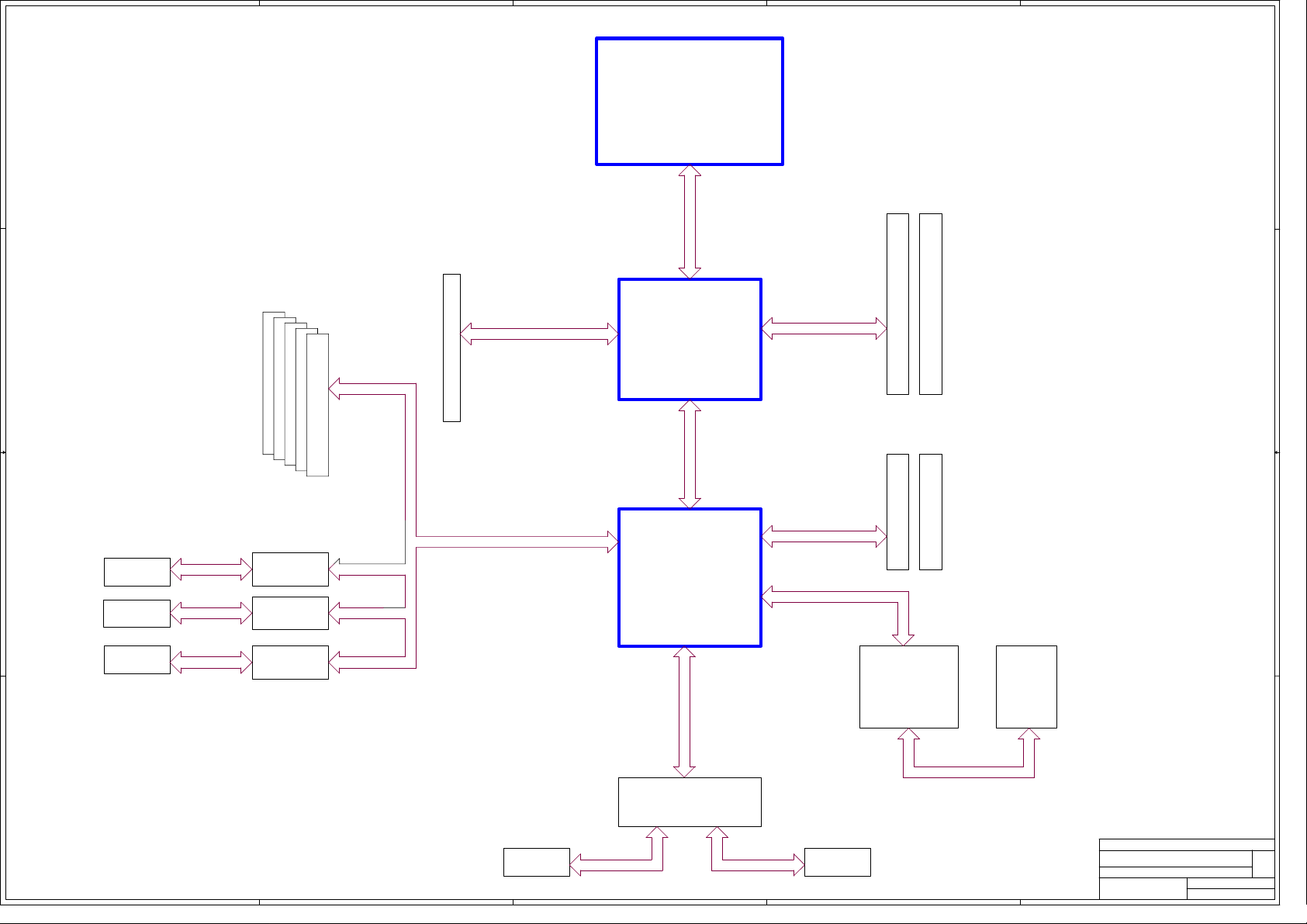

Block Diagram

2

3GPIO SPEC

4,5AMD 462 PGA Socket

Clock Synthesizer 6

KT600 7,8,9,10

System Memory

DDR Terminations

11,12

13,14

AGP SLOT 15

VT8235 / VT8237

PCI Connectors

C C

RTL655 / Connector

ATA 66/100 Connectors

LAN PHY(RTL8201B)

Front USB Port

Rear USB Port

LPC I/O

16,17,18

19,20,21

22

23

24

25

26

27

28Keyboard/Mouse Connectors

LPT/COM Port

VRM HIP6301 / 6302

CPU Ratio / Vcore

B B

DC POWER / AMD CPU Thermal P ro t ec t io n

MS-7 ACPI POWER

Front Panel

BULK / Decoupling

PWR map/CLOCK map

29

30

31

32

33

34

35

36

History 37

A A

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

1

Cover Sheet

MS-7021

Last Revision Date:

Sheet

Rev

100

Friday, September 19, 2003

137

of

5

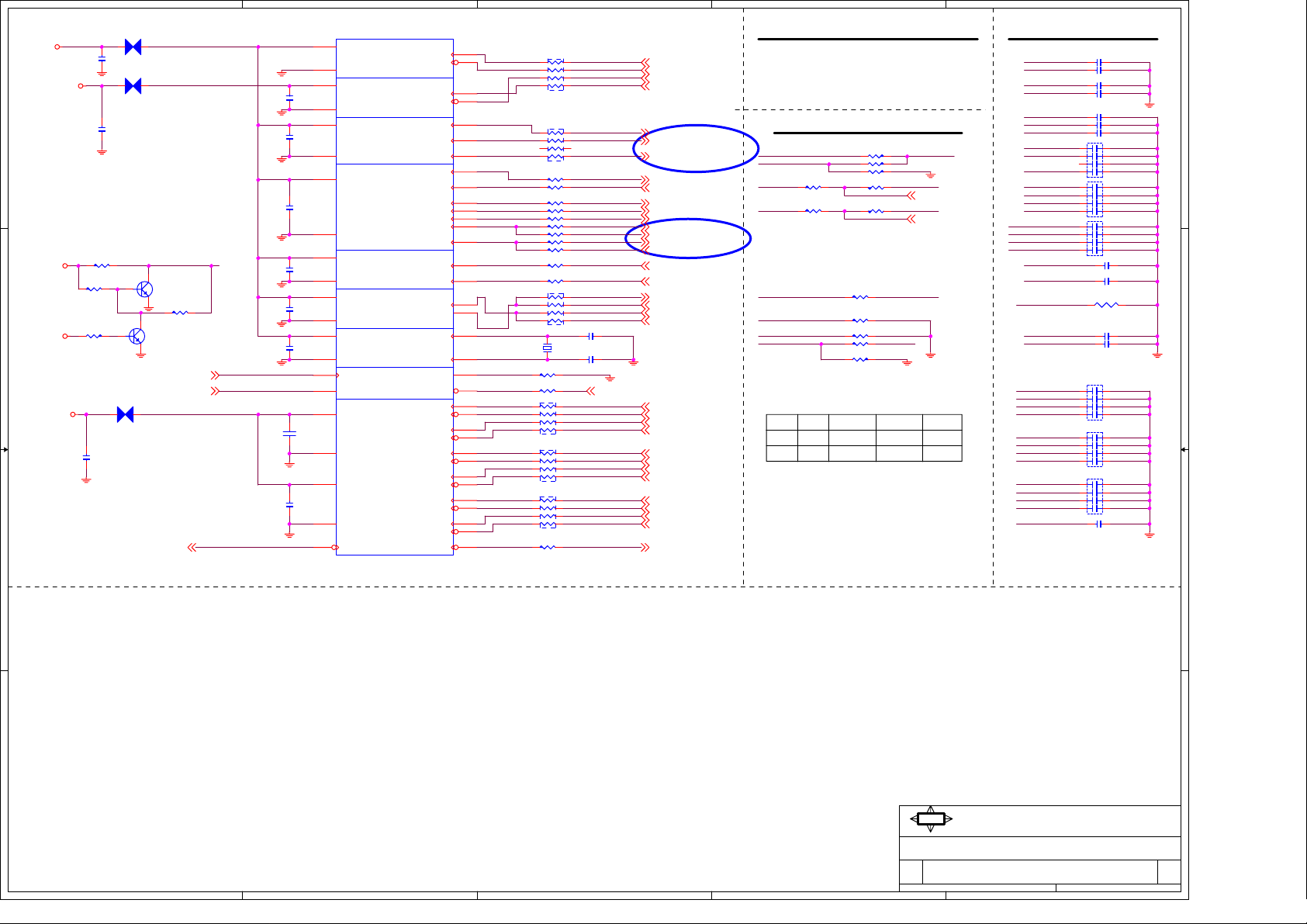

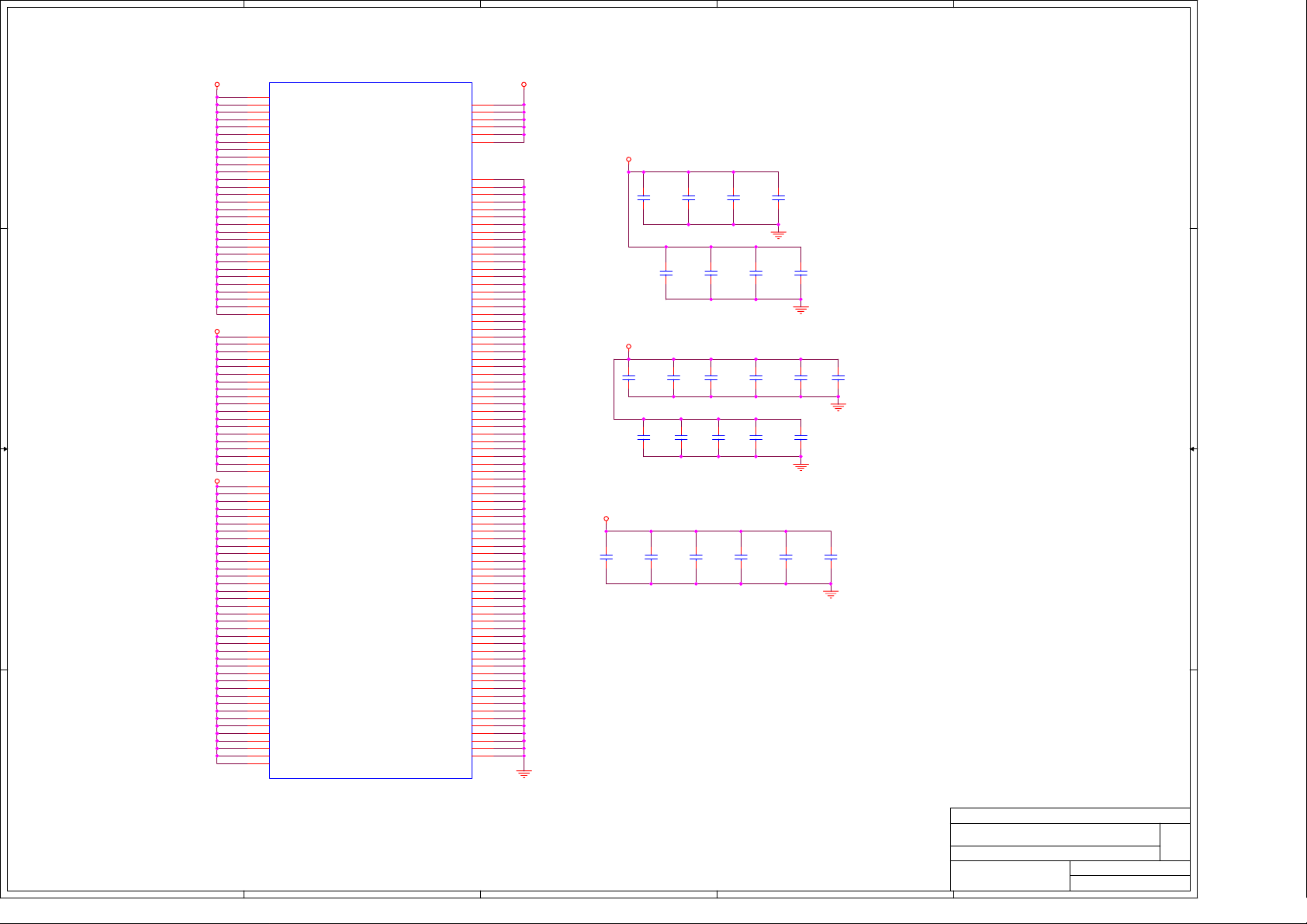

Block Diagram

4

3

2

1

D D

AMD Socket 462

FSB

100/133

166/200

A

C C

5 PCI Slots

G

P

AGP 8X /Fast Write

KT600

DDR 400

VLINK 8X

PCI-33

B B

6 ch share

by MIC

IDE Con x1

H/W

Audio

Controller

IDE

Controller

VT8237

VT8235

Dual ATA

100/133

LPC BUS

Rear 10/100

Port x1

RTL8201B

SUPER I/O ROM

USB 2.0

X BUS

A A

Rear x4 Front x1

5

4

Dual USB 1.1 OHCI

/2.0 EHCI 6 Ports

3

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Block Diagram

MS-7021

1

Last Revision Date:

Sheet

Rev

100

Friday, September 19, 2003

237

of

5

4

3

2

1

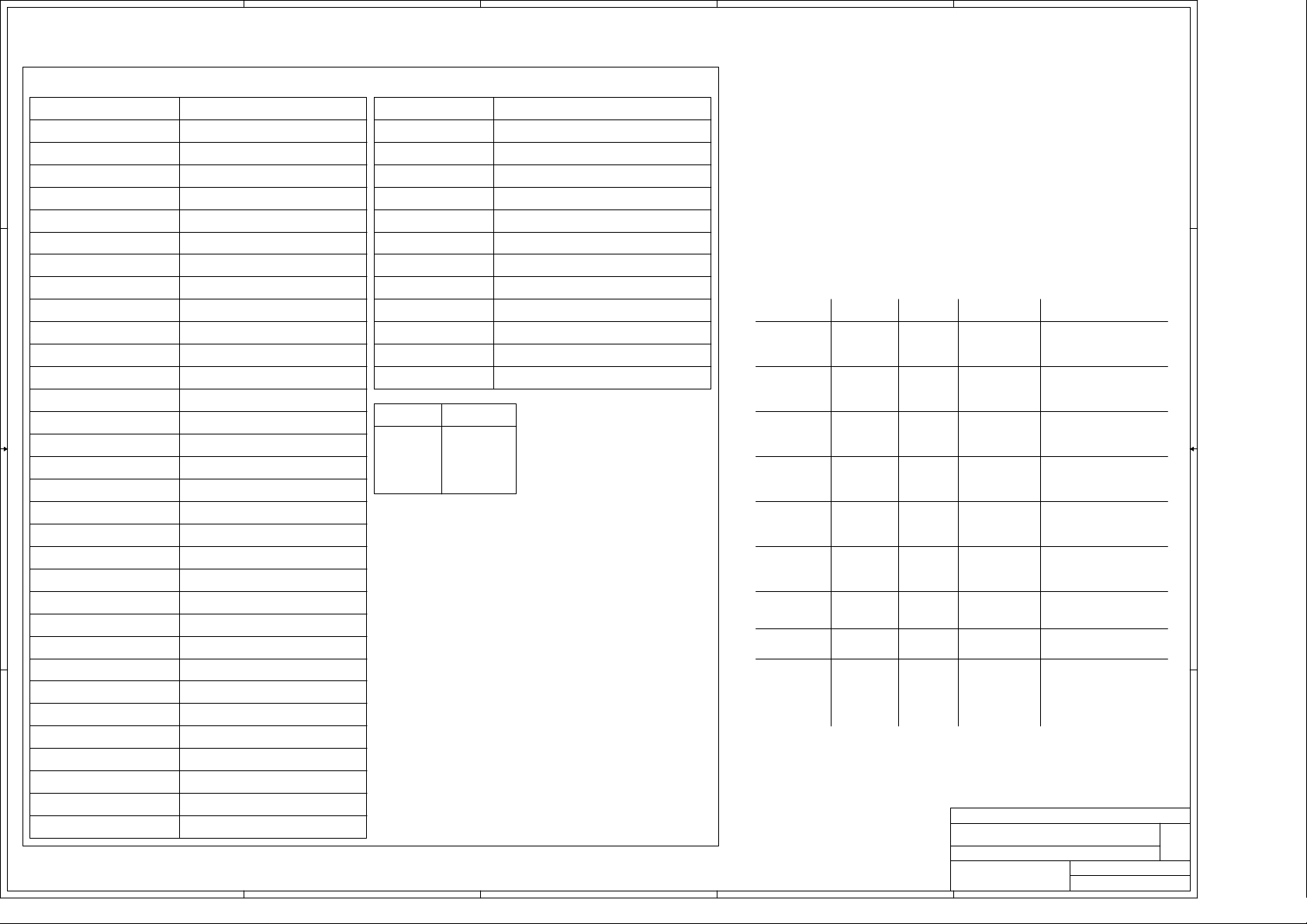

GPIO FUNCTION

VT8235 (CE) GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/GNT5#

GPO8/GPI8/PCREQA

GPO9/GPI9/PCREQB

C C

GPO0

SUSA#

SUSB#

SUSST1#

SUSCLK

CPUSTP#

PCISTP#

GNT5#

Exteranl Pull up to VCC3

Exteranl Pull up to VCC3

GPO10/GPI10

GPO11/GPI11

GPO12/GPI12/INTE#/PCGMA

GPO13/GPI13/INTF#/PCGMB

GPO14/GPI14/INTG#

GPO15/GPI15/INTH#

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/GHI#

GPO23/GPI23/PPSLP#

GPO12

GPO13

GPO14

GPO15

CPU FID0 Strapping

CPU FID1 Strapping

CPU FID2 Strapping

CPU FID3 Strapping

GPO20

GPO21

GPO22

GPO23

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

VIDSEL/SATA LED

GPO29/GPI29/

A A

VRDSLP

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

5

PIN NAME Function defineFunction define

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/AGPBZ#

GPI7/REQ5#

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

DDR Voltage

2.5V

2.6V

2.7V

2.8V

4

SET1 SET2

11

1

0

1

0

00

GPI0

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

Exteranl Pull up to 3VDUAL

PME#

Exteranl Pull up to 3VDUAL

Exteranl Pull down

Exteranl Pull up to 3VDUAL

THRM#

Exteranl Pull up to VCC3

3

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

2

PCI

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#B

INT#C

INT#D

INT#A

IDSEL

AD16

AD17

AD18

AD19

AD21

REQ#/GNT#

PREQ#0

PGNT#0

PREQ#1

PGNT#1

PREQ#2

PGNT#2

PCIREQ#3

PCIGNT#3

PCIREQ#4

PCIGNT#4

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

CLOCK

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

GPIO Spec.

MS-7021

Last Revision Date:

Friday, September 19, 2003

Sheet

337

1

Rev

100

of

5

4

3

2

1

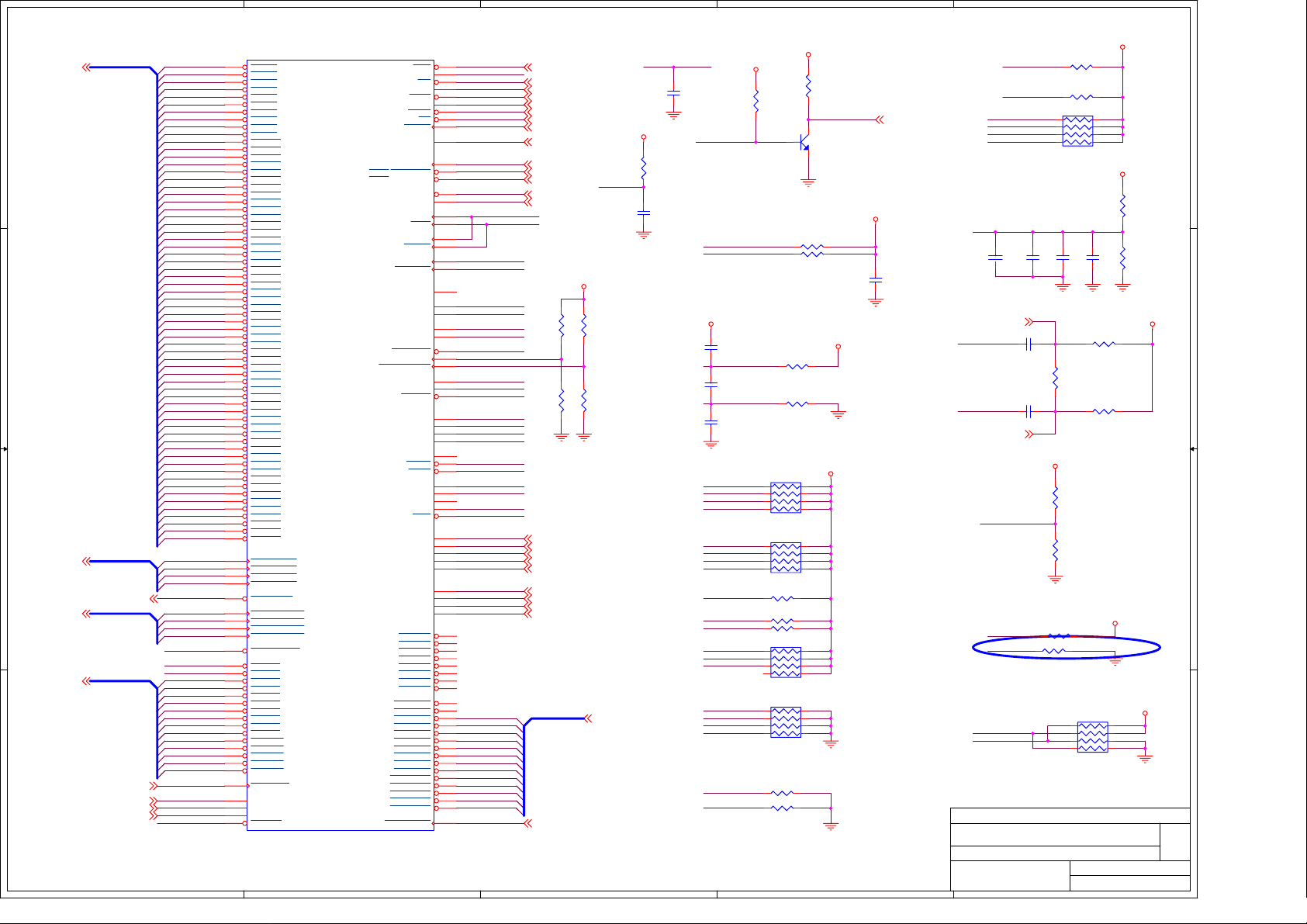

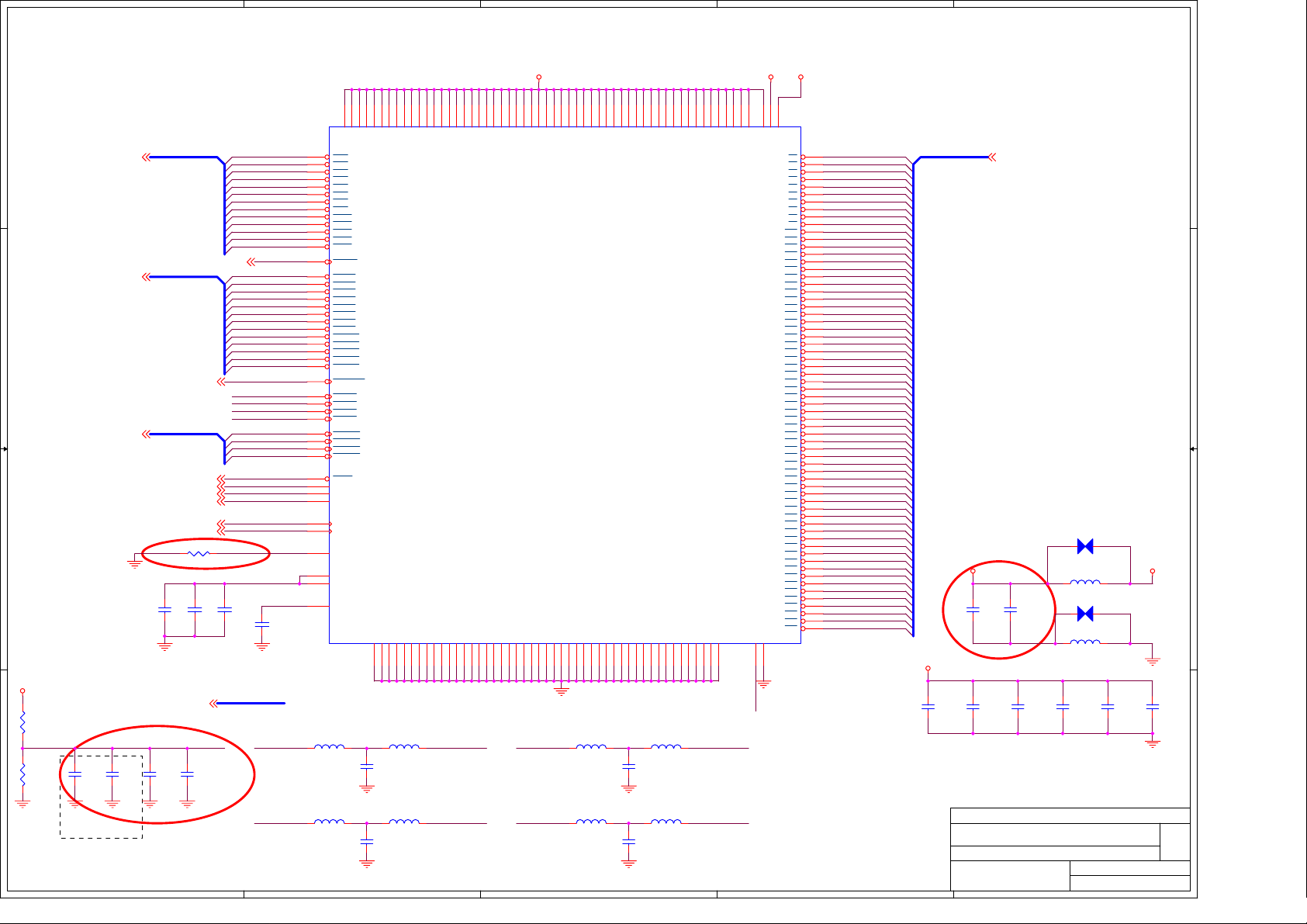

SOCKET 462 Part 1

SDATA#[0..63]7

D D

C C

DICLK#[0..3]7

B B

DOCLK#[0..3]7

AIN#[2..14]7

A A

SDATA#[0..63]

DICLK#[0..3]

DIVAL#7

DOCLK#[0..3]

AIN#[2..14]

AICLK#7

CFWDRST7

CONNECT7

PROCDRY7

SDATA#0

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

DICLK#0

DICLK#1

DICLK#2

DICLK#3

DIVAL#

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DOVAL#

5

AIN#0

AIN#1

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

CFWDRST

CONNECT

PROCDRY

FILVAL#

AA35

W37

W35

AA33

AE37

AC33

AC37

AA37

AC35

W33

AN33

AE35

AL31

AJ29

AL29

AG33

AJ37

AL35

AE33

AJ35

AG37

AL33

AN37

AL37

AG35

AN29

AN35

AN31

AJ33

AJ21

AL23

AN23

AJ31

Y35

U35

U33

S37

S33

Y37

S35

Q37

Q35

N37

J33

G33

G37

E37

G35

Q33

N33

L33

N35

L37

J37

A37

E35

E31

E29

A27

A25

E21

C23

C27

A23

A35

C35

C33

C31

A29

C29

E23

C25

E17

E13

E11

C15

A13

C21

A21

E19

C19

C17

A11

A17

A15

J35

E27

E15

C37

A33

C11

E9

C9

A9

SDATA0

SDATA1

SDATA2

SDATA3

SDATA4

SDATA5

SDATA6

SDATA7

SDATA8

SDATA9

SDATA10

SDATA11

SDATA12

SDATA13

SDATA14

SDATA15

SDATA16

SDATA17

SDATA18

SDATA19

SDATA20

SDATA21

SDATA22

SDATA23

SDATA24

SDATA25

SDATA26

SDATA27

SDATA28

SDATA29

SDATA30

SDATA31

SDATA32

SDATA33

SDATA34

SDATA35

SDATA36

SDATA37

SDATA38

SDATA39

SDATA40

SDATA41

SDATA42

SDATA43

SDATA44

SDATA45

SDATA46

SDATA47

SDATA48

SDATA49

SDATA50

SDATA51

SDATA52

SDATA53

SDATA54

SDATA55

SDATA56

SDATA57

SDATA58

SDATA59

SDATA60

SDATA61

SDATA62

SDATA63

SDATAINCLK0

SDATAINCLK1

SDATAINCLK2

SDATAINCLK3

SDATAINVAL

SDATAOUTCLK0

SDATAOUTCLK1

SDATAOUTCLK2

SDATAOUTCLK3

SDTATOUTVAL

SADDIN0

SADDIN1

SADDIN2

SADDIN3

SADDIN4

SADDIN5

SADDIN6

SADDIN7

SADDIN8

SADDIN9

SADDIN10

SADDIN11

SADDIN12

SADDIN13

SADDIN14

SADDINCLK

CLKFWDRST

CONNECT

PROCRDY

SFILLVAL

4

CPU1A

A20M

FERR

INIT

INTR

IGNNE

NMI

RESET

SMI

STPCLK

PWROK

PICCLK

PICD0/BYPASSCLK

PICD1/BYPASSCLK

COREFB-

COREFB+

CLKIN

CLKIN

RSTCLK

RSTCLK

K7CLKOUT

K7CLKOUT

ANALOG

SYSVREFMODE

VREF_SYS

PLLBYPASS

PLLBYPASSCLK

PLLBYPASSCLK

PLLMON1

PLLMON2

PLLTEST

SCANCLK1

SCANCLK2

SCANINTEVAL

SCANSHIFTEN

DBRDY

DBREQ

FLUSH

TCK

TDO

TMS

TRST

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

SCHECK0

SCHECK1

SCHECK2

SCHECK3

SCHECK4

SCHECK5

SCHECK6

SCHECK7

SADDOUT0

SADDOUT1

SADDOUT2

SADDOUT3

SADDOUT4

SADDOUT5

SADDOUT6

SADDOUT7

SADDOUT8

SADDOUT9

SADDOUT10

SADDOUT11

SADDOUT12

SADDOUT13

SADDOUT14

SADDOUTCLK

AE1

AG1

AJ3

AL1

AJ1

AN3

AG3

AN5

AC1

AE3

N1

N3

N5

AG13

AG11

AN17

AL17

AN19

AL19

AL21

AN21

AJ13

AA5

W5

AC5

ZN

AE5

ZP

AJ25

AN15

AL15

AN13

AL13

AC3

S1

S5

S3

Q5

AA1

AA3

AL3

Q1

U1

TDI

U5

Q3

U3

L1

L3

L5

L7

J7

W1

W3

Y1

Y3

U37

Y33

L35

E33

E25

A31

C13

A19

J1

J3

C7

A7

E5

A5

E7

C1

C5

C3

G1

E1

A3

G5

G3

E3

A20M#

FERR

CPUINIT#

INTR

IGNNE#

NMI

CPURST#

SMI#

STPCLK#

APICCLK_CPU

APICD0#

APICD1#

COREFB#

COREFB

CLKOUT

CLKOUT#

VREFMODE

VREF_SYS

ZN

ZP

PLLBP#

PLLMON1

PLLMON2

PLLTEST#

SCANCLK1

SCANCLK2

SINTVAL

SSHIFTEN

DBREQ#

FLUSH#

CPU_TCK

CPU_TDI

CPU_TMS

CPU_TRST#

VID0

VID1

VID2

VID3

VID4

FID0

FID1

FID2

FID3

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

N12-4620011-F02

CPUCLK_R

CPUCLK#_R

A20M# 16

CPUINIT# 16

INTR 16

IGNNE# 16

NMI 16

CPURST# 33

SMI# 16

STPCLK# 16

K7PWRGD 33

APICCLK_CPU 6

APICD0# 16

APICD1# 16

COREFB# 30

COREFB 30

VCORE

R89

100

R88

100

VID0 31

VID1 31

VID2 31

VID3 31

VID4 31

FID0 31

FID1 31

FID2 31

FID3 31

AOUT#[2..14]

AOCLK# 7

K7PWRGD

R93

100

R92

100

AOUT#[2..14] 7

3

VCORE

CPURST#

C28

X_100P

R48

4.7K

12

C660

68p

VCORE

VCORE

FERR

New Update

APICD0#

APICD1#

C34

X_225P/0805

COREFB

C35

X_106P/0805

COREFB#

C37

X_105P

CPUINIT#

CPURST#

IGNNE#

A20M#

STPCLK#

NMI

SMI#

INTR

FLUSH#

PLLMON1

PLLMON2

AIN#1

AIN#0

PLLBP#

SSHIFTEN

SCANCLK1

SINTVAL

SCANCLK2

DOVAL#

FILVAL#

R80

680

Pull to 2.5V

R64 330

R55 330

R74 10K

R81 10K

RN14

1 2

3 4

5 6

7 8

8P4R-680

RN15

1 2

3 4

5 6

7 8

8P4R-680

R67 680

R87 56

R86 56

RN28

1 2

3 4

5 6

7 8

8P4R-680

RN1

1 2

3 4

5 6

7 8

8P4R-270

R569 270

R570 270

VCC3

R78

510

FERR#

Q15

2N3904S

VCORE

VCORE

R49 510

DBREQ#

R54 510

PLLTEST#

FERR# 16

VCC2_5

C21

X_39P

CPUCLK_R

CPUCLK#_R

CPUCLK#6

CPU_TCK

CPU_TMS

CPU_TRST#

CPU_TDI

VREF_SYS

C120

4.7u-0805

CPUCLK6

VREFMODE

C59

680P

C61

680P

C12

104P

VCORE

1 2

3 4

5 6

7 8

VREFMODE=Low=No voltage scaling

ZN

R50 40.2RST

R53 40.2RST

ZP

match the transmission line

Push-pull compensation circuit

CLKOUT

CLKOUT#

* Trace lengths of CLKOUT

and -CLKOUT are between

2" and 3"

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

SOCKET 462 Part 1

MS-7021

RN2

8P4R-510

0.6 * VCORE

C41

473P

R95 60.4RST

R96

301RST

R98 60.4RST

close Socket 462

R45

for internal

X_1K

VREFSYS

R40

270

RN24

1 2

3 4

5 6

7 8

8P4R-100

Last Revision Date:

Friday, September 19, 2003

Sheet

1

VCORE

VCORE

R85

60.4RST

C40

R84

473P

60.4RST

VCORE

VCORE

New Update

VCORE

Rev

100

of

437

5

SOCKET 462 Part 2

4

3

2

1

Power supply from MS-5

D D

Used when

spec.

change

C69

102P

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

C82

39P

R101 10

C79

39P

VCCA_PLL1VCCA_PLL

C65

39P

Place al filters close to the PGA.

Max 150mA,

Design for

100mA

C C

H12

H16

H20

H24M8P30R8T30V8X30Z8AB30

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_SRAM1

VCC_SRAM2

VCC_SRAM3

VCC_SRAM4

VCC_SRAM5

VCC_SRAM6

VCC_SRAM7

VCC_SRAM8

VCC_SRAM9

VCC_SRAM11

VCC_SRAM13

VCC_SRAM14

VCC_SRAM16

VCC_SRAM17

VCC_SRAM19

VCC_SRAM20

VCC_SRAM21

VCC_SRAM22

VCC_SRAM23

VCC_SRAM24

VCC_SRAM25

VCC_SRAM26

VCC_SRAM27

VCC_SRAM28

VCC_SRAM29

VCC_SRAM30

VCC_SRAM31

KEY4

KEY6

KEY8

KEY10

KEY12

KEY14

KEY16

KEY18

VCC_CORE6

AD30

AD8

AF10

AF28

AF30

AF32

AF6

AF8

FSB1

FSB131

166/200 detect

B B

AH30

AH8

AK8

AM8

AN7

G25

G17

AG7

AG15

AG29

AJ9

AL9

F30

F8

H10

H28

H30

H32

H6

H8

K30

K8

AJ7

AL7

G9

N7

Y7

VCC_CORE7

VCC_CORE8

VCC_CORE9

VCC_CORE10

AF14

AF18

VCC_CORE11

VCC_CORE12

VCC_CORE13

VCC_CORE14

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

AF22

AF26

AM34

AK36

AK34

AK30

AK26

AK22

AK18

AK14

AK10

AL5

AH26

AM30

AH22

AH18

AH14

AH10

AH4

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

AH2

AF36

AF34

AD6

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

AM26

AD4

AD2

AB36

AB34

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

AB32Z6Z4Z2X36

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCORE

X34

AM22

X32V6V4V2T36

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

T34

T32R6R4R2AM18

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

P36

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

VCC_CORE61

P34

P32M4M6M2K36

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

K34

K32H4H2

VCC_CORE66

VCC_CORE67

VCC_CORE68

VCC_CORE69

VCC_CORE70

AM14

F36

F34

F32

VCC_CORE71

VCC_CORE72

VCC_CORE73

VCC_CORE74

VCC_CORE75

F28

F24

F20

F16

VCC_CORE76

VCC_CORE77

VCC_CORE78

VCC_CORE79

F12

D32

D28

AM10

VCC_CORE80

VCC_CORE81

VCC_CORE82

VCC_CORE83

D24

D20

D16

D12D8D4D2B36

VCC_CORE84

VCC_CORE85

VCC_CORE86

VCC_CORE87

B32

VCC_CORE88

VCC_CORE89

VCC_CORE90

VCC_CORE91

VCC_CORE92

AM2

B28

B24

B20

VCC_CORE93

VCC_CORE94

VCC_CORE95

VCC_CORE96

B16

B12B8B4

VCC_CORE97

VCC_CORE98

VCC_CORE99

VCC_CORE100

VCCA_PLL

AJ5

AC7

VCC_Z

NC1

VCC_CORE101

NC2

NC3

NC6

NC7

NC8

NC9

NC10

NC11

NC12

NC13

NC15

NC16

NC17

NC18

NC19

NC20

NC21

NC22

NC23

NC24

NC25

NC27

NC28

NC29

NC30

NC31

NC32

NC33

NC34

NC35

NC36

NC37

NC42

NC43

NC44

NC45

BP0_CUT

BP1_CUT

BP2_CUT

BP3_CUT

0~32 mA,

2.25~2.75V

CPU1B

AJ23

N12-4620011-F02

VCC_A

AA31

AC31

AE31

AG23

AG25

AG31

AG5

AJ11

AJ15

AJ17

AJ19

AJ27

AL11

AN11

AN9

G11

G13

G27

G29

G31

J31

J5

L31

N31

Q31

S31

S7

U31

U7

W31

W7

Y31

Y5

AG19

G21

AG21

G19

AN27

AL27

AN25

AL25

FSB0

FSB0 31

100/133 detect

BP4 31

THERMDP 32

THERMDN 32

For AMD CPU Thermal

protection

BP0 31

BP1 31

BP2 31

BP3 31

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS_Z

H14

H18

H22

H26

A A

M30P8R30T8V30X8Z30

5

AB8

AF12

AF16

AF20

AF24

AM36

AK32

AK28

AK24

AK20

AK16

AK12

AK4

AK2

AH36

AM32

AH34

AH32

AH28

4

AH24

AH20

AH16

AH12

AF4

AF2

AD36

AD34

AD32

AB6

AB4

AB2

Z36

Z34

Z32X6AM28X4X2

V36

V34

V32T6T4T2R36

R34

AM24

R32P6P4P2M36

M34

M32K6K4K2AM20

H36

H34

F26

F22

F18

F14

F10F6F4F2AM16

D36

D34

D30

D26

D22

D18

D14

D10D6B34

AM12

B30

B26

B22

B18

B14

B10B6B2

AM4

AK6

AM6

AE7

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

3

2

http://www.msi.com.tw

SOCKET 462 Part 2

MS-7021

Last Revision Date:

Sheet

1

Friday, September 19, 2003

537

Rev

100

of

5

4

3

2

1

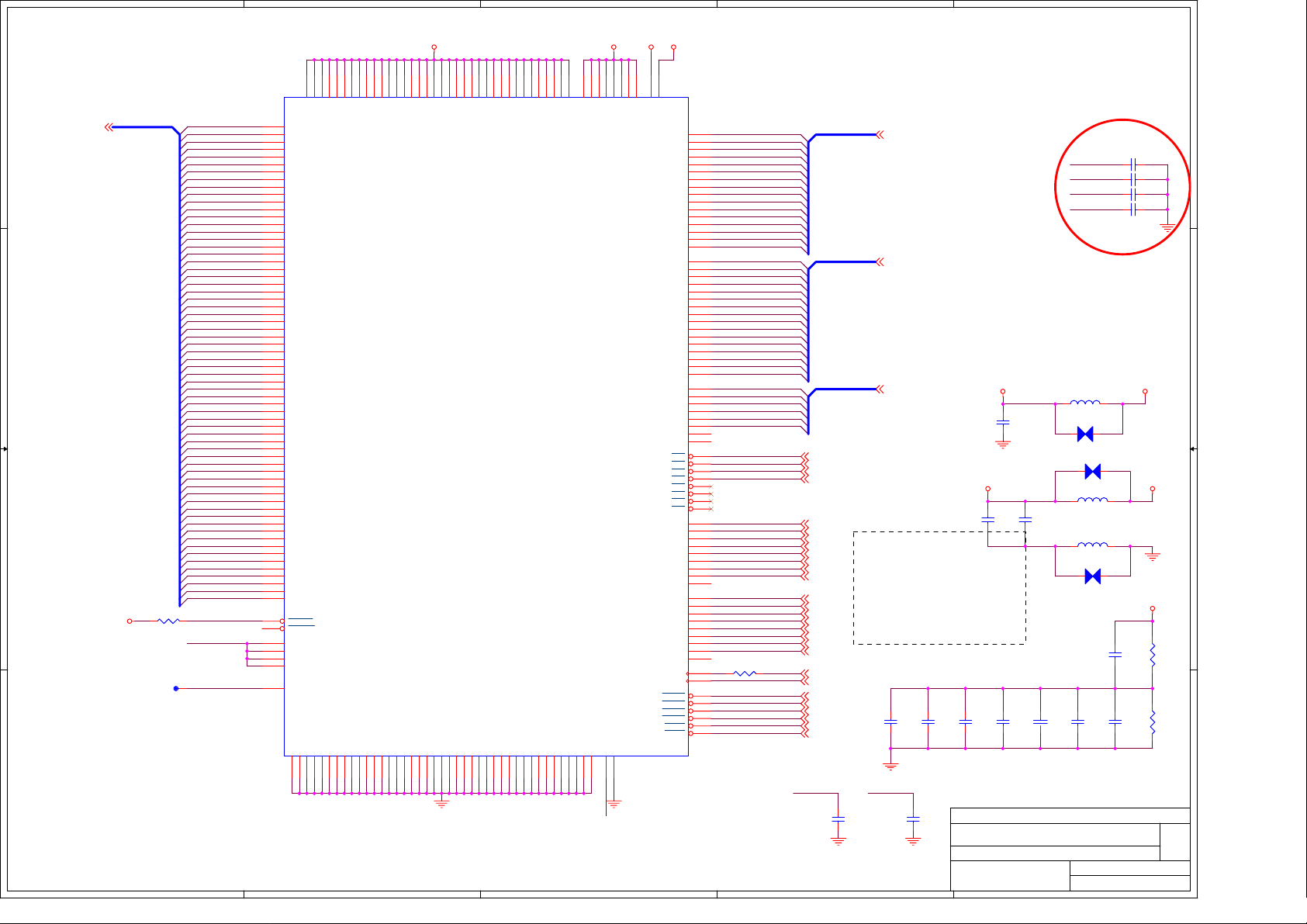

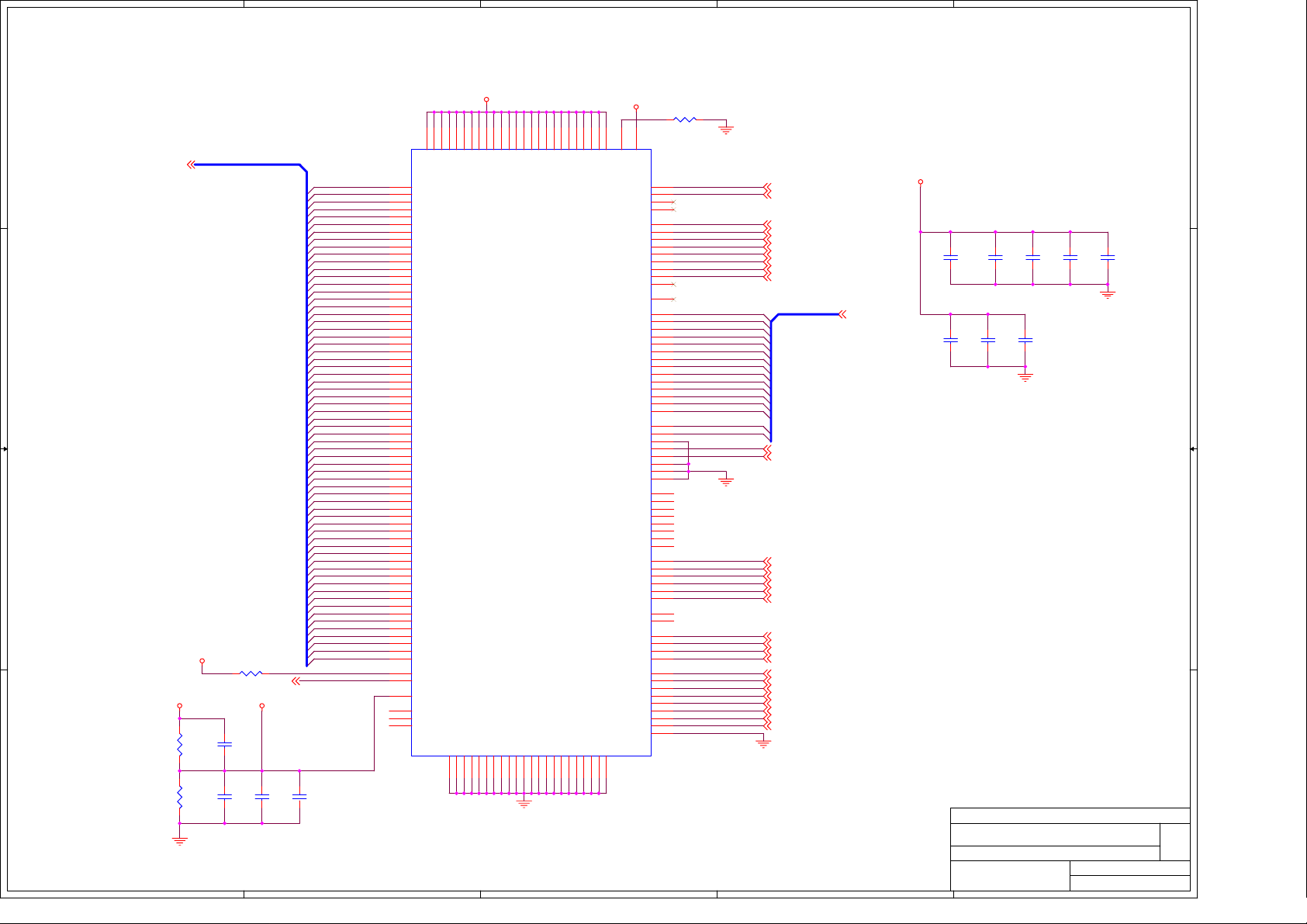

filtering from 10K~1M

VCC3

VCC2_5

D D

VCC3

VCORE

C C

VCC2_5

B B

CP24 X_COPPER

C661

C10U10Y0805

CP25

C669

C10U10Y0805

R721 X_10KR

R724 10KR

R726 220R

CP26

X_COPPER

C687

C10U10Y0805

VCC3V

VCC2.5A

X_COPPER

VTTGD#

Q100

X_N-MMBT3904_SOT23

R725 4.7KR

Q101

N-MMBT3904_SOT23

SMBCLK111,12,17,19,31,33

SMBDATA111,12,17,19,31,33

VCC2.5B

DCLKO8 DCLKI 8

1U25Y

1U25Y

U34

51

CPU_VDD3.3

54

CPU_GND3.3

50

CPU_VDD2.5

C667

47

CPU_GND2.5

C672

16

C674

13

22

C676

1U25Y

19

55

C679

1U25Y

2

23

C684

1U25Y

24

27

28

34

C686

104P

33

40

C689

1U25Y

39

45 46

SEL_CK408/K7/AGP1

PCI_VDD

SEL_SDR/DDR#/PCI1

PCI_GND

48_VDD

48_GND

REF_VDD

REF_GND

CORE_VDD

CORE_GND

SCLK

SDATA

DDR/SDR_VDD

DDR/SDR_GND

DDR/SDR_VDD

DDR/SDR_GND

BUF_IN FB_OUT

ICS950910_SSOP56

CPUCLK

CPUCLK#

CPUCLKCS

CPUCLKCS#

Mode/AGP03V66_VDD

PCISTOP#/AGP23V66_GND

FS1/PCI_F

MULTSEL/PCI2

PCI3

PCI4

PCI5

CLKSTOP#/PCI6

FS3/48MHz

FS2/24_48MHz

FS0/REF0

VTT_GD#/REF1

IREF

PD#/RESET#

DDR0/SDR0

DDR#0/SDR1

DDR1/SDR2

DDR#1/SDR3

DDR2/SDR4

DDR#2/SDR5

DDR3/SDR6

DDR#3/SDR7

DDR4/SDR8

DDR#4/SDR9

DDR5/SDR10

DDR#5/SDR11

53

52

48

49

MODE

65

SEL_CK408

7

RN155

8P4R-33R

89

FS1

10

SEL_SDR/DDR

11

MULT

12

14

15

17

18

FS3

20

FS2

21

RN157

8P4R-10R

1

FS0

56

VTTGD#

3

X1

4

X2

25

26

44

43

42

41

38

37

36

35

32

31

30

29

8P4R-33R

RN154

R60 33R

R61 33R

R712 33R

R713 33R

R716 33R1U25Y

R717 10R

R718 10R

R719 x_33R

R720 0R

R722 33R

R723 33R

R728 475R1%

R729 33R

DCLK2_R

1 2

DCLK#2_R

3 4

DCLK1_R

5 6

DCLK#1_R

7 8

RN159 8P4R-10R

DCLK0_R

1 2

DCLK#0_R

3 4

DCLK3_R

5 6

DCLK#3_R

7 8

RN1608P4R-10R

DCLK4_R

1 2

DCLK#4_R

3 4

DCLK5_R

5 6

DCLK#5_R

7 8

RN1618P4R-10R

R732 33R

1 2

3 4

5 6

7 8

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

X1 14.318MHZ32P_D

C33P50NC681

C33P50NC685

FP_RST# 31,33,35

CPUCLK 4

CPUCLK# 4

HCLK# 7

HCLK 7

AGPCLK_NB 9

VCLK 16

AGPCLK 15

SIOPCLK 27

SB_PCLK 16

PCICLK1 19

PCICLK2 19

PCICLK3 20

PCICLK4 20

PCICLK5_1 21

PCICLK5 21

TRU# 27

USBCLK_SB 18

SIO48M 27

APICCLK 16

SB_OSC14 17

APICCLK_CPU 4

MS-3_14M 31

Share CLK Trace same length

DCLK2 11

DCLK#2 11

DCLK1 11

DCLK#1 11

DCLK0 11

DCLK#0 11

DCLK3 12

DCLK#3 12

DCLK4 12

DCLK#4 12

DCLK5 12

DCLK#5 12

Shut Source Termination Resistors Pull-Down Capacitors

CPUCLK

CPUCLK#

HCLK

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

CLOCK STRAPPING RESISTORS

FS3

FS2

R710 10KR

FS1

FS0

R714 10KR

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

MODE VCC3V

SEL_CK408

SEL_SDR/DDR

MULT

2210

910:Add R719,R700 romve R720,R718,R701

916:remove R719,R700 add R720,R718,R701

R707 10KR

R708 10KR

R709 X_10KR

R711 x_1.5KR

R715 x_1.5KR

VCC3V

VCC3V

166_200_DET_SB 17,31

VCC3V

100_133_DET_SB 17,31

FSB (MHz)FS3 FS2 FS1 FS0

100 MHz

133 MHz

200 MHz

166 MHz

R70 x_10KR

R82 10KR

R83 x_10KR

R102 x_10KR

R727 X_10KR

5.00mA 1.0V

VCC3V

IohIrefRrMULT

4*Iref

Voh

2.32mA 0.7V6*Iref4751

K7 MODE

HCLK#

AGPCLK_NB

AGPCLK

VCLK

SIOPCLK

7

SB_PCLK

5

3

PCICLK1

1

PCICLK2

7

PCICLK3

5

PCICLK4

3

PCICLK5

USBCLK_SB

SIO48M

1

7

5

3

1

R56 x_150RST

CN23 8P4C-10P50N

1

3

5

7

CN24 8P4C-10P50N

1

3

5

7

CN25 8P4C-10P50N

1

3

5

7

APICCLK

SB_OSC14

APICCLK_CPU

MS-3_14M

APICCLK_CPU

SMBCLK1

SMBDATA1

DCLK2

DCLK#2

DCLK1

DCLK#1

DCLK0

DCLK#0

DCLK3

DCLK#3

DCLK4

DCLK#4

DCLK5

DCLK#5

DCLKI

used only for EMI issue

Trace less 0.2"

C10P50NC663

C10P50NC664

C10P50NC665

C10P50NC666

X_C10P50NC668

X_C10P50NC671

x_C10P50NC673

8

CN21

6

X_8P4C-10P50N

4

2

8

CN22

6

X_8P4C-10P50N

4

2

8

CN2

6

X_8P4C-10P50N

4

2

X_C10P50NC675

X_C10P50NC677

X_C10P50NC682

X_C10P50NC683

2

4

6

8

2

4

6

8

2

4

6

8

X_C10P50NC690

A A

MSI

Title

Size Document Number Rev

5

4

3

2

Date: Sheet

<OrgName>

Clock Generator

MS-7021

100

637Friday, September 19, 2003

1

of

5

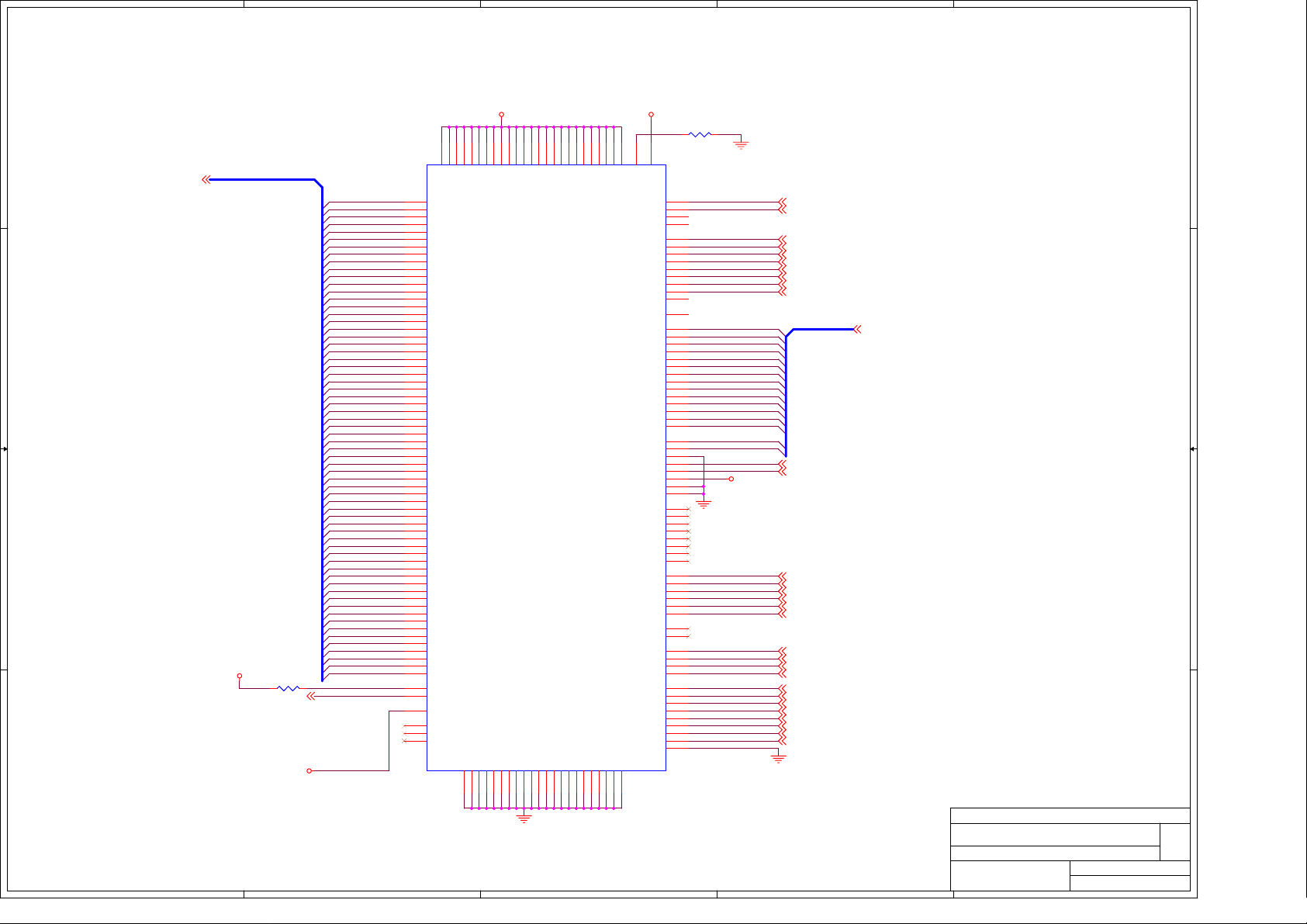

D D

AICLK#4

C14

104P

DICLK#[0..3]

AIN#2

AIN#3

AIN#4

AIN#5

AIN#6

AIN#7

AIN#8

AIN#9

AIN#10

AIN#11

AIN#12

AIN#13

AIN#14

AOUT#2

AOUT#3

AOUT#4

AOUT#5

AOUT#6

AOUT#7

AOUT#8

AOUT#9

AOUT#10

AOUT#11

AOUT#12

AOUT#13

AOUT#14

AOCLK#

DICLK_N#0

DICLK_N#1

DICLK_N#2

DICLK_N#3

DOCLK#0

DOCLK#1

DOCLK#2

DOCLK#3

DIVAL#

CFWDRST

CONNECT

PROCDRY

HCLK

HCLK#

E26

A25

E24

A26

C25

D25

C24

C23

D23

D26

E23

A24

B23

AICLK#

B25

W34

W33

Y32

AA32

W32

AB32

Y34

AA34

AB34

AB31

AA31

W31

AB33

AA33

B28

F33

L32

T34

C28

F32

K32

T33

A23

A22

E22

C22

K29

L29

G30

AA30

E25

VID#

AA29

C494

X_104P/B

DICLK#0 DICLK_N#0

10nH

AIN#[14..2]

10U/1206

C493

104P/B

C19

AOUT#[14..2]

AOCLK#4

DOCLK#[0..3]

DIVAL#4

CFWDRST4

CONNECT4

PROCDRY4

HCLK#6

R130 60.4RST

S2K_VREF

DICLK#[0..3]4

S2K_VREF

C506

x_473P/B

HCLK6

C13

105P

C500

X_103P/0805/B

AOUT#[14..2]4

C C

DOCLK#[0..3]4

B B

VCORE

R158

60.4RST

R160

60.4RST

A A

C495

104P/B

AIN2

AIN3

AIN4

AIN5

AIN6

AIN7

AIN8

AIN9

AIN10

AIN11

AIN12

AIN13

AIN14

AINCLK

AOUT2

AOUT3

AOUT4

AOUT5

AOUT6

AOUT7

AOUT8

AOUT9

AOUT10

AOUT11

AOUT12

AOUT13

AOUT14

AOUTCLK

DICLK0

DICLK1

DICLK2

DICLK3

DOCLK0

DOCLK1

DOCLK2

DOCLK3

DIVAL

CFWDRST

CONNECT

PROCRDY

HCLK+

HCLK-

S2KCOMP

S2KVREF0

S2KVREF1

VID

L21

M18

VTT

4

A20

A21

B20

B21

C20

C21

D20

D21

E20

E21

F20

F21

L20

L21

L22

L23

M20

M21

M22

M23

M24

A33

A34

B33

B34

L18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VTT

VSS

VSS

VSS

VSS

VSS

VSS

D30

E33

E31

F27

F26

D31

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

A32

B30

B24

B27

C135

5P

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D24

D27

B31

B32

C31

C33

C34

L23

10nH

N23

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H33

H31

H29

L33

L31

J29

M30

DICLK#2 DICLK_N#2

3

AVDD1 VCC2_5VCORE

G29

K30

P23

P24

R23

R24

T23

T24

U23

U24

V23

V24

W23

W24

AD29

AD30

AD31

AD32

AD33

AD34

AE29

AE30

VTT

VSS

W30

10nH

AE31

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VSS

VSS

VSS

VSS

VSS

D22

AC34

AC33

AC32

AC31

AC30

N24

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VSS

VTT

VSS

VSS

VSS

VSS

VSS

VSS

U33

U31

B22

Y33

Y31

Y30

L20

C129

5P

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N30

P33

P31

P30

P29

R30

R29

T30

T29

L19

10nH

AE32

VTT

VSS

AC29

AE33

VTT

AE34

VTT

H30

L19

M19

U9A

VTT

VTT

VTS2K

VDS2K

AVDD1

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

VSS2K

AGND1

VT8377

F30

L30

AGND1

2

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

E29

A29

B29

A30

C29

C30

A31

C27

E27

C26

E28

A28

D28

B26

D29

D32

D34

E30

H32

J34

F31

G31

H34

C32

D33

G34

E34

E32

F34

G32

G33

J30

K31

M31

M32

N31

N34

M34

N33

J32

J31

J33

K34

L34

K33

N32

M33

R31

V32

V33

T32

V34

U34

V31

V30

P34

P32

R34

R33

R32

U30

T31

U32

SDATA#1

SDATA#2

SDATA#3

SDATA#4

SDATA#5

SDATA#6

SDATA#7

SDATA#8

SDATA#9

SDATA#10

SDATA#11

SDATA#12

SDATA#13

SDATA#14

SDATA#15

SDATA#16

SDATA#17

SDATA#18

SDATA#19

SDATA#20

SDATA#21

SDATA#22

SDATA#23

SDATA#24

SDATA#25

SDATA#26

SDATA#27

SDATA#28

SDATA#29

SDATA#30

SDATA#31

SDATA#32

SDATA#33

SDATA#34

SDATA#35

SDATA#36

SDATA#37

SDATA#38

SDATA#39

SDATA#40

SDATA#41

SDATA#42

SDATA#43

SDATA#44

SDATA#45

SDATA#46

SDATA#47

SDATA#48

SDATA#49

SDATA#50

SDATA#51

SDATA#52

SDATA#53

SDATA#54

SDATA#55

SDATA#56

SDATA#57

SDATA#58

SDATA#59

SDATA#60

SDATA#61

SDATA#62

SDATA#63

SDATA#0

A27

SDATA#[63..0]

change to top side

C490

103P/B

VCORE

C497

C484

x_104P/B

x_104P/B

SDATA#[63..0] 4AIN#[14..2]4

C474

105P/B

AGND1

C496

x_104P/B

1

CP17

X_COPPER

L60

X_L02-8008044-J07

CP16

X_COPPER

L59

X_L02-8008044-J07

C504

C492

x_104P/B

x_104P/B

VCC2_5AVDD1

C508

x_104P/B

SOLDER

SIDE

change to top side

5

10nH

L18

L22

DICLK_N#1DICLK#1

10nH

C134

5P

4

L15

10nH

3

C110

5P

L16

DICLK_N#3DICLK#3

10nH

2

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

VT8377 CPU

MS-7021

Last Revision Date:

Friday, September 19, 2003

Sheet

737

1

Rev

100

of

5

4

3

2

1

VDDR VCC2_5

AG1

AG2

AG3

AG4

AG5

AG6

AH1

AH2

AH3

AH4

AH5

AH6

AJ1

AJ2

AJ3

AJ4

AJ5

AJ6

AF29

AF30

AF31

AF32

AF33

AF34

AG29

AG30

AG31

AG32

AG33

AG34

AH29

AH30

AH31

AH32

AH33

AH34

AJ10

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VSS

AK16

VSS

VSS

AK19

AN2

VSS

AN5

VSS

AN8

VSS

VCC3

VSS

AN11

AN14

D D

C C

B B

A A

MD[63..0]14

VDDR

MD[63..0]

5

R162 4.7K

GCKE

MD0

AK31

AM33

AN32

AP33

AK32

AL34

AN34

AP34

AP32

AM31

AM29

AM28

AN31

AP31

AN29

AP29

AN28

AP27

AM26

AP25

AP28

AM27

AM25

AN25

AM24

AN23

AP22

AM21

AP24

AP23

AN22

AP21

AM14

AN13

AP12

AM11

AP14

AP13

AN12

AP11

AN10

AM9

AP8

AM8

AP10

AM10

AN7

AP7

AM7

AM6

AN4

AP3

AP6

AN6

AP4

AM4

AP1

AN3

AL1

AK1

AP2

AN1

AM2

AK2

AK11

AK27

AJ28

AJ19

AJ12

AK29

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

QDRRD

QDRWR

MVREF0

MVREF1

MVREF2

AJ7

MVREF3

GCKE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AL18

AL19

AL21

AL24

AL27

VSS

AL30

AL33

VSS

AK18

VSS

AJ8

AJ9

AJ15

AJ16

AJ20

AJ26

AJ27

AJ29

AJ30

AJ31

AJ32

AL2

AL5

AL8

AL11

AL14

AL16

AJ23

4

AL17

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

QDRRD

MVREF_NB

GCKE MVREF_NB

VCC3

VSS

AN17

VCC3

VSS

AN18

VCC3

VSS

AN21

VCC3

VSS

AN24

VCC3

VSS

AN27

VSS

VDD

VSS

AN30

AJ11

VDD

VSS

AN33

AJ13

VDD

3

AJ14

AJ21

VDD

AGND2

AJ33

AJ18

AGND2

AVDD2 AVDD3

AJ22

AJ24

AJ25

VDD

VDD

VDD

AGND3

AJ34

AJ17

VDD

AVDD2

MPD0/CKE0

MPD1/CKE1

MPD2/CKE2

MPD3/CKE3

MPD4/CKE4

MPD5/CKE5

MPD6/CKE6

MPD7/CKE7

AVDD3

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

MAB15

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

DQM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

DCLKO

DCLKI

SRASA

SRASB

SCASA

SCASB

SWEA

SWEB

VT8377

CS0

CS1

CS2

CS3

CS4

CS5

CS6

CS7

U9B

AM15

AM16

AM18

AM20

AK20

AL23

AK22

AL25

AK24

AK26

AK15

AL12

AL13

AL28

AK30

AL31

AL15

AK17

AP17

AM19

AL20

AL22

AK21

AK25

AK23

AL26

AK14

AK12

AK13

AK28

AL29

AL32

AN19

AP19

AN15

AP15

AP20

AN20

AP16

AN16

AL7

AK5

AK6

AM5

AL4

AK4

AL3

AK3

AM32

AP30

AP26

AM22

AM12

AN9

AL6

AM3

AM17

AM34

AM30

AN26

AM23

AM13

AP9

AP5

AM1

AP18

AK33

AK34

AL9

AL10

AK7

AK9

AK10

AK8

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

MAA14

MAA15

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB12

MAB13

MAB14

MAB15

MCKE0

MCKE1

MCKE2

MCKE3

MCKE4

MCKE5

MCS#0

MCS#1

MCS#2

MCS#3

MDQM#0

MDQM#1

MDQM#2

MDQM#3

MDQM#4

MDQM#5

MDQM#6

MDQM#7

MDQS#0

MDQS#1

MDQS#2

MDQS#3

MDQS#4

MDQS#5

MDQS#6

MDQS#7

R134 10

MSRASA#

MSRASB#

MSCASA#

MSCASB#

MSWEA#

MSWEB#

DCLKO

DCLKI

MAA[15..0]

MAB[15..0]

MCKE[5..0]

MCS#0 11,13

MCS#1 11,13

MCS#2 12,13

MCS#3 12,13

MDQM#0 14

MDQM#1 14

MDQM#2 14

MDQM#3 14

MDQM#4 14

MDQM#5 14

MDQM#6 14

MDQM#7 14

MDQS#0 11,12,13,14

MDQS#1 11,12,13,14

MDQS#2 11,12,13,14

MDQS#3 11,12,13,14

MDQS#4 11,12,13,14

MDQS#5 11,12,13,14

MDQS#6 11,12,13,14

MDQS#7 11,12,13,14

DCLKO 6

DCLKI 6

MSRASA# 11,13

MSRASB# 12,13

MSCASA# 11,13

MSCASB# 12,13

MSWEA# 11,13

MSWEB# 12,13

DCLKIDCLKO

C142

X_5P

Place as close

as to VT8366

2

MAA[15..0] 11,13

MAB[15..0] 12,13

MCKE[5..0] 11,12

C522

C485

105P/B

104P/B

C487

X_20P

MCS#0

MCS#1

MCS#2

MCS#3

Delay CS# timing

placement botton

side

For VIA KT400

AVDD3

C489

105P/B

AVDD2

C486

103P/B

Place resistors as close as to

NB;Length is 2.5"~3".

Solder side

C509

C526

105P/B

102P/B

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

VT8377 Memory

C481

105P/B

AGND2

C118

4.7u-0805

MS-7021

L24

X_L02-8008044-J07

CP5

X_COPPER

CP18

X_COPPER

L61

X_L02-8008044-J07

L62

X_L02-8008044-J07

CP19

X_COPPER

C128

x_104P

Last Revision Date:

Sheet

1

C81 X_5P

C124 X_5P

C143 X_5P

C144 X_5P

VCC2_5

VCC2_5

VDDR

R129

C136

X_105P

1KST

R126

C132

105P

1KST

Rev

100

Friday, September 19, 2003

of

837

5

4

3

2

1

VSUS2_5

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

SB_STBF

SB_STBS

GFRAME

GDEVSEL

AGP8XDET

AGPVREF0

AGPVREF1

AGPCOMP

VSS

VSS

AF3

AF4

AF5

GD0

GD1

GD2

GD3

GD4

GD5

GD6

GD7

GD8

GD9

GD10

GD11

GD12

GD13

GD14

GD15

GD16

GD17

GD18

GD19

GD20

GD21

GD22

GD23

GD24

GD25

GD26

GD27

GD28

GD29

GD30

GD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

C/BE0

C/BE1

C/BE2

C/BE3

DBIH

DBIL

GIRDY

GTRDY

GSTOP

GPAR

PIPE

RBF

WBF

GREQ

GGNT

GSERR

ST0

ST1

ST2

GCLK

VSS

VSS

VT8377

AF6

U9C

C540

X_103P/B

M1

L1

K2

K1

K3

J1

J2

J3

F1

G3

F2

F3

E1

D1

D2

D3

C5

D6

A4

B5

A5

E7

B6

A6

B8

A8

D8

C8

A9

C9

B9

A10

B14

A14

A13

C14

A11

C11

C10

B11

H1

B1

A3

A7

G2

G1

C6

C7

B12

A12

E8

E9

E3

F4

G4

E10

H3

L3

D9

D11

E11

E14

D14

J4

E12

C13

D12

C12

F10

J5

K5

M2

GAD0

GAD1

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

GC/BE#0

GC/BE#1

GC/BE#2

GC/BE#3

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

SB_STBF

SB_STBS

DBIH

DBIL

GFRAME

GIRDY

GTRDY

GDEVSEL

GSTOP

GPAR

PIPE

RBF

WBF

GREQ

GGNT

GSERR

AGP8XDET#

ST0

ST1

ST2

VREF_GC

AGPCOMP

AGPCLK_NB

GAD0 15

GAD1 15

GAD2 15

GAD3 15

GAD4 15

GAD5 15

GAD6 15

GAD7 15

GAD8 15

GAD9 15

GAD10 15

GAD11 15

GAD12 15

GAD13 15

GAD14 15

GAD15 15

GAD16 15

GAD17 15

GAD18 15

GAD19 15

GAD20 15

GAD21 15

GAD22 15

GAD23 15

GAD24 15

GAD25 15

GAD26 15

GAD27 15

GAD28 15

GAD29 15

GAD30 15

GAD31 15

SBA0 15

SBA1 15

SBA2 15

SBA3 15

SBA4 15

SBA5 15

SBA6 15

SBA7 15

GC/BE#0 15

GC/BE#1 15

GC/BE#2 15

GC/BE#3 15

AD_STBF0 15

AD_STBS0 15

AD_STBF1 15

AD_STBS1 15

SB_STBF 15

SB_STBS 15

DBIH 15

DBIL 15

GFRAME 15

GIRDY 15

GTRDY 15

GDEVSEL 15

GSTOP 15

GPAR 15

PIPE 15

RBF 15

WBF 15

GREQ 15

GGNT 15

GSERR 15

AGP8XDET# 15

ST0 15

ST1 15

ST2 15

VREF_GC 15

R179 60.4RST

AGPCLK_NB 6

VDDQ

VREF_GC

C215

4.7u-0805

close to NB pin

VREF_GC

C109

C32

104P

4.7u-0805

C531

x_104P/B

C204

104P

C523

x_105P/B

C205

105P

VDDQ

A1A2B2B3C2C3C4D4D5E5E6F5F6F7F8N4N5N6P1P2P3P4P5P6R1R2R3R4R5

D D

C C

VLAD016

VLAD116

VLAD216

VLAD316

VLAD416

VLAD516

VLAD616

VLAD716

VBE0#16

VPAR16

R177 360RST

UPCMD16

DNCMD16

DNSTB16

DNSTB#16

UPSTB16

UPSTB#16

PWROK_NB#17,18

PCIRST2#27,31,33

NMI_NB16

VCC2_5

R128 4.7K

SUSST#17,18

VLAD0

VLAD1

VLAD2 GAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE0#

VPAR

VLREF_NB

VCOMPP_NB

UPCMD

DNCMD

DNSTB

DNSTB#

UPSTB

UPSTB#

PWROK_NB#

PCIRST2#

NMI_NB

TESTIN#

AB30

AB29

AA3

AA1

AB2

AB1

AB3

AB4

AA5

AB5

V3

VD0

V1

VD1

VD2

VD3

U1

VD4

U3

VD5

VD6

VD7

W2

VBE

U2

VPAR

W4

LVREF

Y5

LCOMPP

UPCMD

Y3

DNCMD

W1

DNSTB

W3

DNSTB

Y1

UPSTB

Y2

UPSTB

PWROK

RESET

NMI

TESTIN

SUS_ST

J6

VCCQQ

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

N1N2N3

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

R6

VCC1

VCC1

Y4

VSUS25

VCC2_5

AA6

VDD

Y6

VDD

W6

AD6

AD5

AD4

AD3

AD2

AD1

AC6

AC5

AC4

AC3

AC2

AC1

VDD

V6

VDD

M6

VDD

L6

VDD

H6

VDD

G6

VDD

F14

VDD

F13

VDD

F12

VDD

F11

VDD

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AE3

AE4

AE5

AE6

VSS

AF1

AF2

VSSQQ

K6

T1

VSS

B4B7B10

B13C1D7

VSS

VSS

VSS

D10

D13E2E4

E13F9G5H2H4H5K4L2L5M3T2T3T4T5T6U4U5U6V2V4V5W5AA2

L4

M4

M5

AA4

AB6

AE1

AE2

VCC2_5

R185

X_ 47

B B

VCC2_5

R198

3KST

VPAR

C191

104P

VCC2_5

VLREF_NB

R197

1KST

A A

VLREF_NB is 0.65V

C190

104P

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

VT8377 AGP

MS-7021

Last Revision Date:

Friday, September 19, 2003

Sheet

937

1

Rev

100

of

5

4

3

2

1

VCC2_5

Y29

VDD

W29

VDD

V29

VDD

VDDQ

VDDR

M29

M13

M14

M16

M15

M12

M11

AD23

AD22

AD21

AD20

AD19

AD18

AD17

AD16

AD15

AD14

AD13

AD12

AC24

AC23

AC22

AC21

AC20

AC19

AC18

AC17

AC16

AC15

AC14

AC13

AC12

AC11

AB24

AB23

AB12

AB11

AA24

AA23

AA12

AA11

U29

VDD

N29

F29

F28

F25

F24

F23

F22

F16

F15

E16

E15

D16

D15

C16

C15

B16

B15

A16

A15

A17

B17

C17

D17

E17

F17

L13

L14

L16

L15

T12

T11

R12

R11

P12

P11

N12

N11

L12

Y23

Y24

Y12

Y11

VDD: NB Core Power

VDD

X50

VDD

VCC1: AGP Power

VDD

X56

VDD

VCC2: VLink Power

VDD

X20

VDD

VCC3: DDR Power

VDD

X68

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC1

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

D D

C C

B B

A A

U9D

VCC2

VCC2

VCC2

VCC2

VCC2

VCC2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VT8377

U11

U12

V11

V12

W11

W12

B19

B18

L17

M17

AA21

AA20

AA19

AA18

AA17

AA16

AA15

AA14

Y21

Y20

Y19

Y18

Y17

Y16

Y15

Y14

W21

W20

W19

W18

W17

W16

W15

W14

V21

V20

V19

V18

V17

V16

V15

V14

U21

U20

U19

U18

U17

U16

U15

U14

T21

T20

T19

T18

T17

T16

T15

T14

R21

R20

R19

R18

R17

R16

R15

R14

P21

P20

P19

P18

P17

P16

P15

P14

F19

F18

E19

E18

D19

D18

C19

C18

A19

A18

VCC2_5

VDDQ

C514

C518

104P/B

104P

C537

104P/B

VDDR

C483

104P/B

C520

104P/B

C488

x_102P/B

C524

102P/B

close to KT400 power pin

VCC2_5

C528

C525

104P/B

C517

104P/B

104P/B

C543

104P

C498

105P/B

C532

x_105P/B

C521

104P/B

C516

104P/B

C530

104P/B

C503

104P/B

C535

102P/B

C533

104P/B

C541

104P/B

C536

104P/B

C511

102P/B

C538

104P/B

C515

105P/B

C491

104P/B

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

VT8377 POWER

MS-7021

Last Revision Date:

Sheet

1

Friday, September 19, 2003

10 37

Rev

100

of

5

SYSTEM MEMORY

4

3

2

1

VDDR

D D

738467085

108

120

148

168223054627796

R51

1KST

R46

1KST

VDDR

DR_MD[63..0]

R196 4.7K

MSWEA#8,13

DDR_VREF

C23

X_104P

C25

105P

C24

104P

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

MSWEA#

C119

Place 104p Cap. near the DIMM

4.7u-0805

VDD0

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

4

SLAVE ADDRESS = 1010000B

NC4

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

3111826344250586674818993

DR_MD[63..0]12,13,14

C C

B B

VDDR

A A

5

104

112

128

136

143

156

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184

DDR DIMM

SOCKET

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

100

116

124

132

139

VDDQ11

VSS17

164

172

1801582

VDDQ12

VDDQ13

VDDQ14

PIN

NC(RESET#)

VSS18

VSS19

VSS20

145

152

160

176

3

VCC3

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

NC/FETEN

A10_AP

SDA

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A11

A12

A13

BA0

BA1

BA2

SCL

SA0

SA1

SA2

R175 10K

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR1

DDRDIMM_184

MCS#0

MCS#1

DR_MDQS#0

DR_MDQS#1

DR_MDQS#2

DR_MDQS#3

DR_MDQS#4

DR_MDQS#5

DR_MDQS#6

DR_MDQS#7

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA13

MAA14

MAA15

MAA11

MAA12

SMBCLK1

SMBDATA1

DCLK0

DCLK#0

DCLK1

DCLK#1

DCLK2

DCLK#2

MCKE0

MCKE1

MSCASA#

MSRASA#

DR_MDQM#0

DR_MDQM#1

DR_MDQM#2

DR_MDQM#3

DR_MDQM#4

DR_MDQM#5

DR_MDQM#6

DR_MDQM#7

DR_MDQM#8

MCS#0 8,13

MCS#1 8,13

DR_MDQS#0 8,12,13,14

DR_MDQS#1 8,12,13,14

DR_MDQS#2 8,12,13,14

DR_MDQS#3 8,12,13,14

DR_MDQS#4 8,12,13,14

DR_MDQS#5 8,12,13,14

DR_MDQS#6 8,12,13,14

DR_MDQS#7 8,12,13,14

MAA[15..0]

SMBCLK1 6,12,17,19,31,33

SMBDATA1 6,12,17,19,31,33

DCLK0 6

DCLK#0 6

DCLK1 6

DCLK#1 6

DCLK2 6

DCLK#2 6

MCKE0 8

MCKE1 8

MSCASA# 8,13

MSRASA# 8,13

DR_MDQM#0 12,13,14

DR_MDQM#1 12,13,14

DR_MDQM#2 12,13,14

DR_MDQM#3 12,13,14

DR_MDQM#4 12,13,14

DR_MDQM#5 12,13,14

DR_MDQM#6 12,13,14

DR_MDQM#7 12,13,14

MAA[15..0] 8,13

2

VDDR

C604

C605

105P

105P

C610

105P

C608

105P

C606

105P

Micro Star Restricted Secret

Title

System Memory : DDR DIMM 1

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

C602

105P

MS-7021

C609

C607

105P

105P

Last Revision Date:

Friday, September 19, 2003

Sheet

11 37

1

Rev

100

of

5

SYSTEM MEMORY

4

3

2

1

D D

738467085

DR_MD[63..0]11,13,14

C C

B B

A A

DR_MD[63..0]

VDDR

R199 4.7K

MSWEB#8,13

DDR_VREF

MSWEB#

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

VDD0

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

VDDR

108

120

148

VDD1

VDD2

VDD3

VDD4

VDD5

168223054627796

VDD6

VDD7

VDD8

VDDQ0

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

104

VDDQ6

112

128

VDDQ7

136

VDDQ8

VDDQ9

143

156

VDDQ10

VDDQ11

184

DDR DIMM

SOCKET

SLAVE ADDRESS = 1010001B

VSS0

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

3111826344250586674818993

100

116

124

132

139

164

172

1801582

VDDQ12

VDDQ13

VDDQ14

PIN

NC(RESET#)

VSS18

VSS19

VSS20

145

152

160

176

VCC3

VDDID

VDDQ15

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

NC/FETEN

A10_AP

A11

A12

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

VSS21

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A13

R176 10K

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR2

DDRDIMM_184

MCS#2

MCS#3

DR_MDQS#0

DR_MDQS#1

DR_MDQS#2

DR_MDQS#3

DR_MDQS#4

DR_MDQS#5

DR_MDQS#6

DR_MDQS#7

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB13

MAB14

MAB15

MAB11

MAB12

SMBCLK1

SMBDATA1

VCC3

DCLK3

DCLK#3

DCLK4

DCLK#4

DCLK5

DCLK#5

MCKE2

MCKE3

MSCASB#

MSRASB#

DR_MDQM#0

DR_MDQM#1

DR_MDQM#2

DR_MDQM#3

DR_MDQM#4

DR_MDQM#5

DR_MDQM#6

DR_MDQM#7

DR_MDQM#8

MCS#2 8,13

MCS#3 8,13

DR_MDQS#0 8,11,13,14

DR_MDQS#1 8,11,13,14

DR_MDQS#2 8,11,13,14

DR_MDQS#3 8,11,13,14

DR_MDQS#4 8,11,13,14

DR_MDQS#5 8,11,13,14

DR_MDQS#6 8,11,13,14

DR_MDQS#7 8,11,13,14

MAB[15..0]

SMBCLK1 6,11,17,19,31,33

SMBDATA1 6,11,17,19,31,33

DCLK3 6

DCLK#3 6

DCLK4 6

DCLK#4 6

DCLK5 6

DCLK#5 6

MCKE2 8

MCKE3 8

MSCASB# 8,13

MSRASB# 8,13

DR_MDQM#0 11,13,14

DR_MDQM#1 11,13,14

DR_MDQM#2 11,13,14

DR_MDQM#3 11,13,14

DR_MDQM#4 11,13,14

DR_MDQM#5 11,13,14

DR_MDQM#6 11,13,14

DR_MDQM#7 11,13,14

MAB[15..0] 8,13

Place 104p Cap. near the DIMM

5

4

3

2

Title

System Memory : DDR DIMM 2

Document Number

MICRO-STAR INT'L

No. 69, Li-De St, Jung-He City,

CO.,LTD.

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-7021

Last Revision Date:

Friday, September 19, 2003

Sheet

12 37

1

Micro Star Restricted Secret

Rev

100

of

Loading...

Loading...