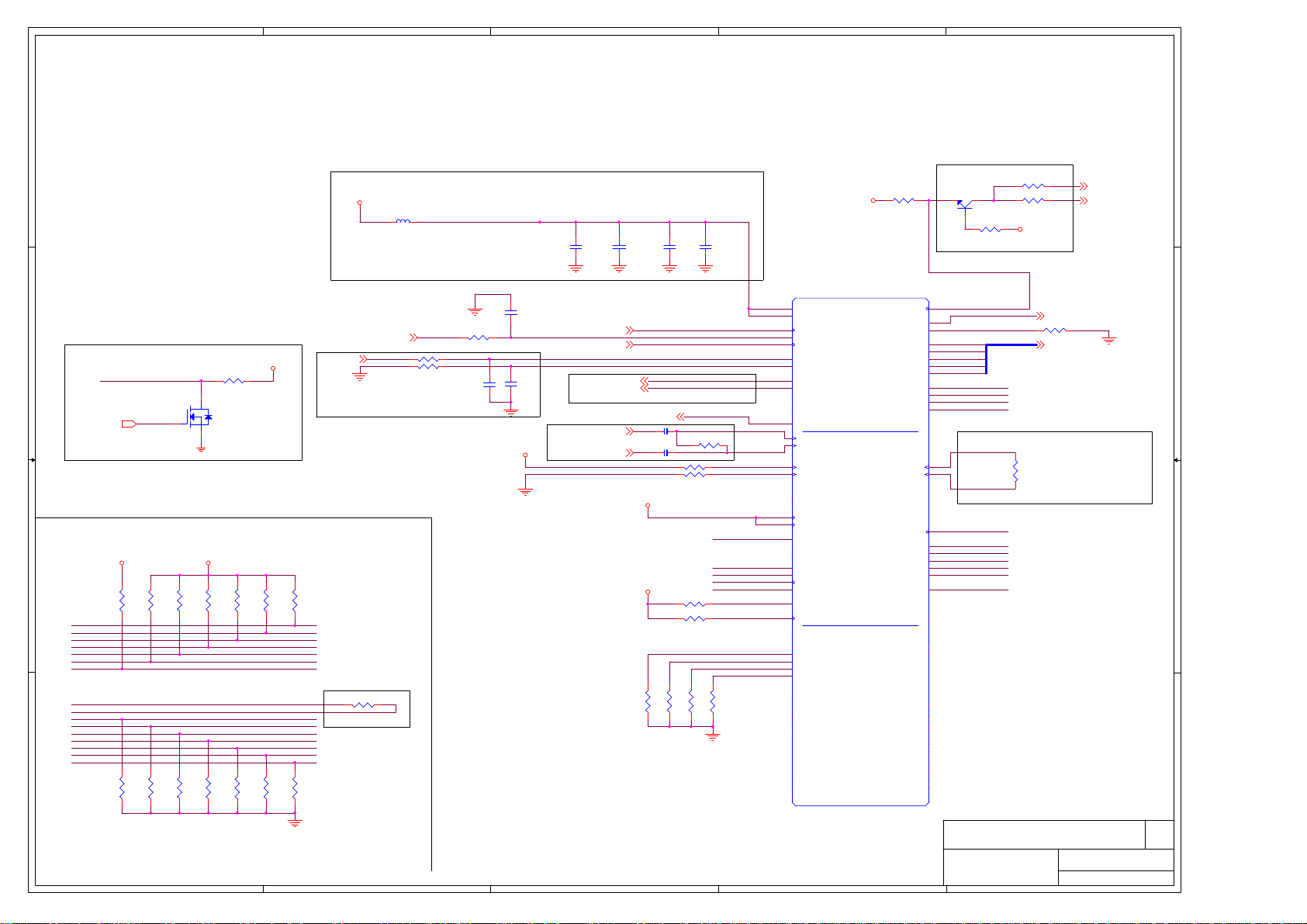

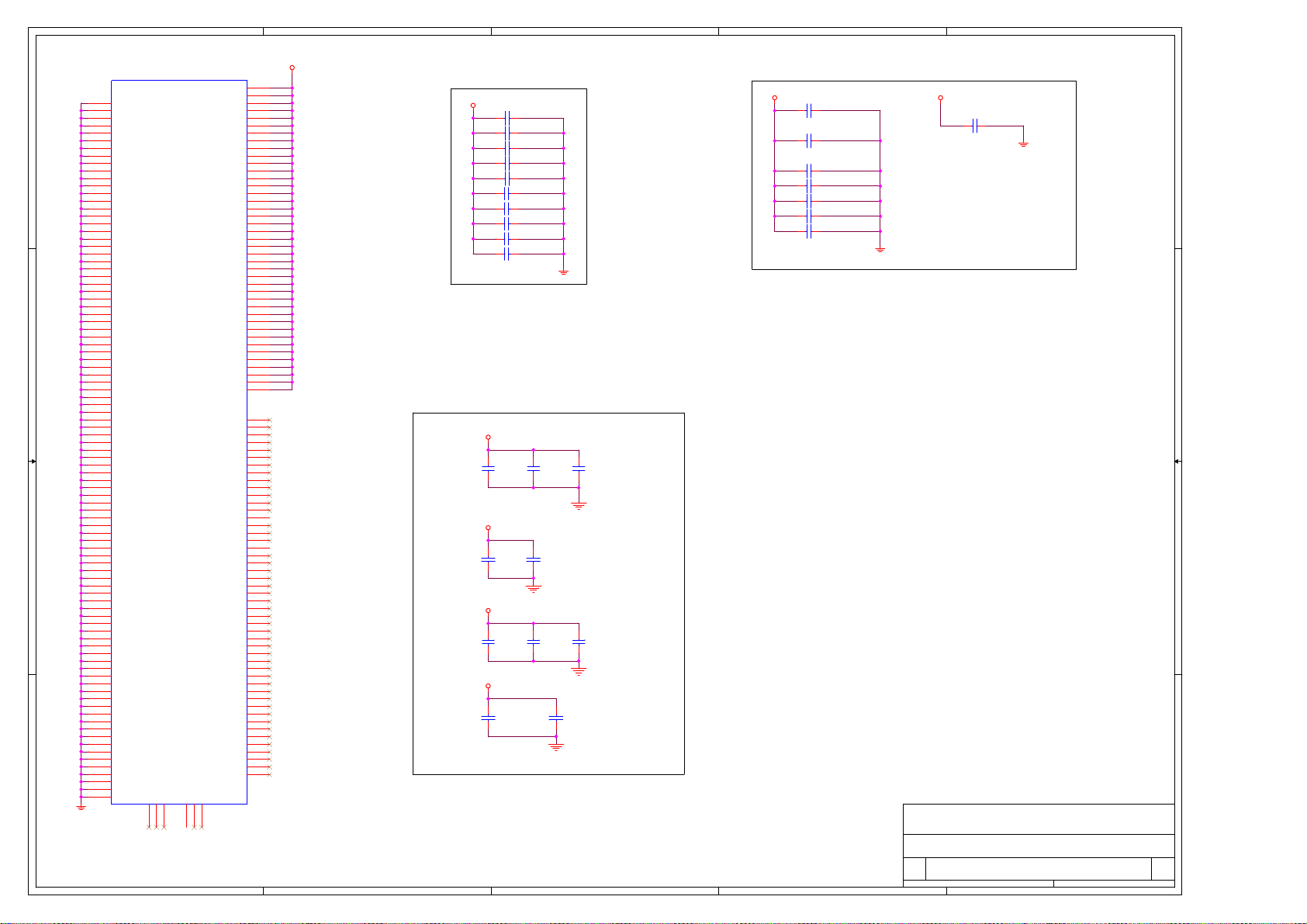

MSI MS-6767 Schematics

5

4

3

2

1

MS-6767 VER:0A ATX

Title Page

Cover Sheet 1

*AMD PGA 754 K8-Processor (DDR 333)

*VIA K8T400M / VT8237 Chipset

D D

(AGP 8X / VLink 8X)

*Winbond 83697HF-VF LPC I/O

*USB 2.0 support (integrated into VT8235)

*Vcore Jumpless support

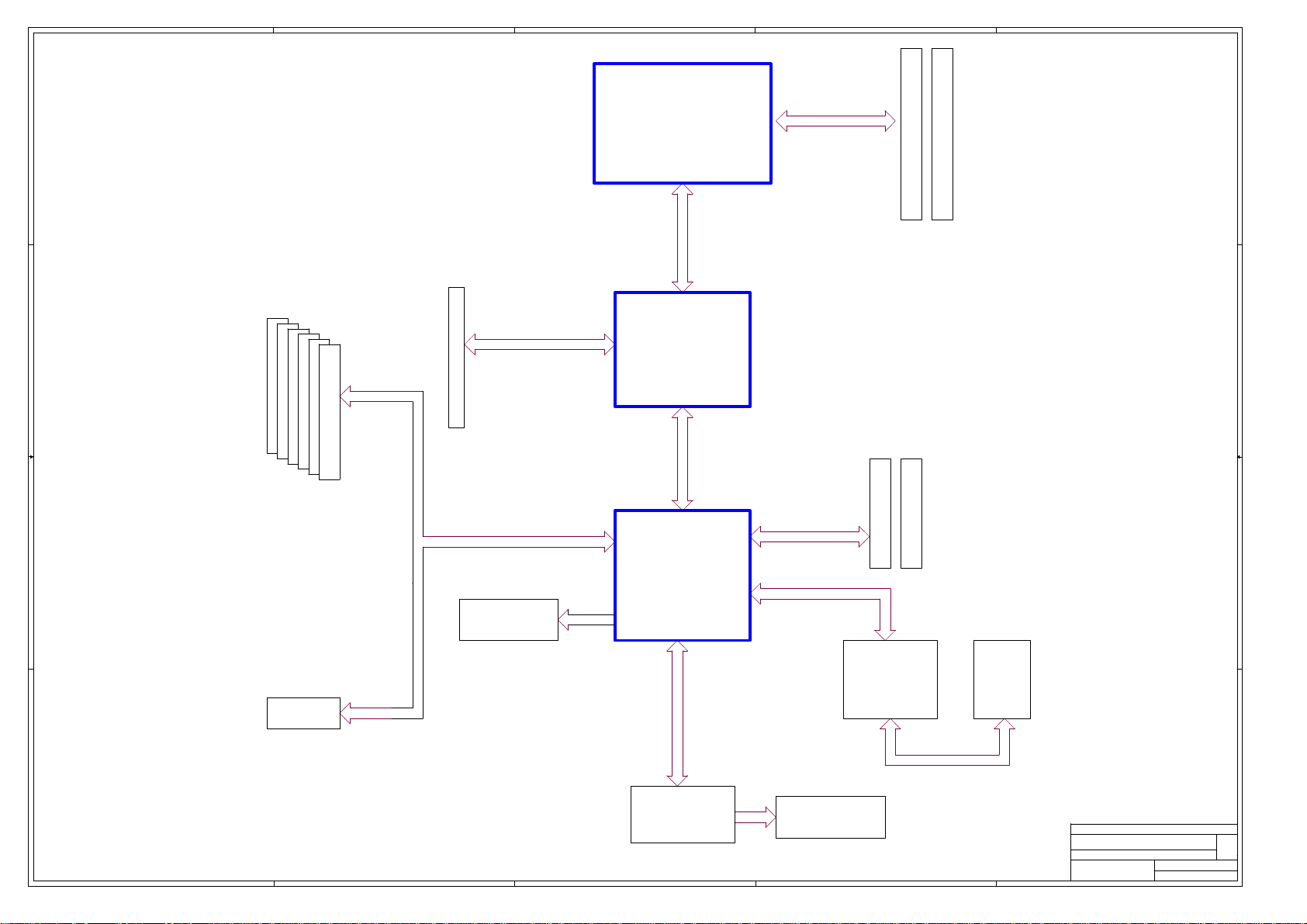

Block Diagram

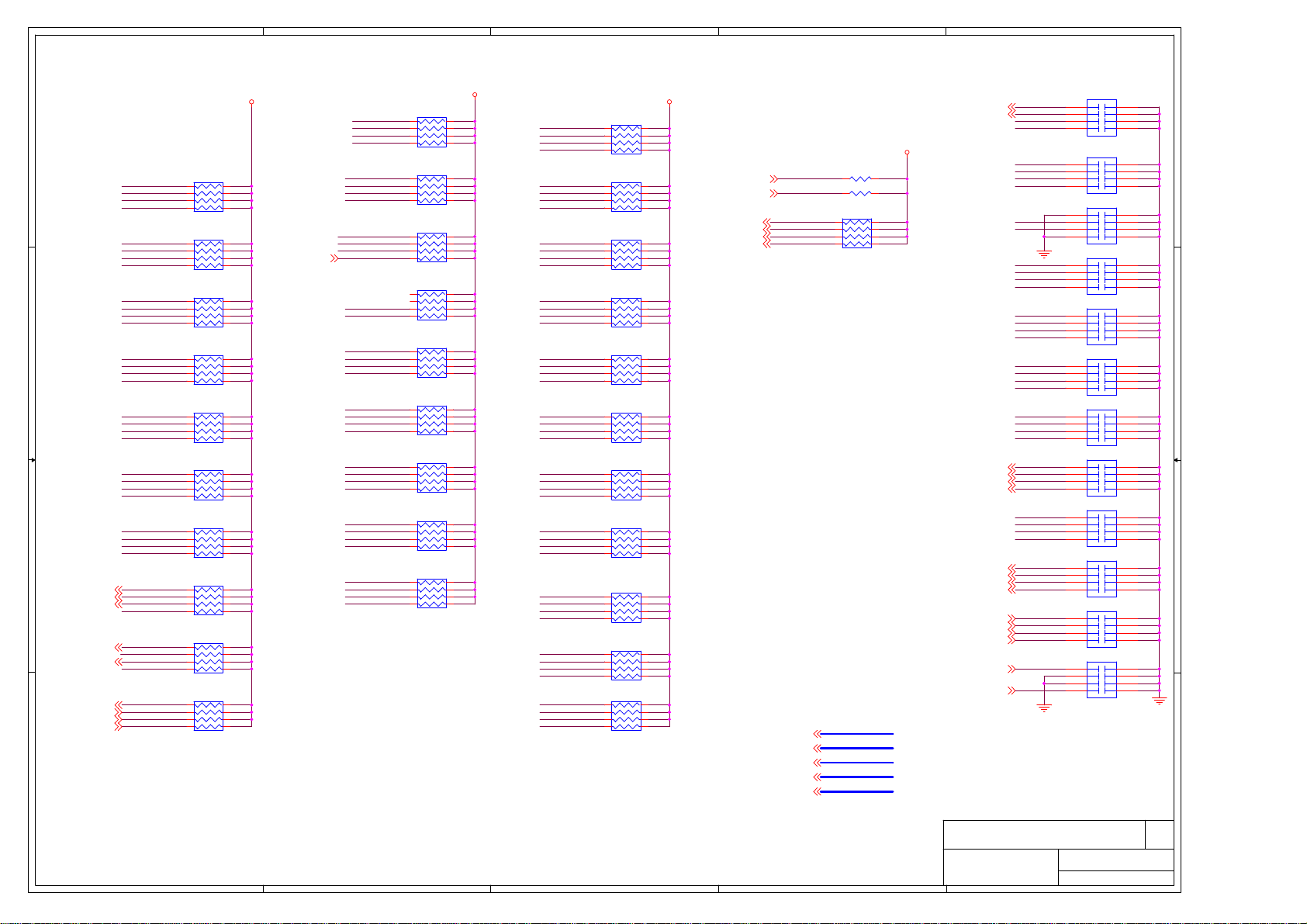

Clock Synthesizer & MS1 7

System Memory

DDR DIMM 1 & 2 8

DDR Terminations R & C

DDR Damping R & Bypass Cap.

*DDR DIMM * 2

*AGP SLOT * 1 ( 8X )

*PCI SLOT * 6

NB VIA K8T400M/VER:0.4 (HT)

K8 Vcore

AGP SLOT 8X

VT8237

C C

PCI Connectors * 6

BUCK Cap. / DLED

CMI9739A 6 channel S/W Audio

IDE ATA 66/100 Connectors * 2

Front USB Port *1 & Blue-Tooth

Rear USB Port *2

LPC I/O W83697HF & Floppy

Hardware monitor & FAN

BIOS ROM & Com Port Wake-Up

Keyboard/Mouse Connectors

B B

LPT/COM Port

VIA LAN

CPU Vcore Setting

AMD CPU Thermal Protection

ACPI Power & Power-Good Circuit

Power OK Sequence (GAL) & Front Panel

Decoupling Cap.

PCI Clock Diagram

Power Sequence

2

3GPIO SPEC

4,5,6AMD K8 -> 754 PGA Socket

9

10

11,12,13

14

15

16,17,18

19,20,21

22

23

24

25

26

27

28

29

30

31

32

33

34

35,36

37,38

39

40

41

History 42

A A

43Optional part

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

5

4

3

2

http://www.msi.com.tw

Cover Sheet

MS-6767

Last Revision Date:

Sheet

1

Rev

Friday, January 17, 2003

of

1 43

0A

5

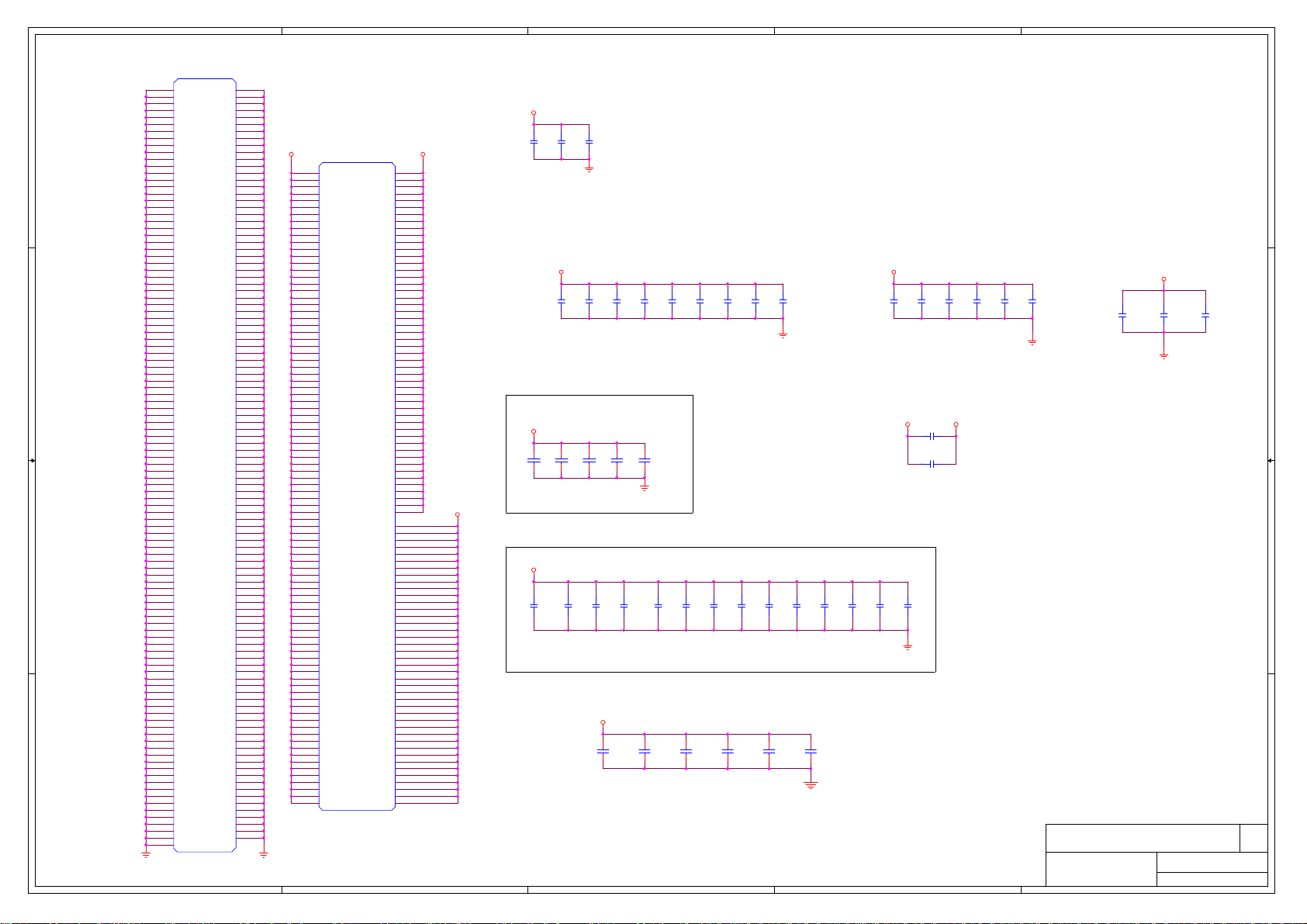

Block Diagram

4

3

2

1

AMD K8 Socket 754

D D

HT

DDR333

DDR * 2

A

G

C C

6 PCI Slots

P

S

L

O

T

AGP 8X /Fast Write

PCI-33

VIA

K8T400M

VLINK

Dual ATA 100/133

IDE Slot

==>ATA66,100,133 *2

B B

AC97 => S/W Audio

CMI9739A / 6 channel

AC97

VT8237

LPC BUS

SUPER I/O W83697HF ROM

USB

Serial Port *2 ,

IDE Port *1

X BUS

A A

Dual USB 1.1 OHCI

/2.0 EHCI 8 Ports

==> Front-Port *4 ,

Back-Port *4

5

4

3

Support *1 Blue-Tooth

Connector ( Share with

USB-Port *1 )

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

Block Diagram

MS-6767

1

Last Revision Date:

Sheet

Rev

Friday, January 17, 2003

of

2 43

0A

5

4

3

2

1

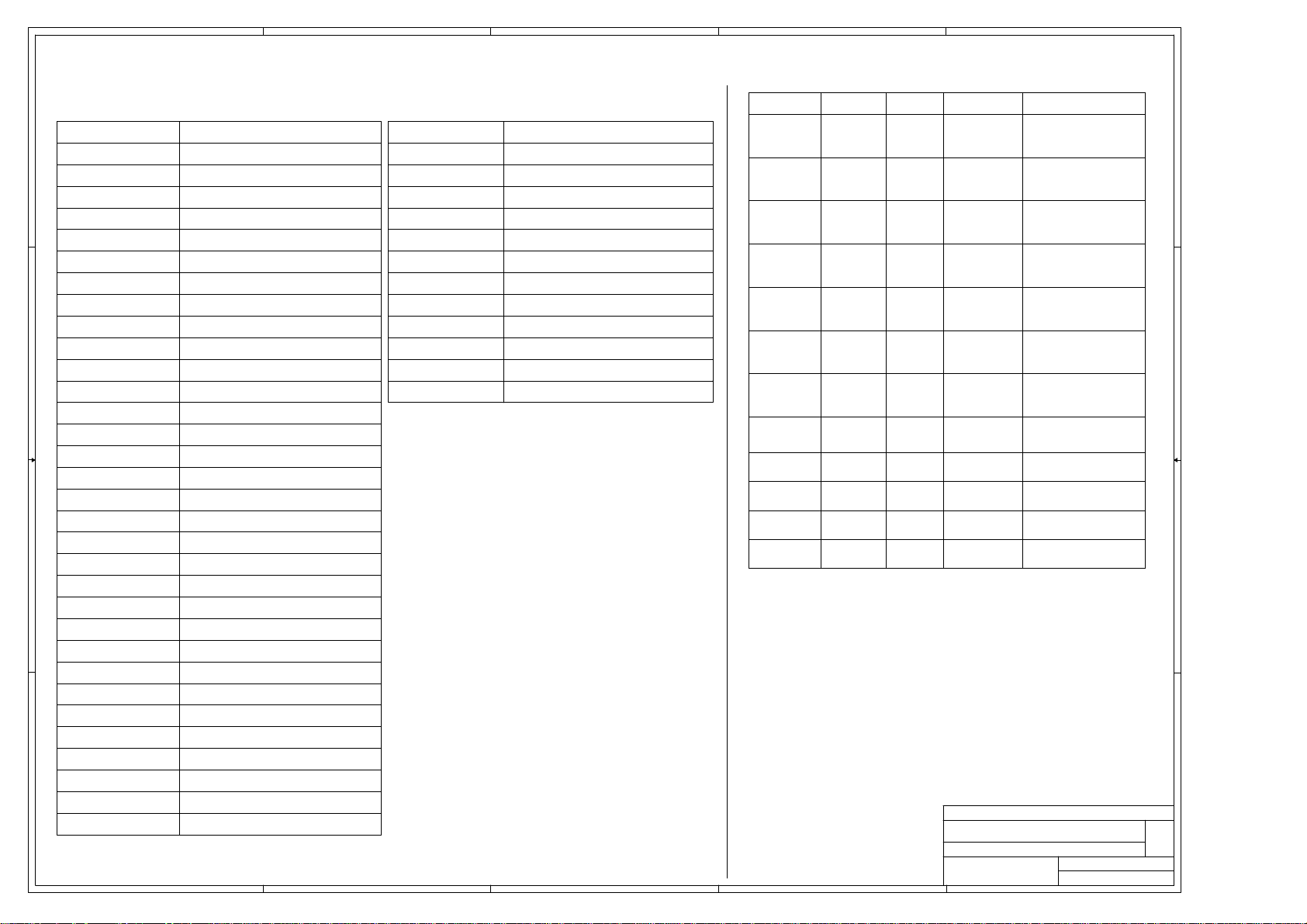

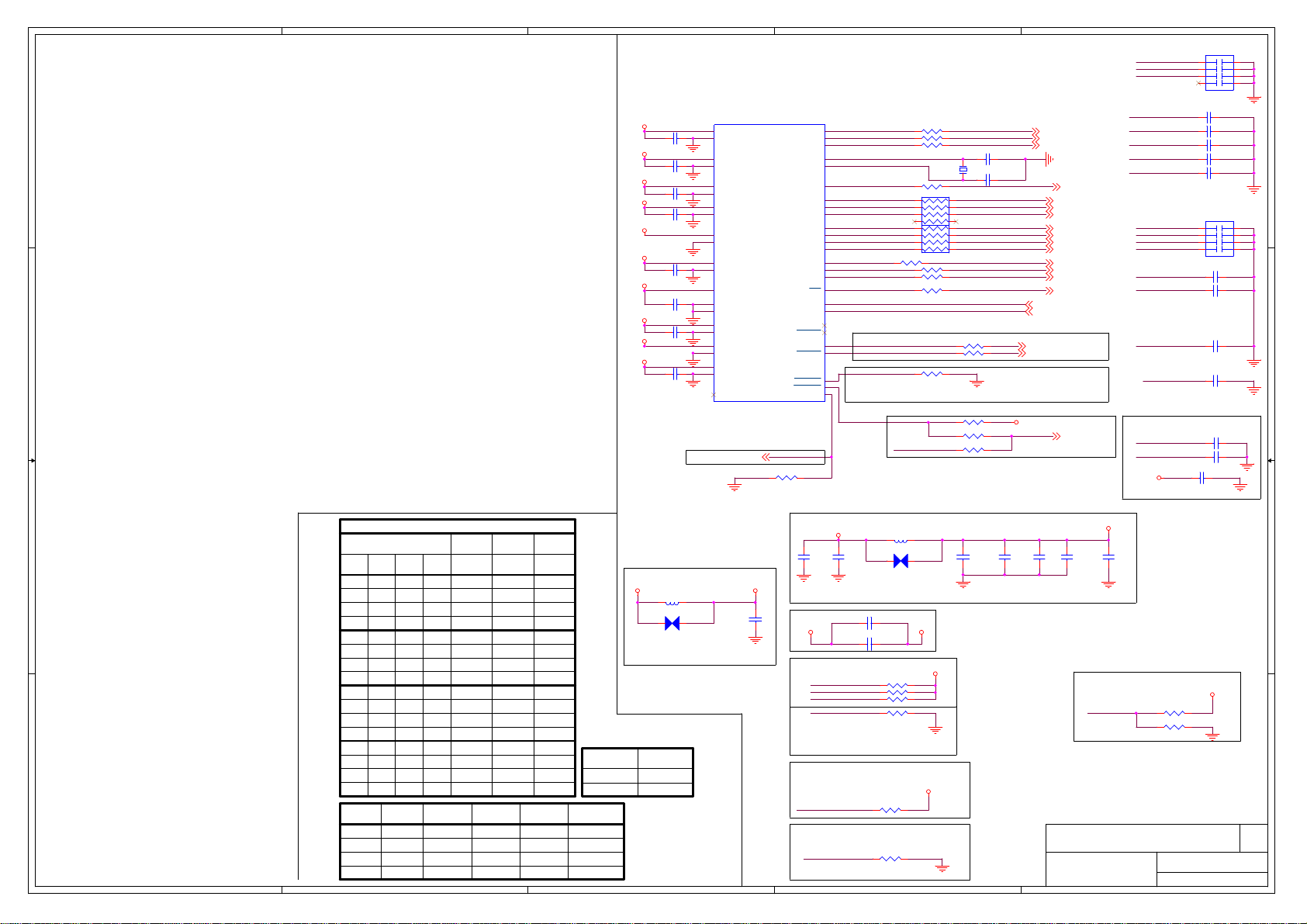

GPIO FUNCTION

VT8233 GPIO Function Define

PIN NAME

D D

GPO0 (VSUS33)

GPO1/SUSA#(VSUS33)

GPO2/SUSB#(VSUS33)

GPO3/SUSST1#(VSUS33)

GPO4/SUSCLK(VSUS33)

GPO5/CPUSTP#

GPO6/PCISTP#

GPO7/SLP#

GPO8/GPI8/IPBIN0

GPO9/GPI9/IPBIN1

C C

GPO10/GPI10/IPBRDFR

GPO11/GPI11/IPBRDCK

GPO12/GPI12/IPBOUT0

GPO13/GPI13/IPBOUT1

GPO14/GPI14/IPBTDFR

GPO15/GPI15/IPBTDCK

GPO16/SA16/STRAP

GPO17/SA17/STRAP

GPO18/SA18/STRAP

GPO19/SA19/STRAP

B B

GPO20/GPI20

/ACSDIN2/PCS0#/EI

GPO21/GPI21/ACSDIN3

/PCS1#/SLPBTN#

GPO22/GPI22/IOR#

GPO23/GPI23/IOW#

GPO24/GPI24/GPIOA

GPO25/GPI25/GPIOC

GPO26/GPI26/SMBDT2

(VSUS33)

GPO27/GPI27/SMBCK2

(VSUS33)

GPO28/GPI28/

APICD0/APICCS#

GPO29/GPI29/

A A

APICD1/APICACK#

GPO30/GPI30/GPIOD

GPO31/GPI31/GPIOE

5

SBGPO0 ( GLAN_EN )

SUSLED ( Power LED )

SUSB#

SUSST#

CTL_PLED1# ( Power LED )

NA (Exteranl Pull up to VCC3)

SBGPO6 ( 1394_EN )

GNT#5

SBGPO8 ->Vcore Setting ( Hi=CPU

Default , Low=Manual )

NA

SVID0

( Vcore Adjusting )

SVID1 ( Vcore Adjusting )

ROMLOCK

SVID2 ( Vcore Adjusting )

SVID3 ( Vcore Adjusting )

SVID4 ( Vcore Adjusting )

LDT Freq Strapping Bit0

LDT Freq Strapping Bit1

LDT Width (Low=8 Bit)

Fast Command (Low=Disable)

NA

(Exteranl Pull down to GND)

NA

(Exteranl Pull down to GND)

NA

NA

DLED1

DLED2

SMBDATA2/Slave SMBUS

SMBCLK2/Slave SMBUS

NA

NA

DLED3

DLED4

PIN NAME Function defineFunction define

GPI0

GPI1

GPI2/EXTSMI#

GPI3/RING#

GPI4/LID#

GPI5/BATLOW#

GPI6/PME#

GPI7/REQ#5

GPI16/INTRUDER#

GPI17/CPUMISS

GPI18/AOLGP1/THRM#

GPI19/IORDY

4

(Exteranl Pull up to VBAT)NA

ATADET0=>Detect IDE1 ATA100/66

EXTSMI#

RING#

ATADET1=>Detect IDE2 ATA100/66

(Exteranl Pull up to 3VDUAL)

NA

PCI_PME#

(Exteranl Pull up to 3VDUAL)

NA

(Exteranl Pull up to VBAT)

NA

(Exteranl Pull up to 3VDUAL)

NA

THRM#

(Exteranl Pull up to VCC3)NA

3

PCI Routing

DEVICES

PCI SLOT 1

PCI SLOT 2

PCI SLOT 3

PCI SLOT 4

PCI SLOT 5

PCI SLOT 6

Giga-Bit

LAN

MS1 #1

SETIAL ATA INT#B AD24 SATAPCLK ->

1394 INT#D AD25 1394_PCLK ->

MS1 #2 ( PREQ#5 )

INT#

INT#A

INT#B

INT#C

INT#D

INT#B

INT#C

INT#D

INT#A

INT#C

INT#D

INT#A

INT#B

INT#D

INT#A

INT#B

INT#C

INT#B

INT#C

INT#D

INT#A

INT#A

INT#B

INT#C

INT#D

INT#A AD26

2

W/O MS1 -> Green Color

W/ MS1 -> Red Color

IDSEL

AD16

AD17

AD18

AD19

AD21

AD20

REQ#/GNT#

PREQ#1

PGNT#1

PREQ#2

( PREQ#9 )

PGNT#2

( PGNT#9 )

PREQ#3

PGNT#3

PREQ#4

PGNT#4

PREQ#5

( PREQ#10 )

PGNT#5

( PGNT#10 )

PREQ#7

PGNT#7

PREQ#1

PGNT#1

PREQ#0

PGNT#0

( PREQ#2 )

( PGNT#2 )

( PREQ#11 )

( PGNT#11 )

( PGNT#5 )

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

CLOCK

PCICLK1 ->

( R_PCICLK0 )

PCICLK2 ->

( R_PCICLK1 )

PCICLK3 ->

( R_PCICLK2 )

PCICLK4 ->

( R_PCICLK3 )

PCICLK5 ->

( R_PCICLK4 )

PCICLK6 ->

( R_PCICLK5 )

GLAN_PCLK ->

( R_PCICLK10 )

MS1_PCLK ->

( R_PCICLKF )

( R_PCICLK13 )

( R_PCICLK12 )

MS2_PCLK ->

( R_PCICLKF )

Micro Star Restricted Secret

GPIO Spec.

MS-6767

Last Revision Date:

Sheet

1

Rev

Friday, January 17, 2003

of

3 43

0A

5

4

3

2

1

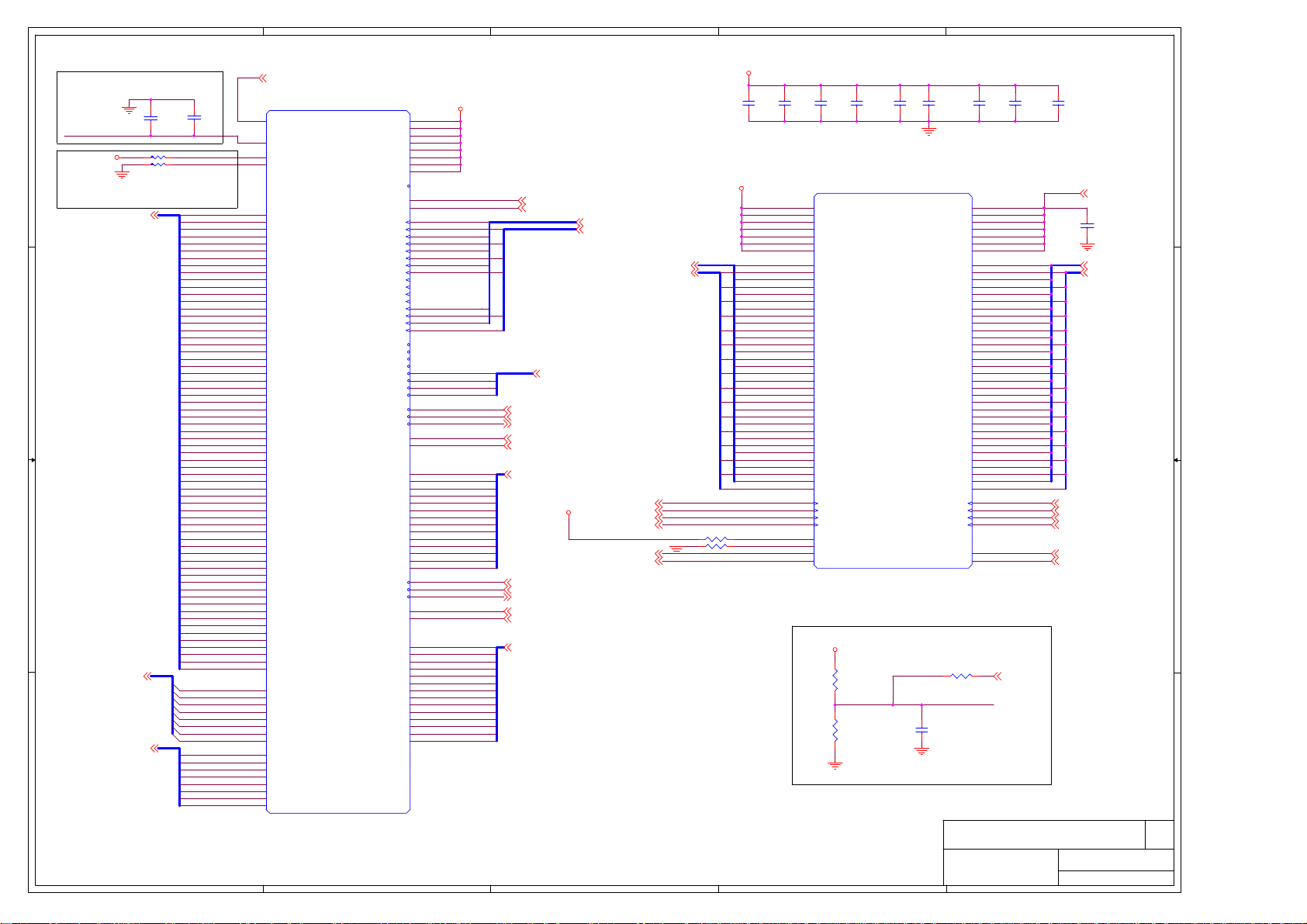

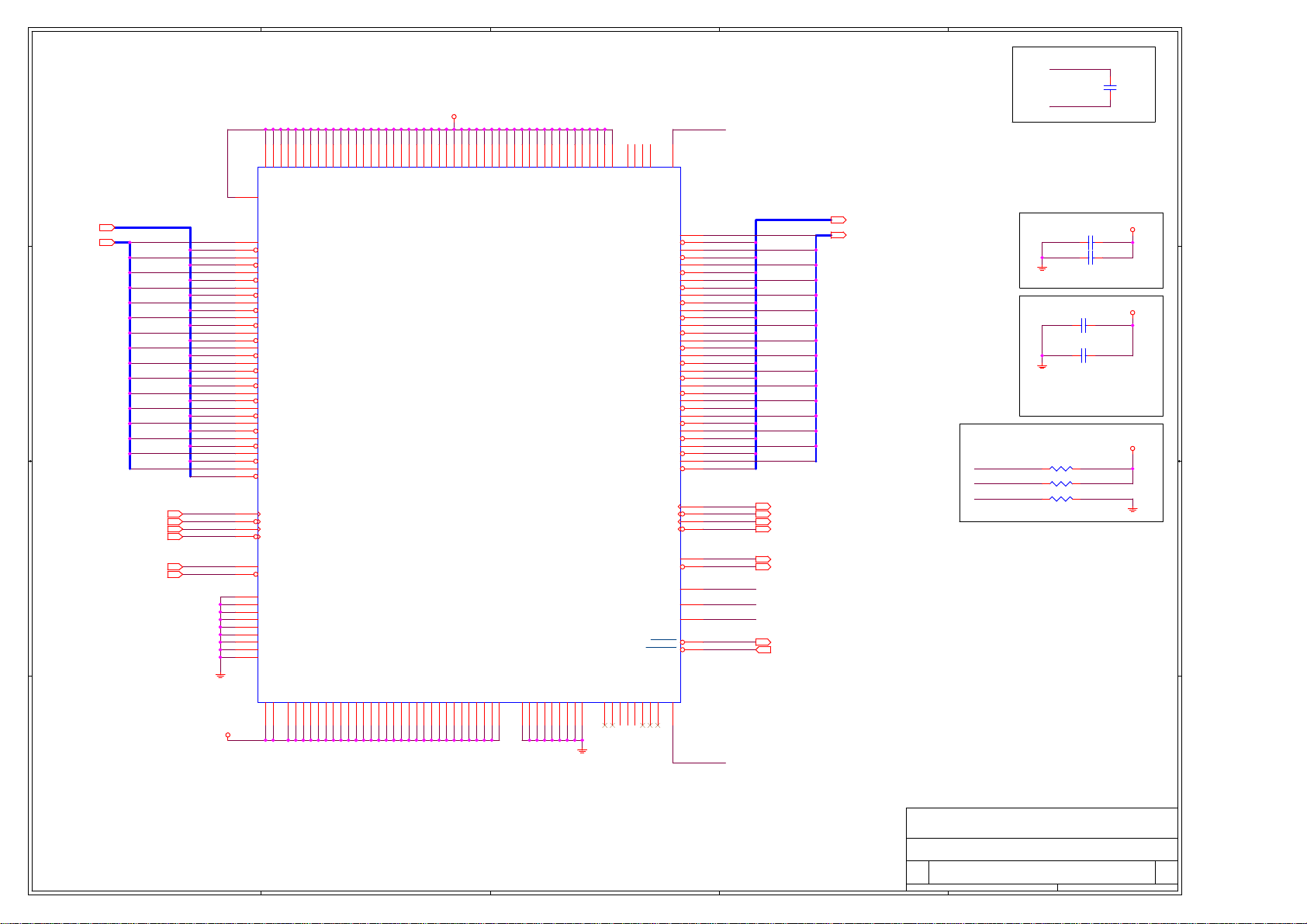

VREF routed as 40~50 mils trace wide ,

Space>25 mils

C62

C1000P50X

R120 44.2R1%

R126 44.2R1%

MD[63..0]10

DM[8..0]10

-MDQS[8..0]10

104P

MEMZN

MEMZP

MD63

MD62

MD61

MD60

MD59

MD58

MD57

MD56

MD55

MD54

MD53

MD52

MD51

MD50

MD49

MD48

MD47

MD46

MD45

MD44

MD43

MD42

MD41

MD40

MD39

MD38

MD37

MD36

MD35

MD34

MD33

MD32

MD31

MD30

MD29

MD28

MD27

MD26

MD25

MD24

MD23

MD22

MD21

MD20

MD19

MD18

MD17 MAA3

MD16

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

-MDQS7

-MDQS6

-MDQS5

-MDQS4

-MDQS3

-MDQS2

-MDQS1

-MDQS0

5

VREF_DDR_CLAW

D D

VDD_25_SUS

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

C C

B B

A A

AE13

AG12

D14

C14

A16

B15

A12

B11

A17

A15

C13

A11

A10

C11

AC1

AC3

AC2

AD1

AE1

AE3

AG3

AJ4

AE2

AF1

AH3

AJ3

AJ5

AJ6

AJ7

AH9

AG5

AH5

AJ9

AJ10

AH11

AJ11

AH15

AJ15

AG11

AJ12

AJ14

AJ16

A13

AA1

AG1

AH7

AH13

A14

AB1

AJ2

AJ8

AJ13

B9

C7

A6

A9

A5

B5

C5

A4

E2

E1

A3

B3

E3

F1

G2

G1

L3

L1

G3

J2

L2

M1

W1

W3

W2

Y1

R1

A7

C2

H1

T1

A8

D1

J1

VTT_SENSE 35

VTT_SENSE

MEMVREF1

MEMZN

MEMZP

MEMDATA63

MEMDATA62

MEMDATA61

MEMDATA60

MEMDATA59

MEMDATA58

MEMDATA57

MEMDATA56

MEMDATA55

MEMDATA54

MEMDATA53

MEMDATA52

MEMDATA51

MEMDATA50

MEMDATA49

MEMDATA48

MEMDATA47

MEMDATA46

MEMDATA45

MEMDATA44

MEMDATA43

MEMDATA42

MEMDATA41

MEMDATA40

MEMDATA39

MEMDATA38

MEMDATA37

MEMDATA36

MEMDATA35

MEMDATA34

MEMDATA33

MEMDATA32

MEMDATA31

MEMDATA30

MEMDATA29

MEMDATA28

MEMDATA27

MEMDATA26

MEMDATA25

MEMDATA24

MEMDATA23

MEMDATA22

MEMDATA21

MEMDATA20

MEMDATA19

MEMDATA18

MEMDATA17

MEMDATA16

MEMDATA15

MEMDATA14

MEMDATA13

MEMDATA12

MEMDATA11

MEMDATA10

MEMDATA9

MEMDATA8

MEMDATA7

MEMDATA6

MEMDATA5

MEMDATA4

MEMDATA3

MEMDATA2

MEMDATA1

MEMDATA0

MEMDQS17

MEMDQS16

MEMDQS15

MEMDQS14

MEMDQS13

MEMDQS12

MEMDQS11

MEMDQS10

MEMDQS9

MEMDQS8

MEMDQS7

MEMDQS6

MEMDQS5

MEMDQS4

MEMDQS3

MEMDQS2

MEMDQS1

MEMDQS0

MEMORY INTERFACE

U7B

MEMRESET_L

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H3

MEMCLK_L3

MEMCLK_H2

MEMCLK_L2

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

MEMRASA_L

MEMCASA_L

MEMWEA_L

MEMBANKA1

MEMBANKA0

RSVD_MEMADDA15

RSVD_MEMADDA14

MEMADDA13

MEMADDA12

MEMADDA11

MEMADDA10

MEMRASB_L

MEMCASB_L

MEMWEB_L

MEMBANKB1

MEMBANKB0

RSVD_MEMADDB15

RSVD_MEMADDB14

MEMADDB13

MEMADDB12

MEMADDB11

MEMADDB10

MEMCHECK7

MEMCHECK6

MEMCHECK5

MEMCHECK4

MEMCHECK3

MEMCHECK2

MEMCHECK1

MEMCHECK0

VTT_A4

VTT_A1

VTT_A2

VTT_A3

VTT_B1

VTT_B2

VTT_B3

VTT_B4

MEMCKEA

MEMCKEB

MEMCS_L7

MEMCS_L6

MEMCS_L5

MEMCS_L4

MEMCS_L3

MEMCS_L2

MEMCS_L1

MEMCS_L0

MEMADDA9

MEMADDA8

MEMADDA7

MEMADDA6

MEMADDA5

MEMADDA4

MEMADDA3

MEMADDA2

MEMADDA1

MEMADDA0

MEMADDB9

MEMADDB8

MEMADDB7

MEMADDB6

MEMADDB5

MEMADDB4

MEMADDB3

MEMADDB2

MEMADDB1

MEMADDB0

4

D17

A18

B17

C17

AF16

AG16

AH16

AJ17

AG10

AE8

AE7

D10

C10

E12

E11

AF8

AG8

AF10

AE10

V3

V4

K5

K4

R5

P5

P3

P4

D8

C8

E8

E7

D6

E6

C4

E5

H5

D4

G5

K3

H3

E13

C12

E10

AE6

AF3

M5

AE5

AB5

AD3

Y5

AB4

Y3

V5

T5

T3

N5

H4

F5

F4

L5

J5

E14

D12

E9

AF6

AF4

M4

AD5

AC5

AD4

AA5

AB3

Y4

W5

U5

T4

M3

N3

N1

U3

V1

N2

P1

U1

U2

VTT_DDR_SUS

MCKE0

MCKE1

MEMCLK_H7

MEMCLK_L7

MEMCLK_H6

MEMCLK_L6

MEMCLK_H5

MEMCLK_L5

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H0

MEMCLK_L0

-MCS3

-MCS2

-MCS1

-MCS0

-MSRASA

-MSCASA

MAA13

MAA12

MAA11

MAA10

MAA9

MAA8

MAA7

MAA6

MAA5

MAA4

MAA2

MAA1

MAA0

MAB13

MAB12

MAB11

MAB10

MAB9

MAB8

MAB7

MAB6

MAB5

MAB4

MAB3

MAB2

MAB1

MAB0

MCKE0 8,9

MCKE1 8,9

MEMCLK_H[7..0]

MEMCLK_L[7..0]

-MCS[3..0]

-MSRASA 8,9

-MSCASA 8,9

-MSWEA 8,9

MEMBANKA1 8,9

MEMBANKA0 8,9

MAA[13..0] 8,9

-MSRASB 8,9

-MSCASB 8,9

-MSWEB 8,9

MEMBAKB1 8,9

MEMBAKB0 8,9

MAB[13..0] 8,9

MEMCLK_H[7..0] 8

MEMCLK_L[7..0] 8

-MCS[3..0] 8,9

VDD_12_A

CADIP[0..15]11

CLKIP111

CLKIN111

CLKIP011

CLKIN011

CTLIP011

CTLIN011

3

R86 49.9R1%

R80 49.9R1%

VDD_12_A

C0.22U16Y

VDD_12_A

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

C171

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP1

CADIP0

CTLIP1

CTLIN1

C0.22U16YC63

W27

W26

AA27

AA26

AB25

AA25

AC27

AC26

AD25

AC25

W29

AB29

AA29

AB27

AB28

AD29

AC29

AD27

AD28

W25

Close to CPU

C160

C0.22U16Y

D29

D27

D25

C28

C26

B29

B27

T25

R25

U27

U26

V25

U25

T27

T28

V29

U29

V27

V28

Y29

Y25

Y27

Y28

R27

R26

T29

R29

VDD_25_SUS

R60

X_1KR1%

R63

X_1KR1%

C162

X_C0.22U16Y

U7A

N12-7540010-A10

VLDT0_A6

VLDT0_A5

VLDT0_A4

VLDT0_A3

VLDT0_A2

VLDT0_A1

VLDT0_A0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

HYPER TRANSPORT - LINK0

2

C221

C230

C237

X_C0.22U16Y

X_C0.22U16Y

VLDT0_B6

VLDT0_B5

VLDT0_B4

VLDT0_B3

VLDT0_B2

VLDT0_B1

VLDT0_B0

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

VREF routed as 40~50 mils trace wide ,

Space>25 mils

R75 0R

VREF_DDR_CLAW

C64

X_104P

Title

Document Number

C161

C0.22U16Y

AH29

AH27

AG28

AG26

AF29

AE28

AF25

N26

CADON15

N27

L25

CADON14

M25

L26

CADON13

L27

J25

CADON12

K25

G25

CADON11

H25

G26

CADON10

G27

E25

CADON9

F25

E26

CADON8

E27

N29

CADON7

P29

M28

CADON6

M27

L29

CADON5

M29

K28

CADON4

K27

H28

CADON3

H27

G29

CADON2

H29

F28

CADON1

F27

E29

CADON0

F29

CLKOP1

J26

CLKON1

J27

CLKOP0

J29

CLKON0

K29

N25

P25

P28

P27

Micro Star Restricted Secret

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

C169

X_C0.22U16Y

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2CADIP2

CADOP1

CADOP0

CTLOP0

CTLON0

MEM_VREF 8

K8 DDR & HT

C222

C0.22U16Y

VLDT0

CLKOP1 11

CLKON1 11

CLKOP0 11

CLKON0 11

CTLOP0 11

CTLON0 11

MS-6767

Last Revision Date:

Friday, January 17, 2003

Sheet

1

VLDT0 5

C69

C4.7U10Y0805

CADOP[0..15] 11

CADON[0..15] 11CADIN[0..15]11

of

4 43

Rev

0A

5

4

3

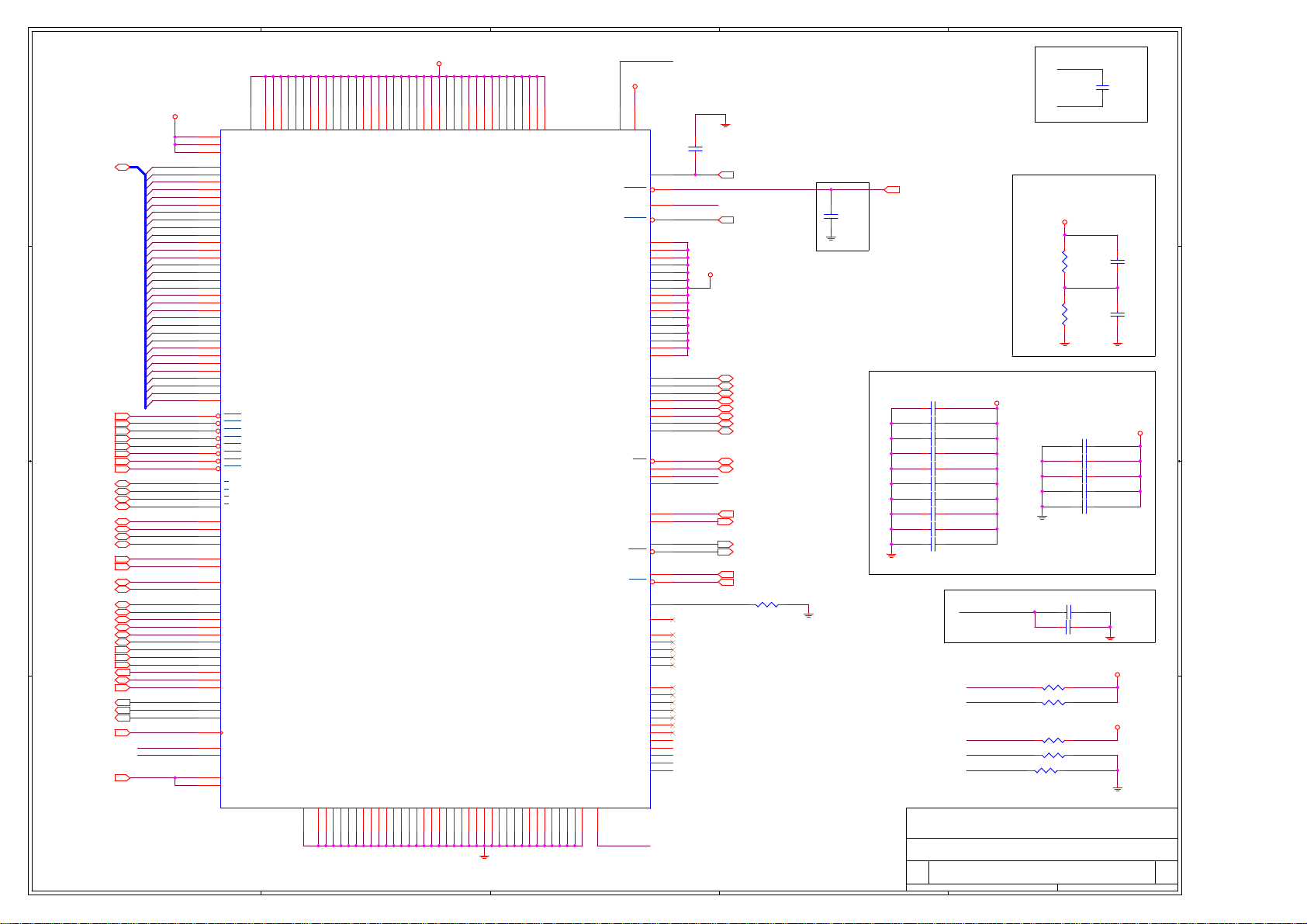

VCCA_PLL trace length from the VR1 to the

PGA must be 0.75".

2

1

Place al filters close to the PGA.

Keep all power and signal trce away from

the VR1.

Place a cut in the GND plane around the

VCCA_PLL regulator circuit.

D D

Near SB/VT8235

VDDA_25

FB1 0.18U450m_1210

LAYOUT: Route VDDA trace approx. 50 mils wide (use 2x25 mil

traces to exit ball field) and 500 mils long.

CPU_VDDA_25

C74

C39

X_C1U10Y

C1U16Y0805

C72

C0.22U16Y

C73

C3300P50X

VCC2_5

R141

1KR

Q41

N-MMBT3904_SOT23

R316

4.7KR

R308 X_0R

R307 0R

VCC2_5

THRMTRIP_EN# 37

THRM# 17,27

C46

CPU_GD37

C C

-LDTSTOP

PS_ON#A37

PS_ON#A

R91 1KR

Q18

N-2N7002_SOT23

VCC2_5

Place near CPU in 1" ,

Routed => 5:10/Trace:Space ,

Same Length

VLDT0

VLDT04

R62 0R

R87 44.2R1%

R83 44.2R1%

C76

C1000P50X

X_C1000P50X

C77

C1000P50X

VCC2_5

Near CPU in 0.5" .

-CPURST37

-LDTSTOP11,18

COREFB_H14

COREFB_L14

Differential , "10:10:5:10:10" .

CPUCLK0_H7

CPUCLK0_L7

VDDIO_SENSE35

C75 C0.039U16X

C78 C0.039U16X

VTT_DDR_SUS

L0_REF1

L0_REF0

R85 169R1%

R74 820R

R64 820R

CPU_PWROK

VDDIO_SENSE

HDT Test Port Signal .

VCC2_5

R130

X_1KR

R135

1KR

R131

X_1KR

R125

1KR

R139

X_1KR

R70

1KR

5

R134

X_1KR

R119

1KR

R61

X_1KR

R118

1KR

R71

X_1KR

Reserved for test

R137

1KR

4

VCC2_5

R133 1KR

R124 1KR

R52

R73

R53

1KR

R69

1KRR607 X

1KR

1KR

3

DBREQ_L

DBRDY

TCK

TMS

TDI

TRST_L

TDO

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

NC_D18

NC_B19

NC_C19

NC_D20

NC_C21

VDD_25_SUS

R138

1KR

R76

1KR

B B

A A

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

DBRDY

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

NC_AE23

NC_AF23

NC_AF22

NC_AF21

AH25

AJ25

AF20

AE18

AJ27

AF27

AE26

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

AG15

AH17

AJ28

AE23

AF23

AF22

AF21

AG2

AH1

AE21

AG4

AG6

AE9

AG9

A23

A24

B23

C16

C15

E20

E17

B21

A21

C18

A19

A28

AA2

B18

C20

C1

J3

R3

D3

C6

VDDA1

VDDA2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VTT_A5

VTT_B5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY1

KEY0

NC_AE23

NC_AF23

NC_AF22

NC_AF21

FREE29

FREE31

FREE33

FREE35

FREE1

FREE37

FREE4

FREE38

FREE41

FREE7

FREE11

FREE12

FREE13

FREE14

FREE40

U7C

THERMTRIP_L

THERMDA

THERMDC

VID4

VID3

VID2

VID1

VID0

NC_AG18

NC_AH18

NC_AG17

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

NC_AF18

RSVD_SCL

RSVD_SDA

FREE26

FREE28

FREE30

FREE32

FREE34

FREE36

FREE10

FREE18

FREE19

FREE42

FREE24

FREE25

FREE27

2

THERMTRIP_CPU_L

A20

THERMDA_CPU

A26

THERMDC_CPU

A27

VID4

AG13

VID3

AF14

VID2

AG14

VID1

AF15

VID0

AE15

NC_AG18

AG18

NC_AH18

AH18

NC_AG17

AG17

NC_AJ18

AJ18

FBCLKOUT_H

AH19

AJ19

AE19

D20

C21

D18

C19

B19

A22

R88

80.6R1%

FBCLKOUT_L

Zdiff = 80 ohm

DBREQ_L

NC_D20

NC_C21

NC_D18

NC_C19

NC_B19

TDO

AF18

D22

C22

B13

B7

C3

K1

R2

AA3

F3

C23

AG7

AE22

C24

A25

C9

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

THERMDA_CPU 34

R123 0R

VID[4..0] 33

LAYOUT: Route

FBCLKOUT_H/L differentially

with 20/8/5/8/20 spacing and

trace width. ( In CPU

breakout => routed 5:5:5 )

K8 HDT & MISC

MS-6767

Last Revision Date:

Friday, January 17, 2003

Sheet

1

of

5 43

Rev

0A

5

4

3

2

1

C614

X_C6.8P50N

X_C6.8P50N

C92

C1U10Y

C129

C10U6.3Y1206

EMI

C609

X_C6.8P50N

C3

X_C0.22U16Y

C140

C10U6.3Y1206

C606

C0.22U16Y

C612

X_C6.8P50N

GND

C123

C136

C0.22U16Y

VDD_25_SUS

C617

C620

X_C6.8P50N

VDD_25_SUS VTT_DDR_SUS

C150

C159

C1U16Y0805

C1U16Y0805

C172

C174

C0.22U16Y

C1U16Y0805

X_C0.22U16Y

C615

<nopop>

<nopop>

X_C6.8P50N

X_C6.8P50N

C56

X_C0.22U16Y

<nopop>

C284

X_C0.22U16Y

<nopop>

C199

C0.22U16Y

GND

C605

C608

<nopop>

X_C6.8P50N

C603

<nopop>

<nopop>

X_C6.8P50N

<nopop>

X_C6.8P50N

X_C6.8P50N

GND

C600

X_C6.8P50N

C619

C610

GND

X_C6.8P50N

X_C6.8P50N

C122

C0.22U16Y

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

K8 POWER & GND

MS-6767

Last Revision Date:

Friday, January 17, 2003

Sheet

1

6 43

R ev

0A

of

U7E

B2

VSS1

AH20

VSS3

AB21

VSS4

W22

VSS5

M23

VSS6

L24

VSS7

AG25

VSS8

AG27

VSS9

AA10

AE16

W20

AA20

AC20

AE20

AG20

AJ20

AD21

AG21

AG29

AA22

AC22

AG22

AH22

AJ22

AB23

AD23

AG23

W24

AA24

AC24

AG24

AJ24

AD26

AF26

AH26

AB17

AD17

AA18

AC18

AB19

AD19

AF19

D2

VSS10

AF2

VSS11

W6

VSS12

Y7

VSS13

AA8

VSS14

AB9

VSS15

VSS16

J12

VSS17

B14

VSS18

Y15

VSS19

VSS20

J18

VSS21

G20

VSS22

R20

VSS23

U20

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

D21

VSS31

F21

VSS32

H21

VSS33

K21

VSS34

M21

VSS35

P21

VSS36

T21

VSS37

V21

VSS38

Y21

VSS39

VSS40

VSS41

B22

VSS42

E22

VSS43

G22

VSS44

J22

VSS45

L22

VSS46

N22

VSS47

R22

VSS48

U22

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

D23

VSS56

F23

VSS57

H23

VSS58

K23

VSS59

P23

VSS60

T23

VSS61

V23

VSS62

Y23

VSS63

VSS64

VSS65

VSS66

E24

VSS67

G24

VSS68

J24

VSS69

N24

VSS70

R24

VSS71

U24

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

B25

VSS78

C25

VSS79

B26

VSS80

D26

VSS81

H26

VSS82

M26

VSS83

T26

VSS84

Y26

VSS85

VSS86

VSS87

VSS88

C27

VSS89

B28

VSS90

D28

VSS91

G28

VSS92

F15

VSS187

H15

VSS188

VSS206

VSS207

B16

VSS208

G18

VSS209

VSS210

VSS211

D19

VSS212

F19

VSS213

H19

VSS214

K19

VSS215

Y19

VSS216

VSS217

VSS218

VSS219

J20

VSS220

L20

VSS221

N20

VSS222

GROUND

5

D D

C C

B B

A A

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS189

VSS190

VSS191

VSS192

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS223

VSS201

VSS202

VSS203

VSS204

VSS205

L28

R28

W28

AC28

AF28

AH28

C29

F2

H2

K2

M2

P2

T2

V2

Y2

AB2

AD2

AH2

B4

AH4

B6

G6

J6

L6

N6

R6

U6

AA6

AC6

AH6

F7

H7

K7

M7

P7

T7

V7

AB7

AD7

B8

G8

J8

L8

N8

R8

U8

W8

AC8

AH8

F9

H9

K9

M9

P9

T9

V9

Y9

AD9

B10

G10

J10

L10

N10

R10

U10

W10

AC10

AH10

F11

H11

K11

Y11

AB11

AD11

B12

G12

AA12

AC12

AH12

F13

H13

K13

Y13

AB13

AD13

AF17

G14

J14

AA14

AC14

AE14

D16

E15

K15

AB15

AD15

AH14

E16

G16

J16

AA16

AC16

AE29

AJ26

E18

F17

H17

K17

Y17

LAYOUT: Place 1 capacitor every 1-1.5"

VCORE

along VDD_CORE perimiter.

C54

VCORE

AC15

AB14

AA15

AB16

AA17

AC17

AE17

AB18

AD18

AG19

AC19

AA19

AB20

AD20

AA21

AC21

AB22

AD22

AA23

AC23

AB24

AD24

AH24

AE25

GNDGND

H18

H22

H24

G13

G15

H16

G17

G19

H20

M20

G21

N21

R21

U21

W21

M22

G23

N23

R23

U23

W23

D24

M24

U7D

L7

VDD1

VDD2

VDD3

B20

VDD4

E21

VDD5

VDD6

J23

VDD7

VDD8

F26

VDD9

N7

VDD10

L9

VDD11

V10

VDD12

VDD13

K14

VDD14

Y14

VDD15

VDD16

VDD17

J15

VDD18

VDD19

VDD20

K16

VDD21

Y16

VDD22

VDD23

VDD24

J17

VDD25

VDD26

VDD27

VDD28

F18

VDD29

K18

VDD30

Y18

VDD31

VDD32

VDD33

VDD34

E19

VDD35

VDD36

VDD39

VDD38

J19

VDD37

F20

VDD40

VDD41

K20

VDD42

VDD43

P20

VDD44

T20

VDD45

V20

VDD46

Y20

VDD47

VDD48

VDD49

VDD50

J21

VDD51

L21

VDD52

VDD53

VDD54

VDD55

VDD56

VDD57

VDD58

F22

VDD59

K22

VDD60

VDD61

P22

VDD62

T22

VDD63

V22

VDD64

Y22

VDD65

VDD66

VDD67

E23

VDD68

VDD69

L23

VDD70

VDD71

VDD72

VDD73

VDD74

VDD75

VDD76

B24

VDD77

VDD78

F24

VDD79

K24

VDD80

VDD81

P24

VDD82

T24

VDD83

V24

VDD84

Y24

VDD85

VDD86

VDD87

VDD88

VDD89

K26

VDD90

P26

VDD91

V26

VDD92

POWER

VDDIO1

VDDIO2

VDDIO3

VDDIO4

VDDIO5

VDDIO7

VDDIO8

VDDIO9

VDDIO10

VDDIO11

VDDIO12

VDDIO13

VDDIO14

VDDIO15

VDDIO16

VDDIO17

VDDIO18

VDDIO19

VDDIO20

VDDIO21

VDDIO22

VDDIO23

VDDIO24

VDDIO25

VDDIO26

VDDIO27

VDDIO28

VDDIO29

VDDIO30

VDDIO31

VDDIO32

VDDIO33

VDDIO34

VDDIO35

VDDIO36

VDDIO37

VDDIO38

VDDIO39

VDDIO40

VDDIO41

VDDIO42

VDDIO43

VDDIO44

VDDIO45

VDDIO46

VDDIO47

VDDIO48

VDDIO49

VDDIO50

VDDIO6

VDD96

VDD97

VDD98

VDD99

VDD100

VDD101

VDD102

VDD103

VDD104

VDD105

VDD106

VDD107

VDD108

VDD109

VDD110

VDD111

VDD112

VDD113

VDD114

VDD115

VDD116

VDD117

VDD118

VDD119

VDD120

VDD121

VDD122

VDD123

VDD124

VDD125

VDD126

VDD127

VDD128

VDD129

VDD130

VDD131

VDD132

VDD133

VDD93

VDD94

VDD95

VDD_25_SUS

E4

G4

J4

L4

N4

U4

W4

AA4

AC4

AE4

D5

AF5

F6

H6

K6

M6

P6

T6

V6

Y6

AB6

AD6

D7

G7

J7

AA7

AC7

AF7

F8

H8

AB8

AD8

D9

G9

AC9

AF9

F10

AD10

D11

AF11

F12

AD12

D13

AF13

F14

AD14

F16

AD16

D15

R4

N28

U28

AA28

AE27

R7

U7

W7

K8

M8

P8

T8

V8

Y8

J9

N9

R9

U9

W9

AA9

H10

K10

M10

P10

T10

Y10

AB10

G11

J11

AA11

AC11

H12

K12

Y12

AB12

J13

AA13

AC13

H14

AB26

E28

J28

4

VCORE

C180

LAYOUT: Place 6 EMI caps along bottom right side of Clawhammer,

2 in middle of HT link, and 12 along bottom left side of Claw-hammer.

Place between DIMN1 & 2

VDD_25_SUS

VDD_25_SUS

C87

C86

X_C6.8P50N

X_C6.8P50N

X_C6.8P50N

GND

VCORE VCORE

C88

104P

C2

104P

C604

C607

X_C6.8P50N

X_C6.8P50N

C181

104P

C616

C249

104P

C611

C601

X_C6.8P50N

X_C6.8P50N

C287

104P

GND

LAYOUT: Place beside processor.

C168

C1U10Y

In CPU.

C187

<nopop>

X_C0.22U16Y

C120

C10U6.3Y1206

3

C232

X_C0.22U16Y

X_C0.22U16Y

C148

C113

C1U10Y

<nopop>

VCORE

C119

C10U6.3Y1206

5

D D

C C

4

3

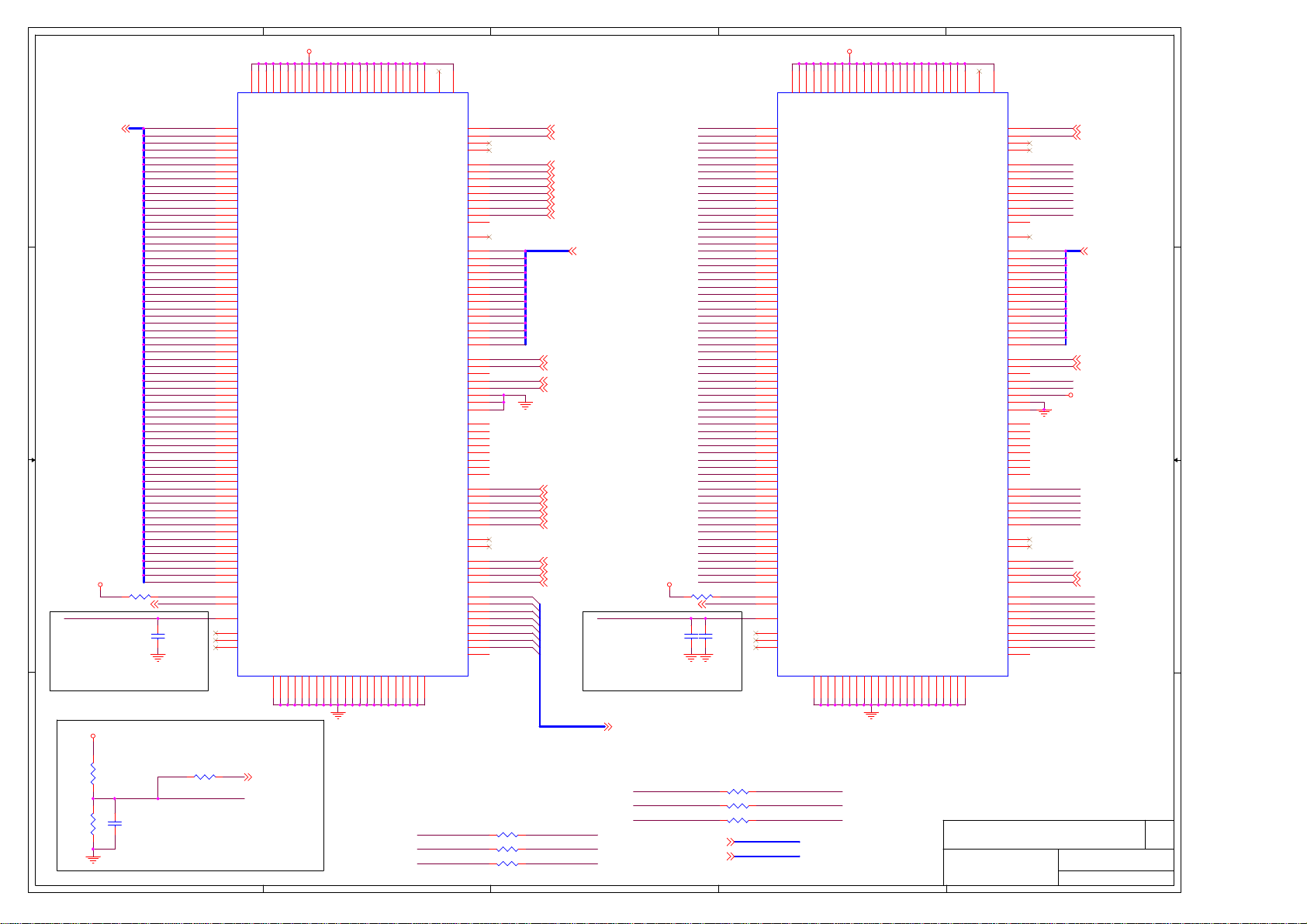

Clock Synthesizer

U22

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVCC3

CLKVDDA

C379 104P

C374 104P

C398 104P

C388 104P

C399 104P

C401 104P

C389 104P

C409 104P

ICS950402_SSOP48

I11-9504002-I02

46

VDD_46

47

VSS_47

2

VDD_2

5

VSS_5

32

VDDF

33

VSSF

9

VDD_9

10

VSS_10

16

VDD_16

15

VSS_15

19

VDD_19

20

VSS_20

29

VDD_29

30

VSS_30

27

VSS_27

38

VDD_38

39

VSS_39

35

VDD_35

34

VSS_34

43

VDDA

42

VSSA

12

NC

Only support in ICS950402

CLK_RESET#38

R315 X_10KR

PCI33_HT66_0

PCI33_HT66_1

PCI33_HT66_2

24_48MHZ/SEL

PCI33_HT66SEL

FS0/REF0

FS1/REF1

FS2/REF2

XOUT

48MHZ

PCI33_0

PCI33_1

PCI33_2

PCI33_3

PCI33_F

PCI33_4

PCI33_5

SDATA

SCLK

CPUT_0

CPUC_0

CPUT_1

CPUC_1

PCISTOP

SPREAD

2

FS0

FS1

FS2

CLKX1

CLKX2

HT_66_0

HT_66_1

HT_66_2

RN125 8P4R-22R

R457 33R

R_CPU_CLK

-R_CPU_CLK

-SEL_66

R295 22R

R667 22R

R313 22R

R332 33R

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

R645 22R

R646 22R

R341 33R

R304 10KR

R_PCICLK5

1

48

45

3

XIN

4

31

7

8

11

R_PCICLK0

13

R_PCICLK1

14

R_PCICLK2

17

R_PCICLK3

18

R_PCICLKF

23

21

R_PCICLK5 SBPCLK

22

SEL_24

28

SMBDATA1

26

SMBCLK1

25

41

40

37

36

6

24

Mode A ( ICS950402 )

44

R_PCICLK6

SB_OSC14

AC_14

APICCLK

C375 C10P50N

X1 14.318MHZ32P_D

C376 C10P50N

VCLK

RN68

GCLK_NB

8P4R-22R

GCLK_SLOT

PCICLK1

PCICLK2

PCICLK3

PCICLK4

SIOPCLK

PCICLK5R_PCICLK4

SIO48M

R326 15R1%

R323 15R1%

"-SEL_66" Freq.-Out select pin =>

Low->66MHz , Hi->33MHz .

( Internal pull-up via 100K ohm )

R604 X_10KR

R622 22R

R647 X_22R

USBCLK_SB48MHZ

SMBDATA1 8,17

SMBCLK1 8,17

CPUCLK0_H 5

CPUCLK0_L 5

CLKVCC3

PCICLK6

SB_OSC14 17

AC_14 23

APICCLK 18

USBCLK_SB 16

VCLK 18

GCLK_NB 12

GCLK_SLOT 15

PCICLK1 19

PCICLK2 19

PCICLK3 20

PCICLK4 20

SIOPCLK 27

PCICLK5 21

SBPCLK 18

SIO48M 27

PCICLK6 21

1

VCLK

GCLK_NB

GCLK_SLOT

USBCLK_SB

SIO48M

SB_OSC14

APICCLK

AC_14

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

SBPCLK

PCICLK6

SIOPCLK

CPUCLK0_H

CPUCLK0_L

VCC3

Decoupling Cap for CPU Clock

CN22

7 8

5 6

3 4

1 2

X_8P4C-10P50N

C400 X_C10P50N

C406 X_C10P50N

C370 X_C10P50N

C383 X_C10P50N

C700 X_C10P50N

CN23

7 8

5 6

3 4

1 2

X_8P4C-10P50N

C392 X_C10P50N

C394 X_C10P50N

C701 X_C10P50N

C699 X_C10P50N

Near CK-Gen in 0.5" .

C395 X_C5P50N

C393 X_C5P50N

C698 104P

ICS950402

Strapping CPU

FS0FS2FS3

1

1 1

1 1

1 1 1

0 0 0

0 0

0 0

0

0 0

0

1 0

1 1

FS1

100.90

1

1

1 1

133.90

168.00

202.00

100.20

133.50

166.70

200.40

150.00

180.00

210.00

240.00

0 0

0

270.00

233.33

0

266.67

300.00

Pin6 Pin7

HTTCLK0

1

ModeA In

PCICLK7 PCICLK8 PCICLK9 PCICLK10

ModeA In

4

B B

0 0 0 0

0 0 0

0 0 0

0 0

0 0 0

0 0

0 0

0

***

1

1 1

1 1

1 1 1

1 1

1 1 1

A A

1 1 1

1 1 1 1

ModeA ModeB

***

5

HTT

PCI

MHz

MHz

67.27 33.63

66.95

67.20

67.33

66.80

66.75

66.68

66.80

60.00

60.00

70.00

60.00

67.50

66.67

66.67

75.00

HTTCLK1 HTTCLK2 PCICLK10

MHz

33.48

33.60

33.67

33.40

33.38

33.34

33.40

33.00

33.00

35.00

30.00

33.75

33.33

33.33

37.50

Pin8 Pin11

HTTCLK1 HT TCLK2 HTTCLK3

PCICLK8 PCICLK9 PCICLK10

VCC3

FB6 X_120L800m_40_0805

CP28

X_COPPER

ICS950403 didn't support ModeC

*** => Default Setting

ModeC Pin24

01PCICLK6

***

PCI_STOP#

3

CLKVDDA

C695

X_C4.7U10Y0805

VCC3

C422

104P

For EMI

VCC3 VCC

"FS0~FS3" are all internal

pull-up via 100K ohm ..

FS0

FS2

FS1

48MHZ

"48MHZ" is "FS3" in ICS950402 ,

But not in cy28330 .

Mode B ( Set Pin 7,8,11 output

clock -> 33 or 66 MHz )

HT_66_0

"24_48MHZ/SEL" Freq.-Out select pin

=> Low->48MHz , Hi->24MHz .

( Internal pull-up via 100K ohm )

SEL_24

FB3 X_120L800m_40_0805

C421

104P

C424 X_104P

C505 X_104P

R301 10KR

R309 10KR

R302 10KR

R331 10KR

R605 10KR

R348 10KR

CP19

X_COPPER

CLKVCC3

CLKVCC3

2

C418

C4.7U10Y0805

C797

104P

C410

104P

Title

Document Number

CLKVCC3

C385

C414

X_104P

104P

ICS950403 didn't support ModeC

Mode C ( Set Pin24 -> Low = PCICLK Out )

R_PCICLKF

R360 X_10KR

R623 X_10KR

Micro Star Restricted Secret

Clock Synthesizer

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MS-6767

1

CLKVCC3

Last Revision Date:

Friday, January 17, 2003

Sheet

of

7 43

R ev

0A

5

104P

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP1

-MSWEA

C35

D D

C C

B B

DR_MD[63..0]9,10

VDD_25_SUS

R220 4.7KR

DDR_VREF

VREF routed as 40~50

mils trace wide ,

Space>25 mils

-MSWEA4,9

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

VDD_25_SUS

108

120

148

168

VDD07VDD138VDD246VDD370VDD485VDD5

VDD6

VDD7

VDD8

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

Place 104p and 1000p Cap. near the DIMM

Place near the DIMM

VDD_25_SUS

R72

1KR1%

A A

R66

1KR1%

C44

C1U16Y0805

VREF routed as 40~50 mils trace wide ,

Space>25 mils

R67 0R

DDR_VREF

5

MEM_VREF 4

4

SYSTEM MEMORY

104

112

128

136

143

156

164

172

180

15

82

184

VDDQ11

VDDQ12

PIN

VSS17

VSS18

145

152

VDDQ13

VDDQ14

VDDQ15

CK1#(CK0#)

NC(RESET#)

VSS19

VSS20

VSS21

160

176

VDDID

VDDSPD

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10_AP

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

CK0(DU)

CK0#(DU)

CK1(CK0)

CK2(DU)

CK2#(DU)

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DDR1

DIMM-184

N13-1840021-F02

MEMCLK_H5

MEMCLK_H0

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

R99 120R1%

R122 120R1%

R107 120R1%

VDDQ7

VDDQ8

VDDQ9

VDDQ10

184

DDR DIMM

SOCKET

VSS14

VSS15

VSS16

100

116

124

132

139

DIMM1 SLAVE ADDRESS

= (1010000X)B = A0

4

3

-MCS0

-MCS0 4,9

-MCS1

-MCS1 4,9

-DR_MDQS0

-DR_MDQS0 9,10

-DR_MDQS1

-DR_MDQS1 9,10

-DR_MDQS2

-DR_MDQS2 9,10

-DR_MDQS3

-DR_MDQS3 9,10

-DR_MDQS4

-DR_MDQS4 9,10

-DR_MDQS5

-DR_MDQS5 9,10

-DR_MDQS6

-DR_MDQS6 9,10

-DR_MDQS7

-DR_MDQS7 9,10

MAA[13..0]

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12 MAB12

MAA13

SMBCLK1

SMBDATA1

MEMCLK_H5

MEMCLK_L5

MEMCLK_H0

MEMCLK_L0

MEMCLK_H7

MEMCLK_L7

MCKE0

MCKE1

-MSCASA

-MSRASA

DR_DM0

DR_DM1

DR_DM2

DR_DM3

DR_DM4

DR_DM5

DR_DM6

DR_DM7

MAA[13..0] 4,9

MEMBANKA0 4,9

MEMBANKA1 4,9

SMBCLK1 7,17

SMBDATA1 7,17

MEMCLK_H5 4

MEMCLK_L5 4

MEMCLK_H0 4

MEMCLK_L0 4

MEMCLK_H7 4

MEMCLK_L7 4

MCKE0 4,9

MCKE1 4,9

-MSCASA 4,9

-MSRASA 4,9

VREF routed as 40~50

mils trace wide ,

Space>25 mils

DDR_VREF

VDD_25_SUS

-MSWEB4,9

C51

104P

R213 4.7KR

C36

X_C1000P50X

DR_MD0

DR_MD1

DR_MD2

DR_MD3

DR_MD4

DR_MD5

DR_MD6

DR_MD7

DR_MD8

DR_MD9

DR_MD10

DR_MD11

DR_MD12

DR_MD13

DR_MD14

DR_MD15

DR_MD16

DR_MD17

DR_MD18

DR_MD19

DR_MD20

DR_MD21

DR_MD22

DR_MD23

DR_MD24

DR_MD25

DR_MD26

DR_MD27

DR_MD28

DR_MD29

DR_MD30

DR_MD31

DR_MD32

DR_MD33

DR_MD34

DR_MD35

DR_MD36

DR_MD37

DR_MD38

DR_MD39

DR_MD40

DR_MD41

DR_MD42

DR_MD43

DR_MD44

DR_MD45

DR_MD46

DR_MD47

DR_MD48

DR_MD49

DR_MD50

DR_MD51

DR_MD52

DR_MD53

DR_MD54

DR_MD55

DR_MD56

DR_MD57

DR_MD58

DR_MD59

DR_MD60

DR_MD61

DR_MD62

DR_MD63

WP2

-MSWEB

2

DQ0

4

DQ1

6

DQ2

8

DQ3

94

DQ4

95

DQ5

98

DQ6

99

DQ7

12

DQ8

13

DQ9

19

DQ10

20

DQ11

105

DQ12

106

DQ13

109

DQ14

110

DQ15

23

DQ16

24

DQ17

28

DQ18

31

DQ19

114

DQ20

117

DQ21

121

DQ22

123

DQ23

33

DQ24

35

DQ25

39

DQ26

40

DQ27

126

DQ28

127

DQ29

131

DQ30

133

DQ31

53

DQ32

55

DQ33

57

DQ34

60

DQ35

146

DQ36

147

DQ37

150

DQ38

151

DQ39

61

DQ40

64

DQ41

68

DQ42

69

DQ43

153

DQ44

155

DQ45

161

DQ46

162

DQ47

72

DQ48

73

DQ49

79

DQ50

80

DQ51

165

DQ52

166

DQ53

170

DQ54

171

DQ55

83

DQ56

84

DQ57

87

DQ58

88

DQ59

174

DQ60

175

DQ61

178

DQ62

179

DQ63

90

WP(NC)

63

WE#

1

VREF

9

NC2

101

NC3

102

NC4

Place 104p and 1000p Cap. near the DIMM

DR_DM[8..0]

DR_DM[8..0] 9,10

Near U8

2

VDD_25_SUS

108

120

148

168

VDD07VDD138VDD246VDD370VDD485VDD5

VDD6

VDD7

VDD8

VSS03VSS111VSS218VSS326VSS434VSS542VSS650VSS758VSS866VSS974VSS1081VSS1189VSS1293VSS13

104

112

VDDQ022VDDQ130VDDQ254VDDQ362VDDQ477VDDQ596VDDQ6

VDDQ7

DDR DIMM

SOCKET

100

128

VDDQ8

VSS14

116

DIMM2 SLAVE ADDRESS

136

143

VDDQ9

VDDQ10

184

VSS15

VSS16

124

132

156

164

VDDQ11

VDDQ12

VSS17

VSS18

139

145

172

180

VDDQ13

PIN

VSS19

152

160

15

82

VDDID

VDDQ14

VDDQ15

A10_AP

CK0(DU)

CK0#(DU)

CK1(CK0)

CK1#(CK0#)

CK2(DU)

CK2#(DU)

NC(RESET#)

VSS20

VSS21

176

CS0#

CS1#

CS2#

CS3#

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

FETEN

A11

A12

A13

BA0

BA1

BA2

SCL

SDA

SA0

SA1

SA2

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC5

CKE0

CKE1

CAS#

RAS#

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

184

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

157

158

71

163

5

14

25

36

56

67

78

86

47

103

48

43

41

130

37

32

125

29

122

27

141

118

115

167

59

52

113

92

91

181

182

183

44

45

49

51

134

135

142

144

16

17

137

138

76

75

173

10

21

111

65

154

97

107

119

129

149

159

169

177

140

DDR2

DIMM-184

N13-1840021-F02

= (1010001X)B = A2

MEMCLK_L4

MEMCLK_L6

MEMCLK_L1

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

System Memory : DDR DIMM 1

MEMCLK_L5

MEMCLK_L7MEMCLK_H7

MEMCLK_L0

MEMCLK_H4

MEMCLK_H6

MEMCLK_H1

3

MEMCLK_L[7..0]4

MEMCLK_H[7..0]4

R97 120R1%

R121 120R1%

R106 120R1%

MEMCLK_L[7..0]

MEMCLK_H[7..0]

-MCS2

-MCS3

-DR_MDQS0

-DR_MDQS1

-DR_MDQS2

-DR_MDQS3

-DR_MDQS4

-DR_MDQS5

-DR_MDQS6

-DR_MDQS7

MAB0

MAB1

MAB2

MAB3

MAB4

MAB5

MAB6

MAB7

MAB8

MAB9

MAB10

MAB11

MAB13

MEMBAKB0

MEMBAKB1

SMBCLK1

SMBDATA1

MEMCLK_H4

MEMCLK_L4

MEMCLK_H1

MEMCLK_L1

MEMCLK_H6

MEMCLK_L6

MCKE0

MCKE1

-MSCASB

-MSRASB

MS-6767

1

DR_DM0

DR_DM1

DR_DM2

DR_DM3

DR_DM4

DR_DM5

DR_DM6

DR_DM7

Last Revision Date:

Sheet

1

-MCS2 4,9

-MCS3 4,9

MAB[13..0] 4,9

MEMBAKB0 4,9

MEMBAKB1 4,9

VDD_25_SUS

-MSCASB 4,9

-MSRASB 4,9

Friday, January 17, 2003

of

8 43

Rev

0A

5

4

3

2

1

DDR Terminations

VTT_DDR_SUS VTT_DDR_SUS

DR_MD40

DR_MD39

DR_MD35

D D

5

RN67 8P4R-47R

7 8

5 6

3 4

1 2

RN65 8P4R-47R

7 8

5 6

3 4

1 2

RN63 8P4R-47R

7 8

5 6

3 4

1 2

RN61 8P4R-47R

7 8

5 6

3 4

1 2

RN59 8P4R-47R

7 8

5 6

3 4

1 2

RN57 8P4R-47R

7 8

5 6

3 4

1 2

RN55 8P4R-47R

7 8

5 6

3 4

1 2

RN53 8P4R-47R

7 8

5 6

3 4

1 2

RN52 8P4R-47R

7 8

5 6

3 4

1 2

RN50 8P4R-47R

7 8

5 6

3 4

1 2

MEMBAKB14,8

DR_MD59

DR_MD63

DR_MD58

DR_MD62

-DR_MDQS7

DR_DM7

DR_MD57

DR_MD61

DR_MD56

DR_MD60

DR_MD51

DR_MD55

C C

B B

-MSCASA4,8

-MSRASB4,8

-MSRASA4,8

MEMBANKA04,8

MEMBAKB04,8

MEMBANKA14,8

A A

DR_MD50

DR_MD54

-DR_MDQS6

DR_DM6

MAA13

MAB13

DR_MD53

DR_MD52

DR_MD49

DR_MD48

DR_MD47

DR_MD46

DR_MD43

DR_MD42

DR_DM5

-DR_MDQS5

-MCS1

-MCS14,8

-MCS0

-MCS04,8

-MSCASA

DR_MD41

-MSWEB

-MSWEB4,8

DR_MD45

-MSRASB

DR_MD44

-MSRASA

DR_MD38

DR_MD34

DR_DM4

-DR_MDQS4

DR_MD37

DR_MD33

DR_MD36

DR_MD32

DR_MD31

DR_MD27

MAA1

MAB1

MAA2

MAB2

MAA3

MAA4

MAB4

MAA6

DR_MD30

MAB3

DR_MD26

DR_DM3

-DR_MDQS3

DR_MD25

DR_MD29

DR_MD28

MAB6

MAB5

MAA5

MAA8

4

VTT_DDR_SUS

RN48 8P4R-47R

7 8

5 6

3 4

1 2

RN46 8P4R-47R

7 8

5 6

3 4

1 2

RN45 8P4R-47R

7 8

5 6

3 4

1 2

RN37 8P4R-47R

7 8

5 6

3 4

1 2

RN33 8P4R-47R

7 8

5 6

3 4

1 2

RN30 8P4R-47R

7 8

5 6

3 4

1 2

RN29 8P4R-47R

7 8

5 6

3 4

1 2

RN28 8P4R-47R

7 8

5 6

3 4

1 2

RN26 8P4R-47R

7 8

5 6

3 4

1 2

DR_MD24

DR_MD19

DR_MD23

MAA7

DR_DM2

MAA9

MAA11

MAA12

MAB8

DR_MD22

MAB7

DR_MD18

MAB9

MAB11

DR_MD21

-DR_MDQS2

DR_MD17

MAB12

DR_MD16

DR_MD20

DR_MD11

DR_MD10

DR_MD15

DR_MD14

DR_DM1

DR_MD13

-DR_MDQS1

DR_MD12

DR_MD9

DR_MD8

DR_MD3

DR_MD7

DR_MD6

DR_MD2

DR_DM0

-DR_MDQS0

DR_MD1

DR_MD5

DR_MD4

DR_MD0

MAB10

MAB0

MAA10

MAA0

RN24 8P4R-47R

7 8

5 6

3 4

1 2

RN22 8P4R-47R

7 8

5 6

3 4

1 2

RN21 8P4R-47R

7 8

5 6

3 4

1 2

RN19 8P4R-47R

7 8

5 6

3 4

1 2

RN17 8P4R-47R

7 8

5 6

3 4

1 2

RN15 8P4R-47R

7 8

5 6

3 4

1 2

RN12 8P4R-47R

7 8

5 6

3 4

1 2

RN10 8P4R-47R

7 8

5 6

3 4

1 2

RN9 8P4R-47R

7 8

5 6

3 4

1 2

RN8 8P4R-47R

7 8

5 6

3 4

1 2

RN126 8P4R-47R

7 8

5 6

3 4

1 2

3

-MCS2

-MCS24,8

-MCS3

-MCS34,8

MAB13

MAA13

VTT_DDR_SUS

MCKE04,8

MCKE14,8

-MCS3

-MCS34,8

-MCS2

-MCS24,8

-MSCASB4,8

-MSCASB

-MSWEA

-MSWEA4,8

DR_DM[8..0]8,10

-DR_MDQS[8..0]8,10

DR_MD[63..0]8,10

MAB[13..0]4,8

MAA[13..0]4,8

R648 47R

R649 47R

RN127 8P4R-47R

7 8

5 6

3 4

1 2

DR_DM[8..0]

-DR_MDQS[8..0]

DR_MD[63..0]

MAB[13..0]

MAA[13..0]

2

-MSCASB4,8

-MSCASA4,8

-MSRASB4,8

-MSRASA4,8

MEMBAKB14,8

MEMBANKA14,8

MEMBAKB04,8

MEMBANKA04,8

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

http://www.msi.com.tw

MAB12

MAA12

MAB11

MAA11

MAB1

MAA1

MAB3

MAA3

MAB2

MAA2

MAB6

MAA6

MAB4

MAA4

MAB8

MAA8

MAA5

MAB5

MAA0

MAA10

MAB0

MAB10

-MSCASB

-MCS0

-MCS04,8

-MSCASA

-MCS1

-MCS14,8

MAA9

MAB9

MAB7

MAA7

-MSRASB

-MSRASA

-MSWEA4,8

-MSWEB4,8

-MSWEA

-MSWEB

MCKE14,8

MCKE04,8

Micro Star Restricted Secret

DDR Terminations Bank 0

MS-6767

Last Revision Date:

Friday, January 17, 2003

Sheet

1

CN21

8P4C-22P50N

CN6

8P4C-22P50N

CN11

8P4C-22P50N

CN10

8P4C-22P50N

CN8

8P4C-22P50N

CN9

8P4C-22P50N

CN15

8P4C-22P50N

CN19

8P4C-22P50N

CN7

8P4C-22P50N

CN18

8P4C-22P50N

CN17

8P4C-22P50N

CN3

8P4C-22P50N

of

9 43

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

Rev

0A

5

4

3

2

1

LAYOUT: Place on backside,

evenly spaced around VTT fill.

VDD_25_SUS

DDR Terminations

D D

RN11 8P4R-10R

MD0

1 2

MD4

3 4

MD5

5 6

MD1

7 8

RN13 8P4R-10R

DM0

1 2

3 4

MD6 DR_MD6

5 6

MD7 DR_MD7

7 8

RN16 8P4R-10R

1 2

MD8 DR_MD8

3 4

MD9 DR_MD9

5 6

7 8

RN18 8P4R-10R

-MDQS1

1 2

MD13 DR_MD13

3 4

DM1

5 6

MD14 DR_MD14

7 8

RN23 8P4R-10R

1 2

C C

B B

MD17

3 4

MD21 DR_MD21

5 6

DM2

7 8

RN20 8P4R-10R

MD10

1 2

3 4

MD20 DR_MD20

5 6

MD16 DR_MD16

7 8

RN25 8P4R-10R

1 2

MD23 DR_MD23

3 4

5 6

MD24

7 8

RN27 8P4R-10R

1 2

MD29

3 4

5 6

-MDQS3

7 8

RN32 8P4R-10R

MD26

1 2

3 4

MD27

5 6

MD31 DR_MD31

7 8

-MDQS[8..0]4

-DR_MDQS[8..0]8,9

DR_MD[63..0]8,9

MD[63..0]4

A A

DR_DM[8..0]8,9

DM[8..0]4

-MDQS[8..0]

-DR_MDQS[8..0]

DR_MD[63..0]

MD[63..0]

DR_DM[8..0]

DM[8..0]

5

DR_MD0

DR_MD4

DR_MD5

DR_MD1

DR_DM0

DR_MD2MD2

DR_MD3MD3

DR_MD12MD12

-DR_MDQS1

DR_DM1

-DR_MDQS2-MDQS2

DR_MD17

DR_DM2

DR_MD10

DR_MD11MD11

DR_MD22MD22

DR_MD19MD19

DR_MD24

DR_MD28MD28

DR_MD29

DR_MD25MD25

-DR_MDQS3

DR_MD26

DR_MD30MD30

DR_MD27

RN42 8P4R-10R

1 2

3 4

5 6

7 8

RN47 8P4R-10R

1 2

-MDQS4 -DR_MDQS4

3 4

DM4

5 6

MD34 DR_MD34

7 8

RN49 8P4R-10R

MD35 DR_MD35

1 2

MD39 DR_MD39

3 4

5 6

MD44 DR_MD44

7 8

RN51 8P4R-10R

1 2

MD41 DR_MD41

3 4

-MDQS5 -DR_MDQS5

5 6

DM5 DR_DM5

7 8

RN54 8P4R-10R

MD43

1 2

MD46 DR_MD46

3 4

MD47 DR_MD47

5 6

7 8

RN58 8P4R-10R

1 2

3 4

MD53 DR_MD53

5 6

7 8

RN60 8P4R-10R

1 2

3 4

MD50

5 6

MD55

7 8

RN62 8P4R-10R

1 2

MD56

3 4

MD61 DR_MD61

5 6

MD57 DR_MD57

7 8

RN64 8P4R-10R

DM7

1 2

-MDQS7

3 4

MD62 DR_MD62

5 6

MD58

7 8

R707 10R

MD63

R664 10R

DM3

R660 10R

MD38

R661 10R

MD42

R662 10R

MD18

R659 10R

MD51

R663 10R

-MDQS0 -DR_MDQS0

R657 10R

MD15

R658 10R

4

DR_MD32MD32

DR_MD36MD36

DR_MD33MD33

DR_MD37MD37

DR_DM4

DR_MD40MD40

DR_MD45MD45

DR_MD43

DR_MD48MD48

DR_MD49MD49

DR_MD52MD52

DR_DM6DM6

-DR_MDQS6-MDQS6

DR_MD54MD54

DR_MD50

DR_MD55

DR_MD60MD60

DR_MD56

DR_DM7

-DR_MDQS7

DR_MD58

DR_MD59MD59

DR_MD63

DR_DM3

DR_MD38

DR_MD42

DR_MD18

DR_MD51

DR_MD15

VDD_25_SUS

VDD_25_SUS VDD_25_SUS VDD_25_SUS VDD_25_SUS VDD_25_SUS

104P

104P

104P

104P

104P

104P

VTT_DDR_SUS

C49

104P

VTT_DDR_SUS

104P

C173

VTT_DDR_SUS

C0.22U16YC79

VTT_DDR_SUS

C1000P50XC190

3

VTT_DDR_SUS

C216

X_C0.22U16Y

C257

X_C0.22U16Y

C285

X_C0.22U16Y

C288

X_C0.22U16Y

C37

C53

104P

C68

C81

C85

C91

C97

LAYOUT: Place alternating caps to GND and VDD_2.5_ SUS in a single line along VTT island.

C71

C59

104P

104P

C189

C182

C90

C83

104P

104P

104P

104P

C206

C197

LAYOUT: Locate close to

Clawhammer socket.

X_C0.22U16YC61

C1U16Y0805

GND

X_C100P50NC12

X_C0.22U16YC14

GND

C67

C1U16Y0805

C0.22U16YC165

C164

VTT_DDR_SUS

C28

X_C0.22U16Y

C15

X_C0.22U16Y

C31

X_C0.22U16Y

C11

X_C0.22U16Y

C65

X_C0.22U16Y

C104

104P

C111

104P

C118

104P

C128

104P

C138

104P

C145

104P

C149

104P

C93

104P

104P

C100

104P

104P

C209

C213

C154

104P

C156

104P

C163

104P

C170

104P

C178

104P

C186

104P

C192

104P

104P

104P

104P

104P

C107

C220

C121

C114

104P

104P

C233

C226

C200

104P

C208

104P

C212

104P

C215

104P

C223

104P

C231

104P

C238

104P

104P

104P

104P

104P

C131

104P

C242

104P

C141

104P

C252

104P

C151

C146

104P

104P

C266

C263

Micro Star Restricted Secret

Title

Document Number

MICRO-STAR INT'L CO.,LTD.

No. 69, Li-De St, Jung-He City,

Taipei Hsien, Taiwan

2

http://www.msi.com.tw

LAYOUT: Locate close

to Clawhammer socket.

VTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUSVTT_DDR_SUS

C248

104P

C259

104P

C265

104P

C268

104P

C272

104P

C281

104P

104P

C155

C270

104P

C157

104P

104P

C274

DDR Terminations Bank 1

104P

C167

GND

104P

C282

GND

MS-6767

Last Revision Date:

Friday, January 17, 2003

Sheet

1

VTT_DDR_SUS

+

EC62

CD1000U6.3EL15

GND

of

10 43

Rev

0A

A

B

C

K8T400M HT Interface

D

E

Reserved

VAVDD2

C203

VDD_12_A

VAGND2

X_C0.01U50X

VAVDD2

4 4

A10

A24

A25

A26

B10

B24

B26

C10

C24

C25

C11

D10

D22

D23

D24

D11

E10

E22

E23

E24

F10

E21

VLDT

VLDT

VLDT

VLDT

F11

VLDT

F15

VLDT

F16

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

E11

VLDTE9VLDT

VLDT

B9

B23

VLDT

VLDT

VLDT

VLDT

VLDT

VLDTA9VLDT

J10

G24

G23

H22

L22

K22

N22

M22

N24

N23

R22

P22

R24

R23

H26

G26

H24

H25

K26

K24

K25

M24

M25

P26

N26

P24

P25

T26

R26

L24

L23

M26

L26

F24

F25

F13

F18

K12

K13

K14

K15

K16

K17

VLDT

RCADP15

RCADN15

J22

RCADP14

RCADN14

J24

RCADP13

J23

RCADN13

RCADP12

RCADN12

RCADP11

RCADN11

RCADP10

RCADN10

RCADP9

RCADN9

RCADP8

RCADN8

RCADP7

RCADN7

RCADP6

RCADN6

RCADP5

J26

RCADN5

RCADP4

RCADN4

RCADP3

RCADN3

RCADP2

RCADN2

RCADP1

RCADN1

RCADP0

RCADN0

RCLKP1

RCLKN1

RCLKP0

RCLKN0

RCTLP

RCTLN

J18

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

From Claw Hammer

CADON[15:0]4

CADOP[15:0]4

3 3

2 2

CADOP15

CADOP14

CADOP13

CADOP12

CADOP11

CADOP10

CADOP9

CADOP8

CADOP7

CADOP6

CADOP5

CADOP4

CADOP3

CADOP2

CADOP1

CADOP0

CLKOP14

CLKON14

CLKOP04

CLKON04

CTLOP04

CTLON04

CADON15

CADON14

CADON13

CADON12

CADON11

CADON10

CADON9

CADON8

CADON7

CADON6

CADON5

CADON4

CADON3

CADON2

CADON1

CADON0

CLKOP1

CLKON1

CLKOP0

CLKON0

CTLOP0

CTLON0

VLDT

VLDT

B25

VLDT

C9

VLDT

VLDT

VLDT

VLDT

C23

VLDT

VLDT

VLDT

VLDTD9VLDT

F19

F20

VLDT

F21

VLDT

F22

VLDT

VLDT

F23

G21

VLDT

G22

VLDT

H21

VLDT

VLDT

J11

J12

VLDT

J13

VLDT

VLDT

J14

J15

VLDT

VLDT

H14

H13

NC_H13

H17

H18

NC_H14

NC_H17

TCADP15

TCADN15

TCADP14

TCADN14

TCADP13

TCADN13

TCADP12

TCADN12

TCADP11

TCADN11

TCADP10

TCADN10

TCADP9

TCADN9

TCADP8

TCADN8

TCADP7

TCADN7

TCADP6

TCADN6

TCADP5

TCADN5

TCADP4

TCADN4

TCADP3

TCADN3

TCADP2

TCADN2

TCADP1

TCADN1

TCADP0

TCADN0

TCLKP1

TCLKN1

TCLKP0

TCLKN0

RNCOMP

RTCOMP

RPCOMP

LDTRST

LDTSTOP

NC_H18

TCTLP

TCTLN

C22

U10A

VIA-K8T400M-VT8385

B01-0838505-V01

AVDD2

E20

D21

D19

C19

E18

E19

D17

C17

D15

C15

E14

E15

D13

C13

E12

E13

B20

C20

A19

A20

B18

C18

A17

A18

A15

A16

B14

C14

A13

A14

B12

C12

E16

E17

B16

C16

A21

A22

D26

C26

D25

B11

A12

CADIN15

CADIN14

CADIN13

CADIN12

CADIN11

CADIN10

CADIN9

CADIN8

CADIN7

CADIN6

CADIN5

CADIN4

CADIN3

CADIN2

CADIN1

CADIN0

CLKIP1

CLKIN1

CLKIP0

CLKIN0

CTLIP0

CTLIN0

PNCOMP

RTCOMP

RPCOMP

-LDTRST

-LDTSTOP

To Claw Hammer

CADIP15

CADIP14

CADIP13

CADIP12

CADIP11

CADIP10

CADIP9

CADIP8

CADIP7

CADIP6

CADIP5

CADIP4

CADIP3

CADIP2

CADIP1

CADIP0

CLKIP1 4

CLKIN1 4

CLKIP0 4

CLKIN0 4

CTLIP0 4

CTLIN0 4

-LDTRST 37

-LDTSTOP 5,18

CADIN[15:0] 4

CADIP[15:0] 4

PNCOMP

RTCOMP

RPCOMP

C205 104P

C204 104P

Around NB

C641 X_104P/BACK

C644 X_104P/BACK

Decoupling capacitors

at NB BGA Area (On

Solder Layer)

R152 49.9R1%

R140 100R1%

R151 49.9R1%

VDD_12_A

VDD_12_A

VDD_12_A

NC_K8K8NC_L8

L8

J19

NC_N19

NC_J19

P19

N19

NC_P19

P2

NC_P3P3NC_P2

NC_P4

P4

AVSS2

C21

VDD_12_A

J16

VLDT

J17

VLDT

K18

VLDT

K21

VLDT

L18

VLDT

L21

VLDT

M18

VLDT

N18

VLDT

N21

VLDT

P18

VLDT

P21

VLDT

R18

VLDT

T18

VLDT

VLDT

T21

T22

VLDT

T23

VLDT

T24

VLDT

T25

VLDT

U18

VLDT

VLDT

U21

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

VLDT

V21

V22

V23

V24

V25

U22

U23

U24

U25

V26

U26

VLDT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M10

VSS

T10

P10

N10

R10

U10

VSS

L10

K10

K11

VAGND2

1 1

Title

Size Document Number Rev

C

A

B

C

D

Date: Sheet of

<OrgName>

NORTH BRIDGE K8T400M/VER:0.4 (HT)

MS-6767

11 43Friday, January 17, 2003

E

0A

A

K8T400M AGP 8X ,V-Link, Misc. Control

VCC2_5

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

W14

W13

W12

AF18

AD18

AE18

AF17

AD17

AD16

AE16

AF16

AF14

AD14

AD13

AE13

AF13

AD12

AF12

AE12

AD10

AE10

AF10

AD9

AF9

AF8

AE9

AD8

AF6

AD7

AE6

AD5

AF5

AF4

AE4

AD4

AC2

AC3

AD1

AD2

AF2

AD3

AE3

AF3

AD15

AF11

AD11

AC7

AE15

AF15

AE7

AF7

AF1

AE1

AC5

AC4

AC9

AC10

AC14

AC11

AC12

AC16

AD6

AC1

AA3

AC15

AA2

AA1

AB1

A11

AC13

AC6

4 4

GAD[31:0]15

3 3

SBA015

SBA115

SBA215

SBA315

SBA415

SBA515

SBA615

SBA715

GC/BE#015

GC/BE#115

GC/BE#215

GC/BE#315

AD_STBF015

AD_STBS015

AD_STBF115

AD_STBS115

SB_STBF15

2 2

SB_STBS15

GFRAME15

GIRDY15

GTRDY15

GDEVSEL15

GSTOP15

GSERR15

AGP8XDET#15

GCLK_NB7

AGPVREF_GC15

1 1

AD_STBF0

AD_STBS0

AD_STBF1

AD_STBS1

SB_STBF

SB_STBS

DBIH

DBIH15

DBIL

DBIL15

GPAR15

RBF15

WBF15

GREQ15

GGNT15

ST015

ST115

ST215

AGPPCOMP

AGPNCOMP AGPPCOMP

AGPVREF_GC