Page 1

8

7

6

5

4

3

2

1

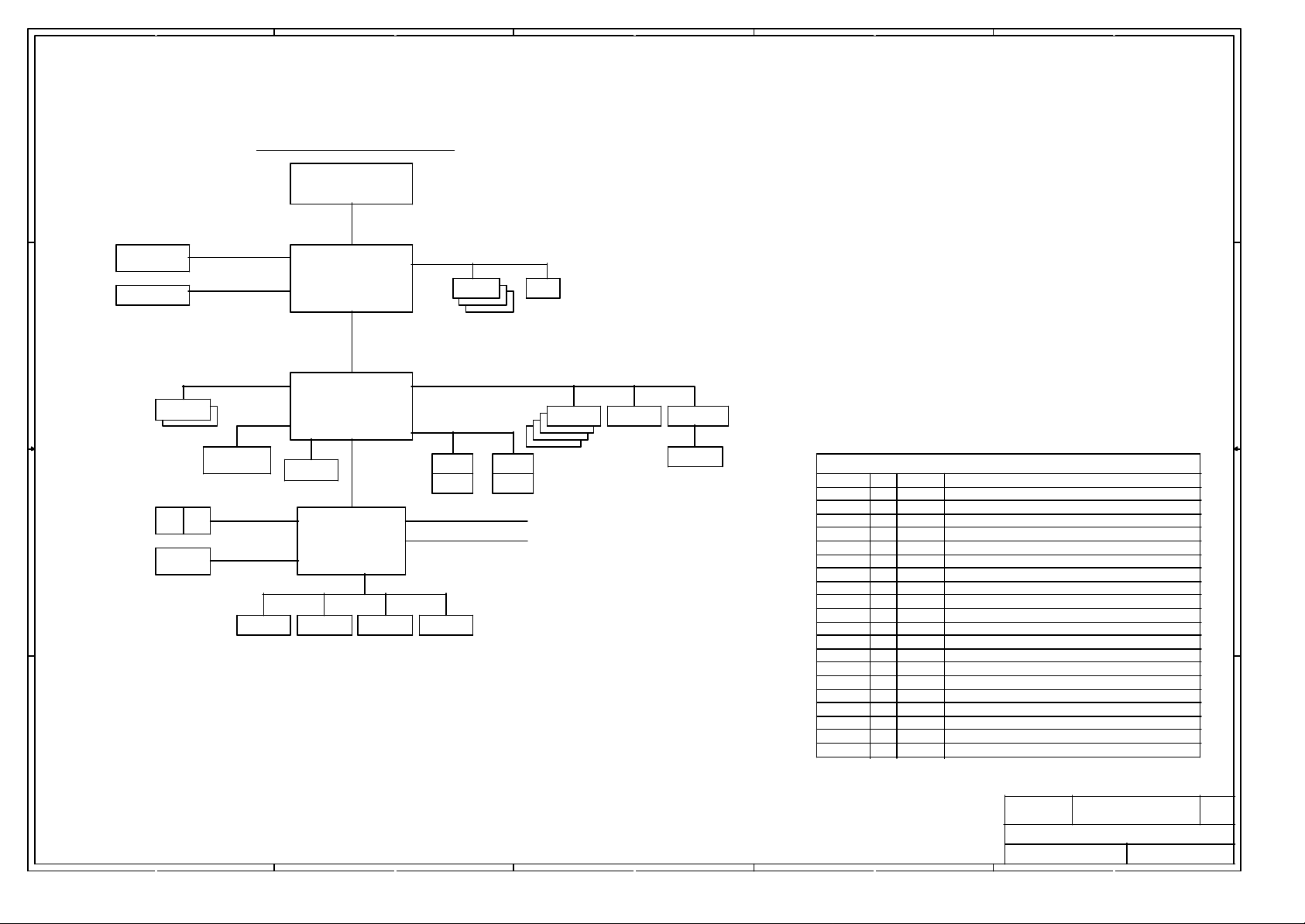

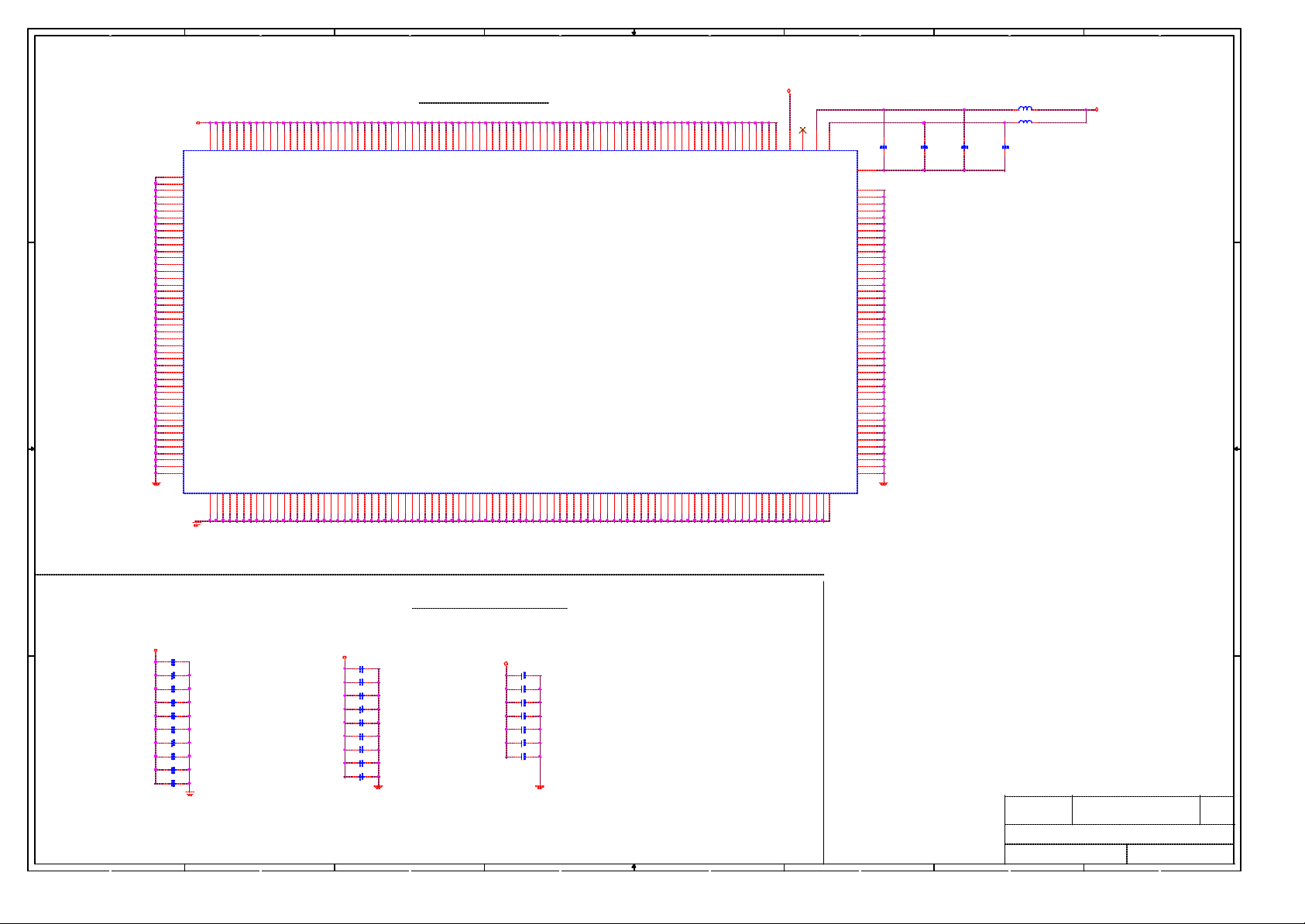

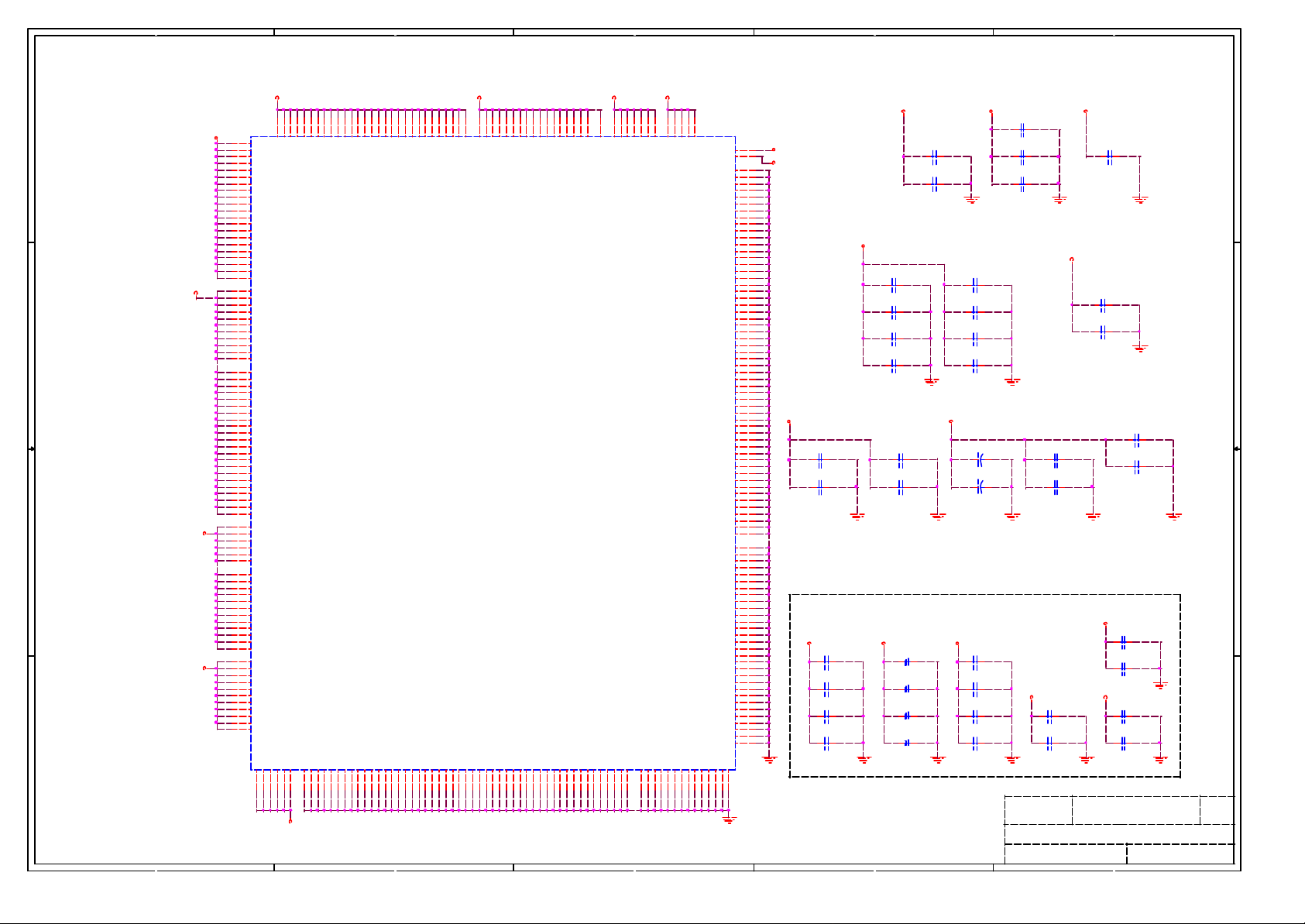

Cover Sheet

Block Diagram

D D

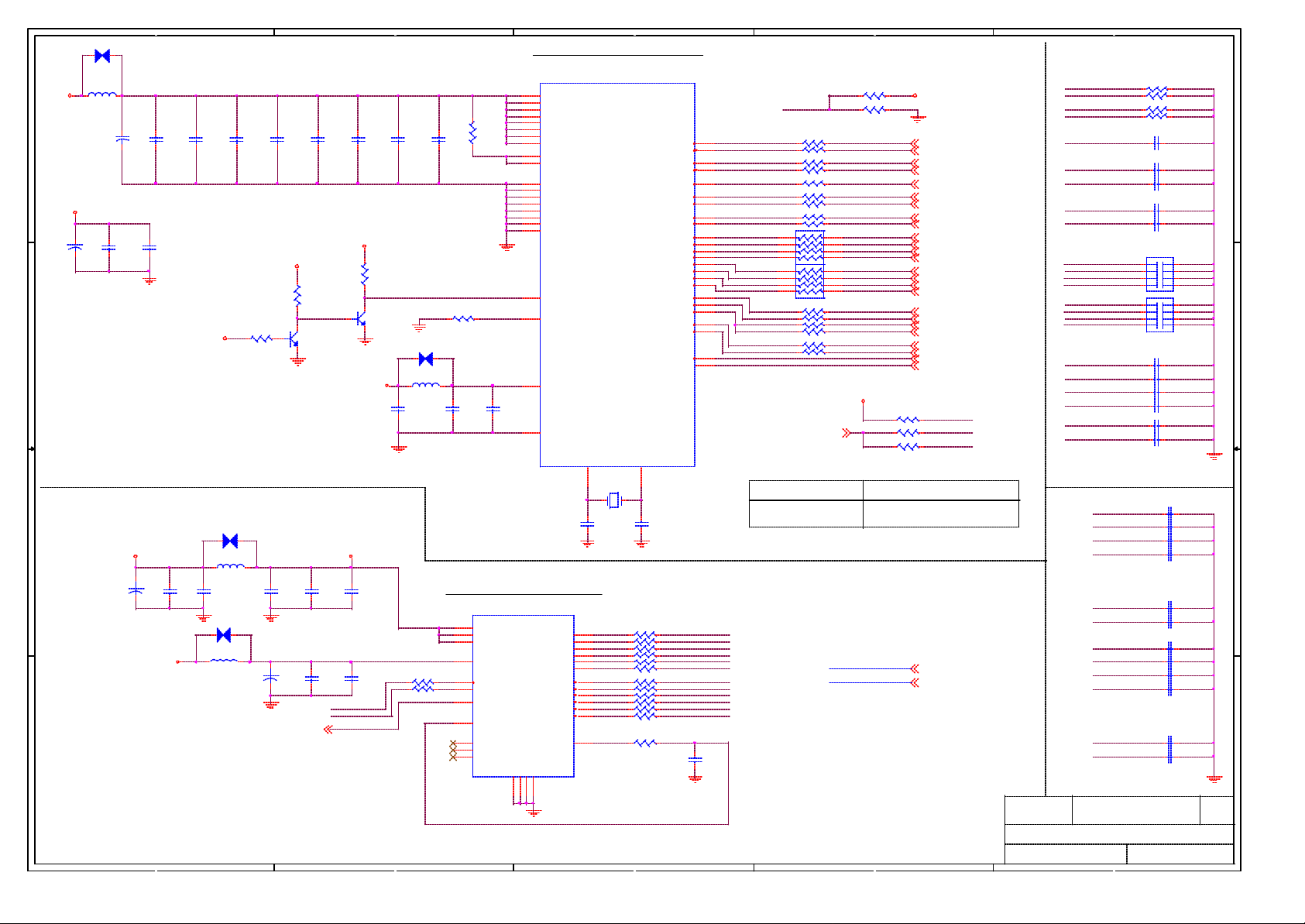

MAIN CLOCK GEN & DDR CLOCK BUFFER

mPGA478-B INTEL CPU Sockets

MS-6564

SIS 645/650 CHIPSET

VERSION:10B

07/22/2002 Update

Willamette/Northwood 478pin mPGA-B Processor Schematics

SIS 645/650 NORTH BRIDGE

DDR SLOT 1,2

DDR SLOT 3,TERMINATOR

SIS 961A SOUTH BRIDGE

AGP SLOT

CPU:

C C

Willamette/Northwood mPGA-478B Processor

PCI SLOTS 1,2,3

PCI SLOTS 4,VIA 1394

System Chipset:

SIS 645/650 (North Bridge)

USB,KB MS PS/2 CONNECT

IDE CONNECTOR

1

2

3

4 - 5

6 - 9

10

11

12 - 14

15

16

17

18

19

+961A (South Bridge)

Audio Section-CMI8738

On Board Chipset:

LPC Super I/O -- W83697HF

Clock Generation -- ICS952001AF

B B

PCI SOUND -- C-MEDIA CMI8738MX

PCI 1394 --VIA VT6306

6 CHANNEL CONTROL

Audio Connector/Game/Amp

FAN & PROTECTION DIODE

LPC I/O(W83697HF)

PARALLEL & SERIAL PORT

20

21

22

23

24

25

Expansion Slots:

AGP2.0 SLOT * 1

PCI2.2 SLOT* 4

VRM 9.X

ACPI CONTROLLER

ATX POWER CON & VGA CON

FRONT PANEL

Decoupling Capacitor

26

27

28

29

30

31Packing

A A

8

7

6

5

History

32

Title

Micro-Star

Document Number

Last Revision Date:

4

3

Wednesday, September 11, 2002

2

MS-6564

Cover Sheet

Sheet of

1

Rev

10A

1 32

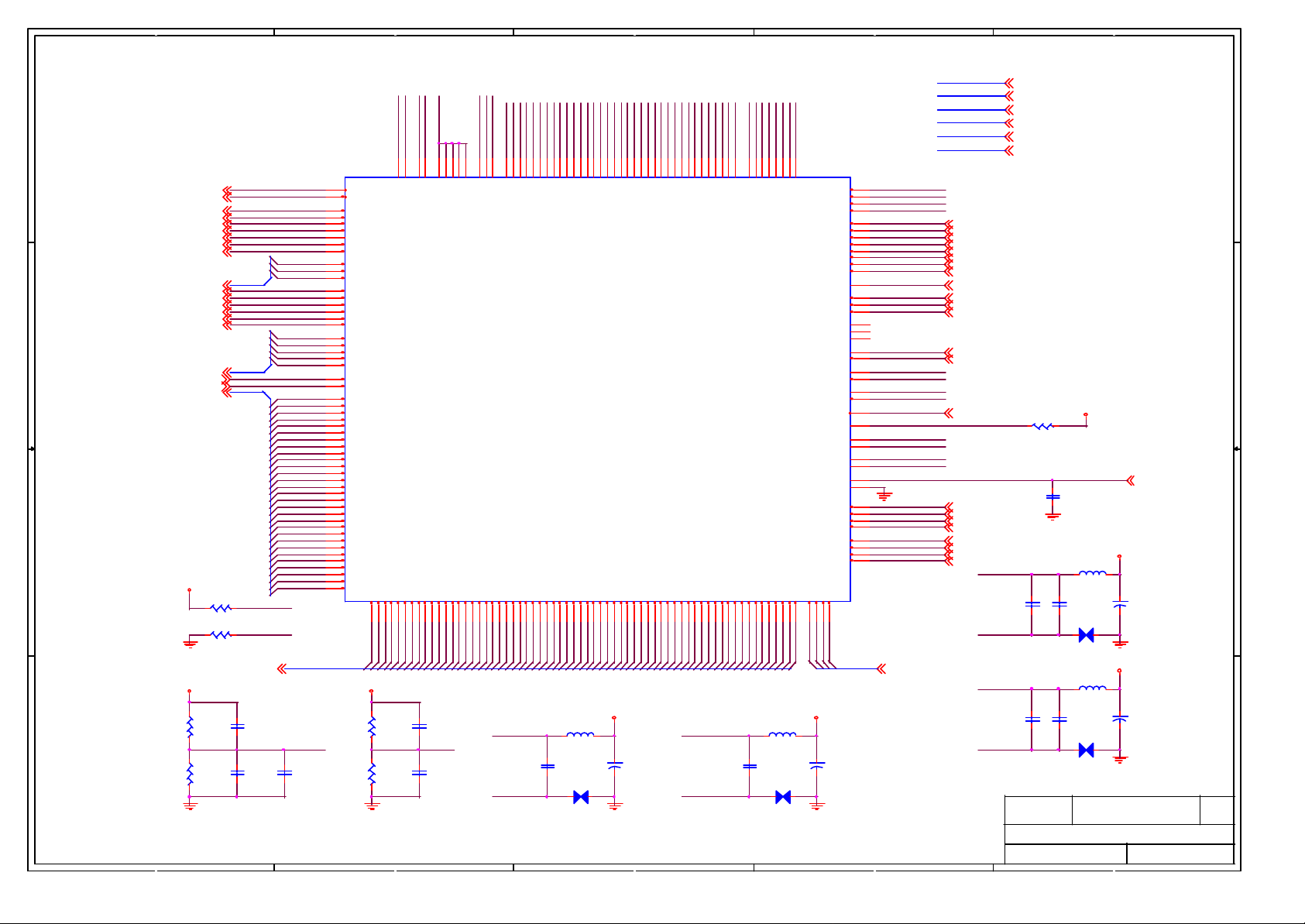

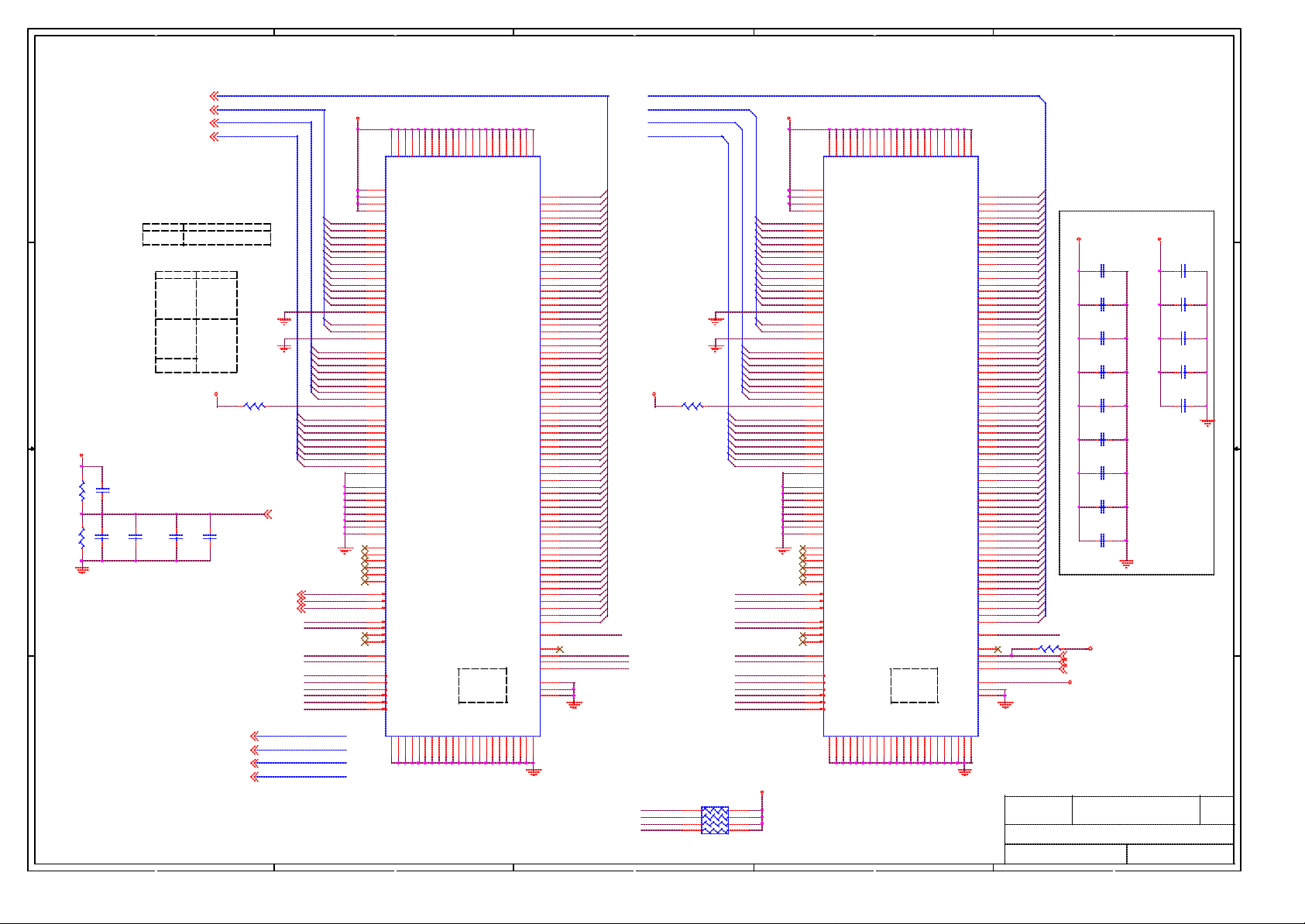

Page 2

5

4

3

2

1

D D

System Block Diagram

SOCKET-478

Support Dual Monitor

VGA

D-SUB

VGA Connector

C C

IDE 1

FAN1FAN

B B

A A

AGP SLOT

VGA CONNECTOR DIMM 1

SiS961

GPIOs

Legacy

ROM

PS/2

KEYBOARD

/MOUSE

FAN CONTROL

2

IR/CIR SERIAL PARALLEL FLOPPY

Host Bus

SIS645/650

VGA

HyperZip

512 MB/S

LPC Bus

LPC Super I/O

DDR SDRAM

USB 0

USB 1

VOLTAGE MONITOR

TEMPERATURE MONITOR

Rtt

SSTL-2 Termination

(Only for DDR)

Support Max to six-PCI Devices

PCI SLOT 1

USB 2

USB 3

1394

VIA-VT6306

Audio

Section-CMI8738

GAME/MIDI

GPIO Table on SIS961

GPIO_0

GPIO_1

GPIO_3

GPIO_4

GPIO_5 I/O

GPIO_6

GPI_7

GPI_8 RESUME

GPI_9

GPI_10

GPIO_11

GPIO_13

GPIO_14

GPIO_15

GPIO_16

GPIO_17

GPIO_18

GPIO_19

GPIO_20

I/O

MAIN

I/O

MAIN

I/OGPIO_2

MAIN

I/O

MAIN

I/O

MAIN

MAIN

I/O

RESUME

I/O

I

I

RESUME

I

RESUME

I/O

RESUME

RESUME

I/O

RESUME

I/O

RESUME

I/O

I/O

RESUME

I/O

RESUME

I/O

RESUME

I/O RESUME

I/O

RESUME SMBCLK

RESUME

I/O

Pull-Up

Pull-Down

THERM#

EXTSMI#

Pull-UpMAIN

PREQ#5(Pull-Up)

PGNT#5(Pull-Up)

Pull-Up

RING

RESERVED

RESERVED

RESERVED

Pull-UpGPIO_12

Flash Rom protection H: Disable, L: Enable

LAN_WAKE#

KBDAT

KBCLK

MSDAT

MSCLK

SMBDAT

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, September 11, 2002

MS-6564

System Block Diagram

Sheet of

1

Rev

10A

2 32

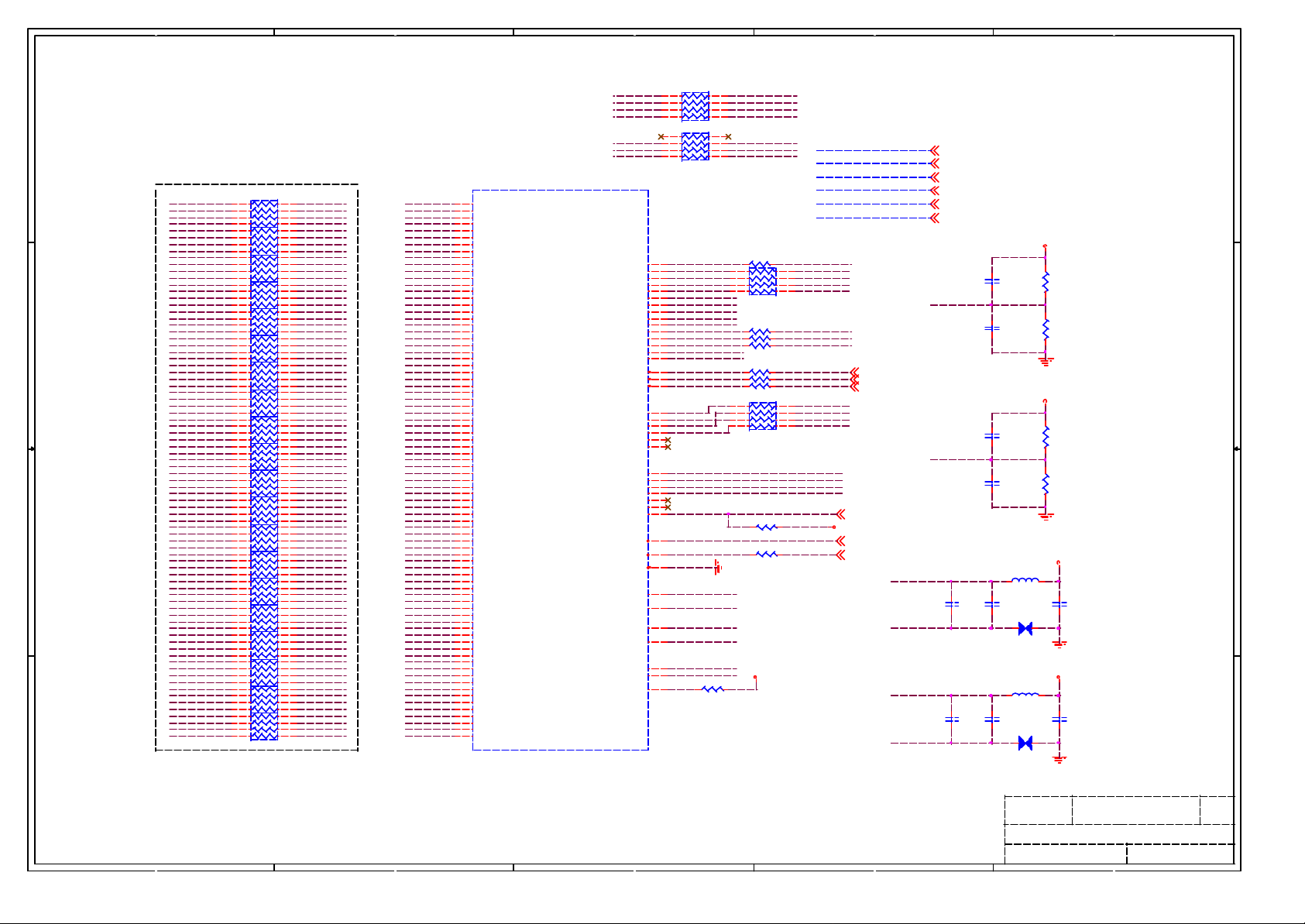

Page 3

CE5

X_10u

CB120

0.1u

VCC2.5V

+

CE10

X_10u

5

CB83

1000p

VCC2.5V

5

CB84

0.1u

VCCP

CP34 X_COPPER

CB203

0.1u

CP33 X_COPPER

CB85

0.1u

R259 10K

L50

X_80-0805

CB204

0.01u

L49

X_80-0805

CB88

CB86

0.1u

0.1u

VCC3

R226

10K

Q29

NPN-MBT3904LT1-S-SOT23

CB195

0.1u

+

CE11

X_10u

FWDSDCLKO7

CB98

0.1u

NPN-MBT3904LT1-S-SOT23

CBVDD

CB190

0.1u

CB202

0.1u

SMBCLK

SMBDAT

FWDSDCLKO

CP20

X_COPPER

L31

VCC3

X_80-0805

D D

VCC3

CE4

X_10u

C C

B B

A A

VCC3

CB200

0.1u

CB198

0.01u

CB87

Q30

VCC3

0.1u

R215

10K

4

CB112

0.1u

R213 475RST

CP28 X_COPPER

L38

X_80-0805

CB118

0.1u

CBVDD

R343

R342 0

0

4

Main Clock Generato r

U14

ICS-ICS952001AF-SSOP48

1

VDDREF

11

VDDZ

13

VDDPCI

19

VDDPCI

28

VDD48

CB100

1000p

29

VDDAGP

42

VDDCPU

48

VDDSD

12

PCI_STOP#

45

CPU_STOP#

5

VSSREF

8

VSSZ

18

VSSPCI

24

VSSPCI

25

VSS48

32

VSSAGP

41

VSSCPU

46

VSSSD

33

PD#/VTT_PWRGD

38

IREF

36

VDDA

37

VSSA

CB108

0.1u

CB115

0.1u

R190

10K

Clock Buffer (DDR)

U20

ICS-ICS93722BF-SSOP28

3

VDD

12

VDD

23

VDD

10

AVDD

7

SCLK

22

SDATA

8

CLK_IN

20

FB_IN

9

NC

18

NC

21

NC

6

GND

111528

GND

GND

GND

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK#0

CLK#1

CLK#2

CLK#3

CLK#4

CLK#5

FB_OUT

XIN

6

Y2

14M-16pf-HC49S-D

C147

10p

R327

2

R336

4

13

R361

17

R362 0

24

R337 0

R330

26

R323

1

R340 0

5

14

R375 0

R376

16

R334

25

R324

27

R355

19

3

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

AGPCLK0

AGPCLK1

PCICLK_F0/FS3

PCICLK_F1/FS4

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

REF0/FS0

REF1/FS1

REF2/FS2

24_48M/MULTISEL

XOUT

7

C148

10p

0

0

0

0

0

0

0

0

22

3

SDCLK

ZCLK0

ZCLK1

48M

SCLK

SDATA

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK8

DDRCLK7

DDRCLK-0

DDRCLK-1

DDRCLK-2

DDRCLK-3

DDRCLK-8

DDRCLK-7

MULTISEL internal Pull-Up 120K

MULTISEL

40

39

44

43

47

31

30

9

10

FS3 96XPCLK

14

FS4 SIOPCLK

15

16

17

20

21

22

23

FS0

2

FS1

3

FS2

4

27

26

MULTISEL

35

34

R209

R212 33

R198

R201

R194 22

R217

R221

R206 22

R208 22

RN23 33

RN24 33

R189

R195 33

R191 33

R192

R229

R242 22

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

33

33

33

22

22

33

33

22

BSEL04

F0~F4 internal Pull-Down 120K

FS4 FS3 FS2 FS1 FS0 CPU SDRAM ZCLK AGP PCI

0 0 0 0

0 01111

FB_OUT

C226

10p

2

R249 X_4.7K

R250 X_4.7K

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

PCICLK1

AUDPCLK

PCICLK4

PCICLK3

PCICLK2

PCICLK1394

REFCLK0

AUDIO_14

REFCLK1

APICCLK

UCLK48M

SIO24M

SMBCLK

SMBDAT

VCC3

R188 2.7K

R200

R248

100 100

DDRCLK[0..8]

DDRCLK-[0..8]

2

VCC3

CPUCLK0 4

CPUCLK-0 4

CPUCLK1 6

CPUCLK-1 6

SDCLK 7

AGPCLK0 6

AGPCLK1 15

ZCLK0 8

ZCLK1 12

96XPCLK 12

SIOPCLK 24

PCICLK1 16

AUDPCLK 20

PCICLK4 17

PCICLK3 16

PCICLK2 16

PCICLK1394 17

REFCLK0 8

AUDIO_14 20

REFCLK1 13

APICCLK 13

UCLK48M 14

SIO24M 24

SMBCLK 10,13,27

SMBDAT 10,13,27

FS0

FS2

X_10K

FS4

X_10K

6666666633

100133

DDRCLK[0..8] 10

DDRCLK-[0..8] 10

33

Micro-Star

Document Number

Last Revision Date:

Wednesday, September 11, 2002

1

CPUCLK0

CPUCLK-0

CPUCLK1

CPUCLK-1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

AUDPCLK

PCICLK1

SIOPCLK

96XPCLK

PCICLK1394

PCICLK2

PCICLK3

PCICLK4

APICCLK

REFCLK0

REFCLK1

AUDIO_14

UCLK48M

SIO24M

DDRCLK0

DDRCLK1

DDRCLK2

DDRCLK3

DDRCLK8

DDRCLK7

DDRCLK-0

DDRCLK-1

DDRCLK-2

DDRCLK-3

DDRCLK-8

DDRCLK-7

Title

R207 49.9RST

R210

R199

R202 49.9RST

C151 X_10p

C165 X_10p

C167 X_10p

C156 X_10p

C159 X_10p

CN14 X_10p

1 2

3 4

5 6

7 8

CN15 X_10p1 2

3 4

5 6

7 8

C150 X_10p

C139 X_10p

C149 X_10p

C153 X_10p

C172 X_10p

C176 X_10p

C213 X_10p

C218 X_10p

C225 X_10p

C229 X_10p

C219 X_10p

C214 X_10p

C208 X_10p

C222 X_10p

C228 X_10p

C230 X_10p

C217 X_10p

C210 X_10p

MS-6564

49.9RST

49.9RST

MAIN CLOCK GEN & BUFFER

Sheet of

1

3 32

Rev

10A

Page 4

8

7

6

5

4

3

2

1

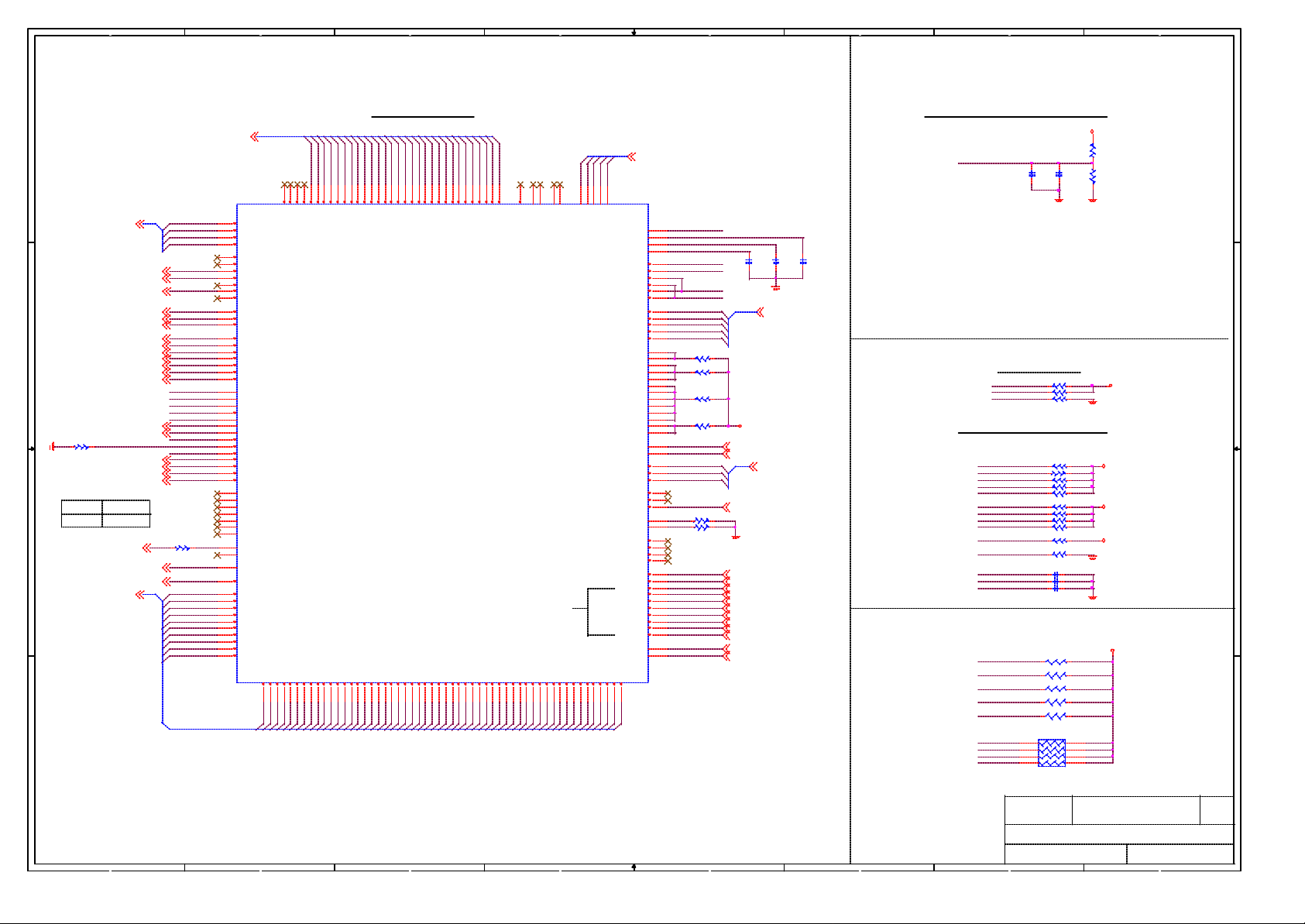

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

VCCP

C126

C124

220p

1u

R167 39

R168 75

R172 27

R171 62

R145 62

R205 220

R159 49.9RST

R203 62

R139 49.9RST

R142 49.9RST

R157 49.9RST

R152 49.9RST

R204 150

R170 680

X_1000PC121

X_1000PC123

X_0.022uC122

RN20

56

Title

R156

49.9RST

R160

100RST

VCCP

VCCP

VCCP

VCCP

VCCP

MS-6564

mPGA478 CPU-1

Sheet of

4 32

1

Rev

10A

HDBI#0

HDBI#1

HDBI#2

HDBI#3

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

CPU_TMPA

THERMTRIP#

PROCHOT#

IGNNE#

SMI#

A20M#

CPUSLP#

CPU_GD

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HA#[3..31]6

G25

AC3

AF26

AB26

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

U10A

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

HD#53

HA#22

HA#25

HA#23

HA#26

HA#27

HA#28

HA#30

HA#29

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

U21

V25

U23

U24

U26

T23

T22

T25

T26

R24

R25

P24

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#52

HD#51

HD#50

HD#48

HD#49

A25#

D40#

R21

N25

HD#40

HA#24

A24#

D39#

N26

HD#39

HD#38

A23#

D38#

M26

HD#37

HA#21

A22#

D37#

N23

HD#36

HA#20

A21#

D36#

M24

HD#35

HA#19

A20#

D35#

P21

HD#34

HA#18

A19#

D34#

N22

HD#33

HA#17

A18#

D33#

M23

HD#32

HA#16

A17#

D32#

H25

HD#31

HA#15

A16#

D31#

K23

HD#30

HA#14

A15#

D30#

J24

HD#29

HA#13

A14#

D29#

L22

HD#28

HA#12

A13#

D28#

M21

HD#27

HA#11

A12#

D27#

H24

HD#26

HA#10

A11#

D26#

G26

HD#25

HA#9

A10#

D25#

L21

HD#24

A9#

D24#

HA#8

A8#

D23#

D26

HD#23

HA#7

A7#

D22#

F26

HD#22

HA#6

A6#

D21#

E25

HD#21

HA#5

A5#

D20#

F24

F23

HD#20

HA#4

HA#3

A4#

D19#

G23

HD#19

HD#18

AE25A5A4

A3#

Differential

Host Data

Strobes

D18#

D17#

D16#

E24

H22

D25

HD#16

HD#15

HD#17

DBR#

D15#

J21

HD#14

D14#

D23

HD#13

AD26

AC26

ITP_CLK1

VCC_SENSE

VSS_SENSE

D13#

D12#

D11#

D10#

C26

H21

G22

B25

HD#10

HD#11

HD#12

ITP_CLK0

D9#

D8#

C24

HD#8

HD#9

C23

HD#7

D7#

VID4

AE1

B24

HD#6

VID3

AE2

VID4#

D6#

D22

HD#5

VID2

AE3

VID3#

D5#

C21

HD#4

VID1

AE4

VID2#

D4#

A25

HD#3

VID0

AE5

VID1#

VID0#

LINT1/NMI

LINT0/INTR

D3#

D2#

A23

B22

HD#2

HD#1

VID[0..4] 26

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

D1#

D0#

PGA-S478-F02

B21

HD#0

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R144 62

R164 62

R140 62

R133 62

RS#2

RS#1

RS#0

R177 49.9RST

R176 49.9RST

C128

220p

HREQ#[0..4] 6

VCCP

CPUCLK-0 3

CPUCLK0 3

RS#[0..2] 6

HBR#0 6

* Short trace

HADSTB#1 6

HADSTB#0 6

HDSTBP#3 6

HDSTBP#2 6

HDSTBP#1 6

HDSTBP#0 6

HDSTBN#3 6

HDSTBN#2 6

HDSTBN#1 6

HDSTBN#0 6

NMI 13

INTR 13

C129

220p

C125

220p

Length < 1.5inch.

GTLREF3

2/3*Vccp

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

ITP_TDO

ITP_TCK

CPU STRAPPING RESISTORS

CLOSED TO SOCKET478

PROCHOT#

CPU_GD

HBR#0

CPURST#

THERMTRIP#

BPM#0

BPM#1

BPM#4

BPM#5

ITP_TDI

ITP_TRST#

CPU_GD

CPURST#CPURST#

CPUSLP#

CLOSED TO SOCKET478

STPCLK#

R169 56

CPUSLP#

SMI#

HINIT#

FERR#

A20M#

INTR

NMI

IGNNE#

R153 56

R158 56

R173 56

R165 62

7 8

5 6

3 4

1 2

NA for S3

D D

HDBI#[0..3]6

FERR#13

STPCLK#13

HINIT#13

HDBSY#6

HDRDY#6

HTRDY#6

HADS#6

HD#[0..63]6

HDEFER#6

CPU_TMPA24

VTIN_GND24

CPUSLP#13

FSB

100 MHz

133 MHz

BSEL03

CPU_GD6

CPURST#6

HLOCK#6

HBNR#6

HIT#6

HITM#6

HBPRI#6

IGNNE#13

SMI#13

A20M#13

R253 X_0

C C

Trace : 10

mil width

10mil

space

R132 X_33

BSEL0

0

1

B B

A A

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Wednesday, September 11, 2002

2

Page 5

8

7

6

5

4

3

2

1

CPU VOLTAGE BLOCK

VCCP

D D

C C

D10

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

U10B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

AA1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AA4

VSS

AA7

VSS

AA9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AB3

VSS

AB6

VSS

AB8

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD4

AD23

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

E13

E15

E17

E19

E23

E7E9F10

E4

E26

E20E8F11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

F12

F14

F16

F18F2F22

F25F5F8

VCC_VID

PLL_VCCBUS

PLL_VCCCORE

AF4

VSS

H26H4J2

AF3

VCC-VID

VSS

VSS

AD20

AE23

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

VSS

J22

J25J5K21

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-F02

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

C116

X_10u-1206

C117

X_10u-1206

CPUVSSA

F13

F15

F17

F19

F9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

G21G6G24

G3H1H23

L23 4.7uH100mA-1206

L24 4.7uH100mA-1206

C112

22u-1206

C113

22u-1206

VCCP

B B

CPU DECOUPLING CAPACITORS

VCCP

A A

CB97

10u-1206

CB96

10u-1206

CB95

10u-1206

CB94

10u-1206

CB93

10u-1206

CB92

10u-1206

CB91

10u-1206

CB90

10u-1206

CB89

10u-1206

CB29

10u-1206

PLACE CAPS WITHIN CPU CAVITY

8

7

VCCP

CB45

10u-1206

CB28

10u-1206

CB44

10u-1206

CB43

10u-1206

CB42

10u-1206

CB26

10u-1206

CB41

10u-1206

CB27

10u-1206

CB71

10u-1206

VCCP

6

CB70

10u-1206

CB69

10u-1206

CB68

10u-1206

CB78

10u-1206

CB77

10u-1206

CB76

10u-1206

CB75

10u-1206

5

Title

Micro-Star

Document Number

Last Revision Date:

4

3

Wednesday, September 11, 2002

2

MS-6564

mPGA478 CPU-2

Sheet of

1

Rev

10A

5 32

Page 6

5

4

3

2

1

AAD[0..31]

SBA[0..7]

ACBE#1

ACBE#0HDEFER#

ADEVSEL#

APAR

ADSTB0

ADSTB1

ADSTB#1

AGPCLK0

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AVREFGC

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

ACBE#[0..3]

ST[0..2]

ADSTB[0..1]

ADSTB#[0..1]

AREQ# 15

AGNT# 15

AFRAME# 15

AIRDY# 15

ATRDY# 15

ADEVSEL# 15

ASERR# 15

ASTOP# 15

APAR 15

RBF# 15

WBF# 15

PIPE# 15

SBSTB 15

SBSTB# 15

AGPCLK0 3

HDSTBN#3 4

HDSTBN#2 4

HDSTBN#1 4

HDSTBN#0 4

HDSTBP#3 4

HDSTBP#2 4

HDSTBP#1 4

HDSTBP#0 4

C1XAVSS

C1XAVDD

C4XAVSS

C4XAVDD

HVREF

HPCOMP

HNCOMP

HNCVREF

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

AAD7

AAD8

AAD9

AAD10

AAD11

AAD12

AAD13

AAD14

AAD15

AAD16

AAD17

AAD18

AAD19

AAD20

AAD21

AAD22

AAD23

AAD24

AAD25

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

SBA7

SBA6

SBA5

SBA4

SBA3

SBA2

SBA1

SBA0

D D

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AREQ#

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

RBF#

WBF#

PIPE#

AGP8XDET

ADBIH

ADBIL

SB_STB

SB_STB#

AD_STB0

AD_STB#0

AD_STB1

AD_STB#1

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

DBI#3

DBI#2

DBI#1

DBI#0

A27

H27

R25

HDBI#2

HDBI#1

HDBI#0

CT19

X_10u-0805

U12A

F6

F3

H4

K5

C9

A6

G2

G1

G3

G4

H5

H1

H3

E8

F8

D9

D10

B3

C4

B5

A4

K1

L1

C1

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

SIS-SIS650GX-VA1

HDBI#[0..3] 4

2

AH25

AJ25

AH27

AJ27

U21

T21

P21

N21

J17

B20

B19

A19A7F9B7M6M5M4L3L6L4K6L2K3J3K4J2J6J4J1H6F4F1G6E3F5E2E4E1D3D4C2F7C3E6B2D5D6A3D7C5A5C6D8

AJ26

CPUCLK13

CPUCLK-13

HDEFER#4

HLOCK#4

HTRDY#4

CPURST#4

CPU_GD4

HBPRI#4

HBR#04

RS#[0..2]

RS#[0..2]4

HADS#4

HITM#4

HIT#4

HDRDY#4

HDBSY#4

HBNR#4

C C

HREQ#[0..4]

HREQ#[0..4]4

HADSTB#14

HADSTB#04

HA#[3..31]

HA#[3..31]4

B B

VCCP

R147 20RST

R150 110RST

VCCP VCCP

R129

75RST

A A

R128

150RST

place this capacitor

under 650 solder side

5

CPUCLK1 ACBE#3

CPUCLK-1 ACBE#2

HLOCK#

HTRDY# AREQ#

CPURST# AGNT#

CPU_GD AFRAME#

HBPRI# AIRDY#

HBR#0 ATRDY#

RS#2 ASERR#

RS#1 ASTOP#

RS#0

HADS#

HITM# RBF#

HIT# WBF#

HDRDY# PIPE#

HDBSY#

HBNR#

HREQ#4

HREQ#3

HREQ#2 SBSTB

HREQ#1 SBSTB#

HREQ#0

HADSTB#1 ADSTB#0

HADSTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

Rds-on(p) = 56 ohm

HPCVERF = 2/3 VCCP

HD#[0..63]4

CB35

0.01u

CB33

0.01u

HD#[0..63]

HVREF

CB34

0.1u

AH26

U26

U24

C20

D19

U25

U29

U28

W26

W28

W29

W24

W25

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

V26

T27

T24

T26

V28

T28

V24

V27

Y27

Y26

Y24

Y28

CPUCLK

CPUCLK#

DEFER#

HLOCK#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

HD#63

B21

HD#63

C1XAVSS

C1XAVDD

C4XAVSS

HOST

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

F19

A21

E19

D22

D20

B22

C22

B23

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

R149

150RST

R148

75RST

4

HVREF0

C4XAVDD

HD#55

HD#54

HD#53

A23

D21

HD#54

HD#53

CB49

0.01u

CB48

0.01u

HVREF1

HD#52

F22

HD#52

HVREF2

HD#51

D24

D23

HD#51

HVREF3

HD#50

HD#50

ST0

ST1

ST2

AAD0

AAD1

AAD2

AAD3

AAD4

AAD5

AAD6

HVREF4

HPCOMP

HNCOMP

HNCOMPVREF

AAD7

650-1

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

C24

B24

E25

E23

D25

A25

C26

B26

B27

D26

B28

E26

F28

G25

F27

F26

G24

H24

HD#49

HD#48

HD#47

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#33

HD#32

HD#34

COST DOWN

C1XAVDD

C1XAVSS

L36 0 L34 80

CB103

0.01u

CP26

1 2

X_COPPER_0

AAD8

HD#32

G29

HD#31

AAD9

AAD10

HD#31

HD#30

J26

HD#30

AAD11

HD#29

G26

HD#29

J25

HD#28

AAD12

AAD13

AAD14

HD#28

HD#27

HD#26

H26

G28

H28

HD#27

HD#26

HD#25

CT23

X_10u-0805

AAD15

HD#25

J24

HD#24

3

AAD16

HD#24

K28

HD#23

AAD17

HD#23

J29

HD#22

AAD18

HD#22

K27

HD#21

AAD19

AAD20

HD#21

HD#20

J28

HD#20

AAD21

HD#19

M24

HD#19

AAD22

HD#18

L26

K26

HD#18

HD#17

C4XAVDD

C4XAVSS

AAD23

HD#17

L25

HD#16

AAD24

AAD25

HD#16

HD#15

L28

HD#15

M26

HD#14

AAD26

AAD27

AAD28

AAD29

AAD30

AAD31

AGP

HD#14

HD#13

HD#12

HD#11

HD#10

HD#9

P26

L29

N24

N26

M27

HD#9

HD#13

HD#12

HD#11

HD#10

HD#8

N28

HD#8

P27

HD#7

SBA7

HD#7

N29

HD#6

CB99

0.01u

SBA6

SBA5

SBA4

SBA3

HD#6

HD#5

HD#4

HD#3

R24

R28

M28

HD#5

HD#4

HD#3

CP24

1 2

X_COPPER_0

P28

HD#2

SBA2

HD#2

R26

HD#1

C7

SBA1

HD#1

R29

HD#0

SBA0

HD#0

E21

HDBI#3

VCC3VCC3

AAD[0..31] 15

SBA[0..7] 15

ACBE#[0..3] 15

ST[0..2] 15

ADSTB[0..1] 15

ADSTB#[0..1] 15

R179 60.4RST

A1XAVDD

CB57

0.1u

A1XAVSSHPCOMP

A4XAVDD

CB55

0.1u

A4XAVSSHNCVREF

Micro-Star

Document Number

Last Revision Date:

Wednesday, September 11, 2002

VDDQ

C132

0.01u

COST DOWN

L30 0

CB58

0.01u

CP19

1 2

X_COPPER_0

L25 80

CB52

0.01u

CP15

1 2

X_COPPER_0

Title

AVREFGC 15

VCC3

CT18

X_10u-0805

VCC3

CT17

X_10u-0805

MS-6564

SIS645/650-1

Sheet of

1

Rev

10A

6

32

Page 7

5

4

3

2

1

MA7

MA8

MA5

MA6

D D

MA14

MA13

MA9

Rs place close to DIMM1

RMD1 MD1 MD0

RMD5 MD5 MD1

RMD4 MD4 MD2

RMD0 MD0 MD3

RMD6 MD6 MD4

RMD2 MD2 MD5

RDQM0 DQM0 MD6

RDQS0 DQS0 MD7

RMD9 MD9 DQM0

RMD8 MD8 DQS0

RMD7 MD7 MD8

RMD3 MD3 MD9 MA2

RMD11 MD11 MD10

RMD10 MD10 MD11

RMD15 MD15 MD12

RMD14 MD14 MD13

RDQM1 DQM1 MD14 MA7

RMD13 MD13 MD15 MA8

RDQS1 DQS1 DQM1 MA9

RMD12 MD12 DQS1 MA10 RMA10

RMD21 MD21 MD16 MA11 RMA11

C C

B B

A A

RMD17 MD17 MD17 MA12 RMA12

RMD16 MD16 MD18 MA13

RMD20 MD20 MD19 MA14

RMD22 MD22 MD20

RMD18 MD18 MD21 SRAS# RSRAS#

RDQM2 DQM2 MD22 SCAS# RSCAS#

RDQS2 DQS2 MD23 SWE# RSWE#

RMD28 MD28 DQM2

RMD24 MD24 DQS2

RMD23 MD23 MD24

RMD19 MD19 MD25 CS-0

RMD31 MD31 MD26

RMD27 MD27 MD27 CS-2

RMD30 MD30 MD28 CS-3

RMD26 MD26 MD29

RDQM3 DQM3 MD30

RDQS3 DQS3 MD31

RMD25 MD25 DQM3

RMD29 MD29 DQS3

RMD37 MD37 MD32 CKE0

RMD33 MD33 MD33 CKE1

RMD36 MD36 MD34 CKE2

RMD32 MD32 MD35 CKE3

RMD38 MD38 MD36

RMD34 MD34 MD37

RDQM4 DQM4 MD38 S3AUXSW#

RDQS4 DQS4 MD39

RMD44 MD44 DQM4

RMD40 MD40 DQS4

RMD35 MD35 MD40 SDCLK

RMD39 MD39 MD41

RDQS5 DQS5 MD42 FWDSDCLKO

RDQM5 DQM5 MD43

RMD41 MD41 MD44

RMD45 MD45 MD45

RMD47 MD47 MD46

RMD43 MD43

RMD42 MD42 DQS5

RMD55 MD55 MD48 SDAVSS

RDQS6 DQS6 MD49

RMD54 MD54 MD50

RDQM6 DQM6 MD51 DDRAVDD

RMD53 MD53 MD52

RMD52 MD52 MD53 DDRAVSS

RMD49 MD49

RMD48 MD48 MD55

RMD56 MD56 DQM6

RMD60 MD60 DQS6 DDRVREFA

RMD51 MD51 MD56 DDRVREFB

RMD50 MD50 MD57

RMD62 MD62

RDQM7 DQM7 MD59 DDRAVDD

RMD57 MD57

RMD61 MD61 MD61

RMD63 MD63

RMD58 MD58

RDQS7 DQS7

1 2

RN51

3 4

5 6

7 8

10

1 2

RN50

3 4

5 6

10

7 8

1 2

RN49

3 4

5 6

7 8

10

RN47101 2

3 4

5 6

7 8

1 2

RN48

3 4

5 6

7 8

10

1 2

RN46

3 4

5 6

7 8

10

1 2

RN45

3 4

5 6

10

7 8

1 2

RN52

3 4

5 6

7 8

10

RN42101 2

3 4

5 6

7 8

1 2

RN43

3 4

5 6

7 8

10

1 2

RN40

3 4

5 6

7 8

10

1 2

RN39

3 4

5 6

10

7 8

1 2

RN38

3 4

5 6

7 8

10

RN37101 2

3 4

5 6

7 8

1 2

RN36

3 4

5 6

10

7 8

1 2

RN34

3 4

5 6

7 8

10

1 2

RN35

3 4

5 6

10

7 8

1 2

RN33

3 4

5 6

7 8

10

RN32101 2

3 4

5 6

7 8

1 2

3 4

5 6

RN31

7 8

10

MD47RMD46 MD46

DQM5 SDAVDD

MD54

MD58

MD60

MD62RMD59 MD59

MD63

DQM7

DQS7

AJ23

AG22

AH21

AJ21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AJ17

AE17

AH18

AD14

AG14

AJ13

AE13

AJ15

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AD8

AG10

AF10

AH9

AD9

AH5

AG4

AH3

AG6

AH4

AD6

AC5

AG2

AG1

AC6

AD4

AD3

AC4

AD2

AC1

AC2

AE9

AF9

AJ9

AE5

AF6

AF5

AF4

AJ3

AE4

AE2

AF3

AF2

AB6

AA6

AB3

AE1

AB4

U12B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS-SIS650GX-VA1

650-2

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

MA13

MA14

SRAS#

SCAS#

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

AH11

AF12

AH12

AG12

AD12

AH15

AF15

AH16

AE15

AD15

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

<---

AA3

--->

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

R252 4.7K

W3

MA5

MA6

CS-1

RN290

RN440

RMA7

78

RMA8

56

RMA5

34

RMA6

12

78

RMA14

56

RMA13

34

12

RMA9

Rs place close to DIMM1

R276

RN41 0

R275

R273

R274

R272 0

R265 0

R271 0

RN28 0

CKE: Open Drain

R287 4.7K

R223 22

HI: DDR

RMD[0..63]

RDQM[0..7]

RDQS[0..7]

RMA[0..14]

RCS-[0..3]

CKE[0..3]

RMA0MA0

0

RMA1MA1

12

RMA2

34

RMA3MA3

56

78

RMA4MA4

0

0

0

RSRAS# 10,11

RSCAS# 10,11

RSWE# 10,11

RCS-0

78

RCS-2

56

RCS-1

34

12

RCS-3

S3AUXSW# 27

VCC3SBY

SDCLK 3

FWDSDCLKO 3

SDAVDD

SDAVSS

DDRAVSS

RMD[0..63] 10,11

RDQM[0..7] 10,11

RDQS[0..7] 10,11

RMA[0..14] 10,11

RCS-[0..3] 10,11

CKE[0..3] 10

DDRVREFA

DDRVREFB

CB113

0.1u

CB114

0.1u

VCCM

CB107

0.01u

CB106

0.01u

VCCM

CB119

0.01u

CB104

0.01u

L39 80

CB116

0.01u

CP36

1 2

X_COPPER_0

L40 80

CB117

0.01u

CP27

1 2

X_COPPER_0

R227

150RST

R219

150RST

R258

150RST

R241

150RST

VCC3

VCC3VCC3SBY

CT26

X_10u-0805

CT24

X_10u-0805

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, September 11, 2002

MS-6564

SIS645/650-2

Sheet of

1

Rev

10A

7

32

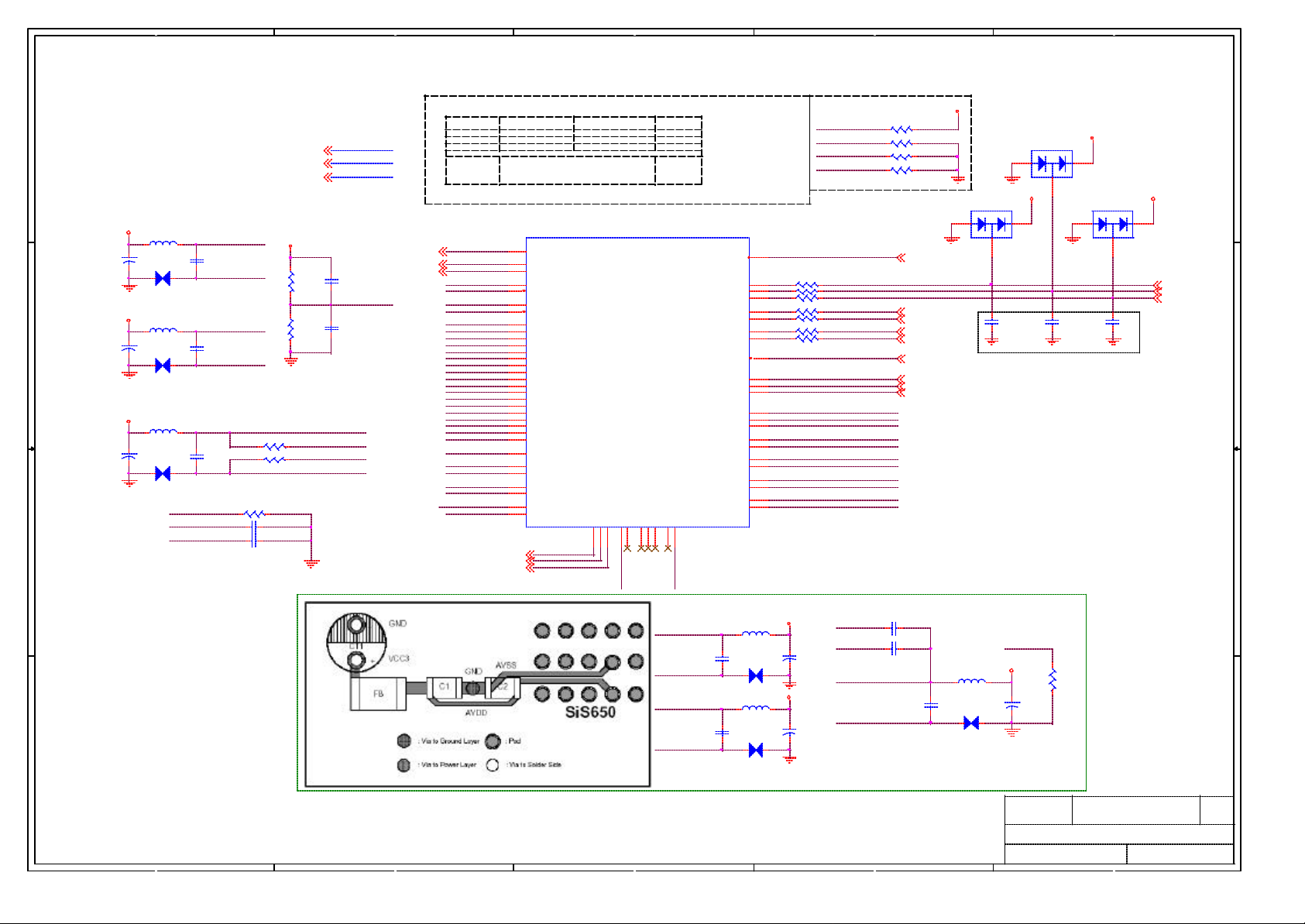

Page 8

5

4

3

2

1

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

D11

TRAP1

TRAP1

E10

TRAP0

A10

Default

1(DDR)

TESTMODE2

TESTMODE1

TESTMODE0

F11

C11

DLLEN#

D D

VCC3

COST DOWN

L35 0

C164

X_10u-0805

C C

B B

X_10u-0805

X_10u-0805

VCC3

C160

VCC1_8

C154

CP25

1 2

X_COPPER_0

COST DOWN

L33 0

CP23

1 2

X_COPPER_0

COST DOWN

L32 0

CP21

1 2

X_COPPER_0

ENTEST

PWRGD

AUXOK

Z1XAVDD

C161

0.1u

Z1XAVSS

Z4XAVDD

C157

0.1u

Z4XAVSS

C152

0.1u

R155 4.7K

C178 0.1u

C186 0.1u

R196 56

R193 56

ZSTB-[0..1]12

VCC1_8

ZAD[0..15]12

ZSTB[0..1]12

R220

150RST

R222

150RST

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

ZAD[0..15]

ZSTB[0..1]

ZSTB-[0..1]

CB111

0.1u

CB102

0.1u

ZVREF

DRAM_SEL

TRAP0

TRAP1

CSYNC

RSYNC

LSYNC

ZCLK0

ZCLK03

ZUREQ

ZUREQ12

ZDREQ

ZDREQ12

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1 HSYNC

ZAD0

ZAD1 DDC1CLK

ZAD2 DDC1DATA

ZAD3

ZAD4

ZAD5 INTA#

ZAD6

ZAD7

ZAD8 CSYNC

ZAD9 RSYNC

ZAD10 LSYNC

ZAD11

ZAD12

ZAD13 VCOMP

ZAD14 VRSET

ZAD15 VVBWN

ZVREF

VDDZCMP

ZCMP_N

ZCMP_P DACAVSS1

VSSZCMP

Z1XAVDD DCLKAVSS

Z1XAVSS

Z4XAVDD ECLKAVSS

Z4XAVSS

0

enable PLL disable PLL

SDR DDR

normal NB debug mode

TV selection, NTSC/PAL(0/1) 0

enable VB

enable VGA interface

enable panel link

U12C

SIS-SIS650GX-VA1

V3

ZCLK

U6

ZUREQ

U1

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

ZAD9

P5

ZAD10

P6

ZAD11

N1

ZAD12

N6

ZAD13

N2

ZAD14

N4

ZAD15

U3

ZVREF

V5

VDDZCMP

U4

ZCMP_N

U2

ZCMP_P

V6

VSSZCMP

W1

Z1XAVDD

W2

Z1XAVSS

V2

Z4XAVDD

V1

Z4XAVSS

PCIRST4#27

PCIRST4#

PWRGD

PWRGD13,26,27

AUXOK

AUXOK13

1

HyperZip

650-3

PCIRST#

PWROK

Y3W4W6

VGA

Stereo

Glass

AUXOK

DLLEN#

E11

0

0

0

1

0

ENTEST

F10

ENTEST

embedded pull-low

(30~50K Ohm)

yes

yes

yes

C15

VOSCI

A12

ROUT

B13

GOUT

A13

BOUT

F13

HSYNC

E13

VSYNC

D13

VGPIO0

D12

VGPIO1

B11

INT#A

E12

CSYNC

A11

RSYNC

F12

LSYNC

E14

VCOMP

D14

VRSET

F14

VVBWN

B12

DACAVDD1

C12

DACAVSS1

C13

DACAVDD2

C14

DACAVSS2

B15

DCLKAVDD

A15

DCLKAVSS

B14

ECLKAVDD

A14

ECLKAVSS

for 650 only

R138 0

R134 0

R131

R161

R162 33

R166 100

R135 100

RSYNC

TRAP1

CSYNC

LSYNC

0

33

REFCLK0

VSYNC

DACAVDD1

DACAVSS1

DACAVDD1

DCLKAVDD

ECLKAVDD

R146 4.7K

R154 4.7K

R175 4.7K

R174 4.7K

REFCLK0 3

HSYNC 28

VSYNC 28

DDC1CLK 28

DDC1DATA 28

INTA# 12,15,16,17

CSYNC 15

RSYNC 15

LSYNC 15

VCC3

UD1

BAV99-S-SOT23

2

VCC1_8

UD2

BAV99-S-SOT23

3

1

2

C119

X_0.1u

EMI reserve

UD4

BAV99-S-SOT23

3

ROUT

GOUT

BOUT

C115

X_0.1u

VCC1_8VCC1_8

1

ROUT 28

GOUT 28

BOUT 28

2

1

3

C120

X_0.1u

CP17

1 2

X_COPPER_0

CP16

1 2

X_COPPER_0

VCC3

CE1

X_10u-0805

VCC3

CE2

X_10u-0805

DCLKAVDD

DCLKAVSS

ECLKAVDD

A A

5

4

ECLKAVSS

3

L27 80

CB60

0.1u

L26 80

CB59

0.1u

VVBWN

DACAVDD1

DACAVSS1

CB38

CB39

0.1u

VCC1_8

CP18

VRSETVCOMP

R141

130RST

CE3

X_10u-0805

Micro-Star

Document Number

Last Revision Date:

Wednesday, September 11, 2002

Title

MS-6564

SIS645/650-3

Sheet of

1

Rev

10A

8

32

X_0.1u

L29 3.6

CB62

0.1u

1 2

X_COPPER_0

2

Page 9

5

4

3

2

1

VCCP VCC1_8 VCC3

H21

H22

J16

J20

J21

J22

K16

K17

K18

K19

K20

K21

L20

M20

N20

P20

R20

R21

T20

U20

V20

W20

Y20

Y21

AA20

AA21

AA22

AB21

AB22

L12

L14

L15

L16

L18

M11

M19

N11

P19

R11

T19

U11

V19

W11

W13

W15

W17

VCCP

C16

C17

C18

D15

D16

D17

D18

AD5

AE10

AE12

AE14

AE16

AE18

AE20

AE22

W18

AA10

AA13

AA14

AA15

AA16

AA17

AB13

AB17

N10

R10

A16

VTT

A17

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

VTT

A18

VTT

B16

VTT

B17

VTT

B18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

E15

VTT

E16

VTT

E17

VTT

E18

VTT

F15

VTT

F16

VTT

F17

VTT

F18

VTT

AB5

VDDM

VDDM

AE6

VDDM

AE8

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

V10

VDDM

V11

VDDM

VDDM

Y9

VDDM

Y10

VDDM

Y12

VDDM

Y14

VDDM

Y16

VDDM

Y18

VDDM

Y19

VDDM

AA8

VDDM

AA9

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

AB8

VDDM

AB9

VDDM

VDDM

VDDM

E5

VDDQ

E7

VDDQ

E9

VDDQ

G5

VDDQ

J5

VDDQ

L5

VDDQ

H8

VDDQ

H9

VDDQ

J8

VDDQ

J9

VDDQ

J10

VDDQ

J13

VDDQ

K9

VDDQ

K11

VDDQ

K13

VDDQ

L10

VDDQ

N9

VDDQ

VDDQ

N5

VDDZ

R5

VDDZ

U5

VDDZ

W5

VDDZ

P9

VDDZ

P10

VDDZ

R9

VDDZ

VDDZ

T9

VDDZ

T10

VDDZ

T11

VDDZ

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L17

L19

N19

R19

U19

W19

M12

M13

M14

M15

M16

M17

M18

N12

N13

N14

N15

N16

N17

N18

P12

VCC1_8

4

VSS

VSS

VSS

P13

P14

P15

650-4

VSS

VSS

VSS

VSS

VSS

VSS

P16

P17

P18

R12

R13

R14

Power

VSS

VSS

VSS

R15

R16

R17

VSS

VSS

VSS

VSS

R18

T12

T13

IVDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T14

T15

T16

T17

T18

U12

U13

D D

VCCM

C C

VDDQ

B B

VCC1_8

A A

5

P11

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDDZ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

U14

U15

U16

U17

U18

V12

V13

V14

V15

VCC3SBY

PVDDM

VSS

VSS

AF25

AG24

AUX1.8

AUX3.3

VSS

AG26

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AH23

VSS

AH24

U12D

U10

U9

A20

A22

A24

A26

C19

C21

C23

C25

C27

E20

E22

E24

F25

H25

K25

M25

P25

T25

V25

Y25

AB25

AD25

E27

G27

J27

L27

N27

R27

U27

W27

AA27

AC27

AE27

D29

F29

H29

K29

M29

P29

T29

V29

Y29

AB29

AD29

AF29

AE24

AG25

B4

B6

C8

C10

D2

F2

H2

K2

P2

T2

V4

AD1

AF1

AC3

AE3

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AJ4

AJ6

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AG27

VSS

SIS-SIS650GX-VA1

VCC1_8SBY

VCC3SBY

VDDQ

CB80

0.1u

CB56

0.1u

Place these capacitors under 650 solder side

VCCP

CB226

0.1u

CB220

0.1u

CB219

0.1u

CB230

0.1u

J14

J15

K15

K10

K12

K14

M10

W10

Y11

Y13

Y15

Y17

PVDD

PVDD

PVDD

PVDD

OVDD

OVDD

OVDD

PVDDM

PVDDM

PVDDM

PVDDM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

V16

V17

V18

B25

C28

C29

D27

D28

E28

E29

AF23

AF24

3

VCCP

VCC1_8

2

VCC3SBY

CB46

1u

CB50

1u

CB30

1u

CB22

1u

CB73

0.1u

CB67

0.1u

CB224

X_1u-0805

CB229

X_1u-0805

CB225

X_1u-0805

CB228

X_1u-0805

CB101

1u

CB121

0.1u

VCCM

VCCM

VCC3

CB61

0.1u

CB31

0.1u

CB21

0.1u

CB23

0.1u

CT21

10u-0805

CT22

10u-0805

CB231

X_0.1u

CB232

X_0.1u

CB235

X_0.1u

CB234

X_0.1u

CB151

0.1u

CB110

0.1u

CB222

X_0.1u

CB221

X_0.1u

VCC1_8

VCC1_8SBY

Title

CB47

1u

CB37

0.1u

CB65

0.1u

VCC3

Micro-Star

Document Number

Last Revision Date:

Wednesday, September 11, 2002

CB82

0.1u

CB122

1u

CB123

0.1u

CB109

1u

CB105

0.1u

VCC3SBY

CB233

X_0.1u

CB227

X_0.1u

VDDQ

CB223

X_0.1u

CB218

X_0.1u

MS-6564

SIS645/650-4

Sheet of

1

Rev

10A

9

32

Page 10

5

4

3

2

1

RMD[0..63]7,11

RMA[0..14]7,11

RDQM[0..7]7,11

VDDID

OPEN

GND

SDR

CS0

CS1

CS2

CS3

CS4

CS5 CS5

CSB0

CSB1

CSB2

CSB3

CSB4

CSB5

CSB6

CSB7

CB129

0.1u

5

RDQS[0..7]7,11

D D

NOTE:

VDDID IS A TRAP ON THE DIMM

MODULE TO INDICATE:

MEMORY MUX TABLE:

C C

DDRVREF GEN. & DECOUPLING

VCCM

75RST

R303

75RST

B B

A A

CB124

0.01u

CB130

0.01u

RMA[0..14] RMA[0..14]

RDQM[0..7] RDQM[0..7]

RDQS[0..7] RDQS[0..7]

REQUIRED POWER

VDD=VDDQ

VDD!=VDDQ

DDR

CS0

CS1

CS2

CS3

CS4

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

VCCM VCCM

CB150

0.1u

DDRCLK[0..8]3

DDRCLK-[0..8]3

DDRVREF

CB125

0.01u

RCS-[0..3]7,11

CKE[0..3]7

DDRVREF

RSRAS#7,11

RSCAS#7,11

RSWE#7,11

RCS-[0..3]

CKE[0..3]

DDRCLK[0..8]

DDRCLK-[0..8]

VCCM

DIMM1

15223054627796

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VSS

VSS

VSS

VSS

145

152

160

176

4

VDDQ

VSS

VSS

VSS

124

132

139

120

148

168

184

48

RMA0 RMD4

RMA1 RMD5

43

RMA2 RMD6

41

RMA3 RMD7

130

RMA4 RMD8

37

32

RMA5 RMD9

RMA6 RMD10

125

RMA7 RMD11

29

RMA8 RMD12

122

RMA9 RMD13

27

141

RMA10 RMD14

RMA13 RMD15

118

RMA14 RMD16

115

103

59

RMA11 RMA11 RMD19

RMA12 RMA12 RMD20

52

113

RDQM0 RMD23

RDQM1 RMD24

RDQM2 RMD25

RDQM3 RMD26

RDQM4 RMD27

RDQM5 RMD28

RDQM6 RMD29

RDQM7 RMD30

RDQS0 RMD33

RDQS1 RMD34

RDQS2 RMD35

RDQS3 RMD36

RDQS4 RMD37

RDQS5 RMD38

RDQS6 RMD39

RDQS7 RMD40

RSRAS# RSRAS# RMD59

RSCAS# RSCAS# RMD60

RSWE# RSWE# RMD61

RCS-0 RCS-2 RMD63

RCS-1 RCS-3

CKE0 WP CKE2

CKE1 SMBCLK CKE3

DDRCLK1

DDRCLK8

DDRCLK2

DDRCLK-1

DDRCLK-8

DDRCLK-2

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

addr =

1010000b

VSS

VSS

VSS

VSS

VSS

VSS

VSS

100

116

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

SCL

SDA

SA0

SA1

SA2

VSS

VDDQ

WP

VSS

3111826344250586674818993

VDDQ

RMD0

2

RMD1

4

RMD2

6

RMD3

8

94

RMD4

RMD5

95

RMD6

98

RMD7

99

RMD8

12

13

RMD9

RMD10

19

RMD11

20

RMD12

105

RMD13

106

109

RMD14

RMD15

110

RMD16

23

RMD17

24

RMD18

28

31

RMD19

RMD20

114

RMD21

117

RMD22

121

RMD23

123

33

RMD24

RMD25

35

RMD26

39

RMD27

40

RMD28

126

127

RMD29

RMD30

131

RMD31

133

RMD32

53

RMD33

55

57

RMD34

RMD35

60

RMD36

146

RMD37

147

RMD38

150

151

RMD39

RMD40

61

RMD41

64

RMD42

68

RMD43

69

153

RMD44

RMD45

155

RMD46

161

RMD47

162

RMD48

72

73

RMD49

RMD50

79

RMD51

80

RMD52

165

RMD53

166

170

RMD54

RMD55

171

RMD56

83

RMD57

84

RMD58

87

88

RMD59

RMD60

174

RMD61

175

RMD62

178

RMD63

179

DDRVREF DDRVREF

1

82

90

92

SMBDAT SMBDAT

91

181

182

183

VSS

DIMM-D184-BK

RMD[0..63]

VCCM

DIMM2

15223054627796

104

112

128

136

143

156

164

172

180738467085108

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDDSPD

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

BA0

BA1

BA2

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS8

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

NC

NC(RESET#)

NC

NC

NC

NC(FETEN)

RAS#

CAS#

WE#

S0#

S1#

NC(S2#)

NC(S3#)

CKE0

CKE1

CK0

CK1

CK2

CK0#

CK1#

CK2#

VSS

VSS

VSS

VSS

145

152

160

176

VDDQ

VSS

VSS

VSS

124

132

139

2

120

148

168

184

RMA0

RMA1

RMA2

RMA3

RMA4

RMA5

RMA6

RMA7

RMA8

RMA9

RMA10

RMA13

RMA14

RDQM0

RDQM1

RDQM2

RDQM3

RDQM4

RDQM5

RDQM6

R293 8.2KR295 8.2K

CKE3

CKE2

CKE0

CKE1

3

RN30

1 2

3 4

5 6

7 8

470

RDQM7

RDQS0

RDQS1

RDQS2

RDQS3

RDQS4

RDQS5

RDQS6

RDQS7

DDRCLK0

DDRCLK7

DDRCLK3

DDRCLK-0

DDRCLK-7

DDRCLK-3

VCCM

48

43

41

130

37

32

125

29

122

27

141

118

115

103

59

52

113

97

107

119

129

149

159

169

177

140

5

14

25

36

56

67

78

86

47

44

45

49

51

134

135

142

144

9

10

101

102

173

167

154

65

63

157

158

71

163

21

111

137

16

76

138

17

75

116

VDDQ

VSS

100

VDDQ

VDDQ

addr =

1010001b

VSS

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

VSS

VDDQ

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VREF

VDDID

VSS

VDDQ

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

SCL

SDA

SA0

SA1

SA2

VSS

VDDQ

WP

VSS

3111826344250586674818993

VDDQ

RMD0

2

RMD1

4

RMD2

6

RMD3

8

94

95

98

99

12

13

19

20

105

106

109

110

23

RMD17

24

RMD18

28

31

114

RMD21

117

RMD22

121

123

33

35

39

40

126

127

131

RMD31

133

RMD32

53

55

57

60

146

147

150

151

61

RMD41

64

RMD42

68

RMD43

69

153

RMD44

RMD45

155

RMD46

161

RMD47

162

RMD48

72

73

RMD49

RMD50

79

RMD51

80

RMD52

165

RMD53

166

170

RMD54

RMD55

171

RMD56

83

RMD57

84

RMD58

87

88

174

175

RMD62

178

179

1

82

90

92

91

181

182

183

VSS

DIMM-D184-BK

Micro-Star

Document Number

Last Revision Date:

Wednesday, September 11, 2002

VCCM VCCM

R294 4.7K

WP

SMBCLK

DIMM DECOUPLING

CB144

0.1u

CB137

0.1u

CB140

0.1u

CB132

0.1u

CB133

0.1u

CB135

0.1u

CB139

0.1uR268

CB142

0.1u

CB136

0.1u

VCCM

WP

SMBCLK 3,13,27

SMBDAT 3,13,27

VCCM

Title

MS-6564

DDR1 & DDR2

1

CB143

0.1u

CB141

0.1u

CB134

0.1u

CB138

0.1u

CB131

0.1u

10

Sheet of

Rev

10A

32

Page 11

5

4

3

2

1

D D

SSTL-2 Termination Resisto rs

SDR

MD/DQM(/DQS)

MA/Control

CS

CKE

C C

B B

RMA0

RMA1

RMA2

A A

LV-CMOS

LV-CMOS

LV-CMOS

OD 3.3V OD 2.5V

RMD1

RN71 47

RMD5

RMD4

RMD0

RMD6

RN70 47

RMD2

RDQM0

RDQS0

RMD9

RN69 47

RMD8

RMD3

RMD7

RDQM1

RN68 47

RMD13

RDQS1

RMD12

RMD11

RN67 47

RMD10

RMD15

RMD14

RDQM2

RN65 47

RMA13

RDQS2

RMD21

RMD17

RN66 47

RMA14

RMD16

RMD20

RMA5

RN63 47

RMD23

RMD19

RMA8

RMD27

RN60 47

RMD30

RMD26

RMA3

RDQM3

RN61 47

RMA4

RDQS3

RMD25

RMA7

RN64 47

RMD22

RMD18

RMA9

RMD29

RN62 47

RMD28

RMD24

RMA6

RN59 47

RMD31

RMD39

RN82 47

RMA11

RMD38

RMD34

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

12

34

56

78

DDR

Rs

SSTL-2

0/10/- 47

SSTL-2

10

SSTL-2

0

RMD36

RN84 47

RMD32

RMA12

RMA10

RDQM4

RN83 47

RDQS4

RMD37

RMD33

RSRAS#

RMD44

RMD40

RMD35

RMD47

RMD46

RMD43

RMD42

RCS-3

RCS-2

RSCAS#

RMD53

RMD52

RMD49

RMD48

RMD55

RDQS6

RMD54

RDQM6

RMD59

RMD63

RMD58

RDQS7

RMD56

RMD60

RMD51

RMD50

RMD62

RDQM7

RMD57

RMD61

RDQS5

RDQM5

RCS-1

RCS-0

RMD41

RMD45

RSWE#

RN81 4712

RN77 4712

RN79 4712

RN76 4712

RN75 4712

RN72 4712

RN74 4712

RN73 4712

RN78 47

RN80 4712

RSRAS#7,10

RSCAS#7,10

RSWE#7,10

Rs

10

0

0

DDR_VTT

12

34

56

78

12

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

34

56

78

DDR_VTT

12

34

56

78

34

56

78

Rtt

47

47

RMD[0..63]7,10

RMA[0..14]7,10

RDQM[0..7]7,10

RDQS[0..7]7,10

RMD[0..63]

RMA[0..14]

RDQM[0..7]

RDQS[0..7]

RCS-[0..5]7,10

DDRCLK[0..8]3,10

DDRCLK-[0..8]3,10

DECOUPLING CAPACITOR FOR SSTL-2 END TERMIANTION VTT ISLAND

DDR_VTT

0603 Package placed within 200mils of VTT Termination R-packs

CB157

0.1u

CB183

0.1u

CB185

0.1u

CB159

0.1u

DDR_VTT

CB158

0.1u

CB173

0.1u

CB161

0.1u

CB179

0.1u

RCS-[0..5]

CKE[0..3]

CKE[0..3]7,10

DDRCLK[0..8]

DDRCLK-[0..8]

CB180

0.1u

CB168

0.1u

CB169

0.1u

CB171

0.1u

CB160

0.1u

CB165

0.1u

CB162

0.1u

CB175

0.1u

CB174

0.1u

CB184

0.1u

CB154

0.1u

CB163

0.1u

CB164

0.1u

CB178

0.1u

CB181

0.1u

CB170

0.1u

CB167

0.1u

CB149

0.1u

CB156

0.1u

CB176

0.1u

CB177

0.1u

CB155

0.1u

CB166

0.1u

CB182

0.1u

Title

Micro-Star

Document Number

Last Revision Date:

5

4

3

2

Wednesday, September 11, 2002

MS-6564

DDR TERMINATOR

Sheet of

1

Rev

10A

11

32

Page 12

5

N19

N20

N16

N17

R19

N18

R18

U20

U19

R20

V20

K20

K19

P18

T20

T19

P20

F1

F2

E1

H5

F3

H3

G1

G2

G3

H4

K3

M4

P1

R4

E3

F4

E2

G4

M3

M1

M2

N4

M5

N3

N1

N2

Y2

C3

AD[0..31]

PREQ#4

PREQ#3

PREQ#2

PREQ#1

PREQ#0

PGNT#4

PGNT#3

PGNT#2

PGNT#1

PGNT#0

C/BE#3

C/BE#2

C/BE#1

C/BE#0

INT#A

INT#B

INT#C

INT#D

FRAME#

IRDY#

TRDY#

STOP#

SERR#

PAR

DEVSEL#

PLOCK#

PCICLK

PCIRST#

ZCLK

ZSTB0

ZSTB0#

ZSTB1

ZSTB1#

ZUREQ

ZDREQ

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

Z1XAVSS

Z4XAVDD

Z4XAVSS

VZREF

ZVSSREF

VCC3

INTB#

INTA#

INTC#

INTD#

D D

C C

ZSTB[0..1]8

ZSTB-[0..1]8

VCC1_8

B B

R311

150RST

R313

150RST

RN54

12

34

56

78

8.2K

PREQ#416,17

PREQ#316,17

PREQ#216

PREQ#116

PREQ#016

PGNT#417

PGNT#317

PGNT#216

C/BE#[0..3]16,17,20

INTA#8,15,16,17

INTB#15,16,17

INTC#16,17,20

INTD#16,17

FRAME#16,17,20

IRDY#16,17,20

TRDY#16,17,20

STOP#16,17,20

SERR#16,17

PAR16,17,20

DEVSEL#16,17,20

PLOCK#16,17

96XPCLK3

PCIRST#17,27

ZCLK13

ZSTB[0..1]

ZSTB-[0..1]

ZUREQ8

ZDREQ8

CB172

0.1u

SZVREF IDEDB12

CB186

0.1u

PGNT#116

PGNT#016

C/BE#3 IDESAA1

C/BE#2 IDESAA0

C/BE#1

C/BE#0 IDECS-A1

INTA#

INTB#

INTC# ICHRDYB

INTD# IDEREQB

FRAME# CBLIDB

IRDY#

TRDY# IDEIOR-B

STOP# IDEIOW-B

SERR#

PAR IDESAB2

DEVSEL# IDESAB1

PLOCK# IDESAB0

96XPCLK IDECS-B1

PCIRST# IDECS-B0

ZCLK1 IDEDA4

ZSTB-0 IDEDA7

ZSTB-1 IDEDA10

ZUREQ IDEDA13

ZDREQ IDEDA14

AD[0..31]16,17,20

PREQ#4

PREQ#3

PREQ#2

PREQ#1

PREQ#0

PGNT#4

PGNT#3

PGNT#2

PGNT#1

PGNT#0

R280 33

ZSTB0 IDEDA6

ZSTB1 IDEDA9

SVDDZCMP IDEDB0

SZCMP_N IDEDB1

SZCMP_P IDEDB3

SVSSZCMP IDEDB4

SZ1XAVDD IDEDB7

SZ1XAVSS IDEDB8

SZ4XAVDD IDEDB10

SZ4XAVSS IDEDB11

SZVREF IDEDB13

4

AD31 ZAD0

AD30 ZAD1

AD29 ZAD2

AD28 ZAD3

AD27 ZAD4

AD26 ZAD5

AD25 ZAD6

AD24 ZAD7

AD23 ZAD8

AD22 ZAD9