Page 1

8

7

6

5

4

3

2

1

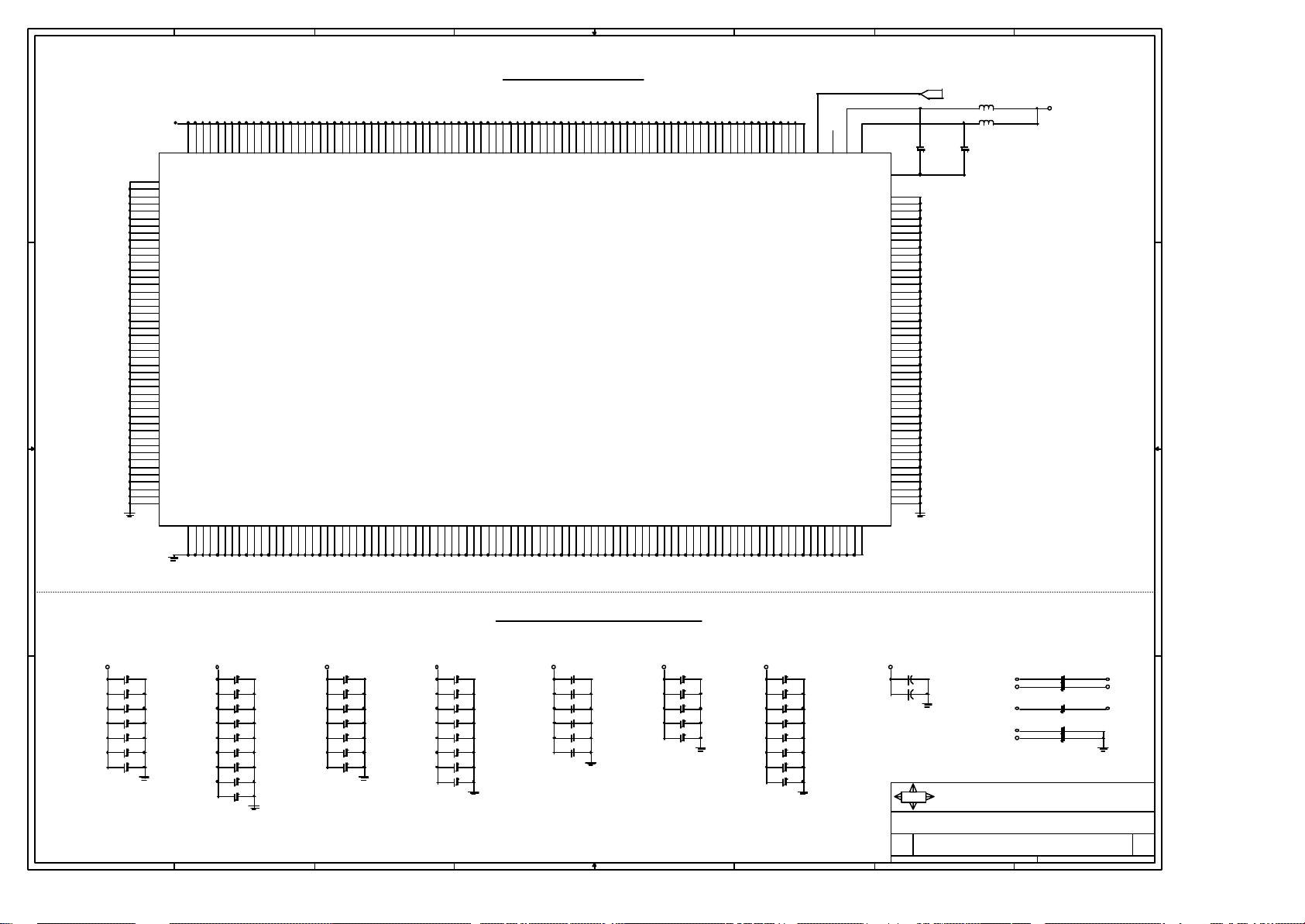

Version 0B

MS-6514

05/21/2001 Update

D D

Cover Sheet

Block Diagram

Clock CY28324 & ATA100 IDE CONNECTORS

mPGA478-B INTEL CPU Sockets

INTEL Brookdale MCH845 -- North Bridge

1

2

3

4 - 5

6 - 7

INTEL (R) Brookdale Chipset

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

System Brookdale Chipset:

INTEL MCH845 (North Bridge) +

INTEL ICH2 -- South Bridge

LPC I/O -- LPC47M142 & H/W Monitoring -- HECETA6

C C

AC'97 Codec AD1885 & Amplifier TL072

8 - 9

10

11

INTEL ICH2 (South Bridge)

On Board Chipset:

BIOS -- FWH

FWH -- BIOS & Manual

SDR DIMM-168

AGP 4X SLOT (1.5V)

PCI SLOT 1 & 2 & 3

IO Connectors

USB Hub & USB Connectors

12

13

14

15

16

17

AC'97 Codec -- AD1885

LPC Super I/O -- LPC47M142

Clock Generation -- CY28324

H/W Monitoring -- HECETA6 (Option)

Expansion Slots:

AGP2.0 SLOT (1.5V) * 1

PCI2.2 SLOT * 3

Front Panel & ATX Connectors & FAN

B B

18

Votlage Regulator

Intersil HIP6301V+HIP6601A/02A-- CPU Power ( VRM9.2 )

JUMPER SETTING

GPIO SETTTING

HISTORY 1

A A

8

7

6

19

20

21

22

23

MSI

Title

Size Document Number Rev

5

4

3

Date: Sheet of

2

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

COVER SHEET

MS-6514

1 23Monday, May 21, 2001

0B

1

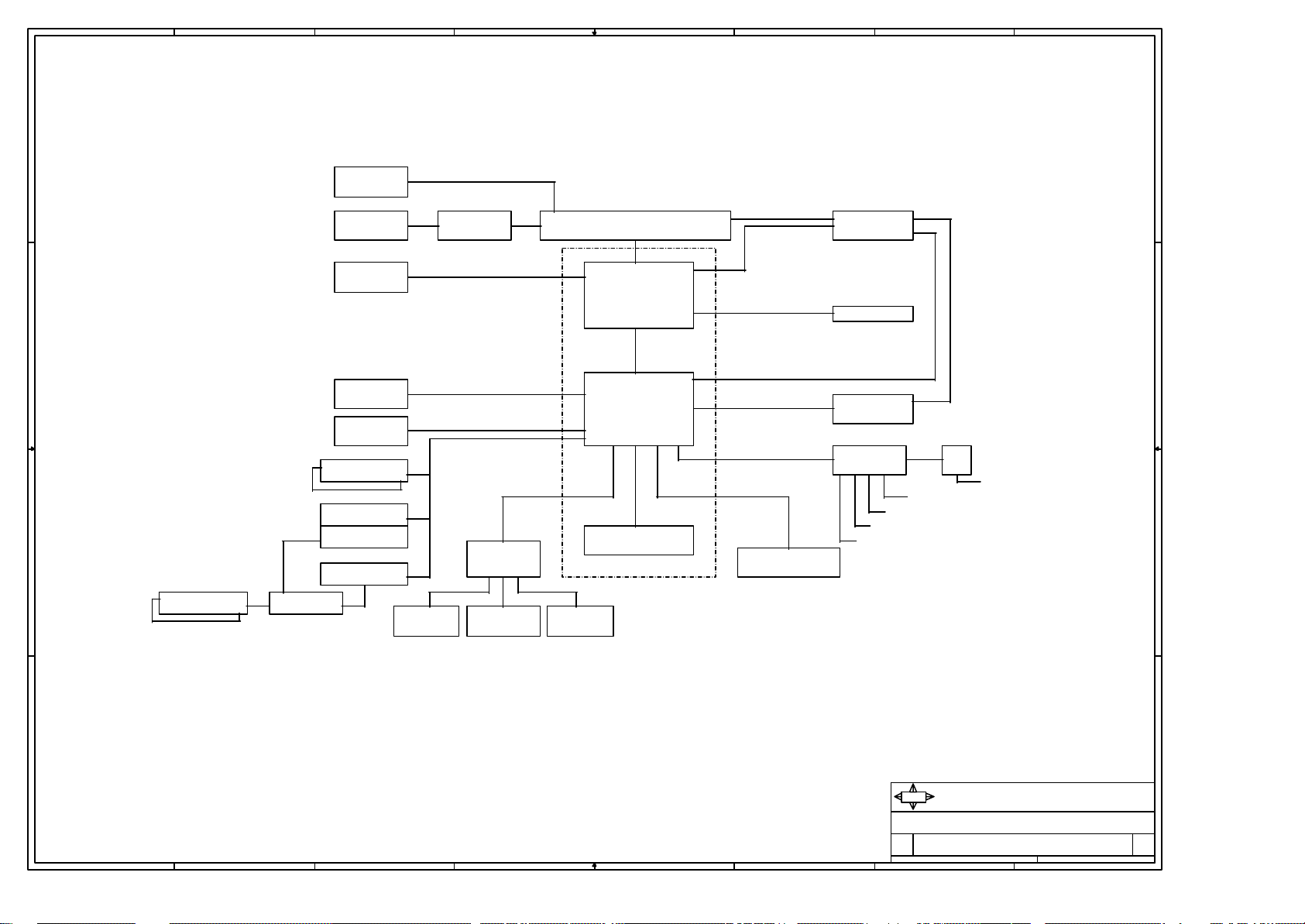

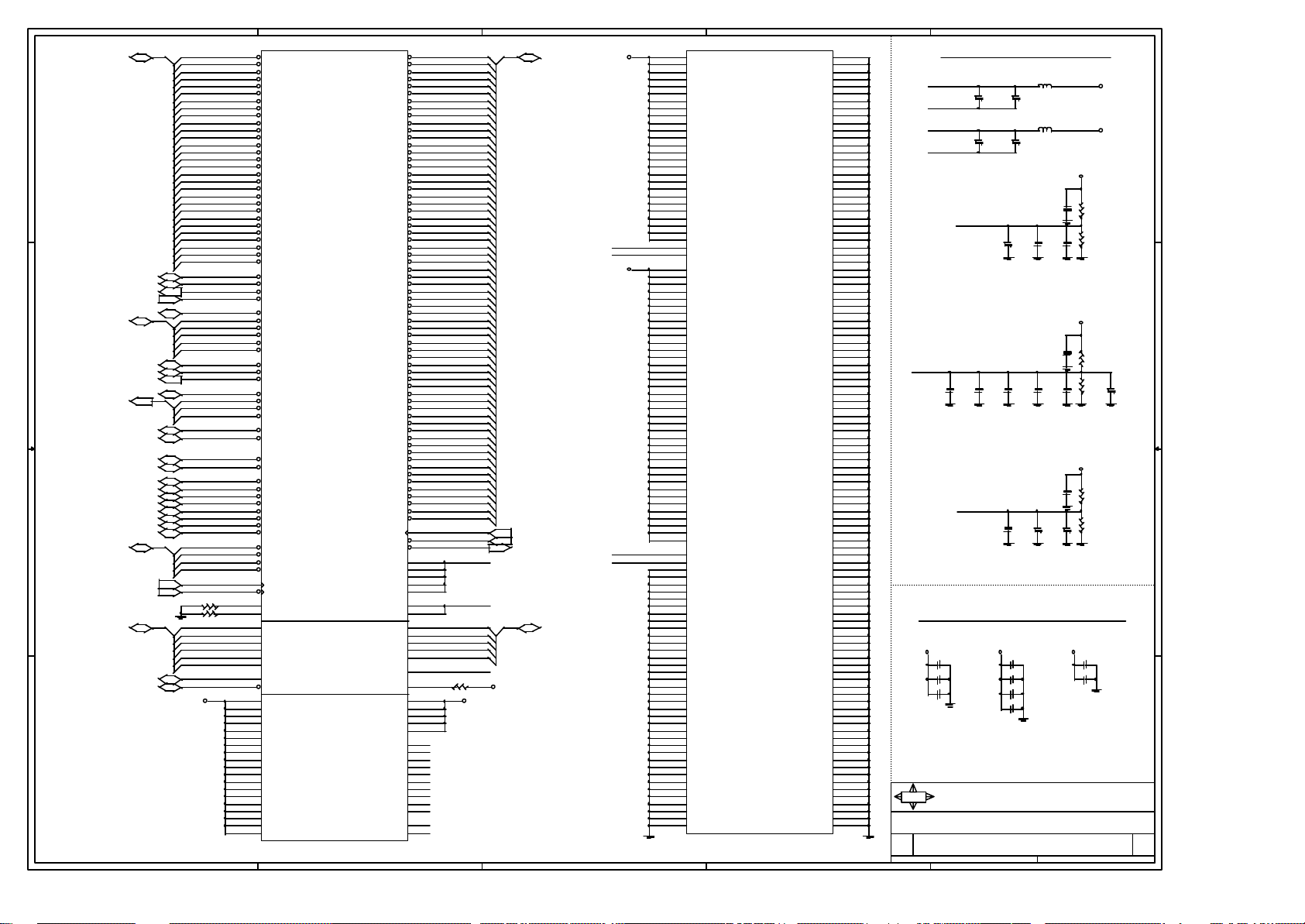

Page 2

8

D D

7

6

5

4

3

2

1

ITP Port

VCC12 Power

Supply CONN

VRM 9.2 CK408 Clock

Willamette/Northwood

Socket (mPGA478-B)

(100MHz)

Scalable Bus

(100MHz)

AGP 4X (1.5V)

AGP CONN

C C

4X (66MHz) AGP

MCH: Memory

Controller HUB

HUB Interface

(133MHz)

DIMM SKTS 1:3

(14.318MHz)

Hardware

Monitor

IDE CONN 1&2

USB Port 0:1

USB Back Panel

USB Port 2

USB Front Panel

USB Port 6

B B

USB Front Panel

USB Port 3

USB Port 4:5

USB Back Panel

USB HUB

PS2 Mouse &

Keyboard

SM Bus

ATA33/ATA66/ATA100

(48MHz)

LPC Bus

SMC I/O

LPC47M142

Parallel (1)

Serial (1)

Controller HUB

FWH: Firmware HUB

Brookdale Chipset

Floppy Disk

Drive CONN

ICH2: I/O

(33MHz)

(33MHz)

PCI (33MHz)

AC Link

H/W Monitoring

HECETA6 (Option)

PCI Slots 1:3

AC '97 Audio

Codec

Line In

AUX In (Option)

CD-ROM (Option)

AMP

Line Out

MIC In

A A

MSI

Title

Size Document Number Rev

8

7

6

5

4

3

Date: Sheet of

2

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

BLOCK DIAGRAM

MS-6514

2 23Monday, May 21, 2001

0B

1

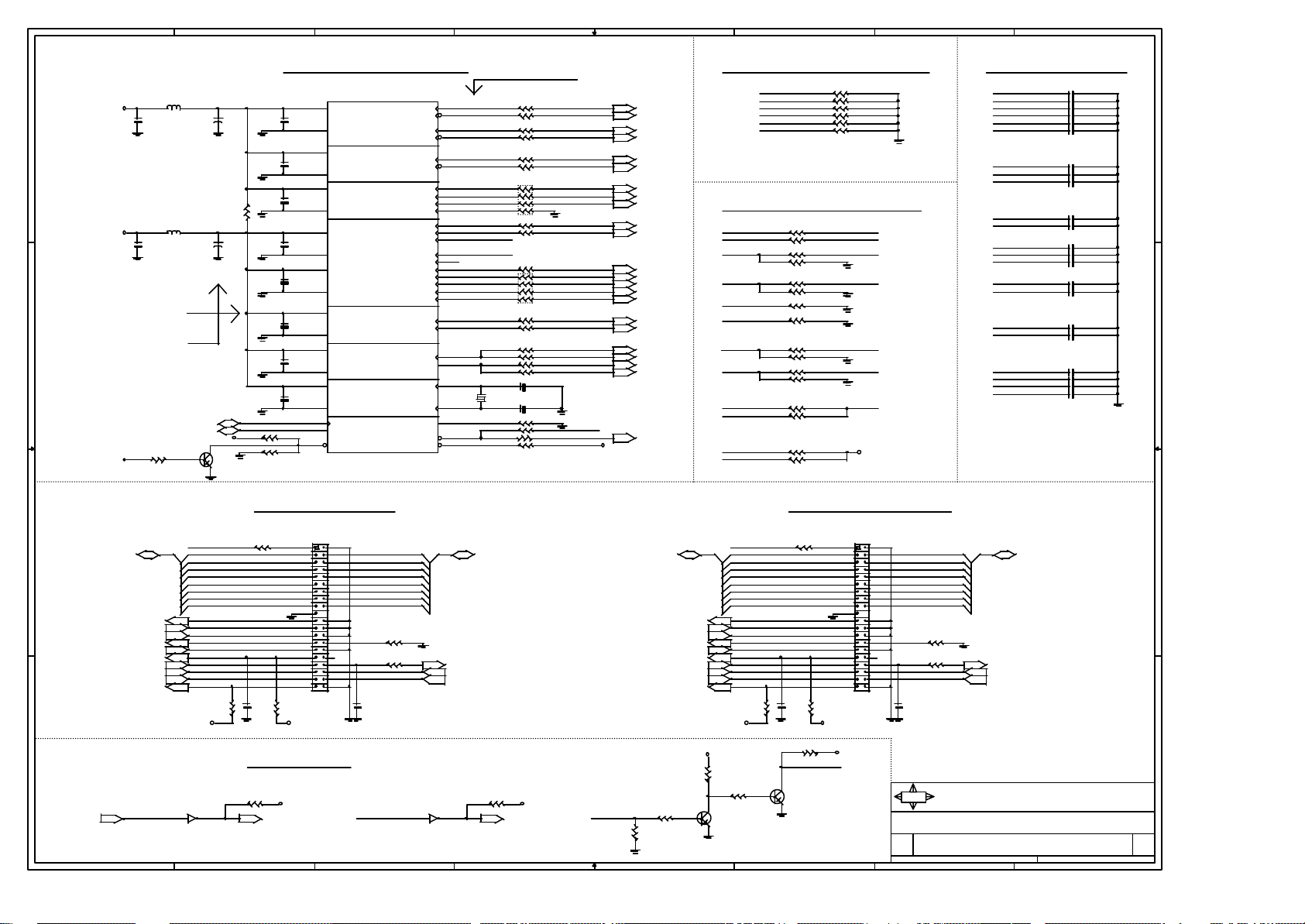

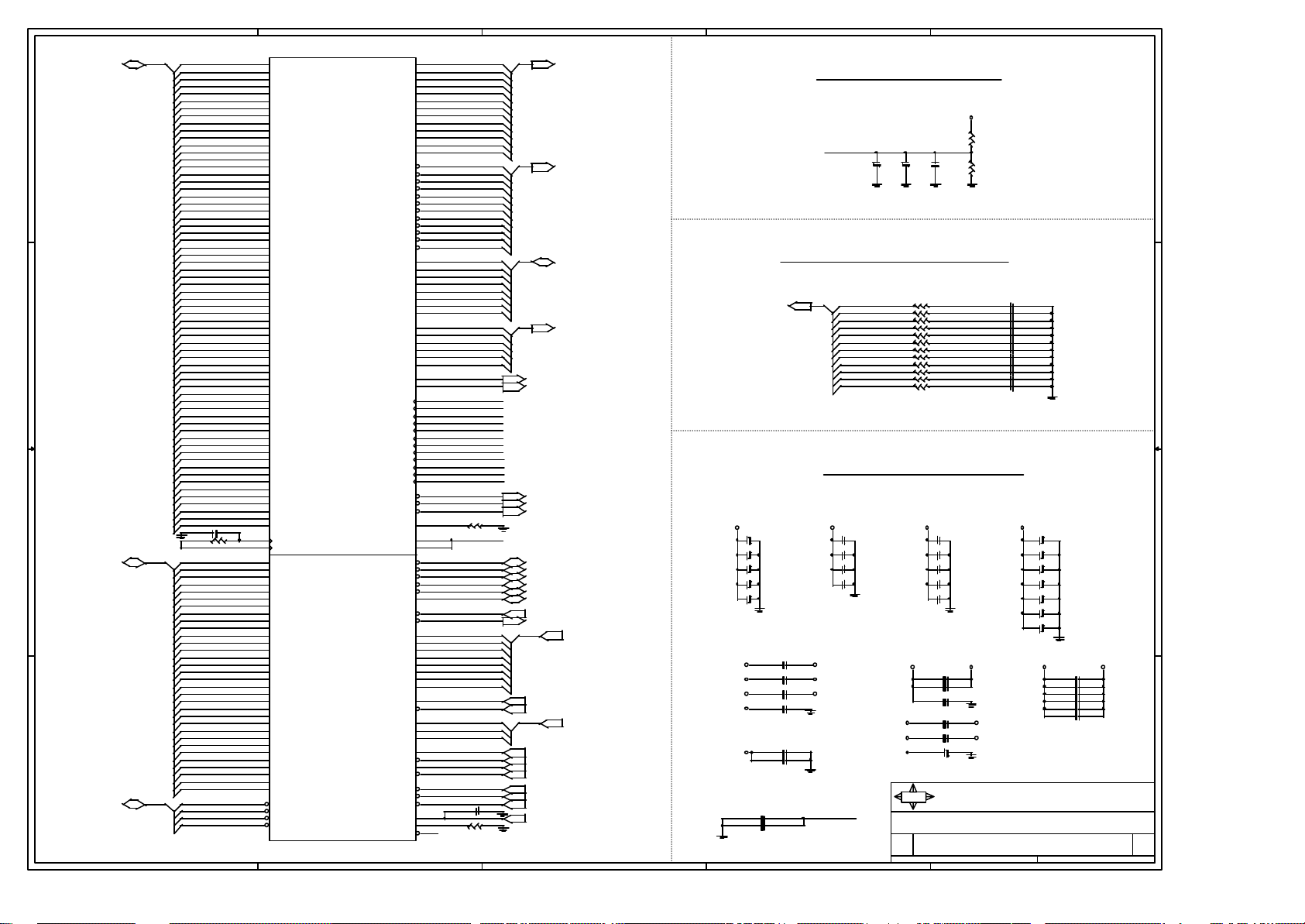

Page 3

8

7

6

5

4

3

2

1

CLOCK GENERATOR BLOCK Shut Source Termination Resistors

VCC3

D D

VCC3

* Put GND copper under Clock Gen.

connect to every GND pin

* 40 mils Trace on Layer 4

with GND copper around it

* put close to every power pin

C C

Trace Width 7mils.

*

Same Group spacing 15mils

*

Different Group spacing 30mils

*

Different mode spacing 7mils on itself

*

VCCP

FB29 600

Rubycon

CB33

0.1u

for good filtering from 10K~1M

FB30 600

Rubycon

CB37

0.1u

for good filtering from 10K~1M

SMBCLK(9,10,13)

SMBDATA(9,10,13)

R122 X_220

/N

+

CT15

10u

R99

/N

X_0

VCC3V

+

CT20

10u

SMBCLK

SMBDATA

R102 X_1K

VCC3

R103 1K

Q12

X_NPN-3904LT1-S-SOT23

PRIMARY IDE BLOCK SECONDARY IDE BLOCK

HD_RST#

R368 33 R344 33

B B

A A

PDD[0..7](9)

PD_DREQ(9)

PD_IOW#(9)

PD_IOR#(9)

PD_IORDY(9)

PD_DACK#(9)

IRQ14(8)

PD_A1(9)

PD_CS#1(9) PD_CS#3 (9)

PD_LED(18)

PCIRST#(8)

PCIRST# PCIRST#

8

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

C242

R354

220p

47K

VCC5 VCC5

RESET BLOCK

1 2

U17A

DM7407-SOIC14

(VCC5_SB) (VCC5_SB)

PCIRST#1 (6,10,12) PCIRST#2 (14,15)

7

U7

39

CB40

0.1u

CB55

0.1u

CB61

0.1u

CB41

0.1u

CB52

0.1u

CB60

0.1u

CB66

0.1u

CB58

0.1u

/N

CPU_VDD

36

CPU_GND

46

MREF_VDD

43

MREF_GND

29

3V66_GND

9

PCI_VDD

5

PCI_GND

18

PCI_VDD

13

PCI_GND

24

48_VDD

21

48_GND

2

REF_VDD

47

REF_GND

34

CORE_VDD

33

CORE_GND

26

SCLK

25

SDATA

19

VTT_GD#

CYPRESS CY28323/4

CPU0

CPU0#

CPU1

CPU1#

CPU2/CPU_STP#

CPU2#/PCI_STP#

3V66_03V66_VDD

3V66_1

3V66_2

3V66_3

FS2/PCI_F0

FS3/PCI_F1

MODE/PCI_F2

FS4/PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

IREF

RST#

PWR_DN#

X1

X2

ATA100 IDE CONNECTORS

IDE2

CN-BH-D2x20-1:21-BL-ZBT-S1

1

2

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

R363

10K

VCC3

VCC3 VCC3

PDD8

PDD9

PDD10

PDD11

PDD12

12

PDD13

PDD14

1615

PDD15

22

24

26

R362 470

28

30

32

34

R316 0 R318 0

36

38

4039

C243

X_4700p

3 4

U17B

DM7407-SOIC14

6

41

40

38

37

45

P_STP#

44

3132

30

28

27

FS2

6

FS3

7

MODE

8

FS4

10

11

12

14

15

16

17

FS0

22

FS1

23

MUL0

48

MUL1

1

3

X2 14M-32pf-HC49S-D

4

35

20

42

PDD[8..15] (9)

PD_DET (9)

PD_A2 (9)PD_A0(9)

R96 330R332 330

*Trace less 0.5"

R83 33

R88 33

R92 33

R94 33

R75 33

R77 33

1 2

RN12

3 4

33

5 6

7 8

R76 33

R80 33

R89 33

7 8

RN11

5 6

33

3 4

1 2

R112 33

R118 33

R62 33

R71 33

R64 33

R65 33

22pC93

32pF

22pC94

R97 475

R105 X_10K

R111 X_0

R82 4.7K

5

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLKC_STP#

ITP_CLK#

MCH_66

ICH_66

AGPCLK

ICH_PCLK

FWH_PCLK

APIC_CLK

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

ICH_48

SIO_48

SIO_14

ICH_14

AC_14

CODE_14

Iref = 2.32mA

/N

VCC3V

/N/N

CLK_RST#

VCC3V

VCC3V

PCIRST#

CPUCLK

R86 49.9

CPUCLK#

R91 49.9

MCHCLK

CPUCLK (4)

CPUCLK# (4)

MCHCLK (6)

MCHCLK# (6)

ITP_CLK (4)

ITP_CLK# (4)

MCH_66 (6)

ICH_66 (9)

AGPCLK (14)

ICH_PCLK (8)

FWH_PCLK (12)

APIC_CLK (8)

PCICLK0 (15)

PCICLK1 (15)

PCICLK2 (15)

SIO_PCLK (10)

ICH_48 (9)

SIO_48 (10)

SIO_14 (10)

ICH_14 (9)

AC_14 (9)

CODE_14 (11)

CLK_RST# (18)

SDD[0..7](9)

SD_DREQ(9)

SD_IOW#(9)

SD_IOR#(9)

SD_IORDY(9)

SD_DACK#(9)

IRQ15(8)

SD_A1(9)

SD_A0(9)

SD_CS#1(9) SD_CS#3 (9)

SD_LED(18)

VCC3

R307

4.7K

R313 4.7K

R311

10K

4

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

CLOCK STRAPPING RESISTORS

FS4

FS3

FS1

FS0

FS2

MODE

MUL0

MUL1

C_STP#

P_STP#

R13, R14 Support CY28324 install.

SMBCLK

SMBDATA

HD_RST#

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

R355

47K

R308 4.7K

Q25

NPN-3904LT1-S-SOT23

R93 49.9

MCHCLK#

R95 49.9

ITP_CLK

R74 49.9

ITP_CLK# ITP_CLK#

R78 49.9

R84 10K

R79 10K

R120 X_10K

R121 1K

R110 10K

R104 X_1K

R73 1K

R85 1K

R67 10K

R70 X_1K

R69 10K

R68 X_1K

R72 X_1K

R81 X_1K

R66 4.7K

R63 4.7K

C228

220p

R306 1K

HD_RST#

Q24

NPN-3904LT1-S-SOT23

VCC3V

VCC3V

/N

VCC3V

VCC3V

/N

VCC3V

/N

VCC3V

/N

/N

VCC3V

/N

VCC3_SB

IDE1

D2x20-1:21-WH-SBT

1

2

3 4

5 6

7 8

91110

13 14

17 18

19

21

23

25

27

29

31

33

35

37

R338

10K

VCC3

VCC5

3

SDD8

SDD9

SDD10

SDD11

SDD12

12

SDD13

SDD14

1615

SDD15

22

24

26

28

R337 470

30

32

34

36

38

4039

C229

/N/N

X_4700p

MSI

Title

Size Document Number Rev

Date: Sheet of

2

Pull-Down Capacitors

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLK

MCH_66

ICH_66

AGPCLK

ICH_PCLK

FWH_PCLK

PCICLK0

PCICLK1

PCICLK2

SIO_PCLK

APIC_CLK

ICH_48

SIO_48

ICH_14

AC_14

CODE_14

SIO_14

used only for EMI issue

Trace less 0.2"

SDD[8..15] (9)

SD_DET (9)

SD_A2 (9)

MICRO-STAR

CLOCK CY28324 & ATA100 IDE

MS-6514

X_10pC102

X_10pC105

X_10pC108

X_10pC110

X_10pC95

X_10pC96

X_10pC113

X_10pC114

X_10pC117

X_10pC97

X_10pC98

X_10pC107

X_10pC109

X_10pC111

X_10pC112

X_10pC103

10pC115

10pC119

10pC92

10pC88

10pC89

10pC90

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

3 23Monday, May 21, 2001

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

0B

1

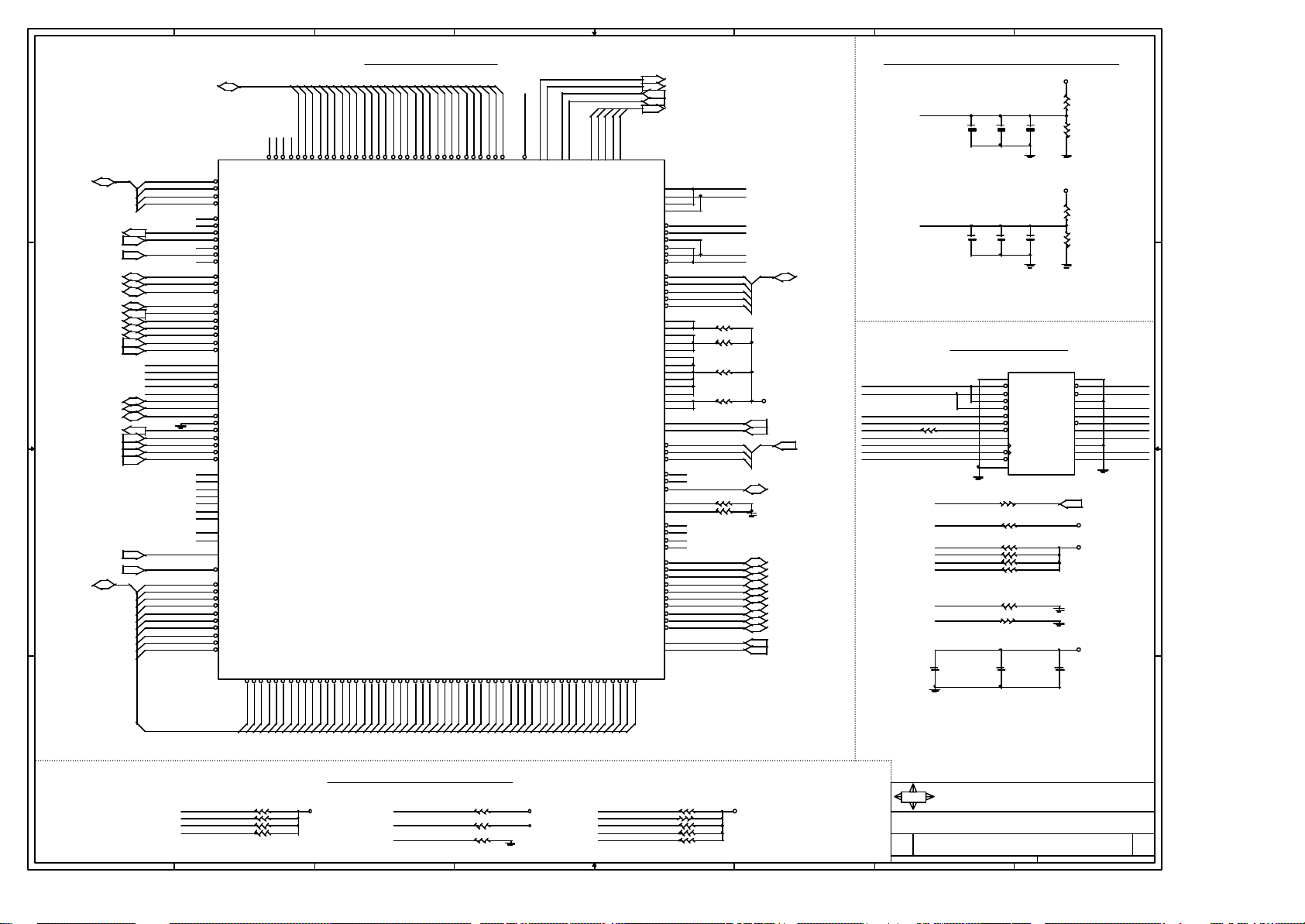

Page 4

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

VCCPS+ (20)

VID0

AE5

VID0#

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

COMP1

COMP0

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

LINT1/NMI

LINT0/INTR

D2#

D1#

D0#

A23

B22

B21

HD#0

HD#2

HD#1

VCCPS- (20)

ITP_CLK# (3)

ITP_CLK (3)

VID[0..4] (10,20)

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

DP3#

DP2#

DP1#

DP0#

SOCKET478

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

GTLREF2

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R127 4.7K

R136 4.7K

R129 4.7K

R135 4.7K

HRS#2

HRS#1

HRS#0

R144 49.9

R145 49.9

HREQ#[0..4] (6)

VCCP

CPUCLK# (3)

CPUCLK (3)

HRS#[0..2] (6)

HBR#0 (6)

* Short trace

HADSTB#1 (6)

HADSTB#0 (6)

HDSTBP#3 (6)

HDSTBP#2 (6)

HDSTBP#1 (6)

HDSTBP#0 (6)

HDSTBN#3 (6)

HDSTBN#2 (6)

HDSTBN#1 (6)

HDSTBN#0 (6)

NMI (8)

INTR (8)

BPM#0

BPM#1

BPM#4

BPM#5

CPURST#

ITP_TCK

ITP_CLK

ITP_CLK#

BPM#5

GTLREF1

GTLREF2

C136

220p

C135

2/3*Vccp

C128

2/3*Vccp

C129

220p

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

CPU ITP BLOCK

JTAG1

1 2

3

5

7

9

11

13

R221 0

ITP_RST#

15 16

17 18

19

21 22

23 24

25

JTAG

ITP_DBR#

R109 0

ITP_DBA#

R214 150

ITP_VCC

R219 1.5K

ITP_TMS

R216 39

ITP_RST#

R217 49.9

ITP_TDO

R220 75

ITP_TCK

R218 27

ITP_FBI

R222 X_220

CB178

0.1u

CB177

0.1u

ALL COMPONENTS CLOSE TO CPU

HA#[3..31](6)

HA#8

HA#22

HA#25

HA#23

HA#26

HA#27

HA#28

HA#30

HA#29

D D

U10A

HDBI#[0..3](6)

FERR#(8)

STPCLK#(8)

HDBI#0

HDBI#1

HDBI#2

HDBI#3

HINIT#(8)

HDBSY#(6)

HDRDY#(6)

HTRDY#(6)

HADS#(6)

HLOCK#(6)

HBNR#(6)

HIT#(6)

HITM#(6)

C C

B B

HBPRI#(6)

HDEFER#(6)

CPU_TMPA(10)

VTIN_GND(10)

TRMTRIP#(16)

PROCHOT#(9)

IGNNE#(8)

HSMI#(8)

A20M#(8)

SLP#(8)

CPU_GD(9)

CPURST#(6)

HD#[0..63](6)

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

TRMTRIP#

CPU_GD

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

G25

AC3

AA3

AB2

AF26

AB26

AD2

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

E21

P26

V21

V6

B6

Y4

W5

H5

H2

J6

G1

G4

G2

F3

E3

D2

E2

C1

D5

F7

E6

D4

B3

C4

A2

C3

B2

B5

C6

A22

A7

Y21

Y24

Y23

Y26

V24

DBI0#

DBI1#

DBI2#

DBI3#

IERR#

MCERR#

FERR#

STPCLK#

BINIT#

INIT#

RSP#

DBSY#

DRDY#

TRDY#

ADS#

LOCK#

BNR#

HIT#

HITM#

BPRI#

DEFER#

TDI

TDO

TMS

TRST#

TCK

THERMDA

THERMDC

THERMTRIP#

GND/SKTOCC#

PROCHOT#

IGNNE#

SMI#

A20M#

SLP#

RESERVED0

RESERVED1

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

D53#

V22

HD#53

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

U21

V25

U23

U24

U26

T23

T22

HD#48

HD#47

HD#51

HD#50

HD#46

HD#49

HD#52

D40#

T25

T26

R24

R25

P24

R21

HD#41

HD#45

HD#42

HD#44

HD#43

HD#40

HA#18

HA#24

A24#

A23#

D39#

D38#

N25

N26

HD#39

HD#38

M26

HD#37

A22#

D37#

N23

HA#16

HA#21

HA#20

HA#19

HA#17

A21#

A20#

A19#

A18#

A17#

A16#

D36#

D35#

D34#

D33#

D32#

D31#

M24

P21

N22

M23

H25

HD#32

HD#34

HD#31

HD#35

HD#33

HD#36

HA#9

HA#5

HA#4

HA#14

HA#10

HA#15

HA#11

HA#13

HA#12

A15#

A14#

A13#

A12#

A11#

A10#

D30#

D29#

D28#

D27#

D26#

D25#

K23

J24

L22

M21

H24

G26

HD#29

HD#26

HD#30

HD#28

HD#25

HD#27

HA#3

HA#7

HA#6

ITP_DBR#

AE25A5A4

AD26

A9#

A8#

A7#

A6#

A5#

A4#

A3#

DBR#

ITP_CLK1

VCC_SENSE

VSS_SENSE

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

D13#

D12#

D11#

L21

D26

F26

E25

F24

F23

G23

E24

H22

HD#19

HD#23

HD#24

HD#16

HD#22

HD#20

HD#18

HD#21

HD#17

D10#

D25

J21

D23

C26

H21

G22

HD#10

HD#14

HD#15

HD#11

HD#12

HD#13

AC26

ITP_CLK0

D9#

D8#

B25

C24

HD#8

HD#9

VID1

VID2

VID4

VID3

AE1

AE2

AE3

AE4

VID4#

VID3#

VID2#

VID1#

D7#

D6#

D5#

D4#

D3#

C23

B24

D22

C21

A25

HD#5

HD#4

HD#3

HD#7

HD#6

VCCP

C118

1u-0805220p

VCCP

C126

1u-0805220p

GND GND

BPM#0

DBA#

BPM#1

DBR#

BPM#2

GND

BPM#3

BPM#4

TMS

BPM#5

TRST#

RESET# TCK

FBO FBI

GND

BCLK

BCLK# VCC

BPM5DR# TDO

GND

/N

TDI

CB176

0.1u

R115

49.9

R116

100

R132

49.9

R134

100

4

6

8

10

12

14

20

ITP_GD (18)

VCC3

VCCP

VCCP

ITP_DBA#

ITP_DBR#

ITP_TDI

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_FBI

ITP_VCC

ITP_TDO

A A

BPM#0

BPM#1

BPM#4

BPM#5

8

R126 49.9

R128 49.9

R133 49.9

R130 49.9

7

CPU STRAPPING RESISTORS

VCCP VCCP VCCP

ITP_TDI

ITP_DBR#

ITP_TRST#

6

R177 150

R215 X_150

R139 680

/N

ALL COMPONENTS CLOSE TO CPU

PROCHOT#

CPU_GD

VCC5

5

HBR#0

CPURST#

TRMTRIP#

R141 62

R131 300

R176 49.9

R114 49.9

R175 62

4

MSI

Title

Size Document Number Rev

3

Date: Sheet of

2

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

INTEL mPGA478-B CPU1

MS-6514

4 23Monday, May 21, 2001

0B

1

Page 5

8

7

6

5

4

3

2

1

CPU VOLTAGE BLOCK

VCC_VID (19)

L1 4.7uH-1206

C121

22u-1206

L2 4.7uH-1206

C122

22u-1206

VCCP

D D

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AB10

C C

B B

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

AC22

AC25

AA1

AA4

AA7

AA9

AB3

AB6

AB8

AC2

AC5

AC7

AC9

AD1

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

F13

F15

F17

F19

VCC

VSS

VCC

VSS

G21G6G24

VCC

VCC

VSS

VSS

G3H1H23

VCC

VSS

VCC

VSS

F9

VCC

VSS

U10B

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VCC

VSS

VSS

VSS

VSS

VSS

VSS

F14

F16

F18F2F22

F25F5F8

D10

VSS

A11

VSS

A13

VSS

A15

VSS

A17

VSS

A19

VSS

A21

VSS

A24

VSS

A26

VSS

A3

VSS

A9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B23

B20

B26B4B8

C11

C13

C15

C17C2C19

C22

C25C5C7C9D12

D14

D16

D18

D20

D21D3D24D6D8E1E11

VSS

E13

E15

E17

E19

E23

E7E9F10

F12

E4

E26

AF4

VCC-VID

VSS

VSS

H26H4J2

AE23

AF3

VCC-VIDPRG

VSS

VSS

VSS

J22

J25J5K21

AD20

VCCA

VSSA

VCC-IOPLL

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SOCKET478

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VCCP

CPU DECOUPLING CAPACITORS

CB124

10u-1206

CB112

10u-1206

CB127

10u-1206

CB125

10u-1206

CB126

10u-1206

CB79

A A

10u-1206

CB150

10u-1206

CB153

10u-1206

CB147

10u-1206

CB145

10u-1206

CB152

10u-1206

CB78

10u-1206

CB77

10u-1206

CB76

10u-1206

CB151

10u-1206

CB128

10u-1206

CB154

10u-1206

CB155

10u-1206

CB144

10u-1206

CB149

10u-1206

CB148

10u-1206

CB146

10u-1206

CB156

10u-1206

CB81

10u-1206

CB82

10u-1206

CB83

10u-1206

CB72

10u-1206

CB75

10u-1206

CB73

10u-1206

CB74

10u-1206

CB80

10u-1206

CB65

0.1u

CB92

0.1u

CB49

0.1u

CB59

0.1u

CB28

0.1u

CB29

0.1u

CB31

0.1u

CB69

0.1u

CB30

0.1u

CB117

0.1u

CB68

0.1u

PLACE CAPS WITHIN CPU

CAVITY SOLDER

CB260

10u-1206

CB261

10u-1206

CB262

10u-1206

CB263

10u-1206

CB114

10u-1206

CB111

10u-1206

CB115

10u-1206

CB113

10u-1206

PLACE CAPS WITHIN CPU CAVITY

8

7

6

5

4

3

VCCPVCCP VCCP VCCPVCCP VCCPVCCP VCCP

+

CT39

150u-2.5V

+

CT41

150u-2.5V

MSI

Title

Size Document Number Rev

Date: Sheet of

INTEL mPGA478-B CPU2

2

C99 0.1u

VCCP

C258 X_0.1u

VCCP VCC5

C260 X_0.1u

VCCP

C257 X_0.1u

VCCP

C259 X_0.1u

VCCP

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

MS-6514

VCC5

/N

/N

VCC3

/N

/N

5 23Monday, May 21, 2001

1

0B

Page 6

5

HA#[3..31](4) HD#[0..63] (4)

D D

HBR#0(4)

HBNR#(4)

HBPRI#(4)

HLOCK#(4)

HADS#(4)

HREQ#[0..4](4)

C C

HIT#(4)

HITM#(4)

HDEFER#(4)

HTRDY#(4)

HRS#[0..2](4)

HDBSY#(4)

HDRDY#(4)

HADSTB#0(4)

HADSTB#1(4)

HDSTBN#0(4)

HDSTBP#0(4)

HDSTBN#1(4)

HDSTBP#1(4)

HDSTBN#2(4)

HDSTBP#2(4)

HDSTBN#3(4)

HDSTBP#3(4)

B B

A A

HDBI#[0..3](4)

MCHCLK(3)

MCHCLK#(3)

HL[0..10](8)

HL_STB(8)

HL_STB#(8)

5

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

R150 24.9

R138 24.9

HL0

HL1

HL2

HL3

HL4

HL5

VCCP

AD4

AD3

AE6

AE7

AE11

AD11

AC15

AC16

AD5

AG4

AH9

AD15

AC2

AC13

M26

M25

AA9

AB8

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

V7

W3

Y7

W5

V3

U6

T7

R7

U5

U2

Y5

Y3

Y4

U7

W2

W7

W6

V5

V4

R5

N6

J8

K8

P25

P24

N27

P23

N25

N24

M8

U8

U11A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

BR0#

BNR#

BPRI#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

RS0#

RS1#

RS2#

DBSY#

DRDY#

HAD_STB0#

HAD_STB1#

HD_STBN0#

HD_STBP0#

HD_STBN1#

HD_STBP1#

HD_STBN2#

HD_STBP2#

HD_STBN3#

HD_STBP3#

DBI0#

DBI1#

DBI2#

DBI3#

BCLK

BCLK#

H_RCOMP0

H_RCOMP1

HI0

HI1

HI2

HI3

HI4

HI5

HI_STB

HI_STB#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

Brookdale_MCH

HOST

HUB LINK

POWER

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

66IN

RSTIN#

CPURST#

H_VREF0

H_VREF1

H_VREF2

H_VREF3

H_VREF4

H_SWNG0

H_SWNG1

HI10

HI_REF

HL_RCOMP

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

RSVD0

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

NC0

NC1

4

3

HD#0

AA2

HD#1

AB5

HD#2

AA5

HD#3

AB3

HD#4

AB4

HD#5

AC5

HD#6

AA3

HD#7

AA6

HD#8

AE3

HD#9

AB7

HD#10

AD7

HD#11

AC7

HD#12

AC6

HD#13

AC3

HD#14

AC8

HD#15

AE2

HD#16

AG5

HD#17

AG2

HD#18

AE8

HD#19

AF6

HD#20

AH2

HD#21

AF3

HD#22

AG3

HD#23

AE5

HD#24

AH7

HD#25

AH3

HD#26

AF4

HD#27

AG8

HD#28

AG7

HD#29

AG6

HD#30

AF8

HD#31

AH5

HD#32

AC11

HD#33

AC12

HD#34

AE9

HD#35

AC9

HD#36

AE10

HD#37

AD9

HD#38

AG9

HD#39

AC10

HD#40

AE12

HD#41

AF10

HD#42

AG11

HD#43

AG10

HD#44

AH11

HD#45

AG12

HD#46

AE13

HD#47

AF12

HD#48

AG13

HD#49

AH13

HD#50

AC14

HD#51

AF14

HD#52

AG14

HD#53

AE14

HD#54

AG15

HD#55

AG16

HD#56

AG17

HD#57

AH15

HD#58

AC17

HD#59

AF16

HD#60

AE15

HD#61

AH17

HD#62

AD17

HD#63

AE16

P22

J27

AE17

HVREF

M7

R8

Y8

AB11

AB17

HSWNG

AA7

AD13

HL6

L28

HI6

HI7

HI8

HI9

L27

M27

N28

M24

P26

P27

L25

L29

M22

N23

N26

B19

C5

C8

C23

C26

D12

F26

H27

K23

K25

AD26

AD27

HL7

HL8

HL9

HL10

HUB_MREF

R163 40.2

VCC1_8

MCH_66 (3)

PCIRST#1 (3)

CPURST# (4,16)

VCC1_8

HL[0..10] (8)

VCC_AGP

VCC_DIMM

3

VTT1

VTT2

VTT_GND1

VTT_GND2

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

G29

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ11

AJ13

AJ15

AJ17

AJ27

R22

R29

U22

U26

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

T13

T17

A5

A9

A13

A17

A21

A25

C1

C29

D7

D11

D15

D19

D23

D25

F6

F10

F14

F18

F22

G1

G4

H8

H10

H12

H14

H16

H18

H20

H22

H24

J5

J7

K6

K22

K24

K26

L23

U13

U17

AJ3

AJ5

AJ7

AJ9

U11C

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

Brookdale_MCH

POWER

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

A3

A7

A11

A15

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J26

J29

K5

K7

K27

L1

L4

L6

L8

L22

L24

L26

M23

N1

N4

N8

N13

N15

N17

N22

N29

P6

P8

P14

P16

R1

R4

R13

R15

R17

R26

T6

T8

T14

T16

T22

U1

U4

U15

U29

V6

V8

V22

W1

W4

W8

W26

Y6

Y22

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

2

Title

Size Document Number Rev

Date: Sheet of

MCH REFERENCE BLOCK

VTT1

VTT_GND1

VTT2

VTT_GND2

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

HVREF

C130

0.01u

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

Place 0.01uF Cap. as Close as possible to MCH

Trace width use 15 mils and 15mils space

HSWNG

C140

HUB_MREF

CB94

0.1u

CB103

0.1u

C137

0.1u

C138

0.01u

C142

MCH Trace Decoupling Capacitors

VCCP VCCP VCC1_8

CB46

0.1u

CB47

0.1u

CB45

0.1u

ADDRESS DATA MCH & ICH2

MSI

1

L3 4.7uH-1206

C124

22u-1206

L4 4.7uH-1206

C125

22u-1206

VCCP

C139

/N

X_1u-0805

C127

C131

0.01u

0.01u

VCCP

C120

/N

X_0.01u

C132

C141

0.01u

0.01u

VCC1_8

C173

/N

X_0.01u

C143

C145

0.1u

0.1u

CB48

0.1u

CB42

0.1u

CB44

0.1u

CB43

0.1u

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Brookdale MCH1

MS-6514

6 23Monday, May 21, 2001

1

R137

301

R143

150

R157

49.9

R159

100

R161

150

R160

1500.01u

VCC_AGP

VCC_AGP

C144

0.1u0.01u

CB182

0.1u

CB188

0.1u

0B

Page 7

5

MD[0..63](13)

D D

C C

B B

A A

GAD[0..31](14)

GC_BE#[0..3](14)

5

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

R183 33

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

U11B

F27

SDQ0

E27

B28

C27

D26

E25

B25

D24

F23

B23

C22

C21

D20

C19

C18

C17

B13

E13

C12

B11

E11

C10

F9

C9

E8

E7

C7

D6

B5

D4

C3

B2

G28

E28

C28

D27

B27

F25

C25

E24

C24

E23

D22

E22

B21

C20

D18

E18

E14

C13

E12

F11

C11

E10

D10

B9

E9

D8

B7

E6

C6

C4

B3

D3

X_10pC159

G3

H3

R27

R28

T25

R25

T26

T27

U27

U28

V26

V27

T23

U23

T24

U24

U25

V24

Y27

Y26

AA28

AB25

AB27

AA27

AB26

Y23

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

V25

V23

Y25

AA23

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

RD_CLKIN

RD_CLKO

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

Brookdale_MCH

SDRAM

AGP

4

SMA10

SMA11

SMA12

SCS0#

SCS1#

SCS2#

SCS3#

SCS4#

SCS5#

SCS6#

SCS7#

SCS8#

SCS9#

SCS10#

SCS11#

SCKE0

SCKE1

SCKE2

SCKE3

SCKE4

SCKE5

SCK10

SCK11

SRAS#

SCAS#

SWE#

SM_RCOMP

SD_REF0

SD_REF1

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_STOP#

G_PAR

G_REQ#

G_GNT#

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

PIPE#

WBF#

AGPREF

G_RCOMP

TESTIN#

4

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SCB0

SCB1

SCB2

SCB3

SCB4

SCB5

SCB6

SCB7

SBS0

SBS1

SCK0

SCK1

SCK2

SCK3

SCK4

SCK5

SCK6

SCK7

SCK8

SCK9

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

RBF#

3

MA0

G22

MA1

E21

MA2

F21

MA3

G21

MA4

E20

MA5

G20

MA6

E19

MA7

F19

MA8

G19

MA9

G18

MA10

E17

MA11

E15

MA12

G12

MCS#0

H23

MCS#1

J23

MCS#2

G7

MCS#3

G8

MCS#4

J24

MCS#5

G24

MCS#6

H7

MCS#7

F7

MCS#8

G25

MCS#9

H25

MCS#10

G6

MCS#11

H6

MDP0

C16

MDP1

E16

MDP2

C15

MDP3

D14

MDP4

B17

MDP5

D16

MDP6

B15

MDP7

C14

MCKE0

G9

MCKE1

F4

MCKE2

G10

MCKE3

F5

MCKE4

G11

MCKE5 MCLK8

E5

F17

G17

CLK0

F13

CLK1

G13

CLK2

E2

CLK3

C2

CLK4

G15

CLK5

G14

CLK6

F3

CLK7

E3

CLK8

G16

CLK9

F15

CLK10

H5

CLK11

G5

G23

J25

G27

J28

R182 20.5

SM_REF

J9

J21

Y24

W27

W24

W28

W23

W25

AG24

AH25

SBA0

AH28

SBA1

AH27

SBA2

AG28

SBA3

AG27

SBA4

AE28

SBA5

AE27

SBA6

AE24

SBA7

AE25

AF27

AF26

ST0

AG25

ST1

AF24

ST2

AG26

R24

R23

AC27

AC28

AF22

AE22

AE23

CB118 0.1u

AA21

AD25

R147 40.2

H26

MA[0..12] (13)

MCS#[0..11] (13)

MDP[0..7] (13)

MCKE[0..5] (13)

MBS0 (13)

MBS1 (13)

MRAS# (13)

MCAS# (13)

MWE# (13)

GFRAME# (14)

GIRDY# (14)

GTRDY# (14)

GDEVSEL# (14)

GSTOP# (14)

GPAR (14)

GREQ# (14)

GGNT# (14)

SBA[0..7] (14)

SB_STB (14)

SB_STB# (14)

ST[0..2] (14)

GAD_STB0 (14)

GAD_STB#0 (14)

GAD_STB1 (14)

GAD_STB#1 (14)

PIPE# (14)

RBF# (14)

WBF# (14)

AGPREF (14)

MCH MEMORY CLOCK RC CIRCUITS

MCLK[0..11](13)

VCC1_8 VCC_DIMMVCC_AGP VCCP

CB141

1u-0805

CB143

0.1u

CB157

0.1u

CB163

100p

CB167

10p

0.1uC133

C134 1u-0805

0.1uC247

0.1uC248

0.1uC249

0.1uC246

0.1uC253

VCC1_8

VCC_DIMM

VCC_DIMM

VCC_AGP

Put MCH845 solder side

3

2

MCH REFERENCE VOLTAGE

VCC_DIMM

SM_REF

MCLK0

MCLK1

MCLK2

MCLK3

MCLK4

MCLK5

MCLK6

MCLK7

MCLK9

MCLK10

MCLK11

C151

0.1u

C174

0.1u

R234 10

R228 10

R197 10

R203 10

R233 10

R232 10

R193 10

R194 10

R231 10

R230 10

R187 10

R191 10

C175

1u-0805

CLK0

CLK1

CLK2

CLK3

CLK4

CLK5

CLK6

CLK7

CLK8

CLK9

CLK10

CLK11

MCH DECOUPLING CAPACITOR

CB159

1u-0805

CB174

0.1u

CB169

0.1u

CB168

100p

CB172

10p

0.1uC221

0.1uC209

0.1uC189

0.1uC123

0.1uC116

CB107 0.1u0.1uC252

Brookdale MCH2 & AGP SLOT

VCC_AGP

VCC_AGP

VCC_AGP

AGPREF

2

CB120

1u-0805

CB106

0.1u

CB129

100p

CB108

10p

VCC_DIMM VCC5

VCC3

VCC3 VCCP

VCC2_5VCC_DIMM

MSI

Title

Size Document Number Rev

Date: Sheet of

R226

49.9

R227

49.9

C181 X_22p

C176 X_22p

C171 X_22p

C172 X_22p

C180 X_22p

C179 X_22p

C166 X_22p

C167 X_22p

C178 X_22p

C177 X_22p

C160 X_22p

C162 X_22p

VCC_AGP

MICRO-STAR

1

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

/N

CB100

0.1u

CB101

0.1u

CB97

0.1u

CB98

0.1u

CB99

0.1u

CB91

10u-1206

CB90

10u-1206

VCC5 VCC3

0.1uC82

0.1uC91

0.1uC190

0.1uC86

0.1uC100

0.1uC101

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

MS-6514

7 23Monday, May 21, 2001

1

0B

Page 8

ICH2 PCI / HUB LINK / CPU / LAN / INTERRUPT SIGNALS

ICH2 SMI# SIGNAL

VCC1_8

D10D2E5

K19

L19P5V9

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

GND1

GND2

GND3

GND4

GND5

A1A2A10B1B2B3B9

E14

GND6

AD[0..31](15)

C_BE#[0..3](15)

DEVSEL#(15)

FRAME#(15)

IRDY#(15)

TRDY#(15)

STOP#(15)

PAR(15)

PLOCK#(15)

SERR#(15)

PERR#(15)

PME#(14,15)

ICH_PCLK(3)

PCIRST#(3)

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

GP0

DOUT

AA4

AB4

AB3

AA5

AB5

AA6

AA8

AB8

AB9

W10

AA10

AA3

AB6

AA9

AB7

AA7

W11

AA15

Y4

W5

W4

Y5

Y3

W6

W3

Y6

Y2

Y1

V2

V1

U4

W9

U3

Y9

U2

U1

T4

Y10

T3

Y8

V3

W8

V4

W1

W2

W7

Y7

Y15

M3

L2

F4

G4

H3

H4

J1

K4

K3

J4

J3

U16A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE#0

CBE#1

CBE#2

CBE#3

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

GPIO0/REQA#

GPIO16/GNTA#

PCICLK

PCIRST#

NC12

NC13

NC14

NC15

NC16

EE_CS

EE_DIN

EE_DOUT

EE_SHCLK

VCC1.8

VCC3

E15

E16

E17

E18

F18

G18

H18

J18

P18

R18R5T5U5V5V6V7V8V14

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

B10C2C3C4C9D5D6D7D8D9E6E7E8E9J9

GND19

VCC3

VCC3

GND20

GND21

VCC3

VCC3

GND22

GND23

J10

VCC3

GND24

J11

J12

VCC1_8SB

V15

V16H5J5

VCCSUS1_8

VCCSUS1_8

GND25

GND26

GND27

J13

J14K9K10

A22

VCCSUS1_8

VCCSUS1_8

VCCSUS1_8

GND28

GND29

GND30

GND31

K11

K12

K13

B21

B22C1D1D3E1E2E3

GND68

GND69

GND70

GND71

GND32

GND33

GND58

GND59

K14J2K1

AA1

AA2

E4

NC5

NC6

NC8

NC9

CPUSLP#

NC10

NC11

NC17

FERR#

IGNNE#

STPCLK#

A20GATE

HL_STB

HL_STB#

HLCOMP

HUBREF

PIRQA#

PIRQB#

PIRQC#

PIRQD#

APICCLK

APICD0

APICD1

SERIRQ

REQ0#

REQ1#

REQ2#

REQ3#

LAN_RSTSYNC

GND62

GND63

GND64

AB1

AB2

AB21

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

LAN_CLK

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

GND67

GND65

GND66

INT-82801BA-VB1

GPIO1/REQB#/REQ5#

GPIO17/GNTB#/GNT5#

GND60

GND61

AA21

AA22

A20M#

INIT#

INTR

NMI

SMI#

RCIN#

HL10

HL11

IRQ14

IRQ15

SMI#

R264 33

C191

100pC193

R297 62

R303 150

R310 150

R304 4.7K

R267 10K

R271 10K

R223 2.7K

R225 X_10K

R235 10K

C187

0.1u

D11

A12

FERR#

R22

A11

C12

C11

B11

SMI#

B12

C10

KB_RST#

B13

A20GATE#

C13

HL0

A4

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

B5

A5

B6

B7

A8

B8

A9

C8

C6

C7

C5

A6

A7

A3

B4

P1

P2

P3

N4

F21

C16

N20

P22

N19

N21

R2

R3

T1

AB10

P4

L3

M2

M1

R4

T2

R1

L4

G3

H2

G2

G1

H1

F3

F2

F1

A21

AB22

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

R240 40.2

HUB_IREF

APIC_CLK

APIC_D0

APIC_D1

SERIRQ

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PREQ#5

PGNT#0

PGNT#1

PGNT#2

PGNT#3

LAN_CLK

A20M# (4)

SLP# (4)

FERR# (4)

IGNNE# (4)

HINIT# (4,12)

INTR (4)

NMI (4)

STPCLK# (4)

KB_RST# (10)

A20GATE# (10)

HL[0..10] (6)

This resistor less than 0.5"

from ICH use 15 mils trace

HL_STB (6)

HL_STB# (6)

VCC1_8

INTA# (14,15)

INTB# (14,15)

INTC# (15)

INTD# (15)

IRQ14 (3)

IRQ15 (3)

APIC_CLK (3)

SERIRQ (10)

PREQ#[0..5] (15)

PGNT#[0..3] (15)

ICH2 STRAPPING RESISTORS

FERR#

APIC_D0

APIC_D1

SERIRQ

KB_RST#

A20GATE#

GP0

DOUT

LAN_CLK

ICH2 REFERENCE VOLTAGE

HUB_IREF

C182

0.01u

C183

0.1u

/N

HSMI# (4)

VCC1_8

VCCP

VCC3

VCC3

VCC5

R241

150

R245

1500.01u

VCC3

CB186

0.1u

CB214

0.1u

Place one 0.1U/0.01U pair in each corner and

2 on opposite sides close to ICH2 if it fit

CB184

0.1u

CB105

0.1u

CB64

CB210

0.1u 0.01u

ICH2 DECOUPLING CAPACITORS

CB203 CB161

0.01u

CB185

0.1u

0.1u

Distribute near the 1.8V

power pin of the ICH2

VCC1_8SBVCC1_8

CB180

CB202

0.1u

0.1u

Distribute near the VCC1_8SB

Power pin of the ICH2

Place Cap. as Close as possible to ICH2

Trace width use 15 mils and 15mils space

MSI

Title

Size Document Number Rev

Date: Sheet of

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Brookdale ICH2 PCI

MS-6514

8 23Monday, May 21, 2001

0B

Page 9

ICH2 ASIC / RTC / AC'97 / GPIO / LPC / USB / IDE SIGNALS

VCC5VCC3

D12

D13

VCPU_IO1

VCPU_IO2

GND49

GND50

N12

N13

N14P9P10

1N5817-S-DO-241AC

V19K2M20

VCC5REF_SUS

GND51

GND52

GND53

GND54

P11

P12

GND55

VCC3_SB

RTC_VCC

U21

T18

GND34

GND35

L10

L11

VCCRTC

GND36

GND37

L12

GND38

L13

L14M9M10

U18

VCC3SUS1

GND39

GND40

SLP_S3#(18,19)

SLP_S5#(19)

PWR_GD(18)

CPU_GD(4)

VRM_GD(20)

PWRBTN#(18)

RING#(16)

SUSCLK(10)

SMBDATA(3,10,13)

SMBCLK(3,10,13)

SM_LNK0(15)

SM_LNK1(15)

ICH_66(3)

ICH_14(3)

ICH_48(3)

AC_RST#(11)

AC_SYNC(11)

AC_SDOUT(11)

AC_SDIN0(11)

SPKR(16)

EXTSMI#(10)

SIO_PME#(10)

GP21(18)

GP22(16)

GP27(18)

LAD0/FWH0(10,12)

LAD1/FWH1(10,12)

LAD2/FWH2(10,12)

LAD3/FWH3(10,12)

LDRQ#(10)

LFRAME#/FWH4(10,12)

USBP0+(17)

USBP0-(17)

USBP1+(17)

USBP1-(17)

USBP2+(17)

USBP2-(17)

USBP3+(17)

USBP3-(17)

OC#2(17)

OC#1(17)

THRM#

PWR_GD

RING#

RSMRST#

SMB_ALERT

SM_LNK0

SM_LNK1

INTRUDER#

RTCRST#

VBIAS

RTCX2

BCLK

AC_SDIN0

AC_SDIN1

EXTSMI#

SIO_PME#

GP21

GP22

GP27

R261 X_10K

AA13

W16

AB18

W21

AA17

AA18

AA16

AB16

AB17

W22

W14

AB15

AB14

AA14

W12

AB13

AB12

/N

AA12

W13

AB11

W17

AB19

AA19

W18

AB20

AA20

W19

W20

U16B

THRM#

SLP_S3#

SLP_S5

R20

PWROK

A13

CPUPWRGD

B15

VRMPWRGD

PWRBTN#

RI#

R21

RSMRST#

Y16

RSM_PWROK

Y17

SUSSTAT#

SUSCLK

SMBDATA

SMBCLK

GPIO11/SMBALERT#

U19

SMLINK0

V20

SMLINK1

T19

INTRUDER#

T20

RTCRST#

T21

VBIAS

U22

RTCX1

T22

RTCX2

D4

CLK66

M19

CLK14

P20

CLK48

V22

AC_RST#

P19

AC_SYNC

R19

AC_BITCLK

P21

AC_SDOUT

Y22

AC_SDIN0

AC_SDIN1

N22

SPKR

GPIO12

GPIO13

L1

GPIO21

B14

GPIO22

A14

GPIO23

GPIO27

GPIO28

Y12

LAD0/FWH0

LAD1/FWH1

LAD2/FWH2

LAD3/FWH3

FS0

Y13

LDRQ0#

LDRQ1#

LFRAME#/FWH4

USBP0+

Y18

USBP0USBP1+

USBP1USBP2+

Y19

USBP2USBP3+

USBP3OC0#

Y20

OC1#

Y21

OC2#

OC3#

L9

F5G5V17

VCC3SUS2

VCC3SUS4

VCC3SUS5

VCC3SUS6

GND41

GND42

GND43

GND44

M11

M12

M13

V18

VCC3SUS7

GND45

GND46

M14N9N10

GND47

VCCP VCC5_SB

GND48

N11

PDCS1#

SDCS1#

PDCS3#

SDCS3#

VCC5REF1

VCC5REF2

PDDREQ

SDDREQ

PDDACK#

SDDACK#

PDIOR#

SDIOR#

PDIOW#

SDIOW#

PIORDY

SIORDY

GPIO2/PIRQE#

GPIO3/PIRQF#

GPIO4/PIRQG#

GPIO5/PIRQH#

GPIO6

GPIO7

GPIO8

GPIO18

GPIO19

GPIO20

GPIO24

GND56

GND57

GPIO25

INT-82801BA-VB1

P13

P14

PDA0

PDA1

PDA2

SDA0

SDA1

SDA2

PDD0

PDD1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

TP0

D3

E21

C15

E19

D15

F20

F19

E22

A16

D16

B16

G22

B18

F22

B17

G19

D17

G21

C17

G20

A17

H19

H22

J19

J22

K21

L20

M21

M22

L22

L21

K22

K20

J21

J20

H21

H20

D18

B19

D19

A20

C20

C21

D22

E20

D21

C22

D20

B20

C19

A19

C18

A18

U20

N3

N2

N1

M4

Y11

AA11

Y14

A15

D14

C14

V21

W15

CB179

0.1u

R302

1K

CB212

0.1u

PDD0

PDD1RTCX1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

BATLOW#

PD_DET

SD_DET

USB_SENS

PWR_LED

GP25

PD_CS#1 (3)

SD_CS#1 (3)

PD_CS#3 (3)

SD_CS#3 (3)

PD_A0 (3)

PD_A1 (3)

PD_A2 (3)

SD_A0 (3)

SD_A1 (3)

SD_A2 (3)

PD_DREQ (3)

SD_DREQ (3)

PD_DACK# (3)

SD_DACK# (3)

PD_IOR# (3)

SD_IOR# (3)

PD_IOW# (3)

SD_IOW# (3)

PD_IORDY (3)

SD_IORDY (3)

INTE# (15)

INTF# (15)

INTG# (15)

INTH# (15)

PD_DET (3)

SD_DET (3)

USB_SENS (17)

PWR_LED (18)

GP25 (18)

JBAT1 Clear CMOS

PDD[0..15] (3)

SDD[0..15] (3)

Normal1 - 2

*

Clear CMOS2 - 3

VCC5_SBVCC3_SB

R391

R401

X_1K

0

R392

X_3K

R353

1K R309 10M

BAT1

PROCHOT BLOCK

R256 4.7K

VCCP

NPN-3904LT1-S-SOT23

PROCHOT#(4)

INTRUDER#

PD_IORDY

SD_IORDY

THRM#

GP21

PWR_LED

PD_DET

SD_DET

AC_SDIN0

AC_SDIN1

RSMRST#

SPKR

PWR_GD

VCC3_SB

R293 10K

R299 4.7K

R274 4.7K

R263 10K

R427 4.7K

R420 4.7K

R315 10K

R317 10K

R374 10K

R375 10K

R273 10K

R292 X_10K

R305 8.2K

X_2.2u-0805

D5

1N4148-S-LL34

D6

1N5817-S-DO-241AC

0.047uC241

RTC_VCC

R352 300K

C232

R387

0.047u

X_20M

R298 10M

R373

C211

X_5.6M

15p

X3

32K-12.5pf-CSA-309-D

+-20PPM

12.5pF

CODEC CLOCK

THRM#

Q21

AC_BCLK(11)

AC_14(3)

ICH2 STRAPPING RESISTORS

RTC_VCC

VCC3

/N

SM_LNK0

SM_LNK1

BATLOW#

SMB_ALERT

EXTSMI#GP22

SIO_PME#

GP25

GP27

RING#

RSMRST#

USB_SENS

R275 4.7K

R265 4.7KR270 4.7K

R266 4.7K

R411 4.7K

R412 4.7K

R269 8.2K

R268 1K

R179 10K

RESUME RESET CIRCUIT BLOCK

C186

/N

5 6R244 X_100K

/N

U15D

U15C

74LCX14-SOIC14

(VCC3_SB)

9 8 R262 X_0

RTC BLOCK

1

JBAT1

2

D1x3-BK

3

R372

1K

R295 X_33

R28 33

1 2

3 4

RN18

5 6

4.7K

7 8

C192

/N

X_1u-0805

/N

RTCRST#

VBIAS

RTCX1

RTCX2

C212

15p

/N

VCC3_SB

VCC3_SB

RSMRST#

BCLK

ICH2 DECOUPLING CAPACITOR

VCC3_SB

CB193

0.1u

VCCP VCC5_SB

CB181

0.1u

CB191

0.1u

CB199

0.1u

RTC_VCC

CB213

0.01u

Distribute near the VCC3_SB power pin of the ICH

CB247

0.1u

VCC5_SBVCC5

CB201

0.1u J3

INTERUDER

INTRUDER#

MSI

Title

1

2

Size Document Number Rev

X_YJ102

Date: Sheet of

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

Brookdale ICH2 OTHER

MS-6514

9 23Monday, May 21, 2001

0B

Page 10

LPC SUPER I/O LPC47M142

H/W MONITOR -- INTEL HECETA6

U13

PCIRST#1(3)

SIO_PCLK(3)

SERIRQ(8)

LDRQ#(9)

LFRAME#/FWH4(9,12)

LAD0/FWH0(9,12)

LAD1/FWH1(9,12)

LAD2/FWH2(9,12)

LAD3/FWH3(9,12)

SYS_CTR1(18)

SYS_CTR2(18)

SYS_FAN1(18)

SYS_FAN2(18)

ITR_LED(18)

SUS_LED(18)

EXTSMI#(9)

SIO_PME#(9)

USBP4+(17)

USBP4-(17)

USBP5+(17)

USBP5-(17)

USBP6+(17)

USBP6-(17)

VCC3_SB

VCC3_SB

VCC3_SB

SUSCLK(9)

SIO_14(3)

SIO_48(3)

VCC3

GP20L(12)

USB0+(17)

USB0-(17)

R229 4.7K

SUS_LED

SIO_ADDR

USB0+

USB0-

R198 4.7K

R199 4.7K

OC#2(17)

R205 4.7K

R210 4.7K

VCC3

VCC3

26

LRESET#

29

LCLK

30

SERIRQ

25

LDRQ#

24

LFRAME#

27

LPC_PD#

20

LAD0

21

LAD1

22

LAD2

23

LAD3

32

JB11/GP10

33

JB12/GP11

34

JB21/GP12

35

JB22/GP13

36

JX1/GP14

37

JY1/GP15

38

JX2/GP16

39

JY2/GP17

41

GP20/P17

46

MIDI_IN/GP25

47

MIDI_OUT/GP26

55

FAN_CTL1/GP33

54

FAN_CTL2/GP32

52

FAN_SEN1/GP31

51

FAN_SEN2/GP30

48

LED1/GP60

49

LED2/GP61

45

SYSOPT/GP24

50

IO_SMI#/GP27

17

IO_PME#/GP42

28

DDRC/GP43

103

USB+

104

USB-

105

PD1+

106

PD1-

107

PD2+

108

PD2-

109

PD3+

110

PD3-

111

PD4+

112

PD4-

118

OC#1

119

OC#2

120

OC#3

121

OC#4

114

EN#1

115

EN#2

116

EN#3

117

EN#4

126

STRP#0

127

STRP#1

6

SUSCLK

19

CLK_14M

123

CLKI_24M/CLK_48M

124

CLKO_24M

44

VREF

40

AVSS

53

VCC3_1

65

VCC3_2

93

VCC3_3

125

VCC3_4

SMSC LPC47M142

DRVDEN0/GP40

DRVDEN1/GP41

DS#1/GP21/P16

MTR#1/GP22/P12

RXD2/GP52/IRRX

CTS#2/GP56

DCD#2/GP51

DSR#2/GP54

TXD2/GP53/IRTX

RTS#2/GP55

DTR2#/GP57

KBRST#/GP36

INDEX#

MTR#0

DS#0

DIR#

STEP#

WDATA#

WGATE#

TRACK0#

WP#

RDATA#

HEAD#

DSKCHG#

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

SLCT

BUSY

ACK#

SLIN#

INIT#

ERR#

AFD#

STB#

IRRX/GP34

IRTX/GP35

RI#1

RXD1

CTS#1

DCD#1

DSR#1

TXD1

RTS#1

DTR#1

RI2#/GP50

GA20/GP37

KBDATA

KBCLK

MSDATA

MSCLK

VTR1

VTR2

VTR3

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

1

2

13

3

42

5

43

8

9

10

11

14

15

16

12

4

68

69

RN17

70

33

71

72

73

RN16

33

74

75

77

78

PE

79

80

67

66

81

82

83

61

62

90

84

88

91

86

85

87

89

92

95

99

94

97

96

98

100

64

63

56

57

58

59

18

113

122

7

31

60

76

101

102

128

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

A20GATE#

KB_RST#

VCC3_SB

LP_D0

LP_D1

LP_D2

LP_D3

LP_D4

LP_D5

LP_D6

LP_D7

GP34

DRVDEN0 (16)

DRVDEN1 (16)

INDEX# (16)

MOT_A# (16)

DRV_B# (16)

DRV_A# (16)

MOT_B# (16)

DIR# (16)

STEP# (16)

WT_DT# (16)

WT_EN# (16)

TRACK0# (16)

WP# (16)

RDATA# (16)

HEAD# (16)

DSKCHG# (16)

LP_D[0..7] (16)

LP_SLCT (16)

LP_PE (16)

LP_BUSY (16)

LP_ACK# (16)

LP_SLIN# (16)

LP_INIT# (16)

LP_ERR# (16)

LP_AFD# (16)

LP_STB# (16)

GP34 (12)

GP35 (12)

RIA# (16)

SINA (16)

CTSA# (16)

DCDA# (16)

DSRA# (16)

SOUTA (16)

RTSA# (16)

DTRA# (16)

A20GATE# (8)

KB_RST# (8)

KBDATA (16)

KBCLK (16)

MSDATA (16)

MSCLK (16)

VID[0..4](4)

SMBCLK(3,9,13)

SMBDATA(3,9,13)

VID4

VID3

VID2

VID1

VID0

+12V

VCC5

VCC3

VCCP

H/W MONITOR DECOUPLING CAPACITORS

VCC3 VCC5 VCCP

CB173

X_0.1u

LPC I/O DECOUPLING CAPACITORS

VCC3 VCC3_SB

U9

5

VID0

6

VID1

7

VID2

8

VID3

19

VID4

21

+12V

20

VCC5

4

VCC3

22

2.5V

23

VCCP

2

SCL

1

SDA

3

GND

X_INTEL HECETA4/6

REMOT1-/TEST_IN#

PWM1/TEST_OUT#

TACH4/SLCT

/N

REMOT1+

REMOT2+

REMOT2-

PWM2

PWM3/EN#

TACH1

TACH2

TACH3

18

17

15

16

24

10

13

11

12

9

14

ADDR.=101110XB

CB139

0.1u

CB171

0.1u

VCC3

CB89

X_0.1u

CB32

0.1u

CB162

0.1u

+12V

CB13

X_0.1u

LPC I/O STRAPPING RESISTOR

CB165

0.1u

CB233

0.1u

CB187

0.1u

CPU_TMPA (4)

VTIN_GND (4)

PWM (18)

CPU_FAN (18)

CB67

/N/N/N/N

X_0.1u

GP34

A20GATE#

KB_RST#

SIO_ADDR

SYS_ADDR

H: 0x04E

L: 0x02E

R192 1K

R186 X_4.7K

R190 X_4.7K

R206 X_4.7K

R204 4.7K

(DEFAULT)

VCC5

VCC3

/N

VCC3

MSI

Title

Size Document Number Rev

Date: Sheet of

USB0+

SUS_LED

R173 1.5K

R388 10K

MICRO-STAR

H/W Project Leader : Andy Chen

H/W Project Engineer : Prudence Wang

VCC3_SB

LPC I/O LPC47M142 & H/W MONITOR HECETA6

MS-6514

10 23Monday, May 21, 2001

0B

Page 11

+5VR

/N

R17 4.7K

/N

/N

AUX_L

AUX_R

CD_L

CD_GND

CD_R

VCC5VCC3

R4 47K

U2

1

DVDD1

9

DVDD2

4

DVSS1

7

DVSS2

2

XTL_IN

3

XTL_OUT

11

RESET#

8

SDATA_IN

5

SDATA_OUT

10

SYNC

6

BIT_CLK

12

PC_BEEP

PHONE

1314151617181920212223

FB9 120

VCC3

CB3

CB6

0.1u

0.1u

X_IN

X_OUT

AC_RST#(9)

AC_SDIN0(9)

AC_SDOUT(9)

AC_SYNC(9)

AC_BCLK(9)

CODE_14(3)

C255 0.1u

LINE_ROUT

R30 X_10

R29 10

X_10pC62

C256 0.1u

PUT SOLDER

C24 1u-0805

VCC5

R15 X_0

4847464544424140394338

NC

NC

AVSS2

TEST6

TEST5

TEST4

TEST2

TEST1

DACOUTL

DACOUTR

AD1885

AUXL

AUXR

VIDEOL

VIDEOR

CDL

CDGND

CDR

2

-12VR

+

-

8 4

C5 1u-0805

MIC1

37

AVDD2

MIC2

U1A

TI-TL072CDR-SOIC83

MONO

LINL

1

LOUTR

LOUTL

AFILT2

AFILT1

LINR

24

NC

NC

VRDA

VRAD

NC

VREF

AVDD1

AVSS1

ADI-AD1885

C16 1u-0805

C22 1u-0805

36

35

34

33

32

31

30

29

28

27

25

26

CB2

0.1u

LINE_ROUT

LINE_LOUT

VREF_OUT

CB1

0.1u

R6 15K

R9 15K

C32

0.01u

CT1 47u

+5VR

+

AC'97 AUDIO CODE AD1885 / CS4299 CHIPSET

C14 X_0.22u

+5VR

+

+5VR

C10

CT2

0.1u

10u

R7 15K

R10 15K

VREF_OUT

R12 1.5K

C251 1u-0805

R13 220C27 1u-0805

R5 33

C9

X_0.1u

/N

R2 X_2.2K

R11 2.2K

C23 0.1u

FB2 120

C7

C12

1000p

/N

C4

1u-0805C31u-0805

C15

1000p

C20

1000p

C26

1000p

AUDIO CODE CRYSTAL CIRCUIT

X1

16pF

/N

C30

1u-0805

/N

CB4

0.1u

+5VR

C51

0

C29

1u-0805

O1I

+12VR+12V

2

3

G

FB8 120FB4 120

TOP VIEW

X_OUT X_IN

C54

X_22p

/N

C13 0.1u

C2

/N

X_1u-0805270pC8270p

CB16

0.1u

+12V

C37

1u-0805

2

3

4

5

1

2

3

4

5

1

C6

0.047u

AUDIO2

L_IN

AUDIO1

MIC

R27 X_10M

X_24M-16pf-HC49S-D

/N

AUDIO CODE REGULATORS

-12VR-12V

C18

1u-0805

VR1

L78L05-TO92-100mA

3 1

VIN VOUT