Page 1

8

7

6

5

4

3

2

1

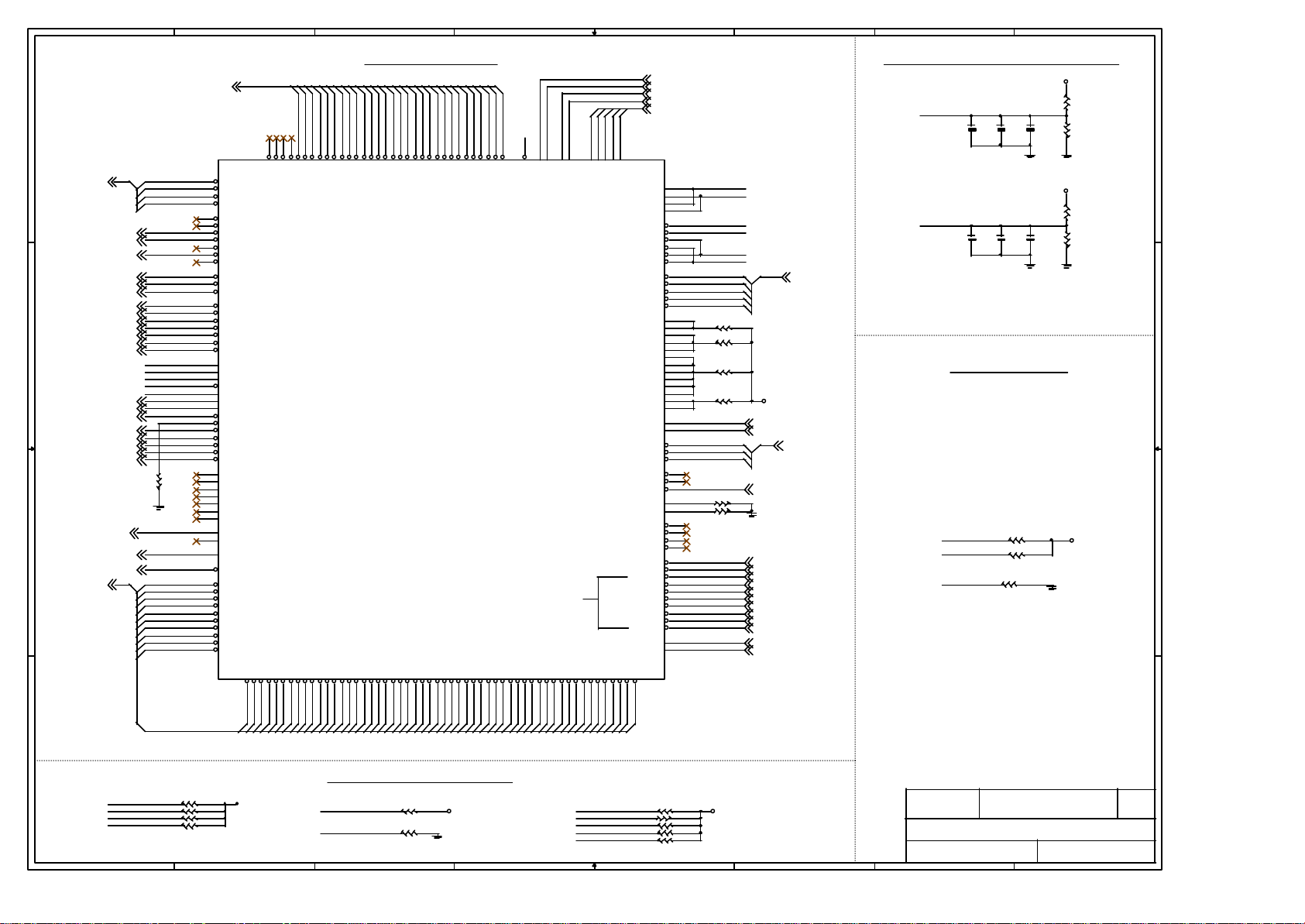

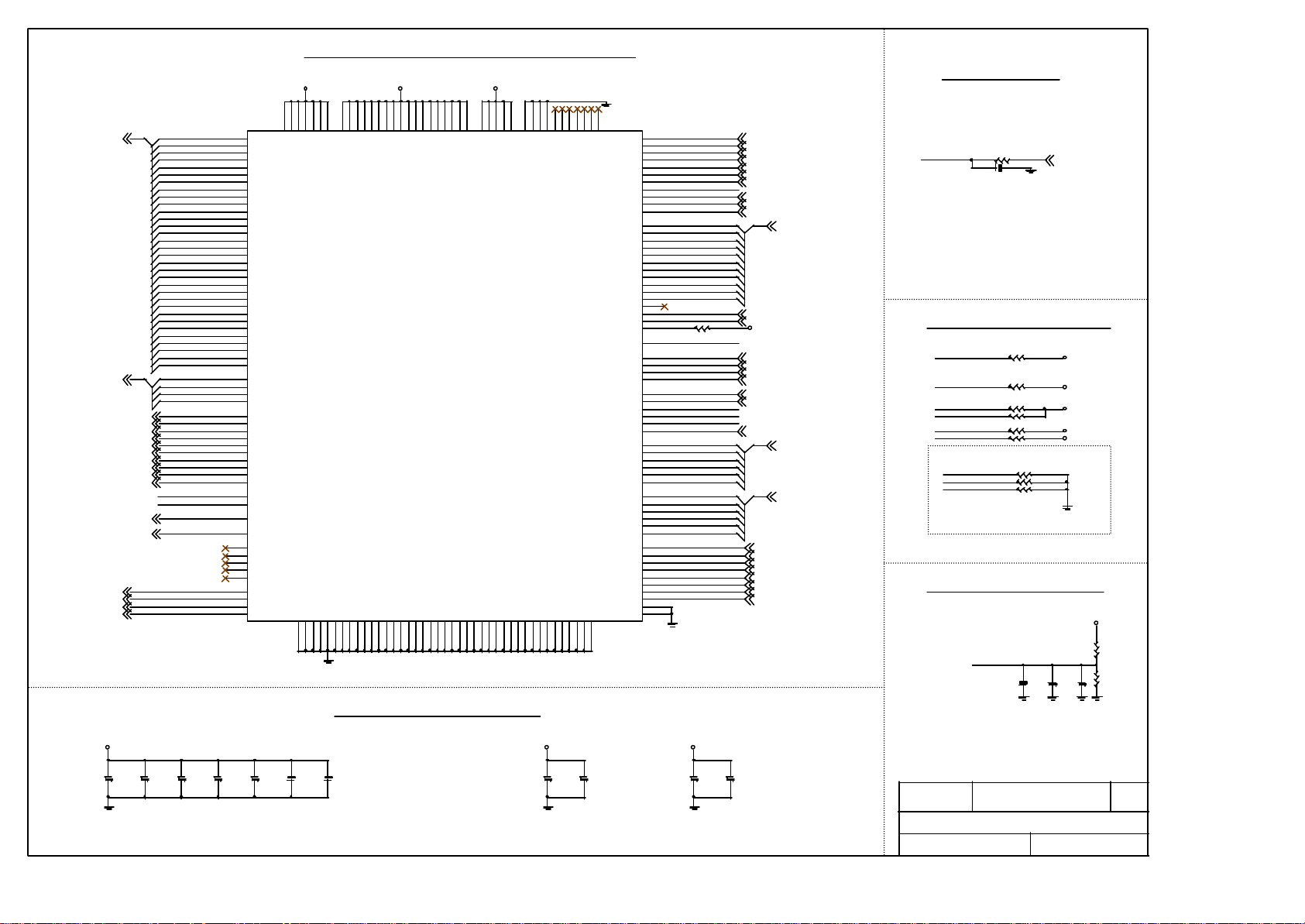

Cover Sheet

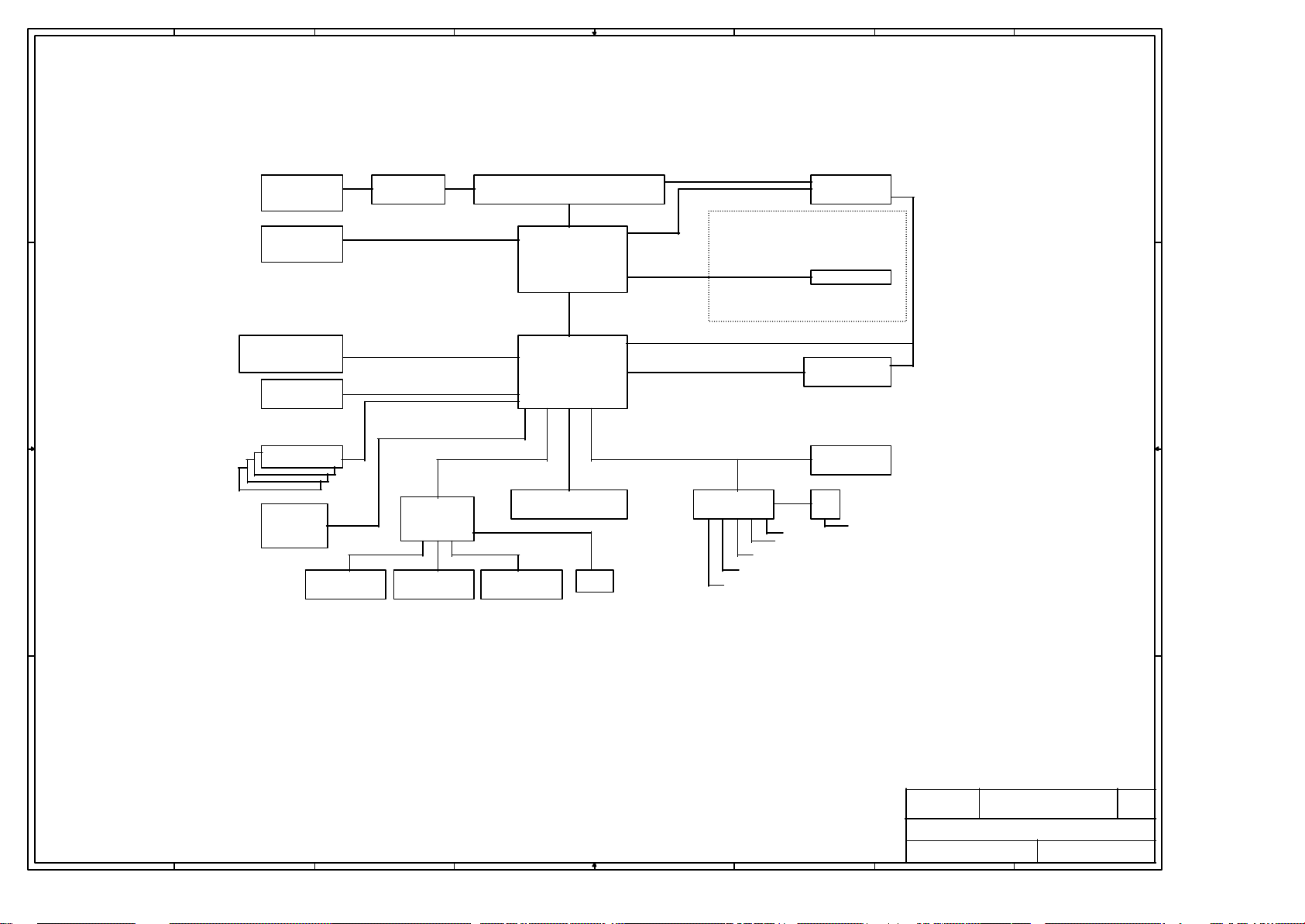

Block Diagram

1

2

MS-6507

Version 0B

06/29/2001 Update

INTEL (R) Brookdale Chipset

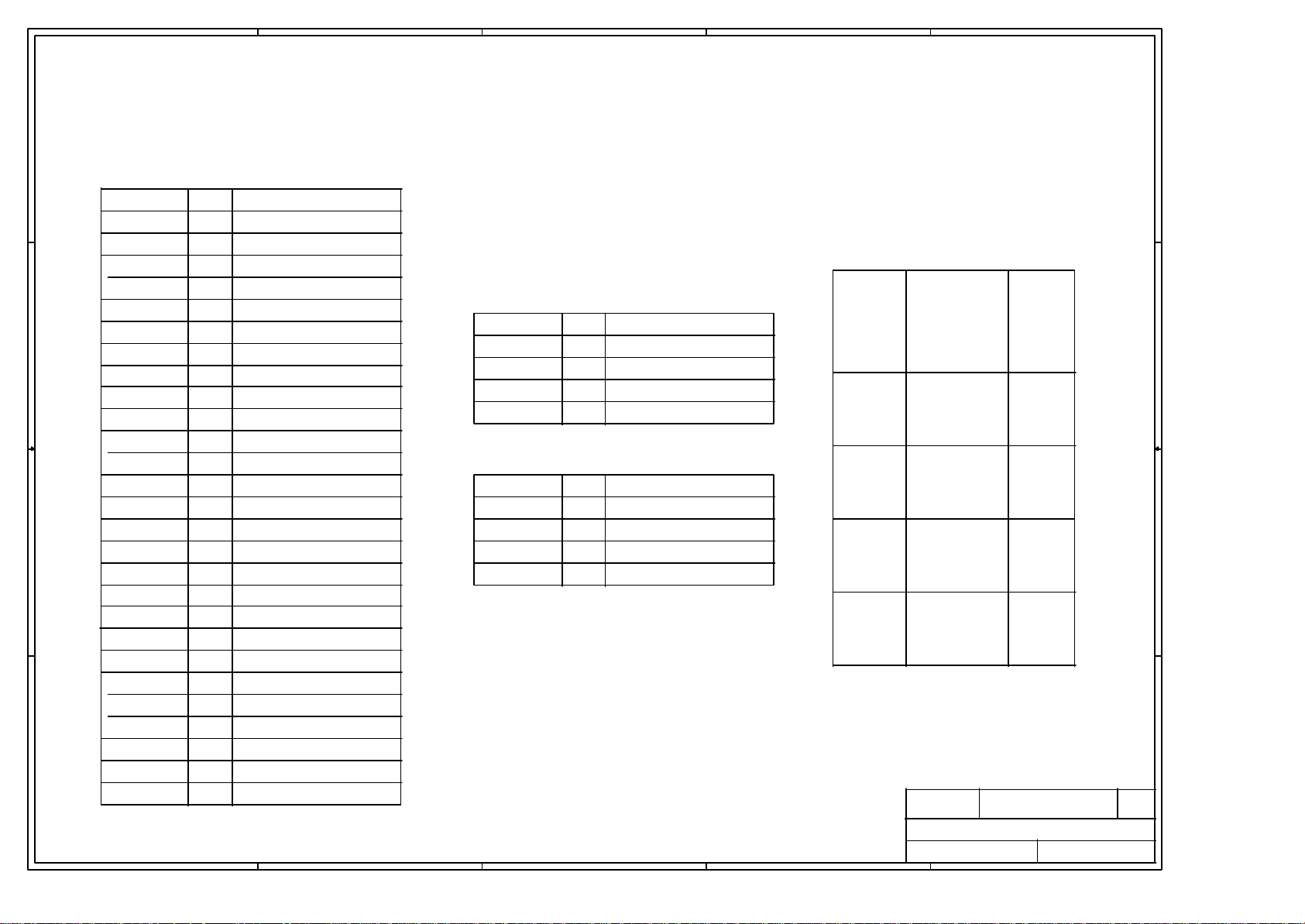

GPIO Spec. 3

D D

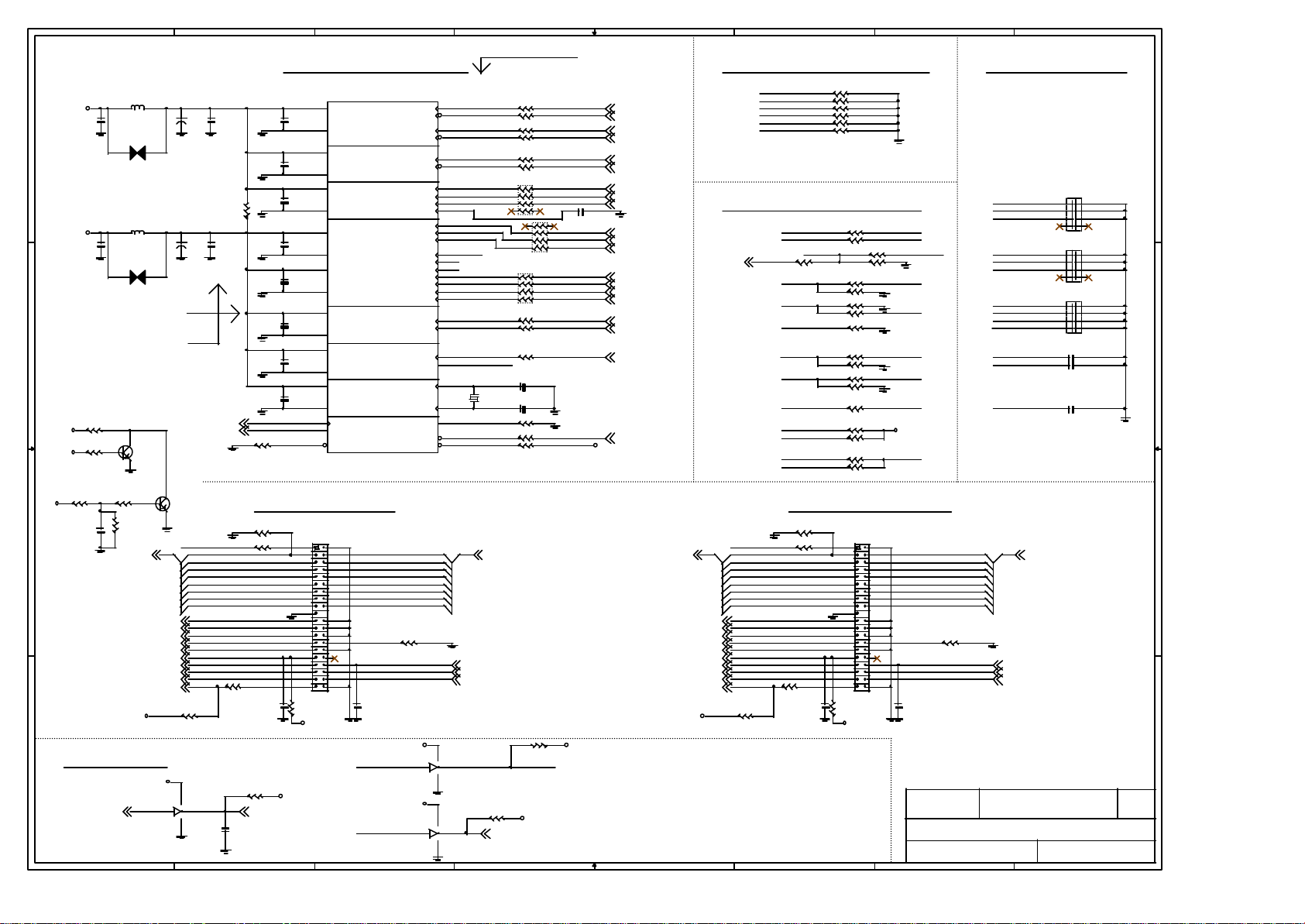

Clock CY28324 & ATA100 IDE CONNECTORS

mPGA478-B INTEL CPU Sockets

INTEL Brookdale MCH -- North Bridge

INTEL ICH2 -- South Bridge

LPC I/O W83627HF

4

5 - 6

7 - 8

9 - 10

11

Willamette/Northwood 478pin mPGA-B Processor Schematics

CPU:

Willamette/Northwood mPGA-478B Processor

CNR RISER

AC'97 Codec

C C

Audio Amp TL072 & GAME

FWH-- BIOS & VCCVID

SDR DIMM-168PIN DIMM1,2

AGP 4X SLOT (1.5V)

PCI SLOT 1 & 2 & 3

Front Panel & Connectors 19

USB & FAN Connectors

B B

D-LED & AUDIO 6 CHANNEL CONTROL

Votlage Regulator

12

13

14

15

16

17

18

20

21

22

System Brookdale Chipset:

INTEL MCH (North Bridge) +

INTEL ICH2 (South Bridge)

On Board Chipset:

BIOS -- FWH

LPC Super I/O -- W83627HF

Clock Generation -- CY28324

PCI SOUND -- C-MEDIA CMI8738

Expansion Slots:

AGP2.0 SLOT * 1

HIP6301V CPU Power ( PWM )-VRM9.2

IO Connectors

23

24

PCI2.2 SLOT * 3

Realtek RTL8100(L) LAN

DDR Damping

DDR Termination

A A

DDR Termination Power

8

7

6

25

26

27

28

29Jumper setting

30Power Delivery Map

5

4

3

Micro-Star

Document Number

Last Revision Date:

Monday, July 23, 2001

Title

MS-6507

Cover Sheet

Sheet of

2

Rev

0B

1 36

1

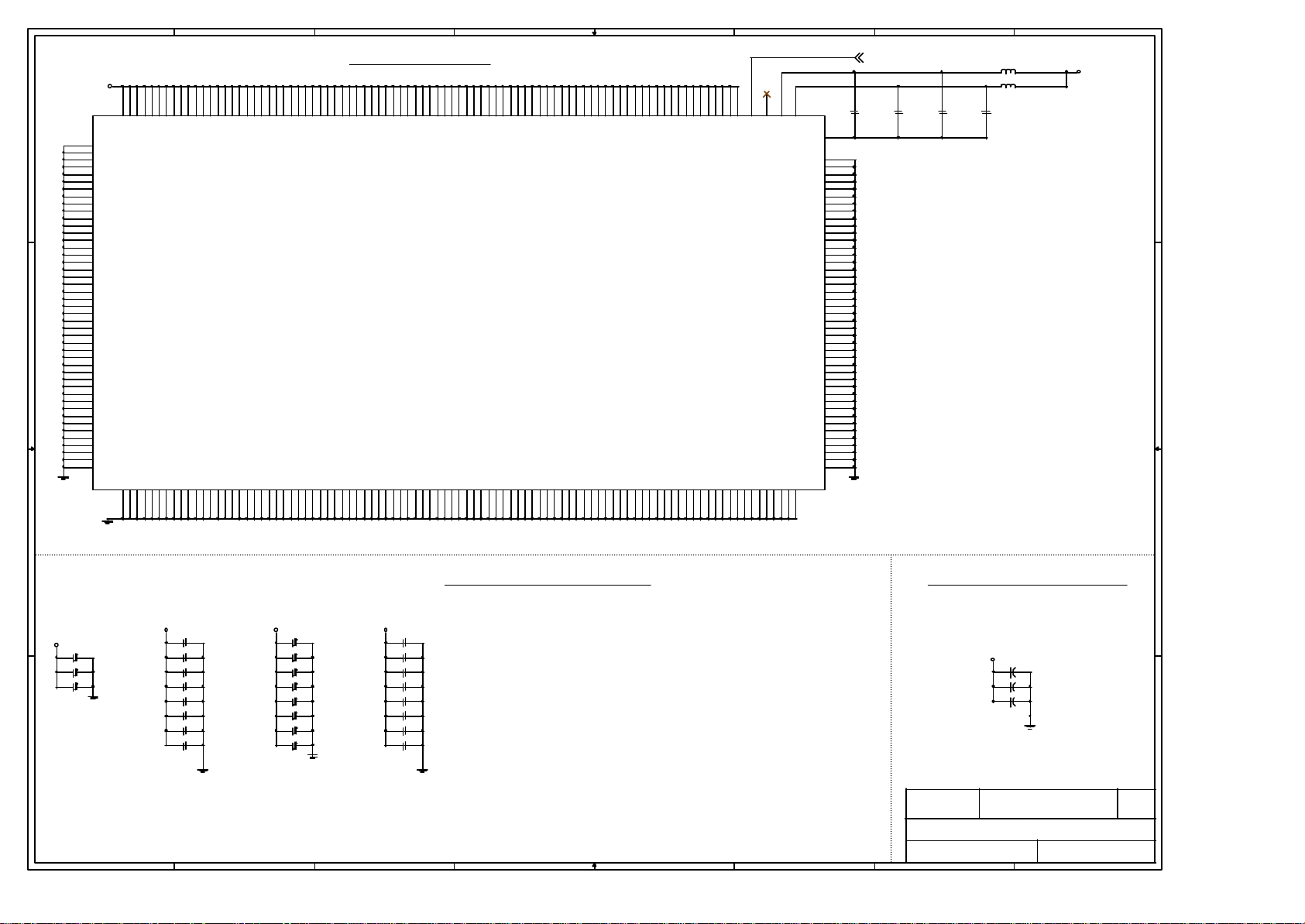

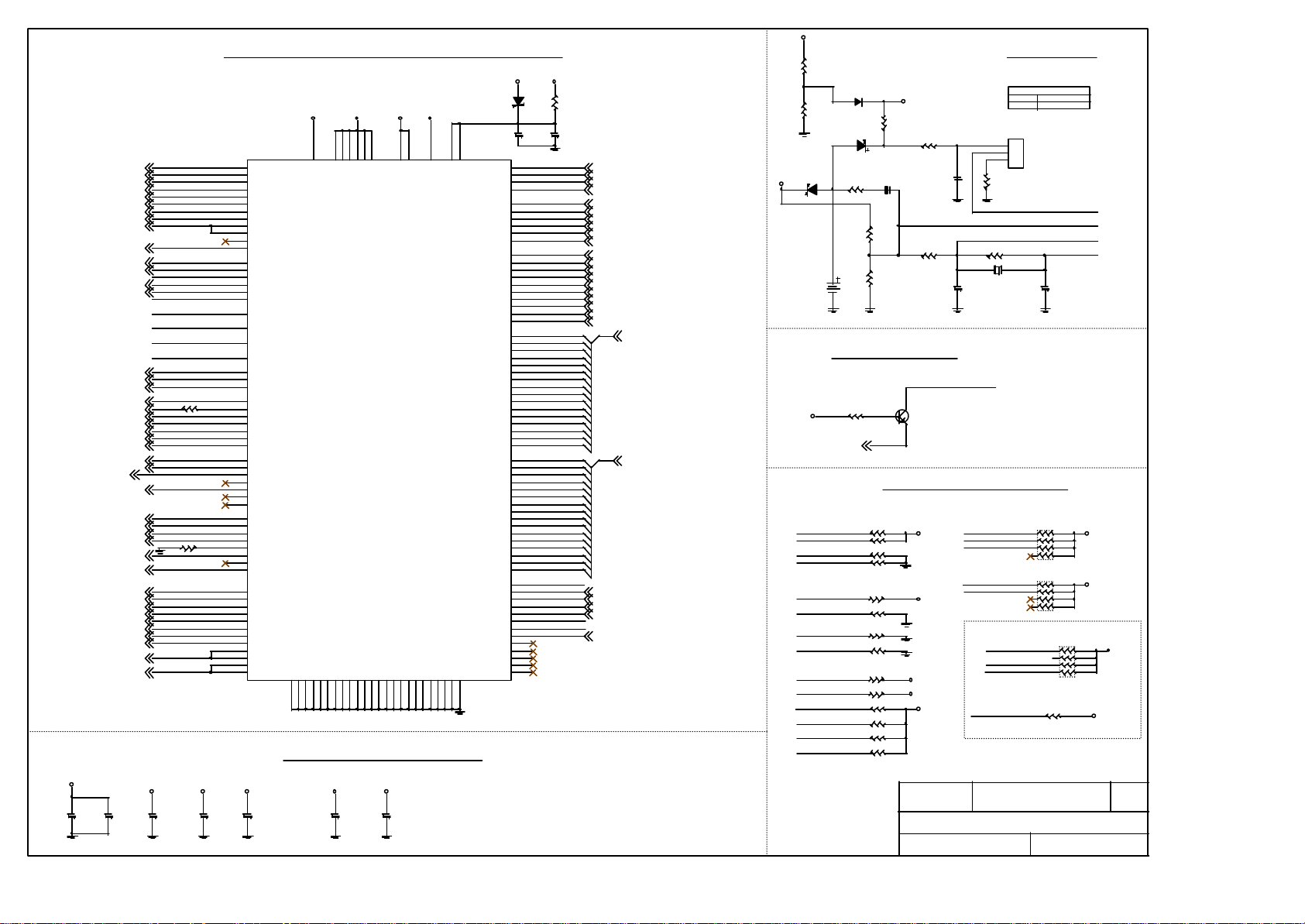

Page 2

8

D D

AGP

4X(1.5V)

AGP CONN

7

Power

Supply

CONN

AGP 4X

(1.5V)

6

VRM

9.2

4X (66MHz) AGP

(593PINS/FCBGA)

5

(478PINS)

Willamette/Northwood

Socket (mPGA478-B)

(400MHz)

Scalable Bus

MCH: Memory

Controller HUB

4

3

2

1

(100MHz)

CK408 Clock

(100MHz)

Scalable Bus/2

(133MHz)

DDR 1:2

( 66MHz X 4 )

HUB Interface

(14.318MHz)

C C

Heceta Hardware

Monitor

IDE CONN 1&2

SM Bus

(360PINS/EBGA)

ICH2: I/O

Controller HUB

PCI (33MHz)

PCI Slots 1:3

(48MHz)

USB Port 0:3

LPC Bus AC Link

FWH: Firmware HUB

PCI LAN /

Realtek

RTL8100

B B

PS2 Mouse &

Keyboard

SIO

Parallel (1)

Serial (2)

Floppy Disk

Drive CONN

(33MHz)

(33MHz)

DLED

AC '97 Audio

Codec

Audio In

Line In

CD-ROM

Telephone In

MIC In

CNR Riser

(Shared slot)

AMP

Line Out

A A

Title

Micro-Star

Document Number

Last Revision Date:

8

7

6

5

4

3

Monday, July 23, 2001

2

MS-6507

Block Diagram

Sheet of

Rev

0B

2 36

1

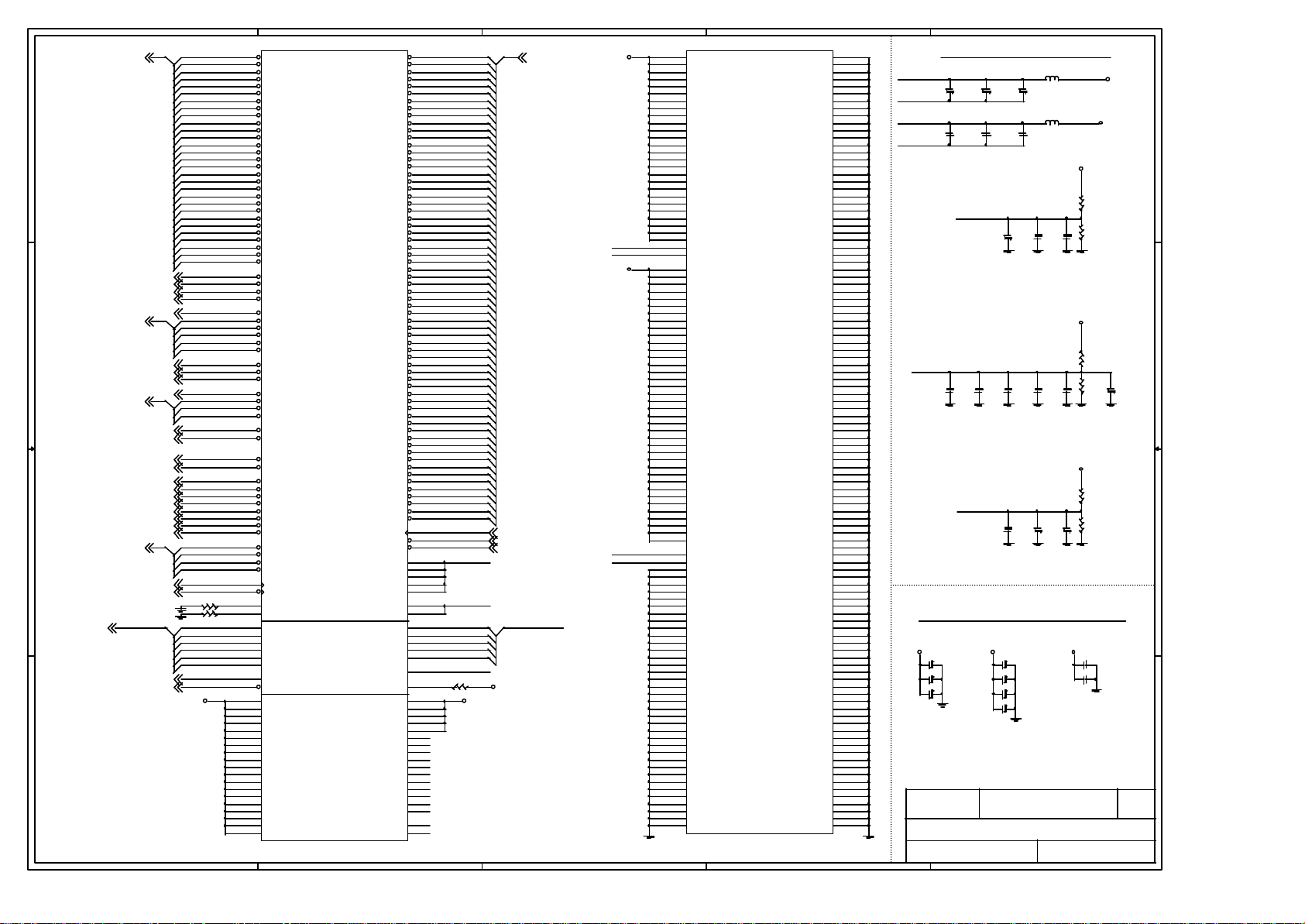

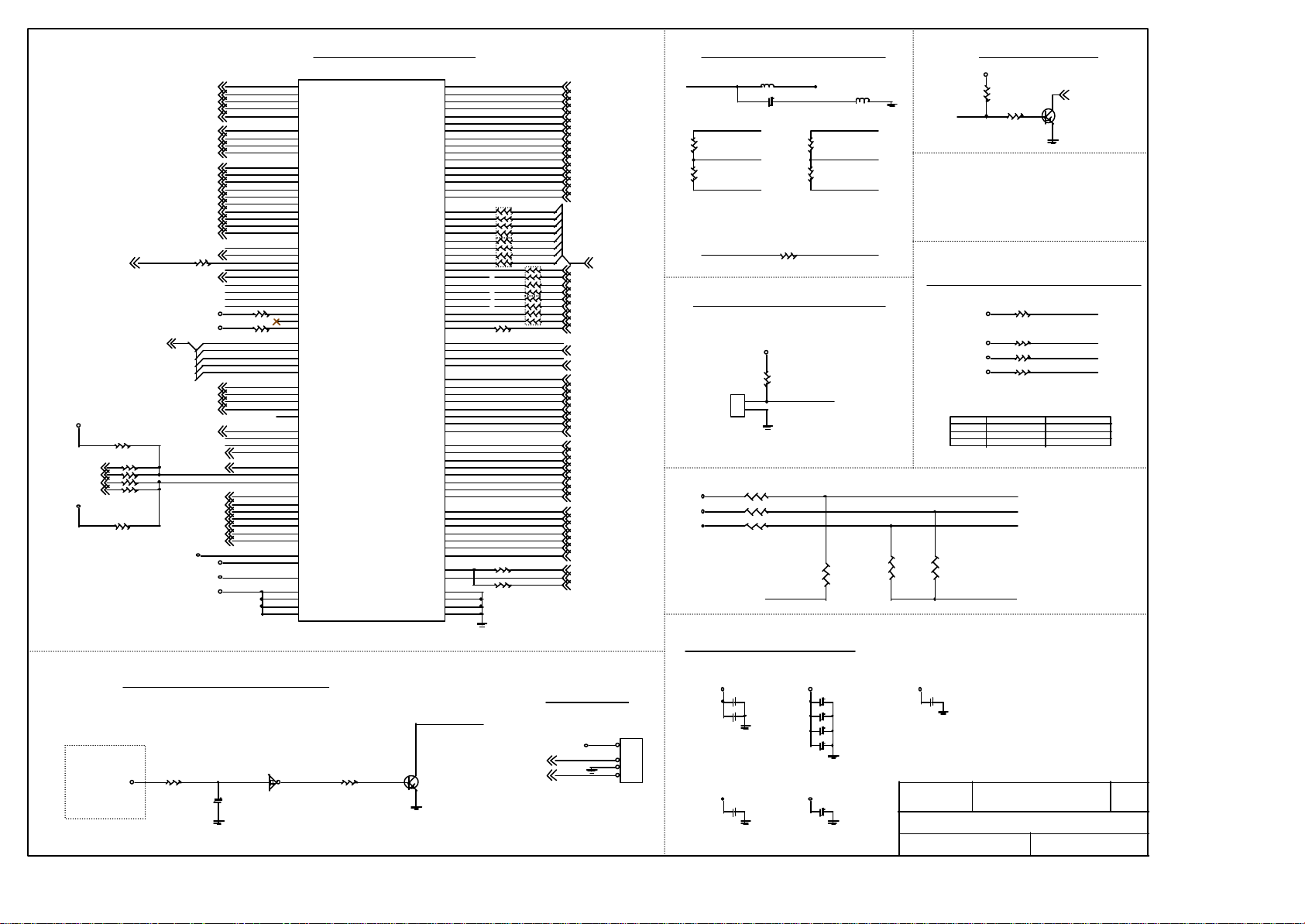

Page 3

5

4

3

2

1

General Purpose I/O Spec.

D D

ICH2

FunctionTypeGPIO Pin

GPIO 0

GPIO 1

GPIO 2~4

GPIO 5

GPIO 6

C C

GPIO 7

GPIO 8

GPIO 9

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14~15

GPIO 16

GPIO 17

B B

GPIO 18

GPIO 19

GPIO 20

GPIO 21

GPIO 22

GPIO 23

GPIO 24

GPIO 25

GPIO 26

A A

GPIO 27

GPIO 28

GPIO 29~31

5

I

Non Connect

I

Non Connect

I

Not Implemented

I

Non Connect

I

AC97 Enabled/Disabled

I

None

I

LAN Wake Up

I

AC'97 Serial Data In

I

Non Connect

I

Non Connect

I

External SMI

I

LPC PME

I

Not Implemented

O

Non Connect

O

Non Connect

O

Not Implemented

O

Not Implemented

O

Not Implemented

O

Audio 6 channel control

O

Non

OD

BIOS Locked/Unlocked

O

Non

O

Non

O

Non

I/O

Non

I/O

non

I/O

Not Implemented

IDSEL

AD16

AD17

FWH

GPIO Pin Type Function

GPI 0

GPI 1

GPI 2

GPI 3

I

ATA IDE 1 Detect

I

ATA IDE 2 Detect

Reserved

I

I

Reserved

DEVICE

PCI Slot 1

ICH INT Pin

INTA#

INTB#

INTC#

INTD#

PCI Slot 2 INTB#

INTC#

INTD#

INTA#

DLED-Super I/O

GPIO Pin Type Function

GP32

GP24

GP34

GP33

I/OD

I/OD

I/OD

I/OD

DLED1

DLED2

DLED3

DLED4

PCI Slot 3

INTC#

INTD#

INTA#

INTB#

PCI Audio

INTD#/INTE#

INTA#

INTB#

INTC#

PCI Lan INTC#/INTF#

AD18

AD23

AD22

INTD#

INTA#

INTB#

Title

Micro-Star

Document Number

Last Revision Date:

4

3

2

Monday, July 23, 2001

MS-6507

GPIO Spec.

Sheet of

1

Rev

0B

3 36

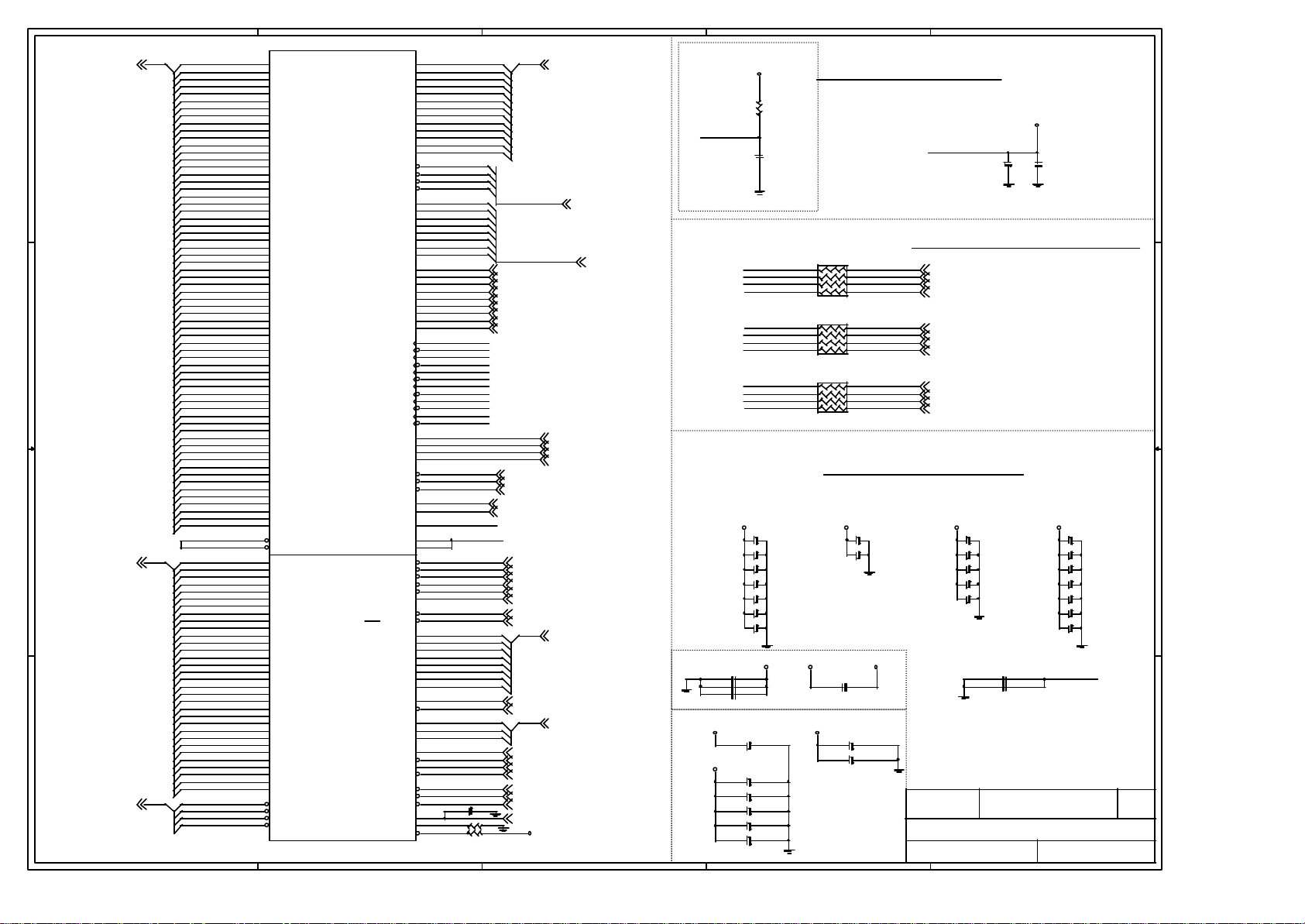

Page 4

8

7

6

5

4

3

2

1

*Trace less 0.5"

CLOCK GENERATOR BLOCK Shut Source Termination Resistors

for good filtering from 10K~1M

VCC3

D D

VCC3

*Put GND copper under Clock Gen.

connect to every GND pin

* 40 mils Trace on Layer 4

with GND copper around it

* put close to every power pin

C C

Trace Width 7mils.

*

Same Group spacing 15mils

*

Different Group spacing 30mils

*

Different mode spacing 7mils on itself

*

VCC3

VCCP

FB18 X_600

CB145

0.1u

X_COPPER

CP600

for good filtering from 10K~1M

FB20 X_600

CB166

0.1u

X_COPPER

CP601

VTT_GD#

R323

10K

R304 220

+

Rubycon

CT34

10u

+

Rubycon

CT36

10u

Q36

NPN-3904LT1-S-SOT23

SMBDATA10,11,12,16

SMBCLK10,11,12,16

CB144

1u

R228

X_0

CB178

1u

VCC3V

SMBCLK

SMBDATA

R318 X_1K

CB154

0.1u

CB151

0.1u

CB153

0.1u

CB183

0.1u

CB177

0.1u

CB164

0.1u

CB165

0.1u

CB152

0.1u

VTT_GD#

U18

39

CPU_VDD

36

CPU_GND

46

MREF_VDD

43

MREF_GND

29

3V66_GND

9

PCI_VDD

5

PCI_GND

18

PCI_VDD

13

PCI_GND

24

48_VDD

21

48_GND

2

REF_VDD

47

REF_GND

34

CORE_VDD

33

CORE_GND

26

SCLK

25

SDATA

19

VTT_GD#

CYP-CY28324

ICS950208

CY28323

CPU0

CPU0#

CPU1

CPU1#

3VMREF/CPU_STP#

3VMREF#/PCI_STP#

3V66_03V66_VDD

3V66_1

3V66_2

3V66_3

FS2/PCI_F0

FS3/PCI_F1

MODE/PCI_F2

FS4/PCI0

PCI1

PCI2

PCI3

PCI4

PCI5

PCI6

FS0/48MHz

FS1/24_48MHz

MUL0/REF0

MUL1/REF1

IREF

RST#

PWR_DN#

41

40

38

37

C_STP

45

P_STP

44

3132

30

28

27

FS2

6

FS3

7

MODE

8

FS4

10

11

12

14

15

16

17

FS0

22

FS1

23

MUL0

48

MUL1

1

3

X1

X1 14M-32pf-HC49S-D

4

X2

35

20

42

R246 33

R247 33

R239 33

R240 33

R243 X_33

R244 X_33

RN17

33

3V66_3

RN24

33

R307 33

R281 33

R251 33

32pF

R227 475

R306 0

R245 4.7K

1 2

3 4

5 6

7 8

7 8

5 6

3 4

1 2

7 8

5 6

3 4

1 2

CPUCLK

CPUCLK#

MCHCLK

MCHCLK#

ITP_CLK

ITP_CLK#

MCH_66

ICH_66

AGPCLK

RN25

ICH_PCLK

FWH_PCLK

SIO_PCLK

33

PCICLK0

PCICLK1

PCICLK2

PCICLK3

ICH_48

SIO_48

ICH_14

18pC171

18pC166

CLK_RST#CRST#

VCC3V

10pC157

CPUCLK 5

CPUCLK# 5

MCHCLK 7

MCHCLK# 7

ITP_CLK 5

ITP_CLK# 5

MCH_66 7

ICH_66 10

AGPCLK 17

ICH_PCLK 9

FWH_PCLK 15

SIO_PCLK 11

PCICLK0 18

PCICLK1 18

PCICLK2 18

PCICLK3 25

ICH_48 10

SIO_48 11

ICH_14 10

CLK_RST# 19

VCC3V

BSEL05

100/133 select

CPUCLK

R233 49.9

CPUCLK#

R234 49.9

MCHCLK

R229 49.9

MCHCLK#

R230 49.9

ITP_CLK

R232 X_49.9

ITP_CLK#

R236 X_49.9

Trace less 0.2"

49.9ohm for 50ohm M/B impedance

CLOCK STRAPPING RESISTORS

FS4

R324 10K

FS3

R334 10K

BSEL0

FS1

R749 X_10K

FS0

R321 10K

R322 X_10K

FS2

R326 X_10K

R325 10K

MODE

R336 X_10K

MUL0

R241 X_10K

R231 10K

MUL1

R316 10K

R315 X_10K

CRST# VCC3V

R305 10K

SMBCLK

R255 4.7K

SMBDATA

R254 4.7K

C_STP

R242 X_1K

P_STP

R235 X_1K

VCC3V

VCC3V

R282 X_10K

R283 10K

VCC3V

VCC3V

VCC3V

VCC3V

VCC3V

VCC3V

VCC3

Pull-Down Capacitors

CN16

MCH_66

ICH_66

AGPCLK

SIO_PCLK

FWH_PCLK

ICH_PCLK

PCICLK0

PCICLK1

PCICLK2

PCICLK3

ICH_48

SIO_48

ICH_14

used only for EMI issue

Trace less 0.2"

X_10p

1

3

5

7

8

6

4

2

7

5

3

1

CN18

X_10p

CN17

X_10p

2

4

6

8

7

5

3

1

8

6

4

2

10pC175

10pC169

10pC164

PD_DREQ10

PD_IOW#10

PD_IORDY10

PD_DACK#10

PD_CS#110

VCC5_SB

PCIRST#

Q705

NPN-3904LT1-S-SOT23

HD_RST# HD_RST#

PDD7

PDD6

PDD5

PDD4

PDD3

PDD2

PDD1

PDD0

PD_IOR#10

IRQ149

PD_A110

PD_A010

R191 8.2K

14

1 2

7

R189 33

PD_LED19

U21A

7407-SOIC14

PRIMARY IDE BLOCK SECONDARY IDE BLOCK

R190 4.7K

R188 33

R388 330

C199

X_10p

7

C79

220p

IDE1

D2x20-1:21-BL-ZBT

1

2

3 4

5 6

7 8

91110

12

13 14

1615

17 18

19

22

21

24

23

26

25

27

29

31

33

35

37

R119

10K

VCC3 VCC3

VCC3

28

30

32

34

36

38

4039

R129 470

C76

X_4700p

VCC5_SB

PCIRST#

VCC5_SB

PCIRST#

6

ATA100 IDE CONNECTORS

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

9 8

U21D

7407-SOIC14

3 4

U21B

7407-SOIC14

PD_DET 15

PD_A2 10

PD_CS#3 10

14

7

14

7

PDD[8..15] 10

R197 330

PCIRST#2 17,18

R407 1K

HD_RST#

VCC3

5

VCC5

SDD[0..7]10

VCC5VCC5

4

R186 4.7K

R187 33

SDD7

SDD6

SDD5

SDD4

SDD3

SDD2

SDD1

SDD0

SD_DREQ10

SD_IOW#10

SD_IOR#10

SD_IORDY10

SD_DACK#10

IRQ159

SD_A110

SD_A010

SD_CS#110

SD_LED19

R103 8.2K

R101 33

C81

3

IDE2

D2x20-1:21-WH-SBT

1

2

3 4

5 6

7 8

91110

12

13 14

1615

17 18

19

22

21

24

23

26

25

28

27

30

29

32

31

34

33

36

35

38

37

4039

R120

10K220p

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

R128 470

C77

X_4700p

Micro-Star

Document Number

Last Revision Date:

Monday, August 06, 2001

2

SDD[8..15] 10

SD_DET 15

SD_A2 10

SD_CS#3 10

Title

MS-6507

Clock CY28323/4 & ATA100 IDE

Sheet of

4 36

1

Rev

0B

+12V

B B

A A

R718 220R719 4.7K

C702

4.7u-0805

R733

4.7K

PDD[0..7]10

RESET BLOCK

PCIRST#9 PCIRST#1 7,11,15,25

8

Page 5

8

7

6

5

4

3

2

1

CPU GTL REFERNCE VOLTAGE BLOCKCPU SIGNAL BLOCK

VCCP

R81

49.9

C58

R79

1u

100

VCCP

R32

X_49.9

R34

C13

X_100

X_1uX_220p

VCCP

VID2

AE3

VID2#

D4#

C21

VID1

VID0

AE4

AE5

VID1#

VID0#

LINT1/NMI

LINT0/INTR

D3#

D2#

A25

A23

B22

VCCPS+ 23

VCCPS- 23

ITP_CLK# 4

ITP_CLK 4

VID[0..4] 11,23

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM5#

BPM4#

BPM3#

BPM2#

BPM1#

BPM0#

REQ4#

REQ3#

REQ2#

REQ1#

REQ0#

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

BCLK1#

BCLK0#

RS2#

RS1#

RS0#

AP1#

AP0#

BR0#

COMP1

COMP0

DP3#

DP2#

DP1#

DP0#

ADSTB1#

ADSTB0#

DSTBP3#

DSTBP2#

DSTBP1#

DSTBP0#

DSTBN3#

DSTBN2#

DSTBN1#

DSTBN0#

D1#

D0#

B21

PGA-S478-F02

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

H3

J3

J4

K5

J1

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

AF23

AF22

F4

G5

F1

V5

AC1

H6

P1

L24

L25

K26

K25

J26

R5

L5

W23

P23

J23

F21

W22

R22

K22

E22

E5

D1

GTLREF1

GTLREF2

BPM#5

BPM#4

BPM#1

BPM#0

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

R77 4.7K

R46 4.7K

R82 4.7K

R45 4.7K

HRS#2

HRS#1

HRS#0

R47 49.9

R80 49.9

HREQ#[0..4] 7

VCCP

CPUCLK# 4

CPUCLK 4

HRS#[0..2] 7

HBR#0 7

* Short trace

HADSTB#1 7

HADSTB#0 7

HDSTBP#3 7

HDSTBP#2 7

HDSTBP#1 7

HDSTBP#0 7

HDSTBN#3 7

HDSTBN#2 7

HDSTBN#1 7

HDSTBN#0 7

NMI 9

INTR 9

GTLREF1

GTLREF2

C49

220p

C36

2/3*Vccp

C48

220p

2/3*Vccp

C35

X_220p

Every pin put one 220pF cap near it.

Trace Width 15mils, Space 15mils.

Keep the voltage dividers within 1.5 inches of the

first GTLREF Pin

CPU ITP BLOCK

ITP_TMS

R17 39

ITP_TDO

R10 75

ITP_TCK

R15 27

HA#[3..31]7

HA#8

HA#22

HA#25

HA#23

HA#26

HA#27

HA#28

HA#30

HA#29

D D

HDBI#[0..3]7

C C

HDEFER#7

Trace : 10

mil width

10mil space

CPU_TMPA11

VTIN_GND11

THERMTRIP#15

PROCHOT#10

100/133 select

B B

CPURST#7

HD#[0..63]7

HDBI#0

HDBI#1

HDBI#2

HDBI#3

FERR#9

STPCLK#9

HINIT#9,15

HDBSY#7

HDRDY#7

HTRDY#7

HADS#7

HLOCK#7

HBNR#7

HIT#7

HITM#7

HBPRI#7

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

ITP_TCK

THERMTRIP#

IGNNE#9

HSMI#9

A20M#9

SLP#9

R78

BSEL0

BSEL04

CPU_GD

CPU_GD10

CPURST#

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

U7A

E21

DBI0#

G25

DBI1#

P26

DBI2#

V21

DBI3#

AC3

IERR#

V6

MCERR#

B6

FERR#

Y4

STPCLK#

AA3

BINIT#

W5

INIT#

AB2

RSP#

H5

DBSY#

H2

DRDY#

J6

TRDY#

G1

ADS#

G4

LOCK#

G2

BNR#

F3

HIT#

E3

HITM#

D2

BPRI#

E2

DEFER#

C1

TDI

D5

TDO

F7

TMS

E6

TRST#

D4

TCK

B3

THERMDA

C4

THERMDC

A2

THERMTRIP#

AF26

GND/SKTOCC#

C3

PROCHOT#

B2

IGNNE#

B5

SMI#

C6

A20M#

AB26

SLP#

A22

RESERVED0

A7

RESERVED1

AD2

X_0

AD3

AE21

AF24

AF25

AD6

AD5

AB23

AB25

AA24

AA22

AA25

W25

W26

Y21

Y24

Y23

Y26

V24

RESERVED2

RESERVED3

RESERVED4

RESERVED5

RESERVED6

BSEL0

BSEL1

PWRGOOD

RESET#

D63#

D62#

D61#

D60#

D59#

D58#

D57#

D56#

D55#

D54#

V22

D53#

HA#31

AB1Y1W2V3U4T5W1R6V2T4U3P6U1T2R3P4P3R2T1N5N4N2M1N1M4M3L2M6L3K1L6K4K2

A35#

A34#

A33#

A32#

A31#

A30#

A29#

A28#

A27#

A26#

A25#

D52#

D51#

D50#

D49#

D48#

D47#

D46#

D45#

D44#

D43#

D42#

D41#

U21

V25

U23

U24

U26

T23

T22

D40#

T25

T26

R24

R25

P24

R21

HA#18

HA#24

A24#

A23#

D39#

D38#

N25

N26

M26

A22#

D37#

N23

HA#16

HA#21

HA#20

HA#19

HA#17

A21#

A20#

A19#

A18#

A17#

A16#

D36#

D35#

D34#

D33#

D32#

D31#

M24

P21

N22

M23

H25

HA#9

HA#5

HA#4

HA#14

HA#10

HA#15

HA#11

HA#13

HA#12

A15#

A14#

A13#

A12#

A11#

A10#

D30#

D29#

D28#

D27#

D26#

D25#

K23

J24

L22

M21

H24

G26

HA#3

HA#7

HA#6

AE25A5A4

A9#

A8#

A7#

A6#

A5#

A4#

A3#

DBR#

VCC_SENSE

Differential

Host Data

Strobes

D24#

D23#

D22#

D21#

D20#

D19#

D18#

D17#

D16#

D15#

D14#

G23

D13#

E24

H22

D25

J21

D23

L21

D26

F26

E25

F24

F23

AD26

AC26

ITP_CLK1

VSS_SENSE

D12#

D11#

D10#

C26

H21

G22

B25

VID4

AE1

ITP_CLK0

D9#

D8#

D7#

C24

C23

B24

VID3

AE2

VID4#

D6#

D22

VID3#

D5#

HD#5

HD#8

HD#7

HD#53

HD#48

HD#51

HD#50

HD#49

HD#52

A A

HD#41

HD#47

HD#46

HD#39

HD#45

HD#42

HD#44

HD#43

HD#40

HD#32

HD#29

HD#34

HD#37

HD#35

HD#33

HD#38

HD#36

HD#26

HD#30

HD#28

HD#31

HD#27

HD#19

HD#23

HD#24

HD#25

HD#16

HD#22

HD#20

HD#18

HD#21

HD#17

CPU STRAPPING RESISTORS

BPM#0

BPM#4

BPM#5

8

R41 49.9

R42 49.9

R44 49.9

R43 49.9

VCCP

7

ITP_TDI

ITP_TRST# CPURST#

R26 150

6

VCCP VCCP

HD#9

HD#10

HD#14

HD#15

HD#11

HD#12

HD#13

ALL COMPONENTS CLOSE TO CPU

PROCHOT#BPM#1

CPU_GD

HBR#0

THERMTRIP#

5

HD#0

HD#2

HD#4

HD#3

HD#1

HD#6

R27 62

R76 300

R64 49.9

R83 49.9R16 680

R66 X_62

4

Title

Micro-Star

Document Number

Last Revision Date:

3

Thursday, August 09, 2001

2

MS-6507

INTEL mPGA478-B CPU1

Sheet of

Rev

0B

5 36

1

Page 6

8

VCCP

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

VCC

VSS

AD18

VCC

VSS

AD21

VCC

VSS

AD23

VCC

VSS

AD4

VCC

VSS

AD8

VCC

VSS

AE11

AA16

VCC

VSS

AE13

U7B

VCC

VCC

D D

D10

A11

A13

A15

A17

A19

A21

A24

A26

A3

A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

C C

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AD10

VSS

AD12

VSS

AD14

VCC

VSS

AD16

VCC

VSS

AA18

AE15

VCC

VSS

AA8

AE17

VCC

VSS

AB11

AE19

VCC

VSS

AB13

AE22

VCC

VSS

AB15

AE24

VCC

VSS

AB17

AE26

7

VCC

VSS

AB19

AE7

VCC

VSS

AB7

AE9

VCC

VSS

AB9

AF1

VCC

VSS

AC10

AF10

VCC

VSS

AC12

AF12

VCC

VSS

AC14

AF14

VCC

VSS

AC16

AF16

VCC

VSS

AC18

AF18

VCC

VSS

AC8

AF20

VCC

VSS

CPU VOLTAGE BLOCK

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF6

AF8

VSS

B10

B12

B14

B16

B18

B23

B20

B26B4B8

VCC

VSS

6

AE16

VCC

VSS

AE18

VCC

VSS

AE20

C11

VCC

VSS

AE6

C13

VCC

VSS

AE8

C15

AF11

VCC

VSS

C17C2C19

AF13

VCC

VSS

VCC

VSS

AF15

AF17

VCC

VSS

C22

AF19

AF2

AF21

AF5

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

C25C5C7C9D12

AF7

VCC

VSS

VCC

VSS

AF9

D14

B11

VCC

VSS

D16

5

B13

B15

B17

B19B7B9

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

D18

D20

D21D3D24D6D8E1E11

VCC

VSS

VCC

VSS

VCC

VSS

4

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

F13

F15

F17

F19

AF4

F9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC-VID

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E13

E15

E17

E19

E23

E7E9F10

F12

F14

F16

E4

E26

F18F2F22

F25F5F8

G21G6G24

VSS

VSS

G3H1H23

VSS

VSS

VSS

H26H4J2

AE23

AF3

VCC-IOPLL

VCC-VIDPRG

VSS

VSS

VSS

VSS

J22

J25J5K21

3

AD20

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

PGA-S478-F02

AD22

Y5

Y25

Y22

Y2

W6

W3

W24

W21

V4

V26

V23

V1

U5

U25

U22

U2

T6

T3

T24

T21

R4

R26

R23

R1

P5

P25

P22

P2

N6

N3

N24

N21

M5

M25

M22

M2

L4

L26

L23

L1

K6

K3

K24

VCC_VID 15,23

C57

C53

10u-1206

10u-1206

2

C56

22u-1206

L2 4.7u-10%

L1 4.7u-10%

C52

22u-1206

1

VCCP

B B

CPU DECOUPLING CAPACITORS

CPU DECOUPLING CAPACITORS

VCCP VCCPVCCP

VCCP

CB32

10u-1206

CB29

10u-1206

CB47

10u-1206

A A

8

CB38

10u-1206

CB55

10u-1206

CB61

10u-1206

CB41

10u-1206

CB14

10u-1206

CB35

10u-1206

CB39

10u-1206

CB44

10u-1206

CB49

10u-1206

CB34

10u-1206

CB27

10u-1206

CB54

10u-1206

CB50

10u-1206

CB52

10u-1206

CB58

10u-1206

CB22

10u-1206

PLACE CAPS WITHIN CPU CAVITY

7

CB21

10u-1206

CB20

10u-1206

CB17

10u-1206

CB51

10u-1206

CB42

10u-1206

CB48

10u-1206

CB45

10u-1206

CB25

10u-1206

PLACE CAPS WITHIN CPU CAVITY SOLDER

Micro-Star

Document Number

Last Revision Date:

6

5

4

3

Monday, September 03, 2001

VCCP

Title

INTEL mPGA478-B CPU2

2

+

+

+

CT9

150u

CT11

150u

CT10

150u

MS-6507

Sheet of

Rev

0B

6 36

1

Page 7

5

HA#[3..31]5

D D

HBNR#5

HBPRI#5

HLOCK#5

HADS#5

HREQ#[0..4]5

C C

HDEFER#5

HRS#[0..2]5

B B

HL[0..10]9

A A

HTRDY#5

HDBSY#5

HDRDY#5

HADSTB#05

HADSTB#15

HDSTBN#05

HDSTBP#05

HDSTBN#15

HDSTBP#15

HDSTBN#25

HDSTBP#25

HDSTBN#35

HDSTBP#35

HDBI#[0..3]5

MCHCLK4

MCHCLK#4

HL[0..10]

HL_STB9

HL_STB#9

5

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HBR#05

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HIT#5

HITM#5

HRS#0

HRS#1

HRS#2

HDBI#0

HDBI#1

HDBI#2

HDBI#3

R98 24.9

R118

HL0

HL1

HL2

HL3

HL4

HL5

VCCP

24.9

AD4

AD3

AE6

AE7

AE11

AD11

AC15

AC16

AD5

AG4

AH9

AD15

AC2

AC13

M26

M25

AA9

AB8

AB18

AB20

AC19

AD18

AD20

AE19

AE21

AF18

AF20

AG19

AG21

AG23

AJ19

AJ21

AJ23

T4

T5

T3

U3

R3

P7

R2

P4

R6

P5

P3

N2

N7

N3

K4

M4

M3

L3

L5

K3

J2

M5

J3

L2

H4

N5

G2

M6

L7

V7

W3

Y7

W5

V3

U6

T7

R7

U5

U2

Y5

Y3

Y4

U7

W2

W7

W6

V5

V4

R5

N6

J8

K8

P25

P24

N27

P23

N25

N24

M8

U8

U12A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

BR0#

BNR#

BPRI#

HLOCK#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HIT#

HITM#

DEFER#

HTRDY#

RS0#

RS1#

RS2#

DBSY#

DRDY#

HAD_STB0#

HAD_STB1#

HD_STBN0#

HD_STBP0#

HD_STBN1#

HD_STBP1#

HD_STBN2#

HD_STBP2#

HD_STBN3#

HD_STBP3#

DBI0#

DBI1#

DBI2#

DBI3#

BCLK

BCLK#

H_RCOMP0

H_RCOMP1

HI0

HI1

HI2

HI3

HI4

HI5

HI_STB

HI_STB#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

INT-82845

HOST

HUB LINK

POWER

4

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

66IN

RSTIN#

CPURST#

H_VREF0

H_VREF1

H_VREF2

H_VREF3

H_VREF4

H_SWNG0

H_SWNG1

HI10

HI_REF

HL_RCOMP

VCC1_8

VCC1_8

VCC1_8

VCC1_8

VCC1_8

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD7

RSVD8

RSVD9

NC0

NC1

4

3

HD#0

AA2

HD#1

AB5

HD#2

AA5

HD#3

AB3

HD#4

AB4

HD#5

AC5

HD#6

AA3

HD#7

AA6

HD#8

AE3

HD#9

AB7

HD#10

AD7

HD#11

AC7

HD#12

AC6

HD#13

AC3

HD#14

AC8

HD#15

AE2

HD#16

AG5

HD#17

AG2

HD#18

AE8

HD#19

AF6

HD#20

AH2

HD#21

AF3

HD#22

AG3

HD#23

AE5

HD#24

AH7

HD#25

AH3

HD#26

AF4

HD#27

AG8

HD#28

AG7

HD#29

AG6

HD#30

AF8

HD#31

AH5

HD#32

AC11

HD#33

AC12

HD#34

AE9

HD#35

AC9

HD#36

AE10

HD#37

AD9

HD#38

AG9

HD#39

AC10

HD#40

AE12

HD#41

AF10

HD#42

AG11

HD#43

AG10

HD#44

AH11

HD#45

AG12

HD#46

AE13

HD#47

AF12

HD#48

AG13

HD#49

AH13

HD#50

AC14

HD#51

AF14

HD#52

AG14

HD#53

AE14

HD#54

AG15

HD#55

AG16

HD#56

AG17

HD#57

AH15

HD#58

AC17

HD#59

AF16

HD#60

AE15

HD#61

AH17

HD#62

AD17

HD#63

AE16

P22

J27

AE17

HVREF

M7

R8

Y8

AB11

AB17

HSWNG

AA7

AD13

HL6

L28

HI6

HI7

HI8

HI9

L27

M27

N28

M24

P26

P27

L25

L29

M22

N23

N26

G9

G10

H6

J25

J23

G16

G17

H7

H27

K23

K25

AD26

AD27

HL7

HL8

HL9

HL10

HUB_MREF

R172 40.2

VCC1_8

HD#[0..63] 5

MCH_66 4

PCIRST#1 4,11,15,25

CPURST# 5

HL[0..10]

VCC1_8

VCC_AGP

V_DIMM

3

VTT1

VTT2

VTT_GND1

VTT_GND2

W22

W29

AA22

AA26

AB21

AC29

AD21

AD23

AE26

AF23

AG29

AJ25

G29

AD12

AD14

AD16

AD19

AD22

AE1

AE4

AE18

AE20

AE29

AF5

AF7

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF25

AG1

AG18

AG20

AG22

AH19

AH21

AH23

AJ11

AJ13

AJ15

AJ17

AJ27

R22

R29

U22

U26

N14

N16

P13

P15

P17

R14

R16

T15

U14

U16

T13

T17

A13

A17

A21

A25

C29

D11

D15

D19

D23

D25

F6

F10

F14

F18

F22

G1

G4

H10

H12

H14

H16

H18

H20

H22

H24

K22

K24

K26

L23

U13

U17

AJ3

AJ5

AJ7

AJ9

A5

A9

C1

D7

H8

J5

J7

K6

U12C

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCC1_5

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

INT-82845

POWER

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

2

A3

A7

A11

A15

A19

A23

A27

D5

D9

D13

D17

D21

E1

E4

E26

E29

F8

F12

F16

F20

F24

G26

H9

H11

H13

H15

H17

H19

H21

J1

J4

J6

J22

J26

J29

K5

K7

K27

L1

L4

L6

L8

L22

L24

L26

M23

N1

N4

N8

N13

N15

N17

N22

N29

P6

P8

P14

P16

R1

R4

R13

R15

R17

R26

T6

T8

T14

T16

T22

U1

U4

U15

U29

V6

V8

V22

W1

W4

W8

W26

Y6

Y22

AA1

AA4

AA8

AA29

AB6

AB9

AB10

AB12

AB13

AB14

AB15

AB16

AB19

AB22

AC1

AC4

AC18

AC20

AC21

AC23

AC26

AD6

AD8

AD10

2

MCH REFERENCE BLOCK

VTT1

VTT_GND1

VTT2

VTT_GND2

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

HVREF

C93

Place 1 Cap. as Close as possible to

every pin of MCH

Trace width use 15 mils and 15mils space

Place 0.01uF Cap. as Close as possible to MCH

Trace width use 15 mils and 15mils space

CB107

0.1u

CB108

0.1u

HSWNG

C70

0.01u

HUB_MREF

C99

22u-1206

C101

10u-1206

0.1u

C69

0.01u

C106

MCH Trace Decoupling Capacitors

VCCP VCCP VCC1_8

CB24

X_0.1u

CB12

X_0.1u

CB46

X_0.1u

ADDRESS

Title

Micro-Star

Document Number

Last Revision Date:

Wednesday, August 29, 2001

1

L5 4.7u_1206

C102

10u-1206

L4 4.7u_1206

C98

22u-1206

C90C68

C87

0.01u

C88

C71

0.01u

0.01u

C107

C108

0.1u

0.1u

CB3

X_0.1u

CB73

X_0.1u

CB60

X_0.1u

CB69

X_0.1u

DATA

MS-6507

Brookdale MCH1

1

VCCP

R130

301

R122

1500.01u

VCCP

R100

49.9

R99

100

VCC1_8

R178

150

R176

1500.01u

MCH & ICH2

Sheet of

7 36

VCC_AGP

VCC_AGP

C72

0.1u0.01u

CB148

0.1u

CB85

0.1u

Rev

0B

Page 8

1" trace

D D

C C

B B

A A

GC_BE#[0..3]17

5

MD[0..63]26

1" Trace

GAD[0..31]17

5

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GC_BE#0

GC_BE#1

GC_BE#2

GC_BE#3

G28

G27

AA28

AB25

AB27

AA27

AB26

AB23

AA24

AA25

AB24

AC25

AC24

AC22

AD24

AA23

F27

C28

E28

H25

F25

B28

E27

C27

B25

C25

B27

D27

D26

E25

D24

E23

C22

E21

C24

B23

D22

B21

C21

D20

C19

D18

C20

E19

C18

E17

E13

C12

B11

C10

B13

C13

C11

D10

E10

E11

G5

G3

R27

R28

T25

R25

T26

T27

U27

U28

V26

V27

T23

U23

T24

U24

U25

V24

Y27

Y26

Y23

V25

V23

Y25

C9

D8

E8

B9

B7

C7

C6

D6

D4

B3

E6

B5

C4

E5

C3

D3

F4

F3

B2

C2

E2

H3

U12B

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

SDQ14

SDQ15

SDQ16

SDQ17

SDQ18

SDQ19

SDQ20

SDQ21

SDQ22

SDQ23

SDQ24

SDQ25

SDQ26

SDQ27

SDQ28

SDQ29

SDQ30

SDQ31

SDQ32

SDQ33

SDQ34

SDQ35

SDQ36

SDQ37

SDQ38

SDQ39

SDQ40

SDQ41

SDQ42

SDQ43

SDQ44

SDQ45

SDQ46

SDQ47

SDQ48

SDQ49

SDQ50

SDQ51

SDQ52

SDQ53

SDQ54

SDQ55

SDQ56

SDQ57

SDQ58

SDQ59

SDQ60

SDQ61

SDQ62

SDQ63

RCVENIN#

RCVENOUT#

G_AD0

G_AD1

G_AD2

G_AD3

G_AD4

G_AD5

G_AD6

G_AD7

G_AD8

G_AD9

G_AD10

G_AD11

G_AD12

G_AD13

G_AD14

G_AD15

G_AD16

G_AD17

G_AD18

G_AD19

G_AD20

G_AD21

G_AD22

G_AD23

G_AD24

G_AD25

G_AD26

G_AD27

G_AD28

G_AD29

G_AD30

G_AD31

G_C/BE0#

G_C/BE1#

G_C/BE2#

G_C/BE3#

INT-82845

AGP

Tri-Stated

during

RSTIN#

assertion

DDR

4

SMA10

SMA11

SMA12

SCS#0

SCS#1

SCS#2

SCS#3

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

SCK#0

SCK#1

SCK#2

SCK#3

SCK#4

SCK#5

SCKE0

SCKE1

SCKE2

SCKE3

SRAS#

SCAS#

SWE#

SM_RCOMP

SD_REF0

SD_REF1

G_FRAME#

G_IRDY#

G_TRDY#

G_DEVSEL#

G_STOP#

G_PAR

G_REQ#

G_GNT#

SB_STB

SB_STB#

AD_STB0

AD_STB0#

AD_STB1

AD_STB1#

PIPE#

WBF#

AGPREF

G_RCOMP

TESTIN#

4

SMA0

SMA1

SMA2

SMA3

SMA4

SMA5

SMA6

SMA7

SMA8

SMA9

SCB0

SCB1

SCB2

SCB3

SCB4

SCB5

SCB6

SCB7

SCK0

SCK1

SCK2

SCK3

SCK4

SCK5

SBS0

SBS1

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

RBF#

E12

F17

E16

G18

G19

E18

F19

G21

G20

F21

F13

E20

G22

E9

F7

F9

E7

C16

D16

B15

C14

B17

C17

C15

D14

F26

C26

C23

B19

D12

C8

C5

E3

E15

E14

F15

J24

G25

G6

G7

G15

G14

E24

G24

H5

F5

G23

E22

H23

F23

F11

G8

G11

G12

G13

J28

J9

J21

Y24

W27

W24

W28

W23

W25

AG24

AH25

AH28

AH27

AG28

AG27

AE28

AE27

AE24

AE25

AF27

AF26

AG25

AF24

AG26

R24

R23

AC27

AC28

AF22

AE22

AE23

AA21

AD25

H26

DDRMAA0

DDRMAA1

DDRMAA2

DDRMAA3

DDRMAA4

DDRMAA5

DDRMAA6

DDRMAA7

DDRMAA8

DDRMAA9

DDRMAA10

DDRMAA11

DDRMAA12

DDRCS#0

DDRCS#1

DDRCS#2

DDRCS#3

CB0

CB1

CB2

CB3

CB4

CB5

CB6

CB7

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDQS8

DCLK0

DCLK#0

DCLK1

DCLK#1

DCLK2

DCLK#2

DCLK3

DCLK#3

DCLK4

DCLK#4

DCLK5

DCLK#5

DDRCKE0

DDRCKE1

DDRCKE2

DDRCKE3

RASA#

CASA#

WEA#

DDRBS0

DDRBS1

MRCOMP

SM_REF

SBA0

SBA1

SBA2

SBA3

SBA4

SBA5

SBA6

SBA7

ST0

ST1

ST2

CB224 X_0.1u

R165 40.2

R168 X_4.7K

DDRMAA[0..12] 16,26,27

DDRCS#[0..3]

CB[0..7]

SDQS0 26

SDQS1 26

SDQS2 26

SDQS3 26

SDQS4 26

SDQS5 26

SDQS6 26

SDQS7 26

SDQS8 26

DDRCKE0 16,27

DDRCKE1 16,27

DDRCKE2 16,27

DDRCKE3 16,27

RASA# 26

CASA# 26

WEA# 26

DDRBS0 16,26,27

DDRBS1 16,26,27

GFRAME# 17

GIRDY# 17

GTRDY# 17

GDEVSEL# 17

GSTOP# 17

GPAR 17

GREQ# 17

GGNT# 17

SBA[0..7] 17

SB_STB 17

SB_STB# 17

ST[0..2] 17

GAD_STB0 17

GAD_STB#0 17

GAD_STB1 17

GAD_STB#1 17

PIPE# 17

RBF# 17

WBF# 17

AGPREF 17

VCC1_8

3

DDRCS#[0..3] 16,26,27

CB[0..7] 26

3

EMI

BACK

close MCH

5/23 update

VCC_AGP

MRCOMP

DDR_VTT

0.1uC208

0.1uC8

R500

30

C500

0.1u

DCLK#1

DCLK1

DCLK#4

DCLK4

DCLK3

DCLK#3

DCLK0

DCLK#0

DCLK2

DCLK#2

DCLK#5

DCLK5

CB93

1u

CB98

0.1u

CB94

0.1u

CB97

0.1u

CB100

0.01u

CB96

10u-1206

CB90

10u-1206

VCC5

V_DIMM VCC5

CB219

X_0.1u

CB222

X_0.1u

CB220

X_0.1u

CB227

X_0.1u

CB223

X_0.1u

CB226

X_0.1u

2

MCH REFERENCE VOLTAGE

SM_REF

MCH MEMORY CLOCK RC CIRCUITS

RN538

7 8

5 6

3 4

1 2

X_0

RN539

1 2

3 4

5 6

7 8

X_0

RN540

1 2

3 4

5 6

7 8

X_0

DCLK#1

DCLK1

DCLK#4

DCLK4

DCLK3

DCLK#3

DCLK0

DCLK#0

DCLK2

DCLK#2

DCLK#5

DCLK5

DCLK#1 16,26

DCLK1 16,26

DCLK#4 16,26

DCLK4 16,26

DCLK3 16,26

DCLK#3 16,26

DCLK0 16,26

DCLK#0 16,26

DCLK2 16,26

DCLK#2 16,26

DCLK#5 16,26

DCLK5 16,26

MCH DECOUPLING CAPACITOR

VCC1_8 V_DIMMVCCP VCC_AGP

CB117

1u

CB116

0.1u

C21

0.1u

V_DIMMVCCP

CB225

X_0.1u

CB221

X_0.1u

Micro-Star

Document Number

Last Revision Date:

2

Wednesday, August 29, 2001

CB114

0.1u

CB115

0.1u

CB126

0.1u

CB118

0.1u

CB106

0.1u

C104 1u

Title

1

DIMMREF

C95

C97

0.1u

0.1u

0.1uC1050.1uC211

MS-6507

Brookdale MCH 2

1

CB89

0.1u

CB76

0.1u

CB101

0.1u

CB86

0.1u

CB78

0.1u

CB84

0.1u

CB81

0.1u

AGPREF

Sheet of

8 36

Rev

0B

Page 9

ICH2 PCI / HUB LINK / CPU / LAN / INTERRUPT SIGNALS

VCC1_8

D10D2E5

K19

L19P5V9

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

GND1

GND2

GND3

GND4

GND5

A1A2A10B1B2B3B9

E14

GND6

AD[0..31]18,25

C_BE#[0..3]18,25

DEVSEL#18,25

FRAME#18,25

PLOCK#18

ICH_PCLK4

PCIRST#4

E_EECS12

CNR_EEDIN12

CNR_EEDOUT12

CNR_SHCLK12

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

C_BE#0

C_BE#1

C_BE#2

C_BE#3

IRDY#18,25

TRDY#18,25

STOP#18,25

PAR18,25

SERR#18,25

PERR#18,25

PME#17,18,25

REQA#

GNTA#

AA4

AB4

AB3

AA5

AB5

AA6

AA8

AB8

AB9

W10

AA10

AA3

AB6

AA9

AB7

AA7

W11

AA15

Y4

W5

W4

Y5

Y3

W6

W3

Y6

Y2

Y1

V2

V1

U4

W9

U3

Y9

U2

U1

T4

Y10

T3

Y8

V3

W8

V4

W1

W2

W7

Y7

Y15

M3

L2

F4

G4

H3

H4

J1

K4

K3

J4

J3

U17A

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE#0

CBE#1

CBE#2

CBE#3

DEVSEL#

FRAME#

IRDY#

TRDY#

STOP#

PAR

PLOCK#

SERR#

PERR#

PME#

GPIO0/REQA#

GPIO16/GNTA#

PCICLK

PCIRST#

NC12

NC13

NC14

NC15

NC16

EE_CS

EE_DIN

EE_DOUT

EE_SHCLK

VCC1.8

VCC3

E15

E16

E17

E18

F18

G18

H18

J18

P18

R18R5T5U5V5V6V7V8V14

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

VCC3

GND7

GND8

GND9

GND10

GND11

GND12

GND13

GND14

GND15

GND16

GND17

GND18

B10C2C3C4C9D5D6D7D8D9E6E7E8E9J9

GND19

VCC3

VCC3

GND20

GND21

VCC3

VCC3

GND22

GND23

J10

VCC3

GND24

J11

J12

VCC1_8SB

V15

V16H5J5

VCCSUS1_8

VCCSUS1_8

GND25

GND26

GND27

J13

J14K9K10

A22

VCCSUS1_8

VCCSUS1_8

VCCSUS1_8

GND28

GND29

GND30

GND31

K11

K12

K13

B21

B22C1D1D3E1E2E3

GND68

GND69

GND70

GND71

GND32

GND33

GND58

GND59

K14J2K1

AA1

AA2

E4

NC5

NC6

NC8

NC9

CPUSLP#

NC10

NC11

NC17

FERR#

IGNNE#

STPCLK#

A20GATE

HL_STB

HL_STB#

HLCOMP

HUBREF

PIRQA#

PIRQB#

PIRQC#

PIRQD#

APICCLK

APICD0

APICD1

SERIRQ

REQ0#

REQ1#

REQ2#

REQ3#

LAN_RSTSYNC

GND62

GND63

GND64

AB1

AB2

AB21

REQ4#

GNT0#

GNT1#

GNT2#

GNT3#

GNT4#

LAN_CLK

LAN_RXD0

LAN_RXD1

LAN_RXD2

LAN_TXD0

LAN_TXD1

LAN_TXD2

GND67

GND65

GND66

82801BA-VB11

GPIO1/REQB#/REQ5#

GPIO17/GNTB#/GNT5#

GND60

GND61

AA21

AA22

A20M#

INIT#

INTR

NMI

SMI#

RCIN#

HL10

HL11

IRQ14

IRQ15

A20M#

D11

A12

FERR#

R22

A11

C12

C11

B11

SMI#

B12

C10

KB_RST#

B13

A20GATE#

C13

HL0

A4

HL0

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

B5

A5

B6

B7

A8

B8

A9

C8

C6

C7

C5

A6

A7

A3

B4

P1

P2

P3

N4

F21

C16

N20

P22

N19

N21

R2

R3

T1

AB10

P4

L3

M2

M1

R4

T2

R1

L4

G3

H2

G2

G1

H1

F3

F2

F1

A21

AB22

HL1

HL2

HL3

HL4

HL5

HL6

HL7

HL8

HL9

HL10

R221 40.2

HUB_IREF

APIC_CLK

APIC_D0

APIC_D1

SERIRQ

PREQ#0

PREQ#1

PREQ#2

PREQ#3

PREQ#4

PREQ#5

PGNT#0

PGNT#1

PGNT#2

PGNT#3

PGNT#4

PGNT#5

A20M# 5

SLP# 5

FERR# 5

IGNNE# 5

HINIT# 5,15

INTR 5

NMI 5

STPCLK# 5

KB_RST# 11

A20GATE# 11

HL[0..10] 7

This resistor less than 0.5"

from ICH use 15 mils trace

HL_STB 7

HL_STB# 7

VCC1_8

INTA# 17,18

INTB# 17,18

INTC# 18

INTD# 18

IRQ14 4

IRQ15 4

SERIRQ 11,18

PREQ#[0..5] 18,25

PGNT#[0..5] 18,25

ELAN_CLK 12

ELAN_SYNC 12

ELAN_RXD0 12

ELAN_RXD1 12

ELAN_RXD2 12

ELAN_TXD0 12

ELAN_TXD1 12

ELAN_TXD2 12

ICH2 SMI# SIGNAL

SMI#

R218 33

HSMI# 5

100pC143

ICH2 STRAPPING RESISTORS

FERR#

SERIRQ

KB_RST#

A20GATE#

REQA#

GNTA#

5/23 update

APIC_D0

APIC_D1

APIC_CLK

R279 62

R256 8.2K

R219 10K

R220 10K

R284 2.7K

R272 X_2.7K

R578 10K

R579 10K

R637 10K

VCCP

VCC3

VCC3

VCC5

VCC3

ICH2 REFERENCE VOLTAGE

VCC1_8

HUB_IREF

C142

C141

C140

0.1u

0.1u

R223

150

R222

1500.01u

VCC3

CB171

0.1u

CB184

0.1u

Place one 0.1U/0.01U pair in each corner and

2 on opposite sides close to ICH2 if it fit

CB146

0.1u

CB170

0.1u

CB167

CB141 CB158

0.1u

0.01u

ICH2 DECOUPLING CAPACITORS

CB142

0.01u

CB134

CB140

0.1u

0.1u

Distribute near the 1.8V

power pin of the ICH2

VCC1_8SBVCC1_8

CB157

0.1u

0.1u

Distribute near the VCC1_8SB

Power pin of the ICH2

Place Cap. as Close as possible to ICH2

Trace width use 15 mils and 15mils space

Title

Micro-Star

Document Number

Last Revision Date:

Tuesday, July 24, 2001

MS-6507

Brookdale ICH2 PCI

Sheet of

9 36

Rev

0B

Page 10

ICH2 ASIC / RTC / AC'97 / GPIO / LPC / USB / IDE SIGNALS

CB181

0.1u

AA13

W16

AB18

W21

AA17

AA18

AA16

AB16

AB17

W22

W14

AB15

AB14

AA14

W12

AB13

AB12

AA12

W13

AB11

W17

AB19

AA19

W18

AB20

AA20

W19

W20

U17B

THRM#

SLP_S3#

SLP_S5

R20

PWROK

A13

CPUPWRGD

B15

VRMPWRGD

PWRBTN#

RI#

R21

RSMRST#

Y16

RSM_PWROK

Y17

SUSSTAT#

SUSCLK

SMBDATA

SMBCLK

GPIO11/SMBALERT#

U19

SMLINK0

V20

SMLINK1

T19

INTRUDER#

T20

RTCRST#

T21

VBIAS

U22

RTCX1

T22

RTCX2

D4

CLK66

M19

CLK14

P20

CLK48

V22

AC_RST#

P19

AC_SYNC

R19

AC_BITCLK

P21

AC_SDOUT

Y22

AC_SDIN0

AC_SDIN1

N22

SPKR

GPIO12

GPIO13

L1

GPIO21

B14

GPIO22

A14

GPIO23

GPIO27

GPIO28

Y12

LAD0/FWH0

LAD1/FWH1

LAD2/FWH2

LAD3/FWH3

FS0

Y13

LDRQ0#

LDRQ1#

LFRAME#/FWH4

USBP0+

Y18

USBP0USBP1+

USBP1USBP2+

Y19

USBP2USBP3+

USBP3OC0#

Y20

OC1#

Y21

OC2#

OC3#

RTC_VCC

RING#24

SPKR19

GP2315

OC#020

OC#112,20

VCCP VCC5_SB

CB147

0.1u

THRM#

PWR_GD

VRM_GD

RING#

RSMRST#

SMB_ALERT

INTRUDER#

RTCRST#

VBIAS

RTCX2

R261 33

SIO_PME#

6CH_CTRL

GP23

R327 X_10K

VCC3_SB

CB193

0.1u

THRM#11

SLP_S3#11,22

SLP_S5#22

PWR_GD19

CPU_GD5

VRM_GD23

PWRBTN#11,15

RSMRST#11

SUSCLK11

SMBDATA4,11,12,16

SMBCLK4,11,12,16

SM_LNK018

SM_LNK118

ICH_664

ICH_144

ICH_484

AC_RST#12

AC_SYNC12,13

AC_BCLK12,13

AC_SDOUT12,13,15

AC_SDIN012,13,15

AC_SDIN112,15

EXTSMI#19

SIO_PME#11

6CH_CTRL21

LAD0/FWH011,15

LAD1/FWH111,15

LAD2/FWH211,15

LAD3/FWH311,15

LDRQ#11

LFRAME#/FWH411,15

USBP0+20

USBP0-20

USBP1+20

USBP1-20

USBP2+20

USBP2-20

USBP3+12,20

USBP3-12,20

CB143

0.1u

Distribute near the VCC3_SB power pin of the ICH

VCC3_SB

RTC_VCC

U21

T18

U18

F5G5V17

V18

VCCRTC

VCC3SUS1

VCC3SUS2

VCC3SUS4

VCC3SUS5

VCC3SUS6

VCC3SUS7

GND34

GND35

GND36

GND37

GND38

GND39

GND40

GND41

GND42

GND43

GND44

GND45

L9

L10

L11

L12

L13

L14M9M10

M11

M12

M13

M14N9N10

GND46

ICH2 DECOUPLING CAPACITOR

VCC5_SBVCC5

CB169

0.01u

CB179

0.1u

VCCP VCC5_SB

D12

D13

V19K2M20

VCPU_IO1

VCPU_IO2

GND47

GND48

GND49

GND50

GND51

GND52

N11

N12

N13

N14P9P10

CB180

0.1u

VCC5REF1

VCC5REF2

VCC5REF_SUS

GPIO2/PIRQE#

GPIO3/PIRQF#

GPIO4/PIRQG#

GPIO5/PIRQH#

GND53

GND54

GND55

GND56

GND57

82801BA-VB11

P11

P12

P13

P14

VCC3

D14

1N5817-S-DO-241AC

CB161

0.1u

E21

PDCS1#

C15

SDCS1#

E19

PDCS3#

D15

SDCS3#

F20

PDA0

F19

PDA1

E22

PDA2

A16

SDA0

D16

SDA1

B16

SDA2

G22

PDDREQ

B18

SDDREQ

F22

PDDACK#

B17

SDDACK#

G19

PDIOR#

D17

SDIOR#

G21

PDIOW#

C17

SDIOW#

G20

PIORDY

A17

SIORDY

H19

PDD0

H22

PDD1

J19

PDD2

J22

PDD3

K21

PDD4

L20

PDD5

M21

PDD6

M22

PDD7

L22

PDD8

L21

PDD9

K22

PDD10

K20

PDD11

J21

PDD12

J20

PDD13

H21

PDD14

H20

PDD15

D18

SDD0

B19

SDD1

D19

SDD2

A20

SDD3

C20

SDD4

C21

SDD5

D22

SDD6

E20

SDD7

D21

SDD8

C22

SDD9

D20

SDD10

B20

SDD11

C19

SDD12

A19

SDD13

C18

SDD14

A18

SDD15

U20

TP0

N3

N2

N1

M4

Y11

GPIO6

AA11

GPIO7

Y14

GPIO8

A15

GPIO18

D14

GPIO19

C14

GPIO20

V21

GPIO24

W15

GPIO25

VCC5

R257

1K

CB156

0.1u

PDD0

PDD1RTCX1

PDD2

PDD3

PDD4

PDD5

PDD6

PDD7

PDD8

PDD9

PDD10

PDD11

PDD12

PDD13

PDD14

PDD15

SDD0

SDD1

SDD2

SDD3

SDD4

SDD5

SDD6

SDD7

SDD8

SDD9

SDD10

SDD11

SDD12

SDD13

SDD14

SDD15

BATLOW#

GP6

GP7

PD_CS#1 4

SD_CS#1 4

PD_CS#3 4

SD_CS#3 4

PD_A0 4

PD_A1 4

PD_A2 4

SD_A0 4

SD_A1 4

SD_A2 4

PD_DREQ 4

SD_DREQ 4

PD_DACK# 4

SD_DACK# 4

PD_IOR# 4

SD_IOR# 4

PD_IOW# 4

SD_IOW# 4

PD_IORDY 4

SD_IORDY 4

PDD[0..15] 4

SDD[0..15] 4

INTE# 18

INTF# 18,25

INTG# 18

INTH# 18

LAN_WAKE 24

VCC5_SB

D21

VBAT

1N5817-S-DO-241AC

VCCP

PD_IORDY

SD_IORDY

PD_DREQ

SD_DREQ

INTRUDER#

RSMRST#

SPKR

PWR_GD

THRM#

VRM_GD

SIO_PME#

RING#

RSMRST#

PWRBTN#

R331

1.5K

D19

1N4148-S-LL34

R340

4.7K

D20

1N5817-S-DO-241AC

R568

1K

BAT1

{MSI-BOM}

PROCHOT BLOCK

R211 4.7K

PROCHOT#5

R133 4.7K

R224 4.7K

R97 5.6K

R225 5.6K

R280 10K

R365 10K

R260 X_10K

R273 8.2K

R345 10K

R216 10K

R377 4.7K

R367 8.2K

R366 1K

R329 10K

RTC_VCC

R567

1K

R411 390K

C167

0.047u

R277

20M

R274

5.6M

C215

0.047u

R317 10M R293 10M

C174

15p

THRM#

Q32

NPN-3904LT1-S-SOT23

1

2

3

R410

1K

X2

32K-12.5pf-CSA-309-D

+-30PPM

32pF

ICH2 STRAPPING RESISTORS

SM_LNK0

SM_LNK1

BATLOW#

SMB_ALERT

RTC_VCC

SLP_S3#

5/21 update

GP23

GP6

VCC3

VCC3

VCC3_SB

GP7

EXTSMI#

Title

Micro-Star

Document Number

Last Revision Date:

Wednesday, August 29, 2001

Brookdale ICH2 Other

RTC BLOCK

JBAT1 Clear CMOS

Normal1 - 2

Clear CMOS2 - 3

JBAT1

D1x3-BK

RTCRST#

VBIAS

RTCX1

RTCX2

C170

15p

RN28

4.7K

1 2

3 4

5 6

7 8

RN32

10K

1 2

3 4

5 6

7 8

RN31

4.7K

1 2

3 4

5 6

7 8

R574 4.7K

MS-6507

Sheet of

*

VCC3_SBVCC3

VCC3_SB

VCC3

VCC3_SB

Rev

0B

10 36

Page 11

Hardware Monitor

CPU_TMPA5

VCC5

CPUFAN20

SMBDATA4,10,12,16

SMBCLK4,10,12,16

SYSFAN20

VCC5

R702 X_0

R630 X_0

R631 0

R632 0

R633 X_0

R703 X_0

LFRAME#/FWH410,15

CPU_TMPA

VID[0..4]5,23

LAD0/FWH010,15

LAD1/FWH110,15

LAD2/FWH210,15

LAD3/FWH310,15

R158

0

VTIN_GND5

CPU_CTRL20

SYS_CTRL20

VCC5_SB

LPC SUPER I/O W83627HF

U13

R143 10K

10K

R153

30

LRESET#

21

LCLK

23

SERIRQ

22

LDRQ#

29

LFRAME#

27

LAD0

26

LAD1

25

LAD2

24

LAD3

125

GPX2/P15/GP14

123

GPY1/GP15

128

GPSA1/P12/GP10

121

GPSA2/GP17

126

GPX1/P14/GP12

124

GPY2/P16/GP14

127

GPSB1/P13/GP11

122

GPSB2/GP16

120

MSO/IRQIN0

119

MSI/GP20

101

VREF

102

VTIN3

103

VTIN2

104

VTIN1

93

AGND

94

-5VIN

95

-12VIN

96

+12VIN

97

AVCC

98

+3.3VIN

99

VCOREB

100

VCOREA

106

VID4

107

VID3

108

VID2

109

VID1

110

VID0

116

FANPWM1

113

FANIO1

115

FANPWM2

112

FANIO2

111

FANIO3

105

OVT#

118

BEEP

76

CASEOPEN#

19

PME#

89

WDTO/GP24

91

SDA/GP22

92

SCL/GP21

67

PSOUT#

68

PSIN#

64

SUSLED/GP35

90

PLED/GP23

72

PWRCTL#/GP31

73

SUSCIN/GP30

18

CLKIN

61

VSB

74

VBAT

28

VCC3

12

VCC_1

48

VCC_2

77

VCC_3

114

VCC_4

{1ST PART FIELD}

WB-W83627HF-AW-VG

SIO

CIRRX/GP34

RSMRST#/GP33

PWROK/GP32

PCIRST#14,7,15,25

SIO_PCLK4

SERIRQ9,18

LDRQ#10

JYS_AX214

JYS_AX114

JYS_PB014

JYS_PB114

JYS_AX014

JYS_AX314

JYS_PB314

JYS_PB214

MID_OUT14

MID_IN14

TMP_VREF

VCCP

THRM#10

SIO_PME#10

PWRBTN#10,15

PWRBTIN#19

SUS_LED19

PWR_LED19

VCC3

SLP_S3#10,22

VBAT

VCC3

VCC5

CPU_TMP

SYS_TMP

VTIN_GND

-5VIN

-12VIN

+12VIN

VTIN_VCC

VID4

VID3

VID2

VID1

VID0

BEEP

CHASISS

DLED221

PSON#19

SIO_484

CPU_TMP20

CPU_FAN20

SYS_FAN20

DRVDEN0

DRVDEN1

INDEX#

MOA#

DSB#

DSA#

MOB#

DIR#

STEP#

WRDATA#

WE#

TRACK0#

WP#

RDDATA#

HEAD#

DSKCHG#

PD0

PD1

PD2

PD3

PD4

PD5

PD6

PD7

SLCT

BUSY

ACK#

SLIN#

INIT#

ERR#

AFD#

STB#

IRRX/GP25

IRTX/GP26

SUSCLKIN

DCDA#

DSRA#

SINA

RTSA#

SOUTA

CTSA#

DTRA#

RIA#

DCDB#

DSRB#

SINB

RTSB#

SOUTB

CTSB#

DTRB#

RIB#

GA20

KBRST

KBDATA

KBCLK

MSDATA

MSCLK

KBLOCK#

VSS1

VSS2

VSS3

VSS4

1

2

3

4

5

6

7

8

9

10

11

13

14

15

16

17

1 2

42

RN5

3 4

41

33

5 6

40

7 8

39

7 8

38

RN6

5 6

37

33

3 4

36

1 2

35

31

32

PE

RN11 33

33

ACK#

34

SLIN#

43

INIT#

44

45

46

47

88

69

87

75

56

50

53

51

54

49

52

57

84

79

82

80

83

78

81

85

59

60

63

62

66

65

58

70

71

20

55

86

117

ACK#PE

PE

INIT#

SLIN#

33

RN12

R142 33

IRRX

IRTX

RTSA#

SOUTA

SOUTB

R146 X_0

R148 0

7 8

5 6

3 4

1 2

1 2

3 4

5 6

7 8

LP_D0

LP_D1

LP_D2

LP_D3

LP_D4

LP_D5

LP_D6

LP_D7

RSMRST#

DRVDEN0 24

DRVDEN1 24

INDEX# 24

MOT_A# 24

DRV_B# 24

DRV_A# 24

MOT_B# 24

DIR# 24

STEP# 24

WT_DT# 24

WT_EN# 24

TRACK0# 24

WP# 24

RDATA# 24

HEAD# 24

DSKCHG# 24

LP_D[0..7] 24

LP_SLCT 24

LP_ACK# 24

LP_BUSY 24

LP_PE 24

LP_INIT# 24

LP_SLIN# 24

LP_ERR# 24

LP_AFD# 24

LP_STB# 24

DLED3 21

SUSCLK 10

DCDA# 24

DSRA# 24

SINA 24

RTSA# 24

SOUTA 24

CTSA# 24

DTRA# 24

RIA# 24

DCDB# 24

DSRB# 24

SINB 24

RTSB# 24

SOUTB 24

CTSB# 24

DTRB# 24

RIB# 24

A20GATE# 9

KB_RST# 9

KBDATA 24

KBCLK 24

MSDATA 24

MSCLK 24

KBLOCK# 19

RSMRST# 10

DLED1 21

DLED4 21

5/22 update

THERMAL RESISTOR BLOCK

VTIN_VCC

NOTE: LOCATE INSIDE

SOCKET478

FB13 120

CB102 0.1u

TMP_VREF

R157

10K

CPU_TMP

RT1

X_10K

VTIN_GND

TMP_VREF CPU_TMPA

R163 30K

VCC5

VTIN_GND

R166

10K

RT2

10K

NOTE: LOCATE CLOSE

STATUS PANEL

CHASISS INTRUSION HEADER

VBAT

R152

2M

+12V

-12V

-5V

J5

1

2

D1x2

R145 28K1 2

R150 232K1 2

R160 120K1 2

CHASISS

12

VTIN_GND

FB12 120

TMP_VREF

SYS_TMP

VTIN_GND

R144

10K

SPEAKER BLOCK

VCC5

R162

10K

BEEP

R164 4.7K

NPN-3904LT1-S-SOT23

SUPER I/O STRAPPING RESISTOR

R214 10K

VCC3_SB

R169 4.7K

VCC5

R151 4.7K

VCC5

R175 X_4.7K

VCC5

SOUTA

L: Disable KBC H: Enable KBC

SOUTB

L: 24MHZ H: 48MHZ

RTSA#

L: CFAD=2E H: CFAD=4E

DTRA# L: PNP Default H: PNP no Default

+12VIN

-12VIN

-5VIN

12

12

R161

R149

56K

56K

TMP_VREF

ALARM 19

Q28

PWRBTN#

SOUTA

SOUTB

RTSA#

DECOUPLING CAPACITOR

5/21 update

VCC3_SB

RESUME RESET CIRCUIT BLOCK

Stuff all for D Version bug

U20A

74LCX14MX-SOIC14

R408 22K

C206

1u

1 2

(VCC3_SB)

R396 4.7K

RSMRST#

Q44

NPN-3904LT1-S-SOT23

IR HEADER

IRRX19

IRTX19

VCC5

IRRX

IRTX

IR1

1

1

3

3

4

4

5

5

D1x5-1:4-BK

VCC3 VCC5

CB133

0.1u

CB119

0.1u

VBAT VCCP

CB104

0.1u

CB121

0.1u

CB103

0.1u

CB11

0.1u

CB120

0.1u

C100

0.1u

VCC5_SB

CB111

0.1u

Title

Micro-Star

Document Number

Last Revision Date:

Wednesday, August 29, 2001

MS-6507

LPC I/O W83627HF

Sheet of

Rev

0B

11 36

Page 12

8

7

6

5

4

3

2

1

VCC3

R747

330

D D

PRI_RST#13

AC_RST#

VCC5_SB

U21C

7407-SOIC14

5 6

14

7

NPN-3904LT1-S-SOT23

R746 4.7K

Q708

R744

10K

R743

DN#

JP2

X_0

1

2

3

D1x3-BK

VCC3

R745 4.7K

C_EEDOUT

R724

10K

+12V

VCC5_SB

-12V

C C

RLAN_TXD1

RLAN_SYNC

RLAN_RXD2

RLAN_RXD0

OC#110,20

VCC3

C_SHCLK

AC_SYNC10,13

R721

B B

10K

AC_SDOUT10,13,15

AC_BCLK10,13

C705

C706

10p

100p C704

CNR1

B1

RESV1

B2

RESV2

B3

RESV3

B4

GND1

B5

RESV4

B6

RESV5

B7

GND2

B8

LAN_TXD1

B9

LAN_RSTSYNC

B10

GND3

B11

LAN_RXD2

B12

LAN_RXD0

B13

GND4

B14

RESV6

B15

+5VDUAL

B16

USB_OC#

B17

GND5

B18

-12V

B19

+3.3VD

B20

GND6

B21

EE_DOUT

B22

EE_SHCLK

B23

GND7

B24

SMB_A0

B25

SMB_SCL

B26

PRIMARY_DN#

B27

GND8

B28

AC97_SYNC

B29

AC97_SDATA_OUT

B30

AC97_BITCLK

CNR-D60

ADDRESS AE

RESV7

RESV8

GND9

RESV9

RESV10

GND10

LAN_TXD2

LAN_TXD0

GND11

LAN_CLK

LAN_RXD1

RESV11

USB+

GND12

USB+12V

GND13

+3.3VDUAL

+5VD

GND14

EE_DIN

EE_CS

SMB_A1

SMB_A2

SMB_SDA

AC97_RESET#

RESV12

AC97_SDATA_IN1

AC97_SDATA_IN0

GND15

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22