Motorola MCM6949YJ10, MCM6949YJ12, MCM6949YJ12R, MCM6949YJ15, MCM6949YJ15R Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Advance Information

1M x 4 Bit Static Random

Access Memory

The MCM6949 is a 4,194,304 bit static random access memory organized as

1,048,576 words of 4 bits. Static design eliminates the need for external clocks

or timing strobes.

The MCM6949 is equipped with chip enable (E

allowing for greater system flexibility and eliminating bus contention problems.

Either input, when high, will force the outputs into high–impedance.

The MCM6949 is available in a 400 mil, 32–lead surface–mount SOJ package.

• Single 3.3 V – 5%, + 10% Power Supply

• Fast Access Time: 8/10/12/15 ns

• Equal Address and Chip Enable Access Time

• All Inputs and Outputs are TTL Compatible

• Three–State Outputs

• Power Operation: 195/165/160/155 mA Maximum, Active AC

) and output enable (G) pins,

Order this document

MCM6949

YJ PACKAGE

400 MIL SOJ

CASE 857A–02

PIN NAMES

A0 – A19 Address Inputs. . . . . . . . . . . . . . . .

W

G

E

DQ Data Input/Output. . . . . . . . . . . . . . . . . .

NC No Connection. . . . . . . . . . . . . . . . . . . . .

V

CC

V

SS

+ 3.3 V Power Supply. . . . . . . . . . . . . .

by MCM6949/D

Write Enable. . . . . . . . . . . . . . . . . . . . . . .

Output Enable. . . . . . . . . . . . . . . . . . . . . .

Chip Enable. . . . . . . . . . . . . . . . . . . . . . . . .

Ground. . . . . . . . . . . . . . . . . . . . . . . . . .

This document contains information on a new product. Specifications and information herein are subject to change without notice.

REV 4

4/2/98

Motorola, Inc. 1998

MOTOROLA FAST SRAM

MCM6949

1

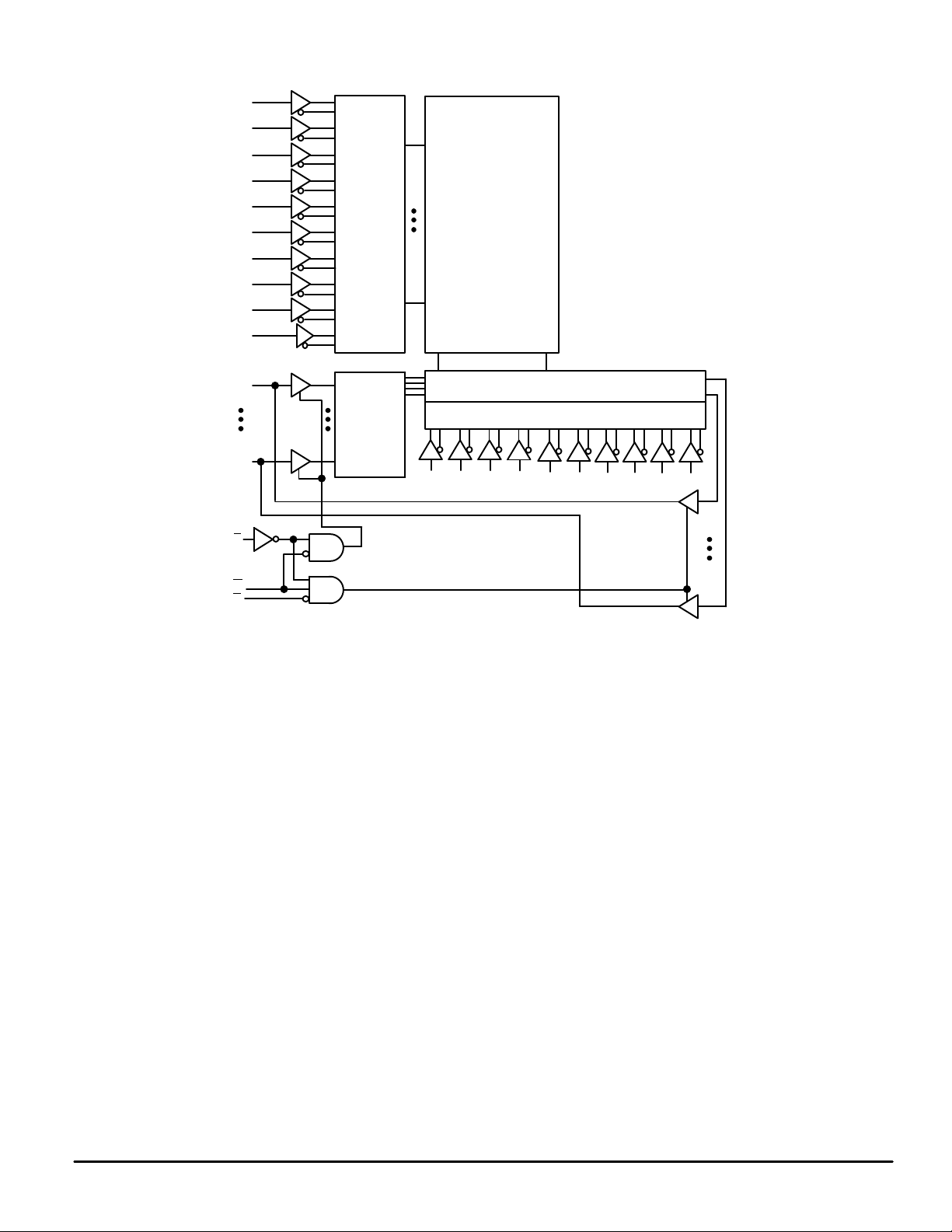

BLOCK DIAGRAM

A

A

A

A

A

A

A

A

A

A

ROW

DECODER

MEMORY MATRIX

DQ

DQ

E

W

G

INPUT

DATA

CONTROL

COLUMN I/O

COLUMN DECODER

AA AAA AAAAA

DQ

DQ

MCM6949

2

MOTOROLA FAST SRAM

PIN ASSIGNMENT

AA

1

A

2

A

3

A

4

A

5

E

6

DQ

7

V

8

CC

V

9

SS

DQ

10

W

11

12

A

13

A

14

A

15

A

ANC

16

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

A

A

A

A

G

DQ

V

V

DQ

A

A

A

A

A

SS

CC

MOTOROLA FAST SRAM

MCM6949

3

Loading...

Loading...