Motorola MCM67T415 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Advance Information

16K x 15 Bit Cache Tag RAM

for Pentium Processors

Order this document

by MCM67T415/D

MCM67T415

The MCM67T415 is a 245,760 bit cache–tag static RAM designed to support

Pentium microprocessors at bus speeds up to 66 MHz. It is organized as 16K words

of 15 bits each and is fabricated using Motorola‘s high performance, silicon gate

BiCMOS technology . There are twelve common I/O tag bits and three separate I/O

status bits. A 12–bit comparator is on–chip to allow fast comparison of the 12 stored

tag bits with the current tag input data. An active high MA TCH output is generated

when the valid bit is true and these two groups of data are the same for a given

address.

This high–speed MA TCH signal, with t

fastest possible enabling of secondary cache accesses.

The three separate I/O status bits (V ALID, DIRTY, and WT) can be configured for

either dedicated or generic functionality, depending on the SFUNC input pin. With

SFUNC low, the status bits are defined and used internally by the device, allowing

easier determination of the validity and use of the given tag data. SFUNC high

releases the defined internal status bit usage and control, allowing users to

configure the status bit information to fit their system needs. A synchronous RESET

pin, when held low at a rising clock edge, will reset all status bits in the array for easy

invalidation of all tag addresses.

The MCM67T415 also provides the option for burst ready (BRDY

within the cache tag itself, based upon MA TCH, VALID bit, WT bit, and other external

inputs provided by the user. This can significantly simplify cache controller logic and

minimize cache decision time. Match and read operations are both asynchronous

in order to provide the fastest access times possible, while write operations are

synchronous for ease of system timing.

The MCM67T415 uses a 5 V power supply on VCC and VSS, with separate V

pins provided for the outputs to offer compliance with both 5 V TTL and 3.3 V L VTTL

logic levels. The PWRDN

significant system power savings.

The MCM67T415 is offered in a space saving 80–pin thin quad flat pack (TQFP)

package.

• 16K x 15 Configuration:

– 12 Tag Bits

– Three Status Bits (V alid, Dirty, and WT)

• V alid Bit used to Qualify Match Output

• High–Speed Address–to–Match Comparison Times – 9/10/12 ns

• BRDY

• Asynchronous Read/Match Operation and Synchronous Write and Reset

• Separate Write Enable for Tag Bits and Status Bits

• Separate Output Enable for Tag Bits, Status Bits, and BRDY

• Synchronous RESET Pin for Invalidation of all Tag Entries

• Dual Chip Selects for Easy Depth Expansion with No Performance

• I/O Pins Both 5 V TTL and 3.3 V L VTTL Compatible with V

• PWRDN

• Drop–In Replacement for IDT71215

• Packaged in an 80–Pin Thin Quad Flat Pack (TQFP)

Circuitry Included Inside the Cache–Tag for the Highest Speed

Operation

Operation

Degradation

Pin to Place Device in Low–Power Mode

pin offers a low–power standby mode, which provides

times as fast as 9 ns, provides the

AVMV

Pins

CCQ

) generation

CCQ

TQ PACKAGE

TQFP

CASE 917A–02

Pentium is a trademark of Intel Corp.

This document contains information on a new product. Motorola reserves the right to change or discontinue this product without notice.

9/10/96

Motorola, Inc. 1996

MOTOROLA FAST SRAM

MCM67T415

1

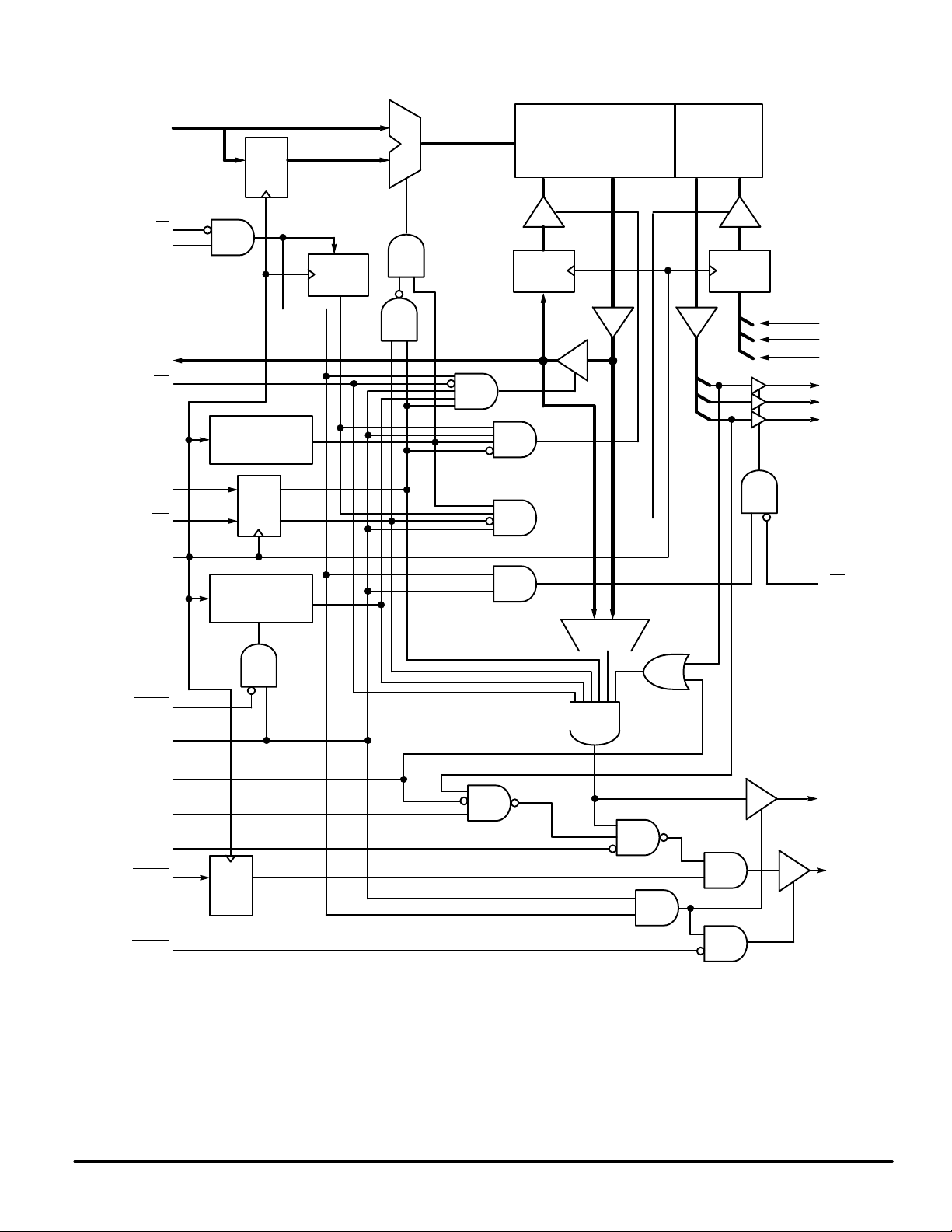

FUNCTIONAL BLOCK DIAGRAM

A0 – A13

E1

E2

TDQ0 – TDQ11

GT

WT

WS

0

REG

REG

WRITE (pos) PULSE

GENERAT OR

REG

K

RESET (neg) PULSE

GENERAT OR

1

DATA IN

REGISTER

16K x 12

MEMORY

TAG BITS

SA SA

16K x 3

MEMORY

STATUS BITS

DATA IN

REGISTER

VALIDD

DIRTYD

WTD

VALIDQ

DIRTYQ

WTQ

GS

RESET

PWRDN

SFUNC

W/R

BRDYH

BRDYD

BRDYG

COMPARE

MATCH

BRDY

REG

MCM67T415

2

MOTOROLA FAST SRAM

Loading...

Loading...