Motorola MC68331CFC16, MC68331VPV20, MC68331VFV20, MC68331MFV20, MC68331MPV16 Datasheet

...

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability

of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and

all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including

"Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others.

Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to

support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer

purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal

injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and ! are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, INC. 1996

MC68331

User’s Manual

MC68331 MOTOROLA

USER’S MANUAL iii

Paragraph Title Page

SECTION 1INTRODUCTION

SECTION 2NOMENCLATURE

2.1 Symbols and Operators ..................................................................................2-1

2.2 CPU32 Registers ............................................................................................2-2

2.3 Pin and Signal Mnemonics .............................................................................2-3

2.4 Register Mnemonics .......................................................................................2-5

2.5 Conventions ...................................................................................................2-6

SECTION 3OVERVIEW

3.1 MCU Features ................................................................................................3-1

3.1.1 System Integration Module (SIM) ...........................................................3-1

3.1.2 Central Processing Unit (CPU32) ...........................................................3-1

3.1.3 Queued Serial Module (QSM) ................................................................3-1

3.1.4 General-Purpose Timer (GPT) ...............................................................3-2

3.2 System Block Diagram and Pin Assignment Diagrams ..................................3-2

3.3 Pin Descriptions .............................................................................................3-5

3.4 Signal Descriptions .........................................................................................3-7

3.5 Intermodule Bus ...........................................................................................3-10

3.6 System Memory Map ...................................................................................3-10

3.6.1 Internal Register Map ...........................................................................3-10

3.6.2 Address Space Maps ...........................................................................3-10

3.7 System Reset ...............................................................................................3-16

3.7.1 SIM Reset Mode Selection ...................................................................3-16

3.7.2 MCU Module Pin Function During Reset .............................................3-17

SECTION 4 SYSTEM INTEGRATION MODULE

4.1 General ...........................................................................................................4-1

4.2 System Configuration and Protection .............................................................4-2

4.2.1 Module Mapping .....................................................................................4-3

4.2.2 Interrupt Arbitration .................................................................................4-3

4.2.3 Show Internal Cycles ..............................................................................4-4

4.2.4 Factory Test Mode .................................................................................4-4

4.2.5 Register Access .....................................................................................4-4

4.2.6 Reset Status ...........................................................................................4-4

4.2.7 Bus Monitor ............................................................................................4-4

4.2.8 Halt Monitor ............................................................................................4-5

4.2.9 Spurious Interrupt Monitor ......................................................................4-5

4.2.10 Software Watchdog ................................................................................4-5

TABLE OF CONTENTS

MOTOROLA MC68331

iv USER’S MANUAL

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

4.2.11 Periodic Interrupt Timer ..........................................................................4-7

4.2.12 Low-Power STOP Operation ..................................................................4-8

4.2.13 Freeze Operation ...................................................................................4-9

4.3 System Clock .................................................................................................4-9

4.3.1 Clock Sources ......................................................................................4-10

4.3.2 Clock Synthesizer Operation ................................................................4-10

4.3.3 External Bus Clock ...............................................................................4-15

4.3.4 Low-Power Operation ...........................................................................4-15

4.3.5 Loss of Reference Signal .....................................................................4-16

4.4 External Bus Interface ..................................................................................4-17

4.4.1 Bus Signals ..........................................................................................4-18

4.4.1.1 Address Bus ................................................................................. 4-18

4.4.1.2 Address Strobe ............................................................................ 4-18

4.4.1.3 Data Bus ...................................................................................... 4-18

4.4.1.4 Data Strobe .................................................................................. 4-18

4.4.1.5 Read/Write Signal ........................................................................ 4-18

4.4.1.6 Size Signals ................................................................................. 4-18

4.4.1.7 Function Codes ............................................................................ 4-19

4.4.1.8 Data and Size Acknowledge Signals ...........................................4-19

4.4.1.9 Bus Error Signal ...........................................................................4-19

4.4.1.10 Halt Signal .................................................................................... 4-20

4.4.1.11 Autovector Signal ......................................................................... 4-20

4.4.2 Dynamic Bus Sizing .............................................................................4-20

4.4.3 Operand Alignment ..............................................................................4-21

4.4.4 Misaligned Operands ...........................................................................4-21

4.4.5 Operand Transfer Cases ......................................................................4-22

4.5 Bus Operation ..............................................................................................4-22

4.5.1 Synchronization to CLKOUT ................................................................4-23

4.5.2 Regular Bus Cycles ..............................................................................4-23

4.5.2.1 Read Cycle ................................................................................... 4-24

4.5.2.2 Write Cycle ................................................................................... 4-25

4.5.3 Fast Termination Cycles .......................................................................4-25

4.5.4 CPU Space Cycles ...............................................................................4-26

4.5.4.1 Breakpoint Acknowledge Cycle .................................................... 4-27

4.5.4.2 LPSTOP Broadcast Cycle ............................................................ 4-30

4.5.5 Bus Exception Control Cycles ..............................................................4-30

4.5.5.1 Bus Errors .................................................................................... 4-32

4.5.5.2 Double Bus Faults ........................................................................ 4-32

4.5.5.3 Retry Operation ............................................................................ 4-33

4.5.5.4 Halt Operation .............................................................................. 4-33

4.5.6 External Bus Arbitration ........................................................................4-34

MC68331 MOTOROLA

USER’S MANUAL v

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

4.5.6.1 Slave (Factory Test) Mode Arbitration ......................................... 4-35

4.5.6.2 Show Cycles ................................................................................ 4-35

4.6 Reset ............................................................................................................ 4-36

4.6.1 Reset Exception Processing ................................................................4-36

4.6.2 Reset Control Logic ..............................................................................4-37

4.6.3 Reset Mode Selection ..........................................................................4-37

4.6.3.1 Data Bus Mode Selection ............................................................. 4-38

4.6.3.2 Clock Mode Selection .................................................................. 4-40

4.6.3.3 Breakpoint Mode Selection .......................................................... 4-40

4.6.4 MCU Module Pin Function During Reset .............................................4-40

4.6.5 Pin State During Reset .........................................................................4-41

4.6.5.1 Reset States of SIM Pins ............................................................. 4-41

4.6.5.2 Reset States of Pins Assigned to Other MCU Modules ............... 4-42

4.6.6 Reset Timing ........................................................................................4-42

4.6.7 Power-On Reset ...................................................................................4-43

4.6.8 Reset Processing Summary .................................................................4-44

4.6.9 Reset Status Register ..........................................................................4-45

4.7 Interrupts ......................................................................................................4-45

4.7.1 Interrupt Exception Processing ............................................................4-45

4.7.2 Interrupt Priority and Recognition .........................................................4-45

4.7.3 Interrupt Acknowledge and Arbitration .................................................4-46

4.7.4 Interrupt Processing Summary .............................................................4-47

4.7.5 Interrupt Acknowledge Bus Cycles .......................................................4-48

4.8 Chip Selects .................................................................................................4-48

4.8.1 Chip-Select Registers ...........................................................................4-50

4.8.1.1 Chip-Select Pin Assignment Registers ........................................ 4-51

4.8.1.2 Chip-Select Base Address Registers ...........................................4-52

4.8.1.3 Chip-Select Option Registers ....................................................... 4-52

4.8.1.4 PORTC Data Register .................................................................. 4-54

4.8.2 Chip-Select Operation ..........................................................................4-54

4.8.3 Using Chip-Select Signals for Interrupt Acknowledge ..........................4-54

4.8.4 Chip-Select Reset Operation ................................................................4-55

4.9 Parallel Input/Output Ports ...........................................................................4-57

4.9.1 Pin Assignment Registers ....................................................................4-57

4.9.2 Data Direction Registers ......................................................................4-57

4.9.3 Data Registers ......................................................................................4-57

4.10 Factory Test .................................................................................................4-57

SECTION 5 CENTRAL PROCESSING UNIT

5.1 General ...........................................................................................................5-1

5.2 CPU32 Registers ............................................................................................5-2

MOTOROLA MC68331

vi USER’S MANUAL

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

5.2.1 Data Registers ........................................................................................5-4

5.2.2 Address Registers ..................................................................................5-5

5.2.3 Program Counter ....................................................................................5-6

5.2.4 Control Registers ....................................................................................5-6

5.2.4.1 Status Register ............................................................................... 5-6

5.2.4.2 Alternate Function Code Registers ................................................ 5-6

5.2.5 Vector Base Register (VBR) ...................................................................5-7

5.3 Memory Organization .....................................................................................5-7

5.4 Virtual Memory ...............................................................................................5-9

5.5 Addressing Modes ..........................................................................................5-9

5.6 Processing States ..........................................................................................5-9

5.7 Privilege Levels ............................................................................................5-10

5.8 Instructions ................................................................................................... 5-10

5.8.1 M68000 Family Compatibility ...............................................................5-14

5.8.2 Special Control Instructions ..................................................................5-14

5.8.2.1 Low Power Stop (LPSTOP) ......................................................... 5-14

5.8.2.2 Table Lookup and Interpolate (TBL) ............................................ 5-14

5.9 Exception Processing ...................................................................................5-14

5.9.1 Exception Vectors ................................................................................5-15

5.9.2 Types of Exceptions .............................................................................5-16

5.9.3 Exception Processing Sequence ..........................................................5-17

5.10 Development Support ...................................................................................5-17

5.10.1 M68000 Family Development Support .................................................5-17

5.10.2 Background Debugging Mode ..............................................................5-18

5.10.2.1 Enabling BDM .............................................................................. 5-19

5.10.2.2 BDM Sources ...............................................................................5-19

5.10.2.3 Entering BDM ............................................................................... 5-20

5.10.2.4 BDM Commands .......................................................................... 5-21

5.10.2.5 Background Mode Registers ........................................................ 5-21

5.10.2.6 Returning from BDM .................................................................... 5-22

5.10.2.7 Serial Interface ............................................................................. 5-22

5.10.2.8 Recommended BDM Connection ................................................. 5-24

5.10.3 Deterministic Opcode Tracking ............................................................5-24

5.10.4 On-Chip Breakpoint Hardware .............................................................5-25

5.11 Loop Mode Instruction Execution .................................................................5-25

SECTION 6QUEUED SERIAL MODULE

6.1 General ...........................................................................................................6-1

6.2 QSM Registers and Address Map ..................................................................6-2

6.2.1 QSM Global Registers ............................................................................6-2

6.2.1.1 Low-Power Stop Operation ............................................................ 6-2

MC68331 MOTOROLA

USER’S MANUAL vii

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

6.2.1.2 Freeze Operation ........................................................................... 6-3

6.2.1.3 QSM Interrupts ............................................................................... 6-3

6.2.2 QSM Pin Control Registers ....................................................................6-4

6.3 Queued Serial Peripheral Interface ................................................................6-5

6.3.1 QSPI Registers .......................................................................................6-6

6.3.1.1 Control Registers ........................................................................... 6-7

6.3.1.2 Status Register ............................................................................... 6-7

6.3.2 QSPI RAM ..............................................................................................6-7

6.3.2.1 Receive RAM ................................................................................. 6-8

6.3.2.2 Transmit RAM ................................................................................ 6-8

6.3.2.3 Command RAM .............................................................................. 6-8

6.3.3 QSPI Pins ...............................................................................................6-8

6.3.4 QSPI Operation ......................................................................................6-9

6.3.5 QSPI Operating Modes ........................................................................6-10

6.3.5.1 Master Mode ................................................................................ 6-17

6.3.5.2 Master Wraparound Mode ........................................................... 6-19

6.3.5.3 Slave Mode .................................................................................. 6-20

6.3.5.4 Slave Wraparound Mode ............................................................. 6-21

6.3.6 Peripheral Chip Selects ........................................................................6-21

6.4 Serial Communication Interface ...................................................................6-22

6.4.1 SCI Registers .......................................................................................6-22

6.4.1.1 Control Registers ......................................................................... 6-22

6.4.1.2 Status Register ............................................................................. 6-25

6.4.1.3 Data Register ............................................................................... 6-25

6.4.2 SCI Pins ...............................................................................................6-25

6.4.3 SCI Operation .......................................................................................6-25

6.4.3.1 Definition of Terms .......................................................................6-26

6.4.3.2 Serial Formats .............................................................................. 6-26

6.4.3.3 Baud Clock ................................................................................... 6-26

6.4.3.4 Parity Checking ............................................................................ 6-27

6.4.3.5 Transmitter Operation .................................................................. 6-27

6.4.3.6 Receiver Operation ...................................................................... 6-29

6.4.3.7 Idle-Line Detection ....................................................................... 6-29

6.4.3.8 Receiver Wakeup ......................................................................... 6-30

6.4.3.9 Internal Loop ................................................................................ 6-31

6.5 QSM Initialization .........................................................................................6-31

SECTION 7GENERAL-PURPOSE TIMER

7.1 General ...........................................................................................................7-1

7.2 GPT Registers and Address Map ...................................................................7-2

7.3 Special Modes of Operation ...........................................................................7-3

MOTOROLA MC68331

viii USER’S MANUAL

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

7.3.1 Low-Power Stop Mode ...........................................................................7-3

7.3.2 Freeze Mode ..........................................................................................7-3

7.3.3 Single-Step Mode ...................................................................................7-3

7.3.4 Test Mode ..............................................................................................7-4

7.4 Polled and Interrupt-Driven Operation ............................................................7-4

7.4.1 Polled Operation .....................................................................................7-4

7.4.2 GPT Interrupts ........................................................................................7-5

7.5 Pin Descriptions .............................................................................................7-6

7.5.1 Input Capture Pins (IC[1:3]) ....................................................................7-6

7.5.2 Input Capture/Output Compare Pin (IC4/OC5) ......................................7-6

7.5.3 Output Compare Pins (OC[1:4]) .............................................................7-6

7.5.4 Pulse Accumulator Input Pin (PAI) .........................................................7-7

7.5.5 Pulse-Width Modulation (PWMA, PWMB) ..............................................7-7

7.5.6 Auxiliary Timer Clock Input (PCLK) ........................................................7-7

7.6 General-Purpose I/O ......................................................................................7-7

7.7 Prescaler ........................................................................................................7-8

7.8 Capture/Compare Unit ...................................................................................7-9

7.8.1 Timer Counter ......................................................................................7-11

7.8.2 Input Capture Functions .......................................................................7-11

7.8.3 Output Compare Functions ..................................................................7-12

7.8.3.1 Output Compare 1 ........................................................................ 7-13

7.8.3.2 Forced Output Compare .............................................................. 7-13

7.9 Input Capture 4/Output Compare 5 ..............................................................7-13

7.10 Pulse Accumulator .......................................................................................7-14

7.11 Pulse-Width Modulation Unit ........................................................................7-15

7.11.1 PWM Counter .......................................................................................7-16

7.11.2 PWM Function ......................................................................................7-17

APPENDIX A ELECTRICAL CHARACTERISTICS

APPENDIX B MECHANICAL DATA AND ORDERING INFORMATION

APPENDIX CDEVELOPMENT SUPPORT

C.1 M68MMDS1632 Modular Development System ...................................... C-1

C.2 M68MEVB1632 Modular Evaluation Board .............................................. C-2

APPENDIX D REGISTER SUMMARY

D.1 Central Processing Unit ............................................................................ D-1

D.1.1 CPU32 Register Model ..................................................................... D-2

D.1.2 — Status Register ............................................................................ D-3

MC68331 MOTOROLA

USER’S MANUAL ix

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

D.2 General-Purpose Timer ............................................................................ D-4

D.2.1 GPTMCR — GPT Module Configuration Register............................ D-4

D.2.2 GPTMTR — GPT Module Test Register (Reserved)........................ D-5

D.2.3 ICR — GPT Interrupt Configuration Register.................................... D-5

D.2.4 DDRGP — Port GP Data Direction Register.....................................D-6

D.2.5 OC1M— OC1 Action Mask Register................................................. D-6

D.2.6 TCNT — Timer Counter Register .....................................................D-6

D.2.7 PACTL — Pulse Accumulator Control Register................................ D-7

D.2.8 TIC[1:3] — Input Capture Registers 1–3 .......................................... D-8

D.2.9 TOC[1:4] — Output Compare Registers 1–4 ...................................D-8

D.2.10 TI4/O5 — Input Capture 4/Output Compare 5 Register.................... D-8

D.2.11 TCTL1/TCTL2 — Timer Control Registers 1 and 2...........................D-8

D.2.12 TMSK1/TMSK2 — Timer Interrupt Mask Registers 1 and 2 .............D-9

D.2.13 TFLG1/TFLG2 — Timer Interrupt Flag Registers 1 and 2.............. D-10

D.2.14 CFORC — Compare Force Register............................................... D-10

D.2.15 PWMA/PWMB — PWM Registers A/B ........................................... D-12

D.2.16 PWMCNT — PWM Count Register ...............................................D-12

D.2.17 PWMBUFA — PWM Buffer Register A .......................................... D-12

D.2.18 PRESCL — GPT Prescaler ............................................................D-12

D.3 System Integration Module ..................................................................... D-13

D.3.1 SIMCR — Module Configuration Register ...................................... D-14

D.3.2 SIMTR — System Integration Test Register................................... D-15

D.3.3 SYNCR — Clock Synthesizer Control Register .............................D-15

D.3.4 RSR — Reset Status Register ....................................................... D-16

D.3.5 SIMTRE — System Integration Test Register (ECLK).................... D-17

D.3.6 PORTE0/PORTE1 — Port E Data Register.................................... D-17

D.3.7 DDRE — Port E Data Direction Register ........................................D-17

D.3.8 PEPAR — Port E Pin Assignment Register.................................... D-17

D.3.9 PORTF0/PORTF1 — Port F Data Register..................................... D-18

D.3.10 DDRF — Port F Data Direction Register.........................................D-18

D.3.11 PFPAR — Port F Pin Assignment Register..................................... D-18

D.3.12 SYPCR — System Protection Control Register.............................. D-19

D.3.13 PICR — Periodic Interrupt Control Register....................................D-20

D.3.14 PITR — Periodic Interrupt Timer Register ...................................... D-20

D.3.15 SWSR — Software Service Register ..............................................D-21

D.3.16 TSTMSRA — Master Shift Register A............................................. D-21

D.3.17 TSTMSRB — Master Shift Register B............................................. D-21

D.3.18 TSTSC — Test Module Shift Count ................................................D-21

D.3.19 TSTRC — Test Module Repetition Count....................................... D-21

D.3.20 CREG — Test Submodule Control Register .................................. D-21

D.3.21 DREG — Distributed Register.........................................................D-21

MOTOROLA MC68331

x USER’S MANUAL

TABLE OF CONTENTS

(Continued)

Paragraph Title Page

D.3.22 PORTC — Port C Data Register..................................................... D-21

D.3.23 CSPAR0 — Chip Select Pin Assignment Register 0....................... D-21

D.3.24 CSPAR1 — Chip Select Pin Assignment Register 1....................... D-22

D.3.25 CSBARBT — Chip Select Base Address Register Boot ROM .......D-23

D.3.26 CSORBT — Chip Select Option Register Boot ROM...................... D-23

D.4 Queued Serial Module ............................................................................ D-25

D.4.1 QSMCR — QSM Configuration Register ........................................D-25

D.4.2 QTEST — QSM Test Register........................................................ D-26

D.4.3 QILR — QSM Interrupt Level Register............................................D-26

D.4.4 SCCR0 — SCI Control Register 0 .................................................. D-27

D.4.5 SCCR1 — SCI Control Register 1................................................... D-27

D.4.6 SCSR — SCI Status Register......................................................... D-29

D.4.7 SCDR — SCI Data Register............................................................ D-30

D.4.8 PORTQS — Port QS Data Register ...............................................D-30

D.4.9 PQSPAR — PORT QS Pin Assignment Register........................... D-30

D.4.10 SPCR0 — QSPI Control Register 0................................................ D-32

D.4.11 SPCR1 — QSPI Control Register 1 ............................................... D-33

D.4.12 SPCR2 — QSPI Control Register 2 ............................................... D-34

D.4.13 SPCR3 — QSPI Control Register 3 ............................................... D-34

D.4.14 RR[0:F] — Receive Data RAM........................................................D-35

D.4.15 TR[0:F] — Transmit Data RAM ...................................................... D-35

D.4.16 CR[0:F] — Command RAM.............................................................D-36

MC68331 MOTOROLA

USER’S MANUAL xi

Figure Title Page

3-1 MCU Block Diagram........................................................................................ 3-3

3-2 Pin Assignments for 132-Pin Package............................................................ 3-4

3-3 Pin Assignments for 144-Pin Package............................................................ 3-5

3-4 Internal Register Memory Map...................................................................... 3-11

3-5 Overall Memory Map..................................................................................... 3-12

3-6 Separate Supervisor and User Space Map................................................... 3-13

3-7 Supervisor Space (Separate Program/Data Space) Map............................. 3-14

3-8 User Space (Separate Program/Data Space) Map....................................... 3-15

4-1 System Integration Module Block Diagram.....................................................4-2

4-2 System Configuration and Protection.............................................................. 4-3

4-3 Periodic Interrupt Timer and Software Watchdog Timer.................................4-7

4-4 System Clock Block Diagram.......................................................................... 4-9

4-5 System Clock Oscillator Circuit.....................................................................4-10

4-6 System Clock Filter Networks....................................................................... 4-11

4-7 MCU Basic System....................................................................................... 4-17

4-8 Operand Byte Order...................................................................................... 4-21

4-9 Word Read Cycle Flowchart..........................................................................4-24

4-10 Write Cycle Flowchart................................................................................... 4-25

4-11 CPU Space Address Encoding..................................................................... 4-27

4-12 Breakpoint Operation Flowchart.................................................................... 4-29

4-13 LPSTOP Interrupt Mask Level.......................................................................4-30

4-14 Bus Arbitration Flowchart for Single Request................................................4-35

4-15 Data Bus Mode Select Conditioning..............................................................4-39

4-16 Power-On Reset............................................................................................ 4-44

4-17 Basic MCU System....................................................................................... 4-49

4-18 Chip-Select Circuit Block Diagram................................................................4-50

4-19 CPU Space Encoding for Interrupt Acknowledge..........................................4-55

5-1 CPU32 Block Diagram.................................................................................... 5-2

5-2 User Programming Model............................................................................... 5-3

5-3 Supervisor Programming Model Supplement..................................................5-3

5-4 Data Organization in Data Registers............................................................... 5-5

5-5 Address Organization in Address Registers....................................................5-5

5-6 Memory Operand Addressing......................................................................... 5-8

5-7 Common In-Circuit Emulator Diagram.......................................................... 5-18

5-8 Bus State Analyzer Configuration................................................................. 5-19

5-9 Debug Serial I/O Block Diagram................................................................... 5-23

5-10 BDM Serial Data Word.................................................................................. 5-24

5-11 BDM Connector Pinout..................................................................................5-24

5-12 Loop Mode Instruction Sequence..................................................................5-25

6-1 QSM Block Diagram........................................................................................ 6-1

6-2 QSPI Block Diagram....................................................................................... 6-6

LIST OF ILLUSTRATIONS

MOTOROLA MC68331

xii USER’S MANUAL

(Continued)

Figure Title Page

LIST OF ILLUSTRATIONS

6-3 QSPI RAM....................................................................................................... 6-7

6-4 Flowchart of QSPI Initialization Operation.....................................................6-11

6-5 Flowchart of QSPI Master Operation (Part 1)............................................... 6-12

6-5 Flowchart of QSPI Master Operation (Part 2)............................................... 6-13

6-5 Flowchart of QSPI Master Operation (Part 3)............................................... 6-14

6-6 Flowchart of QSPI Slave Operation (Part 1)................................................. 6-15

6-6 Flowchart of QSPI Slave Operation (Part 2)................................................. 6-16

6-7 SCI Transmitter Block Diagram..................................................................... 6-23

6-8 SCI Receiver Block Diagram......................................................................... 6-24

7-1 GPT Block Diagram.........................................................................................7-2

7-2 Prescaler Block Diagram................................................................................. 7-9

7-3 Capture/Compare Unit Block Diagram.......................................................... 7-10

7-4 Input Capture Timing Example...................................................................... 7-12

7-5 Pulse Accumulator Block Diagram................................................................ 7-15

7-6 PWM Block Diagram.....................................................................................7-16

A-1 CLKOUT Output Timing Diagram..................................................................A-12

A-2 External Clock Input Timing Diagram............................................................A-12

A-3 ECLK Output Timing Diagram.......................................................................A-12

A-4 Read Cycle Timing Diagram .........................................................................A-13

A-5 Write Cycle Timing Diagram..........................................................................A-14

A-6 Fast Termination Read Cycle Timing Diagram .............................................A-15

A-7 Fast Termination Write Cycle Timing Diagram..............................................A-16

A-8 Bus Arbitration Timing Diagram — Active Bus Case ....................................A-17

A-9 Bus Arbitration Timing Diagram — Idle Bus Case ........................................A-18

A-10 Show Cycle Timing Diagram.........................................................................A-18

A-11 Chip Select Timing Diagram..........................................................................A-19

A-12 Reset and Mode Select Timing Diagram.......................................................A-19

A-13 Background Debugging Mode Timing Diagram—Serial Communication......A-21

A-14 Background Debugging Mode Timing Diagram —Freeze Assertion.............A-21

A-15 ECLK Timing Diagram...................................................................................A-23

A-16 QSPI Timing — Master, CPHA = 0 ...............................................................A-25

A-17 QSPI Timing — Master, CPHA = 1 ...............................................................A-25

A-18 QSPI Timing — Slave, CPHA = 0 .................................................................A-26

A-19 QSPI Timing — Slave, CPHA = 1 .................................................................A-26

B-1 132-Pin Plastic Surface Mount Package Pin Assignments.............................B-2

B-2 144-Pin Plastic Surface Mount Package Pin Assignments.............................B-3

D-1 User Programming Model...............................................................................D-2

D-2 Supervisor Programming Model Supplement..................................................D-2

MC68331 MOTOROLA

USER’S MANUAL xiii

Table Title Page

3-1 MCU Driver Types .......................................................................................... 3-6

3-2 MCU Pin Characteristics ................................................................................3-6

3-3 MCU Power Connections ............................................................................... 3-7

3-4 Signal Characteristics .....................................................................................3-7

3-5 Signal Function ...............................................................................................3-8

3-6 SIM Reset Mode Selection ........................................................................... 3-16

3-7 Module Pin Functions ................................................................................... 3-17

4-1 Show Cycle Enable Bits ................................................................................. 4-4

4-2 Bus Monitor Period ......................................................................................... 4-5

4-3 MODCLK Pin and SWP Bit During Reset ...................................................... 4-6

4-4 Software Watchdog Ratio ...............................................................................4-6

4-5 MODCLK Pin and PTP Bit at Reset ............................................................... 4-7

4-6 Periodic Interrupt Priority ................................................................................ 4-8

4-7 Clock Control Multipliers ...............................................................................4-12

4-8 System Frequencies from 32.768-kHz Reference ....................................... 4-14

4-9 Clock Control ................................................................................................ 4-16

4-10 Size Signal Encoding ................................................................................... 4-19

4-11 Address Space Encoding ............................................................................. 4-19

4-12 Effect of DSACK Signals .............................................................................. 4-20

4-13 Operand Transfer Cases .............................................................................. 4-22

4-14 DSACK, BERR, and HALT Assertion Results .............................................4-31

4-15 Reset Source Summary ...............................................................................4-37

4-16 Reset Mode Selection .................................................................................. 4-38

4-17 Module Pin Functions ................................................................................... 4-41

4-18 SIM Pin Reset States ................................................................................... 4-42

4-19 Chip-Select Pin Functions ............................................................................ 4-51

4-20 Pin Assignment Field Encoding ....................................................................4-51

4-21 Block Size Encoding .....................................................................................4-52

4-22 Option Register Function Summary .............................................................4-53

4-23 Chip Select Base and Option Register Reset Values .................................. 4-56

4-24 CSBOOT Base and Option Register Reset Values .....................................4-57

5-1 Instruction Set Summary .............................................................................. 5-11

5-2 Exception Vector Assignments .....................................................................5-16

5-3 BDM Source Summary .................................................................................5-19

5-4 Polling the BDM Entry Source ...................................................................... 5-20

5-5 Background Mode Command Summary ......................................................5-21

5-6 CPU Generated Message Encoding ............................................................ 5-24

6-1 QSM Pin Function .......................................................................................... 6-4

6-2 QSPI Pin Function .......................................................................................... 6-9

6-3 BITS Encoding ............................................................................................. 6-18

6-4 SCI Pin Function .......................................................................................... 6-25

LIST OF TABLES

MOTOROLA MC68331

xiv USER’S MANUAL

(Continued)

Table Title Page

LIST OF TABLES

6-5 Serial Frame Formats ...................................................................................6-26

6-6 Effect of Parity Checking on Data Size .........................................................6-27

7-1 GPT Status Flags ............................................................................................7-4

7-2 GPT Interrupt Sources ....................................................................................7-5

7-3 PWM Frequency Ranges Using 16.78-MHz/20.97-MHz System Clocks ......7-17

A-1 Maximum Ratings ..........................................................................................A-1

A-2 Typical Ratings, 16.78 MHz Operation ..........................................................A-2

A-2 Typical Ratings, 20.97 MHz Operation .........................................................A-2

A-3 Thermal Characteristics .................................................................................A-3

A-4 16.78 MHz Clock Control Timing ...................................................................A-3

A-4 20.97 MHz Clock Control Timing ...................................................................A-4

A-5 16.78 MHz DC Characteristics .......................................................................A-5

A-5 20.97 MHz DC Characteristics .......................................................................A-6

A-6 16.78 MHz AC Timing .................................................................................... A-8

A-6 20.97 MHz AC Timing .................................................................................... A-9

A-7 Background Debugging Mode Timing .......................................................... A-20

A-8 16.78 MHz ECLK Bus Timing ......................................................................A-22

A-8 20.97 MHz ECLK Bus Timing ......................................................................A-22

A-9 QSPI Timing .................................................................................................A-24

B-1 MCU Ordering Information ............................................................................. B-4

B-2 Quantity Order Suffix ......................................................................................B-4

C-1 MC68331 Development Tools ........................................................................C-1

D-1 Module Address Map .....................................................................................D-1

D-2 GPT Address Map ..........................................................................................D-4

D-3 SIM Address Map .........................................................................................D-13

D-4 Port E Pin Assignments ...............................................................................D-18

D-5 Port F Pin Assignments ................................................................................D-19

D-6 Software Watchdog Ratio ............................................................................D-19

D-7 Bus Monitor Period .......................................................................................D-20

D-8 CSPAR0 Pin Assignments ...........................................................................D-22

D-9 CSPAR1 Pin Assignments ...........................................................................D-22

D-10 CSPAR0 and CSPAR1 Pin Assignment Field Encoding ..............................D-22

D-11 Block Size Encoding ....................................................................................D-23

D-12 Option Register Function Summary .............................................................D-24

D-13 QSM Address Map .......................................................................................D-25

D-14 PQSPAR Pin Assignments ..........................................................................D-31

D-15 Effect of DDRQS on PORTQS Pins .............................................................D-31

D-16 Effect of DDRQS on QSM Pin Function .......................................................D-32

D-17 MC68331 Module Address Map ...................................................................D-37

D-18 Register Bit and Field Mnemonics ...............................................................D-40

MC68331

INTRODUCTION

MOTOROLA

USER’S MANUAL 1-1

1

SECTION 1INTRODUCTION

The MC68331, a highly-integrated 32-bit microcontroller, combines high-performance

data manipulation capabilities with powerful peripheral subsystems. The MCU is built

up from standard modules that interface through a common intermodule bus (IMB).

Standardization facilitates rapid development of devices tailored for specific applications.

The MCU incorporates a 32-bit CPU (CPU32), a system integration module (SIM), a

general-purpose timer (GPT), and a queued serial module (QSM).

The MCU can either synthesize an internal clock signal from an external reference or

use an external clock input directly. Operation with a 32.768-kHz reference frequency

is standard. Because MCU operation is fully static, register and memory contents are

not affected by a loss of clock.

High-density complementary metal-oxide semiconductor (HCMOS) architecture

makes the basic power consumption of the MCU low. Power consumption can be minimized by stopping the system clock. The CPU32 instruction set includes a low-power

stop (LPSTOP) command that efficiently implements this capability.

Documentation for the Modular Microcontroller Family follows the modular construction of the devices in the product line. Each microcontroller has a comprehensive user's manual that provides sufficient information for normal operation of the device. The

user's manual is supplemented by module reference manuals that provide detailed information about module operation and applications. Refer to Motorola publication

Ad-

vanced Microcontroller Unit (AMCU) Literature

(BR1116/D) for a complete listing of

documentation.

MOTOROLA

INTRODUCTION

MC68331

1-2 USER’S MANUAL

1

MC68331

NOMENCLATURE

MOTOROLA

USER’S MANUAL 2-1

2

SECTION 2NOMENCLATURE

The following nomenclature is used throughout the manual. Nomenclature used only

in certain sections, such as register bit mnemonics, is defined in those sections.

2.1 Symbols and Operators

+

— Addition

−

— Subtraction or negation (two's complement)

∗

— Multiplication

/

— Division

>

— Greater

<

— Less

=

— Equal

≥

— Equal or greater

≤

— Equal or less

≠

— Not equal

• — AND

✛

— Inclusive OR (OR)

⊕

— Exclusive OR (EOR)

NOT

— Complementation

:

— Concatenation

⇒

— Transferred

⇔

— Exchanged

±

— Sign bit; also used to show tolerance

« — Sign extension

% — Binary value

$ — Hexadecimal value

MOTOROLA

NOMENCLATURE

MC68331

2-2 USER’S MANUAL

2

2.2 CPU32 Registers

A6–A0 — Address registers (index registers)

A7 (SSP) — Supervisor Stack Pointer

A7 (USP) — User Stack Pointer

CCR — Condition code register (user portion of SR)

D7–D0 — Data Registers (index registers)

DFC — Alternate function code register

PC — Program counter

SFC — Alternate function code register

SR — Status register

VBR — Vector base register

X — Extend indicator

N — Negative indicator

Z — Zero indicator

V — Two's complement overflow indicator

C — Carry/borrow indicator

MC68331

NOMENCLATURE

MOTOROLA

USER’S MANUAL 2-3

2

2.3 Pin and Signal Mnemonics

ADDR[23:0] — Address Bus

AS

— Address Strobe

AVEC

— Autovector

BERR

— Bus Error

BG

— Bus Grant

BGACK

— Bus Grant Acknowledge

BKPT

— Breakpoint

BR

— Bus Request

CLKOUT — System Clock

CS[10:0]

— Chip Selects

CSBOOT

— Boot ROM Chip Select

DATA[15:0] — Data Bus

DS

— Data Strobe

DSACK[1:0]

— Data and Size Acknowledge

DSCLK — Development Serial Clock

DSI — Development Serial Input

DSO — Development Serial Output

EXTAL — External Crystal Oscillator Connection

FC[2:0] — Function Codes

FREEZE — Freeze

HALT

— Halt

IC[4:1] — Input Capture

IFETCH

— Instruction Fetch

IPIPE

— Instruction Pipeline

IRQ[7:1]

— Interrupt Request

MISO — Master In Slave Out

MODCLK — Clock Mode Select

MOSI — Master Out Slave In

OC[5:1] — Output Compare

PAI — Pulse Accumulator Input

PC[6:0] — SIM I/O Port C

PCLK — Pulse Accumulator Clock

PCS[3:0] — Peripheral Chip Selects

PE[7:0] — SIM I/O Port E

PF[7:0] — SIM I/O Port F

PGP[7:0] — GPT I/O Port

PQS[7:0] — QSM I/O Port

PWMA, PWMB — Pulse Width Modulator Output

QUOT — Quotient Out

MOTOROLA

NOMENCLATURE

MC68331

2-4 USER’S MANUAL

2

R/W — Read/Write

RESET

— Reset

RMC

— Read-Modify-Write Cycle

RXD — SCI Receive Data

SCK — QSPI Serial Clock

SIZ[1:0] — Size

SS

— Slave Select

TSC — Three-State Control

TXD — SCI Transmit Data

XFC — External Filter Capacitor

XTAL — External Crystal Oscillator Connection

MC68331

NOMENCLATURE

MOTOROLA

USER’S MANUAL 2-5

2

2.4 Register Mnemonics

CFORC — GPT Compare Force Register

CREG — Test Control Register C

CR[0:F] — QSM Command RAM

CSBARBT — Chip-Select Base Address Register Boot ROM

CSBAR[0:10] — Chip-Select Base Address Registers [0:10]

CSORBT — Chip-Select Option Register Boot ROM

CSOR[0:10] — Chip-Select Option Register [0:10]

CSPAR[0:1] — Chip-Select Pin Assignment Registers [0:1]

DDRE — Port E Data Direction Register

DDRF — Port F Data Direction Register

DDRGP — Port GP Data Direction Register

DDRQS — Port QS Data Direction Register

DREG — SIM Test Module Distributed Register

GPTMCR — GPT Module Configuration Register

ICR — GPT Interrupt Configuration Register

OC1D — Output Compare 1 Action Data Register

OC1M — Output Compare 1 Action Mask Register

PACNT — Pulse Accumulator Counter

PACTL — Pulse Accumulator Control Register

PEPAR — Port E Pin Assignment Register

PFPAR — Port F Pin Assignment Register

PICR — Periodic Interrupt Control Register

PITR — Periodic Interrupt Timer Register

PORTC — Port C Data Register

PORTE — Port E Data Register

PORTF — Port F Data Register

PORTGP — Port GP Data Register

PORTQS — Port QS Data Register

PQSPAR — Port QS Pin Assignment Register

PRESCL — GPT Prescaler Register

PWMA — PWM Control Register A

PWMB — PWM Control Register B

PWMBUFA — PWM Buffer Register A

PWMBUFB — PWM Buffer Register B

PWMC — PWM Control Register C

PWMCNT — PWM Counter

QILR — QSM Interrupt Level Register

QIVR — QSM Interrupt Vector Register

QSMCR — QSM Configuration Register

MOTOROLA

NOMENCLATURE

MC68331

2-6 USER’S MANUAL

2

2.5 Conventions

Logic level one is the voltage that corresponds to a Boolean true (1) state.

Logic level zero is the voltage that corresponds to a Boolean false (0) state.

Set refers specifically to establishing logic level one on a bit or bits.

Clear refers specifically to establishing logic level zero on a bit or bits.

Asserted means that a signal is in active logic state. An active low signal changes

from logic level one to logic level zero when asserted, and an active high signal changes from logic level zero to logic level one.

Negated means that an asserted signal changes logic state. An active low signal

changes from logic level zero to logic level one when negated, and an active high signal changes from logic level one to logic level zero.

QTEST — QSM Test Register

RR[0:F] — QSM Receive Data RAM

RSR — Reset Status Register

SCCR[0:1] — SCI Control Registers [0:1]

SCDR — SCI Data Register

SCSR — SCI Status Register

SIMCR — SIM Module Configuration Register

SIMTR — System Integration Test Register

SIMTRE — System Integration Test Register (ECLK)

SPCR[0:3] — QSPI Control Registers [0:3]

SPSR — QSPI Status Register

SWSR — Software Watchdog Service Register

SYNCR — Clock Synthesizer Control Register

SYPCR — System Protection Control Register

TCNT — Timer Counter Register

TCTL[1:2] — Timer Control Registers [1:2]

TFLG[1:2] — Timer Interrupt Flag Registers [1:2]

TI4/O5 — Timer Input Capture 4/Output Compare 5 Register

TIC[1:3] — Timer Input Capture Registers [1:3]

TMSK[1:2] — Timer Interrupt Mask Register [1:2]

TOC[1:4] — Timer Output Compare Registers [1:4]

TR[0:F] — QSM Transmit Data RAM

TSTMSRA — Test Module Master Shift Register A

TSTMSRB — Test Module Master Shift Register B

TSTRC — Test Module Repetition Count Register

TSTSC — Test Module Shift Count Register

MC68331 NOMENCLATURE MOTOROLA

USER’S MANUAL 2-7

2

A specific mnemonic within a range is referred to by mnemonic and number. A15 is

bit 15 of accumulator A; ADDR7 is line 7 of the address bus; CSOR0 is chip-select option register 0. A range of mnemonics is referred to by mnemonic and the numbers

that define the range. AM[35:30] are bits 35 to 30 of accumulator M; CSOR[0:5] are

the first six option registers.

Parentheses are used to indicate the content of a register or memory location, rather

than the register or memory location itself. (A) is the content of accumulator A. (M : M

+ 1) is the content of the word at address M.

LSB means least significant bit or bits. MSB means most significant bit or bits. Refer-

ences to low and high bytes are spelled out.

LSW means least significant word or words. MSW means most significant word or

words.

ADDR is the address bus. ADDR[7:0] are the eight LSB of the address bus.

DATA is the data bus. DATA[15:8] are the eight MSB of the data bus.

MOTOROLA NOMENCLATURE MC68331

2-8 USER’S MANUAL

2

MC68331 OVERVIEW MOTOROLA

USER’S MANUAL 3-1

3

SECTION 3OVERVIEW

This section contains information about the entire modular microcontroller. It lists the

features of each module, shows device functional divisions and pin assignments, summarizes signal and pin functions, discusses the intermodule bus, and provides system

memory maps. Timing and electrical specifications for the entire microcontroller and

for individual modules are provided in APPENDIX A ELECTRICAL CHARACTERIS-

TICS. Comprehensive module register descriptions and memory maps are provided

in APPENDIX D REGISTER SUMMARY.

3.1 MCU Features

The following paragraphs highlight capabilities of each of the microcontroller modules.

Each module is discussed separately in a subsequent section of this user's manual.

3.1.1 System Integration Module (SIM)

• External Bus Support

• Programmable Chip-Select Outputs

• System Protection Logic

• Watchdog Timer, Clock Monitor, and Bus Monitor

• System Protection Logic

• PLL System Clock for Low Power Operation

• Background Debugging Mode

3.1.2 Central Processing Unit (CPU32)

• Instruction Set Supports Controller Applications

• 32-Bit Architecture

• Virtual Memory Implementation

• Loop Mode of Instruction Execution

• Table Lookup and Interpolate Instruction

• Improved Exception Handling for Controller Applications

• Trace on Change of Flow

• Hardware Breakpoint Signal, Background Mode

• Fully Static Operation

3.1.3 Queued Serial Module (QSM)

• Serial Communication Interface (SCI), Enhanced Universal Asynchronous Receiver Transmitter (UART) with Modulus Baud Rate, Parity

• Queued Serial Peripheral Interface (SPI), High Speed Bidirectional Interface, 80Byte RAM, Up to 16 Automatic Transfers

• Dual Function I/O Ports

• Continuous Cycling, 8 to 16 Bits per Transfer

MOTOROLA OVERVIEW MC68331

3-2 USER’S MANUAL

3

3.1.4 General-Purpose Timer (GPT)

• Two 16-Bit Free-Running Counters With One Nine-Stage Prescaler

• Three Input Capture Channels

• Four Output Compare Channels

• One Input Capture/Output Compare Channel

• One Pulse Accumulator/Event Counter Input

• Two Pulse-Width Modulation Outputs

• Optional External Clock Input

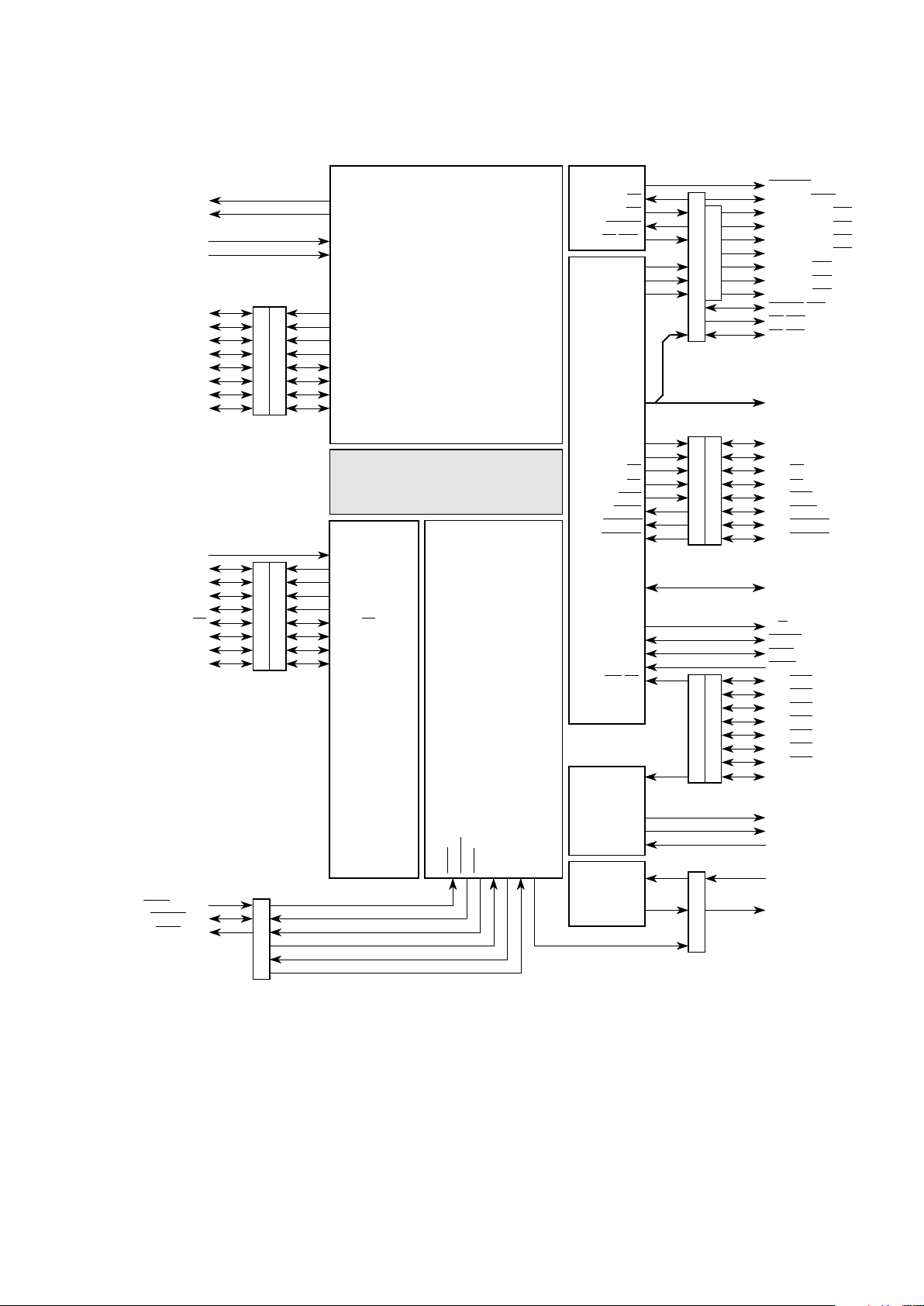

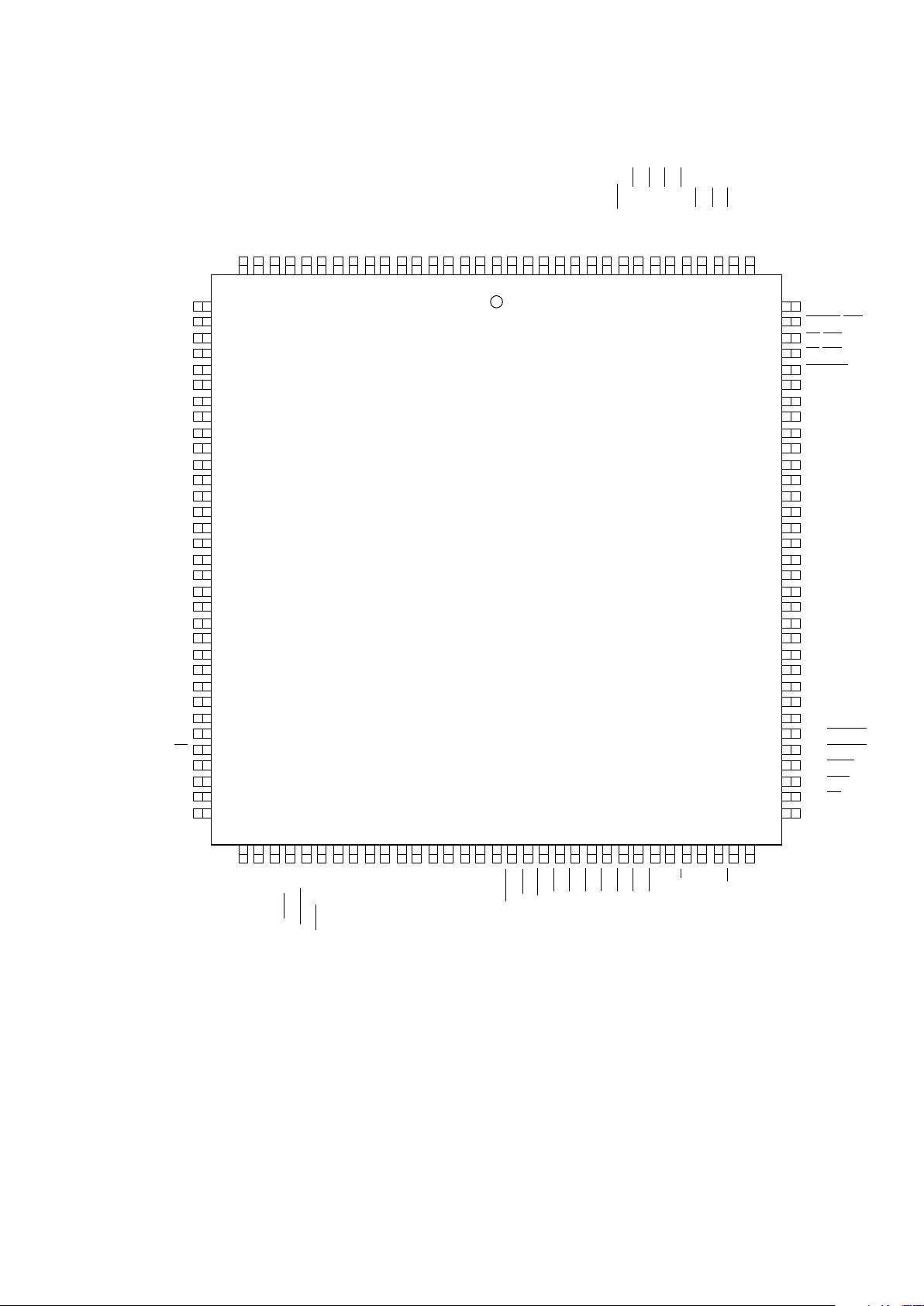

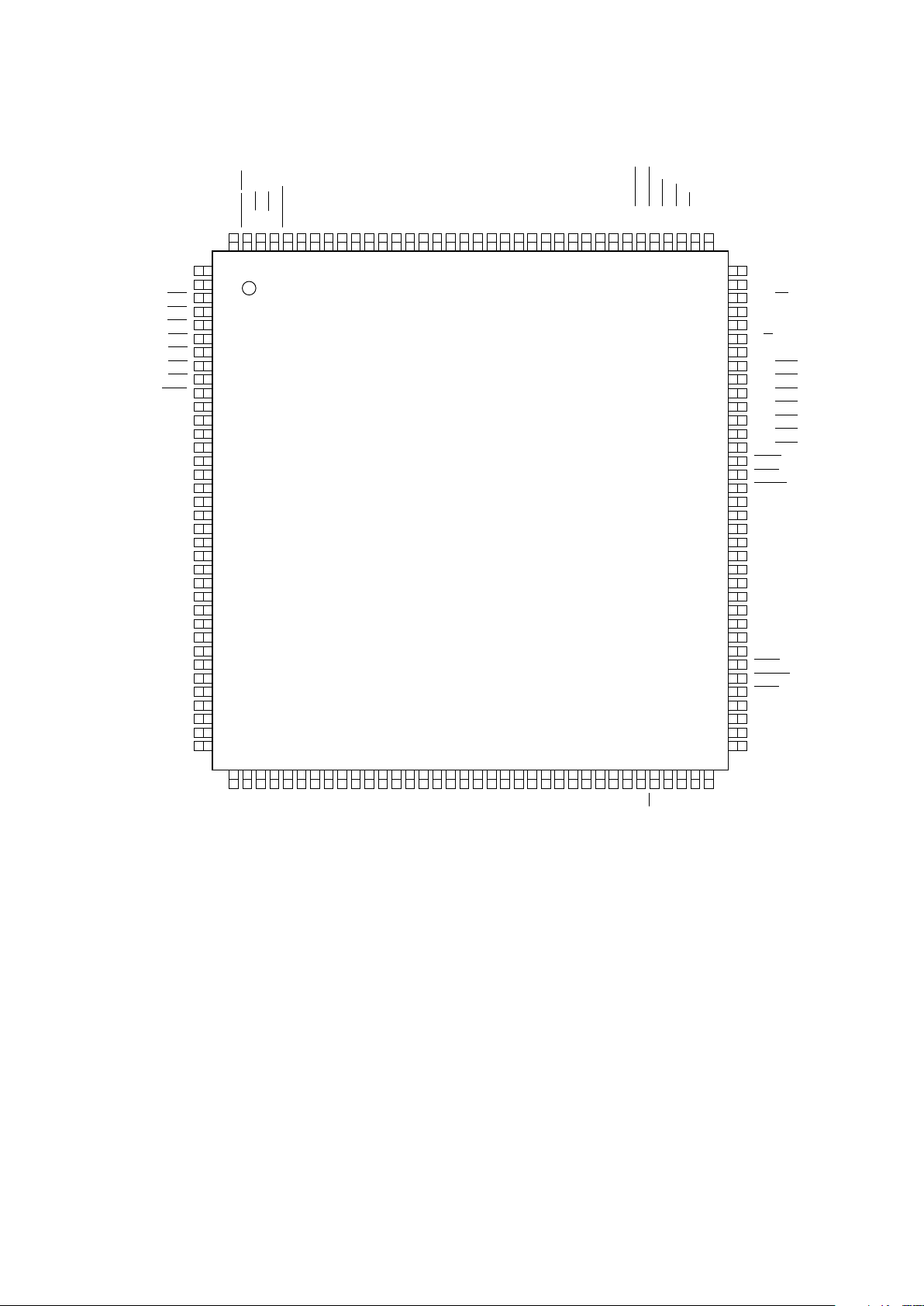

3.2 System Block Diagram and Pin Assignment Diagrams

Figure 3-1 is a functional diagram of the MCU. Although diagram blocks represent the

relative size of the physical modules, there is not a one-to-one correspondence between location and size of blocks in the diagram and location and size of integratedcircuit modules. Figure 3-2 shows the pin assignments of the 132-pin plastic surfacemount package. Figure 3-3 shows the pin assignments of the 144-pin plastic surfacemount package. Refer to APPENDIX B MECHANICAL DATA AND ORDERING IN-

FORMATION for package dimensions. All pin functions and signal names are shown

in this drawing. Refer to subsequent paragraphs in this section for pin and signal descriptions.

MC68331 OVERVIEW MOTOROLA

USER’S MANUAL 3-3

3

Figure 3-1 MCU Block Diagram

331 BLOCK

PQS5/PCS2

PQS7/TXD

PQS4/PCS1

PQS6/PCS3

CPU32

QSM

IMB

GPT

PQS0/MISO

PQS1/MOSI

PQS2/SCK

PORT QS

TXD

PCS2

SCK

MISO

MOSI

CONTROL

PCS1

PQS3/PCS0/SS PCS0/SS

RXD

PCS3

BKPT/DSCLK

IFETCH

/DSI

IPIPE/DSO

DSI

DSO

IPIPE

IFETCH

BKPT

IRQ[7:1]

ADDR[23:0]

CONTROL

PORT F PORT C

FC2

FC1

FC0

BG

BR

BGACK

MODCLK

ADDR[23:19]

CLOCK

EBI

CS

[10:0]

BR/CS0

BG/CS1

BGACK/CS2

R/W

RESET

HALT

BERR

CLKOUT

XTAL

EXTAL

CHIP

SELECTS

CSBOOT

ADDR[18:0]

DATA[15:0]DATA[15:0]

QUOT

TEST

FREEZE/QUOT

TSC

CONTROL

TSC

PC0/FC0/CS3

PC1/FC1/CS4

PC2/FC2/CS5

PC3/ADDR19/CS6

PC4/ADDR20/CS7

PC5/ADDR21/CS8

PC6/ADDR22/CS9

ADDR23/CS10

PF7/IRQ7

PF6/IRQ6

PF5/IRQ5

PF4/IRQ4

PF3/IRQ3

PF2/IRQ2

PF1/IRQ1

PF0/MODCLK

CONTROL

PORT E

SIZ1 PE7/SIZ1

SIZ0 PE6/SIZ0

DSACK0 PE0/DSACK0

DSACK1 PE1/DSACK1

AVEC PE2/AVEC

PE3/RMC

DS PE5/DS

RMC

PE4/AS

PWMA PWMA

CONTROL

AS

CONTROL

DSCLK

FREEZE

PORT GP

PGP7/IC4/OC5/OC1

PGP5/OC3/OC1

PGP2/IC3

PGP0/IC1

PGP1/IC2

CONTROL

PGP4/OC2/OC1

PGP3/OC1

PWMB

PGP6/OC4/OC1

PCLK

PAI

PWMB

PCLK

PAI

PGP7/IC4/OC5/OC1

PGP5/OC3/OC1

PGP2/IC3

PGP0/IC1

PGP1/IC2

PGP4/OC2/OC1

PGP3/OC1

PGP6/OC4/OC1

MOTOROLA OVERVIEW MC68331

3-4 USER’S MANUAL

3

Figure 3-2 Pin Assignments for 132-Pin Package

331 132-PIN QFP

MC68331

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

DATA9

DATA10

DATA11

DATA12

DATA13

DATA14

DATA15

ADDR0

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

ADDR9

ADDR10

ADDR11

ADDR12

ADDR13

ADDR14

ADDR15

ADDR16

ADDR17

ADDR18

PQS0/MISO

PQS1/MOSI

PQS2/SCK

PQS3/PCS0/SS

PQS4/PCS1

PQS5/PCS2

PQS6/PCS3

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7

DATA8

V

DD

V

SS

V

DD

PE1/DSACK1

PE0/DSACK0

PE2/AVEC

PE3/RMC

PE5/DS

CSBOOT

BGACK/CS2

BG/CS1

BR/CS0

51

17

117

16151413121110

9876543

131

130

129

128

127

126

125

124

123

122

121

120

119

118

52535455565758596061626364656667686970717273747576777879808182

83

PQS7/TXD

RXD

IPIPE/DSO

FREEZE/QUOT

XTAL

EXTAL

XFC

CLKOUT

PF0/MODCLK

PE7/SIZ1

PE6/SIZ0

NC

PGP0/IC1

PGP1/IC2

PGP2/IC3

PGP3/OC1

PGP4/OC2/OC1

PGP5/OC3/OC1NCPGP6/OC4/OC1

PGP7/IC4/OC5/OC1

PAI

NC

NC

PWMA

PWMB

PCLK

NC

V

SS

V

DD

V

SS

PC0/FC0/CS3

PC1/FC1/CS4

PC2/FC2/CS5

PC3/ADDR19/CS6

PC4/ADDR20/CS7

PC5/ADDR21/CS8

PC6/ADDR22/CS9

ADDR23/CS10

PE4/AS

R/W

PF1/IRQ1

PF2/IRQ2

PF3/IRQ3

PF4/IRQ4

PF5/IRQ5

PF6/IRQ6

PF7/IRQ7

BERR

HALT

RESET

TSC

BKPT/DSCLK

IFETCH/DSI

2

1

132

V

DDSYN

V

SS

VSSV

DD

VSSV

DD

V

SS

V

DD

V

SS

V

SS

V

DD

V

DD

V

SS

VDDVDDV

SS

V

SS

V

DD

V

SS

V

SS

V

SS

V

DD

V

DD

NC

MC68331 OVERVIEW MOTOROLA

USER’S MANUAL 3-5

3

Figure 3-3 Pin Assignments for 144-Pin Package

3.3 Pin Descriptions

The following tables are a summary of the functional characteristics of MCU pins. Table 3-1 shows types of output drivers. Table 3-2 shows all inputs and outputs. Digital

inputs and outputs use CMOS logic levels. An entry in the Discrete I/O column indicates that a pin can also be used for general-purpose input, output, or both. The I/O

port designation is given when it applies. Table 3-3 shows characteristics of power

pins. Refer to Figure 3-1 for port organization.

331 144-PIN QFP

V

SS

NC

FC0/CS3

FC1/CS4

FC2/CS5

ADDR19/CS6

ADDR20/CS7

ADDR21/CS8

ADDR22/CS9

ADDR23/CS10

V

DD

PCLK

PWMB

PWMA

NC

NC

NC

NC

PAI

PGP6/OC4

V

DD

V

SS

NC

PGP5/OC3/OC1

PGP4/OC2/OC1

PGP3/OC1

MC68331

NC

PE4/AS

PE6/SIZ0

PE7/SIZ1

R/W

PF0/MODCLK

PF1/IRQ1

PF2/IRQ2

PF3/IRQ3

PF4/IRQ4

PF5/IRQ5

PF6/IRQ6

PF7/IRQ7

BERR

HALT

RESET

CLKOUT

NC

XFC

EXTAL

V

DD

XTAL

FREEZE/QUOT

TSC

BKPT/DSCLK

IFETCH/DSI

IPIPE/DSO

RXD

PQS7/TXD

V

SS

NC

PGP2/IC3

PGP1/IC2

PGP0/IC1

NC

NC

2

1

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

107

108

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

31

32

33

34

35

36

BGACK/CS2

BG/CS1

BR/CS0

CSBOOT

DATA0

DATA1

DATA2

DATA3

DATA4

DATA5

DATA6

DATA7NCDATA8NCDATA9

DATA10NCDATA11

VSSDATA12

DATA13

DATA14

DATA15

ADDR0

PE0/DSACK0

PE1/DSACK1

PE2/AVEC

PE3/RMC

PE5/DS

V

DD

NC

ADDR1

ADDR2

ADDR3

ADDR4

ADDR5

ADDR6

ADDR7

ADDR8

V

DD

V

SS

ADDR9

ADDR10

ADDR11

ADDR12

NC

NC

ADDR13

ADDR14

ADDR15NCADDR16

ADDR17

ADDR18

PQS0/MISO

PQS1/MOSI

PQS2/SCK

PQS3/PCS0/SS

PQS4/PCS1

PQS5/PCS2

PQS6/PCS3

143

144

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

37

65

68

383940414243444546474849505152535455565758596061626364666769707172

V

SS

V

DD

V

SS

V

DD

V

SS

V

DD

V

DD

V

SS

V

SS

V

DD

V

SS

VSSV

DD

V

DD

V

SS

V

DD

V

SS

V

SS

V

DD

P7/IC4/OC5/OC1

MOTOROLA OVERVIEW MC68331

3-6 USER’S MANUAL

3

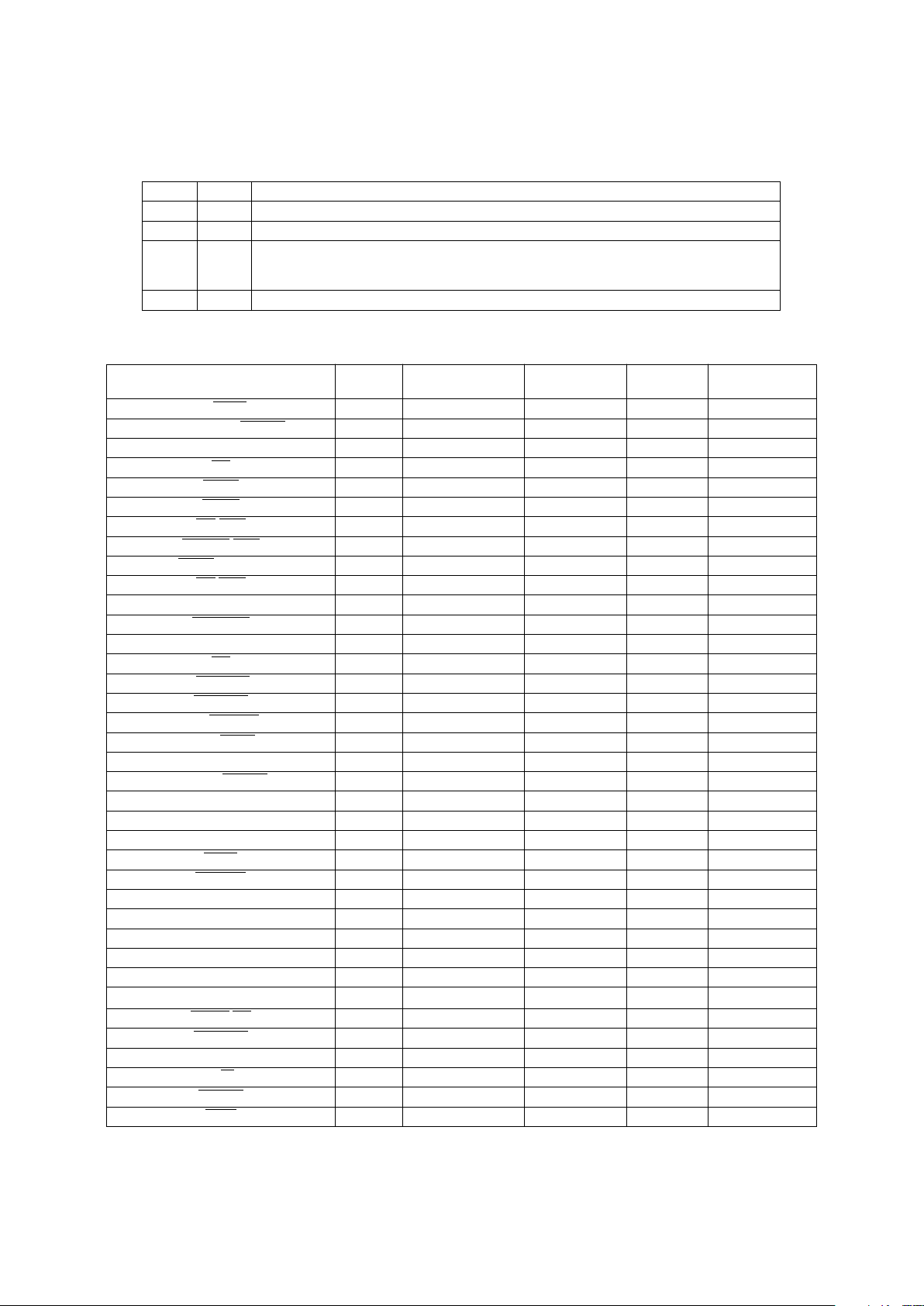

Table 3-1 MCU Driver Types

Type I/O Description

A O Output-only signals that are always driven; no external pull-up required

Aw O Type A output with weak P-channel pull-up during reset

B O Three-state output that includes circuitry to pull up output before high impedance is

established, to ensure rapid rise time. An external holding resistor is required to maintain

logic level while the pin is in the high-impedance state.

Bo O Type B output that can be operated in an open-drain mode

Table 3-2 MCU Pin Characteristics

Pin

Mnemonic

Output

Driver

Input

Synchronized

Input

Hysteresis

Discrete

I/O

Port

Designation

ADDR23/CS10

/ECLK A Y N O —

ADDR[22:19]/CS[9:6]

A Y N O PC[6:3]

ADDR[18:0] A Y N — —

AS

B Y N I/O PE5

A

VEC B Y N I/O PE2

BERR

B Y N — —

BG

/CS1 B — — — —

BGA

CK/CS2 B Y N — —

BKPT

/DSCLK — Y Y — —

BR

/CS0 B Y N — —

CLKOUT A — — — —

CSBOO

T B — — — —

DATA[15:0]1 Aw Y N — —

DS

B Y N I/O PE4

DSA

CK1 B Y N I/O PE1

DSA

CK0 B Y N I/O PE0

DSI/IFETCH

A Y Y — —

DSO/IPIPE

A — — — —

EXTAL2 — — Special — —

FC[2:0]/CS[5:3]

A Y N O PC[2:0]

FREEZE/QUOT A — — — —

IC4/OC5 A Y Y I/O GP4

IC[3:1] A Y Y I/O GP[7:5]

HAL

T Bo Y N — —

IRQ[7:1]

B Y Y I/O PF[7:1]

MISO Bo Y Y I/O PQS0

MODCLK

1

B Y N I/O PF0

MOSI Bo Y Y I/O PQS1

OC[4:1] A Y Y I/O GP[3:0]

PAI

2

— Y Y I —

PCLK

2

— Y Y I —

PCSO

/SS Bo Y Y I/O PQS3

PCS[3:1]

Bo Y Y I/O PQS[6:4]

PWMA, PWMB A — — O —

R/W

A Y N — —

RESET

Bo Y Y — —

RMC

B Y N I/O PE3

MC68331 OVERVIEW MOTOROLA

USER’S MANUAL 3-7

3

3.4 Signal Descriptions

The following tables define MCU signals. Table 3-4 shows signal origin, type, and active state. Table 3-5 describes signal functions. Both tables are sorted alphabetically

by mnemonic. MCU pins often have multiple functions. More than one description can

apply to a pin.

1. DATA[15:0] are synchronized during reset only. MODCLK is synchronized only when used as an input port pin.

2. EXTAL, XFC, and XTAL are clock reference connections.

3. PAI and PCLK can be used for discrete input, but are not part of an I/O port.

RXD — N N — —

SCK Bo Y Y I/O PQS2

SIZ[1:0] B Y N I/O PE[7:6]

TSC — Y Y — —

TXD Bo Y Y I/O PQS7

XFC

3

— — — Special —

XTAL

3

— — — Special —

Table 3-3 MCU Power Connections

Pin Mnemonic Description

V

DDSYN

Clock Synthesizer Power

V

SSE/VDDE

External Periphery Power (Source and Drain)

V

SS

I/V

DDI

Internal Module Power (Source and Drain)

Table 3-4 Signal Characteristics

Signal

Name

MCU

Module

Signal

Type

Active

State

ADDR[23:0] SIM Bus —

AS

SIM Output 0

A

VEC SIM Input 0

BERR

SIM Input 0

BG

SIM Output 0

BGA

CK SIM Input 0

BKPT

CPU32 Input 0

BR

SIM Input 0

CLKOUT SIM Output —

CS[10:0]

SIM Output 0

CSBOO

T SIM Output 0

DATA[15:0] SIM Bus —

DS

SIM Output 0

DSA

CK[1:0] SIM Input 0

DSCLK CPU32 Input Serial Clock

DSI CPU32 Input (Serial Data)

DSO CPU32 Output (Serial Data)

EXTAL SIM Input —

Table 3-2 MCU Pin Characteristics (Continued)

Pin

Mnemonic

Output

Driver

Input

Synchronized

Input

Hysteresis

Discrete

I/O

Port

Designation

MOTOROLA OVERVIEW MC68331

3-8 USER’S MANUAL

3

FC[2:0] SIM Output —

FREEZE SIM Output 1

HAL

T SIM Input/Output 0

IC[4:1] GPT Input —

IFETCH

CPU32 Output —

IPIPE

CPU32 Output —

IRQ[7:1]

SIM Input 0

MISO QSM Input/Output —

MODCLK SIM Input —

MOSI QSM Input/Output —

OC[5:1] GPT Output —

PAI GPT Input —

PC[6:0] SIM Output (Port)

PCS[3:0] QSM Input/Output —