Order this document by

MC68307/D

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

MOTOROLA (Parts Not Suitable for New Designs)

SEMICONDUCTOR

TECHNICAL INFORMATION

Technical Summary

Integrated Multiple-Bus Processor

MC68307

MC68307V

MOTOROLA, 1993

The MC68307 is an integrated processor combining a static 68EC000 processor with multiple interchip bus

interfaces. The MC68307 is designed to provide optimal integration and performance for applications such as

digital cordless telephones, portable measuring equipment, and point-of-sale terminals. By providing 3.3 V,

static operation in a small package, the MC68307 delivers cost-effective performance to handheld, batterypowered applications.

The MC68307 (shown in Figure 1) contains a static EC000 core processor, multiple bus interfaces, a serial

channel, two timers, and common system glue logic. The multiple bus interfaces include: dynamic 68000 bus,

8051 bus, and Motorola bus (M-bus) or I

2

C bus

1

. The dynamically sized 68000 bus allows 16-bit performance

out of static random access memory (SRAM) while still providing a low-cost interface to an 8-bit read-only

memory (ROM). The 8051 bus interfaces gluelessly to 8051-type devices and allows the reuse of applicationspecific integrated circuits (ASICs) designed for this industry standard bus. The M-bus is an industry standard

2-wire interface which provides efficient communications with peripherals such as EEPROM, analog/digital (A/

D) converters, and liquid crystal display (LCD) drivers. Thus, the MC68307 interfaces gluelessly to boot ROM,

SRAM, 8051 devices, M-bus devices, and memory-mapped peripherals. The MC68307 also incorporates a

slave mode which allows the EC000 core to be turned off, providing a 3.3-V static, low-power multi-function

peripheral for higher performance M68000 family processors.

1.

I

2

C bus is a proprietary Philips interface bus.

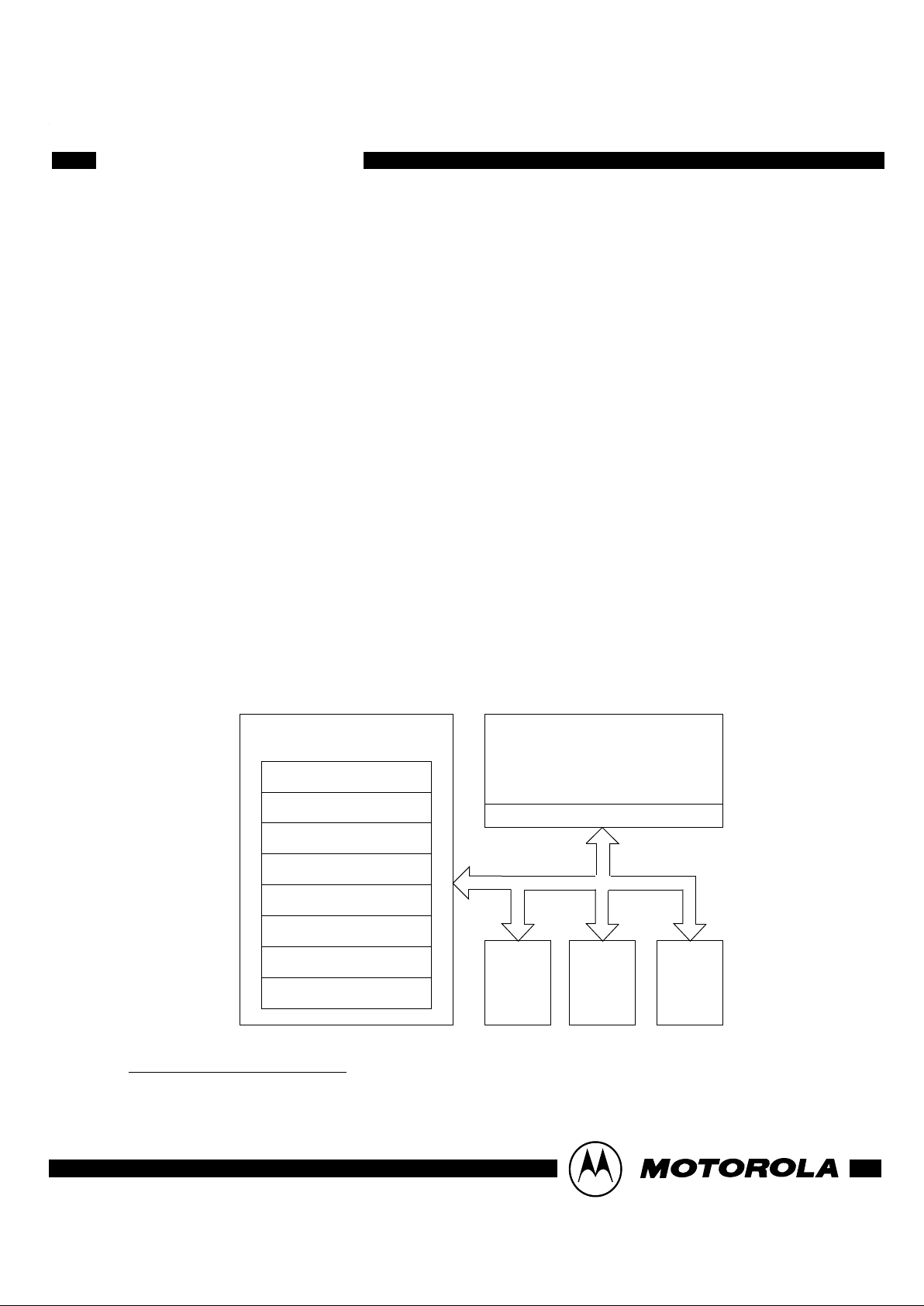

PROCESSOR CONTROL, CLOCK

AND LOW POWER

68000 INTERNAL BUS

8/16-BIT M68000

BUS INTERFACE

INTERRUPT

CONTROLLER

DUAL

TIMER

MODULE

UART

SERIAL I/O

M-BUS

MODULE

STATIC EC000 CORE PROCESSOR

DYNAMIC BUS SIZING EXTENSION

SYSTEM INTEGRATION MODULE

(SIM07)

8051 BUS INTERFACE

CHIP SELECT AND DTACK

Figure 1. MC68307 Block Diagram

PARALLEL I/O PORTS

SYSTEM PROTECTION

JTAG PORT

Thid t tdithF Mk 402

2 MC68307 TECHNICAL INFORMA TION MOT OROLA

The main features of the MC68307 include:

• Static EC000 Core Processor—Identical to MC68EC000 Microprocessor

—Full compatibility with MC68000 and MC68EC000

—24-bit address bus, for 16-Mbyte off-chip address space

—16-bit on-chip data bus for MC68000 bus operations

—Static design allows processor clock to be stopped providing dramatic power savings

—2.4 MIPS performance at 16.67-MHz processor clock

• External M68000 Bus Interface with Dynamic Bus Sizing for 8-bit and 16-bit Data Ports

• External 8-Bit Data Bus Interface (8051-Compatible)

• M-Bus Module

—Provides interchip bus interface for EEPROMs, LCD controllers, A/D converters, etc.

—Compatible with industry-standard I

2

C bus

—Master or slave operation modes, supports multiple masters

—Automatic interrupt generation with programmable level

—Software-programmable clock frequency

—Data rates from 4–100 Kbit/s above 3.0-MHz system clock

• Universal Asynchronous Receiver/Transmitter (UART) Module

—Flexible baud rate generator

—Based on MC68681 Dual Universal Asynchronous Receiver/Transmitter (DUART) programming

model

—5 Mbits/s maximum transfer rate at 16.67-MHz system clock

—Automatic interrupt generation with programmable level

—Modem control signals available (CTS

,RTS)

• Timer Module

—Dual channel 16-bit general purpose counter/timer

—Multimode operation, independent capture/compare registers

—Automatic interrupt generation with programmable level

—Third 16-bit timer configured as a software watchdog

—60-ns resolution at 16.67-MHz system clock

—Each timer has an input and an output pin

• System Integration Module (SIM07), Incorporating Many Functions Typically Relegated to External Programmable Array Logic (PALs), Transistor-Transistor Logic (TTL), and ASICs, such as:

—System configuration, programmable address mapping

—System protection by hardware watchdog logic

—Power-down mode control, programmable processor clock driver

—Four programmable chip selects with wait state generation logic

—Three simple peripheral chip selects

—Parallel input/output ports, some with interrupt capability

—Programmed interrupt vector response for on-chip peripheral modules

—IEEE 1149.1 boundary scan test access port (JTAG)

• Operation from DC to 16.67 MHz (Processor Clock)

• Operating Voltages of 3.3V ± 0.3V and 5V ± 0.5V

• Compact 100-Lead Quad Flat Pack (QFP) Package

MOT OROLA MC68307 TECHNICAL INFORMA TION 3

M68300 FAMILY

The MC68307 is one of a series of components in Motorola's M68300 family. Other members of the family

include the MC68302, MC68306, MC68330, MC68331, MC68332, MC68F333, MC68334, MC68340,

MC68341, MC68349, and MC68360.

ORGANIZATION

The M68300 family of integrated processors and controllers is built on an M68000 core processor and a

selection of intelligent peripherals appropriate for a set of applications. Common system glue logic such as

address decoding, wait state insertion, interrupt prioritization, and watchdog timing is also included.

Each member of the M68300 family is distinguished by its selection of on-chip peripherals. Peripherals are

chosen to address specific applications but are often useful in a wide variety of applications. The peripherals

may be highly sophisticated timing or protocol engines that have their own processors, or they may be more

traditional peripheral functions, such as UARTs and timers.

ADVANTAGES

By incorporating so many major features into a single M68300 family chip, a system designer can realize

significant savings in design time, power consumption, cost, board space, pin count, and programming. The

equivalent functionality can easily require 20 separate components. Each component might have 16–64 pins,

totaling over 350 connections. Most of these connections require interconnects or are duplications. Each

connection is a candidate for a bad solder joint or misrouted trace. Each component is another part to qualify,

purchase, inventory, and maintain. Each component requires a share of the printed circuit board. Each

component draws power, which is often used to drive large buffers to get the signal to another chip. The

cumulative power consumption of all the components must be available from the power supply. The signals

between the central processing unit (CPU) and a peripheral might not be compatible nor run from the same

clock, requiring time delays or other special design considerations.

In an M68300 family component, the major functions and glue logic are all properly connected internally, timed

with the same clock, fully tested, and uniformly documented. Only essential signals are brought out to pins.

The primary package is the surface-mount plastic QFP for the smallest possible footprint.

4 MC68307 TECHNICAL INFORMA TION MOT OROLA

MC68307 ARCHITECTURE

To improve total system throughput and reduce part count, board size and cost of system implementation, the

MC68307 integrates a powerful processor, intelligent peripheral modules, and typical system interface logic.

These functions include the SIM07, timers, UART, M-bus interface, and 8051-compatible bus interface.

The EC000 processor core communicates with these modules via an internal bus, providing the opportunity for

fully synchronized communication between all modules and allowing interrupts to be handled in parallel with data

transfers, greatly improving system performance.

STATIC EC000 CORE

The EC000 core is a core implementation of the MC68000 32-bit microprocessor architecture. The features of

the EC000 core processor include:

• Low power, static HCMOS implementation

• 24-bit address bus, 16-bit data bus

• Seventeen 32-bit data and address registers

• 56 powerful instruction types that support high level development languages

• 14 addressing modes and five main data types

• Seven priority levels for interrupt control

The EC000 core is completely upward user code-compatible with all other members of the M68000

microprocessor families and thus has access to a broad base of established real-time kernels, operating

systems, languages, applications, and development tools.

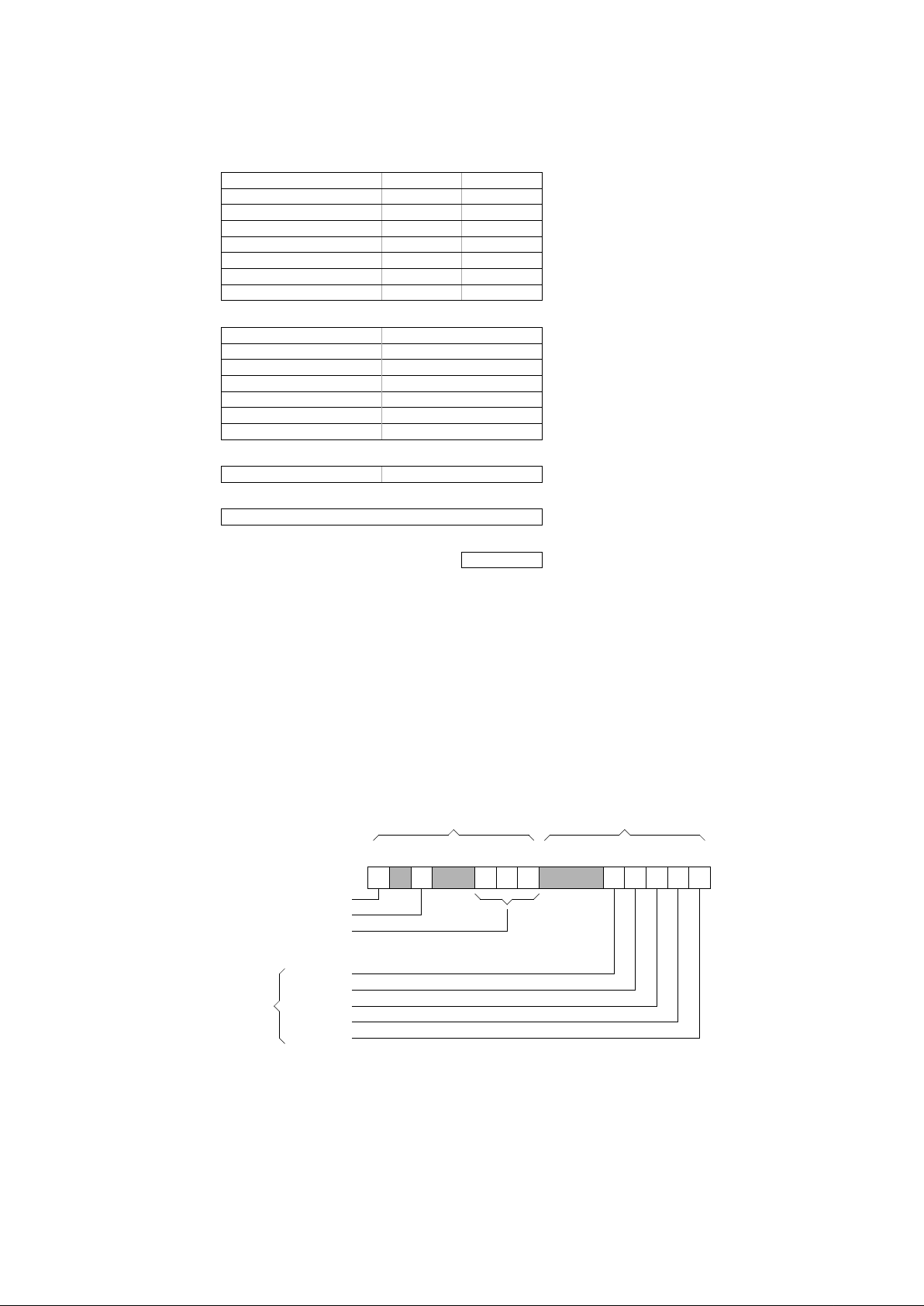

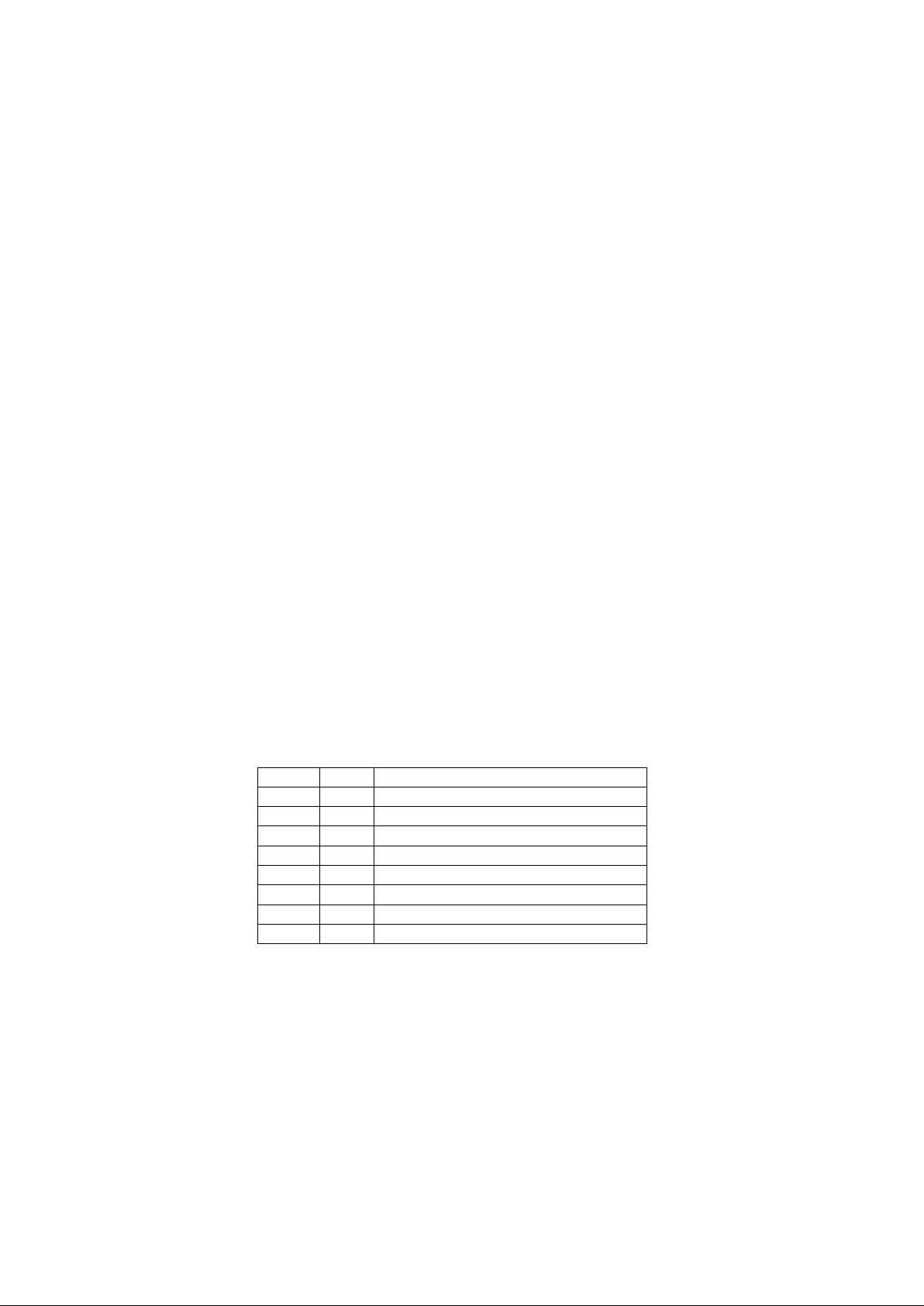

EC000 Core Programming Model

The EC000 core offers sixteen 32-bit registers and a 32-bit program counter (see Figure 2). The first eight

registers (D7–D0) are used as data registers for byte (8-bit), word (16-bit) and long-word (32-bit) operations.

Because the use of the data registers will affect the condition code register (indicating negative number, carry,

and overflow conditions) they are primarily used for data manipulation. The second set of seven registers (A6–

A0) and the user stack pointer (USP) may be used as software stack pointers and base address registers. These

registers can be used for word and long-word operations and do not affect the condition code register. All of the

registers (D7–D0 and A6–A0) may be used as index registers.

In supervisor mode, the upper byte of the status register (SR) and the supervisor stack pointer (SSP) are also

available to the programmer. These registers are shown in Figure 3.

The SR (refer to Figure 4) contains the interrupt mask (seven levels available) as well as the following condition

codes: extend (X), negative (N), zero (Z), overflow (V), and carry (C). Additional status bits indicate whether the

processor is in trace mode (T-bit) and in supervisor or user state (S-bit).

MOT OROLA MC68307 TECHNICAL INFORMA TION 5

Figure 2. User Programming Model

Figure 3. Supervisor Programming Model Supplement

Figure 4. Status Register

DATA REGISTERS

ADDRESS REGISTERS

31 16 15

8

7

0

USER STACK POINTERA7 (USP)

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

0151631

31 16 15 0

31 0

0

PC PROGRAM COUNTER

STATUS REGISTERCCR

7

TS I

2

I

1

I

0

XNZVC

15 13 10 8 4 0

TRACE MODE

SUPERVISOR STATE

INTERRUPT MASK

EXTEND

NEGATIVE

OVERFLOW

CARRY

SYSTEM BYTE USER BYTE

CONDITION CODES ZERO

6 MC68307 TECHNICAL INFORMA TION MOT OROLA

Data Types and Addressing Modes

Five basic data types are supported:

1.) Bits

2.) Binary coded decimal (BCD) digits (4 bits)

3.) Bytes (8 bits)

4.) Words (16 bits)

5.) Long words (32 bits)

In addition, operations on other data types such as memory addresses, status word data, etc. are provided in the

instruction set.

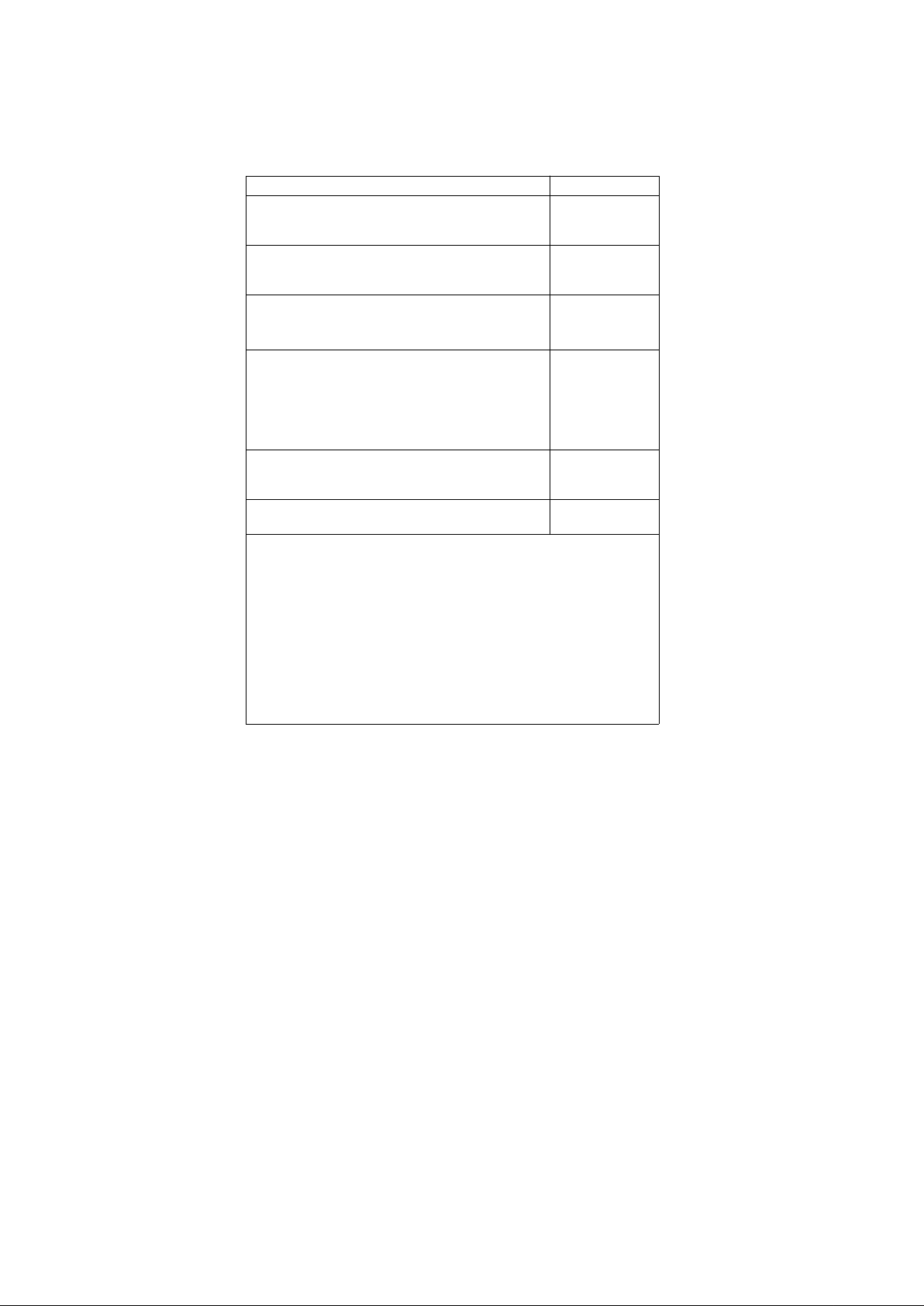

The 14 addressing modes listed in Table 1 include six basic types:

1.) Register direct

2.) Register indirect

3.) Absolute

4.) Program counter relative

5.) Immediate

6.) Implied

Included in the register indirect addressing modes is the capability to perform postincrementing,

predecrementing, offsetting, and indexing. The program counter relative mode can also be modified via indexing

and offsetting.

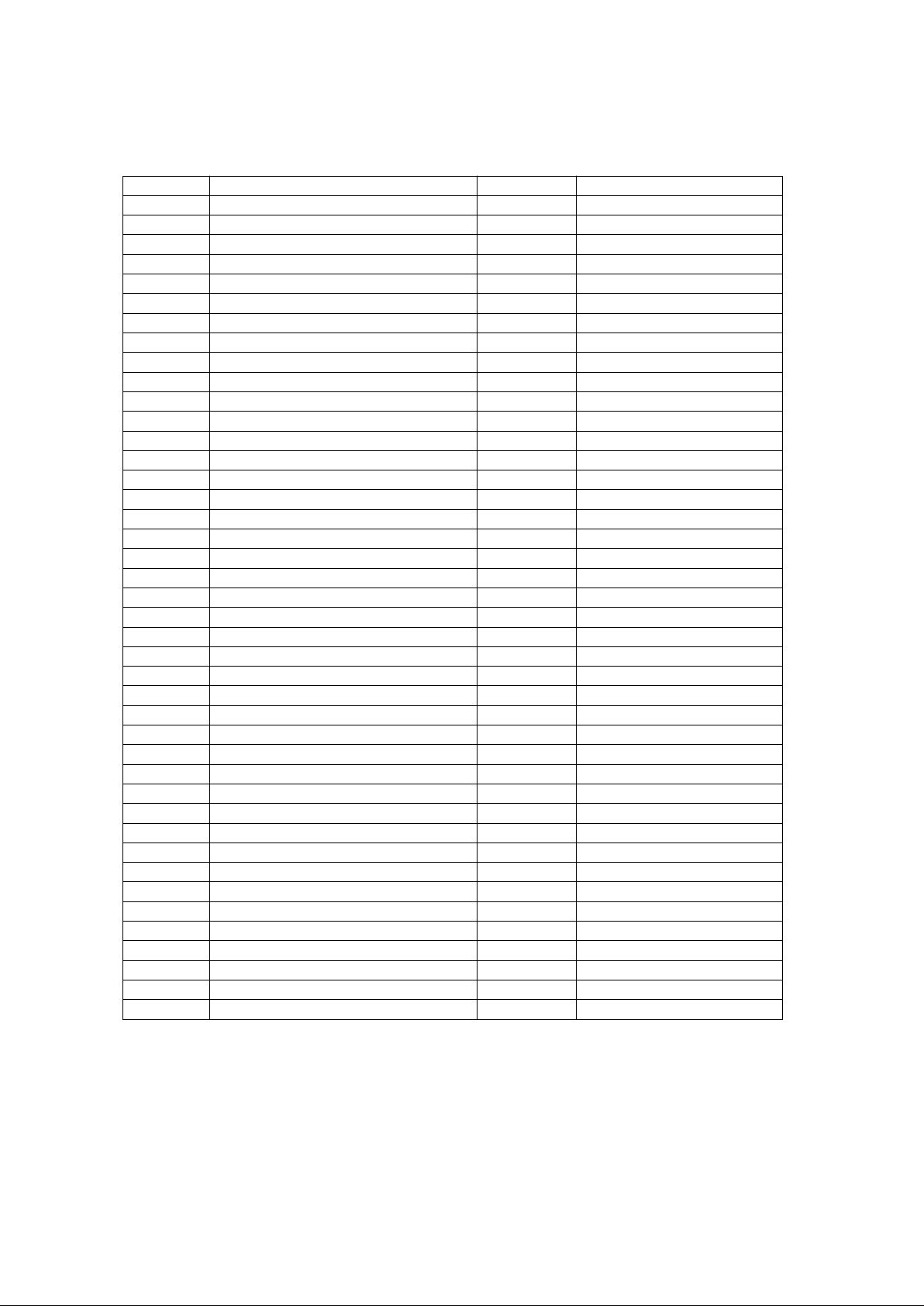

Instruction Set Overview

The EC000 core instruction set is listed in Table 2. The instruction set facilitates ease of programming by

supporting high-level languages. Each instruction, with few exceptions, operates on bytes, words, and longwords, and most instructions can use any of the 14 addressing modes. Combining instruction types, data types,

and addressing modes, over 1000 useful instructions are provided. These instructions include signed and

unsigned, multiply and divide, quick arithmetic operations, BCD arithmetic, and expanded operations (through

traps).

MOT OROLA MC68307 TECHNICAL INFORMA TION 7

Table 1. Addressing Modes

Addressing modes Syntax

Register direct addressing

Data register direct

Address register direct

Dn

An

Absolute data addressing

Absolute short

Absolute long

xxx.W

xxx.L

Program counter relative addressing

Relative with offset

Relative with index offset

d

16

(PC)

d

8

(PC, Xn)

Register indirect addressing register

Register indirect

Postincrement register indirect

Predecrement register indirect

Register indirect with offset

Indexed register indirect with offset

(An)

(An)+

–(An)

d

16

(An)

d

8

(An, Xn)

Immediate data addressing

Immediate

Quick immediate

#xxx

#1–#8

Implied addressing

Implied register SR/USP/SP/PC

Legend:

Dn = Data Register

An = Address Register

Xn = Address or Data Register Used as Index Register

SR = Status Register

PC = Program Counter

SP = Stack Pointer

USP = User Stack Pointer

<> = Effective Address

d

8

= 8-Bit Offset (Displacement)

d

16

= 16-Bit Offset (Displacement)

#xxx = Immediate Data

8 MC68307 TECHNICAL INFORMA TION MOT OROLA

Table 2. Instruction Set

Mnemonic Description Mnemonic Description

ABCD Add decimal with extend MOVEM Move multiple registers

ADD Add MOVEP Move peripheral data

ADDA Add address MOVEQ Move quick

ADDQ Add quick MOVE from SR Move from status register

ADDI Add immediate MOVE to SR Move to status register

ADDX Add with extend MOVE to CCR Move to condition codes

AND Logical AND MOVE USP Move user stack pointer

ANDI AND immediate MULS Signed multiply

ANDI to CCR AND immediate to condition codes MULU Unsigned multiply

ANDI to SR AND immediate to status register NBCD Negate decimal with extend

ASL Arithmetic shift left NEG Negate

ASR Arithmetic shift right NEGX Negate with extend

Bcc Branch conditionally NOP No operation

BCHG Bit test and change NOT Ones complement

BCLR Bit test and clear OR Logical OR

BRA Branch always ORI OR immediate

BSET Bit test and set ORI to CCR OR immediate to condition codes

BSR Branch to subroutined set ORI to SR OR immediate to status register

BTST Bit test PEA Push effective address

CHK Check register against bounds RESET Reset external devices

CLR Clear operand ROL Rotate left without extend

CMP Compare ROR Rotate right without extend

CMPA Compare address ROXL Rotate left with extend

CMPM Compare memory ROXR Rotate right with extend

CMPI Compare immediate RTE Return from exception

DBcc Test cond, decrement and branch RTR Return and restore

DIVS Signed divide RTS Return from subroutine

DIVU Unsigned divide SBCD Subtract decimal with extend

EOR Exclusive OR Scc Set conditional

EORI Exclusive OR immediate STOP Stop

EORI to CCR Exclusive OR immediate to condition codes SUB Subtract

EORI to SR Exclusive OR immediate to status register SUBA Subtract address

EXG Exchange registers SUBI Subtract immediate

EXT Sign extend SUBQ Subtract quick

JMP Jump SUBX Subtract with extend

JSR Jump to subroutine SWAP Swap data register halves

LEA Load effective address TAS Test and set operand

LINK Link stack TRAP Trap

LSL Logical shift left TRAPV Trap on overflow

LSR Logical shift right TST Test

MOVE Move UNLK Unlink

MOVEA Move address — —

MOT OROLA MC68307 TECHNICAL INFORMA TION 9

SYSTEM INTEGRATION MODULE

The MC68307 system integration module (SIM07) consists of several functions that control the system start-up,

initialization, configuration, and the external bus with a minimum of external devices.

The SIM07 features include:

• System configuration

• Oscillator & clock dividers

• Reset control, power-down mode control

• Chip-selects and wait states

• External bus interfaces, 68000 and 8051-compatible

• Parallel input/outputs with interrupt capability

• Interrupt configuration/response

• Software watchdog

• JTAG test access port

System Configuration

The MC68307 system configuration logic consists of a module base address register (MBAR) and a system

control register (SCR) which together allow the user to configure operation of the following functions:

• Base address and address space of internal peripheral registers

• Low-power (stand-by) modes

• Hardware watchdog for system protection

• 8051-compatible bus

• Peripheral chip selects

• Data bus size control for chip selected address ranges

Chip Select Logic and Dynamic Bus Sizing

The MC68307 provides four programmable chip-select signals (CS3

–CS0). For a given chip-select block, the

user may choose whether the chip-select allows read-only , write-only, or both read and write accesses, whether

the chip-select should match only one function code value or all values, whether a DTACK

is automatically

generated for this chip-select, and after how many wait states (from zero to six) the DTACK

will be generated.

Each of the chip selects includes a dynamic bus-sizing extension to the basic 68000 bus which allows the system

designer to mix 16-bit and 8-bit contiguous address memory devices (RAM, ROM) on a 16-bit data bus system.

An additional feature of CS2 allows the user to opt either to use the programmable chip select CS2 or to use four

peripheral chip selects (CS2A, CS2B, CS2C, and CS2D). When the four peripheral chip selects are enabled,

each one selects a16-Kbyte block within the programmed range of CS2.

10 MC68307 TECHNICAL INFORMATION MOTOROLA

External Bus Interface

The external bus interface handles the transfer of information between the internal EC000 core and the memory ,

peripherals, or other processing elements in the external address space. It consists of a 68000 bus interface and

an 8051-compatible bus interface. The external 68000 bus provides up to 24 address lines and 16 data lines.

Each bus access can appear externally either as a 68000 bus cycle (either 16-bit or 8-bit dynamic data bus width)

or as an 8-bit wide 8051-compatible bus cycle (multiplexing 8 bits of address and data) with the appropriate sets

of control signals.

Parallel General-Purpose I/O Ports

The MC68307 supports two general-purpose I/O ports, port A (8-bits) and port B (16-bits), whose pins can be

configured as general-purpose I/O pins or as dedicated peripheral interface pins for the on-chip modules.

Each port pin can be independently programmed as general-purpose I/O pins, even when other pins related to

the same on-chip peripheral are used as dedicated pins. Even if all the pins for a particular peripheral are

configured as general-purpose I/O, the peripheral will still operate normally (although this is only useful in the

case of the timer module). Power consumption may be reduced by turning off unused modules.

Interrupt Controller

The interrupt controller supports interrupts from three sources. The first source is an external, nonmaskable

interrupt input on the IRQ7

signal, which always causes an interrupt priority level 7 request to the EC000 core.

Assuming no other source is programmed as a level 7 source, this input will always obtain the immediate

attention of the core.

The second source is an external interrupt received through the 8-channel latched interrupt port (INT8–INT1).

Each INTx signal can be programmed with an interrupt priority level, and each can have pending interrupts

cleared independently of the others.

The third source of interrupts is the on-chip peripherals. The interrupt controller allows the user to assign the

interrupt priority level each of the four on-chip peripherals will use, and to determine a particular vector number

to be presented when the respective module receives an interrupt acknowledge from the processor via the

interrupt controller logic.

Software Watchdog

A software watchdog timer is used to protect against system failures by providing a means to escape from

unexpected input conditions, external events, or programming errors. Once started, the software watchdog timer

must be cleared by software on a regular basis so that it never reaches its time-out value. Upon reaching the

time-out value, the assumption is made that a system failure has occurred, and the software watchdog logic

resets the MC68307.

MOT OROLA MC68307 TECHNICAL INFORMA TION 11

Low-Power Stop Logic

Various options for power-saving are available: turning off unused peripherals, reducing processor clock speed,

disabling the processor altogether or a combination of these.

A wake-up from power-down can be achieved by causing an interrupt at the interrupt controller logic which runs

throughout the period of processor power-down. Any interrupt will cause a wake-up of the EC000 core followed

by processing of that interrupt.

The on-chip peripherals can initiate a wake-up; for example, the timer can be set to wake-up after a certain

elapsed time, or number of external events, or the UART can cause a wake-up on receiving serial data.

The clocks provided to the various internal modules can all be disabled to further reduce power consumption. In

the case of the UART, its clock is restarted automatically by a transition on the RxD pin, so that incoming data is

clocked in. When the data has been completely received, an interrupt from the UART wakes-up the processor

core. If the other on-chip peripherals (the timer and M-bus) are required to cause a wake-up, then their clocks

should not be disabled in this manner.

JTAG Test Access Port

To aid in system diagnostics the MC68307 includes dedicated user-accessible test logic that is fully compliant

with the IEEE 1149.1 standard for boundary scan testability, often referred to as JTAG (joint test action group).

SIM07 Programming Model

The SIM07 programming model is listed in Tables 3–7. The FC (function code) column in each table indicates

whether a register is restricted to supervisor access (S) or programmable to exist in either supervisor or user

space (S/U). With the exception of the system configuration registers (listed in Table 3), the address column

of each table contains the offset from the base address (MBASE) contained in the MBAR.

Table 3. SIM07 System Configuration Registers

Address FC Register Name

$0000F0 — Reserved—No external bus access

$0000F2 S Module Base Address Register (MBAR)

$0000F4 S System Control Register (SCR)

$0000F6 S System Control Register (SCR)

$0000F8 — Reserved—No external bus access

$0000FA — Reserved—No external bus access

$0000FC — Reserved—No external bus access

$0000FE — Reserved—No external bus access

Loading...

Loading...