Semiconductor Components Industries, LLC, 2000

May, 2000 – Rev. 4

1 Publication Order Number:

MC14490/D

MC14490

Hex Contact Bounce

Eliminator

The MC14490 is constructed with complementary MOS

enhancement mode devices, and is used for the elimination of

extraneous level changes that result when interfacing with mechanical

contacts. The digital contact bounce eliminator circuit takes an input

signal from a bouncing contact and generates a clean digital signal

four clock periods after the input has stabilized. The bounce eliminator

circuit will remove bounce on both the “make” and the “break” of a

contact closure. The clock for operation of the MC14490 is derived

from an internal R–C oscillator which requires only an external

capacitor to adjust for the desired operating frequency (bounce delay).

The clock may also be driven from an external clock source or the

oscillator of another MC14490 (see Figure 5).

NOTE: Immediately after power–up, the outputs of the MC14490

are in indeterminate states.

• Diode Protection on All Inputs

• Six Debouncers Per Package

• Internal Pullups on All Data Inputs

• Can Be Used as a Digital Integrator, System Synchronizer, or Delay

Line

• Internal Oscillator (R–C), or External Clock Source

• TTL Compatible Data Inputs/Outputs

• Single Line Input, Debounces Both “Make” and “Break” Contacts

• Does Not Require “Form C” (Single Pole Double Throw) Input

Signal

• Cascadable for Longer Time Delays

• Schmitt Trigger on Clock Input (Pin 7)

• Supply Voltage Range = 3.0 V to 18 V

• Chip Complexity: 546 FETs or 136.5 Equivalent Gates

MAXIMUM RATINGS (Voltages Referenced to V

SS

) (Note 2.)

Symbol Parameter Value Unit

V

DD

DC Supply Voltage Range –0.5 to +18.0 V

Vin, V

out

Input or Output Voltage Range

(DC or Transient)

–0.5 to VDD + 0.5 V

I

in

Input Current

(DC or Transient) per Pin

±10 mA

P

D

Power Dissipation,

per Package (Note 3.)

500 mW

T

A

Ambient Temperature Range –55 to +125 °C

T

stg

Storage Temperature Range –65 to +150 °C

T

L

Lead Temperature

(8–Second Soldering)

260 °C

2. Maximum Ratings are those values beyond which damage to the device

may occur.

3. Temperature Derating:

Plastic “P and D/DW” Packages: – 7.0 mW/_C From 65_C T o 125_C

http://onsemi.com

A = Assembly Location

WL or L = Wafer Lot

YY or Y = Year

WW or W = Work Week

Device Package Shipping

ORDERING INFORMATION

MC14490DW SOIC–16 47/Rail

MC14490DWR2 SOIC–16 1000/Tape & Reel

MC14490F SOEIAJ–16 See Note 1.

1. For ordering information on the EIAJ version of

the SOIC packages, please contact your local

ON Semiconductor representative.

MARKING

DIAGRAMS

1

16

PDIP–16

P SUFFIX

CASE 648

MC14490P

AWLYYWW

MC14490FEL SOEIAJ–16 See Note 1.

MC14490P PDIP–16 25/Rail

SOIC–16

DW SUFFIX

CASE 751G

1

16

14490

AWLYYWW

This device contains protection circuitry to guard

against damage due to high static voltages or electric

fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated

voltages to this high–impedance circuit. For proper

operation, V

in

and V

out

should be constrained to the

range V

SS

v (Vin or V

out

) v VDD.

Unused inputs must always be tied to an appropriate

logic voltage level (e.g., either V

SS

or VDD). Unused out-

puts must be left open.

SOEIAJ–16

F SUFFIX

CASE 966

1

16

MC14490

AWLYWW

MC14490

http://onsemi.com

2

PIN ASSIGNMENT

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

D

in

C

out

B

in

V

DD

OSC

out

F

in

E

out

D

out

C

in

B

out

A

in

V

SS

OSC

in

F

out

E

in

A

out

BLOCK DIAGRAM

Ain1

OSC

in

7

OSC

out

9

B

in

14

C

in

3

D

in

12

Ein5

F

in

10

+V

DD

φ1

φ2

OSCILLATOR

AND

TWO–PHASE

CLOCK GENERATOR

DATA

SHIFT LOAD

4–BIT STATIC SHIFT REGISTER

1/2–BIT

DELAY

φ1 φ2

φ1 φ2

15 A

out

VDD = PIN 16

V

SS

= PIN 8

φ1 φ2

φ1 φ2

φ1 φ2

φ1 φ2

φ1 φ2

2B

out

13 C

out

4D

out

11 E

out

6F

out

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

IDENTICAL TO ABOVE STAGE

MC14490

http://onsemi.com

3

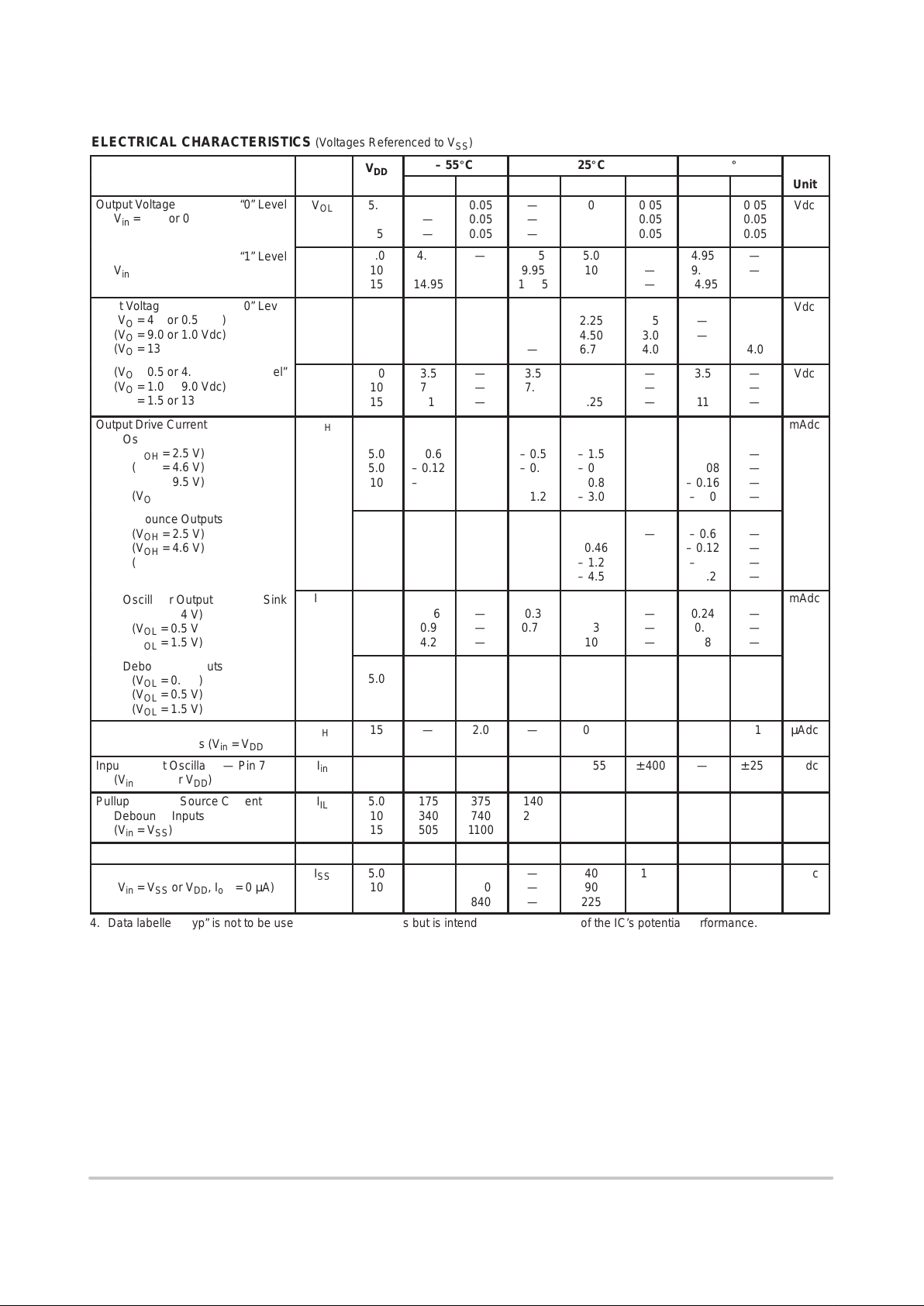

ELECTRICAL CHARACTERISTICS (Voltages Referenced to V

SS

)

V

DD

– 55_C

25_C

125_C

Characteristic

Symbol

DD

Vdc

Min

Max

Min

Typ

(4.)

Max

Min

Max

Unit

ОООООООО

Î

Output Voltage “0” Level

Vin = VDD or 0

ÎÎ

Î

V

OL

Î

Î

5.0

10

15

Î

Î

—

—

—

Î

Î

0.05

0.05

0.05

ÎÎ

Î

—

—

—

Î

Î

0

0

0

ÎÎ

Î

0.05

0.05

0.05

Î

Î

—

—

—

Î

Î

0.05

0.05

0.05

Î

Î

Vdc

ОООООООО

Î

“1” Level

Vin = 0 or V

DD

ÎÎ

Î

V

OH

Î

Î

5.0

10

15

Î

Î

4.95

9.95

14.95

Î

Î

—

—

—

ÎÎ

Î

4.95

9.95

14.95

Î

Î

5.0

10

15

ÎÎ

Î

—

—

—

Î

Î

4.95

9.95

14.95

Î

Î

—

—

—

Î

Î

Vdc

ОООООООО

Î

ОООООООО

Î

Input Voltage “0” Level

(VO = 4.5 or 0.5 Vdc)

(V

O

= 9.0 or 1.0 Vdc)

(VO = 13.5 or 1.5 Vdc)

ÎÎ

Î

ÎÎ

Î

V

IL

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

1.5

3.0

4.0

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

2.25

4.50

6.75

ÎÎ

Î

ÎÎ

Î

1.5

3.0

4.0

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

1.5

3.0

4.0

Î

Î

Î

Î

Vdc

ОООООООО

Î

(VO = 0.5 or 4.5 Vdc) “1 Level”

(VO = 1.0 or 9.0 Vdc)

(VO = 1.5 or 13.5 Vdc)

ÎÎ

Î

V

IH

Î

Î

5.0

10

15

Î

Î

3.5

7.0

11

Î

Î

—

—

—

ÎÎ

Î

3.5

7.0

11

Î

Î

2.75

5.50

8.25

ÎÎ

Î

—

—

—

Î

Î

3.5

7.0

11

Î

Î

—

—

—

Î

Î

Vdc

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

Output Drive Current

Oscillator Output Source

(VOH = 2.5 V)

(V

OH

= 4.6 V)

(VOH = 9.5 V)

(VOH = 13.5 V)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

I

OH

Î

Î

Î

Î

Î

Î

5.0

5.0

10

15

Î

Î

Î

Î

Î

Î

– 0.6

– 0.12

– 0.23

– 1.4

Î

Î

Î

Î

Î

Î

—

—

—

—

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

– 0.5

– 0.1

– 0.2

– 1.2

Î

Î

Î

Î

Î

Î

– 1.5

– 0.3

– 0.8

– 3.0

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

—

—

—

—

Î

Î

Î

Î

Î

Î

– 0.4

– 0.08

– 0.16

– 1.0

Î

Î

Î

Î

Î

Î

—

—

—

—

Î

Î

Î

Î

Î

Î

mAdc

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

Debounce Outputs

(V

OH

= 2.5 V)

(V

OH

= 4.6 V)

(VOH = 9.5 V)

(VOH = 13.5 V)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

Î

Î

Î

Î

Î

Î

5.0

5.0

10

15

Î

Î

Î

Î

Î

Î

– 0.9

– 0.19

– 0.6

1.8

Î

Î

Î

Î

Î

Î

—

—

—

—

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

– 0.75

– 0.16

– 0.5

– 1.5

Î

Î

Î

Î

Î

Î

– 2.2

– 0.46

– 1.2

– 4.5

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

—

—

—

—

Î

Î

Î

Î

Î

Î

– 0.6

– 0.12

– 0.4

– 1.2

Î

Î

Î

Î

Î

Î

—

—

—

—

Î

Î

Î

Î

Î

Î

ОООООООО

Î

Oscillator Output Sink

(VOL = 0.4 V)

(VOL = 0.5 V)

(V

OL

= 1.5 V)

ÎÎ

Î

I

OL

Î

Î

5.0

10

15

Î

Î

0.36

0.9

4.2

Î

Î

—

—

—

ÎÎ

Î

0.3

0.75

3.5

Î

Î

0.9

2.3

10

ÎÎ

Î

—

—

—

Î

Î

0.24

0.6

2.8

Î

Î

—

—

—

Î

Î

mAdc

ОООООООО

Î

ОООООООО

Î

Debounce Outputs

(V

OL

= 0.4 V)

(VOL = 0.5 V)

(VOL = 1.5 V)

ÎÎ

Î

ÎÎ

Î

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

2.6

4.0

12

Î

Î

Î

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

2.2

3.3

10

Î

Î

Î

Î

4.0

9.0

35

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

1.8

2.7

8.1

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

ОООООООО

Î

Input Current

Debounce Inputs (V

in

= VDD)

ÎÎ

Î

I

IH

Î

Î

15

Î

Î

—

Î

Î

2.0

ÎÎ

Î

—

Î

Î

0.2

ÎÎ

Î

2.0

Î

Î

—

Î

Î

11

Î

Î

µAdc

Input Current Oscillator — Pin 7

(Vin = VSS or VDD)

I

in

15

—

± 620

—

± 255

± 400

—

± 250

µAdc

ОООООООО

Î

Pullup Resistor Source Current

Debounce Inputs

(Vin = VSS)

ÎÎ

Î

I

IL

Î

Î

5.0

10

15

Î

Î

175

340

505

Î

Î

375

740

1100

ÎÎ

Î

140

280

415

Î

Î

190

380

570

ÎÎ

Î

255

500

750

Î

Î

70

145

215

Î

Î

225

440

660

Î

Î

µAdc

Input Capacitance

C

in

—

—

—

—

5.0

7.5

—

—

pF

ОООООООО

Î

ОООООООО

Î

Quiescent Current

(Vin = VSS or VDD, I

out

= 0 µA)

ÎÎ

Î

ÎÎ

Î

I

SS

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

150

280

840

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

40

90

225

ÎÎ

Î

ÎÎ

Î

100

225

650

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

90

180

550

Î

Î

Î

Î

µAdc

4. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

MC14490

http://onsemi.com

4

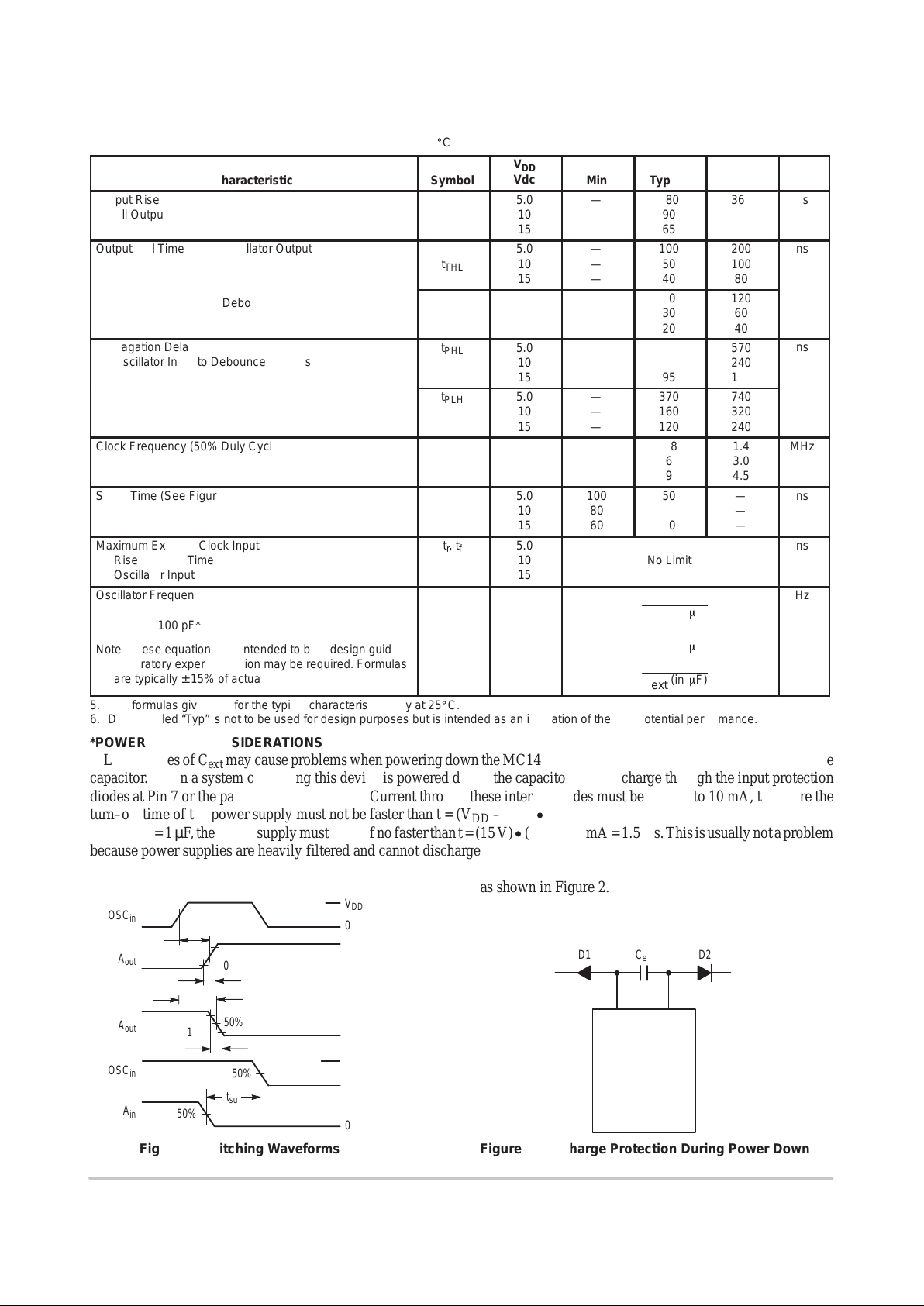

SWITCHING CHARACTERISTICS

(5.)

(C

L

= 50 pF, T

A

= 25_C)

Characteristic

ÎÎÎÎ

Symbol

V

DD

Vdc

Min

Typ

(6.)

Max

Unit

ОООООООООООООО

Î

Output Rise Time

All Outputs

ÎÎÎÎ

ÎÎÎ

Î

t

TLH

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

180

90

65

ÎÎ

Î

360

180

130

Î

Î

ns

ОООООООООООООО

Î

ОООООООООООООО

Î

Output Fall Time Oscillator Output

ÎÎÎÎ

ÎÎÎ

Î

ÎÎÎ

Î

t

THL

ÎÎ

Î

ÎÎ

Î

5.0

10

15

ÎÎ

Î

ÎÎ

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

100

50

40

ÎÎ

Î

ÎÎ

Î

200

100

80

Î

Î

Î

Î

ns

ОООООООООООООО

Î

Debounce Outputs

ÎÎÎÎ

ÎÎÎ

Î

t

THL

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

60

30

20

ÎÎ

Î

120

60

40

Î

Î

ОООООООООООООО

Î

Propagation Delay Time

Oscillator Input to Debounce Outputs

ÎÎÎÎ

ÎÎÎ

Î

t

PHL

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

285

120

95

ÎÎ

Î

570

240

190

Î

Î

ns

ОООООООООООООО

Î

ÎÎÎÎ

ÎÎÎ

Î

t

PLH

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

370

160

120

ÎÎ

Î

740

320

240

Î

Î

ОООООООООООООО

Î

Clock Frequency (50% Duly Cycle)

(External Clock)

ÎÎÎÎ

ÎÎÎ

Î

f

cl

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

2.8

6

9

ÎÎ

Î

1.4

3.0

4.5

Î

Î

MHz

ОООООООООООООО

Î

Setup Time (See Figure 1)

ÎÎÎÎ

ÎÎÎ

Î

t

su

ÎÎ

Î

5.0

10

15

ÎÎ

Î

100

80

60

ÎÎ

Î

50

40

30

ÎÎ

Î

—

—

—

Î

Î

ns

ОООООООООООООО

Î

Maximum External Clock Input

Rise and Fall Time

Oscillator Input

ÎÎÎÎ

ÎÎÎ

Î

tr, t

f

ÎÎ

Î

5.0

10

15

ОООООООО

Î

No Limit

Î

Î

ns

ОООООООООООООО

Î

ОООООООООООООО

Î

ОООООООООООООО

Î

ОООООООООООООО

Î

Oscillator Frequency

OSC

out

C

ext

≥ 100 pF*

Note: These equations are intended to be a design guide.

Laboratory experimentation may be required. Formulas

are typically ± 15% of actual frequencies.

ÎÎÎÎ

ÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

Î

ÎÎÎ

Î

f

osc

, typ

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

5.0

10

15

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

1.5

C

ext

(inmF)

4.5

C

ext

(inmF)

6.5

C

ext

(inmF)

Î

Î

Î

Î

Î

Î

Î

Î

Hz

5. The formulas given are for the typical characteristics only at 25_C.

6. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

*POWER–DOWN CONSIDERATIONS

Large values of C

ext

may cause problems when powering down the MC14490 because of the amount of energy stored in the

capacitor. When a system containing this device is powered down, the capacitor may discharge through the input protection

diodes at Pin 7 or the parasitic diodes at Pin 9. Current through these internal diodes must be limited to 10 mA, therefore the

turn–off time of the power supply must not be faster than t = (VDD – VSS) C

ext

/(10 mA). For example, If VDD – VSS = 15

V and C

ext

= 1 µF , the power supply must turn off no faster than t = (15 V) (1 µF)/10 mA = 1.5 ms. This is usually not a problem

because power supplies are heavily filtered and cannot discharge at this rate.

When a more rapid decrease of the power supply to zero volts occurs, the MC14490 may sustain damage. To avoid this

possibility, use external clamping diodes, D1 and D2, connected as shown in Figure 2.

Figure 1. Switching Waveforms Figure 2. Discharge Protection During Power Down

OSC

in

A

out

A

out

OSC

in

A

in

V

DD

0 V

V

DD

0 V

V

DD

0 V

50%

90%

50%

10%

t

r

t

f

t

PHL

90%

10%

50%

50%

t

su

50%

D1 D2C

ext

9

7

OSC

in

OSC

out

MC14490

t

PLH

V

DD

V

DD

Loading...

Loading...