MOTOROLA MC14049UBFEL, MC14049UBFL1, MC14049UBFL2, MC14049UBFR1, MC14049UBDR2 Datasheet

...

Semiconductor Components Industries, LLC, 2000

March, 2000 – Rev. 3

1 Publication Order Number:

MC14049UB/D

MC14049UB

Hex Buffers

The MC14049UB hex inverter/buffer is constructed with MOS

P–channel and N–channel enhancement mode devices in a single

monolithic structure. This complementary MOS device finds primary

use where low power dissipation and/or high noise immunity is

desired. This device provides logic–level conversion using only one

supply voltage, V

DD

. The input–signal high level (VIH) can exceed the

VDD supply voltage for logic–level conversions. Two TTL/DTL

Loads can be driven when the device is used as CMOS–to–TTL/DTL

converters (VDD = 5.0 V, VOL v 0.4 V, IOL ≥ 3.2 mA). Note that pins

13 and 16 are not connected internally on this device; consequently

connections to these terminals will not affect circuit operation.

• High Source and Sink Currents

• High–to–Low Level Converter

• Supply Voltage Range = 3.0 V to 18 V

• Meets JEDEC UB Specifications

• V

IN

can exceed V

DD

• Improved ESD Protection on All Inputs

MAXIMUM RATINGS (Voltages Referenced to V

SS

) (Note 2.)

Symbol

Parameter Value Unit

V

DD

DC Supply Voltage Range –0.5 to +18.0 V

V

in

Input Voltage Range

(DC or Transient)

–0.5 to +18.0 V

V

out

Output Voltage Range

(DC or Transient)

–0.5 to VDD +0.5 V

I

in

Input Current

(DC or Transient) per Pin

±10 mA

I

out

Output Current

(DC or Transient) per Pin

+45 mA

P

D

Power Dissipation,

per Package (Note 3.)

Plastic

SOIC

825

740

mW

T

A

Ambient Temperature Range –55 to +125 °C

T

stg

Storage Temperature Range –65 to +150 °C

T

L

Lead Temperature

(8–Second Soldering)

260 °C

2. Maximum Ratings are those values beyond which damage to the device

may occur.

3. Temperature Derating:

All Packages: See Figure 4.

This device contains circuitry to protect the inputs against damage due to high

static voltages or electric fields referenced to the V

SS

pin, only. Extra precautions

must be taken to avoid applications of any voltage higher than the maximum rated

voltages to this high–impedance circuit. For proper operation, the ranges V

SS

v

V

in

v 18 V and VSS v V

out

v VDD are recommended.

Unused inputs must always be tied to an appropriate logic voltage level (e.g.,

either V

SS

or VDD). Unused outputs must be left open.

http://onsemi.com

A = Assembly Location

WL or L = Wafer Lot

YY or Y = Year

WW or W = Work Week

Device Package Shipping

ORDERING INFORMATION

MC14049UBCP PDIP–16 2000/Box

MC14049UBD SOIC–16 2400/Box

MC14049UBDR2 SOIC–16 2500/Tape & Reel

1. For ordering information on the EIAJ version of

the SOIC packages, please contact your local

ON Semiconductor representative.

MARKING

DIAGRAMS

1

16

PDIP–16

P SUFFIX

CASE 648

MC14049UBCP

AWLYYWW

SOIC–16

D SUFFIX

CASE 751B

1

16

14049U

AWLYWW

SOEIAJ–16

F SUFFIX

CASE 966

1

16

MC14049U

AWLYWW

MC14049UBDT TSSOP–16 96/Rail

MC14049UBDTR2 TSSOP–16 2500/Tape & Reel

MC14049UBF SOEIAJ–16 See Note 1.

MC14049UBFEL SOEIAJ–16 See Note 1.

TSSOP–16

DT SUFFIX

CASE 948F

14

049U

ALYW

1

16

MC14049UB

http://onsemi.com

2

PIN ASSIGNMENT

13

14

15

16

9

10

11

125

4

3

2

1

8

7

6

OUT

E

NC

IN

F

OUT

F

NC

IN

D

OUT

D

IN

E

OUT

B

IN

A

OUT

A

V

DD

V

SS

IN

C

OUT

C

IN

B

NC = NO CONNECTION

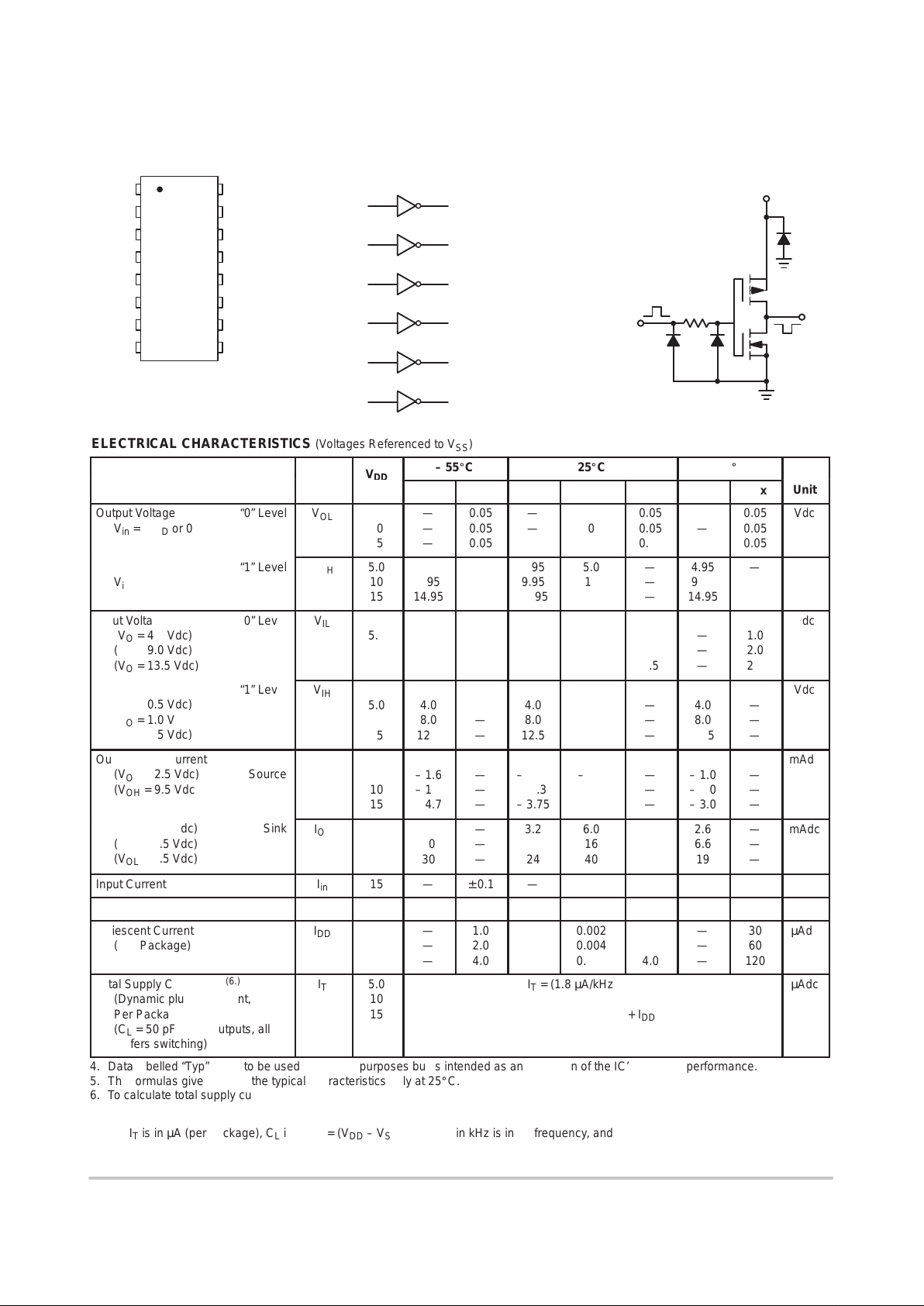

LOGIC DIAGRAM

MC14049UB

14 15

11

9

7

5

3

12

10

6

4

2

NC = PIN 13, 16

V

SS

= PIN 8

V

DD

= PIN 1

CIRCUIT SCHEMATIC

(1/6 OF CIRCUIT SHOWN)

V

DD

V

SS

MC14049UB

ELECTRICAL CHARACTERISTICS (Voltages Referenced to V

SS

)

V

– 55_C

25_C

125_C

Characteristic

Symbol

V

DD

Vdc

Min

Max

Min

Typ

(4.)

Max

Min

Max

Unit

ОООООООО

Î

Output Voltage “0” Level

V

in

= VDD or 0

ÎÎ

Î

V

OL

Î

Î

5.0

10

15

Î

Î

—

—

—

Î

Î

0.05

0.05

0.05

ÎÎ

Î

—

—

—

Î

Î

0

0

0

ÎÎ

Î

0.05

0.05

0.05

Î

Î

—

—

—

Î

Î

0.05

0.05

0.05

Î

Î

Vdc

ОООООООО

Î

“1” Level

V

in

= 0 or V

DD

ÎÎ

Î

V

OH

Î

Î

5.0

10

15

Î

Î

4.95

9.95

14.95

Î

Î

—

—

—

ÎÎ

Î

4.95

9.95

14.95

Î

Î

5.0

10

15

ÎÎ

Î

—

—

—

Î

Î

4.95

9.95

14.95

Î

Î

—

—

—

Î

Î

Vdc

ОООООООО

Î

ОООООООО

Î

Input Voltage “0” Level

(V

O

= 4.5 Vdc)

(V

O

= 9.0 Vdc)

(V

O

= 13.5 Vdc)

ÎÎ

Î

ÎÎ

Î

V

IL

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

1.0

2.0

2.5

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

2.25

4.50

6.75

ÎÎ

Î

ÎÎ

Î

1.0

2.0

2.5

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

1.0

2.0

2.5

Î

Î

Î

Î

Vdc

ОООООООО

Î

ОООООООО

Î

“1” Level

(V

O

= 0.5 Vdc)

(V

O

= 1.0 Vdc)

(V

O

= 1.5 Vdc)

ÎÎ

Î

ÎÎ

Î

V

IH

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

4.0

8.0

12.5

Î

Î

Î

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

4.0

8.0

12.5

Î

Î

Î

Î

2.75

5.50

8.25

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

4.0

8.0

12.5

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

Vdc

ОООООООО

Î

ОООООООО

Î

Output Drive Current

(V

OH

= 2.5 Vdc) Source

(V

OH

= 9.5 Vdc)

(V

OH

= 13.5 Vdc)

ÎÎ

Î

ÎÎ

Î

I

OH

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

– 1.6

– 1.6

– 4.7

Î

Î

Î

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

– 1.25

– 1.3

– 3.75

Î

Î

Î

Î

– 2.5

– 2.6

– 10

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

– 1.0

– 1.0

– 3.0

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

mAdc

ОООООООО

Î

ОООООООО

Î

(VOL = 0.4 Vdc) Sink

(V

OL

= 0.5 Vdc)

(V

OL

= 1.5 Vdc)

ÎÎ

Î

ÎÎ

Î

I

OL

Î

Î

Î

Î

5.0

10

15

Î

Î

Î

Î

3.75

10

30

Î

Î

Î

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

3.2

8.0

24

Î

Î

Î

Î

6.0

16

40

ÎÎ

Î

ÎÎ

Î

—

—

—

Î

Î

Î

Î

2.6

6.6

19

Î

Î

Î

Î

—

—

—

Î

Î

Î

Î

mAdc

Input Current

I

in

15

—

± 0.1

—

±0.00001

± 0.1

—

± 1.0

µAdc

Input Capacitance (Vin = 0)

C

in

—

—

—

—

10

20

—

—

pF

ОООООООО

Î

Quiescent Current

(Per Package)

ÎÎ

Î

I

DD

Î

Î

5.0

10

15

Î

Î

—

—

—

Î

Î

1.0

2.0

4.0

ÎÎ

Î

—

—

—

Î

Î

0.002

0.004

0.006

ÎÎ

Î

1.0

2.0

4.0

Î

Î

—

—

—

Î

Î

30

60

120

Î

Î

µAdc

ОООООООО

Î

ОООООООО

Î

ОООООООО

Î

Total Supply Current

(5.) (6.)

(Dynamic plus Quiescent,

Per Package)

(C

L

= 50 pF on all outputs, all

buffers switching)

ÎÎ

Î

ÎÎ

Î

ÎÎ

Î

I

T

Î

Î

Î

Î

Î

Î

5.0

10

15

ООООООООООООООО

Î

ООООООООООООООО

Î

ООООООООООООООО

Î

IT = (1.8 µA/kHz) f + I

DD

IT = (3.5 µA/kHz) f + I

DD

IT = (5.3 µA/kHz) f + I

DD

Î

Î

Î

Î

Î

Î

µAdc

4. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

5. The formulas given are for the typical characteristics only at 25_C.

6. To calculate total supply current at loads other than 50 pF:

I

T(CL

) = IT(50 pF) + (CL – 50) Vfk

where: I

T

is in µA (per package), CL in pF, V = (VDD – VSS) in volts, f in kHz is input frequency, and k = 0.002.

MC14049UB

http://onsemi.com

3

SWITCHING CHARACTERISTICS

(7.)

(C

L

= 50 pF, T

A

= 25_C)

ООООООООООООО

Î

Characteristic

ÎÎÎ

Î

Symbol

ÎÎ

Î

V

DD

Vdc

ÎÎ

Î

Min

ÎÎ

Î

Typ

(8.)

ÎÎ

Î

Max

Î

Î

Unit

ООООООООООООО

Î

Output Rise Time

t

TLH

= (0.8 ns/pF) CL + 60 ns

t

TLH

= (0.3 ns/pF) CL + 35 ns

t

TLH

= (0.27 ns/pF) CL + 26.5 ns

ÎÎÎ

Î

t

TLH

ÎÎ

Î

5.0

10

15

ÎÎ

Î

—

—

—

ÎÎ

Î

100

50

40

ÎÎ

Î

160

100

60

Î

Î

ns

ООООООООООООО

Î

ООООООООООООО

Î

Output Fall Time

t

THL

= (0.3 ns/pF) CL + 25 ns

t

THL

= (0.12 ns/pF) CL + 14 ns

t

THL

= (0.1 ns/pF) CL + 10 ns

ÎÎÎ

Î

ÎÎÎ

Î

t

THL

ÎÎ

Î

ÎÎ

Î

5.0

10

15

ÎÎ

Î

ÎÎ

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

40

20

15

ÎÎ

Î

ÎÎ

Î

60

40

30

Î

Î

Î

Î

ns

ООООООООООООО

Î

ООООООООООООО

Î

Propagation Delay Time

t

PLH

= (0.38 ns/pF) CL + 61 ns

t

PLH

= (0.20 ns/pF) CL + 30 ns

t

PLH

= (0.11 ns/pF) CL + 24.5 ns

ÎÎÎ

Î

ÎÎÎ

Î

t

PLH

ÎÎ

Î

ÎÎ

Î

5.0

10

15

ÎÎ

Î

ÎÎ

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

80

40

30

ÎÎ

Î

ÎÎ

Î

120

65

50

Î

Î

Î

Î

ns

ООООООООООООО

Î

ООООООООООООО

Î

Propagation Delay Time

t

PHL

= (0.38 ns/pF) CL + 11 ns

t

PHL

= (0.12 ns/PF) CL + 9 ns

t

PHL

= (0.11 ns/pF) CL + 4.5 ns

ÎÎÎ

Î

ÎÎÎ

Î

t

PHL

ÎÎ

Î

ÎÎ

Î

5.0

10

15

ÎÎ

Î

ÎÎ

Î

—

—

—

ÎÎ

Î

ÎÎ

Î

30

15

10

ÎÎ

Î

ÎÎ

Î

60

30

20

Î

Î

Î

Î

ns

7. The formulas given are for the typical characteristics only at 25_C.

8. Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

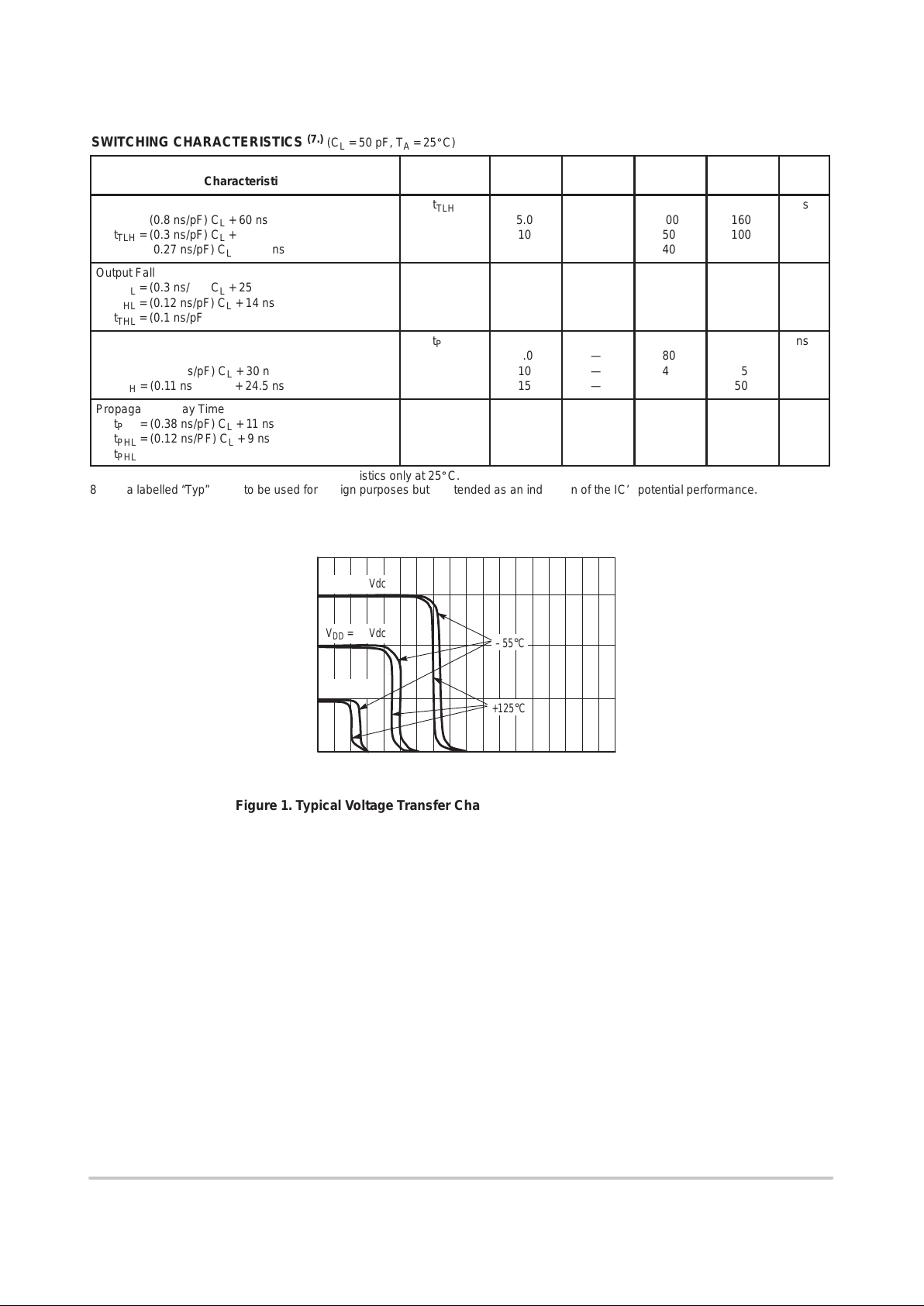

Figure 1. Typical Voltage Transfer Characteristics versus Temperature

V

out

, OUTPUT VOLTAGE (Vdc)

18

15

10

5

1815105

V

in

, INPUT VOLTAGE (Vdc)

VDD = 5 Vdc

VDD = 15 Vdc

–55°C

+125°C

VDD = 10 Vdc

Loading...

Loading...