MOTOROLA MC10H161MEL, MC10H161ML1, MC10H161ML2, MC10H161MR1, MC10H161M Datasheet

...

SEMICONDUCTOR TECHNICAL DATA

2–249

REV 5

Motorola, Inc. 1996

3/93

The MC10H161 provides parallel decoding of a three bit binary word to one

of eight lines. The MC10H161 is useful in high–speed multiplexer/demultiplexer

applications.

The MC10H161 is designed to decode a three bit input word to one of eight

output lines. The MC10H161 output will be low when selected while all other

output are high. The enable inputs, when either or both are high, force all

outputs high.

The MC10H161 is a true parallel decoder. This eliminates unequal parallel

path delay times found in other decoder designs. These devices are ideally

suited for multiplexer/demultiplexer applications.

• Propagation Delay, 1.0 ns Typical

• Power Dissipation, 315 mW Typical (same as MECL 10K)

• Improved Noise Margin 150 mV (Over Operating Voltage and

Temperature Range)

• Voltage Compensated

• MECL 10K–Compatible

MAXIMUM RATINGS

Characteristic Symbol Rating Unit

Power Supply (VCC = 0) V

EE

–8.0 to 0 Vdc

Input Voltage (VCC = 0) V

I

0 to V

EE

Vdc

Output Current— Continuous

— Surge

I

out

50

100

mA

Operating Temperature Range T

A

0 to +75 °C

Storage Temperature Range— Plastic

— Ceramic

T

stg

–55 to +150

–55 to +165

°C

°C

ELECTRICAL CHARACTERISTICS (VEE = –5.2 V ±5%) (See Note)

0° 25° 75°

Characteristic Symbol Min Max Min Max Min Max Unit

Power Supply Current I

E

— 84 — 76 — 84 mA

Input Current High I

inH

— 465 — 275 — 275 µA

Input Current Low I

inL

0.5 — 0.5 — 0.3 — µA

High Output Voltage V

OH

–1.02 –0.84 –0.98 –0.81 –0.92 –0.735 Vdc

Low Output Voltage V

OL

–1.95 –1.63 –1.95 –1.63 –1.95 –1.60 Vdc

High Input Voltage V

IH

–1.17 –0.84 –1.13 –0.81 –1.07 –0.735 Vdc

Low Input Voltage V

IL

–1.95 –1.48 –1.95 –1.48 –1.95 –1.45 Vdc

AC PARAMETERS

Propagation Delay

Data

Enable

t

pd

0.6

0.8

2.0

2.3

0.65

0.8

2.1

2.4

0.7

0.9

2.2

2.5

ns

Rise Time t

r

0.55 1.7 0.65 1.8 0.7 1.9 ns

Fall Time t

f

0.55 1.7 0.65 1.8 0.7 1.9 ns

NOTE:

Each MECL 10H series circuit has been designed to meet the dc specifications shown in the test table,

after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit

board and transverse air flow greater than 500 Iinear fpm is maintained. Outputs are terminated through

a 50–ohm resistor to –2.0 volts.

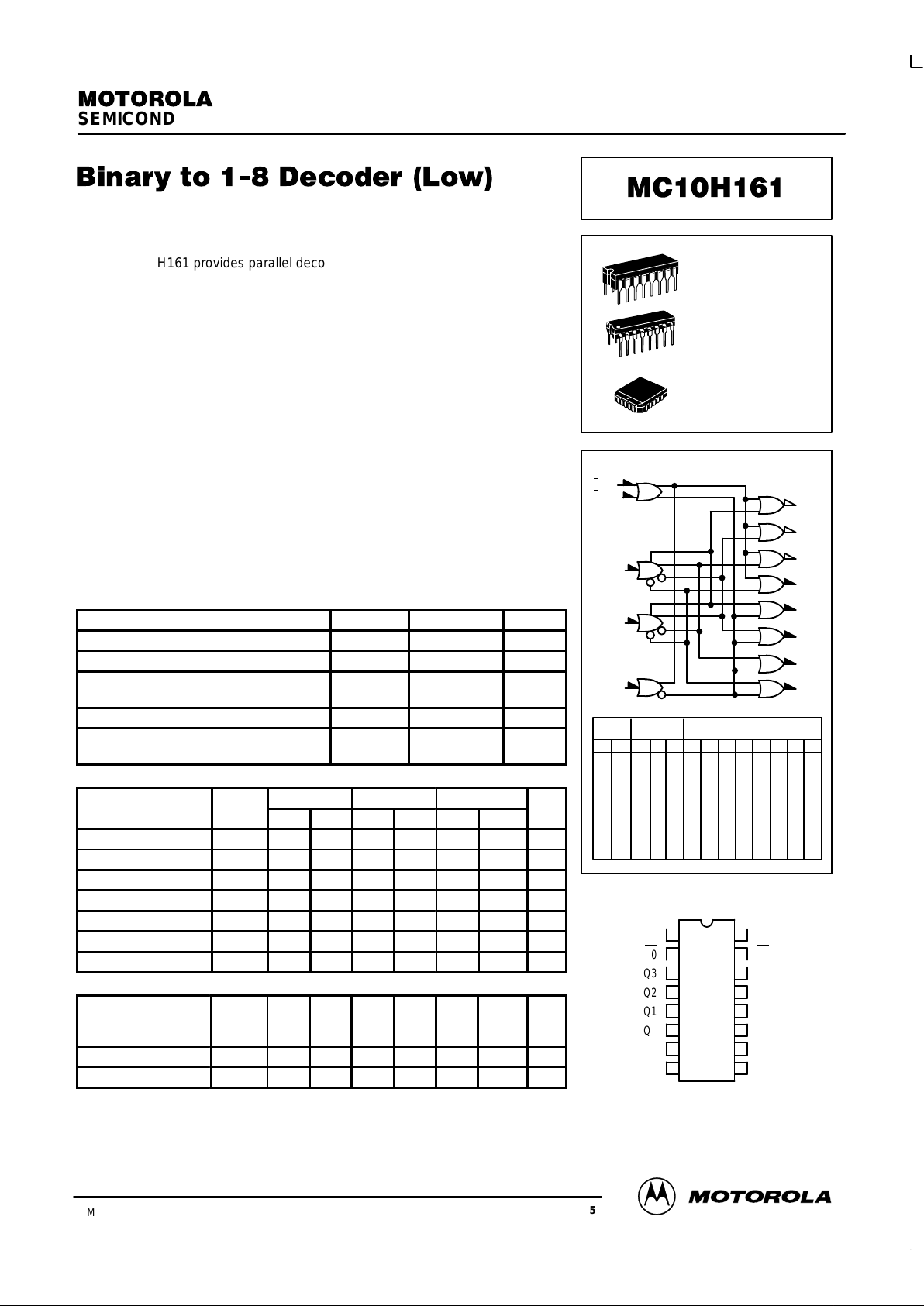

LOGIC DIAGRAM

DIP

PIN ASSIGNMENT

V

CC1

E0

Q3

Q2

Q1

Q0

A

V

EE

V

CC2

E1

C

Q4

Q5

Q6

Q7

B

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

V

CC1

= Pin 1

V

CC2

= Pin 16

VEE= Pin 8

E02

E115

A7

B9

C14

6Q0

5Q1

4Q2

3Q3

13 Q4

12 Q5

11 Q6

10 Q7

H

H

H

H

L

H

H

H

H

H

L

L

L

L

L

L

L

L

X

H

TRUTH TABLE

ENABLE

INPUTS

INPUTS OUTPUTS

L

L

L

L

L

L

L

L

H

X

L

L

L

L

H

H

H

H

X

X

L

L

H

H

L

L

H

H

X

X

L

H

L

H

L

H

L

H

X

X

L

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

L

H

H

H

H

H

H

H

H

H

H

L

H

H

Q4E0E1 C B A Q0 Q1 Q2 Q3 Q5 Q6 Q7

L SUFFIX

CERAMIC PACKAGE

CASE 620–10

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

FN SUFFIX

PLCC

CASE 775–02

Pin assignment is for Dual–in–Line Package.

For PLCC pin assignment, see the Pin Conversion

T ables on page 6–11 of the Motorola MECL Data

Book (DL122/D).

MC10H161

MOTOROLA MECL Data

DL122 — Rev 6

2–250

D

out

D

out

D

out

D

out

D

out

D

out

ABC

E

MC10H164

ABC

E

MC10H164

D

out

ABC

E

MC10H164

ABC

E

MC10H164

ABC

E

MC10H164

ABC

E

MC10H164

ABC

E

MC10H164

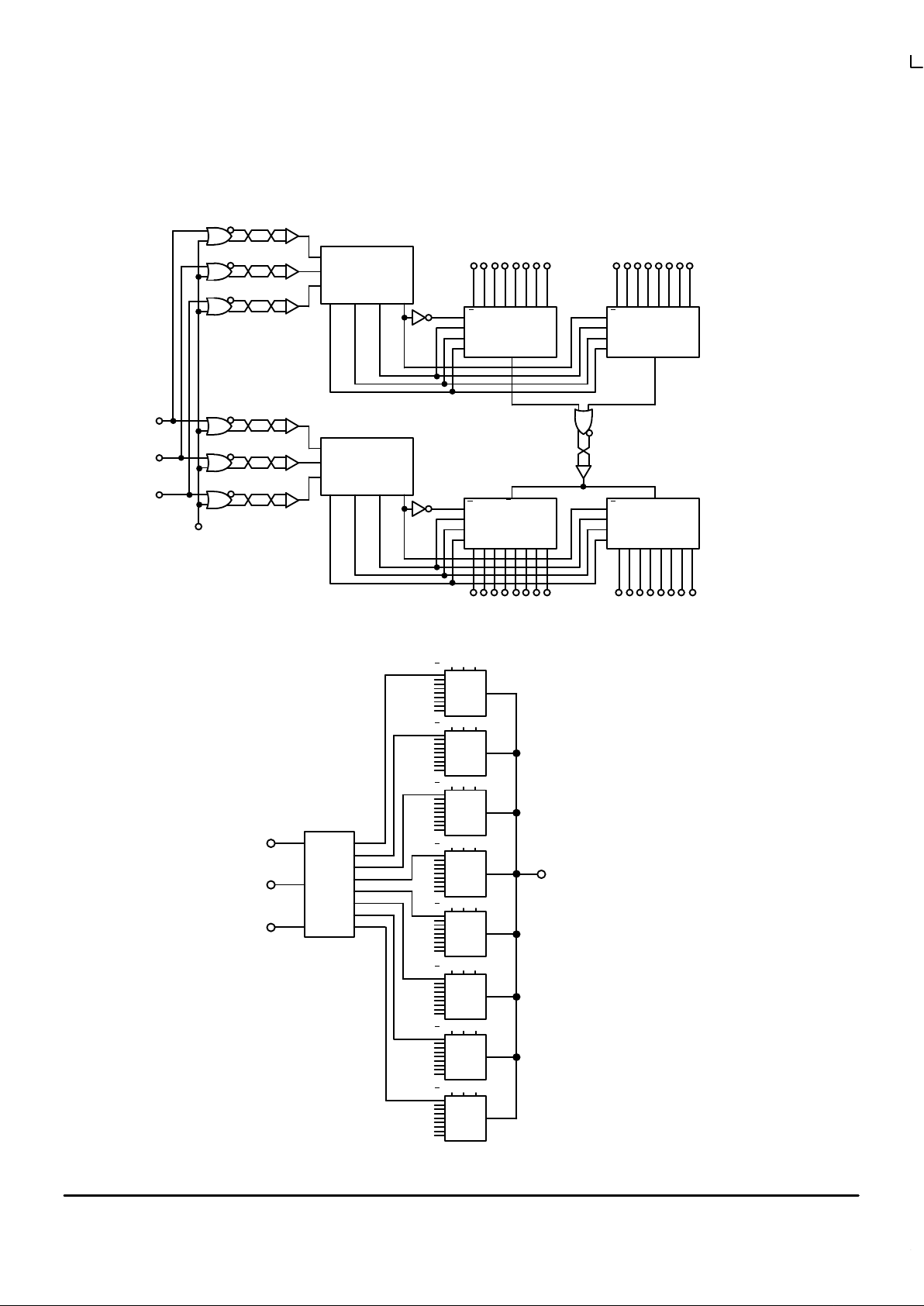

FIGURE 2 — 1–OF–64 LINE MULTIPLEXER

FIGURE 1 — HIGH SPEED 16–BIT MULTIPLEXER/DEMULTIPLEXER

TYPICAL APPLICATIONS

The Bit chosen is dependent on six–bit

code present on inputs 7, 9, 14 of the

MC10H161 and the A, B, C inputs of the

MC10H164.

MC10H161

D

out

ABC

MSB

LSB

Q7

Q6

Q5

Q4

Q3

Q2

Q1

Q0

14

9

7

E

MC10H164

MC10H161

E1

C

B

A

MC10H136

MC10H161

S0

S1

C

R

ABCD

E

1

C

B

A

E

0

MC10H164

765432

1

0

E

1

C

B

A

D0

Control Selection

MC10H136

MC10H164

S0

S1

C

R

ABCD

15 14 13 12 11 10 9 8

76543210

E1

C

B

A

D0

Start/Stop

S0

15 141312 11 10 9 8

E0

S1

C

R

Loading...

Loading...