Freescale Semiconductor, Inc.

M68HC11E Family

nc...

I

Data Sheet

cale Semiconductor,

Frees

M68HC11

Microcontrollers

MOTOROLA.COM/SEMICONDUCTORS

M68HC11E/D

Rev. 5

6/2003

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

MC68HC11E Family

Data Sheet

nc...

I

cale Semiconductor,

Frees

To provide the most up-to-date information, the revision of our documents on the

World Wide Web will be the most current. Your printed copy may be an earlier

revision. To verify you have the latest information available, refer to:

http://www.motorola.com/semiconductors/

The following revision history table summarizes changes contained in this

document. For your convenience, the page number designators have been linked

to the appropriate location.

Motorola and the Stylized M Logo are registered trademarks of Motorola, Inc.

DigitalDNA is a trademark of Motorola, Inc. © Motorola, Inc., 2003

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA 3

For More Information On This Product,

Go to: www.freescale.com

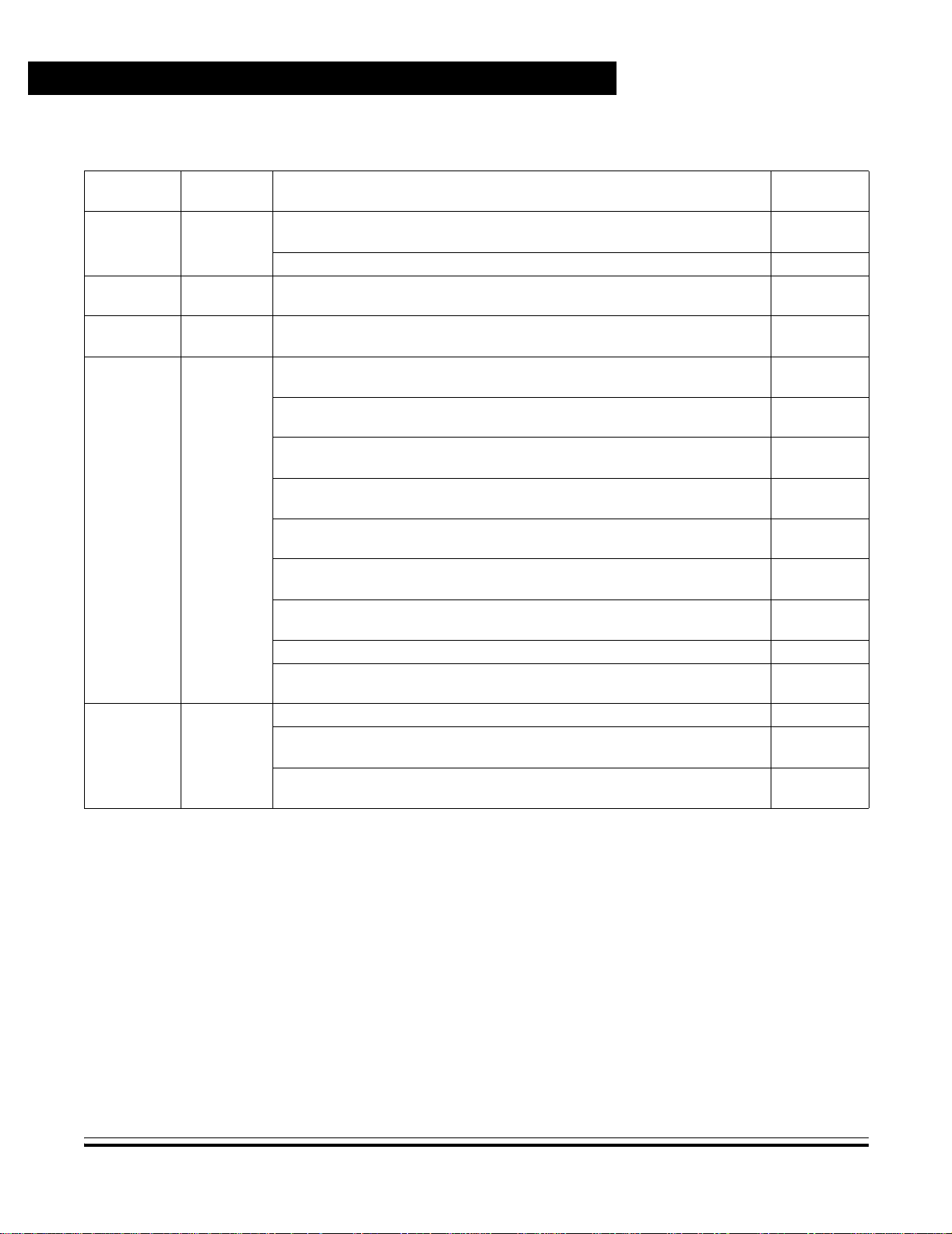

Revision History

Freescale Semiconductor, Inc.

Revision History

Date

May, 2001 3.1

June, 2001 3.2

December,

2001

nc...

I

July, 2002 4

June, 2003 5

cale Semiconductor,

Revision

Level

3.3

Description

2.3.3.1 System Configuration Register — Addition to NOCOP bit

description

Added 10.21 EPROM Characteristics 191

10.21 EPROM Characteristics — For clarity, addition to note 2 following the

table

7.7.2 Serial Communications Control Register 1 — SCCR1 bit 4 (M)

description corrected

10.7 MC68L11E9/E20 DC Electrical Characteristics — Title changed to

include the MC68L11E20

10.8 MC68L11E9/E20 Supply Currents and Power Dissipation — Title

changed to include the MC68L11E20

10.10 MC68L11E9/E20 Control Timing — Title changed to include the

MC68L11E20

10.12 MC68L11E9/E20 Peripheral Port Timing — Title changed to include

the MC68L11E20

10.14 MC68L11E9/E20 Analog-to-Digital Converter Characteristics —

Title changed to include the MC68L11E20

10.16 MC68L11E9/E20 Expansion Bus Timing Characteristics — Title

changed to include the MC68L11E20

10.18 MC68L11E9/E20 Serial Peirpheral Interface Characteristics — Title

changed to include the MC68L11E20

— Title changed to include the MC68L11E20 191

11.4 Extended Voltage Device Ordering Information (3.0 Vdc to 5.5 Vdc)

— Updated table to include MC68L1120

Format updated to current publications standards Throughout

1.4.6 Non-Maskable Interrupt (XIRQ/VPPE) — Added Caution note

pertaining to EPROM programming of the MC68HC711E9 device only.

10.21 EPROM Characteristics — Added note pertaining to EPROM

programming of the MC68HC711E9 device only.

Page

Number(s)

49

191

123

169

170

173

179

183

185

188

197

26

191

Frees

Data Sheet M68HC11E Family — Rev. 5

4 Revision History MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Data Sheet — M68HC11E Family

Section 1. General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Section 2. Operating Modes and On-Chip Memory. . . . . . . . . . . . . . .33

Section 3. Analog-to-Digital (A/D) Converter . . . . . . . . . . . . . . . . . . . .63

List of Sections

nc...

I

cale Semiconductor,

Frees

Section 4. Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . .73

Section 5. Resets and Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .89

Section 6. Parallel Input/Output (I/O) Ports . . . . . . . . . . . . . . . . . . . .109

Section 7. Serial Communications Interface (SCI). . . . . . . . . . . . . . .117

Section 8. Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . .133

Section 9. Timing System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141

Section 10. Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . .165

Section 11. Ordering Information

and Mechanical Specifications . . . . . . . . . . . . . . . . . . .193

Appendix A. Development Support. . . . . . . . . . . . . . . . . . . . . . . . . . .203

Appendix B. EVBU Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . .209

EB184 — Enabling the Security Feature

on the MC68HC711E9 Devices with PCbug11

on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .255

EB188 — Enabling the Security Feature

on M68HC811E2 Devices with PCbug11

on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .259

EB296 — Programming MC68HC711E9 Devices

with PCbug11 and the M68HC11EVBU . . . . . . . . . . . . . . . . . . . . .263

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA List of Sections 5

For More Information On This Product,

Go to: www.freescale.com

List of Sections

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Data Sheet M68HC11E Family — Rev. 5

6 List of Sections MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

nc...

I

cale Semiconductor,

Frees

Freescale Semiconductor, Inc.

Technical Data — M68HC11E Family

Section 1. General Description

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

1.3 Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

1.4 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.4.1 V

1.4.2 RESET

1.4.3 Crystal Driver and External Clock Input

1.4.4 E-Clock Output (E) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.4.5 Interrupt Request (IRQ

1.4.6 Non-Maskable Interrupt (XIRQ

1.4.7 MODA and MODB (MODA/LIR

1.4.7.1 V

1.4.8 STRA/AS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

1.4.9 STRB/R/W

1.4.10 Port Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.4.10.1 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

1.4.10.2 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.4.10.3 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

1.4.10.4 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

1.4.10.5 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

2.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.1 Single-Chip Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.2 Expanded Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.2.3 Test Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.2.4 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.1 RAM and Input/Output Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.3.2 Mode Selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

and VSS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

DD

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

(XTAL and EXTAL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

and VRH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

RL

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Section 2. Operating Modes and On-Chip Memory

Table of Contents

) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

/V

). . . . . . . . . . . . . . . . . . . . . . . . 26

PPE

and MODB/V

) . . . . . . . . . . . . . 26

STBY

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA Table of Contents 7

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

2.3.3 System Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.3.3.1 System Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.3.3.2 RAM and I/O Mapping Register . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.3.3.3 System Configuration Options Register . . . . . . . . . . . . . . . . . . . . 51

2.4 EPROM/OTPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

2.4.1 Programming an Individual EPROM Address. . . . . . . . . . . . . . . . . . 53

2.4.2 Programming the EPROM with Downloaded Data. . . . . . . . . . . . . . 54

2.4.3 EPROM and EEPROM Programming Control Register . . . . . . . . . . 54

2.5 EEPROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.5.1 EEPROM and CONFIG Programming and Erasure. . . . . . . . . . . . . 57

2.5.1.1 Block Protect Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.5.1.2 EPROM and EEPROM Programming Control Register . . . . . . . . 58

2.5.1.3 EEPROM Bulk Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

2.5.1.4 EEPROM Row Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

2.5.1.5 EEPROM Byte Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2.5.1.6 CONFIG Register Programming . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2.5.2 EEPROM Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

cale Semiconductor,

Frees

Section 3. Analog-to-Digital (A/D) Converter

3.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.2 Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.2.1 Multiplexer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3.2.2 Analog Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.2.3 Digital Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.2.4 Result Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.2.5 A/D Converter Clocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

3.2.6 Conversion Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

3.3 A/D Converter Power-Up and Clock Select . . . . . . . . . . . . . . . . . . . . . . 66

3.4 Conversion Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.5 Channel Assignments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

3.6 Single-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.7 Multiple-Channel Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

3.8 Operation in Stop and Wait Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.9 A/D Control/Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

3.10 A/D Converter Result Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Section 4. Central Processor Unit (CPU)

4.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.2 CPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.2.1 Accumulators A, B, and D. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

4.2.2 Index Register X (IX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.2.3 Index Register Y (IY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Data Sheet M68HC11E Family — Rev. 5

8 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

4.2.4 Stack Pointer (SP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.2.5 Program Counter (PC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4.2.6 Condition Code Register (CCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.1 Carry/Borrow (C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.2 Overflow (V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.3 Zero (Z) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.4 Negative (N) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.5 Interrupt Mask (I). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

4.2.6.6 Half Carry (H) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.2.6.7 X Interrupt Mask (X) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.2.6.8 STOP Disable (S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.3 Data Types. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.4 Opcodes and Operands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Table of Contents

nc...

I

cale Semiconductor,

Frees

4.5 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.5.1 Immediate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.5.2 Direct . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.5.3 Extended. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.5.4 Indexed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.5.5 Inherent. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.5.6 Relative. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.6 Instruction Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Section 5. Resets and Interrupts

5.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.2 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.2.1 Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.2.2 External Reset (RESET

5.2.3 Computer Operating Properly (COP) Reset. . . . . . . . . . . . . . . . . . . 90

5.2.4 Clock Monitor Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.2.5 System Configuration Options Register . . . . . . . . . . . . . . . . . . . . . . 92

5.2.6 Configuration Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.3 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.3.1 Central Processor Unit (CPU). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.3.2 Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.3.3 Timer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.3.4 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.3.5 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.3.6 Computer Operating Properly (COP) . . . . . . . . . . . . . . . . . . . . . . . . 95

5.3.7 Serial Communications Interface (SCI) . . . . . . . . . . . . . . . . . . . . . . 95

5.3.8 Serial Peripheral Interface (SPI). . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.3.9 Analog-to-Digital (A/D) Converter. . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.3.10 System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.4 Reset and Interrupt Priority. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.4.1 Highest Priority Interrupt and Miscellaneous Register . . . . . . . . . . . 97

). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA Table of Contents 9

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

5.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.5.1 Interrupt Recognition and Register Stacking . . . . . . . . . . . . . . . . . 100

5.5.2 Non-Maskable Interrupt Request (XIRQ

5.5.3 Illegal Opcode Trap . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.5.4 Software Interrupt (SWI). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.5.5 Maskable Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.5.6 Reset and Interrupt Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.6 Low-Power Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.6.1 Wait Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

5.6.2 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

) . . . . . . . . . . . . . . . . . . . . 100

Section 6. Parallel Input/Output (I/O) Ports

6.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.2 Port A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.3 Port B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

cale Semiconductor,

Frees

6.4 Port C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

6.5 Port D . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

6.6 Port E . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

6.7 Handshake Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

6.8 Parallel I/O Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Section 7. Serial Communications Interface (SCI)

7.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.2 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.3 Transmit Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

7.4 Receive Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.5 Wakeup Feature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.5.1 Idle-Line Wakeup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.5.2 Address-Mark Wakeup. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

7.6 SCI Error Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

7.7 SCI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

7.7.1 Serial Communications Data Register . . . . . . . . . . . . . . . . . . . . . . 122

7.7.2 Serial Communications Control Register 1. . . . . . . . . . . . . . . . . . . 123

7.7.3 Serial Communications Control Register 2. . . . . . . . . . . . . . . . . . . 124

7.7.4 Serial Communication Status Register. . . . . . . . . . . . . . . . . . . . . . 125

7.7.5 Baud Rate Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

7.8 Status Flags and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

7.9 Receiver Flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Data Sheet M68HC11E Family — Rev. 5

10 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Table of Contents

Section 8. Serial Peripheral Interface (SPI)

8.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

8.3 SPI Transfer Formats. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

8.4 Clock Phase and Polarity Controls. . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

8.5 SPI Signals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

8.5.1 Master In/Slave Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

8.5.2 Master Out/Slave In . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

8.5.3 Serial Clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

8.5.4 Slave Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

8.6 SPI System Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

8.7 SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

nc...

I

8.7.1 Serial Peripheral Control Register . . . . . . . . . . . . . . . . . . . . . . . . . 138

8.7.2 Serial Peripheral Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . 139

8.7.3 Serial Peripheral Data I/O Register . . . . . . . . . . . . . . . . . . . . . . . . 140

cale Semiconductor,

Frees

Section 9. Timing System

9.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141

9.2 Timer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

9.3 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

9.3.1 Timer Control Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

9.3.2 Timer Input Capture Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146

9.3.3 Timer Input Capture 4/Output Compare 5 Register . . . . . . . . . . . . 148

9.4 Output Compare. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

9.4.1 Timer Output Compare Registers. . . . . . . . . . . . . . . . . . . . . . . . . . 149

9.4.2 Timer Compare Force Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

9.4.3 Output Compare Mask Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 152

9.4.4 Output Compare Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

9.4.5 Timer Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

9.4.6 Timer Control Register 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

9.4.7 Timer Interrupt Mask 1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 154

9.4.8 Timer Interrupt Flag 1 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

9.4.9 Timer Interrupt Mask 2 Register. . . . . . . . . . . . . . . . . . . . . . . . . . . 155

9.4.10 Timer Interrupt Flag Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

9.5 Real-Time Interrupt (RTI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

9.5.1 Timer Interrupt Mask Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . 157

9.5.2 Timer Interrupt Flag Register 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

9.5.3 Pulse Accumulator Control Register. . . . . . . . . . . . . . . . . . . . . . . . 159

9.6 Computer Operating Properly (COP) Watchdog Function . . . . . . . . . . 159

9.7 Pulse Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

9.7.1 Pulse Accumulator Control Register. . . . . . . . . . . . . . . . . . . . . . . . 161

9.7.2 Pulse Accumulator Count Register. . . . . . . . . . . . . . . . . . . . . . . . . 162

9.7.3 Pulse Accumulator Status and Interrupt Bits . . . . . . . . . . . . . . . . . 162

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA Table of Contents 11

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

Section 10. Electrical Characteristics

10.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

10.2 Maximum Ratings for Standard

and Extended Voltage Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

10.3 Functional Operating Range. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

10.4 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

10.5 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

10.6 Supply Currents and Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . 168

10.7 MC68L11E9/E20 DC Electrical Characteristics . . . . . . . . . . . . . . . . . . 169

10.8 MC68L11E9/E20 Supply Currents

and Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

10.9 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

10.10 MC68L11E9/E20 Control Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

cale Semiconductor,

Frees

10.11 Peripheral Port Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

10.12 MC68L11E9/E20 Peripheral Port Timing . . . . . . . . . . . . . . . . . . . . . . . 179

10.13 Analog-to-Digital Converter Characteristics . . . . . . . . . . . . . . . . . . . . . 182

10.14 MC68L11E9/E20 Analog-to-Digital

Converter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

10.15 Expansion Bus Timing Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . 184

10.16 MC68L11E9/E20 Expansion Bus Timing Characteristics. . . . . . . . . . . 185

10.17 Serial Peripheral Interface Timing Characteristics . . . . . . . . . . . . . . . . 187

10.18 MC68L11E9/E20 Serial Peripheral Interface Characteristics. . . . . . . . 188

10.19 EEPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

10.20 MC68L11E9/E20 EEPROM Characteristics. . . . . . . . . . . . . . . . . . . . . 191

10.21 EPROM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

Section 11. Ordering Information

and Mechanical Specifications

11.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

11.2 Standard Device Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . 193

11.3 Custom ROM Device Ordering Information . . . . . . . . . . . . . . . . . . . . . 196

11.4 Extended Voltage Device Ordering Information

(3.0 Vdc to 5.5 Vdc). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

11.5 52-Pin Plastic-Leaded Chip Carrier (Case 778). . . . . . . . . . . . . . . . . . 198

11.6 52-Pin Windowed Ceramic-Leaded Chip Carrier

(Case 778B) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

11.7 64-Pin Quad Flat Pack (Case 840C) . . . . . . . . . . . . . . . . . . . . . . . . . . 200

11.8 52-Pin Thin Quad Flat Pack (Case 848D) . . . . . . . . . . . . . . . . . . . . . . 201

Data Sheet M68HC11E Family — Rev. 5

12 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

11.9 56-Pin Dual in-Line Package (Case 859). . . . . . . . . . . . . . . . . . . . . . . 202

11.10 48-Pin Plastic DIP (Case 767) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 202

Table of Contents

Appendix A. Development Support

A.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

A.2 Motorola M68HC11 E-Series Development Tools . . . . . . . . . . . . . . . . 203

A.3 EVS — Evaluation System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 204

A.4 Motorola Modular Development System (MMDS11) . . . . . . . . . . . . . . 204

A.5 SPGMR11 — Serial Programmer for M68HC11 MCUs . . . . . . . . . . . . 206

Appendix B. EVBU Schematic

MC68HC11EVBU Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

nc...

I

AN1060

cale Semiconductor,

Frees

AN1060 — M68HC11 Bootstrap Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 209

EB184

EB184 — Enabling the Security Feature on the MC68HC711E9

Devices with PCbug11 on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . 255

EB188

EB188 — Enabling the Security Feature on M68HC811E2

Devices with PCbug11 on the M68HC711E9PGMR . . . . . . . . . . . . . . . . . 259

EB296

EB296 — Programming MC68HC711E9 Devices

with PCbug11 and the M68HC11EVBU . . . . . . . . . . . . . . . . . . . . . . . . . . . 263

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA Table of Contents 13

For More Information On This Product,

Go to: www.freescale.com

Table of Contents

nc...

I

Freescale Semiconductor, Inc.

cale Semiconductor,

Frees

Data Sheet M68HC11E Family — Rev. 5

14 Table of Contents MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Data Sheet — M68HC11E Family

Section 1. General Description

1.1 Introduction

This document contains a detailed description of the M68HC11 E series of 8-bit

microcontroller units (MCUs). These MCUs all combine the M68HC11 central

processor unit (CPU) with high-performance, on-chip peripherals.

The E series is comprised of many devices with various configurations of:

nc...

I

• Random-access memory (RAM)

• Read-only memory (ROM)

cale Semiconductor,

Frees

1.2 Features

• Erasable programmable read-only memory (EPROM)

• Electrically erasable programmable read-only memory (EEPROM)

• Several low-voltage devices are also available.

With the exception of a few minor differences, the operation of all E-series MCUs

is identical. A fully static design and high-density complementary metal-oxide

semiconductor (HCMOS) fabrication process allow the E-series devices to operate

at frequencies from 3 MHz to dc with very low power consumption.

Features of the E-series devices include:

• M68HC11 CPU

• Power-saving stop and wait modes

• Low-voltage devices available (3.0–5.5 Vdc)

• 0, 256, 512, or 768 bytes of on-chip RAM, data retained during standby

• 0, 12, or 20 Kbytes of on-chip ROM or EPROM

• 0, 512, or 2048 bytes of on-chip EEPROM with block protect for security

• 2048 bytes of EEPROM with selectable base address in the MC68HC811E2

• Asynchronous non-return-to-zero (NRZ) serial communications interface

(SCI)

• Additional baud rates available on MC68HC(7)11E20

• Synchronous serial peripheral interface (SPI)

• 8-channel, 8-bit analog-to-digital (A/D) converter

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 15

For More Information On This Product,

Go to: www.freescale.com

General Description

• 16-bit timer system:

• 8-bit pulse accumulator

• Real-time interrupt circuit

• Computer operating properly (COP) watchdog system

• 38 general-purpose input/output (I/O) pins:

Freescale Semiconductor, Inc.

– Three input capture (IC) channels

– Four output compare (OC) channels

– One additional channel, selectable as fourth IC or fifth OC

– 16 bidirectional I/O pins

– 11 input-only pins

– 11 output-only pins

nc...

I

cale Semiconductor,

Frees

1.3 Structure

• Several packaging options:

– 52-pin plastic-leaded chip carrier (PLCC)

– 52-pin windowed ceramic leaded chip carrier (CLCC)

– 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

– 64-pin quad flat pack (QFP)

– 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

– 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

See Figure 1-1 for a functional diagram of the E-series MCUs. Differen ces among

devices are noted in the table accompanying Figure 1-1.

Data Sheet M68HC11E Family — Rev. 5

16 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

MODA/

LIR

MODB/

V

STBY

Freescale Semiconductor, Inc.

XTAL EXTAL E IRQ XIRQ/V

PPE*

RESET

General Description

Structure

nc...

I

cale Semiconductor,

Frees

MODE CONTROL

TIMER

SYSTEM

COPPULSE ACCUMULATOR

OC2

OC3

OC4

OC5/IC4/OC1

IC1

PAI

PORT A

PA7/PAI

PA6/OC2/OC1

PA5/OC3/OC1

* V

applies only to devices with EPROM/OTPROM.

PPE

IC2

PA2/IC1

PA1/IC2

PA4/OC4/OC1

PA3/OC5/IC4/OC1

OSC

CLOCK LOGIC

PERIODIC INTERRUPT

BUS EXPANSION

ADDRESS

IC3

PORT B

PA0/IC3

PB7/ADDR15

PB6/ADDR14

M68HC11 CPU

ADDRESS/DATA

STROBE AND HANDSHAKE

PARALLEL I/O

PB1/ADDR9

PB5/ADDR13

PB4/ADDR12

PB0/ADDR8

PB3/ADDR11

PB2/ADDR10

PC7/ADDR7/DATA7

INTERRUPT

CONTROL

PORT C

PC6/ADDR6/DATA6

PC5/ADDR5/DATA5

PC4/ADDR4/DATA4

LOGIC

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

PC1/ADDR1/DATA1

R/W

STRB

STRB/R/W

PC0/ADDR0/DATA0

SERIAL

PERIPHERAL

AS

INTERFACE

STRA

STRA/AS

DEVICE

MC68HC11E0

MC68HC11E1

MC68HC11E9

MC68HC711E9

MC68HC11E20

MC68HC711E20

SPI

SCK

SS

CONTROL

PD5/SS

PORT D

PD4/SCK

ROM OR EPROM

(SEE TABLE)

EEPROM

(SEE TABLE)

RAM

(SEE TABLE)

COMMUNICATION

INTERFACE

MOSI

MISO

TxD

RxD

PD1/TxD

PD2/MISO

PD0/RxD

ROM

—

—

12 K

—

20 K

—

PD3/MOSI

RAM

512

512

512

512

768

768

256 — — 2048MC68HC811E2

SERIAL

SCI

A/D CONVERTER

PORT E

PE7/AN7

PE6/AN6

EPROM

—

—

—

12 K

—

20 K

PE5/AN5

PE4/AN4

PE3/AN3

EEPROM

PE2/AN2

—

512

512

512

512

512

V

DD

V

SS

V

RH

V

RL

PE1/AN1

PE0/AN0

Figure 1-1. M68HC11 E-Series Block Diagram

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 17

For More Information On This Product,

Go to: www.freescale.com

General Description

1.4 Pin Descriptions

nc...

I

Freescale Semiconductor, Inc.

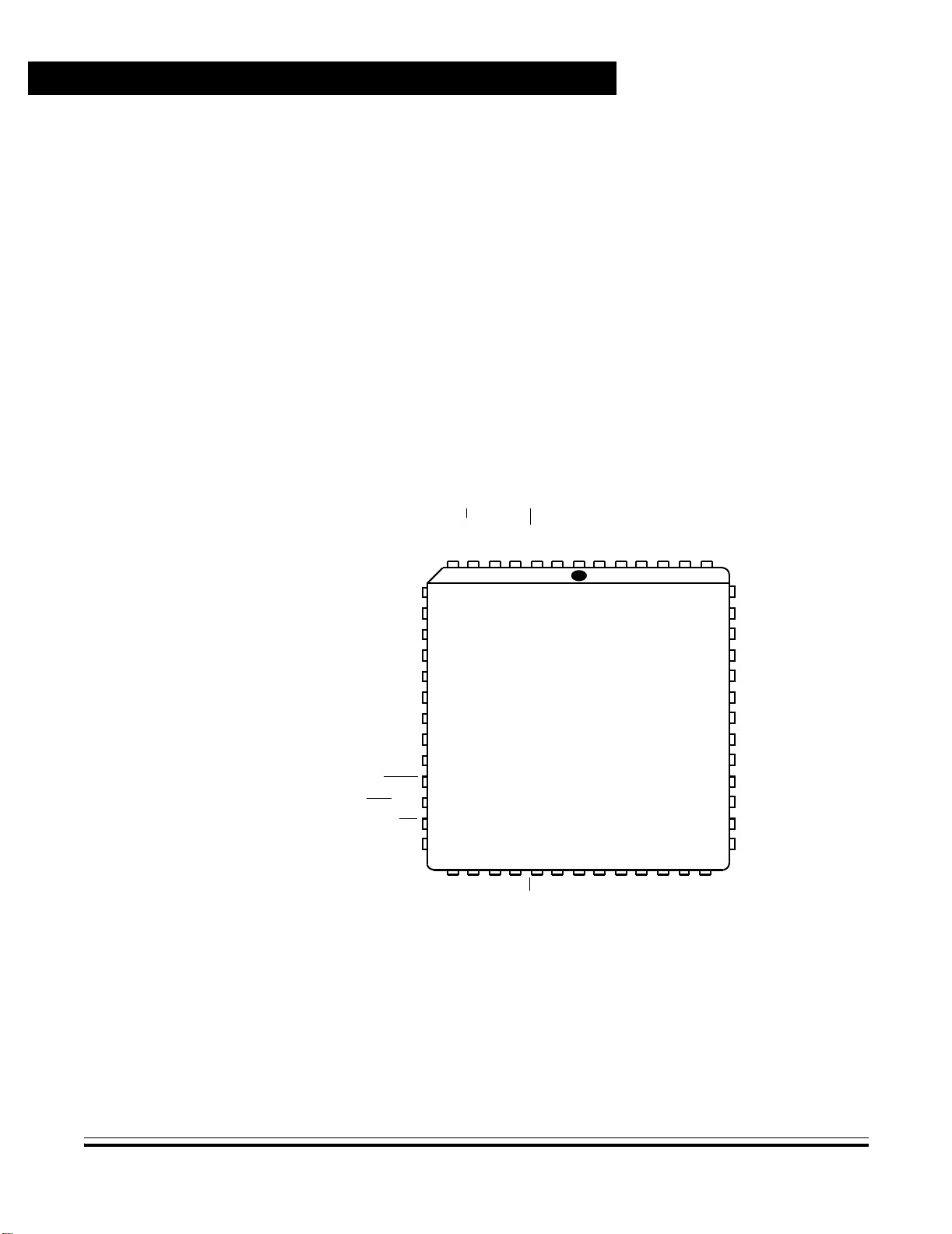

M68HC11 E-series MCUs are available packaged in:

• 52-pin plastic-leaded chip carrier (PLCC)

• 52-pin windowed ceramic leaded chip carrier (CLCC)

• 52-pin plastic thin quad flat pack, 10 mm x 10 mm (TQFP)

• 64-pin quad flat pack (QFP)

• 48-pin plastic dual in-line package (DIP), MC68HC811E2 only

• 56-pin plastic shrink dual in-line package, .070-inch lead spacing (SDIP)

Most pins on these MCUs serve two or more functions, as described in the

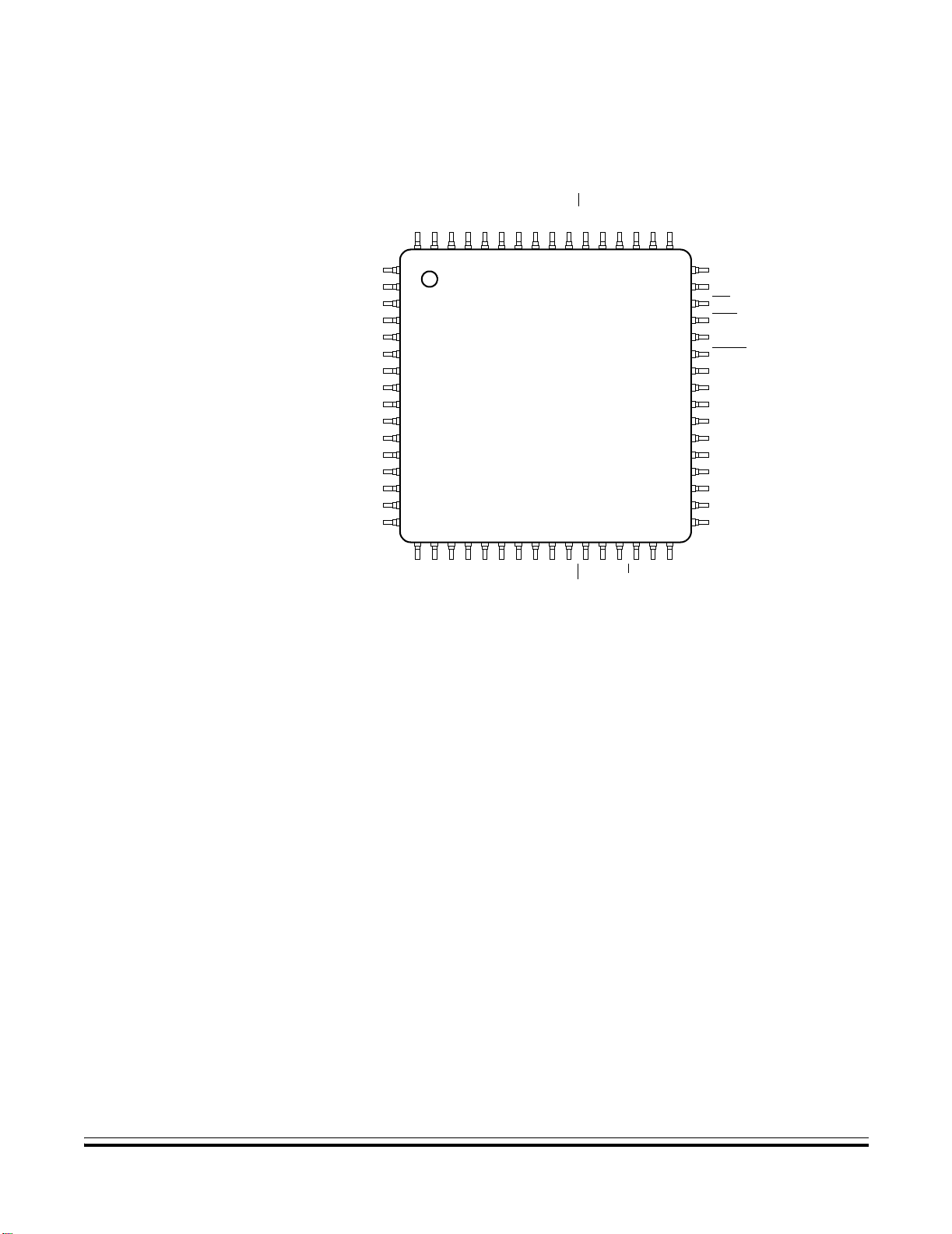

following paragraphs. Refer to Figure 1-2, Figure 1-3, Figure 1-4, Figure 1-5, and

Figure 1-6 which show the M68HC11 E-series pin assignments for the

PLCC/CLCC, QFP, TQFP, SDIP, and DIP packages.

cale Semiconductor,

Frees

EXTAL

STRB/R/WESTRA/AS

7

6

5

4

XTAL

8

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ/V

PD0/RxD

* V

applies only to devices with EPROM/OTPROM.

PPE

PPE

IRQ

9

10

11

12

13

14

15

16

17

18

19

20

2122232425

PD1/TxD

PD2/MISO

M68HC11 E SERIES

PD4/SCK

PD3/MOSI

STBY

MODA/LIR

MODB/V

VSSVRHVRLPE7/AN7

312

26

2728293031

DD

V

PD5/SS

PA7/PAI/OC1

52

51

50

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PE3/AN3

PE6/AN648PE2/AN2

49

PA2/IC132PA1/IC2

PA3/OC5/IC4/OC1

47

45

44

43

42

41

40

39

38

37

36

35

34

33

PE5/AN546

PE1/AN1

PE4/AN4

PE0/AN0

PB0/ADDR8

PB1/ADDR9

PB2/ADDR10

PB3/ADDR11

PB4/ADDR12

PB5/ADDR13

PB6/ADDR14

PB7/ADDR15

PA0/IC3

Figure 1-2. Pin Assignments for 52-Pin PLCC and CLCC

Data Sheet M68HC11E Family — Rev. 5

18 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

General Description

Pin Descriptions

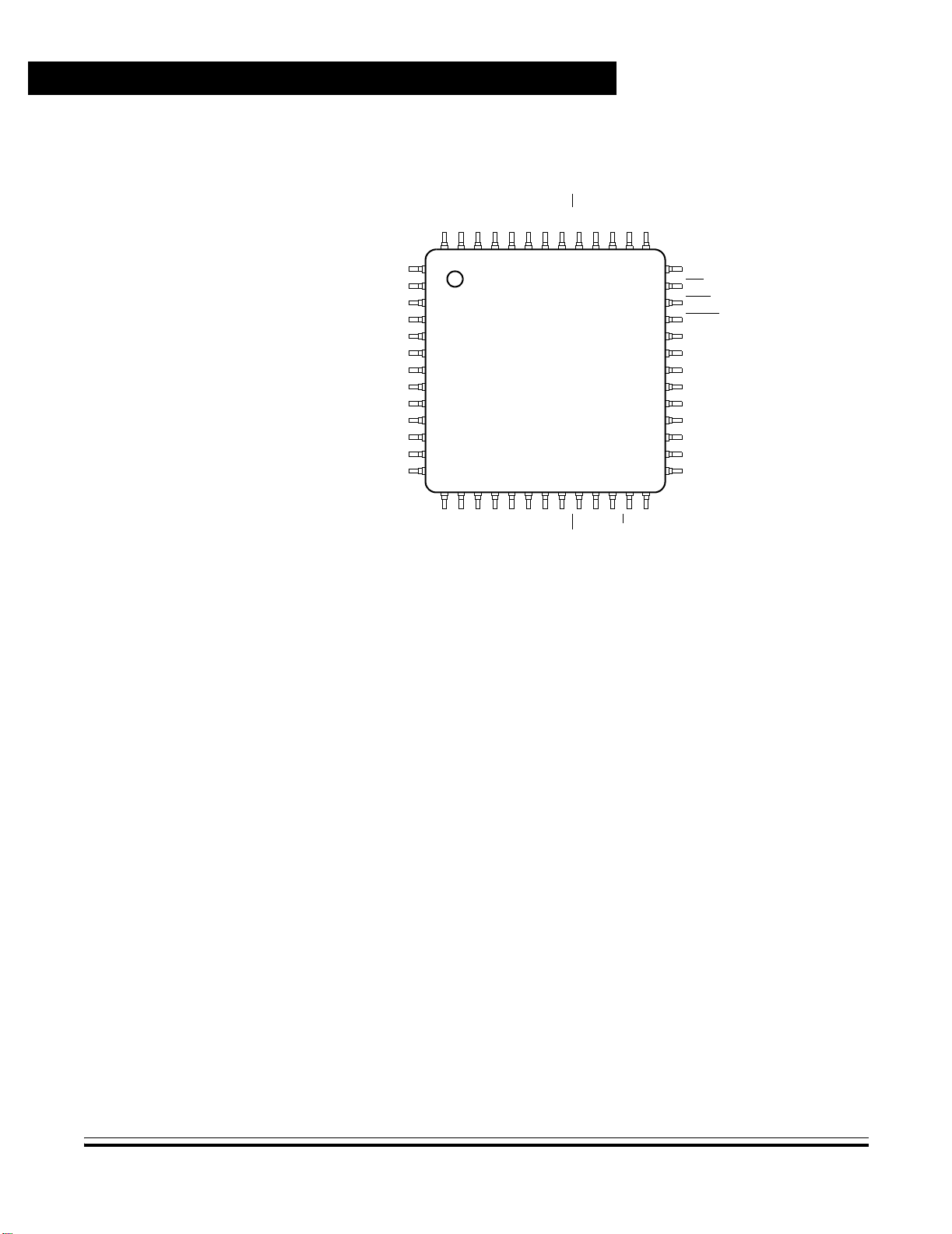

PA1/IC2

PA2/IC1

PA3/OC5/IC4/OC1NCNC

64

63626160595857

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

nc...

I

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

1. V

PPE

1

NC

2

NC

3

NC

4

5

6

7

8

9

10

11

12

13

14

15

16

17181920212223

PE2/AN2

PE6/AN6

PE3/AN3

applies only to devices with EPROM/OTPROM.

PA4/OC4/OC1

PA5/OC3/OC1

PA6/OC2/OC1

PA7/PAI/OC1

56

M68HC11 E SERIES

25

24

PE7/AN7

RL

V

SS

RH

VSSV

V

STBY

MODB/V

PD5/SS

VDDPD4/SCK

55

26

NC

PD3/MOSI

5352515049

54

2829303132

27

E

STRA/AS

MODA/LIR

Figure 1-3. Pin Assignments for 64-Pin QFP

cale Semiconductor,

SS

PD2/MISO

PD1/TxD

V

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

NC

EXTAL

STRB/R/W

NC

PD0/RxD

IRQ

XIRQ/V

NC

RESET

PC7/ADDR7/DATA7

PC6/ADDR6/DATA6

PC5/ADDR5/DATA5

PC4/ADDR4/DATA4

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

PC1/ADDR1/DATA1

NC

PC0/ADDR0/DATA0

XTAL

PPE

(1)

Frees

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 19

For More Information On This Product,

Go to: www.freescale.com

General Description

nc...

I

Freescale Semiconductor, Inc.

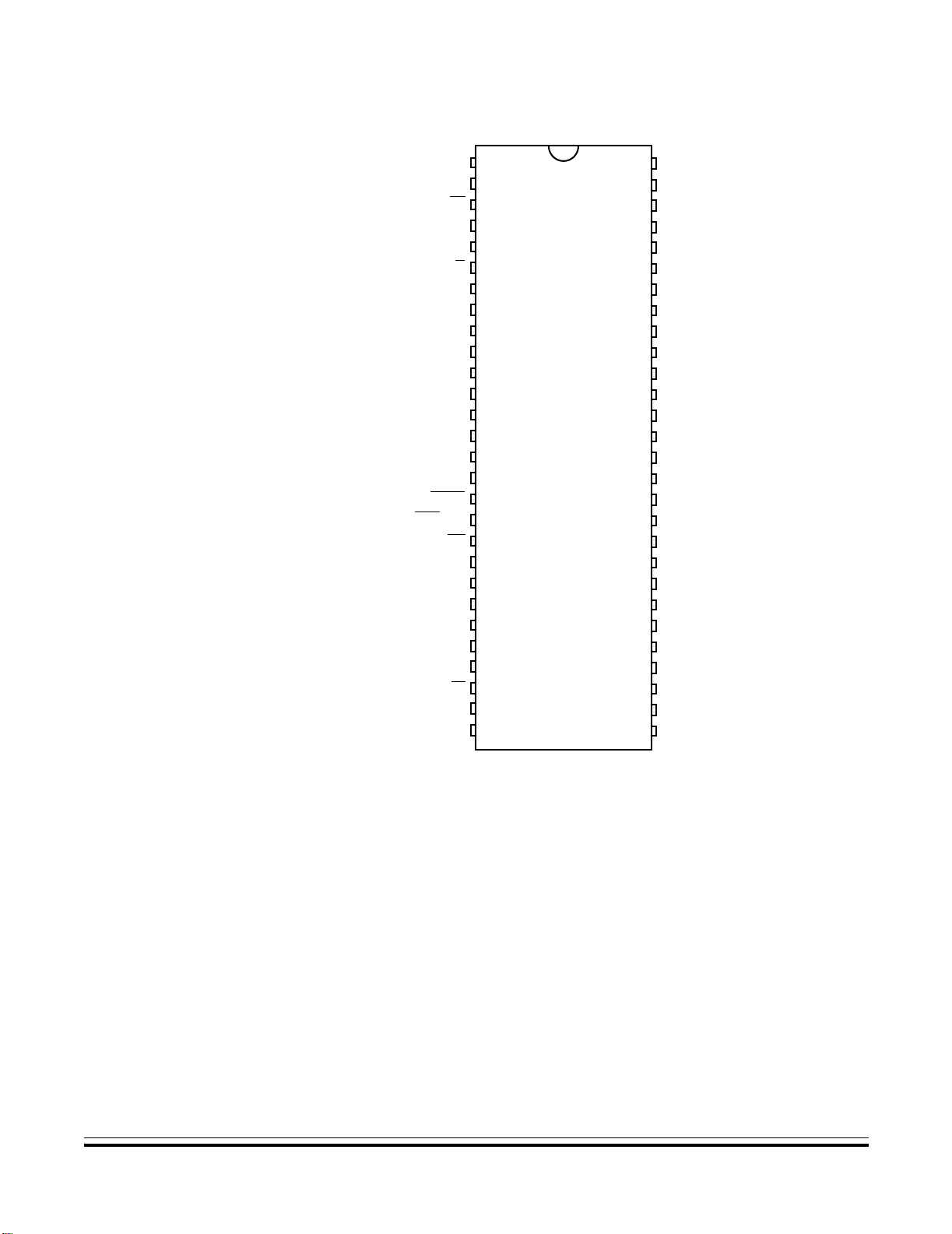

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE4/AN4

PE1/AN1

PE5/AN5

PA1/IC2

PA2/IC1

PA3/OC5/IC4/OC1

PA4/OC4/OC1

PA5/OC3/OC1

PA6/OC2/OC1

PA7/PAI/OC1

52

51504948474645

1

2

3

4

5

6

7

8

9

10

11

12

13

M68HC11 E SERIES

1415161718192021222423

PD5/SS

VDDPD4/SCK

44

PD3/MOSI

PD2/MISO

PD1/TxD

42

43

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

25

26

PD0/RxD

IRQ

XIRQ/V

RESET

PC7/ADDR7/DATA7

PC6/ADDR6/DATA6

PC5/ADDR5/DATA5

PC4/ADDR4/DATA4

PC3/ADDR3/DATA3

PC2/ADDR2/DATA2

PC1/ADDR1/DATA1

PC0/ADDR0/DATA0

XTAL

PPE

(1)

cale Semiconductor,

Frees

RL

SS

RH

V

V

V

PE2/AN2

PE6/AN6

PE3/AN3

PE7/AN7

1. V

applies only to devices with EPROM/OTPROM.

PPE

STBY

MODB/V

E

STRA/AS

MODA/LIR

EXTAL

STRB/R/W

Figure 1-4. Pin Assignments for 52-Pin TQFP

Data Sheet M68HC11E Family — Rev. 5

20 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

General Description

Pin Descriptions

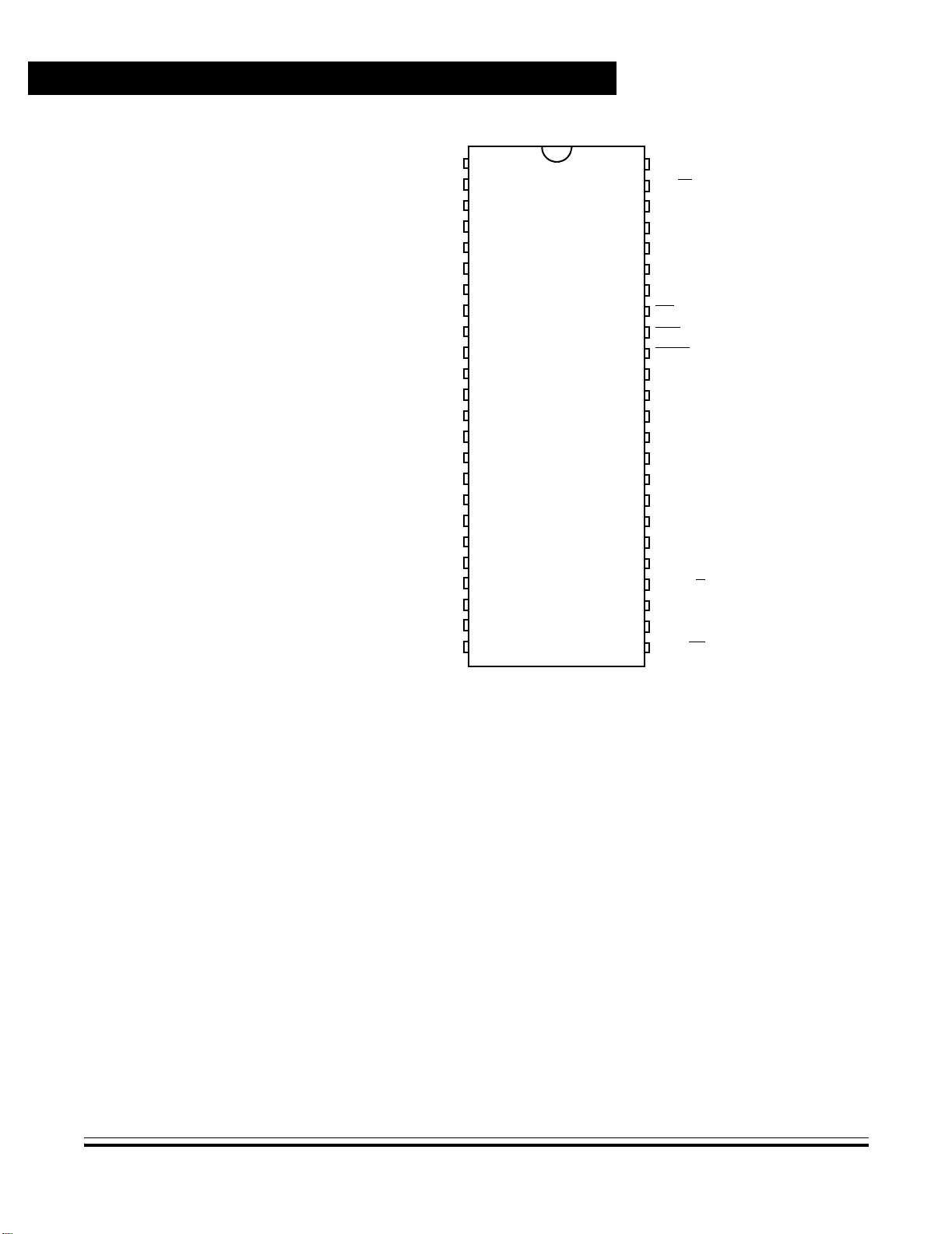

V

SS

STBY

EXTAL

XTAL

PPE

IRQ

EV

SS

V

DD

V

SS

1

2

3

4

E

5

6

7

8

9

10

11

12

13

14

15

M68HC11 E SERIES

16

17

18

19

20

21

22

23

24

25

26

27

28

MODB/V

MODA/LIR

STRA/AS

STRB/R/W

PC0/ADDR0/DATA0

PC1/ADDR1/DATA1

PC2/ADDR2/DATA2

PC3/ADDR3/DATA3

PC4/ADDR4/DATA4

nc...

I

cale Semiconductor,

PC5/ADDR5/DATA5

PC6/ADDR6/DATA6

PC7/ADDR7/DATA7

RESET

* XIRQ/V

PD0/RxD

PD1/TxD

PD2/MISO

PD3/MOSI

PD4/SCK

PD5/SS

* V

applies only to devices with EPROM/OTPROM.

PPE

Figure 1-5. Pin Assignments for 56-Pin SDIP

EV

56

SS

V

RH

55

V

54

RL

PE7/AN7

53

PE3/AN3

52

PE6/AN6

51

PE2/AN2

50

PE5/AN5

49

PE1/AN1

48

PE4/AN4

47

PE0/AN0

46

PB0/ADDR8

45

PB1/ADDR9

44

PB2/ADDR10

43

PB3/ADDR11

42

PB4/ADDR12

41

PB5/ADDR13

40

PB6/ADDR14

39

PB7/ADDR15

38

PA0/IC3

37

PA1/IC2

36

PA2/IC1

35

PA3/OC5/IC4/OC1

34

PA4/OC4/OC1

33

PA5/OC3/OC1

32

PA6/OC2/OC1

31

PA7/PAI/OC1

30

EV

29

DD

Frees

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 21

For More Information On This Product,

Go to: www.freescale.com

General Description

Freescale Semiconductor, Inc.

PA7/PAI/OC1

PA6/OC2/OC1

PA5/OC3/OC1

PA4/OC4/OC1

PA3/OC5/IC4/OC1

PA2/IC1

PA1/IC2

PA0/IC3

PB7/ADDR15

PB6/ADDR14

PB5/ADDR13

PB4/ADDR12

PB3/ADDR11

nc...

I

PB2/ADDR10

PB1/ADDR9

PB0/ADDR8

PE0/AN0

PE1/AN1

PE2/AN2

PE3/AN3

MODB/V

V

V

V

STBY

1

2

3

4

5

6

7

8

9

10

11

MC68HC811E2

12

13

14

15

16

17

18

19

20

21

RL

22

RH

23

SS

24

Figure 1-6. Pin Assignments for 48-Pin DIP (MC68HC811E2)

cale Semiconductor,

V

48

DD

PD5/SS

47

PD4/SCK46

PD3/MOSI

45

PD2/MISO44

PD1/TxD

43

PD0/RxD42

IRQ

41

XIRQ

40

RESET

39

PC7/ADDR7/DATA7

38

PC6/ADDR6/DATA6

37

PC5/ADDR5/DATA5

36

PC4/ADDR4/DATA4

35

PC3/ADDR3/DATA3

34

PC2/ADDR2/DATA2

33

PC1/ADDR1/DATA1

32

PC0/ADDR0/DATA0

31

XTAL

30

EXTAL

29

STRB/R/W

28

E27

STRA/AS26

25

MODA/LIR

Frees

Data Sheet M68HC11E Family — Rev. 5

22 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

1.4.1 VDD and VSS

Freescale Semiconductor, Inc.

General Description

Pin Descriptions

nc...

I

cale Semiconductor,

Frees

Power is supplied to the MCU through V

and VSS. VDD is the power supply, VSS

DD

is ground. The MCU operates from a single 5-volt (nominal) power supply.

Low-voltage devices in the E series operate at 3.0–5.5 volts.

Very fast signal transitions occur on the MCU pins. The short rise and fall times

place high, short duration current demands on the power supply. To prevent noise

problems, provide good power supply bypassing at the MCU. Also, use bypass

capacitors that have good

high-frequency characteristics and situate them as close to the MCU as possible.

Bypass requirements vary, depending on how heavily the MCU pins are loaded.

V

DD

2

IN

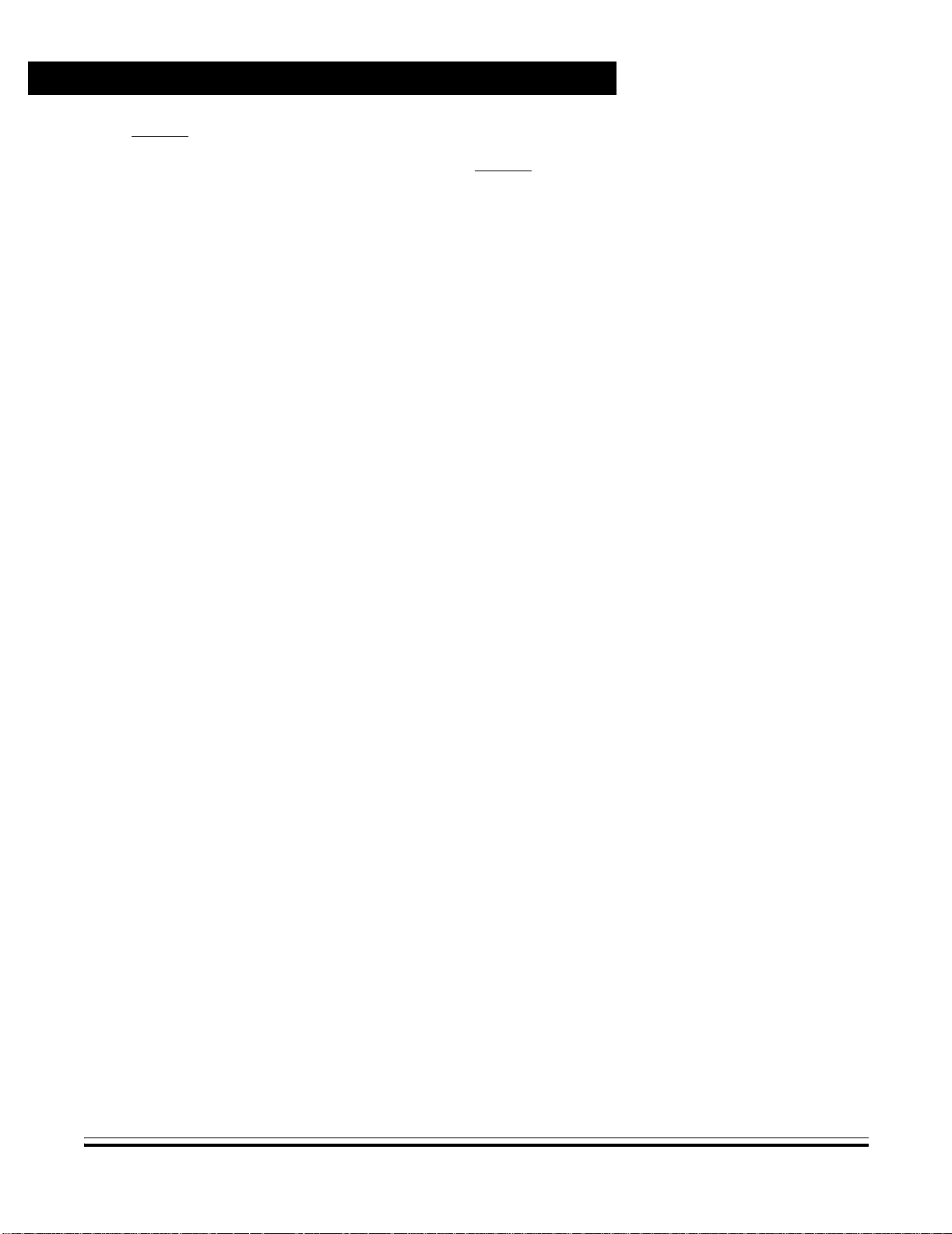

RESET

MC34(0/1)64

GND

3

V

DD

4.7 kΩ

1

TO RESET

OF M68HC11

Figure 1-7. External Reset Circuit

MANUAL

RESET SWITCH

4.7 kΩ

V

DD

IN

RESET

V

DD

4.7 kΩ

MC34064

GND

V

DD

4.7 kΩ

TO RESET

OF M68HC11

1.0 µF

IN

RESET

MC34164

GND

OPTIONAL POWER-ON DELAY AND MANUAL RESET SWITCH

Figure 1-8. External Reset Circuit with Delay

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 23

For More Information On This Product,

Go to: www.freescale.com

General Description

1.4.2 RESET

Freescale Semiconductor, Inc.

A bidirectional control signal, RESET

known startup state. It also acts as an open-drain output to indicate that an internal

failure has been detected in either the clock monitor or computer operating prop erly

(COP) watchdog circuit. The CPU distinguishes between internal and external

reset conditions by sensing whether the reset pin rises to a logic 1 in less than t wo

E-clock cycles after a reset has occurred. See Figure 1-7 and Figure 1-8.

, acts as an input to initialize the MCU to a

CAUTION: Do not connect an external resistor capacitor (RC) power-up delay circuit to the

reset pin of M68HC11 devices because the circuit charge time constant can cause

the device to misinterpret the type of reset that occurred.

Because the CPU is not able to fetch and execute instructions properly when V

falls below the minimum operating voltage level, reset must be controlled. A

nc...

I

cale Semiconductor,

low-voltage inhibit (LVI) circuit is required primarily for protection of EEPROM

contents. However, since the configuration register (CONFIG) value is read from

the EEPROM, protection is required even if the EEPROM array is not being used.

Presently, there are several economical ways to solve this problem. For example,

two good external components for LVI reset are:

1. The Seiko S0854HN (or other S805 series devices):

a. Extremely low power (2 µA)

a. TO-92 package

a. Limited temperature range, –20°C to +70°C

a. Available in various trip-point voltage ranges

2. The Motorola MC34064:

a. TO-92 or SO-8 package

a. Draws about 300 µA

a. Temperature range –40°C to 85°C

a. Well controlled trip point

a. Inexpensive

DD

Frees

Refer to Section 5. Resets and Interrupts for further information.

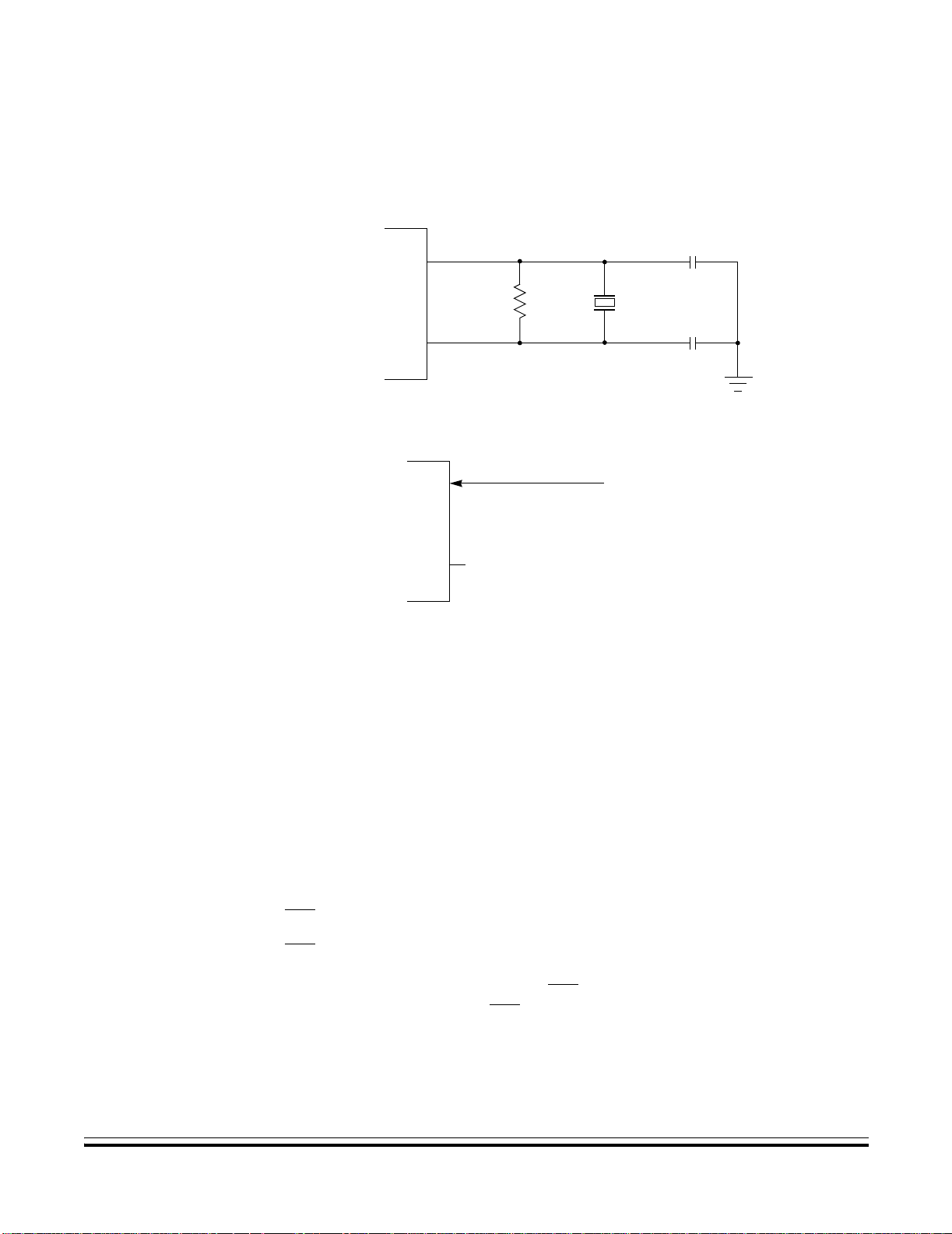

1.4.3 Crystal Driver and External Clock Input (XTAL and EXTAL)

These two pins provide the interface for either a crystal or a CMOS- compatible

clock to control the internal clock generator circuitry. The frequency applied to

these pins is four times higher than the desired E-clock rate.

The XTAL pin must be left unterminated when an external CMOS- compatible clock

input is connected to the EXTAL pin. The XTAL output is normally intended to drive

only a crystal. Refer to Figure 1-9 and Figure 1-10.

Data Sheet M68HC11E Family — Rev. 5

24 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

General Description

Pin Descriptions

CAUTION: In all cases, use caution around the oscillator pins. Load capacitances shown in the

oscillator circuit are specified by the crystal manufacturer and should include all

stray layout capacitances.

C

EXTAL

L

nc...

I

cale Semiconductor,

Frees

1.4.4 E-Clock Output (E)

E is the output connection for the internally generated E clock. The signal from E

is used as a timing reference. The frequency of the E-clock outpu t is one fourth that

of the input frequency at the XTAL and EXTAL pins. When E-clock output is low,

an internal process is taking place. When it is high, data is being accessed.

All clocks, including the E clock, are halted when the MCU is in stop mode. To

reduce RFI emissions, the E-clock output of most E-series devices can be disabled

while operating in single-chip modes.

The E-clock signal is always enabled on the MC68HC811E2.

MCU

XTAL

Figure 1-9. Common Parallel Resonant Crystal Connections

EXTAL

MCU

XTAL

Figure 1-10. External Oscillator Connections

NC

10 MΩ

4 x E

CRYSTAL

C

L

4 x E

CMOS-COMPATIBLE

EXTERNAL OSCILLATOR

1.4.5 Interrupt Request (IRQ

The IRQ

MCU. Either negative edge-sensitive triggering or level-sensitive triggering is

program selectable (OPTION register). IRQ

triggering at reset. When using IRQ

connect an external pullup resistor, typically 4.7 kΩ, to V

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 25

)

input provides a means of applying asynchronous interrupt requests to the

is always configured to level-sensitive

in a level-sensitive wired-OR configuration,

.

DD

For More Information On This Product,

Go to: www.freescale.com

General Description

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

1.4.6 Non-Maskable Interrupt (XIRQ/V

The XIRQ

reset initialization. During reset, the X bit in the condition code register (CCR) is set

and any interrupt is masked until MCU software enables it. Because the XIRQ

is level-sensitive, it can be connected to a multiple-source wired-OR network with

an external pullup resistor to V

interrupt.

Whenever XIRQ

drive the interrupt input with an open-drain type of driver to avoid contention

between outputs.

NOTE: IRQ

source of IRQ

There should be a single pullup resistor near the MCU interrupt input pin (typically

4.7 kΩ). There must also be an interlock mechanism at each interrupt source so

that the source holds the interrupt line low until the MCU recognizes and

acknowledges the interrupt request. If one or more interrupt sources are still

pending after the MCU services a request, the interrupt line will still be held low and

the MCU will be interrupted again as soon as the interrupt mask bit in the MCU is

cleared (normally upon return from an interrupt). Refer to Section 5. Resets and

Interrupts.

V

PPE

EPROM/OTPROM programming. On devices without EPROM/OTPROM, this pin

is only an XIRQ

input provides a means of requesting a non-maskable interrupt after

or IRQ is used with multiple interrupt sources each source must

must be configured for level-sensitive operation if there is more than one

interrupt.

is the input for the 12-volt nominal programming voltage required for

input.

CAUTION: During EPROM programming of the MC68HC711E9 device, the V

may latch-up and be damaged if the input current is not limited to 10 mA. For mo re

information please refer to MC68HC711E9 8-Bit Microcontroller Unit Mask Set

Errata 3 (Motorola document order number 68HC711E9MSE3.

1.4.7 MODA and MODB (MODA/LIR

During reset, MODA and MODB select one of the four operating modes:

• Single-chip mode

• Expanded mode

• Test mode

• Bootstrap mode

and MODB/V

PPE

)

input

. XIRQ is often used as a power loss detect

DD

STBY

pin circuitry

PPE

)

Refer to Section 2. Operating Modes and On-Chip Memory.

After the operating mode has been selected, the load instru ction register (LIR

provides an open-drain output to indicate that execution of an instruction has

begun. A series of E-clock cycles occurs during execution of each instruction. The

signal goes low during the first E-clock cycle of each instruction (opcode fetch).

LIR

This output is provided for assistance in program debugging.

Data Sheet M68HC11E Family — Rev. 5

26 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

) pin

Freescale Semiconductor, Inc.

General Description

Pin Descriptions

The V

When the voltage on this pin is more than one MOS threshold (about 0.7 volts)

above the V

from this signal rather than the V

without V

removed and must remain low until V

1.4.7.1 V

nc...

I

1.4.8 STRA/AS

cale Semiconductor,

1.4.9 STRB/R/W

and VRH

RL

These two inputs provide the reference voltages for the analog-to-digital (A/D)

converter circuitry:

•V

•V

For proper A/D converter operation:

•V

•V

The strobe A (STRA) and address strobe (AS) pin performs either o f two separate

functions, depending on the operating mode:

• In single-chip mode, STRA performs an input handshake (strobe input)

• In the expand ed multiplexed mode, AS provides an address strobe function.

AS can be used to demultiplex the address and data signals at port C. Refer to

Section 2. Operating Modes and On-Chip Memory.

The strobe B (STRB) and read/write (R/W

a data bus direction indicator, depending on the operating mode.

pin is used to input random-access memory (RAM) standby power.

STBY

voltage, the internal RAM and part of the reset logic are powered

DD

input. This allows RAM contents to be retained

DD

power applied to the MCU. Reset must be driven low before VDD is

DD

has been restored to a valid level.

DD

is the low reference, typically 0 Vdc.

RL

is the high reference.

RH

should be at least 3 Vdc greater than VRL.

RH

and VRH should be between VSS and VDD.

RL

function.

) pin act as either an output strobe or as

Frees

In single-chip operating mode, STRB acts as a programmable strobe for

handshake with other parallel devices. Refer to Section 6. Parallel Input/Output

(I/O) Ports for further information.

In expanded multiplexed operating mode, R/W

transfers on the external data bus. A low on the R/W

written to the external data bus. A high on this pin indicates that a read cycle is in

progress. R/W

double-byte store. It is possible for data to be driven out of port C, if internal read

visibility (IRV) is enabled and an internal address is read, even though R/W

high-impedance state. Refer to Section 2. Operating Modes and On-Chip

Memory for more information about IRVNE (internal read visibility not E).

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 27

stays low during consecutive data bus write cycles, such as a

For More Information On This Product,

Go to: www.freescale.com

is used to indicate the direction of

pin indicates data is being

is in a

General Description

1.4.10 Port Signals

nc...

I

1.4.10.1 Port A

Freescale Semiconductor, Inc.

Port pins have different functions in different operating modes. Pin functions for

port A, port D, and port E are independent of operating modes. Port B and port C,

however, are affected by operating mode. Port B provides eight general-purpose

output signals in single-chip operating modes. When the microcontroller is in

expanded multiplexed operating mode, port B pins are the eight high-order address

lines.

Port C provides eight general-purpose input/output signals when the MCU is in the

single-chip operating mode. When the microcontroller is in the expanded

multiplexed operating mode, port C pins are a multiplexed address/data bus.

Refer to Table 1-1 for a functional description of the 40 port signals within different

operating modes. Terminate unused inputs and input/output (I/O) pins configured

as inputs high or low.

cale Semiconductor,

Frees

In all operating modes, port A can be configured for three timer input capture (IC)

functions and four timer output compare (OC) functions. An additional pin can be

configured as either the fourth IC or the fifth OC. Any port A pin that is not currently

being used for a timer function can be used as either a general-purpose input or

output line. Only port A pins PA7 and PA3 have an associated data direction

control bit that allows the pin to be selectively configured as input or output. Bits

DDRA7 and DDRA3 located in PACTL register control data direction for PA7 and

PA3, respectively. All other port A pins are fixed as either input or output.

PA7 can function as general-purpose I/O or as timer output compare for OC1. PA7

is also the input to the pulse accumulator, even while functioning as a

general-purpose I/O or an OC1 output.

PA6–PA4 serve as either general-purpose outputs, timer input captures, or timer

output compare 2–4. In addition, PA6–PA4 can be controlled by OC1.

PA3 can be a general-purpose I/O pin or a timer IC/OC pin. Timer functions

associated with this pin include OC1 and IC4/OC5. IC4/OC5 is software selectable

as either a fourth input capture or a fifth output compare. PA3 can also be

configured to allow OC1 edges to trigger IC4 captures.

PA2–PA0 serve as general-purpose inputs or as IC1–IC3.

PORTA can be read at any time. Reads of pins configured as inputs return the logic

level present on the pin. Pins configured as outputs return the logic level present

at the pin driver input. If written, PORTA stores the data in an internal latch, bits 7

and 3. It drives the pins only if they are configured as outputs. Writes to PORTA do

not change the pin state when pins are configured for timer input captures or output

compares. Refer to Section 6. Parallel Input/Output (I/O) Ports.

Data Sheet M68HC11E Family — Rev. 5

28 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Freescale Semiconductor, Inc.

Table 1-1. Port Signal Functions

General Description

Pin Descriptions

nc...

I

cale Semiconductor,

Frees

Port/Bit

PA0 PA0/IC3

PA1 PA1/IC2

PA2 PA2/IC1

PA3 PA3/OC5/IC4/OC1

PA4 PA4/OC4/OC1

PA5 PA5/OC3/OC1

PA6 PA6/OC2/OC1

PA7 PA7/PAI/OC1

PB0 PB0 ADDR8

PB1 PB1 ADDR9

PB2 PB2 ADDR10

PB3 PB3 ADDR11

PB4 PB4 ADDR12

PB5 PB5 ADDR13

PB6 PB6 ADDR14

PB7 PB7 ADDR15

PC0 PC0 ADDR0/DATA0

PC1 PC1 ADDR1/DATA1

PC2 PC2 ADDR2/DATA2

PC3 PC3 ADDR3/DATA3

PC4 PC4 ADDR4/DATA4

PC5 PC5 ADDR5/DATA5

PC6 PC6 ADDR6/DATA6

PC7 PC7 ADDR7/DATA7

PD0 PD0/RxD

PD1 PD1/TxD

PD2 PD2/MISO

PD3 PD3/MOSI

PD4 PD4/SCK

PD5 PD5/SS

— STRA AS

—STRB R/W

PE0 PE0/AN0

PE1 PE1/AN1

PE2 PE3/AN2

PE3 PE3/AN3

PE4 PE4/AN4

PE5 PE5/AN5

PE6 PE6/AN6

PE7 PE7/AN7

Single-Chip and

Bootstrap Modes

Expanded and

Test Modes

M68HC11E Family — Rev. 5 Data Sheet

MOTOROLA General Description 29

For More Information On This Product,

Go to: www.freescale.com

General Description

1.4.10.2 Port B

During single-chip operating modes, all port B pins are general-purpose output

pins. During MCU reads of this port, the level sensed at the input side of the po rt B

output drivers is read. Port B can also be used in simple strobed output mode. In

this mode, an output pulse appears at the STRB signal each time data is written to

port B.

In expanded multiplexed operating modes, all of the port B pins act as high order

address output signals. During each MCU cycle, bits 15–8 of the address bus are

output on the PB7–PB0 pins. The PORTB register is treated as an external

address in expanded modes.

1.4.10.3 Port C

Freescale Semiconductor, Inc.

nc...

I

cale Semiconductor,

Frees

While in single-chip operating modes, all port C pins are general-purpose I/O pins.

Port C inputs can be latched into an alternate PORTCL register by providing an

input transition to the STRA signal. Port C can also be used in full handshake

modes of parallel I/O where the STRA input and STRB output act as handshake

control lines.

When in expanded multiplexed modes, all port C pins are configured as

multiplexed address/data signals. During the address portion of each MCU cycle,

bits 7–0 of the address are output on the PC7–PC0 pins. During the data portion

of each MCU cycle (E high), PC7–PC0 are bidirectional data signals,

DATA7–DATA0. The direction of data at the port C pins is indicated by the R/W

signal.

The CWOM control bit in the PIOC register disables the port C P-channel output

driver. CWOM simultaneously affects all eight bits of port C. Because the

N-channel driver is not affected by CWOM, setting CWOM causes port C to

become an open-drain type output port suitable for wired-OR operation.

In wired-OR mode:

• When a port C bit is at logic level 0, it is driven low by the N-channel driver.

• When a port C b it is at logic level 1, the associated pin has high-impedance,

as neither the N-channel nor the P-channel devices are active.

It is customary to have an external pullup resistor on lines that are driven by

open-drain devices. Port C can only be configured for wired-OR operation when

the MCU is in single-chip mode. Refer to Section 6. Parallel Input/Output (I/O)

Ports for additional information about port C functions.

Data Sheet M68HC11E Family — Rev. 5

30 General Description MOTOROLA

For More Information On This Product,

Go to: www.freescale.com

Loading...

Loading...