Page 1

DSP56000

24-BIT

DIGITAL SIGNAL PROCESSOR

FAMILY MANUAL

Motorola, Inc.

Semiconductor Products Sector

DSP Division

6501 William Cannon Drive, West

Austin, Texas 78735-8598

Page 2

Order this document by DSP56KFAMUM/AD

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its

patent rights nor the rights of others. Motorola products are not authorized for use as components

in life support devices or systems intended for surgical implant into the body or intended to support

or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola

shall determine availability and suitability of its product or products for the use intended. Motorola

and M are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity /Affirmative Action Employer.

OnCE is a trade mark of Motorola, Inc.

Motorola Inc., 1994

Page 3

“1 ≤ N ≤

”.

Order this document by

MOTOROLA

SEMICONDUCTOR

DSP56KFAMUM/AD

TECHNICAL DATA

DSP56K Family

Addendum to

24-bit Digital Signal Processor

Family Manual

This document, containing changes, additional features, further explanations, and clarifications, is

a supplement to the original document:

DSP56KFAMUM/AD Family Manual DSP56K Family

24-bit Digital Signal Processors

Change the following:

TM

Page 11-4, Section 11.2.1 - Delete “4. NeXT

Page A-83, third line - Replace

Page A-104, Under the “Operation:” heading - Replace “

Page A-104, Second sentence after “Description:” heading - Replace “

of D.

” with “

One is added to the LSB of D; i.e. bit 0 of A0 or B0.

“1;leN;le24”

under Mach”.

with

24”

D -1 ⇒ D

” with “

”

D+1 ⇒ D

One is added from the LSB

”.

Page A-130, First symbolic description under the “Operation:” heading - Replace “

“

If S[n]=1

Page A-218, Timing description - Replace “ Timing:

6 + ea + ap oscillator clock cycles

Page A-219, Timing description - Replace “ Timing:

6 + ea + ap oscillator clock cycles

Page A-225, Timing description - Replace “ Timing:

2+mvp oscillator clock cycles

Page A-261, Timing description - Replace “ Timing:

oscillator clock cycles

Page A-261, Memory description - Replace “Memory:

program words

Page B-11, An inch below the middle of the page - Replace the “

Page B-16, 7

”.

”.

”.

”.

”.

”.

th

instruction from bottom - Replace “

2+mvp oscillator clock cycles

2+mvp oscillator clock cycles

4+mvp oscillator clock cycles

4 oscillator clock cycles

1 program words

cir

” instruction with “

lsl A,n0

” with “

lsl B A,n0

” with “ Timing:

” with “Memory:

If S[n]=0

” with “ Timing:

” with “ Timing:

” with “ Timing:

clr

” with

2+mvp

1+ mv

”.

MOTOROLA INC., 1995

Page 4

MOTOROLA

SEMICONDUCTOR

TECHNICAL DATA

MOTOROLA INC., 1995

Page 5

OnCE

TM

is a trade mark of Motorola, Inc.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability

arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters can and do vary in different applications. All operating parameters, including “Typical”, must be validated for each customer application by customer's technical experts. Motorola does not

convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized

for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain

life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death

may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall

indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims,

costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or

death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the

design or manufacture of the part.

Motorola and

b are registered trademarks of Motorola, Inc.

Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Center; 88 Tanners Drive, Blakelands, Milton

Keynes, MK14 5BP, Great Britain.

Page 6

TABLE OF CONTENTS

Paragraph Page

Number Title Number

SECTION 1

DSP56K FAMILY INTRODUCTION

1.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.2 ORIGIN OF DIGITAL SIGNAL PROCESSING . . . . . . . . . . . . . . . . . . . . . . . .1-3

1.3 SUMMARY OF DSP56K FAMILY FEATURES . . . . . . . . . . . . . . . . . . . . . . . .1-9

1.4 MANUAL ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-11

SECTION 2

DSP56K CENTRAL ARCHITECTURE

OVERVIEW

2.1 DSP56K CENTRAL ARCHITECTURE OVERVIEW . . . . . . . . . . . . . . . . . . . .2-3

2.2 DATA BUSES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.3 ADDRESS BUSES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.4 DATA ALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.5 ADDRESS GENERATION UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.6 PROGRAM CONTROL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.7 MEMORY EXPANSION PORT (PORT A) . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.8 ON-CHIP EMULATOR (OnCE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.9 PHASE-LOCKED LOOP (PLL) BASED CLOCKING . . . . . . . . . . . . . . . . . . .2-6

SECTION 3

DATA ARITHMETIC LOGIC UNIT

3.1 DATA ARITHMETIC LOGIC UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.2 OVERVIEW AND DATA ALU ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . .3-3

3.3 DATA REPRESENTATION AND ROUNDING . . . . . . . . . . . . . . . . . . . . . . .3-10

3.4 DOUBLE PRECISION MULTIPLY MODE . . . . . . . . . . . . . . . . . . . . . . . . . .3-16

MOTOROLA

TABLE OF CONTENTS

iii

Page 7

iv

Table of Contents (Continued)

Paragraph Page

Number Title Number

3.5 DATA ALU PROGRAMMING MODEL . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

3.6 DATA ALU SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-19

SECTION 4

ADDRESS GENERATION UNIT

4.1 ADDRESS GENERATION UNIT AND ADDRESSING MODES . . . . . . . . . . .4-3

4.2 AGU ARCHITECTURE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-3

4.3 PROGRAMMING MODEL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-6

4.4 ADDRESSING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-8

SECTION 5

PROGRAM CONTROL UNIT

5.1 PROGRAM CONTROL UNIT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

5.2 OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-3

5.3 PROGRAM CONTROL UNIT (PCU) ARCHITECTURE . . . . . . . . . . . . . . . . .5-5

5.4 PROGRAMMING MODEL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-8

SECTION 6

INSTRUCTION SET INTRODUCTION

6.1 INSTRUCTION SET INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.2 SYNTAX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.3 INSTRUCTION FORMATS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-3

6.4 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-20

SECTION 7

PROCESSING STATES

7.1 PROCESSING STATES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.2 NORMAL PROCESSING STATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-3

7.3 EXCEPTION PROCESSING STATE (INTERRUPT PROCESSING) . . . . . .7-10

TABLE OF CONTENTS MOTOROLA

Page 8

Table of Contents (Continued)

Paragraph Page

Number Title Number

7.4 RESET PROCESSING STATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-33

7.5 WAIT PROCESSING STATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-36

7.6 STOP PROCESSING STATE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-37

SECTION 8

PORT A

8.1 PORT A OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

8.2 PORT A INTERFACE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-3

SECTION 9

PLL CLOCK OSCILLATOR

9.1 PLL CLOCK OSCILLATOR INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . .9-3

9.2 PLL COMPONENTS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-3

9.3 PLL PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-9

9.4 PLL OPERATION CONSIDERATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . .9-11

SECTION 10

ON-CHIP EMULATION (OnCE)

10.1 ON-CHIP EMULATION INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

10.2 ON-CHIP EMULATION (OnCE) PINS . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-3

10.3 OnCE CONTROLLER AND SERIAL INTERFACE . . . . . . . . . . . . . . . . . . . .10-6

10.4 OnCE MEMORY BREAKPOINT LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . .10-11

10.5 OnCE TRACE LOGIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-13

10.6 METHODS OF ENTERING THE DEBUG MODE . . . . . . . . . . . . . . . . . . . .10-14

10.7 PIPELINE INFORMATION AND GLOBAL DATA BUS REGISTER . . . . . .10-16

10.8 PROGRAM ADDRESS BUS HISTORY BUFFER . . . . . . . . . . . . . . . . . . .10-18

10.9 SERIAL PROTOCOL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-19

10.10 DSP56K TARGET SITE DEBUG SYSTEM REQUIREMENTS . . . . . . . . .10-19

10.11 USING THE OnCE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-20

MOTOROLA

TABLE OF CONTENTS

v

Page 9

vi

Table of Contents (Continued)

Paragraph Page

Number Title Number

SECTION 11

ADDITIONAL SUPPORT

11.1 USER SUPPORT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-3

11.2 MOTOROLA DSP PRODUCT SUPPORT . . . . . . . . . . . . . . . . . . . . . . . . . .11-4

11.3 DSP56KADSx APPLICATION DEVELOPMENT SYSTEM . . . . . . . . . . . . .11-6

11.4 Dr. BuB ELECTRONIC BULLETIN BOARD . . . . . . . . . . . . . . . . . . . . . . . . .11-7

11.5 MOTOROLA DSP NEWS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-16

11.6 MOTOROLA FIELD APPLICATION ENGINEERS . . . . . . . . . . . . . . . . . . .11-16

11.7 DESIGN HOTLINE– 1-800-521-6274 . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-16

11.8 DSP HELP LINE – (512) 891-3230 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-16

11.9 MARKETING INFORMATION– (512) 891-2030 . . . . . . . . . . . . . . . . . . . . .11-16

11.10 THIRD-PARTY SUPPORT INFORMATION – (512) 891-3098 . . . . . . . . . .11-16

11.11 UNIVERSITY SUPPORT – (512) 891-3098 . . . . . . . . . . . . . . . . . . . . . . . .11-16

11.12 TRAINING COURSES – (602) 897-3665 or (800) 521-6274 . . . . . . . . . . .11-17

11.13 REFERENCE BOOKS AND MANUALS . . . . . . . . . . . . . . . . . . . . . . . . . . .11-17

APPENDIX A

INSTRUCTION SET DETAILS

A.1 APPENDIX A INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A.2 INSTRUCTION GUIDE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-3

A.3 NOTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-4

A.4 ADDRESSING MODES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-10

A.5 CONDITION CODE COMPUTATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-15

A.6 PARALLEL MOVE DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-20

A.7 INSTRUCTION DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-21

A.8 INSTRUCTION TIMING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-294

A.9 INSTRUCTION SEQUENCE RESTRICTIONS . . . . . . . . . . . . . . . . . . . . . A-305

A.10 INSTRUCTION ENCODING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-311

APPENDIX B

BENCHMARK PROGRAMS

B.1 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

B.2 BENCHMARK PROGRAMS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-3

TABLE OF CONTENTS MOTOROLA

Page 10

LIST of FIGURES

Figure Page

Number Title Number

1-1 Analog Signal Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1-2 Digital Signal Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1-3 DSP Hardware Origins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

2-1 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

3-1 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3-2 Data ALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3-3 MAC Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3-4 DATA ALU Accumulator Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3-5 Saturation Arithmetic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3-6 Integer-to-Fractional Data Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3-7 Bit Weighting and Alignment of Operands . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3-8 Integer/Fractional Number Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3-9 Integer/Fractional Multiplication Comparison . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3-10 Convergent Rounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3-11 Full Double Precision Multiply Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3-12 Single X Double Multiply Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-17

3-13 Single X Double Multiply-Accumulate Algorithm . . . . . . . . . . . . . . . . . . . . . . 3-18

3-14 DSP56K Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-19

4-1 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4-2 AGU Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

4-3 AGU Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4-4 Address Register Indirect — No Update . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-10

4-5 Address Register Indirect — Postincrement . . . . . . . . . . . . . . . . . . . . . . . . . 4-11

4-6 Address Register Indirect — Postdecrement . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4-7 Address Register Indirect — Postincrement by Offset Nn . . . . . . . . . . . . . . 4-13

4-8 Address Register Indirect — Postdecrement by Offset Nn . . . . . . . . . . . . . . 4-14

4-9 Address Register Indirect — Indexed by Offset Nn . . . . . . . . . . . . . . . . . . . 4-15

4-10 Address Register Indirect — Predecrement . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

4-11 Circular Buffer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-19

4-12 Linear Addressing with a Modulo Modifier . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4-13 Modulo Modifier Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

MOTOROLA

Revision 2.1 DSP56004 DESIGN SPECIFICATION vii

LIST of FIGURES

vii

Page 11

List of Figures (Continued)

Figure Page

Number Title Number

4-14 Bit-Reverse Address Calculation Example . . . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4-15 Address Modifier Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-26

5-1 Program Address Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5-2 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5-3 Three-Stage Pipeline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-7

5-4 Program Control Unit Programming Model . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5-5 Status Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-9

5-6 OMR Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

5-7 Stack Pointer Register Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5-8 SP Register Values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5-9 DSP56K Central Processing Module Programming Model . . . . . . . . . . . . . . 5-18

6-1 DSP56K Central Processing Module Programming Model . . . . . . . . . . . . . . 6-4

6-2 General Format of an Instruction Operation Word . . . . . . . . . . . . . . . . . . . . 6-5

6-3 Operand Sizes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6-4 Reading and Writing the ALU Extension Registers . . . . . . . . . . . . . . . . . . . . 6-7

6-5 Reading and Writing the Address ALU Registers . . . . . . . . . . . . . . . . . . . . . 6-7

6-6 Reading and Writing Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6-7 Special Addressing – Immediate Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-15

6-8 Special Addressing – Absolute Addressing . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6-9 Special Addressing – Immediate Short Data . . . . . . . . . . . . . . . . . . . . . . . . 6-17

6-10 Special Addressing – Short Jump Address . . . . . . . . . . . . . . . . . . . . . . . . . . 6-18

6-11 Special Addressing – Absolute Short Address . . . . . . . . . . . . . . . . . . . . . . . 6-19

6-12 Special Addressing – I/O Short Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-20

6-13 Hardware DO Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6-14 Nested DO Loops . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-26

6-15 Classifications of Parallel Data Moves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6-16 Parallel Move Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-28

7-1 Fast and Long Interrupt Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-13

7-2 Interrupt Priority Register (Addr X:$FFFF) . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-3 Interrupting an SWI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-18

7-4 Illegal Instruction Interrupt Serviced by a Fast Interrupt . . . . . . . . . . . . . . . . 7-19

7-5 Illegal Instruction Interrupt Serviced by a Long Interrupt . . . . . . . . . . . . . . . . 7-20

7-6 Repeated Illegal Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-21

7-7 Trace Exception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-23

7-8 Fast Interrupt Service Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-27

7-9 Two Consecutive Fast Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-28

7-10 Long Interrupt Service Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-30

7-11 JSR First Instruction of a Fast Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-31

7-12 JSR Second Instruction of a Fast Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . 7-32

viii

LIST of FIGURES MOTOROLA

Page 12

List of Figures (Continued)

Figure Page

Number Title Number

7-13 Interrupting an REP Instruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-34

7-14 Interrupting Sequential REP Instructions . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-35

7-15 Wait Instruction Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-36

7-16 Simultaneous Wait Instruction and Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . 7-37

7-17 STOP Instruction Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-38

7-18 STOP Instruction Sequence Followed by IRQA . . . . . . . . . . . . . . . . . . . . . . 7-39

7-19 STOP Instruction Sequence Recovering with RESET . . . . . . . . . . . . . . . . . 7-42

8-1 Port A Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-4

9-1 PLL Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9-2 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9-3 PLL Control Register (PCTL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

10-1 OnCE Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10-2 DSP56K Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10-3 OnCE Controller and Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-6

10-4 OnCE Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

10-5 OnCE Status and Control Register (OSCR) . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

10-6 OnCE Memory Breakpoint Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-12

10-7 OnCE Trace Logic Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-14

10-8 OnCE Pipeline Information and GDB Registers . . . . . . . . . . . . . . . . . . . . . . 10-16

10-9 OnCE PAB FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-17

B-1 20-Tap FIR Filter Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-5

B-2 Radix 2, In-Place, Decimation-In-Time FFT. . . . . . . . . . . . . . . . . . . . . . . . . . B-7

B-3 8-Pole 4-Multiply Cascaded Canonic IIR Filter . . . . . . . . . . . . . . . . . . . . . . . B-9

B-4 LMS FIR Adaptive Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . B-11

B-5 Real Input FFT Based on Glenn Bergland Algorithm. . . . . . . . . . . . . . . . . . . B-12

MOTOROLA

LIST of FIGURES

ix

Page 13

x

LIST of TABLES

Table Page

Number Title Number

1-1 Benchmark Summary in Instruction Cycles. . . . . . . . . . . . . . . . . . . . . . . . . 1-6

3-1 Limited Data Values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

4-1 Address Register Indirect Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4-2 Address Modifier Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4-3 Bit-Reverse Addressing Sequence Example. . . . . . . . . . . . . . . . . . . . . . . . 4-23

6-1 Addressing Modes Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-21

7-1 Instruction Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7-2 Status Register Interrupt Mask Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

7-3 Interrupt Priority Level Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7-4 External Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-15

7-5 Central Processor Interrupt Priorities Within an IPL . . . . . . . . . . . . . . . . . . 7-15

7-6 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-16

9-1 Multiplication Factor Bits MF0-MF11 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-6

9-2 Division Factor Bits DF0-DF3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-7

9-3 PSTP and PEN Relationship . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9-4 Clock Output Disable Bits COD0-COD1 . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-9

10-1 Chip Status Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

10-2 OnCE Register Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-7

10-3 Memory Breakpoint Control Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-10

A-1 Instruction Description Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-5

A-2 DSP56K Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-11

A-3 DSP56K Addressing Mode Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-12

A-4 Addressing Mode Modifier Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-14

A-5 Condition Code Computations for Instructions (No Parallel Move) . . . . . . . A-19

A-6 Instruction Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-301

A-7 Parallel Data Move Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-302

A-8 MOVEC Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-302

A-9 MOVEP Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-302

LIST of TABLES MOTOROLA

Page 14

List of Tables (Continued)

Table Page

Number Title Number

A-10 Bit Manipulation Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-303

A-11 Jump Instruction Timing Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-303

A-12 RTI/RTS Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-304

A-13 Addressing Mode Timing Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-304

A-14 Memory Access Timing Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-305

A-15 Single-Bit Register Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-312

A-16 Single-Bit Special Register Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-312

A-17 Double-Bit Register Encodings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-312

A-18 Triple-Bit Register Encodings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-313

A-19 (a)Four-Bit Register Encodings for 12 Registers in Data ALU . . . . . . . . . . . A-313

A-19 (b)Four-Bit Register Encodings for 16 Condition Codes . . . . . . . . . . . . . . . . A-313

A-20 Five-Bit Register Encodings for 28 Registers in

Data ALU and Address ALU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-314

A-21 Six-Bit Register Encodings for 43 Registers On-Chip . . . . . . . . . . . . . . . . . A-314

A-22 Write Control Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-314

A-23 Memory Space Bit Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-314

A-24 Program Controller Register Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-315

A-25 Condition Code and Address Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . A-315

A-26 Effective Addressing Mode Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-316

A-27 Operation Code K0-2 Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-331

A-28 Operation Code QQQ Decode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-332

A-29 Nonmultiply Instruction Encoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-333

A-30 Special Case #1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-334

A-31 Special Case #2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-334

B-1 27-MHz Benchmark Results for the DSP56001R27 . . . . . . . . . . . . . . . . . . B-4

MOTOROLA

LIST of TABLES

xi

Page 15

List of Tables (Continued)

Table Page

Number Title Number

xii

LIST of TABLES MOTOROLA

Page 16

SECTION 1

DSP56K FAMILY INTRODUCTION

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 1

Page 17

SECTION CONTENTS

SECTION 1.1 INTRODUCTION ........................................................................3

SECTION 1.2 ORIGIN OF DIGITAL SIGNAL PROCESSING ..........................3

SECTION 1.2 SUMMARY OF DSP56K FAMILY FEATURES ..........................9

SECTION 1.3 MANUAL ORGANIZATION ........................................................11

1 - 2 DSP56K FAMILY INTRODUCTION

MOTOROLA

Page 18

INTRODUCTION

1.1 INTRODUCTION

The DSP56K Family is Motorola’s series of 24-bit general purpose Digital Signal Processors (DSPs

*

). The family architecture features a central processing module that is

common to the various family members, such as the DSP56002 and the DSP56004.

Note: The DSP56000 and the DSP56001 are not based on the central processing module

architecture and should not be used with this manual. They will continue to be described

in the DSP56000/DSP56001 User’s Manual (DSP56000UM/AD Rev. 2).

This manual describes the DSP56K Family’s central processor and instruction set. It is

intended to be used with a family member’s User’s Manual, such as the DSP56002 User’s

Manual .

The User’s Manual presents the device’s specifics, including pin descriptions, operating

modes, and peripherals. Packaging and timing information can be found in the device’s

Technical Data Sheet.

This chapter introduces general DSP theory and discusses the features and benefits of

the Motorola DSP56K family of 24-bit processors. It also presents a brief description of

each of the sections of the manual.

1.2 ORIGIN OF DIGITAL SIGNAL PROCESSING

DSP is the arithmetic processing of real-time signals sampled at regular intervals and digitized. Examples of DSP processing include the following:

• Filtering of signals

• Convolution, which is the mixing of two signals

• Correlation, which is a comparison of two signals

• Rectification, amplification, and/or transformation of a signal

All of these functions have traditionally been performed using analog circuits. Only recent-

ly has semiconductor technology provided the processing power necessary to digitally

perform these and other functions using DSPs.

Figure 1-1 shows a description of analog signal processing. The circuit in the illustration

filters a signal from a sensor using an operational amplifier, and controls an actuator with

the result. Since the ideal filter is impossible to design, the engineer must design the filter

for acceptable response, considering variations in temperature, component aging, power

supply variation, and component accuracy. The resulting circuit typically has low noise immunity, requires adjustments, and is difficult to modify.

*This manual uses the acronym DSP for Digital Signal Processing or Digital Signal Processor, de-

pending on the context.

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 3

Page 19

x(t)

INPUT

FROM

SENSOR

ORIGIN OF DIGITAL SIGNAL PROCESSING

ANALOG FILTER

R

f

C

f

x(t)

R

i

+

-

y(t)

OUTPUT

ACTUATOR

y(t)

TO

GAIN

FREQUENCY

t

yt()

---------

xt()

FREQUENCY CHARACTERISTICS

IDEAL

FILTER

f

c

f

R

f

------

–=

R

i

1

----------------------------- +

1 jwR

fCf

Figure 1-1 Analog Signal Processing

The equivalent circuit using a DSP is shown in Figure 1-2. This application requires an

analog-to-digital (A/D) converter and digital-to-analog (D/A) converter in addition to the

DSP. Even with these additional parts, the component count can be lower using a DSP

due to the high integration available with current components.

Processing in this circuit begins by band-limiting the input with an anti-alias filter, eliminating out-of-band signals that can be aliased back into the pass band due to the sampling

process. The signal is then sampled, digitized with an A/D converter, and sent to the DSP.

The filter implemented by the DSP is strictly a matter of software. The DSP can directly

implement any filter that can also be implemented using analog techniques. Also, adaptive filters can be easily implemented using DSP, whereas these filters are extremely

difficult to implement using analog techniques.

The DSP output is processed by a D/A converter and is low-pass filtered to remove the

effects of digitizing. In summary, the advantages of using the DSP include the following:

1- 4 DSP56K FAMILY INTRODUCTION

MOTOROLA

Page 20

ORIGIN OF DIGITAL SIGNAL PROCESSING

• Fewer components

• Stable, deterministic performance

• Wide range of applications

• High noise immunity and

•

Self-test can be built in

•

No filter adjustments

•

Filters with much closer tolerances

•

Adaptive filters easily implemented

power-supply rejection

LOW-PASS

ANTIALIASING

FILTER

ANALOG IN ANALOG OUT

SAMPLER AND

ANALOG-TO-DIGITAL

CONVERTER

A/D D/A

x(n) y(n) y(t)x(t)

A

IDEAL

FILTER

GAIN

DSP OPERATION

FIR FILTER

N

ck() nk–()×

∑

k0=

FINITE IMPULSE

RESPONSE

DIGITAL-TO-ANALOG

CONVERTER

RECONSTRUCTION

LOW-PASS

FILTER

FREQUENCY

A

ANALOG

FILTER

DIGITAL

FILTER

GAIN

FREQUENCY

A

GAIN

FREQUENCY

Figure 1-2 Digital Signal Processing

f

f

c

f

f

c

f

f

c

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 5

Page 21

ORIGIN OF DIGITAL SIGNAL PROCESSING

The DSP56K family is not designed for a particular application but is designed to execute

commonly used DSP benchmarks in a minimum time for a single-multiplier architecture.

For example, a cascaded, 2nd-order, four-coefficient infinite impulse response (IIR) biquad section has four multiplies for each section. For that algorithm, the theoretical

minimum number of operations for a single-multiplier architecture is four per section. Table 1-1 shows a list of benchmarks with the number of instruction cycles a DSP56K chip

uses compared to the number of multiplies the algorithm requires.

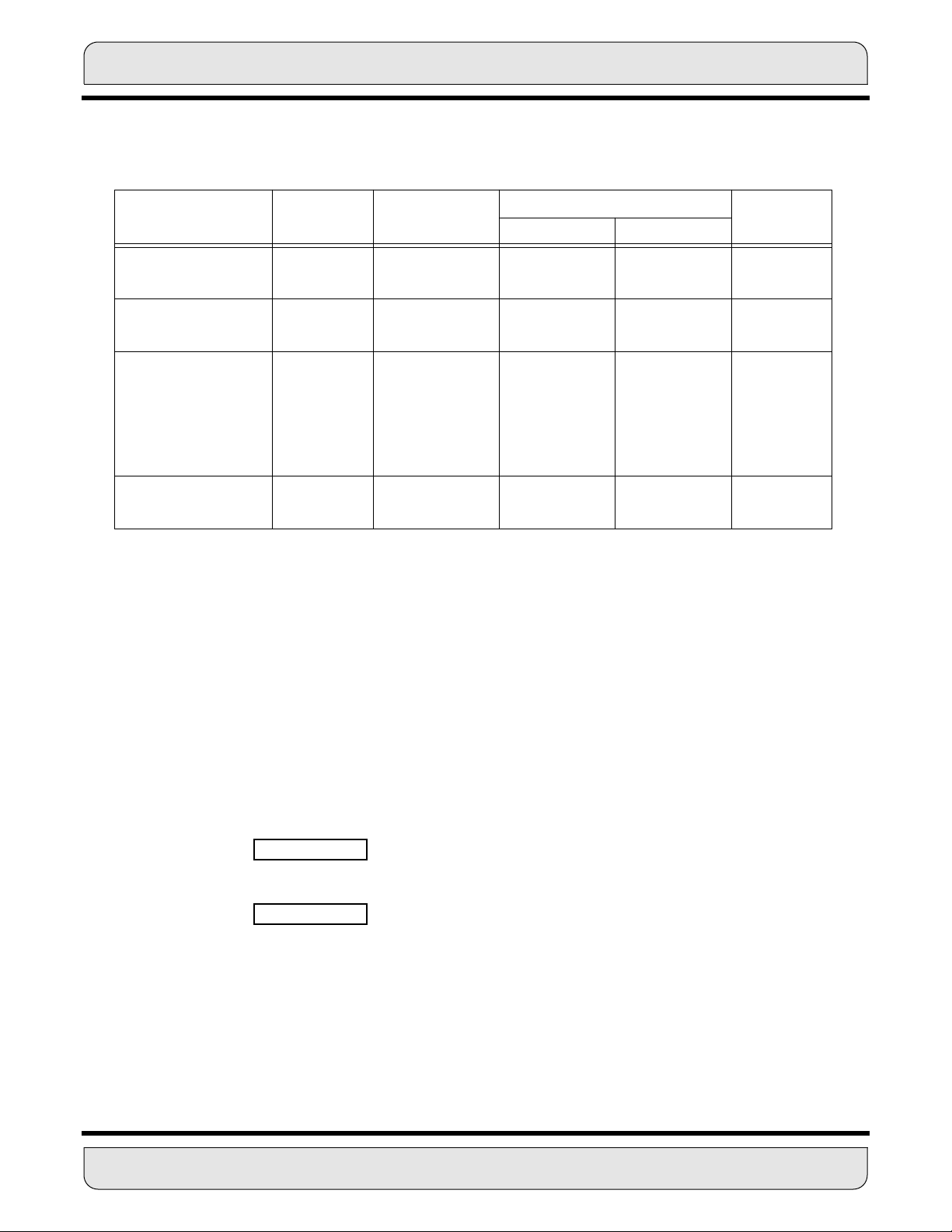

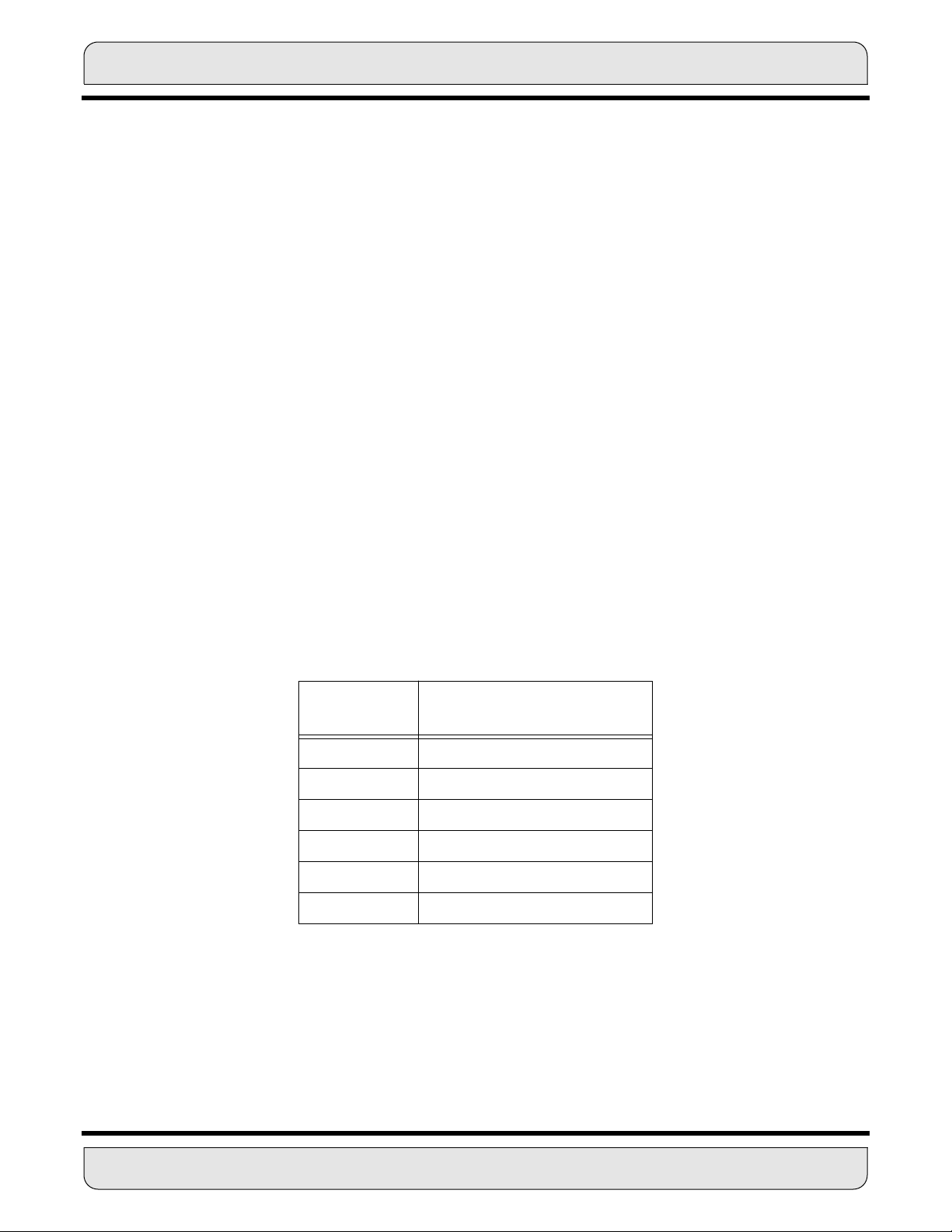

Table 1-1 Benchmark Summary in Instruction Cycles

Number of

Benchmark Number of Cycles

Algorithm

Multiplies

Real Multiply 3 1

N Real Multiplies 2N N

Real Update 4 1

N Real Updates 2N N

N Term Real Convolution (FIR) N N

N Term Real * Complex Convolution 2N N

Complex Multiply 6 4

N Complex Multiplies 4N N

Complex Update 7 4

N Complex Updates 4N 4N

N Term Complex Convolution (FIR) 4N 4N

th

- Order Power Series 2N 2N

N

2nd - Order Real Biquad Filter 7 4

N Cascaded 2

N Radix Two FFT Butterflies 6N 4N

nd

- Order Biquads 4N 4N

These benchmarks and others are used independently or in combination to implement

functions whose characteristics are controlled by the coefficients of the benchmarks being

executed. Useful functions using these and other benchmarks include the following:

1- 6 DSP56K FAMILY INTRODUCTION

MOTOROLA

Page 22

ORIGIN OF DIGITAL SIGNAL PROCESSING

Digital Filtering

Finite Impulse Response (FIR)

Infinite Impulse Response (IIR)

Matched Filters (Correlators)

Hilbert Transforms

Windowing

Adaptive Filters/Equalizers

Signal Processing

Compression (e.g., Linear Predictive

Coding of Speech Signals)

Expansion

Averaging

Energy Calculations

Homomorphic Processing

Mu-law/A-law to/from Linear Data

Conversion

Data Processing

Encryption/Scrambling

Encoding (e.g., Trellis Coding)

Decoding (e.g., Viterbi Decoding)

Numeric Processing

Scaler, Vector, and Matrix Arithmetic

Transcendental Function Computation

(e.g., Sin(X), Exp(X))

Other Nonlinear Functions

Pseudo-Random-Number Generation

Modulation

Amplitude

Frequency

Phase

Spectral Analysis

Fast Fourier Transform (FFT)

Discrete Fourier Transform (DFT)

Sine/Cosine Transforms

Moving Average (MA) Modeling

Autoregressive (AR) Modeling

ARMA Modeling

Useful applications are based on combining these and other functions. DSP applications

affect almost every area in electronics because any application for analog electronic circuitry can be duplicated using DSP. The advantages in doing so are becoming more

compelling as DSPs become faster and more cost effective.Some typical applications for

DSPs are presented in the following list:

Telecommunication

Tone Generation

Dual-Tone Multifrequency (DTMF)

Subscriber Line Interface

Full-Duplex Speakerphone

Teleconferencing

Voice Mail

Adaptive Differential Pulse Code

Modulation (ADPCM) Transcoder

Medium-Rate Vocoders

Noise Cancelation

Repeaters

Integrated Services Digital Network

(ISDN) Transceivers

Secure Telephones

Data Communication

High-Speed Modems

Multiple Bit-Rate Modems

High-Speed Facsimile

Radio Communication

Secure Communications

Point-to-Point Communications

Broadcast Communications

Cellular Mobile Telephone

Computer

Array Processors

Work Stations

Personal Computers

Graphics Accelerators

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 7

Page 23

ORIGIN OF DIGITAL SIGNAL PROCESSING

Image Processing

Pattern Recognition

Optical Character Recognition

Image Restoration

Image Compression

Image Enhancement

Robot Vision

Graphics

3-D Rendering

Computer-Aided Engineering (CAE)

Desktop Publishing

Animation

Instrumentation

Spectral Analysis

Waveform Generation

Transient Analysis

Data Acquisition

Speech Processing

Speech Synthesizer

Speech Recognizer

Voice Mail

Vocoder

Speaker Authentication

Speaker Verification

Audio Signal Processing

Digital AM/FM Radio

Digital Hi-Fi Preamplifier

Noise Cancelation

Music Synthesis

Music Processing

Acoustic Equalizer

High-Speed Control

Laser-Printer Servo

Hard-Disk Servo

Robotics

Motor Controller

Position and Rate Controller

Vibration Analysis

Electric Motors

Jet Engines

Turbines

Medical Electronics

Cat Scanners

Sonographs

X-Ray Analysis

Electrocardiogram

Electroencephalogram

Nuclear Magnetic Resonance Analysis

Digital Video

Digital Television

High-Resolution Monitors

Radar and Sonar Processing

Navigation

Oceanography

Automatic Vehicle Location

Search and Tracking

Seismic Processing

Oil Exploration

Geological Exploration

As shown in Figure 1-3, the keys to DSP are as follows:

• The Multiply/Accumulate (MAC) operation

• Fetching operands for the MAC

• Program control to provide versatile operation

• Input/Output to move data in and out of the DSP

MAC is the basic operation used in DSP. The DSP56K family of processors has a dual

Harvard architecture optimized for MAC operations. Figure 1-3 shows how the DSP56K

1- 8 DSP56K FAMILY INTRODUCTION

MOTOROLA

Page 24

SUMMARY OF DSP56K FAMILY FEATURES

architecture matches the shape of the MAC operation. The two operands, C() and X(), are

directed to a multiply operation, and the result is summed. This process is built into the

chip by using two separate memories (X and Y) to feed a single-cycle MAC. The entire

process must occur under program control to direct the correct operands to the multiplier

and save the accumulator as needed. Since the two memories and the MAC are independent, the DSP can perform two moves, a multiply and an accumulate, in a single

operation. As a result, many of the benchmarks shown in Table 1-1 can be executed at or

near the theoretical maximum speed for a single-multiplier architecture.

1.3 SUMMARY OF DSP56K FAMILY FEATURES

The high throughput of the DSP56K family of processors makes them well suited for communication, high-speed control, numeric processing and computer and audio

applications. The main features that contribute to this high throughput include:

• Speed — Speeds high enough to easily address applications traditionally served by

low-end floating point DSPs.

FIR FILTER

N

ck() nk–()×

A/D D/A

x(n) y(n) y(t)x(t)

∑

k0=

X

∑

X

MEMORY

Y

MEMORY

X

PROGRAM

∑

MAC

Figure 1-3 DSP Hardware Origins

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 9

Page 25

SUMMARY OF DSP56K FAMILY FEATURES

• Precision — The data paths are 24 bits wide, providing 144 dB of dynamic range;

intermediate results held in the 56-bit accumulators can range over 336 dB.

• Parallelism — Each on-chip execution unit (AGU, program control unit, data ALU),

memory, and peripheral operates independently and in parallel with the other units

through a sophisticated bus system. The data ALU, AGU, and program control unit

operate in parallel so that an instruction prefetch, a 24-bit x 24-bit multiplication, a 56bit addition, two data moves, and two address-pointer updates using one of three

types of arithmetic (linear, modulo, or reverse-carry) can be executed in a single

instruction cycle. This parallelism allows a four-coefficient IIR filter section to be

executed in only four cycles, the theoretical minimum for single-multiplier architecture.

At the same time, the two serial controllers can send and receive full-duplex data, and

the host port can send/receive simplex data.

• Flexibility — While many other DSPs need external communications circuitry to

interface with peripheral circuits (such as A/D converters, D/A converters, or host

processors), the DSP56K family provides on-chip serial and parallel interfaces which

can support various configurations of memory and peripheral modules

• Sophisticated Debugging — Motorola’s on-chip emulation technology (OnCE) allows

simple, inexpensive, and speed independent access to the internal registers for

debugging. OnCE tells application programmers exactly what the status is within the

registers, memory locations, buses, and even the last five instructions that were

executed.

• Phase-locked Loop (PLL) Based Clocking — PLL allows the chip to use almost any

available external system clock for full-speed operation while also supplying an output

clock synchronized to a synthesized internal core clock. It improves the synchronous

timing of the processors’ external memory port, eliminating the timing skew common

on other processors.

• Invisible Pipeline — The three-stage instruction pipeline is essentially invisible to the

programmer, allowing straightforward program development in either assembly

language or a high-level language such as a full Kernighan and Ritchie C.

• Instruction Set — The instruction mnemonics are MCU-like, making the transition

from programming microprocessors to programming the chip as easy as possible. The

orthogonal syntax controls the parallel execution units. The hardware DO loop

instruction and the repeat (REP) instruction make writing straight-line code obsolete.

1- 10 DSP56K FAMILY INTRODUCTION

MOTOROLA

Page 26

MANUAL ORGANIZATION

DSP56001 Compatibility — All members of the DSP56K family are downward

compatible with the DSP56001, and also have added flexibility, speed, and

functionality.

• Low Power — As a CMOS part, the DSP56000/DSP56001 is inherently very low

power and the STOP and WAIT instructions further reduce power requirements.

1.4 MANUAL ORGANIZATION

This manual describes the central processing module of the DSP56K family in detail and

provides practical information to help the user:

• Understand the operation of the DSP56K family

• Design parallel communication links

• Design serial communication links

• Code DSP algorithms

• Code communication routines

• Code data manipulation algorithms

• Locate additional support

•

The following list describes the contents of each section and each appendix:

Section 2 – DSP56K Central Architecture Overview

The DSP56K central architecture consists of the data arithmetic logic unit (ALU), address generation unit (AGU), program control unit, On-Chip Emulation (OnCE)

circuitry, the phase locked loop (PLL) based clock oscillator, and an external memory

port (Port A). This section describes each subsystem and the buses interconnecting

the major components in the DSP56K central processing module.

Section 3 – Data Arithmetic Logic Unit

This section describes in detail the data ALU and its programming model.

Section 4 – Address Generation Unit

This section specifically describes the AGU, its programming model, address indirect

modes, and address modifiers.

Section 5 – Program Control Unit

This section describes in detail the program control unit and its programming model.

Section 6 – Instruction Set Introduction

This section presents a brief description of the syntax, instruction formats, operand/memory references, data organization, addressing modes, and instruction set. A

detailed description of each instruction is given in APPENDIX A - INSTRUCTION SET

DETAILS.

MOTOROLA DSP56K FAMILY INTRODUCTION 1 - 11

Page 27

MANUAL ORGANIZATION

Section 7 – Processing States

This section describes the five processing states (normal, exception, reset, wait, and

stop).

Section 8 – Port A

This section describes the external memory port, its control register, and control

signals.

Section 9 – PLL Clock Oscillator

This section describes the PLL and its functions

Section 10 – On-Chip Emulator (OnCE)

This section describes the OnCE circuitry and its functions.

Section 11 – Additional Support

This section presents a brief description of current support products and services and

information on where to obtain them.

Appendix A – Instruction Set Details

A detailed description of each DSP56K family instruction, its use, and its affect on the

processor are presented.

Appendix B – Benchmarks

DSP5K family benchmark results are listed in this appendix.

1- 12 DSP56K FAMILY INTRODUCTION MOTOROLA

Page 28

SECTION 2

DSP56K CENTRAL ARCHITECTURE

OVERVIEW

MOTOROLA DSP56K CENTRAL ARCHITECTURE OVERVIEW 2 - 1

Page 29

SECTION CONTENTS

SECTION 2.1 DSP56K CENTRAL ARCHITECTURE OVERVIEW ..................3

SECTION 2.2 DATA BUSES .............................................................................3

SECTION 2.3 ADDRESS BUSES .....................................................................4

SECTION 2.4 DATA ALU ..................................................................................5

SECTION 2.5 ADDRESS GENERATION UNIT ................................................5

SECTION 2.6 PROGRAM CONTROL UNIT .....................................................5

SECTION 2.7 MEMORY EXPANSION PORT (PORT A) ..................................6

SECTION 2.8 ON-CHIP EMULATOR (OnCE) ..................................................6

SECTION 2.9 PHASE-LOCKED LOOP (PLL) BASED CLOCKING ..................6

2 - 2 DSP56K CENTRAL ARCHITECTURE OVERVIEW

MOTOROLA

Page 30

DSP56K CENTRAL ARCHITECTURE OVERVIEW

2.1 DSP56K CENTRAL ARCHITECTURE OVERVIEW

The DSP56K family of processors is built on a standard central processing module. In the

expansion area around the central processing module, the chip can support various configurations of memory and peripheral modules which may change from family member to

family member. This section introduces the architecture and the major components of the

central processing module.

The central components are:

• Data Buses

• Address Buses

• Data Arithmetic Logic Unit (data ALU)

• Address Generation Unit (AGU)

• Program Control Unit (PCU)

• Memory Expansion (Port A)

• On-Chip Emulator (OnCE™) circuitry

• Phase-locked Loop (PLL) based clock circuitry

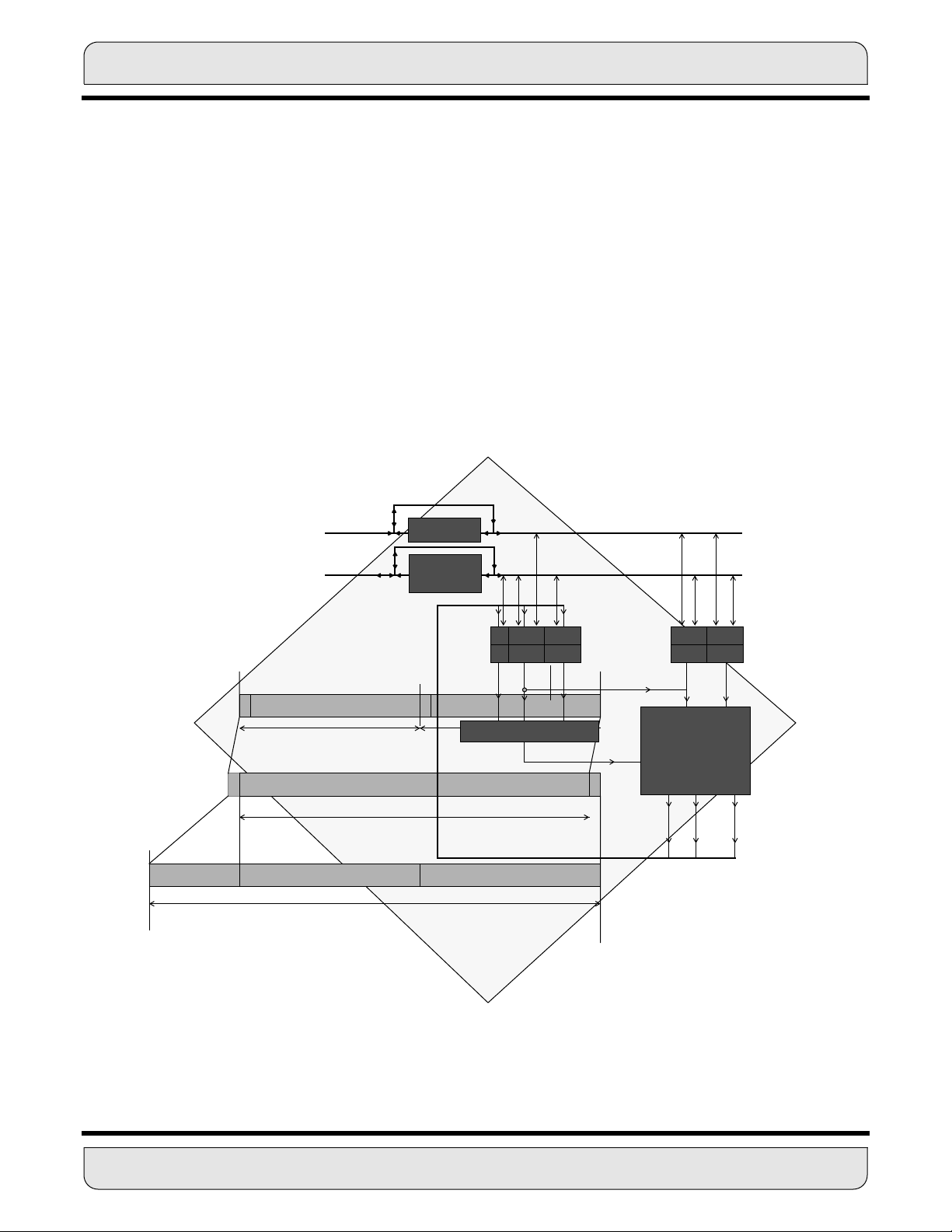

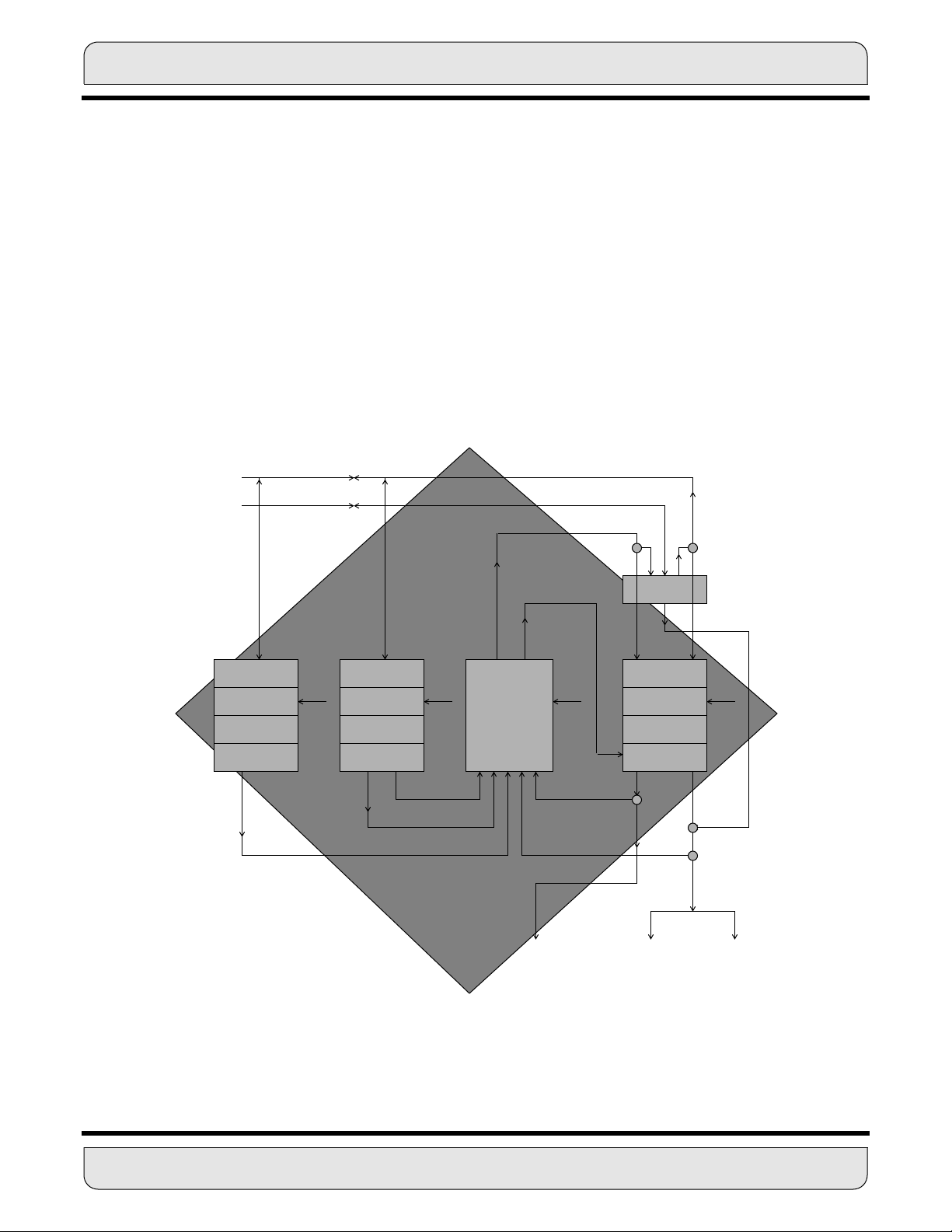

Figure 2-1 shows a block diagram of a typical DSP56K family processor, including the

central processing module and a nonspecific expansion area for memory and peripherals.

The following paragraphs give brief descriptions of each of the central components. Each

of the components is explained in detail in subsequent chapters.

2.2 DATA BUSES

The DSP56K central processing module is organized around the registers of three independent execution units: the PCU, the AGU, and the data ALU. Data movement between

the execution units occurs over four bidirectional 24-bit buses: the X data bus (XDB), the

Y data bus (YDB), the program data bus (PDB), and the global data bus (GDB). (Certain

instructions treat the X and Y data buses as one 48-bit data bus by concatenating them.)

Data transfers between the data ALU and the X data memory or Y data memory occur

over XDB and YDB, respectively. XDB and YDB are kept local on the chip to maximize

speed and minimize power dissipation. All other data transfers, such as I/O transfers with

peripherals, occur over the GDB. Instruction word prefetches occur in parallel over the

PDB.

The bus structure supports general register-to-register, register-to-memory, and memoryto-register data movement. It can transfer up to two 24-bit words and one 56-bit word in

the same instruction cycle. Transfers between buses occur in the internal bus switch.

MOTOROLA DSP56K CENTRAL ARCHITECTURE OVERVIEW 2 - 3

Page 31

PERIPHERAL

PINS

24-Bit 56K

Module

PERIPHERAL

MODULES

ADDRESS

GENERATION

UNIT

ADDRESS BUSES

PROGRAM

RAM/ROM

EXPANSION

X MEMORY

RAM/ROM

EXPANSION

YAB

XAB

PAB

Y MEMORY

RAM/ROM

EXPANSION

EXPANSION

AREA

EXTERNAL

ADDRESS

BUS

SWITCH

ADDRESS

INTERNAL

DATA

BUS

SWITCH

PLL

CLOCK

GENERATOR

PROGRAM

INTERRUPT

CONTROLLER

PROGRAM

DECODE

CONTROLLER

Program Control Unit

MODC/NMI

MODB/IRQB

MODA/IRQA

RESET

PROGRAM

ADDRESS

GENERA TOR

YDB

XDB

PDB

GDB

DATA ALU

24X24+56→56-BIT MAC

TWO 56-BIT ACCUMULATORS

BUS

CONTROL

EXTERNAL

DATA BUS

SWITCH

OnCE™

16 BITS

24 BITS

PORT A

CONTROL

DATA

Figure 2-1 DSP56K Block Diagram

2.3 ADDRESS BUSES

Addresses are specified for internal X data memory and Y data memory on two unidirectional 16-bit buses — X address bus (XAB) and Y address bus (YAB). Program memory

addresses are specified on the bidirectional program address bus (PAB). External mem-

2- 4 DSP56K CENTRAL ARCHITECTURE OVERVIEW

MOTOROLA

Page 32

DATA ALU

ory spaces are addressed over a single 16-bit unidirectional address bus driven by a

three-input multiplexer that can select the XAB, the YAB, or the PAB. Only one external

memory access can be made in an instruction cycle. There is no speed penalty if only one

external memory space is accessed in an instruction cycle. However, if two or three external memory spaces are accessed in a single instruction, there will be a one or two

instruction cycle execution delay, respectively.

A bus arbitrator controls external access.

2.3.1 Internal Bus Switch

Transfers between buses occur in the internal bus switch. The internal bus switch, which

is similar to a switch matrix, can connect any two internal buses without adding any pipeline delays. This flexibility simplifies programming.

2.3.2 Bit Manipulation Unit

The bit manipulation unit is physically located in the internal bus switch block because the

internal data bus switch can access each memory space. The bit manipulation unit performs bit manipulation operations on memory locations, address registers, control

registers, and data registers over the XDB, YDB, and GDB.

2.4 DATA ALU

The data ALU performs all of the arithmetic and logical operations on data operands. It

consists of four 24-bit input registers, two 48-bit accumulator registers, two 8-bit accumulator extension registers, an accumulator shifter, two data bus shifter/limiter circuits, and

a parallel, single-cycle, nonpipelined Multiply-Accumulator (MAC) unit.

2.5 ADDRESS GENERATION UNIT

The AGU performs all of the address storage and address calculations necessary to indirectly address data operands in memory. It operates in parallel with other chip resources

to minimize address generation overhead. The AGU has two identical address arithmetic

units that can generate two 16-bit addresses every instruction cycle. Each of the arithmetic units can perform three types of arithmetic: linear, modulo, and reverse-carry.

2.6 PROGRAM CONTROL UNIT

The program control unit performs instruction prefetch, instruction decoding, hardware

DO loop control, and interrupt (or exception) processing. It consists of three components:

the program address generator, the program decode controller, and the program interrupt

controller. It contains a 15-level by 32-bit system stack memory and the following six di-

MOTOROLA DSP56K CENTRAL ARCHITECTURE OVERVIEW 2 - 5

Page 33

MEMORY EXPANSION PORT (PORT A)

rectly addressable registers: the program counter (PC), loop address (LA), loop counter

(LC), status register (SR), operating mode register (OMR), and stack pointer (SP). The

16-bit PC can address 65,536 locations in program memory space.

There are four mode and interrupt control pins that provide input to the program interrupt

controller. The Mode Select A/External Interrupt Request A(MODA/IRQA

lect B/External Interrupt Request B (MODB/IRQB

and receive interrupt requests from external sources.

) pins select the chip operating mode

) and Mode Se-

The Mode Select C/Non-Maskable Interrupt (MODC/NMI

mode options and non-maskable interrupt input.

The RESET pin resets the chip. When it is asserted, it initializes the chip and places it in

the reset state. When it is deasserted, the chip assumes the operating mode indicated by

the MODA, MODB, and MODC pins.

2.7 MEMORY EXPANSION PORT (PORT A)

Port A synchronously interfaces with a wide variety of memory and peripheral devices

over a common 24-bit data bus. These devices include high-speed static RAMs, slower

memory devices, and other DSPs and MPUs in master/slave configurations. This variety

is possible because the expansion bus timing is programmable and can be tailored to

match the speed requirements of the different memory spaces. Not all DSP56K family

members feature a memory expansion port. See the individual device’s User’s Manual to

determine if a particular chip includes this feature.

2.8 ON-CHIP EMULATOR (OnCE)

DSP56K on-chip emulation (OnCE) circuitry allows the user to interact with the DSP56K

and its peripherals non-intrusively to examine registers, memory, or on-chip peripherals.

It provides simple, inexpensive, and speed independent access to the internal registers

for sophisticated debugging and economical system development.

) pin provides further operating

Dedicated OnCE pins allow the user to insert the DSP into its target system and retain

debug control without sacrificing other user accessible on-chip resources. The design

eliminates the costly cabling and the access to processor pins required by traditional emulator systems.

2.9 PHASE-LOCKED LOOP (PLL) BASED CLOCKING

The PLL allows the DSP to use almost any available external system clock for full-speed

operation, while also supplying an output clock synchronized to a synthesized internal

clock. The PLL performs frequency multiplication, skew elimination, and low-power

division.

2- 6 DSP56K CENTRAL ARCHITECTURE OVERVIEW

MOTOROLA

Page 34

SECTION 3

DATA ARITHMETIC LOGIC UNIT

MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 - 1

Page 35

SECTION CONTENTS

SECTION 3.1 DATA ARITHMETIC LOGIC UNIT .............................................3

SECTION 3.2 OVERVIEW AND DATA ALU ARCHITECTURE .......................3

3.2.1 Data ALU Input Registers (X1, X0, Y1, Y0) ........................................5

3.2.2 MAC and Logic Unit ............................................................................6

3.2.3 Data ALU A and B Accumulators ........................................................7

3.2.4 Accumulator Shifter ............................................................................ 9

3.2.5 Data Shifter/Limiter ............................................................................. 9

3.2.5.1 Limiting (Saturation Arithmetic) .................................................. 9

3.2.5.2 Scaling ........................................................................................ 10

SECTION 3.3 DATA REPRESENTATION AND ROUNDING ..........................10

SECTION 3.4 DOUBLE PRECISION MULTIPLY MODE .................................16

SECTION 3.5 DATA ALU PROGRAMMING MODEL .......................................19

SECTION 3.6 DATA ALU SUMMARY ..............................................................19

3 - 2 DATA ARITHMETIC LOGIC UNIT

MOTOROLA

Page 36

DATA ARITHMETIC LOGIC UNIT

3.1 DATA ARITHMETIC LOGIC UNIT

This section describes the operation of the Data ALU registers and hardware. It discusses data representation, rounding, and saturation arithmetic used within the Data

ALU, and concludes with a discussion of the programming model.

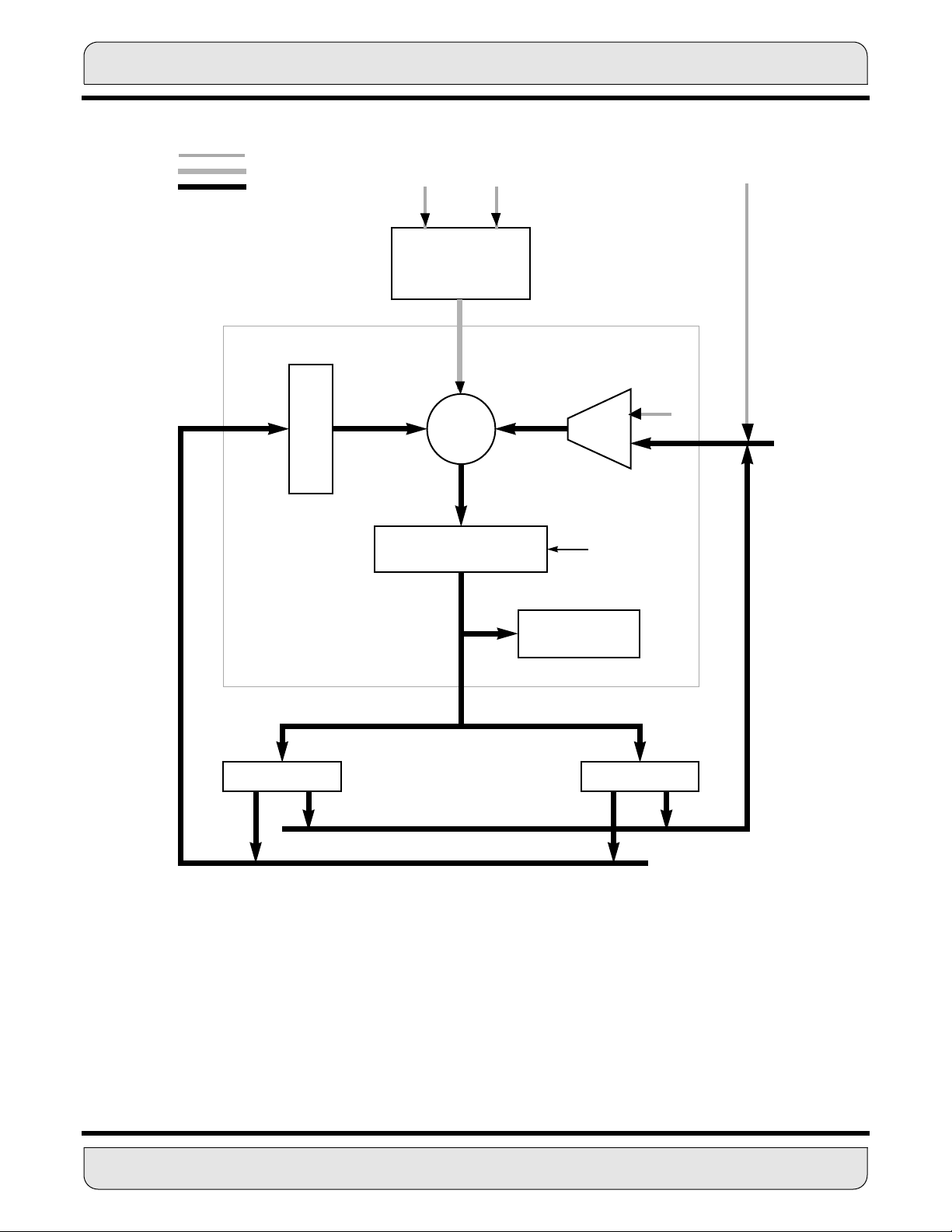

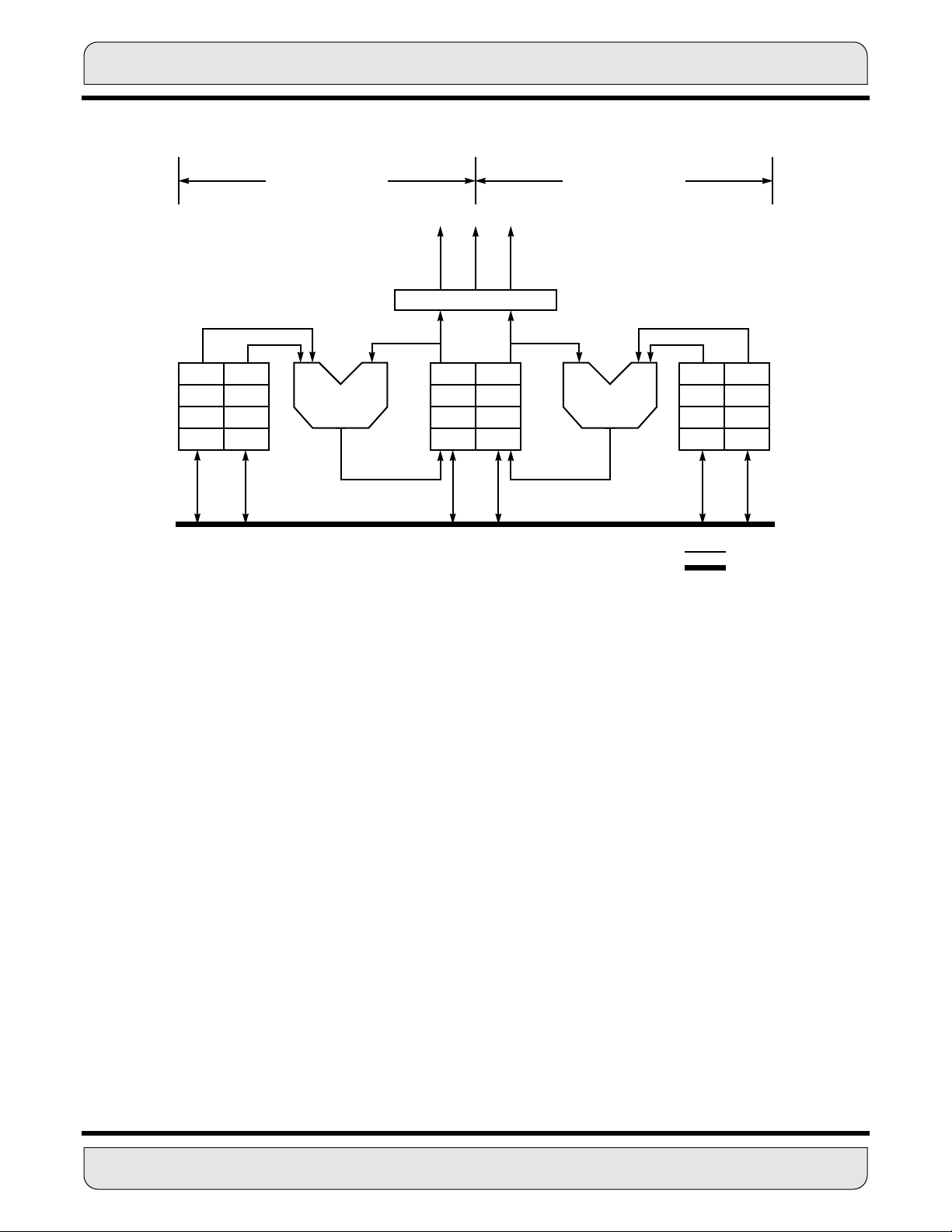

3.2 OVERVIEW AND DATA ALU ARCHITECTURE

As described in Section 2, The DSP56K family central processing module is composed

of three execution units that operate in parallel. They are the Data ALU, address generation unit (AGU), and the program control unit (PCU) (see Figure 3-1). These three units

are register oriented rather than bus oriented and interface over the system buses with

memory and memory-mapped I/O devices.

The Data ALU (see Figure 3-2) is the first of these execution units to be presented. It balances speed with the capability to process signals that have a wide dynamic range and

performs all arithmetic and logical operations on data operands.

The Data ALU registers may be read or written over the XDB and the YDB as 24- or 48bit operands. The source operands for the Data ALU, which may be 24, 48, or 56 bits,

always originate from Data ALU registers. The results of all Data ALU operations are

stored in an accumulator.

The 24-bit data words provide 144 dB of dynamic range. This range is sufficient for most

real-world applications since the majority of data converters are 16 bits or less – and certainly not greater than 24 bits. The 56-bit accumulator inside the Data ALU provides 336

dB of internal dynamic range so that no loss of precision will occur due to intermediate

processing. Special circuitry handles data overflows and roundoff errors.

The Data ALU can perform any of the following operations in a single instruction cycle:

multiplication, multiply-accumulate with positive or negative accumulation, convergent

rounding, multiply-accumulate with positive or negative accumulation and convergent

rounding, addition, subtraction, a divide iteration, a normalization iteration, shifting, and

logical operations.

The components of the Data ALU are:

• Four 24-bit input registers

• A parallel, single-cycle, nonpipelined multiply-accumulator/logic unit (MAC)

• Two 48-bit accumulator registers

• Two 8-bit accumulator extension registers

• An accumulator shifter

• Two data bus shifter/limiter circuits

MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 - 3

Page 37

PERIPHERAL

PINS

24 Bit 56K

Module

OVERVIEW AND DATA ALU ARCHITECTURE

PERIPHERAL

MODULES

ADDRESS

GENERATION

UNIT

PROGRAM

RAM/ROM

EXPANSION

YAB

XAB

PAB

X MEMORY

RAM/ROM

EXPANSION

Y MEMORY

RAM/ROM

EXPANSION

EXPANSION

AREA

EXTERNAL

ADDRESS

BUS

SWITCH

ADDRESS

INTERNAL

DATA

BUS

SWITCH

PLL

CLOCK

GENERATOR

PROGRAM

INTERRUPT

CONTROLLER

PROGRAM

DECODE

CONTROLLER

Program Control Unit

MODC/NMI

MODB/IRQB

MODA/IRQA

RESET

PROGRAM

ADDRESS

GENERA TOR

YDB

XDB

PDB

GDB

DATA ALU

24X24+56→56-BIT MAC

TWO 56-BIT ACCUMULATORS

BUS

CONTROL

EXTERNAL

DATA BUS

SWITCH

OnCE™

16 BITS

24 BITS

PORT A

CONTROL

DATA

Figure 3-1 DSP56K Block Diagram

The following paragraphs describe each of these components and provide a description

of data representation, rounding, and saturation arithmetic.

3 - 4 DATA ARITHMETIC LOGIC UNIT

MOTOROLA

Page 38

OVERVIEW AND DATA ALU ARCHITECTURE

3.2.1 Data ALU Input Registers (X1, X0, Y1, Y0)

X1, X0, Y1, and Y0 are four 24-bit, general-purpose data registers. They can be treated

as four independent, 24-bit registers or as two 48-bit registers called X and Y, developed

by concatenating X1:X0 and Y1:Y0, respectively. X1 is the most significant word in X and

Y1 is the most significant word in Y. The registers serve as input buffer registers between

the XDB or YDB and the MAC unit. They act as Data ALU source operands and allow

new operands to be loaded for the next instruction while the current instruction uses the

X DATA BUS

Y DATA BUS

2424

X0

X1

Y0

Y1

56

SHIFTER

24 24

MULTIPLIER

ACCUMULATOR,

ROUNDING,

AND LOGIC UNIT

56

A (56)

B (56)

5656

SHIFTER/LIMITER

56

24

24

Figure 3-2 Data ALU

MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 - 5

Page 39

OVERVIEW AND DATA ALU ARCHITECTURE

register contents. The registers may also be read back out to the appropriate data bus to

implement memory-delay operations and save/restore operations for interrupt service

routines.

3.2.2 MAC and Logic Unit

The MAC and logic unit shown in Figure 3-3 conduct the main arithmetic processing and

perform all calculations on data operands in the DSP.

For arithmetic instructions, the unit accepts up to three input operands and outputs one

56-bit result in the following form: extension:most significant product:least significant

product (EXT:MSP:LSP). The operation of the MAC unit occurs independently and in parallel with XDB and YDB activity, and its registers facilitate buffering for Data ALU inputs

and outputs. Latches on the MAC unit input permit writing an input register which is the

source for a Data ALU operation in the same instruction.

The arithmetic unit contains a multiplier and two accumulators. The input to the multiplier

can only come from the X or Y registers (X1, X0, Y1, Y0). The multiplier executes 24-bit

x 24-bit, parallel, twos-complement fractional multiplies. The 48-bit product is right justified and added to the 56-bit contents of either the A or B accumulator. The 56-bit sum is

stored back in the same accumulator (see Figure 3-3). An 8-bit adder, which acts as an

extension accumulator for the MAC array, accommodates overflow of up to 256 and allows the two 56-bit accumulators to be added to and subtracted from each other. The

extension adder output is the EXT portion of the MAC unit output. This multiply/accumulate operation is not pipelined, but is a single-cycle operation. If the instruction specifies a

multiply without accumulation (MPY), the MAC clears the accumulator and then adds the

contents to the product.

In summary, the results of all arithmetic instructions are valid (sign-extended and zerofilled) 56-bit operands in the form of EXT:MSP:LSP (A2:A1:A0 or B2:B1:B0). When a 56bit result is to be stored as a 24-bit operand, the LSP can be simply truncated, or it can be

rounded (using convergent rounding) into the MSP.

Convergent rounding (round-to-nearest) is performed when the instruction (for example,

the signed multiply-accumulate and round (MACR) instruction) specifies adding the multiplier’s product to the contents of the accumulator. The scaling mode bits in the status

register specify which bit in the accumulator shall be rounded.

The logic unit performs the logical operations AND, OR, EOR, and NOT on Data ALU registers. It is 24 bits wide and operates on data in the MSP portion of the accumulator. The

LSP and EXT portions of the accumulator are not affected.

3 - 6 DATA ARITHMETIC LOGIC UNIT

MOTOROLA

Page 40

OVERVIEW AND DATA ALU ARCHITECTURE

24 BITS

48 BITS

56 BITS

X0,X1,

Y0, OR Y1

24-BITx24-BIT

FRACTIONAL

MULTIPLIER

S

H

I

F

T

E

R

CONVERGENT - ROUNDING

FORCING FUNCTION

X0,X1,

Y0, OR Y1

+

–

56 - BIT

ARITHMETIC AND

LOGIC UNIT

SCALING

MODE BITS

R

X0,X1,

Y0, OR Y1

24

CONDITION

CODE GENERATOR

ACCUMULATOR A ACCUMULATOR B

Figure 3-3 MAC Unit

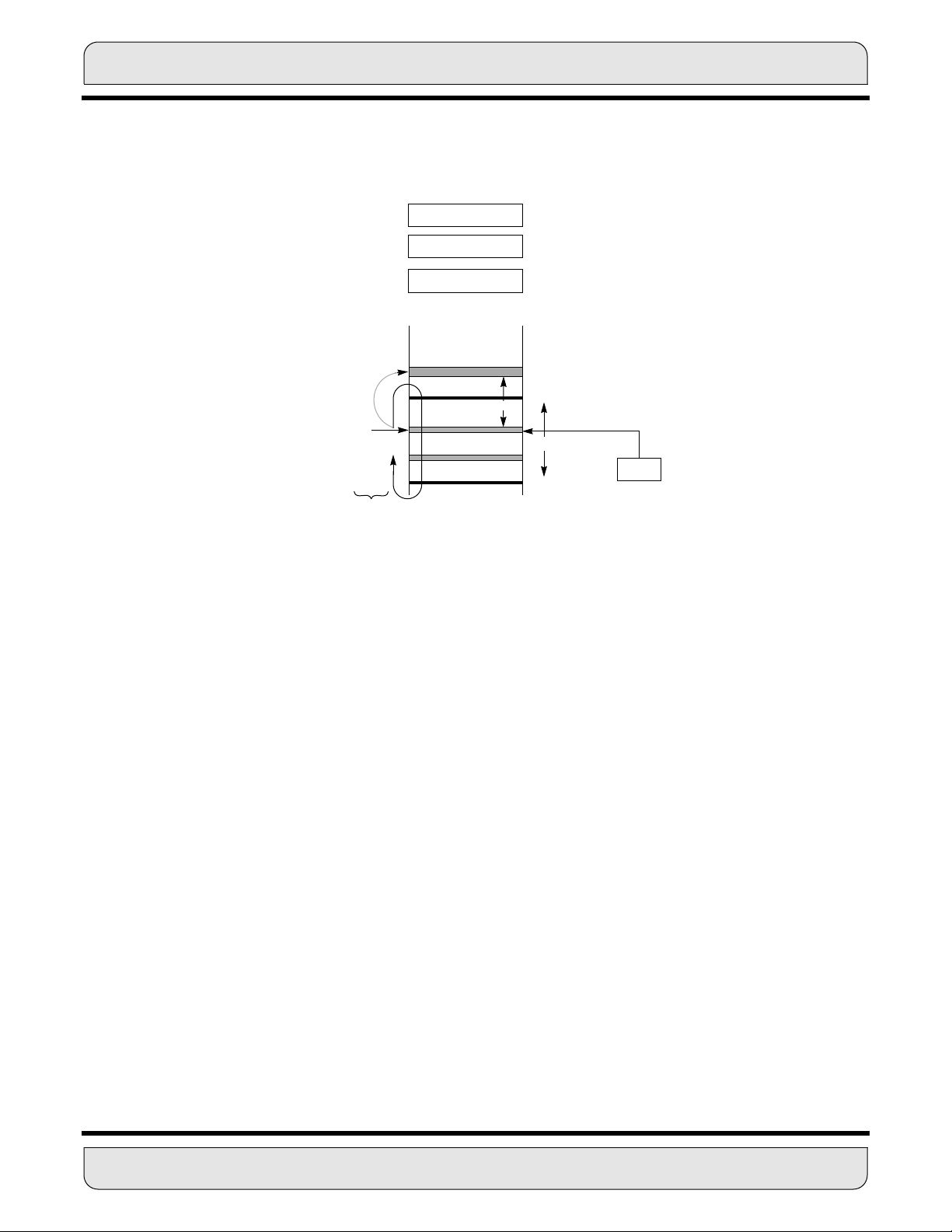

3.2.3 Data ALU A and B Accumulators

The Data ALU features two general-purpose, 56-bit accumulators, A and B. Each consists of three concatenated registers (A2:A1:A0 and B2:B1:B0, respectively). The 8-bit

sign extension (EXT) is stored in A2 or B2 and is used when more than 48-bit accuracy is

needed; the 24-bit most significant product (MSP) is stored in A1 or B1; the 24-bit least

MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 - 7

Page 41

OVERVIEW AND DATA ALU ARCHITECTURE

DATA ALU ACCUMULATOR REGISTERS

Accumulator A

A2 A1 A0

*

7023 023 0

Accumulator B

55 055 0

B2

*

7023 023 0

B1 B0

EXT MSP LSP

*Read as sign extension bits, written as don’t care.

EXT MSP LSP

Figure 3-4 DATA ALU Accumulator Registers

significant product (LSP) is stored in A0 or B0 as shown in Figure 3-4.

Overflow occurs when a source operand requires more bits for accurate representation

than are available in the destination. The 8-bit extension registers offer protection

against overflow. In the DSP56K chip family, the extreme values that a word operand

can assume are - 1 and + 0.9999998. If the sum of two numbers is less than - 1 or

greater than + 0.9999998, the result (which cannot be represented in a 24 bit word operand) has underflowed or overflowed. The 8-bit extension registers can accurately represent the result of 255 overflows or 255 underflows. Whenever the accumulator extension

registers are in use, the V bit in the status register is set.

Automatic sign extension occurs when the 56-bit accumulator is written with a smaller

operand of 48 or 24 bits. A 24-bit operand is written to the MSP (A1 or B1) portion of the

accumulator, the LSP (A0 or B0) portion is zero filled, and the EXT (A2 or B2) portion is

sign extended from MSP. A 48-bit operand is written into the MSP:LSP portion (A1:A0 or

B1:B0) of the accumulator, and the EXT portion is sign extended from MSP. No sign

extension occurs if an individual 24-bit register is written (A1, A0, B1, or B0).When either

A or B is read, it may be optionally scaled one bit left or one bit right for block floatingpoint arithmetic. Sign extension can also occur when writing A or B from the XDB and/or

YDB or with the results of certain Data ALU operations (such as the transfer conditionally

(Tcc) or transfer Data ALU register (TFR) instructions).

Overflow protection occurs when the contents of A or B are transferred over the XDB and

YDB by substituting a limiting constant for the data. Limiting does not affect the content

of A or B – only the value transferred over the XDB or YDB is limited. This overflow protection occurs after the contents of the accumulator has been shifted according to the

scaling mode. Shifting and limiting occur only when the entire 56-bit A or B accumulator

is specified as the source for a parallel data move over the XDB or YDB. When individual

registers A0, A1, A2, B0, B1, or B2 are specified as the source for a parallel data move,

3 - 8 DATA ARITHMETIC LOGIC UNIT

MOTOROLA

Page 42

OVERVIEW AND DATA ALU ARCHITECTURE

shifting and limiting are not performed.

3.2.4 Accumulator Shifter

The accumulator shifter (see Figure 3-3) is an asynchronous parallel shifter with a 56-bit

input and a 56-bit output that is implemented immediately before the MAC accumulator

input. The source accumulator shifting operations are as follows:

• No Shift (Unmodified)

• 1-Bit Left Shift (Arithmetic or Logical) ASL, LSL, ROL

• 1-Bit Right Shift (Arithmetic or Logical) ASR, LSR, ROR

• Force to zero

3.2.5 Data Shifter/Limiter

The data shifter/limiter circuits (see Figure 3-3) provide special post-processing on data

read from the Data ALU A and B accumulators out to the XDB or YDB. There are two independent shifter/limiter circuits (one for XDB and one for the YDB); each consists of a

shifter followed by a limiting circuit.

3.2.5.1 Limiting (Saturation Arithmetic)

The A and B accumulators serve as buffer registers between the MAC unit and the XDB

and/or YDB. They act both as Data ALU source and destination operands.Test logic exists

in each accumulator register to support the operation of the data shifter/limiter circuits.

This test logic detects overflows out of the data shifter so that the limiter can substitute

one of several constants to minimize errors due to the overflow. This process is called saturation arithmetic

The Data ALU A and B accumulators have eight extension bits. Limiting occurs when the

extension bits are in use and either A or B is the source being read over XDB or YDB. If

the contents of the selected source accumulator can be represented without overflow in

the destination operand size (i.e., accumulator extension register not in use), the data limiter is disabled, and the operand is not modified. If contents of the selected source

accumulator cannot be represented without overflow in the destination operand size, the

data limiter will substitute a limited data value with maximum magnitude (saturated) and

with the same sign as the source accumulator contents: $7FFFFF for 24-bit or $7FFFFF

FFFFFF for 48-bit positive numbers, $800000 for 24-bit or $800000 000000 for 48-bit negative numbers. This process is called saturation arithmetic. The value in the accumulator

register is not shifted and can be reused within the Data ALU. When limiting does occur,

a flag is set and latched in the status register.Two limiters allow two-word operands to be

limited independently in the same instruction cycle. The two data limiters can also be com-

MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 - 9

Page 43

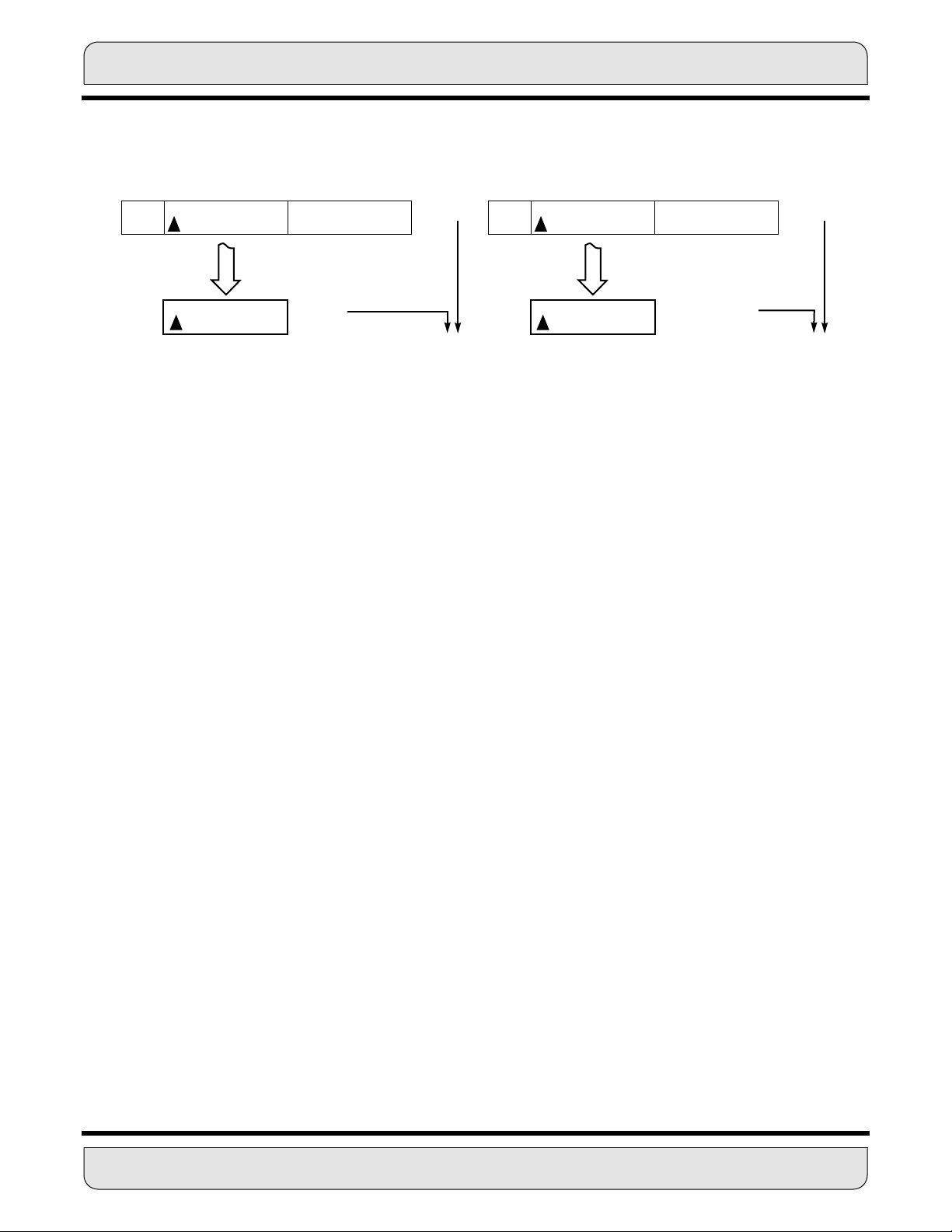

DATA REPRESENTATION AND ROUNDING

WITHOUT LIMITING* WITH LIMITING*

55 0

0 . . . 0 1 0 0 . . . . . . . . . . . 0 0 0 0 . . . . . . . . . . . . 0 0

7 0 23 0 23 0

MOVE A1, X0

1 0 0 . . . . . . . . . . . 0 0 0 1 1 . . . . . . . . . . . 1 1

23 0 23 0

* Limiting automatically occurs when the 56 - bit operands A or B (not A2, A1, A0, B2, B1, or B0) are read. The contents

of A or B are NOT changed.

X0 = -1.0 X0 = +0.9999999

A = +1.0

|ERROR| = 2.0

55 0

0. . . 0 1 0 0 . . . . . . . . . . . 0 0 0 0 . . . . . . . . . . . . 0 0

7 0 23 0 23 0

MOVE A, X0

|ERROR| = .0000001

A = +1.0

Figure 3-5 Saturation Arithmetic

bined to form one 48-bit data limiter for long-word operands.

For example, if the source operand were 01.100 (+ 1.5 decimal) and the destination reg-

ister were only four bits, the destination register would contain 1.100 (- 1.5 decimal) after

the transfer, assuming signed fractional arithmetic. This is clearly in error as overflow has

occurred. To minimize the error due to overflow, it is preferable to write the maximum

(“limited”) value the destination can assume. In the example, the limited value would be

0.111 (+ 0.875 decimal), which is clearly closer to + 1.5 than - 1.5 and therefore introduces less error.

Figure 3-5 shows the effects of saturation arithmetic on a move from register A1 to register X0. The instruction “MOVE A1,X0” causes a move without limiting, and the instruction

“MOVE A,X0” causes a move of the same 24 bits with limiting. The error without limiting

is 2.0; whereas, it is 0.0000001 with limiting. Table 3-1 shows a more complete set of

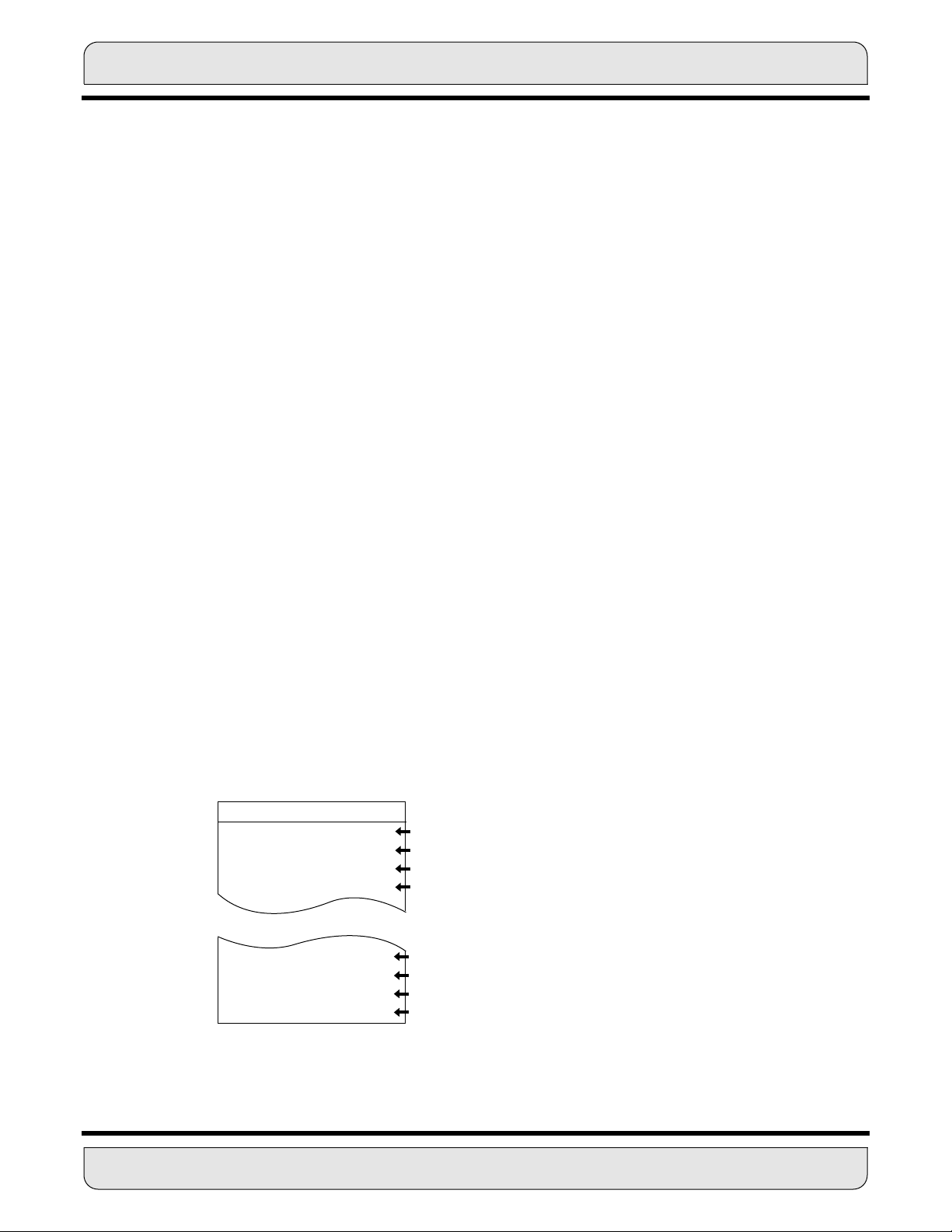

limiting situations.